Received January 21, 2021, accepted January 25, 2021, date of publication January 29, 2021, date of current version February 16, 2021. *Digital Object Identifier* 10.1109/ACCESS.2021.3055650

# Systematic Approach for State-of-the-Art Architectures and System-on-Chip Selection for Heterogeneous IoT Applications

RAMESH KRISHNAMOORTHY<sup>®</sup><sup>1</sup>, (Member, IEEE), KALIMUTHU KRISHNAN<sup>®</sup><sup>1</sup>, BHARATIRAJA CHOKKALINGAM<sup>®</sup><sup>2</sup>, (Senior Member, IEEE), SANJEEVIKUMAR PADMANABAN<sup>®</sup><sup>3</sup>, (Senior Member, IEEE), ZBIGNIEW LEONOWICZ<sup>®</sup><sup>4</sup>, (Senior Member, IEEE), JENS BO HOLM-NIELSEN<sup>®</sup><sup>3</sup>, AND MASSIMO MITOLO<sup>®</sup><sup>5</sup>, (Fellow, IEEE)

<sup>1</sup>Department of Electronics and Communication Engineering, SRM Institute of Science and Technology, Chennai 603203, India <sup>2</sup>Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Chennai 603203, India <sup>3</sup>Center for Bioenergy and Green Engineering, Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark <sup>4</sup>Faculty of Electrical Engineering, Wroclaw University of Science and Technology, 50370 Wroclaw, Poland <sup>5</sup>School of Integrated Design, Engineering, and Automation, Irvine Valley College, Irvine, CA 92618, USA

Corresponding authors: Ramesh Krishnamoorthy (rameshk.tn@gmail.com) and Sanjeevikumar Padmanaban (san@et.aau.dk)

This work was supported by the Visvesvaraya PhD Scheme, Ministry of Electronics and Information Technology (MeitY), Government of India <MEITY-PHD-2822>.

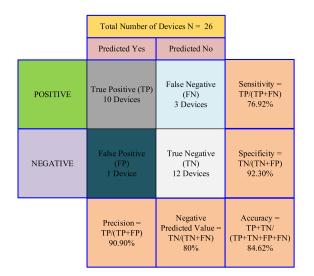

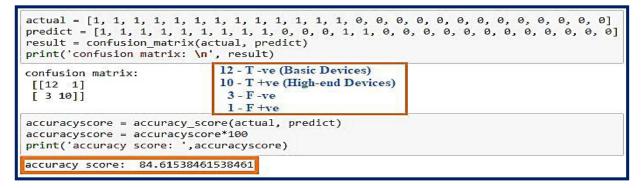

**ABSTRACT** The Internet of Things (IoT) refers to a network of physical devices, which collects data and processes into a system without human intervention. In the commercialized market, IoT architectures are upgrading day by day to reduce data transmission costs, latency, and bandwidth usage for various application requirements. The extensively available IoT architectures and their specification resist the researchers to select a system-on-chip (SoC) for heterogeneous IoT applications. This paper seeks to comprehend the various IoT device specifications and their characteristics to support multiple applications. Moreover, microprocessor architectures and their components are detailed to facilitate developer knowledge in advanced methodology and technology. The various instructions set architectures (ISA) are implemented in a Zynq-7000 (xc7Zz20clg484-1) FPGA device to examine the feasibility of design space requirements for real-time hardware execution. To select specific system-on-chip (SoC) architecture for heterogeneous IoT applications, a genetic algorithm (GA) based optimization method is implemented in MATLAB. The proposed algorithm identifies the optimized SoC architecture concerning device parameters such as a clock, cache, RAM space, external storage, network support, etc. Further, the confusion matrix method evaluates the proposed algorithm's accuracy, which yields 84.62% accuracy. The outcome of SoCs attained through the GA are tested by analyzing their execution time and performance using various evaluation benchmarks. This article helps the researchers and field engineers to comprehend the microarchitecture device configurations and to identify the superior SoC for next-generation IoT practices.

**INDEX TERMS** Internet of Things, microprocessors, system-on-chip, heterogeneous architectures, and edge computing.

## I. INTRODUCTION

The IoT refers to a universal presence of interconnected physical devices for a wide range of applications, such as consumer electronics, smart healthcare systems, and intelligent vehicles [1]–[3]. The IoT enabled gateway devices collects

The associate editor coordinating the review of this manuscript and approving it for publication was Ramazan Bayindir<sup>(D)</sup>.

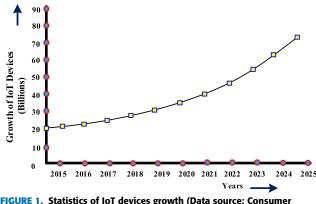

the necessary data from sensors or edge devices and sends to the cloud without human intervention [4]. Fig. 1 represents the number of IoT devices connected globally for upcoming years (2015-25). The data interpretation observed that several IoT devices installed for 2025 expect to grow more than fifty percent [5]. The critical requirement for using primary tools is to keep the bill of materials (BoM) as low as possible by utilizing low-cost microcontrollers with in-built memory

FIGURE 1. Statistics of IoT devices growth (Data source: Consumer electronics - 16 November 2016 [2]).

and storage. Based on an accurate study of device specifications, including a clock, RAM, Flash, Cache, power, and operating temperature, users can choose high-end devices. Besides, the advanced support features like camera, security, and audio/video support the devices should be considered for safety-critical applications. The SoC devices are semiconductor ICs with integrated components that enable the chip to operate as a standalone system. SoCs are more capable of increasing the system performance. The SoC lean towards to minimizing the latency delivered through various elements that are deliberately placed on the IoT boards to reduce the interference and interconnection delays and also to speed up the data transmission practice.

## A. MOTIVATION

To develop the real-world embedded system SoC is inevitable for broad range of applications. The designers should follow the set of guidelines for selecting SoC devices. It is not necessary to find the proper match among the devices features and requirements during the initial stage. A small change in the addition of peripheral chips or requirements will impact the cost associated with the device. The evaluation process of several IoT devices should begin with categorizing the devices into basic, medium and advanced levels as determined by the application. The current researches are mainly focusing on the design of IoT applications for data sensing, centralized management, and automation services by making use of well-known devices familiar to the specific research group. In the industrial market, wide range of SoC devices are available, delivering high performance for diverse IoT applications. The recent research efforts focus on hardware acceleration on IoT and provided comprehensive survey of hardware devices for embedded prototyping. However, there is currently very little research that characterizes SoC device selection for IoT applications. This research gap motivates the author to develop a systematic methodology for optimal SoC device selection.

## B. BACKGROUND ON IoT SoC

The SoC devices are semiconductor ICs with integrated components that enable the chip to operate as a standalone system. The SoCs has many features integrated on a single-chip, which is also capable of running an operating system on a smart device [6]–[8]. The microcontroller is the core of SoC technology, which is programmable and used for a wide range of embedded real-time applications such as home automation, smart appliances, security applications, etc. SoC devices are customizable, cost-effective, and more reliable. In contrast, advanced devices serve as a gateway to perform translation between different network protocols. These devices will manage the application control logic and wireless area network (WAN) interface. A smart home application where users can remotely monitor and control the status of appliances, whether turned ON or OFF, is achieved through necessary IoT based application development. In an industrial environment, the boiler's temperature can be remotely monitored and controlled using IoT devices.

The IoT devices embedded in the edge nodes are 32-bit or 64-bit microcontroller units (MCUs), which has versatile features in a single chip [9], [10]. The MCUs have more number of General-Purpose Input/Output (GPIO) signals for sensors integration. The wide range of embedded applications such as home appliances, wearable devices, building management systems and industrial automation, etc. makes use of IoT devices. Microcontroller's potential growth in smart appliances may frequently update the cloud server's data through the edge node. An edge node is a centralized node; it collects the data from devices and processes it to the cloud server. The evolution of the IoT increases the acquired and transmitted data considerably, which poses latency and bandwidth challenges. As IoT devices usage is rising; the devices should operate with low power and low latency. The devices and sensors placed under varying environments are battery-operated. Therefore, to preserve the battery lifecycle, IoT devices have to steadily wakeup from sleep mode to fetch new information. In case the device has less chance for data sharing, the device becomes dormant and runs at a slow speed [11]. Many IoT devices operate through a wireless connection. They utilize significantly less bandwidth, but due to more devices, they share the internet, and hence more bandwidth is required. That is, the amount of data collected and transmitted by the IoT devices will increase the bandwidth. For instance, video processing applications may significantly pose higher bandwidth. To alleviate the bandwidth challenges, the designer should consider the system won't always transmit or receive the data only through a wireless connection. These challenges force the embedded edge node resource constraints like complexity, battery capacity, cost, etc. Current research work progress on how IoT devices are connected and issues in establishing the device to device communication. But there are minimal research articles focused on addressing the critical microprocessor architecture device characteristics and selection requirements needed to design and develop applications.

Edge computing's impact is to reduce the latency and the data processing carried out at the cloud server via either Wi-Fi, 4G/5G networks to enable efficient networking [12]. Ching Chen et al. presented intelligent IoT gateway architecture using multiple collaborative microcontrollers by applying master-slave principles [13]. The master MCU performs the local gateway computing there by the IoT system, saves the bandwidth costs, and reduces the communication response time between multiple devices. Here the gateway is realized by combining the multi-MCU design with a fieldprogrammable gate array (FPGA) [14]. Increasing the data processing abilities of the cloud server does not shell out an increase in network latency. But it utilizes very minimal computational resources at the edge, which improves performance [15]. The more significant number of computational resources used in application domains has laid the path for designing the system by utilizing application-specific multicore processors to achieve high-performance requirements. Tiago Gomes et al. concluded that endpoint devices might significantly reduce computational resource availability by deploying a heterogeneous architecture-based edge device to handle parallel tasks [16], [17]. Each pipeline stage's activity rate will produce significant improvements in a pipelined processor [18]. Maryam et al. had proposed a low-cost instruction pre-fetching scheme with ultra-low power multicore processors. This mechanism allows the cache hit rate of 95%, thereby improving the performance double-times [19]. Due to more number of pipeline stages, the prefetching of instruction from the memory and processing through the queue enables the processors to achieve high performance. The modern processors like ARMv9 uses five stages of pipeline such as fetch, decode, execute, memory and writeback. Tobias Strauch has developed a thread controller using the ARM Cortex M3 processor with the supported peripherals. The standard CPU architecture may be transformed into multi-threaded CPU architecture by a well-known C-Slow Retiming (CSR) design transformation method [20]. The multithreaded CPU architectures with System Hyper Pipeline (SHP) method executes multiple threads, while the CSR method fails due to its limitations. In addition to scheduling threads in a dynamic fashion, the SHP method combines with parallel processing and CSR methods, which will deliver higher performance for critical tasks [21].

# C. STRUCTURE AND CONTRIBUTION OF THE ARTICLE

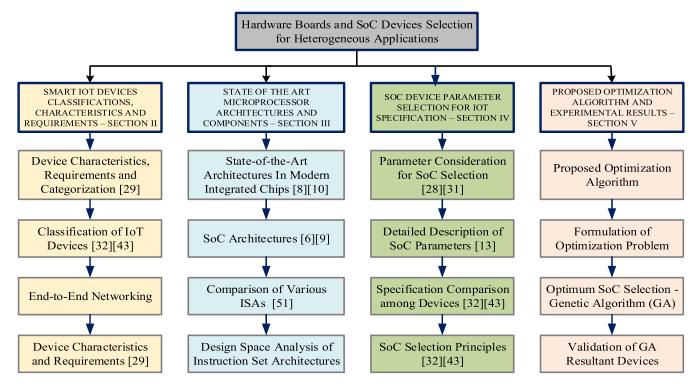

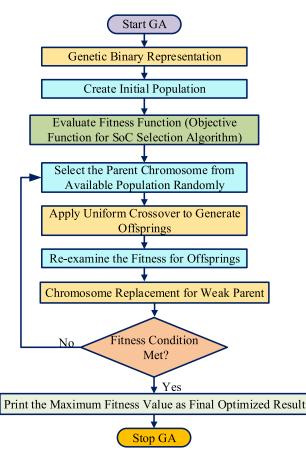

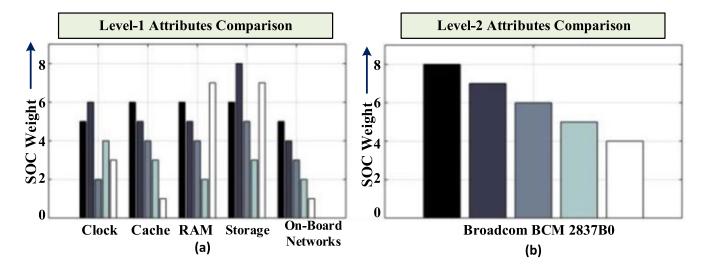

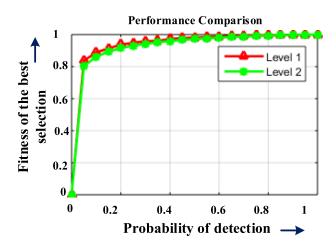

The overview of the proposed work is shown in Fig. 2. In comparison, this paper aims to develop a genetic algorithm based optimization technique to identify the precise SoC for IoT applications. The main contribution of the paper as follows:

- This paper aims to provide a systematic methodology for the research community to determine the SoC selection requirements for IoT applications.

- We categorized the IoT devices based on basic, medium, and advanced devices, related the device characteristics and requirements with practical use-cases.

- We propose the design space investigation of various processor architecture. The results attained significantly

proved that ARM architecture supports for fastest memory and I/O handling capability, registers utilization, and signal processing functionalities.

- This paper utilizes genetic algorithm optimization for optimal device selection. The genetic algorithm produces the results based on the SoC devices database loaded within the MATLAB.

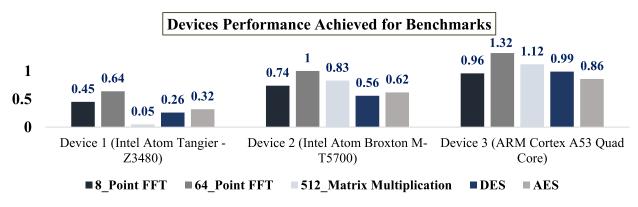

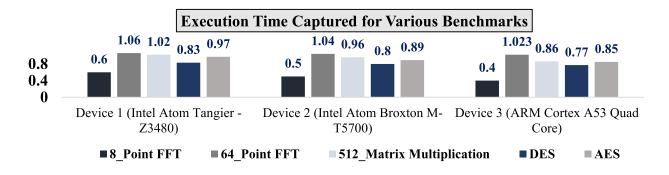

- In this work, the GA results with multiple devices. The benchmark execution time and performance are experimented and tabulated to ensure the proposed work's effectiveness.

- The accuracy estimation for the proposed optimization algorithm is evaluated using the confusion matrix method and python programming model for the dataset of 26 devices.

# D. RELATED WORKS

The existing works are focused on data sensing and image processing applications through IoT devices to enable the user to receive the information on time [22]-[24]. The IoT devices support for capturing of data from the environment without the intervention of the user. Linguaglossa et al. has proposed the extensive overview of the hardware architectures for network function virtualization (NFV) to provide abstractions for accessing components and physical resources into the ecosystem [25]. P. Shantharama et al. have demonstrated the Intel QAT hardware acceleration that performs image compression and decompression and achieved high network bandwidth [26], [27]. The work in [27] surveyed the emerging hardware platforms for executing softwarized network functions. P. Shantharama et al. has surveyed the emerging hardware platforms for executing softwarized network functions. There are few works in [25]-[27] that provides a comprehensive survey of hardware accelerated platforms associated for architectural enhancement by reducing the core utilization and expanding the ISA and cache memory access. Table 1 shows the works carried out in various literature. Initially, Kansakar et al. proposed a design space investigation methodology for choosing microarchitecture configurations for high-performance IoT processors. PARSEC and SPLASH2 benchmarks were taken and discussed the importance of low-power optimized processor design to evaluate the design space. The processor selection approach remained carried out using greedy search methods. The proposed processor configuration utilizes only 3% to 5% of the overall design space, significantly increasing the average speed up on processor design [28]. The work in [28] is significant towards the processor selection constraint. However, the greedy algorithms be unsuccessful to find the globally optimal solution for the reason that they do not consider all the data. Adegbija et al. seek to comprehend the microarchitectural characteristics to perform edge computing in the IoT. The four different CPU cores are considered and analyzed the impact of the stagnant energy on overall energy consumption using the matrixTrans\_128 application benchmark. The power gating technique reduces the leakage power consumption by

FIGURE 2. The overview of proposed work.

| TABLE 1. | Contribution | of works i | in existing | literatures. |

|----------|--------------|------------|-------------|--------------|

|----------|--------------|------------|-------------|--------------|

| Contributions                            | This<br>Paper | Kansakar <i>et.al</i><br>[22] | Tosiron <i>et.al</i><br>[23] | Kansakar <i>et.al</i><br>[24] | Tosiron <i>et.al</i><br>[25] | Mike <i>et.al</i><br>[26] |

|------------------------------------------|---------------|-------------------------------|------------------------------|-------------------------------|------------------------------|---------------------------|

| Design Space Exploration                 | ✓             | √                             | √                            | √                             | ✓                            | ×                         |

| Benchmarks Utilized                      | ✓             | ✓                             | ✓                            | ✓                             | ✓                            | ×                         |

| Survey of Processor Architectures        | √             | √                             | √                            | √                             | √                            | ✓                         |

| Performance Optimization                 | √             | √                             | √                            | √                             | √                            | √                         |

| Execution Time Estimation                | √             | √                             | ×                            | √                             | ×                            | ×                         |

| IoT Application Overview                 | √             | √                             | √                            | ✓                             | ✓                            | ✓                         |

| Edge Computing                           | √             | ×                             | √                            | ×                             | ✓                            | ✓                         |

| Survey of IoT Device Categories          | √             | ×                             | ✓                            | ×                             | ×                            | ✓                         |

| Optimum Device Selection                 | √             | ×                             | ×                            | ×                             | ×                            | ×                         |

| Future Trends and Research<br>Challenges | ~             | ✓                             | $\checkmark$                 | ×                             | ×                            | 1                         |

shutting off the unused blocks, where the leakage power is reduced strictly by 95%. The performance and efficiency of conf1, conf2, and conf3 normalized to conf4 for all the benchmarks were computed in a non-energy constrained system. Results reveal that conf1, conf2, and conf3 degrade the performance approximately to 171x, 17x, and 8x, respectively. Compared to conf4, conf1 degraded the efficiency by 33x, while conf2 and conf3 degraded the efficiency by 33x, while conf2 and conf3 degraded the efficiency by 4x. These results reveal the significant improvements achieved by using the larger configurations [29]. The work in [29] provides a foundation for advanced research to understand application requirements and architectures that support edge computing. However, the paper deals only with four specific hardware boards to analyze the benchmark implementation results. Kansakar *et al.* has utilized exhaustive and greedy search algorithms for design space investigation and parameter optimization for multicore architectures. The design space estimation was performed using the cycle-accurate simulator and shared-memory computer benchmarks. The proposed algorithm using greedy search yields the best settings of 1.35% to 3.69% compared to a fully exhaustive search approach. The proposed methodology produces a better solution during the search phase upon considering more evaluation parameters [30]. The work in [30] followed the same approach presented in [28]. Moreover, the design space estimation for the considered benchmarks are again evaluated using the greedy algorithm which is computationally slow when compared to the evolutionary algorithms. Adegbija *et al.* presented a

**IEEE** Access

comprehensive overview of architectures that explore the research challenges empowering the right provisioned architecture for IoT edge device computing [31].

The rest of the paper is organized as follows: In section II, this paper explores the smart IoT device characteristics and requirements. We discuss the comprehensive study of several microprocessor architectures and their internal components. In section III, we perform the design space analysis of various architectural configurations. In Section IV, we present the complete core factors that need to considered while selecting SoC configurations to improve the systems overall performance. Several microcontrollers available in the market with unique features and competitive improvements in their packing size, built-in communication interfaces, and memory capacity. It makes them adequate and inadequate for specific applications. Thus, repeatedly to circumvent the problem that comes while choosing the right microcontroller, developers usually choose the microcontrollers well-known. Finally, in section V, this paper presents our optimum algorithm for SoC selection, and the corresponding experimental results.

# II. SMART IOT DEVICES CLASSIFICATIONS, CHARACTERISTICS AND REQUIREMENTS

The commercially available IoT devices are categorized as a basic, medium, and advanced, and their supported features are shown in Table 2. The low-end IoT devices operate with clock frequency ranging from 8 MHz to 400 MHz. These devices access the internal RAM ranging from 2 KB to 512 KB without cache memory. Flash memory supports to the range of 32 KB to 8 MB. These low-end devices do not have inbuilt advanced features, including security, camera, and audio/video. These devices are constrained to operate in windows or Linux OS environment with limited resources. Examples of basic devices are Atmel SmartD21, ESP32 Azure, and Libelium Waspmote.

However, for sensing and actuating applications, these devices are primarily used. In contrast, the medium-range IoT devices function with clock frequency from 1 GHz to 2.13 GHz. These devices contain 16 KB of level1 cache and 512 KB of level2 cache and involve a maximum of up to 2 MB of on-chip cache. These devices support internal RAM access from 512 MB to 2 GB (DDR3) and up to 4 GB of flash memory. The middle-end IoT devices, support advanced features like security, camera, audio/video processing, and consist of one or more communication interfaces, unlike basic devices. Examples for medium devices are Cubie Board, BeagleBone Black, and Intel Edison Compute Module. Considering highend IoT devices, they operate with clock frequency ranging from 1 GHz to 2.13 GHz.

The devices consist of 16 KB of level1 and a maximum of 2 MB of on-chip Cache. It supports internal RAM access from 512 MB to 4 GB (DDR3) and up to 16 GB of eMMC memory. All the commercially available devices may support advanced features like security, camera, and audio/video in the high-end IoT devices. These devices are familiar with their onboard communication network support such as Ethernet, Wi-Fi, and

Bluetooth, etc. Also, these can process multimedia applications using a camera serial interface (CSI) module and execute complex machine learning algorithms. These advanced devices are IoT gateways due to a high level of onboard features, making them more effective in performing intelligent data analytics at the edge network. These devices are useful for applications including media computer vision, virtual reality (VR), augmented reality (AR), industrial automation, etc.

The comprehensive survey of categorizing IoT devices into low, medium, and the high-end application was presented in [32]–[34]. The characteristics of IoT systems that differentiate from other linked systems are discussed [35]. During the boot sequence of a device, the processor executes the boot loader's software, target compatible operating system software, and other application softwares. Immediately upon the successful boot process execution, the device must operate more securely. The IoT solutions usually comprise sensors, connectivity, data processing, and a user interface.

# A. THINGS

The IoT technology is essential for the smart home device, such as a camera for monitoring the home during abnormal conditions. An Internet protocol (IP) enabled camera framework can monitor, capture and send the video instantly to the user through the web interface. A smart clock is used to play music, weather display, cricket scores updates, and controlling smart home devices through voice. Simultaneously, the intelligent thermostat can self-learn about the individual users expected indoor temperature and indicate the user if something goes wrong. The IoT devices with sensors and actuators will detect the event, monitor the environment's transitions, and convert these physical quantities into electrical signals. Sensors are the entities that gather data and transfer through the internet for processing information from sensors such as image, smoke, light, and temperature. The sensor output are shared with the other devices with the availability of connectivity support. Therefore, wired or wireless connectivity among the devices is most vital. The processing capability and quantity of storage space required to handle this information is also significantly high. Thus, the interfacing of devices with cloud infrastructure enables higher support for processing and storage. In contrast, the actuator can operate in the environment to maintain and deliver the IoT devices' functionality. The actuator used in various categories can support interfacing motors, solenoids, and relays. The cluster of nodes associated with various protocols can communicate through the gateway.

# B. GATEWAY

Extensive infrastructure has been provided by cloud platforms to allow authentication and identity control of devices. The gateway performs connectivity, processing, and data storage in the cloud infrastructure referred to as data models [36]–[38]. The gateway also performs authenticating, monitoring, controlling, software update, and maintenance.

# TABLE 2. Devices categorization with supported peripherals.

| Devices                                     | CPU                                                                                                        | Clock        | Cache                                        | I               | RAM                      | Flash                                          | Security | Camera    | Audio/Vide<br>Support |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------|-----------------|--------------------------|------------------------------------------------|----------|-----------|-----------------------|

|                                             |                                                                                                            |              | BASIC I                                      | DEVICE          | s                        |                                                |          |           |                       |

| ATMEL Smart<br>D21                          | ARM Cortex-M0 (32-Bit)                                                                                     | 48<br>MHz    | None                                         | 2               | 56 KB                    | 32 KB                                          | No       | No        | No                    |

| Light Blue Bean+                            | ATMega 328P MCU (8-<br>Bit)                                                                                | 8 MHz        | None                                         | :               | 2 KB                     | 32 KB                                          | No       | No        | No                    |

| Particle Photon                             | ARM-based STM32F205<br>Cortex M3 processor,<br>SOC-STM32F205 (32-<br>Bit)                                  | 120<br>MHz   | No<br>Cache -<br>No<br>MMU                   | 1:              | 28 KB                    | 1 MB<br>Flash                                  | No       | No        | No                    |

| Arduino UNO R3                              | Atheros AR9331, SOC-<br>ATmega32U4 @ 16 MHz<br>(8-Bit)                                                     | 400<br>MHz   | None                                         |                 | B DDR2,<br>B SRAM        | 16 MB<br>Flash                                 | No       | No        | No                    |

| LibeliumWaspmote                            | ATmega1281, SOC-<br>ATmega1281 @ 14.74<br>MHz (8-Bit)                                                      | 14.74<br>MHz | None                                         | 8 K.            | 3 SRAM                   | 128 KB<br>Flash                                | No       | No        | No                    |

| SIPEED<br>Maixduino RISC-<br>V-AIIoT        | RISC-V Dual core 64-bit<br>with FPU, neural network<br>processor (64-Bit)                                  | 400<br>MHz   | None                                         | 2               | 56 KB                    | 32 KB                                          | No       | No        | No                    |

| NXP K64F                                    | MK64FN1M0VLL12<br>(32-Bit)                                                                                 | 120<br>MHz   | None                                         | 2               | 56 KB                    | 1 MB                                           | No       | No        | No                    |

| MEDIATEK<br>LINKIT ONE                      | ARM 7EJ-S, SOC-<br>MT2502A (32-Bit)                                                                        | 260<br>MHz   | None                                         | 4               | 4 MB                     | 16 MB                                          | No       | No        | No                    |

| Microsoft ESP32-<br>Azure IoT Kit           | Single core Xtensa 32-bit<br>LX7 CPU (32-Bit)                                                              | 240<br>MHz   | None                                         | 3               | 20 KB                    | 128 KB                                         | Yes      | No        | Audio-Yes             |

| Kinetics K22F                               | ARM Cortex-M4 MCU<br>with FPU (32-Bit)                                                                     | 120<br>MHz   | None                                         |                 | KB and 4<br>FlexRAM      | 1 MB                                           | Yes      | No        | No                    |

| Intel Galileo Board                         | 32-bit Intel Pentium ISA<br>Compatible processor,<br>SOC-Intel Quark SOC<br>(32-Bit)                       | 400<br>MHz   | 16 KB<br>L1<br>Cache                         | and             | IB DRAM<br>512 KB<br>RAM | 8 MB<br>NOR Flash                              | No       | No        | NO                    |

|                                             |                                                                                                            | •            | MEDIUM                                       | DEVIC           | ES                       |                                                |          |           | -                     |

| Cubie Board                                 | ARM Cortex-A8, SOC-<br>AllWinner A20 SOC (32-<br>Bit)                                                      | 1 GHz        | L1: 32 K<br>Cache + 3<br>D-Cache<br>512 KB ( | 32 KB<br>, L2:  | 1 GB<br>DDR3             | Up to 32<br>GB SD<br>Slot, 4 GB<br>Flash       | Yes      | No        | Yes                   |

| Humming Board                               | i.MX6 based Quad Core<br>processor CPU: ARM<br>Cortex A9 Core (32-Bit)                                     | 1 GHz        | Non                                          | e               | 2 GB<br>DDR3             | 8 GB<br>eMMC                                   | No       | Yes       | Yes                   |

| BeagleBone Black                            | ARM Cortex A8, SOC-<br>Sitara AM3358/9 (32-Bit)                                                            | 1 GHz        | L1: 32 K<br>Cache + 3<br>D-Cache<br>256 KB ( | 32 KB<br>5, L2: | SDRAM<br>512 MB<br>DDR3  | 4 GB<br>eMMC<br>Flash                          | No       | No        | Yes                   |

| Intel Edison<br>Compute Module              | Intel Atom Tangier<br>Z3480 (64-Bit), SOC-<br>Intel Quark MCU @ 100<br>MHz and Intel Atom Mcu<br>@ 500 MHz | 2.13<br>GHz  | 1 MB Smart 1 GB<br>Cache DDR3                |                 | 4 GB<br>eMMC<br>Flash    | No                                             | No       | Audio-Yes |                       |

| UDOO NEO                                    | NXP i.MX6 soloX<br>processor                                                                               | 200<br>MHz   | Non                                          | e               | 1 GB                     | None                                           | No       | No        | Yes                   |

| MINNOW<br>BOARD MAX<br>TURBOT QUAD-<br>CORE | Quad Core Intel Atom<br>E3845 (32-Bit and 64-<br>Bit)                                                      | 1.91<br>GHz  | 2 MB On<br>Cach                              |                 | 2 GB<br>DDR3L            | SPI<br>Flash/Boot<br>Rom, 8<br>MB SPI<br>Flash | No       | No        | Yes                   |

| AllWinner R8                                | ARM Cortex A8, SOC-<br>AllWinner R8 (32-Bit)                                                               | 1 GHz        | L1: 32 K<br>Cache + 3<br>D-Cache<br>256 KB ( | 32 KB<br>, L2:  | 512 MB<br>SDRAM          | None                                           | No       | No        | Yes                   |

#### TABLE 2. (Continued.) Devices categorization with supported peripherals.

|                               |                                                                      | A                                                                    | DVANCED DEV                                                                   | ICES                    |                  |     |     |     |

|-------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------|------------------|-----|-----|-----|

| SAMSUNG<br>ARTIK 530S         | ARM Cortex-A9 Quad<br>Core, SOC-MT2502A<br>(32-Bit)                  | 1.2 GHz                                                              | L1: I Cache -<br>32KB D-<br>Cache - 32KB<br>and L2: 1 MB<br>Shared            | 1 GB<br>DDR3            | 4 GB<br>eMMCv4.5 | Yes | Yes | Yes |

| SAMSUNG<br>ARTIK 5            | ARM Cortex-A7 Dual<br>Core 32-Bit)                                   | 1.0 GHz                                                              | L1: I Cache -<br>32KB D-<br>Cache - 32KB<br>and L2: 1 MB<br>Shared            | 512 MB<br>LPDDR3        | 4 GB<br>eMMCv4.5 | Yes | Yes | Yes |

| Qualcomm Dragon<br>Board 410C | ARM Cortex-A53 Quad<br>Core (64-Bit)                                 | 1.2 GHz                                                              | None                                                                          | 1 GB<br>LPDDR3          | 8 GB<br>eMMCv4.5 | Yes | Yes | Yes |

| NXP i.MX 7 Dual<br>Processors | Two ARM Cortex-A7<br>Plus and One ARM<br>Cortex-M4 (32-Bit)          | ARM<br>Cortex-A7<br>@ 1 GHz<br>and ARM<br>Cortex-<br>M4 @ 200<br>MHz | In Cortex-A7:<br>32KB Cache<br>In Cortex-A4:<br>32KB Cache<br>and 64KB<br>TCM | None                    | None             | Yes | Yes | Yes |

| Raspberry Pi 3<br>Model B+    | ARM Cortex Quad-core<br>A53, SOC-Broadcom<br>BCM 2837B0 (64-Bit)     | 1.4 GHz                                                              | L1: 16 KB I-<br>Cache + D-<br>Cache, L2:<br>128 KB                            | 1 GB<br>LPDDR2<br>SDRAM | 4 GB             | Yes | Yes | Yes |

| MIPS Creator<br>CI20          | MIPS-Xburst Dual-core,<br>SOC-Ingenic JZ4780 (32-<br>Bit)            | 1.2 GHz                                                              | L1: 32 KB I-<br>Cache + 32<br>KB D-Cache,<br>L2: 512 KB<br>Cache              | 1 GB<br>DDR3            | None             | Yes | Yes | Yes |

| Intel Joule<br>Compute Module | Intel Atom Processor<br>Quad-Core, SOC-Intel<br>Atom Broxton-M T5700 | 1.7 GHz                                                              | 4 MB Level-1                                                                  | 4 GB<br>DDR4            | 16 GB<br>eMMC    | Yes | Yes | Yes |

The installed device can automatically establish communication between the other devices. After successfully collecting data, the device transfers the data to the cloud server

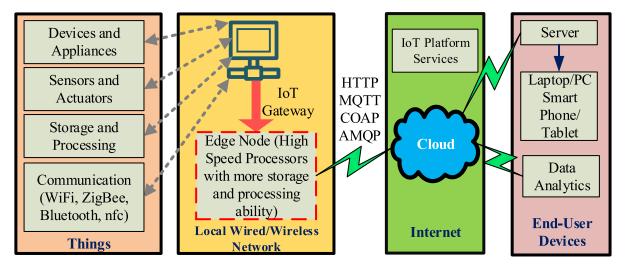

and receives messages serially from the cloud. The encryption algorithm can be ported in the device to enable secure data transmission among the devices. In the back end, the transport layer security and secure socket layer protocols to facilitate data security. The devices connected to the cloud environment can perform the software update and maintenance to ensure better compatibility with devices. The primary aspect is to provide extensive infrastructure to handle device applications and firmware. Thereby the infrastructure shall fix the bugs, manage security-oriented issues, and increases the functionality. In an IoT, the most commonly used end nodes are microcontrollers, human-machine interfaces, sensors, and actuators. In some applications, the end nodes directly communicate with the cloud without using a gateway or edge node. A generalized block diagram of the interaction between IoT devices and cloud servers is shown in Fig. 3.

# C. PROTOCOLS

The MQTT protocol is a lightweight protocol intended for the machine to machine applications, which allows the publish/subscribe communication model [39]. It is beneficial for connections with distance locations where network bandwidth is exceptional. The CoAP is suitable to operate in a resource-constrained environment. CoAP enables request/response messaging model between endpoints, quickly interprets HTTP for more straightforward web integration, and allows multicast topology with reduced overhead. The HTTP protocol allows the client-server architecture model, which is primarily useful for web applications. It can be used by the IoT devices to publish a

bunch of data. It accepts a standard IP header for packet routing and runs over TCP and UDP protocol. The HTTP is essential to collect and process the big data from the entire ecosphere, and the message size of HTTP is large compared to MQTT. The AMQP is an application layer protocol designed for interoperable message-oriented middleware applications. The AMQP supports the client/server communication model in IoT device management. AMQP delivers a secure connection and message acknowledgment to ensure reliable message transfer and provide extensibility support.

## **D. END-USER DEVICES**

The end node devices are low-cost microcontrollers with integrated sensors that utilize wireless protocols such as Bluetooth, ZigBee, etc. The long range communication can be established using TCP/IP supporting devices. These devices may also support energy harvesting with intensive power management strategies. On the other side, the edge nodes

FIGURE 3. Things and end-user device networking.

#### TABLE 3. Security protocol stack layer.

| Protocol | Corresponding Layer | Security Support                                                                                                                                                                                                                     |

|----------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Zigbee   | Physical/Mac layer  | The Zigbee protocol uses AES-128 encryption which makes it secure for IoT applications while using mesh topology. The requirements include providing the best functionality with security measures in place.                         |

| MQTT     | Application layer   | On the transport level, the communication sequence is encrypted and identities are authenticated. The MQTT protocol provides a client identifier and username/password credentials to authenticate devices on the application level. |

| CoAP     | Application layer   | CoAP is a UDP protocol rather than a TCP protocol, TLS is not used by default. Instead, encryption is implemented using Datagram Transport Layer Security (DTLS) and alternately with IPSec.                                         |

| 6LowPan  | Adaptation layer    | Bootstrapping keys, IP Sec, RSA, ECC. This protocol used to shorten IPv6 packets and located between the network and data link layer.                                                                                                |

| AMQP     | Application Layer   | This protocol uses either SASL or TLS encryption on the transport layer and defends communication among nearby devices on wireless personal area networks.                                                                           |

are the most potent multiprocessor devices with high computation capabilities, and it can operate without an operating system for low-end applications. Moreover, the complex application requires an RTOS or GPOS, such as Linux, often being deployed. Real-time operating system (RTOS) provides functionalities such as device driver handling, memory management, scheduling, TCP/IP, upper-layer protocol stack interface, etc. Due to limited computation features, the basic devices do not use the operating system. To handle several RTOS functionalities, advanced devices with complex computation abilities will utilize OS effectively. These devices are built with a high-performance internet protocol stack to enable efficient networking. A general-purpose operating system (GPOS) is a primary component in system design and responsible for running the application. It supports the execution of multiple tasks and appropriate scheduling policy to dispatch threads and processes that enable higher throughput for desktop applications. For instance, Windows, Linux is GPOS. The significant limitations of GPOS are latency and no guarantee for high priority thread execution. RTOS is a software-based design used for time-dependent use cases where the processing time should be less than GPOS.

VOLUME 9, 2021

The porting of RTOS enables rewriting the application in embedded hardware. GPOS cannot handle real-time application tasks due to its latency issues.

In contrast, RTOS codes are scalable and suitable for realtime applications. Therefore, developers can choose the necessary kernel objects based on their application requirements. The future IoT devices require modern, optimized microprocessors that can operate under varying environments and characteristics. The device characteristics and requirements of IoT devices summarized as follows.

#### E. SMART

The IoT system implemented using hardware and software incorporating algorithms and computations makes the devices more intelligent. The intelligence in IoT devices strengthens its capabilities, which helps to react smartly and support the devices to complete the precise tasks. Artificial intelligence and machine learning create the devices to think cognitively and make appropriate decisions based on earlier experiences [40]. The smart devices placed in the critical environment can withstand even in hazardous locations to enable real-time data transmission for robotics, industrial control, and self-driven vehicle applications.

# F. DATA SENSING AND CONNECTIVITY

The IoT devices can understand the environment and process the analog data received from real-world applications. The sensors connected with the devices shall continuously monitor the real-time environment changes or appliances and report its status to the end-user [41]. The connectivity role is pivotal in enabling new market opportunities, compatibility, and networking among smart appliances. The devices state is dynamic, i.e., devices may operate either in power-down mode or default mode, connected or disconnected mode. Sometimes, the number of devices sharing the network also changes dynamically to time and place.

## G. COLOSSAL SCALE

Due to the rapidly increasing number of smart consumer electronics devices, those devices must adequately manage to communicate with each other through internet technologies [42]. The enormous amount of data generated from smart appliances will cause data handling and interpretation more critical.

# H. DIVERSIFICATION

IoT devices developed using different hardware boards and networks to work together with other devices over diversified networks [43]. The microprocessor architecture should support network connectivity directly in heterogeneous networks. The primary design necessities in IoT are scalable, extensible, and commutable.

# I. ENERGY

The development of IoT brings a massive amount of edge devices. The edge node devices can be deployed quickly and do not require a physical connection to electrical infrastructure [44]. The microprocessor selection can bring the system to operate in low power mode and wait for an interrupt signal to awaken the system. Integrating a considerable number of devices that run on batteries can create a severe problem. Therefore, researchers and product development teams should focus on energy harvesting, charging topologies, and infrastructure to design a smart power ecosystem.

# J. SAFETY AND SECURITY

The safety and security measures support various IoT protocols in different layers listed in Table 3. Multiple device interfaces, significant data handling, multiple network connectivity, and exploiting various IoT protocols will make the system more complex and less secure [45]. The early detection of deformities in safety applications is vital. Failing to locate anomalies may sometimes cause catastrophic failure. Therefore, it is mandatory to monitor the system consistently and gather the logging activities for troubleshooting abnormalities. Consequently, to secure the end nodes, edge nodes, networks, and data transfer across all nodes to create

25602

a security paradigm to prevent data from vulnerable attacks, additional efforts must be taken [46].

# III. STATE OF THE ART MICROPROCESSOR ARCHITECTURES AND COMPONENTS

### A. EXTENSIBLE OR SCALABLE ARCHITECTURE

The scalable microprocessor architecture-based design practices are becoming more complex due to increased networked devices. However, it provides the best possible functionality with faster response times and reduced power consumption. The deployment of scalable edge devices close to cloud infrastructures results in low latency, decreased reliability, and an increase in bandwidth [47]. The edge computing device significantly requires high-performance computing resources to address latency and bandwidth issues. Therefore, an essential requirement is to design reliable architectural resources and reduce the cost of hardware and software development for scalable architectures. However, we aim to address the cache memory implications within the scalable microprocessor architecture devices due to which it has a significant impact on processor performance. The IoT microprocessors should be adaptable following the IoT application necessities. The configurations of the microprocessor should be modified during design to achieve better efficiency. The reconfigured microprocessor with more internal components will be adaptable for various application design. The major factors, such as pre-fetch issue queue and pipeline mechanisms, have an essential role in performance improvement. The scalable architectures utilize the cache memory area efficiently rather than using the main memory. Since the cache has a potential impact on the microprocessors area, power, and performance in this section, we focus on the significance of cache memory. The register file is tightly coupled to the microprocessor core [48]. The memory hierarchy is categorizing as primary level and secondary level. In the primary level, Level-1 (L1) or primary cache and tightly coupled memories (TCMs) are associated with the processor through on-chip interfaces. In addition to this, the main memory is allied with the primary level (SRAM, DRAM, and flash memory) to store the programs while the processor is executing. In comparison, secondary level memory devices such as external disk drives and removable memory storage have a large area and are almost slow. The data accessed from the peripherals require too long access times. A cache can be included across any particular hierarchy. However, the access time varies among the memory components [49].

The cache memory takes data and instruction from disks, central memory (DRAM), off-chip cache (SRAM) and places near the processor core to increase the performance, ability, and cost per bit. Some of the IoT processor devices have Level-1 (L1), Level-2 (L2), and Level-3 (L3) caches. The L1 cache is an on-chip memory area that stores the program and data from onboard memory temporarily to reduce the access time required for both data and code. The L2 secondary cache is on the processor chip located between the

primary cache and board-level memory. While, the L1 cache is located directly on the CPU itself, and it ranges from 8KB to 64KB. However, to perform read operation from the CPU, L1 is the faster memory type. In multicore CPUs, each core has an L1 cache separately. Generally, L2 and L3 have a large volume of memory compared to L1, but it requires a long time to access data. The L2 cache memory usually a distinct chip located between the CPU and random access memory (RAM). The data types enable the processor core to access the main memory directly. The ARM7 through the ARM10 processor family uses a logical cache where the data can be accessed directly by the processor from the logical cache without the memory management unit (MMU). The cache has a significant implication in terms of security as the threat and backset vulnerabilities.

## **B. SHARED HETEROGENEOUS ARCHITECTURE**

From the design perspective, the foremost benefits of heterogeneous architectures for IoT microprocessors core consists of CPUs, digital signal processors (DSPs), graphics processing units (GPUs), etc. and it can be able to reuse again in the implementation stage. This permits earlier design and verification exertions to be paying off. Though the design space offered by the processor architectures (HPA) is considerably smaller, unlike adaptable architectures [50].

The HPA requires diligent effort in finding the most exceptional processor core configurations that will fulfill the application necessities. Moreover, in a system with vast applications, the configuration optimization potential is realized lower in heterogeneous cores than configurable cores. During the cache miss operation, the CPU can't do anything, but in the meantime, another thread can utilize the processor resources. If the algorithm discloses high-level instruction parallelism, then the core available in sequence would be slower and inefficient. While performing floatingpoint operations and single instruction multiple data (SIMD) instructions, the memory access has long dormancy. A processor can achieve maximum throughput upon having more pipeline stages and considering the code optimization techniques explicitly for the processor architecture instructions. The processor takes more cycles to fill the pipeline stages, which may cause an increase in latency. The presence of multiple cores increases the speed execution speed; however, the power consumption will be slightly high. Notably, in ARM Cortex A8 IoT CPU core, the unavailability of multicore and order of execution pipelined architecture operates with reduced power consumption and area. The multicore processors are more beneficial to deliver high performance for edge computing applications such as audio-video processing and complex data acquisition systems [51]. The CPU can effectively exploit the branch prediction techniques. Thereby a considerable amount of power and area is reduced. Therefore, the multicore heterogeneous architectures are more proficient in executing operational codes in both out-of-order and in-order routines. Considerable earlier research works have directed heterogeneous cores in embedded systems and

general-purpose computers, though their application to IoT microprocessors should be determined [52]. The applications designed with suitable cores and selections of appropriate cores are the prime challenges that need to address while designing and developing various microprocessors. The designers entail knowledge on core configurations and prior understanding and analysis of applications, exemplified in the microprocessor. The symmetric multiprocessing system consists of a single kernel, different cores utilizing the same instruction set architecture, and execute an available operating system using shared memory. The scheduler will decide the environment to empower load balancing, permitting processes to run on several cores at different times. On the other hand, an asymmetric multiprocessing (AMP) system consists of multiple cores, numerous software processing abilities, supports heterogeneous architecture using shared or separate memory [53]. Typically, the new OS is running on the system, which is unglued for each core architecture.

For example, a gateway requires high-speed internet connectivity to process graphical information, which runs on the Cortex-A core. In contrast, the process control and algorithms for monitoring purposes will run on the Cortex- M core separately. The AMP system is optimized to perform computation like off-loading audio processing towards low power Cortex-M processor core. Most of these operations require an RTOS to run with hard real-time constraints. The developed architecture near the Cortex-M core must enable single-cycle access at high speed between masters to the slave device to facilitate these necessities. The high-performance RTOSs such as Nucleus can deliver real-time processing on the ARM Cortex-A processor core. To attain higher efficiency in processing audio, video, data with reduced power consumption, a heterogeneous multicore configuration executing in the AMP approach is the right choice.

## C. ENERGY SAVING ARCHITECTURE

Smart home devices are emerging in recent years, as they become innovative, ranging to not just automation and also provides safety and security. Handling smart electrical appliances such as microwave oven, a smart induction cooktop that tip-off before the malfunction, and protects the user from any terrible situations. The energy-saving in IoT smart home is another challenge; therefore, smart thermostats and smart illumination system supports the user in saving energy and the cost of electric bills. The sensors and home appliances will communicate information directly to the user using IoT endpoint devices with internet connectivity support. Therefore, battery-operated devices (BODs) are becoming an unavoidable option; however, battery replacement is not economical for specific applications. Since the device requires sufficient power, foraging energy is another approach that can address battery-oriented problems.

The energy harvesting can facilitate electronic systems to drive for years on varying power sources. Chen Pan *et al.* proposed an ENZYME software model to improve edge-nodes

| Architecture | Low<br>Power<br>Support | Industry<br>standard<br>Software<br>Support | Cache<br>Support | Pipeline<br>Stages | Hardware<br>Design                           | Instruction<br>Size | Available<br>Registers                    | Memory<br>Access                 | Reference(s) |

|--------------|-------------------------|---------------------------------------------|------------------|--------------------|----------------------------------------------|---------------------|-------------------------------------------|----------------------------------|--------------|

| VLIW         | Yes                     | Yes                                         | Yes              | 5                  | Multiple<br>Pipelining<br>Stages             | One size            | Many GP<br>Registers                      | Load/Store<br>Architecture       | [57]         |

| MIPS         | No                      | Yes                                         | Yes              | 5                  | Support multiple<br>stage of<br>pipelining   | 4 Bytes             | Many GP<br>Registers                      | Load/Store<br>Architecture       | [58], [59]   |

| RISC-V       | Yes                     | Yes                                         | Yes              | 6                  | Single stage<br>pipeline<br>implementation   | 32-Bits             | Many GP<br>Registers                      | Load/Store<br>Architecture       | [60], [61]   |

| ARMv7        | Yes                     | Yes                                         | Yes              | 3                  | Three stage<br>pipelining with<br>microcoded | Varies              | Many GP<br>Registers                      | Load/Store<br>Architecture       | [62]         |

| CISC         | No                      | Yes                                         | No               | 5                  | Support<br>microcoded<br>implementation      | Varies              | Registers<br>with special<br>instructions | Supports<br>CISC<br>instructions | [63]         |

#### TABLE 4. Comparison of instruction set architectures.

energy efficiency using ultra-low energy harvesting (EH) power supplies [54]. The energy harvesting system (EHS) consists of sensors and data conversion circuits in which the sensor acquires energy from various sources and converts into electrical form. Lithium-ion (Li-ion), alkaline, nickel-cadmium (NiCd) batteries, and super-capacitors can be used to store and process the transformed electrical energy. The regulator will handle the power according to the system requirements.

## D. APPLICATION-SPECIFIC PROCESSOR ARCHITECTURE

Table 4 illustrates the comparison of state-of-the-architectures instruction set architectures. To attain better performance, efficient energy requirements in IoT applications, the hardware-based design methods are utilized typically. The most common hardware design approaches such as application-specific integrated circuits (ASIC) and FPGA based solutions are well suited for IoT applications in which ASIC can deliver better performance. Still, a diligent effort must be taken in design [55]. Due to reduce overhead in architecture, the ASIC has a significant benefit compared to general-purpose processors (GPPs). Designing a processor with a limited set of functions required by the application may achieve very high performance, surpassing GPPs. Broadly ASIC design lack the competence to adapt and accord with changing application necessities [56].

The organization of cache differs from a general-purpose processor to DSP or ASIC devices. The industry is currently moving towards structured ASIC from a full custom or general-purpose processor based on the volume and end product shelf life. The application functionalities designed for microcontrollers must be programmed using register-transfer levels (RTL) logic programming languages such as Very High-Speed Integrated Circuits Hardware Description Language (VHDL) or system Verilog. Many high-level synthesis tools exist for ease of ASIC design. Using the appropriate platform, the designer can create hardware from software, providing a meaningful improvement in development time and effort to RTL design. The increasing acceptance of IoT move from the existing chip designs to custom silicon. Subsequently, there has been a substantial transformation in the complete IoT ecosystem. The semiconductor organizations can influence the market, considering they can design customized IoT chip at less cost.

Rather than contingent on using off-the-shelf components in IoT edge product design and development, the ASIC designers utilize the customized silicon design. The utilization of custom ASIC design for various IoT applications significantly improves the functionality and allows greater flexibility in design. To diminish the dynamic power consumption among multiple plants, the designers adopt power-saving methods appropriate to lower geometry systems, typically ranging from 180nm to 4nm technology. The researchers currently focus on attaining better dynamic power through clock gating techniques to strengthen the geometrical aspect, avoiding power leakage through proper biasing.

The foremost architectures presently used by IoT developers are Advanced RISC Machine (ARMv7), Microprocessor without Interlocked Pipeline stages (MIPS), and X86. The other traditional architectures, including RISC and variablelength instruction word (VLIW) [57] cannot adapt at runtime. In contrast, we have made a design space investigation of CPU architectures, including variable-length instruction word (VLIW), MIPS [58], [59], reduced instruction set computer (RISC) [60], [61], and ARMv7 [62], [63] architectures. This work is compiled and synthesized using the Xilinx Vivado v.2016.4 software tool and implemented using Xilinx Zynq-7000 (xc7Zz20clg484-1) FPGA Device. We tested the processors' data path structures and functional simulation of their internal components. We synthesized the VHDL script for processor architectures and the internal components using the inbuilt CPU clock frequency (FCPU) in the FPGA board. The processors are tested by writing a data word to an external

memory location in the FPGA devices to ensure the working of designed code modules. We developed and analyzed the PERL scripts code for the various sub-modules, including a register file, barrel shifter, ALU, address decoding, and control unit.

The implementation of processor architectures demonstrates resource utilization and area consumption in an FPGA device. The other coprocessors available on the board can utilize remaining memory resources. The processor's speed performance can be achieved by thoroughly analyzing and optimizing the architectures' pipelining flow. From the results (shown in Table-V) attained for the high-end design, the devices with higher performance such as ARMv7 architectures and MIPS are significant due to availability of bonded input-output (I/O) blocks. The I/O blocks are used to perform the I/O operations for interfacing the external memory and peripheral device in an FPGA.

In terms of image processing applications, the devices that support DSP operations are reliable such that ARMv7 uses three DSP modules, VLIW uses two DSP cores. In comparison, the other MIPS and x86 architectures are undependable.

The slice registers occupancy for ARMv7 followed by MIPS is higher than that of other processor architectures. It will support the fastest data access using the registers and allow the compiler to execute the instructions independently. We realize that the VLIW, X86, and RISC architectures use fewer slice LUTs and slice registers compared to ARMv7 and MIPS. The processor architecture's resource utilization in FPGA is verified based on the number of slice registers, slice LUTs, Bonded IOBs, memory usage, and signal processing capabilities. The result shown in Table 5 demonstrates ARMv7, and MIPS architectures utilize more slice logic, registers, and bonded IOBs, followed by RISC, X86, and VLIW architectures. In the future, design space study with contemporary architectures such as ARM Cortex A53, A57, and A72 configurations will be investigated for the growth of low-power IoT systems.

# IV. SoC DEVICE PARAMETER SELECTION FOR IoT SPECIFICATIONS

The designer's primary concern is to fulfill the sensor node selection since an end node with an 8-bit MCU that can sense and transmits the limited data times in a day. Though for involved end nodes and smart gateway devices requires advanced algorithms; therefore, 32-bit MCU is the right option. The 32-bit microcontrollers, such as the ARM Cortex-M series MCU core, have floating-point units for implementing sophisticated algorithms. The higher processing power of the 32-bit MCUs empowers processing faster by switching to sleep mode and save power [64], [65]. Moreover, these MCUs have higher flash and RAM area, enabling the designers to develop the complete protocol stack and application program code on the microcontroller devoid of requiring an additional CPU in the system. While performing sophisticated filtering approaches for energy management applications like H-infinity and Kalman filtering, the processor depends on complex matrix computations. As a result, 32-bit MCUs with FPUs can be used [59]. The microcontroller choice is reliant on the functional requirements of the IoT product performance, low power requirement, wireless integration, or robust security. Many IoT products in industries and health are much complicated and have additional computational power and energy limitations. Thus, IoT requires more study and standards to appraise the needs of the microcontroller. This section describes certain principles to determine which microcontroller is precise for the application needs.

## A. MEMORY

The processing speed and performance depends on the memory sizes of the chosen microcontroller. The commercial microcontrollers have different memory sizes and usually have two memory components, such as RAM and ROM. The RAM holds the data access by the processor and performs read and write operations. The ROM saves the application code inside the microcontroller. The device cost factor becomes high when the size of the ROM is large. Few microcontrollers are designed with memory protection regions by imposing rights and access rules to address the memory locations. Table 6 list the memory specifications of various IoT devices.

## B. SPEED

The speed of processing is essential for IoT products. However, IoT products require high-speed microcontrollers to execute demanding real-time tasks. The clock determines the speed of processing delivered by the specific device to achieve a higher data rate. The IoT device can perform functions like sensing or sending raw video to the storage entity by collecting data from one or more source after performing economic analysis. The microcontroller requires enough processing power to execute the tasks and functions [28].

# C. INBUILT NETWORK INTERFACES

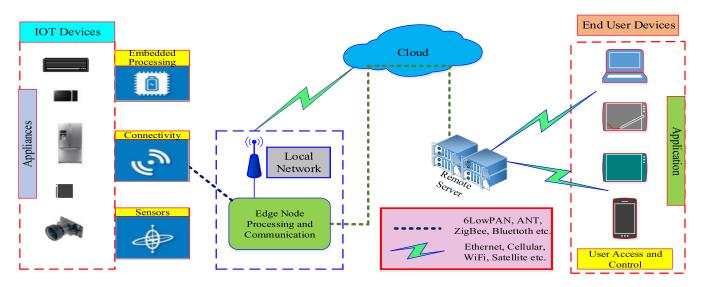

The network interfaces of microcontrollers will communicate with devices nearby and transfer the data to the IoT device for any computational analysis. The IoT devices connected through a wireless standard such as Wi-Fi mesh, Zigbee, Z-Wave, KNX, Thread, and Bluetooth for short-range communication and LPWAN, LoRA, 2G/3G/4G cellular network technologies for long-range communication [66]. These network interfaces are necessary to share the data to enable endto-end networking, as illustrated in Fig. 4. The inexpensive link, low energy consumption, and cost are the foremost considerations for choosing the radio frequency (RF) technology. The Wi-Fi and Bluetooth standards utilized in IoT applications can operate under real-time conditions since Bluetooth enables point-to-point connections with smart devices like mobile phones, laptops to control the appliances in connected home applications. At the same time, Wi-Fi is most appropriate for bandwidth-demanding applications like wireless cameras. Ultra-low-power Sub GHz radio transceivers ICs

#### TABLE 5. Design space requirements of instruction set architectures.

| Architecture           |           | VLIW | MIPS | RISC | ARMv7 | X86  |

|------------------------|-----------|------|------|------|-------|------|

| Site Type              | Available | Used | Used | Used | Used  | Used |

| Slice Logic            |           |      |      |      |       |      |

| Slice LUTs             | 53200     | 54   | 931  | 903  | 3392  | 104  |

| LUT as Logic           | 53200     | 54   | 931  | 903  | 3320  | 92   |

| LUT as Memory          | 17400     | 0    | 0    | 0    | 72    | 24   |

| Slice Registers        | 106400    | 68   | 1055 | 534  | 2231  | 75   |

| Registers as Flip-flop | 106400    | 22   | 1055 | 534  | 2231  | 75   |

| Registers as Latch     | 106400    | 0    | 0    | 0    | 0     | 0    |

| F7 Muxes               | 26600     | 0    | 288  | 5    | 54    | 0    |

| F8 Muxes               | 13300     | 0    | 92   | 0    | 0     | 0    |

| Memory                 |           |      |      |      |       |      |

| Block RAM Tile         | 140       | 2    | 0    | 0    | 4     | 0    |

| RAM B36/FIFO           | 140       | 0    | 0    | 0    | 0     | 0    |

| RAM B18                | 280       | 4    | 0    | 0    | 8     | 0    |

| DSP                    |           |      |      |      |       |      |

| DSPs                   | 220       | 2    | 0    | 1    | 3     | 0    |

| Ю                      |           |      |      |      |       |      |

| Bonded IOB             | 200       | 11   | 198  | 4    | 152   | 105  |

#### TABLE 6. Memory specifications of IoT devices.

| SOC                           | CACHE                                                | RAM                      | STORAGE                                                          | OPERATING<br>TEMPERATURE | OPERATING<br>VOLTAGE |

|-------------------------------|------------------------------------------------------|--------------------------|------------------------------------------------------------------|--------------------------|----------------------|

| AllWinner R8                  | L1: 32KB I-Cache + 32KB,<br>D-Cache, L2: 256KB Cache | 512MB SDRAM              | MicroSD                                                          | -20°C to 70°C            | 3.3V                 |

| Broadcom BCM<br>2837B0        | L1: 16KB I-Cache + D-<br>Cache, L2: 128KB            | 1GB LPDDR2<br>SDRAM      | MicroSD                                                          | 0 to 50°C                | 5V                   |

| Sitara AM3358/9               | L1: 32KB I-Cache + 32KB,<br>D-Cache, L2: 256KB Cache | SDRAM 512MB<br>DDR3      | MicroSD, 4GB eMMC Flash                                          | -40°C to 105°C           | 1.8V to 3.3V         |

| Ingenic JZ4780                | L1: 32KB I-Cache + 32KB<br>D-Cache, L2: 512KB Cache  | 1GB DDR3                 | MicroSD, 8GB Flash                                               | -40°C to 125°C           | 3.6V                 |

| Intel Quark/Atom<br>MCUs      | 1MB Smart Cache                                      | 1GB DDR3                 | MicroSD, 4GB eMMC Flash                                          | 0 to 70°C                | 3.6V to 5.25V        |

| Intel Atom Broxtor<br>M T5700 | -4MB Level-1                                         | 4GB DDR4                 | MicroSD, 16GB eMMC                                               | 0 to 70°C                | 3.6V to 5.25V        |

| STM32F205                     | No Cache - No MMU                                    | 128KB                    | 1MB Flash                                                        | -40°C to 85°C            | 1.8V to 3.6V         |

| ATmega32u4                    | None                                                 | 64MB DDR2,<br>2.5KB SRAM | MicroSD, 16MB Flash                                              | -40°C to 85°C            | 2.7V to 5.5V         |

| ATmega1281                    | None                                                 | 8KB SRAM                 | 16GB, eMMC, 128KB Flash                                          | -40°C to 85°C            | 2.7V to 5.5V         |

| AllWinner A20                 | L1: 32KB I-Cache + 32KB                              | 1GB DDR3                 | Up to 32GB SD                                                    | -20°C to 70°C            | 1.7V to 3.6V         |

| Tensilica Xtensa<br>L106      | 512KB Cache, 32KB I-<br>Cache, 80KB D-Cache          | SRAM up to<br>160KB      | Slot, 4GB Flash Internal 4MB<br>Flash, External Flash up to 16MB | -40°C to 125°C           | 2.5V to 3.6V         |

(e.g., ADF7024) are used to operate the devices for several years without changing the battery allows better transmission range and effectively penetrate through walls.

#### D. WAKE-UP TIME

The ultra-low-power smart home appliances like connected lights, intelligent refrigerators, and the camera usually spend most of the time in low power operational mode (sleep mode) to handle the task and rapidly return to the low power mode. Therefore, it is necessary to choose an MCU with an active wake-up time. The MCU cannot carry out any additional tasks during sleep mode, which results in energy saving, and therefore devices can attain the optimum low-power consumption.

### E. COST AND MANUFACTURER SUPPORT

The microcontroller cost can differ for different use cases and impose licensing charges for individual device drivers.

25606

Detailed documentation supports the microcontroller users to make an appropriate conclusion on the features and specifications. The manufacturer allows professional support apart from standard support for platform development by enabling direct contact with the manufacturing organizations experts [67]. Furthermore, community support must know the real problems, implementation issues, error occurrences, and their solutions to transform the product [68].

#### F. COMMUNICATION PORTS

The ports are inbuilt into the microcontroller chip, or a separate I/O controller can be used. The I/O port in the microcontroller performs data transfer between the central processing unit and the peripheral devices. The I/O processor on an embedded board can have a series of components connected like LCD, LED, Motor, and CRT. The digital I/O can be programmed as an input or output port. Besides, analog ports used for instances such as speed, and temperature

FIGURE 4. IoT end to end communication and networking.

measurement. The designer can select the microcontroller based on the type and specifications [69].

## G. SECURITY AND STANDARDS

In the digital era, data security is the primary concern for microcontroller manufacturers and the end consumers working on the IoT domain [70]. Often chip manufacturers set up security measures to protect the system access from threat activities. Since several connected devices increases, vulnerability towards attacks may increases. In embedded design security procedures are essential through all layers similar to internal device storage, communication protocols, hardware interfaces, gateway implementation, and cloud computation. Security must be considered in the initial stage of the design by defining the security category that a specific product requires and examining the resources that necessitate protection. Thus, the designer will recognize the fundamental threat and security procedures that should be undergone to protect the design. Contingent on the IoT application needs, the security level can be examined. For instance, the application such as industrial control, nuclear engineering, medical devices, and traffic management requires a higher security level. However, smart home appliances such as a refrigerator, and the washing machine does not entail higher security measures. Additionally, designers are formulating more dedicated security chips that can be incorporated within the microcontroller to store user authorizations and encryption keys securely. Often attackers insert harmful code into the IoT microcontroller device; this situation leads to the worst consequences. To avoiding device attacking, few microcontrollers come with ingrained tamper detection. Usually, microcontroller chip manufacturers provide Crypto-Boot loader for security and firmware updates.

Ultimately, to prevent data leakages through the update process, the boot-loader encodes security keys in advance

of the update. The encoding and decoding process utilizes internal microcontroller memory and clock cycles, lessens other events scheduled for execution. Some microcontrollers add accelerating algorithms in hardware to speed up the cryptography process. Conversely, Boot ROM is a writeprotected flash set inside the microprocessor chip. It holds the initialization code, which is fetched and executed by the processor during power-on-reset. The standards developed by various industries, national and international bodies, are agreed upon by standard development organizations (SDOs), special interest groups (SIGs), and technology manufacturers. Table 7 shows the list of IoT and Machine to Machine (M2M) standards that are ideally suitable for IoT applications. The purpose of standards ensures interoperability and enables a cost-effective solution. The architectural framework described in the IEEE-P2413 standard will support cross-domain interactivity, assist system interoperability and operational compatibility, and further the IoT market [71]. IEEE Technology Report on Wake-Up Radio: An Application, Market, and Technology Impact Analysis of Low-Power/Low-Latency 802.11 Wireless LAN Interfaces describe how to attain low latency and low power at the same time. This report is beneficial for IoT device manufacturers and consumers to make superior business decisions [72].

#### H. ENERGY MANAGEMENT