# POLITECNICO DI TORINO Repository ISTITUZIONALE

Systematic Electromagnetic Interference Filter Design Based on Information From In-Circuit Impedance Measurements

Original

Systematic Electromagnetic Interference Filter Design Based on Information From In-Circuit Impedance Measurements / Tarateeraseth, V.; Kye Yak, See; Canavero, Flavio; Chang, R. W.. - In: IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY. - ISSN 0018-9375. - STAMPA. - 52:3(2010), pp. 588-598. [10.1109/TEMC.2010.2046419]

*Availability:* This version is available at: 11583/2419719 since:

*Publisher:* IEEE

Published DOI:10.1109/TEMC.2010.2046419

Terms of use: openAccess

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

(Article begins on next page)

# Systematic Electromagnetic Interference Filter Design Based on Information From In-Circuit Impedance Measurements

Vuttipon Tarateeraseth, *Student Member, IEEE*, Kye Yak See, *Senior Member, IEEE*, Flavio G. Canavero, *Fellow, IEEE*, and Richard Weng-Yew Chang, *Member, IEEE*

Abstract—Based on a two-probe measurement approach, the noise source and noise termination impedances of a switched-mode power supply (SMPS) under its normal operating condition are measured. With the accurate noise source and noise termination impedances, an electromagnetic interference (EMI) filter can be optimally designed. A practical example of the design of an EMI filter to comply with a regulatory conducted EMI limit using the proposed procedure is demonstrated and compared with the cases, where the noise source and noise termination impedances are not taken into account, or coarse estimates of them are considered. Although all approaches allow filtered SMPS to pass the regulation limits, designing EMI filters with the accurate noise source and termination impedances leads to optimal component values and avoids overdesign.

*Index Terms*—Electromagnetic interference (EMI), EMI filter, line impedance stabilization network (LISN), noise source impedance, switched-mode power supply (SMPS).

# I. INTRODUCTION

➤ ONDUCTED electromagnetic interference (EMI) is one of the meinter and a second s of the major concerns for switched-mode power supply (SMPS) design [1]. To comply with the international regulatory EMI requirements, an EMI filter is necessary to lower the conducted EMI level of the SMPS below the limit [2]. For filter designs of communications and microwave applications, the source and termination impedances are well defined (usually specified at 50  $\Omega$ ). However, the impedance levels of the noise source inside an SMPS are not readily available. On the other hand, the impedance level of the filter output, which is conventionally a line impedance stabilization network (LISN), is well defined [3]. One could think of estimating the noise source impedance of an SMPS using the datasheet or typical values, but such estimates are not reliable. In fact, the noise source impedance differs from the nominal impedances of the SMPS and not the SMPS itself (provided by the constructor), due to converter topology, component parasitics, print circuit

Manuscript received November 10, 2009; revised February 4, 2010; accepted March 14, 2010. Date of publication April 12, 2010; date of current version August 18, 2010.

V. Tarateeraseth and F. G. Canavero are with the Dipartimento di Elettronica, Politecnico di Torino, Torino 10129, Italy (e-mail: vuttipon.tarateeraseth@ polito.it; flavio.canavero@polito.it).

K. Y. See is with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798 (e-mail: EKYSEE@ntu.edu.sg).

R. W.-Y. Chang is with the Guided Systems Division, DSO National Laboratories, Singapore 118230 (e-mail: cwengyew@dso.org.sg).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TEMC.2010.2046419

board layout, etc. [4]. Also, the complexity of the noise-coupling mechanism makes the generation of adequate models for SMPS a hard task, and engineers prefer to resort to characterization measurements. SMPS may not be easily modeled [5]. Hence, the design of an EMI filter without known noise source impedances can be a challenging task [6]–[8]. In addition, conducted EMI exists in two modes, the common mode (CM) and the differential mode (DM), which further complicates the filter design process as the EMI filter is required to effectively suppress both CM and DM emissions.

Some EMI filter design methods adopt a simplistic approach to design an EMI filter without taking into account the noise source impedance and the noise termination impedance [9]-[11]. Other EMI filter design methods do take into account the noise source and the noise termination impedances but approximate them as purely resistive elements [12], [13]. As there are some approximations being made in these methods, worst case conditions (maximum or minimum possible CM and DM impedances) have to be assumed to design the EMI filter [13]. Although EMI filter design prescriptions of above methods allow the filtered SMPS to pass the regulation limits, they usually lead to overdesign or nonoptimal choice of the filter components. Without precise information (magnitude and phase) of the noise source and noise termination impedances over the frequency range of interest, it is difficult to decide on an appropriate EMI filter configuration and to design an optimal filter for an SMPS to meet a specific conducted EMI limit.

In this paper, based on an in-circuit impedance measurement setup, the amplitude and phase information of the noise source and noise termination impedances can be measured and extracted under actual device operating conditions. The assumption underlying our extraction procedure is that the input impedance of the power supply behaves linearly. This is reasonably true, since, according to [14], the "ON" state impedance prevails during operation and the impedance probing is done by means of small signal perturbations, thus allowing linearization [15]. With the known impedance information, the design limitations of the methods mentioned earlier can be overcome and a systematic EMI filter configuration to achieve the desired filter insertion loss performance becomes possible.

# **II. IN-CIRCUIT IMPEDANCE MEASUREMENT**

In order to extract the noise source impedances, two approaches are available. The passive approach, proposed in [14],

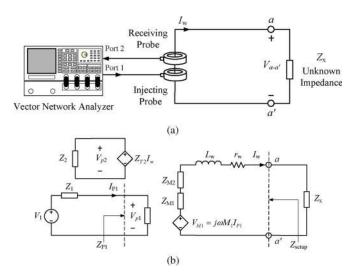

Fig. 1. (a) Conceptual two-probe in-circuit measurement setup. (b) Equivalent circuit of the measurement setup.

amounts to a direct measurements of an SMPS in offline condition; although conceptually simple, this method requires two measurements with a series and shunt load on the SMPS input, and recovers only the impedance magnitude because it relies on insertion loss determination. Alternatively, the active approach, proposed in [16], by means of injecting and receiving current probes extracts the DM and CM impedances of SMPS. However, careful selections of isolating chokes and coupling capacitors are required to measure the noise source impedance. Moreover, only the magnitude of the noise source impedances can be extracted. Unlike the former two-probe method, the proposed method, [17], uses direct clamp-on current probes, and therefore, there is no direct electrical contact to the power line wires between the LISN and the SMPS. Hence, it eliminates the need for the coupling capacitors. Also, no isolating chokes are needed, making the measurement setup simple to implement. With the vector network analyzer (VNA) as a measurement instrument, both the magnitude and the phase information can be extracted accurately.

Fig. 1(a) shows the basic setup to measure the unknown impedance  $Z_x$  in a circuit loop, where the loop can be carrying high voltage and/or high current. The setup requires an injecting current probe, a receiving current probe, and a VNA. The two current probes couple to the circuit through inductive couplings without direct connection to the circuit. By transferring the primary circuits of the injecting and receiving probes in the coupled circuit loop, the equivalent circuit of the setup is given in Fig. 1(b).  $Z_{M1}$  and  $Z_{M2}$  are the equivalent impedances of the injecting and receiving probes, respectively.  $V_{M1}$  is the induced signal voltage in the circuit loop from port 1 of the VNA through the injecting probe.  $L_w$  and  $r_w$  are the loop inductance and resistance, respectively.

$Z_x$  is the impedance to be measured and all the other impedances present in the circuit loop are due to the measurement setup (let us define  $Z_{setup} = Z_{M1} + Z_{M2} + r_w + j\omega L_w$ ). Also, the current flowing in the circuit loop due to the injected signal through injecting probe is given by

$$I_w = \frac{V_{M1}}{Z_{\text{setup}} + Z_x}.$$

(1)

Finally, the induced voltage in the loop is given by

$$V_{M1} = j\omega M_1 \left(\frac{V_1}{Z_{p1} + Z_1}\right) \tag{2}$$

where  $M_1$  is the mutual inductance between the injecting probe and the coupling loop,  $V_1$  and  $Z_1$  are the Thévenin equivalent voltage source and impedance, respectively, of port 1 of the VNA, and  $Z_{p1}$  is the input impedance of the injecting probe.

The received signal at port 2 of the VNA depends on the current  $I_w$  measured by the receiving current probe, that is,

$$V_{p2} = Z_{T2}I_w \tag{3}$$

where  $Z_{T2}$  is the calibrated transfer impedance of the receiving probe provided by the probe manufacturer.

By substituting (2) and (3) into (1), the unknown impedance to be measured can be determined as follows:

$$Z_x = K\left(\frac{V_{p1}}{V_{p2}}\right) - Z_{\text{setup}} \tag{4}$$

where  $K = (j\omega M_1 Z_{T2})/(Z_{p1})$  is a frequency-dependent coefficient. The premeasurement calibration process to obtain Kand  $Z_{\text{setup}}$  is described in detail in [17] and will not be repeated here.

It is ought to be noted that for the sake of clarity, Fig. 1 is simplified and does not contain the LISN, which powers the active device under test (the SMPS, in our case). The LISN impedance should be considered a part of  $Z_{setup}$  without limitations. An additional remark is that the injected signal of the VNA must be much larger than the background noise generated by the device under test in the frequency range of interest so that the background noise does not alter the  $Z_x$  value, superimposing on the measured quantities. For most of the low- and medium-power active systems, such a condition can usually be met. However, if the active system is characterized by very high power and generates significant background noise, one could add a power amplifier at the output of port 1 of the VNA to increase the power of the injected signal so that the aforementioned condition could be fulfilled. Moreover, a premeasurement calibration process not properly set jeopardizes the accuracy of the proposed method.

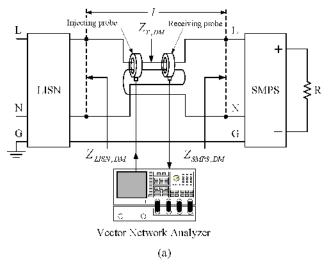

The in-circuit DM and CM impedance measurement setups for the SMPS powered through a LISN are shown in Fig. 2(a) and (b), respectively. The current probes Solar 9144-1N (10 kHz– 100 MHz) and the Schaffner CPS-8455 (10 kHz–1000 MHz) are chosen for the noise injection and detection, respectively. The VNA R&S ZVB8 (300 kHz–8 GHz) is selected for the measurement of the voltage ratio,  $V_{p1}/V_{p2}$ .

Using the aforementioned setups, the DM and CM impedances of the LISN (acting as a noise sink) and the SMPS (acting as a noise source) can be extracted through the following procedure:

1) Premeasurement calibration process: The setup impedances ( $Z_{setup,DM}$  and  $Z_{setup,CM}$ ) and the frequency-dependent coefficients ( $K_{DM}$  and  $K_{CM}$ ) of

Fig. 2. In-circuit measurement setup. (a) DM. (b) CM.

the measurement setups of Fig. 2(a) and (b) will be determined according to the procedure outlined in [17]. Once these parameters are known, the measurement setup is ready to measure any unknown impedance using (4).

- 2) Measurement of the noise termination impedances  $(Z_{\text{LISN},\text{DM}} \text{ and } Z_{\text{LISN},\text{CM}})$ : As the SMPS is powered through the LISN, the LISN acts as a termination for the SMPS noise. To measure the LISN impedance, the SMPS will be replaced by a capacitor, which serves as an ac short at high frequency. In the DM measurement setup, a 1- $\mu$ F capacitor is connected between line and neutral (nodes L and N in Fig. 2 (a), with SMPS removed). In the CM measurement setup, a 1- $\mu$ F capacitor is connected between neutral (nodes L and R in Fig. 2 (a), with SMPS removed). In the CM measurement setup, a 1- $\mu$ F capacitor is connected between neutral and ground [nodes L and G in Fig. 2(b)] and another 1- $\mu$ F capacitor is connected between neutral and ground [nodes N and G in Fig. 2(b)], and the SMPS is removed. The DM and CM impedances of the LISN can be determined by means of (4).

- 3) Measurement of the noise source impedances ( $Z_{\text{SMPS,DM}}$ ) and  $Z_{\text{SMPS,CM}}$ ): In Fig. 2(a) and (b), the measured impedance using the two-probe setup is the total impedance in the circuit loop; we designate such measured impedances as  $Z_{T,\text{DM}}$  and  $Z_{T,\text{CM}}$ . With the known setup impedance obtained from step 1 and the known LISN impedance from step 2, the respective DM and CM impedances of the noise source (SMPS) can be found as follows:

$$Z_{\rm SMPS,DM} = Z_{T,\rm DM} - Z_{\rm LISN,DM} - Z_{\rm setup,DM}$$

(5)

$$Z_{\rm SMPS,CM} = Z_{T,CM} - Z_{\rm LISN,CM} - Z_{\rm setup,CM}.$$

(6)

As an example, an SMPS (VTM22WB, 15 W, +12 Vdc/ 0.75 A, 12 Vdc/0.5 A) is powered through a LISN (Electro-Metrics MIL 5-25/2) and characterized by means of the setups shown in Fig. 2(a) and (b). The DM and CM impedances of the LISN (noise termination) and the SMPS (noise source) are determined with steps 1–3 described earlier.

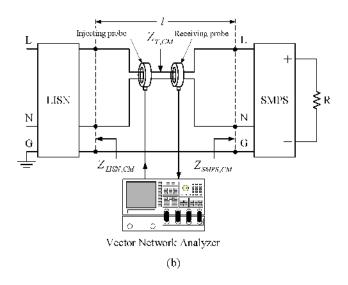

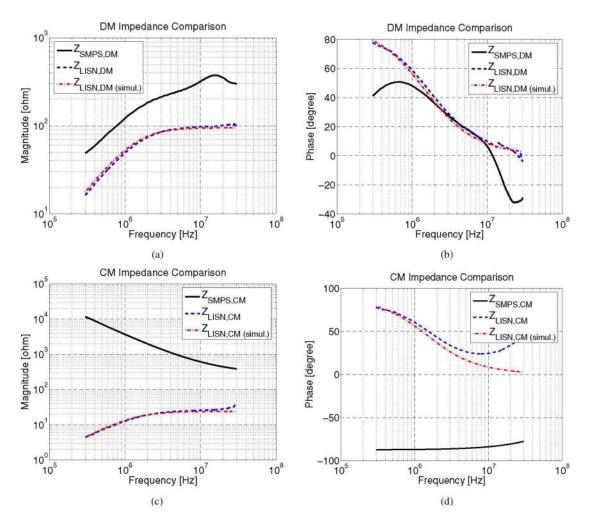

Since the LISN schematics and component values are provided by the manufacturers or standards, the DM and CM impedances of the LISN can be readily calculated. For comparison purposes, the simulated DM and CM impedances of the LISN using the datasheet provided by manufacturer are also plotted as shown in Fig. 3(a)-(d). Fig. 3(a) and (b) shows the magnitudes and phases of the measured LISN and SMPS impedances for the DM, respectively. Fig. 3(c) and (d) shows the magnitudes and phases of the measured LISN and SMPS impedances for the CM. From Fig. 3(a) and (b), the DM SMPS impedance magnitude is higher than the DM LISN impedance by a few ten  $\Omega$  to a few hundred  $\Omega$ , and their phases are spanning approximately 90° over the frequency range of measurements. Fig. 3(c) and (d) shows that the CM SMPS impedance is capacitive and rather regular over the frequency range of measurements, while the CM LISN impedance shows a phase change not easily explainable in terms of elementary circuit equivalents. With the known magnitudes and phases of the noise source (SMPS) and noise termination (LISN) impedances, systematic design of an EMI filter to meet a specific conducted EMI limit becomes possible.

#### III. EMI FILTER DESIGN PROCEDURE

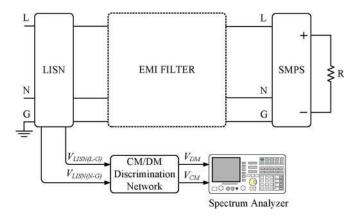

The same SMPS mentioned earlier is used to guide the reader throughout the design procedure. The intended conducted EMI limit to be met by the SMPS is the CISPR 22 Class B limit [2]. The LISN specified by this standard can only measure the total conducted emissions consisting of the both DM and CM components. Therefore, a discrimination network is needed to separate the DM and CM components from the LISN so that they can be measured separately [18] and used to set the required DM and CM filter insertion losses. The measurement setup is shown in Fig. 4 and a HP 8595E spectrum analyzer (9 kHz–6.5 GHz bandwidth, and peak detection mode) is chosen for the conducted emissions measurement.

Fig. 3. Measured LISN and SMPS impedances. (a) DM magnitude. (b) DM phase. (c) CM magnitude. (d) CM phase. LISN impedances (dashed lines) are compared with theoretical values (dash-dotted lines) simulated from component values supplied by the manufacturer.

Fig. 4. Conducted EMI measurement scheme with a CM/DM discrimination network.

## A. Determination of the Required Insertion Losses

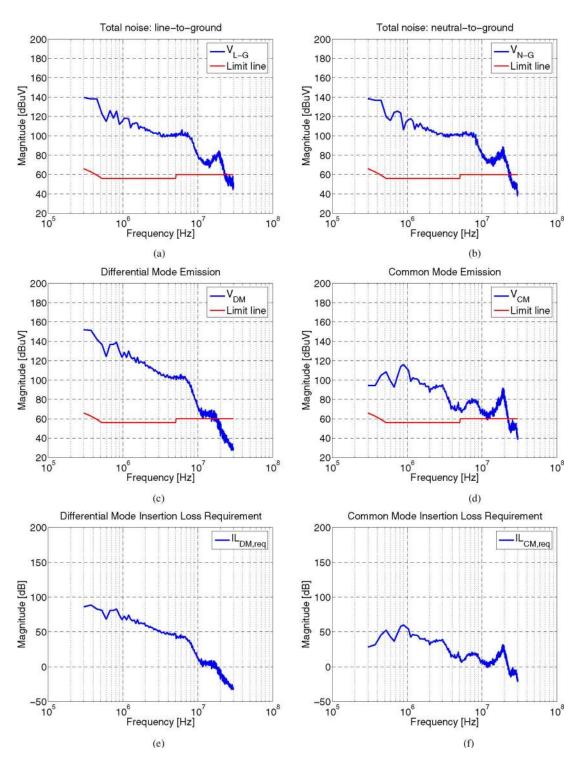

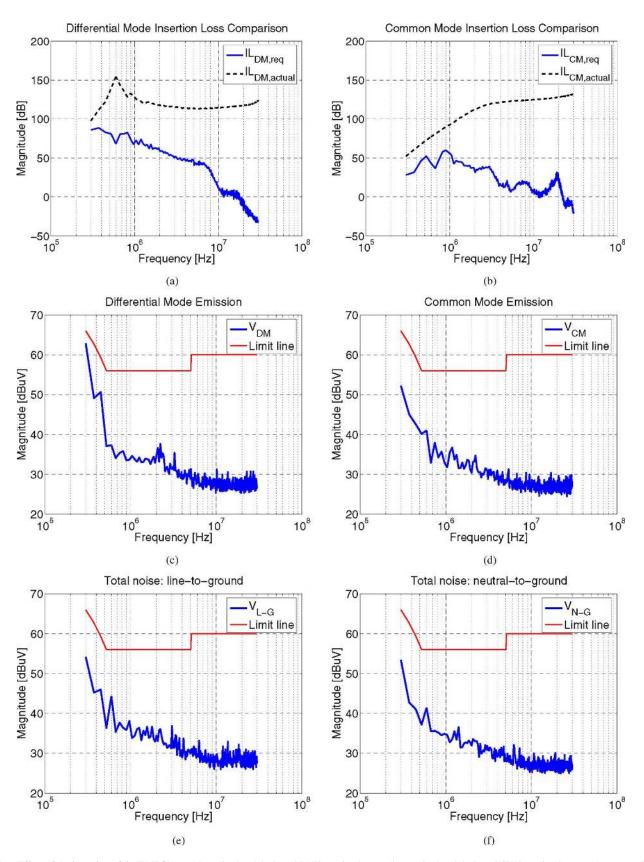

The conducted emissions of the SMPS without the filter are measured with the LISN alone. The line-to-ground and neutralto-ground conducted emissions are shown in Fig. 5(a) and (b), respectively. Obviously, the SMPS can never meet the required EMI limit without an EMI filter. With the help of the discrimination network proposed in [18], the DM and CM conducted emissions of the SMPS without the filter are measured and shown in Fig. 5(c) and (d), respectively. Thus, the required DM and CM filter insertion losses can be found by subtracting the standard limit, i.e.,

$$IL_{DM,reg} = V_{DM} [dB\mu V] - V_{LIMIT} [dB\mu V]$$

(7)

$$IL_{CM,req} = V_{CM}[dB\mu V] - V_{LIMIT}[dB\mu V]$$

(8)

where

- $V_{\rm DM}$  measured DM emission from SMPS without filter [dB $\mu$ V];

- $V_{\rm CM}$  measured CM emission from SMPS without filter [dB $\mu$ V];

- $V_{\text{LIMIT}}$  CISPR 22 Class B conducted emission limit [dB $\mu$ V].

The required DM and CM filter insertion losses are plotted in Fig. 5(e) and (f), respectively.

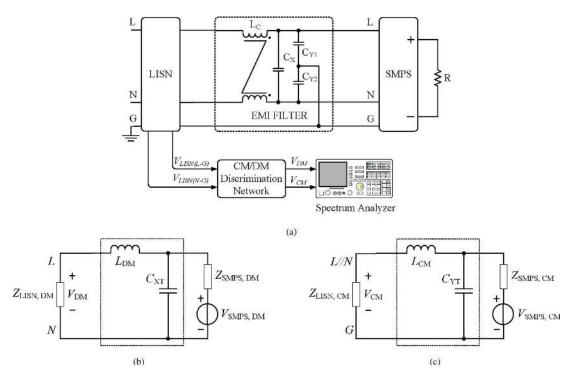

# B. Selection of the DM/CM Filter Topologies Based on Termination Impedances

The adopted filter configuration is illustrated in Fig. 6(a). The filter is composed of one CM choke  $(L_C)$ , one DM capacitor  $(C_X)$ , and two CM capacitors  $(C_{Y1} \text{ and } C_{Y2})$ . Due to the leakage inductance of  $L_C$ , it behaves as two DM inductors in the line

Fig. 5. Measured conducted emissions without filter. (a) Line-to-ground. (b) Neutral-to-ground. (c) DM. (d) CM. (e) Required DM filter insertion loss. (f) Required CM filter insertion loss.

and neutral lines. This particular configuration, with the capacitors facing the SPMS side, is needed in order to achieve the optimal filter attenuation, since the DM and CM SMPS impedances are higher than the corresponding LISN impedances, as clearly documented by Fig. 3(a) and (c). In fact, the capacitor, to be effective, must be placed in parallel to a high impedance and the inductor must be connected in series with a low impedance [19]. The DM and CM interpretation of Fig. 6(a) leads to two separate circuits, shown in Fig. 6(b) and (c), respectively. Fig. 6(b) presents the DM-suppressing part of the filter and is composed of  $L_{\rm DM}$ , which is the DM inductance due to  $L_C$ , and by  $C_{XT}$ , which represents the effective DM capacitor ( $C_{Y1}$  and  $C_{Y2}$ in series and then in parallel with  $C_X$ ). Fig. 6(c) presents the CM-suppressing part of the filter and is composed by  $L_{\rm CM}$ ,

Fig. 6. Conducted EMI measurement in the presence of the EMI filter. (a) Test setup with CM/DM discrimination network. (b) DM part of the filter. (c) CM part of the filter.

which is the CM inductance due to  $L_C$  and by  $C_{YT}$ , which is the effective CM capacitor ( $C_{Y1}$  and  $C_{Y2}$  in parallel).

From Fig. 6(b) and (c), the expressions of DM and CM filter insertion losses can be evaluated, according to [7], [8]

$$IL_{DM,estimate} = 20 \log \left| s^2 \left( \frac{L_{DM} C_{XT} Z_{SMPS,DM}}{Z_{LISN,DM} + Z_{SMPS,DM}} \right) + s \left( \frac{L_{DM} + C_{XT} Z_{SMPS,DM} Z_{LISN,DM}}{Z_{LISN,DM} + Z_{SMPS,DM}} \right) + 1 \right|$$

(9)

$$IL_{CM,estimate} = 20 \log \left| s^2 \left( \frac{L_{CM} C_{YT} Z_{SMPS,CM}}{Z_{LISN,CM} + Z_{SMPS,CM}} \right) + s \left( \frac{L_{CM} + C_{YT} Z_{SMPS,CM} Z_{LISN,CM}}{Z_{LISN,CM} + Z_{SMPS,CM}} \right) + 1 \right|$$

(10)

where

$= j2\pi f;$ s $C_{YT}$  $= C_{Y1} / / C_{Y2} [F];$  $C_{XT}$  $= C_X / (C_{Y1} + C_{Y2})$ [F];  $L_{\rm CM}$ CM inductance of CM choke [H];  $L_{\rm DM}$ equivalent DM inductance of CM choke [H]; DM SMPS impedance  $[\Omega]$ ;  $Z_{\rm SMPS,DM}$ CM SMPS impedance  $[\Omega]$ ;  $Z_{\rm SMPS,CM}$ DM LISN impedance  $[\Omega]$ ;  $Z_{\rm LISN,DM}$  $Z_{\text{LISN,CM}}$ CM LISN impedance  $[\Omega]$ .

# C. CM Filter Design

The CM capacitor is usually constrained by safety requirements, e.g., EN 60335-1 Class I portable, and therefore, the maximum capacitance connected to ground cannot exceed about 4700 pF on each phase for 250-Vac 50-Hz mains [20]. Hence,  $C_{Y1}$  and  $C_{Y2}$  are chosen to be 1000 pF each. Substituting the known CM LISN and SMPS impedances and the chosen CM capacitors into (10) and assuming that the filter elements are ideal, the required CM inductance that could provide the CM filter insertion loss higher than IL<sub>CM,req</sub>, indicated in Fig. 5(f), is about 2 mH. Hence, two 1000-pF Class Y capacitors and a 2-mH CM choke (NEC/TOKIN SC-02-10A1) are chosen for the CM filter.

In contrast, the conventional design approach [9], not taking into account the SMPS and LISN impedances, leads to a possible overdesign of the CM choke. The IL<sub>CM,req</sub> needs to be 38.85 dB at 300 kHz; the cutoff frequency can be found by  $f_{c,CM} =$  $f_{n,CM}/10^{IL_{CM,req}/\beta} = 32$  kHz, where  $f_{n,CM} = 300$  kHz and  $\beta = 40$  dB/decade [10], [21]. Substituting the value  $C_{YT} =$ 2000 pF and  $f_{c,CM} = 32$  kHz into the cutoff frequency formula ( $f_{c,CM} = 1/2\pi\sqrt{L_{CM}C_{YT}}$ ) of the simplistic approach, the needed CM choke results in about 12 mH, which is six times larger than the inductance required by the proposed method. The reduction of the inductance value introduced by the proposed method corresponds to significant size and weight savings.

## D. DM Filter Design

Once the CM choke and the CM capacitors are selected, we proceed with the DM filter design. For the DM capacitor, since there is no safety issue, the value can be chosen to be as large as possible but larger capacitors usually exhibit a low self-resonant frequency [22]. Substituting the known DM LISN and SMPS impedances and the measured DM inductance of the CM choke ( $L_{\rm DM} = 17.6 \ \mu {\rm H}$ ) into (9), the required

Fig. 7. DM filter design based on extracted DM impedance according to conventional approach [14]. (a) DM impedance magnitude. (b) Required and estimated DM insertion losses.

DM capacitor that could provide the necessary DM filter insertion loss higher than  $IL_{DM,req}$ , indicated in Fig. 5(e), is about 1.5  $\mu$ F.

On the contrary, the conventional design approach (e.g., [9]), not taking into account the SMPS and LISN impedances, leads to a possible overdesign of the DM capacitor. If we apply the conventional design procedure to our example, we need to satisfy the constraint of the IL<sub>DM,req</sub> = 86 dB at 300 kHz; hence, the cutoff frequency is given by  $f_{c,DM} = f_{n,DM}/10^{\text{IL}_{DM,req}/\beta} =$ 2 kHz, where  $f_{n,DM} = 300$  kHz and  $\beta = 40$  dB/decade [10], [21]. Accounting for the already-determined choke inductance  $L_{DM} = 17.6 \ \mu\text{H}$ , the cutoff frequency formula  $f_{c,DM} =$  $1/2\pi \sqrt{L_{DM}C_X}$  of the simplistic approach allows to determine the DM capacitor value, resulting in about 319  $\mu$ F, which is not only an impractical value, but also significantly larger than the capacitance required by the proposed method. This problem is also discussed in [9], and the advocated solution consists in adding DM chokes, which correspond to overdesigning an EMI filter with more components than necessary.

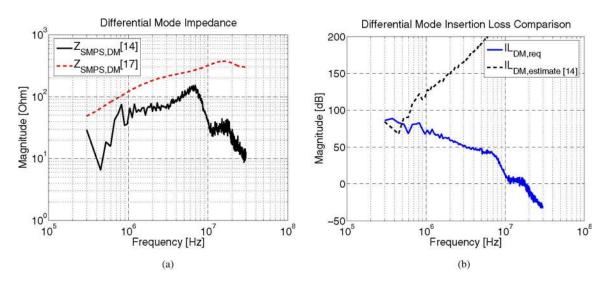

As a further step, let us discuss the impact of an incomplete determination of the load impedances of the filter on the compliance prediction. For comparison purposes, DM impedance is measured according to the procedure proposed by [14] and is compared with the measured results obtained from Section II [17] [see Fig. 7(a)]. This approach is coherent with what is commonly done in practice, i.e., to measure only the magnitude of the noise source impedance, and then using it in the insertion loss expressions as if the impedances were totally resistive [13]. Although [14] suggests to reconstruct the phase by means of

the classical Hilbert transform approach, in reality, often only magnitude of the noise source impedances is taken into consideration in order to avoid complex mathematical manipulations. The use of such incompletely determined DM impedance of SMPS in (9) indicates that the designed filter is unable to meet the IL<sub>DM,req</sub> for frequencies below 500 kHz, as illustrated in Fig. 7(b). The required DM capacitor that could provide the necessary DM filter insertion loss larger than IL<sub>DM,req</sub> amounts to about 4  $\mu$ F, which is about three times larger than the capacitance required by the proposed method. Again, the reduction of the capacitance value required by the proposed method corresponds to cost saving.

It is worth noting that because the CM noise source impedance is capacitive in nature and in the range of several kiloomega, which is much larger than the CM impedance of the LISN (25  $\Omega$ ) [12], CM impedance determination according to [14] has no significant effect on the CM filter design.

# E. Actual Insertion Losses and Validations

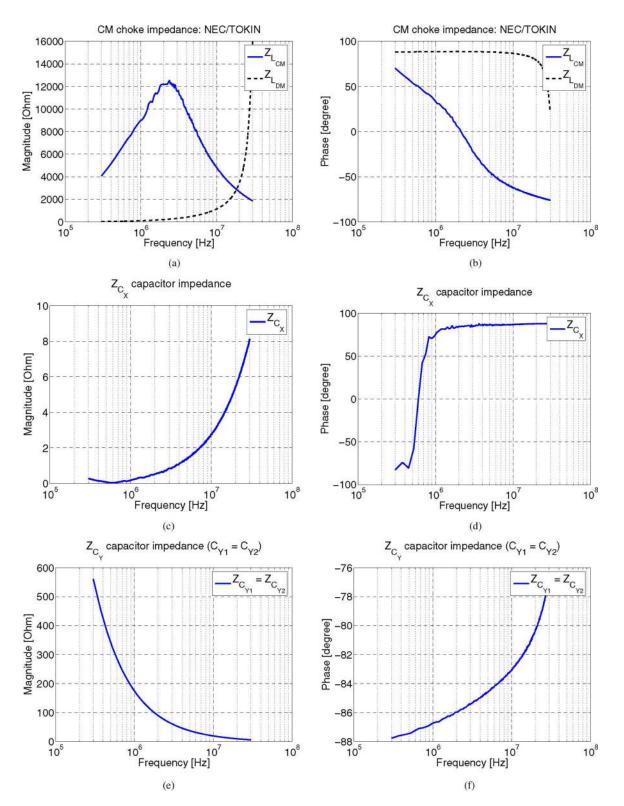

The impedance behavior of the filter components, chosen according to the aforementioned considerations, were measured by means of a HP 4396B impedance analyzer (100 kHz–1.8 GHz), and the results are shown in Fig. 8(a)–(f). The actual insertion losses of the DM and CM filters of Fig. 6(b) and (c) can be worked out as an adaptation of (9) and (10) with the inclusion of the parasitic effects of the filter components [7], [8], and (11) as well as (12) shown at the bottom of the page, where

$Z_{L_{DM}} \quad \text{Effective DM impedance of the CM choke } [\Omega];$  $Z_{L_{CM}} \quad \text{CM impedance of the CM choke } [\Omega];$

$$IL_{DM,actual} = 20 \log \left| \frac{Z_{C_{XT}} \left( Z_{L_{DM}} + Z_{LISN,DM} \right) + Z_{SMPS,DM} \left( Z_{C_{XT}} + Z_{L_{DM}} + Z_{LISN,DM} \right)}{Z_{C_{XT}} \left( Z_{LISN,DM} + Z_{SMPS,DM} \right)} \right|$$

(11)

$$IL_{CM,actual} = 20 \log \left| \frac{Z_{C_{YT}} \left( Z_{L_{CM}} + Z_{LISN,CM} \right) + Z_{SMPS,CM} \left( Z_{C_{YT}} + Z_{L_{CM}} + Z_{LISN,CM} \right)}{Z_{C_{YT}} \left( Z_{LISN,CM} + Z_{SMPS,CM} \right)} \right|$$

(12)

Fig. 8. Measured impedance of the chosen filter components. (a) and (b) CM choke (NEC/TOKIN). (c) and (d)  $C_X = 1.5$ - $\mu$ F capacitance. (e) and (f)  $C_{Y1} = C_{Y2} = 1000$ -pF capacitances.

$Z_{C_{YT}}$  Effective CM impedance of  $C_{Y1}//C_{Y2}[\Omega];$

$Z_{C_{XT}}$  Effective DM impedance of  $C_X //(C_{Y1} + C_{Y2})[\Omega]$ . Using the measured impedances of all the chosen filter com-

ponents [see Fig. 8(a)–(f)], as well as the LISN and SMPS impedance behavior [see Fig. 3(a)–(d)], the actual insertion

losses of the DM and the CM filters [computed by means of (11) and (12)] are plotted in Fig. 9(a) and (b), respectively. For comparison, the required DM and CM filter insertion losses are also shown in the same figures. Both the actual DM and CM filter insertion losses are higher than the required ones, which

Fig. 9. Effect of the insertion of the EMI filter. (a) Required and designed DM insertion losses; (b) required and designed CM insertion losses; (c) measured DM conducted emissions with filter; (d) measured CM conducted emissions with filter; (e) measured total conducted emissions for line-to-ground; (f) measured total conducted emissions for neutral-to-ground.

indicate that the designed EMI filter is able to suppress the DM and CM conducted emissions below the CISPR 22 Class B limit. Fig. 9(c) and (d) shows the measured DM and CM conducted emissions after the designed EMI filter is inserted. Both the DM and CM conducted emissions are below the limit, confirming that the designed EMI filter fulfills the requirement. As a final compliance check, Fig. 9(e) and (f) shows the line-to-ground and the neutral-to-ground conducted emissions, respectively, and their results indicate that the filtered SMPS complies with the regulations limits.

## IV. CONCLUSION

Information on the noise source and termination impedances of an SMPS connected to mains has been proven to be a useful input for designing an optimal EMI filter to meet a specific EMI limit in a systematic manner. The noise source (SMPS) and noise termination (LISN) impedances are measured by means of a two-probe measurement approach under in-circuit operating conditions. Both the DM and CM filter insertion losses for any EMI filter can be determined accurately so that the designer has a very clear picture of the EMI filter insertion loss characteristics. Undoubtedly, designing EMI filters without taking into account the termination impedances or with adopting incomplete measurement of them allow filtered SMPS to pass the regulation limits. However, they are overdesigned, which leads to bulky and costly final products. On the contrary, with the proposed EMI filter design methodology, the appropriate filter configurations and the optimal filter component values can be systematically chosen. Hence, optimal results can be achieved without incurring excessive design costs for EMI compliance. However, the proposed EMI filter design methodology does not take into account mode conversion (CM to DM or DM to CM) that can arise due to asymmetric design and the parasitic coupling of the filter components. A careful layout design is also needed in order to minimize the mode conversion so as to assure EMI compliance of the final product.

## References

- R. Redl, "Electromagnetic environmental impact of power electronics equipment," *Proc. IEEE*, vol. 89, no. 6, pp. 926–938, Jun. 2001.

- [2] Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment, CISPR 22, 2004.

- [3] Specification for Radio Disturbance and Immunity Measuring Apparatus and Methods Part 1: Radio Disturbance and Immunity Measuring Apparatus, CISPR 16-1, 1999.

- [4] L. Tihanyi, *Electromagnetic Compatibility in Power Electronics*. Piscataway, NJ: IEEE Press, 1997.

- [5] J. A. Ferreira, P. R. Willcock, and S. R. Holm, "Sources, paths and traps of conducted EMI in switch mode circuits," in *Proc. 1997 IEEE Ind. Appl. Conf.*, pp. 1584–1591.

- [6] B. Garry and R. Nelson, "Effect of impedance and frequency variation on insertion loss for a typical power line filter," in *Proc. 1998 IEEE EMC Symp.*, pp. 691–695.

- [7] B. Audone and L. Bolla, "Insertion loss of mismatched EMI suppressors," *IEEE Trans. Electromagn. Compat.*, vol. EMC-20, no. 3, pp. 384–389, Sep. 1978.

- [8] S. M. Vakil, "A technique for determination of filter insertion loss as a function of arbitrary generator and load impedances," *IEEE Trans. Electromagn. Compat.*, vol. EMC-20, no. 2, pp. 273–278, Sep. 1978.

- [9] F.-Y. Shih et al., "A procedure for designing EMI filters for AC line applications," *IEEE Trans. Power Electron.*, vol. 11, no. 1, pp. 170–181, Jan. 1996.

- [10] M. Kumar and V. Agarwal, "Power line filter design for conducted electromagnetic interference using time-domain measurements," *IEEE Trans. Electromagn. Compat.*, vol. 48, no. 1, pp. 178–186, Feb. 2006.

- [11] T. Nussbaumer, M. L. Heldwein, and J. W. Kolar, "Differential mode input filter design for a three-phase buck-type PWM rectifier based on modeling of the EMC test receiver," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1649–1661, Oct. 2006.

- [12] M. J. Nave, Power Line Filter Design for Switched Mode Power Supplies. New York: Van Nostrand Reinhold, 1991.

- [13] S. Ye, W. Eberle, and Y. F. Liu, "A novel EMI filter design method for switching power supplies," *IEEE Trans. Power Electron.*, vol. 19, no. 6, pp. 1668–1678, Nov. 2004.

- [14] D. Zhang, D. Y. Chen, M. J. Nave, and D. Sable, "Measurement of noise source impedance of off-line converters," *IEEE Trans. Power Electron.*, vol. 15, no. 5, pp. 820–824, Sep. 2000.

- [15] D. M. Mitchell, DC-DC Switching Regulator Analysis. New York: McGraw-Hil, 1988, ch. 4.

- [16] K. Y. See and J. Deng, "Measurement of noise source impedance of SMPS using a two probes approach," *IEEE Trans. Power Electron.*, vol. 19, no. 3, pp. 862–868, May 2004.

- [17] V. Tarateeraseth, H. Bo, K. Y. See, and F. Canavero, "Accurate extraction of noise source impedance of SMPS under operating condition," *IEEE Trans. Power Electron.*, vol. 25, no. 1, pp. 111–117, Jan. 2010.

- [18] K. Y. See, "Network for conducted EMI diagnosis," *IEE Electron. Lett.*, vol. 35, no. 17, pp. 1446–1447, Aug. 1999.

- [19] J. J. Goedbloed, *Electromagnetic Compatibility*. Englewood Cliffs, NJ: Prentice-Hall, 1990.

- [20] T. Williams, EMC for Product Designers, 4th ed. London, U.K.: Newnes, 2007.

- [21] R. L. Ozenbaugh, *EMI Filter Design*, 2nd ed. New York: Marcel Dekker, 2001.

- [22] S. Wang, F. C. Lee, and J. D. Van Wyk, "A study of integration of parasitic cancellation techniques for EMI filter design with discrete components," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 3094–3102, Nov. 2008.

Vuttipon Tarateeraseth (S'06) received the B.Eng. degree (second-class Hons.) and M.Eng. degree in electrical engineering from King's Mongkut Institute of Technology Ladkrabang (KMITL), Bangkok, Thailand, in 1998 and 2004, respectively, and the Ph.D. degree in electronics and communications engineering from Politecnico di Torino, Torino, Italy, in February 2010.

He was the Head of the Environment Testing Laboratory, Research and Development Section, Delta Electronics, Thailand for three years. He was also an

electromagnetic compatibility (EMC) engineer for two years under the Joint Development of Teaching Materials to Improve EMC Skills of Academic Staff and Postgraduate Electronic Designers Project funded by European Commission under the ASEAN-EU UNIVERSITY NETWORK PROGRAMME (AUNP). He was a Lecturer at the Department of Electrical Engineering, Srinakharinwirot University, Thailand for three years. His research interests include electromagnetic interference (EMI) reduction techniques, EMC/EMI modeling, EMC measurement techniques, and EMI filter design.

**Kye Yak See** (SM'02) received the B.Eng. degree from the National University of Singapore, Singapore, in 1986 and the Ph.D. degree from Imperial College, London, U.K., in 1997.

He was engaged in various senior technical and management positions in the industry in Singapore, UK, and Hong Kong for eight years. He joined Nanyang Technological University (NTU), Singapore, in 1994, where he is currently an Associate Professor of the School of Electrical and Electronic Engineering. He is also the Deputy Head of

Division of Circuits and Systems and the Director of Electromagnetic Effects Research Laboratory.

Dr. See is the founding Chairman of the IEEE EMC Society Singapore Chapter, a Technical Assessor for Singapore Laboratory Accreditation Scheme, Singapore Accreditation Council (SAC-SINGLAS), and a member of Singapore Technical Committee of EMC and Radio Interference.

**Flavio G. Canavero** (F'07) received the Laurea degree in electronic engineering from the Politecnico di Torino, Torino, Italy, in 1977, and the Ph.D. degree from Georgia Institute of Technology, Atlanta, in 1986.

He is currently a Professor of circuit theory and electromagnetic compatibility (EMC) in the Department of Electronics, Politecnico di Torino. His research interests include signal integrity and EMC. He has significantly contributed to the modeling of circuit and electronic interconnects. He is a Technical

Editor of the *EMC Newsletter*. He is currently a member of the Editorial Boards for several scientific journals. He has authored or coauthored more than 200 papers published in international journals and conference proceedings.

Prof. Canavero is a member of the IEEE Press Editorial Board. He has been the Editor-in-Chief of the IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY. He has been the Chair of the International Union of Radio Science (URSI) Commission E (Noise and Interference). He received the International Business Machines Corporation (IBM) Faculty Award for the triennium 2003–2005, the Intel Research Grant for 2008, and several Best Paper Awards and IEEE recognitions. He has been the Organizer of the Workshop on Signal Propagation on Interconnects (SPI) during 2001–2003 and 2007. He is currently a member of the Scientific Steering Committees of several international conferences in the field of EMC and electrical performance of interconnects and packages.

**Richard Weng-Yew Chang** (M'06) received the Diploma (EEE,Merit) degree from Ngee Ann Polytechnic, Singapore, in March 1987, and the B.Eng and M.Sc. degrees from Nanyang Technological University (NTU), Singapore, in 1994 and 2001, respectively. He was awarded a DSO scholarship in December 2005 to work toward the Ph.D. degree at NTU under the supervision of K. Y. See.

He joined Defense Science Organization now known as "DSO National Laboratories" in 1994 as a Designer in the Weapon Electronics Laboratory,

where he was involved in the development of an airborne embedded digital processing system, and became the Project Lead in numerous hardware designs involving embedded digital signal processing (DSP) digital systems and airborne radar digital system, and is currently the Group Head for Airborne Radar Digital Electronics Team, Division of Guided Systems. His research interests include signal integrity for high-speed digital circuit design, high-speed measurements, practical techniques in design for electromagnetic interference (EMI)/electromagnetic compatibility (EMC) consideration and airborne embedded digital electronics design.