Delft University of Technology

### Targeting static and dynamic workloads with a reconfigurable VLIW processor

Hoozemans, Joost

DOI 10.4233/uuid:c3be6373-f4f2-4865-b3f0-750bfb17871e

Publication date 2018 **Document Version**

Final published version

Citation (APA) Hoozemans, J. (2018). Targeting static and dynamic workloads with a reconfigurable VLIW processor. https://doi.org/10.4233/uuid:c3be6373-f4f2-4865-b3f0-750bfb17871e

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Targeting static and dynamic workloads with a reconfigurable VLIW processor

# Targeting static and dynamic workloads with a reconfigurable VLIW processor

## Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. dr. ir. T.H.J.J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op donderdag 21 juni 2018 om 10:00 uur

door

## **Joost Johannes HOOZEMANS**

Master of Science in Computer Engineering, Technische Universiteit Delft, geboren te Delft, Nederland. Dit proefschrift is goedgekeurd door de

promotor: prof. dr. K.L.M. Bertels copromotor: dr. ir. J.S.S.M. Wong

Samenstelling promotiecommissie:

| Rector Magnificus,       | voorzitter                                |

|--------------------------|-------------------------------------------|

| Prof. dr. K.L.M. Bertels | Technische Universiteit Delft, promotor   |

| Dr. ir. J.S.S.M. Wong    | Technische Universiteit Delft, copromotor |

*Onafhankelijke leden:* Prof. dr. H.P. Hofstee Prof. dr. H. Corporaal Prof. dr. -ing. M. Hübner Prof. dr. ir. C. Vuik Prof. dr. ir. S. Hamdioui

Technische Universiteit Delft Technische Universiteit Eindhoven Ruhr-Universität Bochum, Duitsland Technische Universiteit Delft Technische Universiteit Delft, reservelid

*Overige leden:* Dr. ir. Z. Al-Ars

Technische Universiteit Delft

This work has been supported by the ALMARVI European Artemis project nr. 621439.

*Keywords:* Computer architecture, VLIW processor, dynamically reconfigurable, polymorphic, embedded computing, FPGA, streaming

Printed by: Ipskamp printing

*Front & Back:* Conceptual diagram created by Bart Kallenbach for the Dig-it! research exhibition.  $\rho$ -VEX logo by Thijs van As, adapted by Jeroen van Straten.

Copyright © 2018 by J.J. Hoozemans

ISBN 978-94-6366-049-5

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

# Contents

| Sι | imm   | ary                                                           | ix   |

|----|-------|---------------------------------------------------------------|------|

| Sa | men   | vatting                                                       | xi   |

| Ac | cknov | wledgements                                                   | xiii |

| 1  | Intr  | oduction                                                      | 1    |

|    |       | Dynamic workloads call for dynamic processors                 | 2    |

|    | 1.2   | Leveraging design-time customization for highly static work-  |      |

|    |       | loads                                                         |      |

|    | 1.3   | Embedded execution platforms                                  |      |

|    |       | 1.3.1 General-purpose                                         |      |

|    |       | 1.3.2 Application-Specific                                    |      |

|    |       | 1.3.3 Reconfigurable                                          |      |

|    | 1.4   | Workload analysis                                             |      |

|    |       | 1.4.1 Requirements                                            |      |

|    |       | 1.4.2 Parallelism                                             |      |

|    |       | 1.4.3 Code characteristics                                    |      |

|    | 1.5   | Problem formulation and scope                                 |      |

|    |       | 1.5.1 Software: Workloads                                     |      |

|    |       | 1.5.2 Hardware: Reconfigurable processors                     |      |

|    |       | 1.5.3 Scheduling: Tasks and processor configurations          |      |

|    | 1.6   | Proposed platform: a design-time configurable, run-time param |      |

|    |       | able VLIW processor                                           |      |

|    |       | 1.6.1 Static (design-time) reconfigurability                  |      |

|    |       | 1.6.2 Dynamic (run-time) parameterization                     |      |

|    |       | 1.6.3 Environment                                             |      |

|    |       | 1.6.4 Platform overview                                       |      |

|    | 1.7   | II ···································                        |      |

|    |       | 1.7.1 Modeling & Simulation                                   |      |

|    |       | 1.7.2 Using FPGA technology                                   |      |

|    |       | 1.7.3 Code characterization method                            |      |

|    |       | 1.7.4 A runtime for scheduling tasks and configurations       |      |

|    |       | 1.7.5 Workload generation                                     |      |

|    |       | 1.7.6 Benchmarks                                              |      |

|    | 1.8   | Contributions and thesis outline                              | 29   |

| Pa | rt 1 | - Static workloads, statically reconfigurable platform                                                                                                                                                                                | 33                                                             |

|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

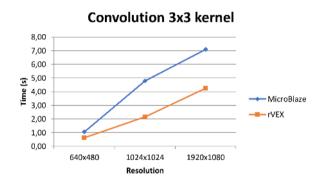

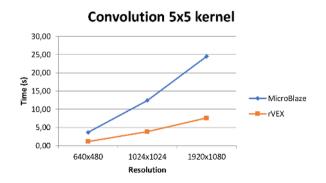

| 2  | Usiı | ng VLIW softcore processors for image processing                                                                                                                                                                                      | 35                                                             |

|    | 2.1  | Introduction.                                                                                                                                                                                                                         | 36                                                             |

|    | 2.2  | Related work                                                                                                                                                                                                                          | 37                                                             |

|    | 2.3  | The $\rho$ -VEX platform                                                                                                                                                                                                              | 38                                                             |

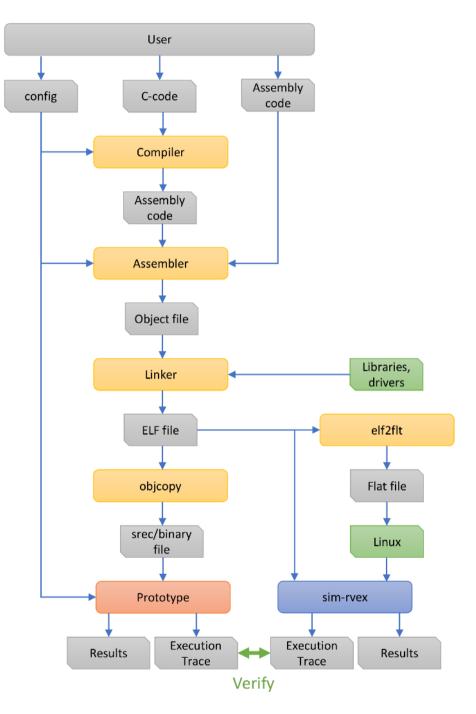

|    |      | 2.3.1 The VEX system: ISA and toolchain                                                                                                                                                                                               | 38                                                             |

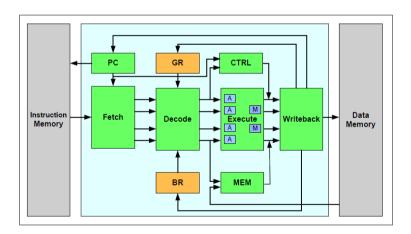

|    |      | 2.3.2 The $\rho$ -VEX VLIW processor                                                                                                                                                                                                  | 38                                                             |

|    | 2.4  | Image processing applications                                                                                                                                                                                                         |                                                                |

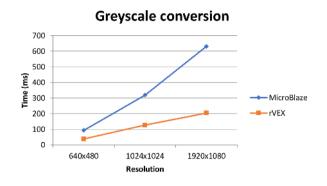

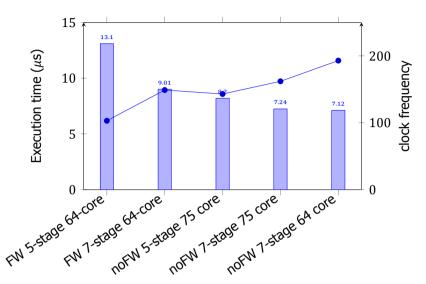

|    | 2.5  | Results and discussion                                                                                                                                                                                                                | 40                                                             |

|    | 2.6  | Conclusions                                                                                                                                                                                                                           | 42                                                             |

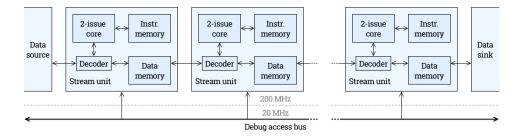

| 3  | A st | treaming FPGA computation fabric                                                                                                                                                                                                      | 43                                                             |

| -  |      | Introduction                                                                                                                                                                                                                          |                                                                |

|    |      | Related work                                                                                                                                                                                                                          |                                                                |

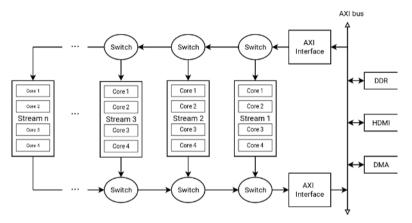

|    |      | Implementation.                                                                                                                                                                                                                       |                                                                |

|    | 0.0  | 3.3.1 Processing elements                                                                                                                                                                                                             |                                                                |

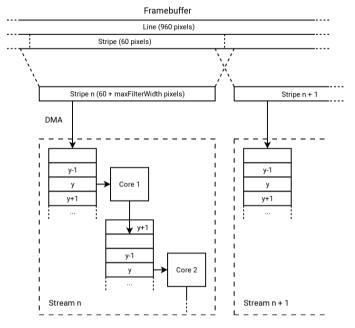

|    |      | 3.3.2 Memory hierarchy                                                                                                                                                                                                                |                                                                |

|    |      | 3.3.3 Platform                                                                                                                                                                                                                        |                                                                |

|    | 3.4  | Experimental setup                                                                                                                                                                                                                    |                                                                |

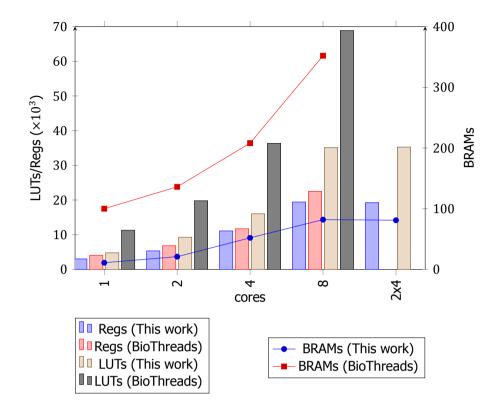

|    |      | Evaluation results                                                                                                                                                                                                                    |                                                                |

|    |      | 3.5.1 Resource utilization                                                                                                                                                                                                            |                                                                |

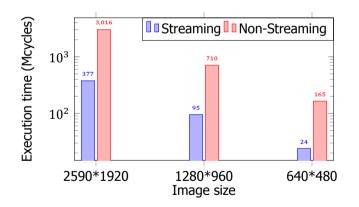

|    |      | 3.5.2 Image processing performance                                                                                                                                                                                                    |                                                                |

|    | 3.6  | Conclusions                                                                                                                                                                                                                           |                                                                |

| 4  | Fra  | me-Based Programming, Stream-Based Processing                                                                                                                                                                                         | 53                                                             |

|    |      | Introduction                                                                                                                                                                                                                          |                                                                |

|    |      | Related work                                                                                                                                                                                                                          |                                                                |

|    | 1.4  | 4.2.1 Optimizing/accelerating image processing workloads                                                                                                                                                                              |                                                                |

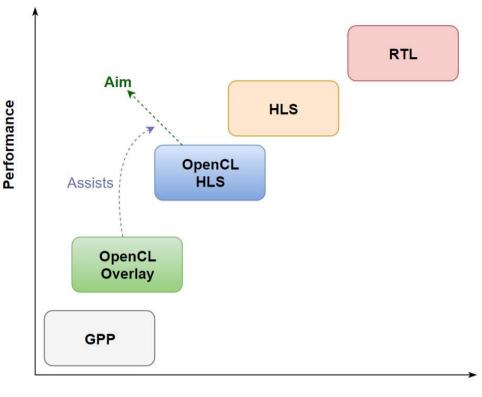

|    |      | 4.2.2 FPGA acceleration                                                                                                                                                                                                               |                                                                |

|    |      | 4.2.3 FPGA overlays.                                                                                                                                                                                                                  |                                                                |

|    |      | 4.2.4 FPGA image processing overlays.                                                                                                                                                                                                 |                                                                |

|    |      | 4.2.5 Integration frameworks                                                                                                                                                                                                          |                                                                |

|    | 43   | Approach                                                                                                                                                                                                                              |                                                                |

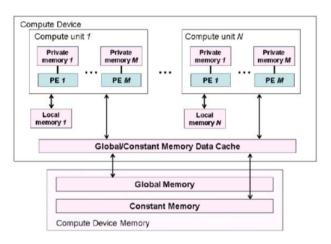

|    |      | 4.3.1 OpenCL's view on parallel computing.                                                                                                                                                                                            |                                                                |

|    |      | 4.3.2 OpenCL memory model                                                                                                                                                                                                             |                                                                |

|    |      |                                                                                                                                                                                                                                       |                                                                |

|    |      |                                                                                                                                                                                                                                       |                                                                |

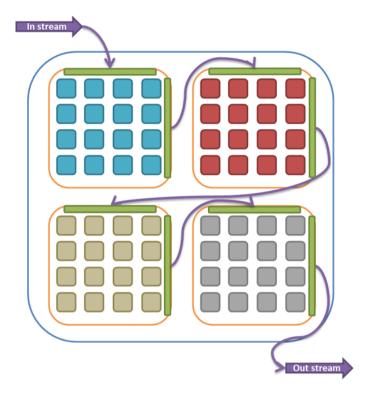

|    |      | 4.3.3 Streaming data and OpenCL                                                                                                                                                                                                       | 59                                                             |

|    | 4.4  | <ul><li>4.3.3 Streaming data and OpenCL</li></ul>                                                                                                                                                                                     | 59<br>60                                                       |

|    | 4.4  | 4.3.3 Streaming data and OpenCL4.3.4 OpenCL data architecture.Implementation - Hardware                                                                                                                                               | 59<br>60<br>61                                                 |

|    | 4.4  | 4.3.3 Streaming data and OpenCL4.3.4 OpenCL data architecture.Implementation - Hardware4.4.1 Processing element.                                                                                                                      | 59<br>60<br>61<br>62                                           |

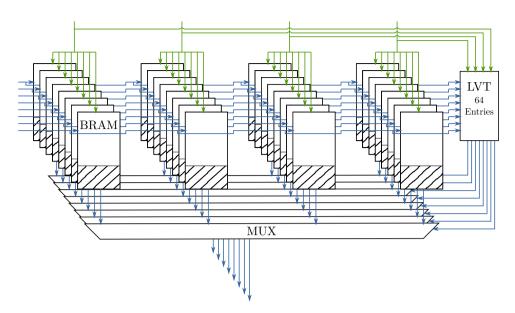

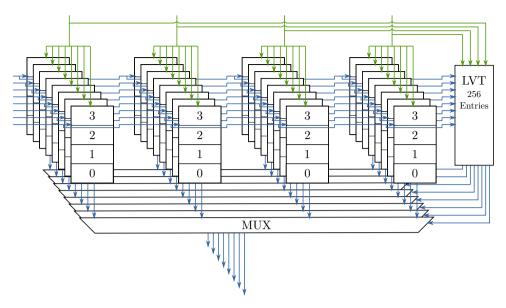

|    | 4.4  | 4.3.3 Streaming data and OpenCL4.3.4 OpenCL data architecture.Implementation - Hardware4.4.1 Processing element.4.4.2 Memory structure                                                                                                | 59<br>60<br>61<br>62<br>62                                     |

|    |      | 4.3.3 Streaming data and OpenCL4.3.4 OpenCL data architecture.Implementation - Hardware4.4.1 Processing element.4.4.2 Memory structure4.4.3 Interfaces                                                                                | 59<br>60<br>61<br>62<br>62<br>64                               |

|    |      | 4.3.3 Streaming data and OpenCL4.3.4 OpenCL data architecture.Implementation - Hardware4.4.1 Processing element.4.4.2 Memory structure4.4.3 InterfacesImplementation - Software                                                       | 59<br>60<br>61<br>62<br>62<br>64<br>65                         |

|    |      | 4.3.3 Streaming data and OpenCL4.3.4 OpenCL data architecture.Implementation - Hardware4.4.1 Processing element.4.4.2 Memory structure4.4.3 InterfacesImplementation - Software4.5.1 Compilation and operation                        | 59<br>60<br>61<br>62<br>62<br>64<br>65<br>65                   |

|    |      | 4.3.3 Streaming data and OpenCL4.3.4 OpenCL data architecture.Implementation - Hardware4.4.1 Processing element.4.4.2 Memory structure4.4.3 InterfacesImplementation - Software                                                       | 59<br>60<br>61<br>62<br>62<br>64<br>65<br>65<br>65             |

|    |      | 4.3.3 Streaming data and OpenCL4.3.4 OpenCL data architecture.Implementation - Hardware4.4.1 Processing element.4.4.2 Memory structure4.4.3 InterfacesImplementation - Software4.5.1 Compilation and operation4.5.2 Buffer management | 59<br>60<br>61<br>62<br>62<br>64<br>65<br>65<br>65<br>66<br>67 |

| Cont | ents |

|------|------|

|------|------|

|    |                                                                                                       | Experiments/Evaluation                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

|----|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Pa | rt 2                                                                                                  | - Dynamic workloads, dynamically reconfigurable platform                                                                                                                                                                                                                                                                                                                     | 73                                                                         |

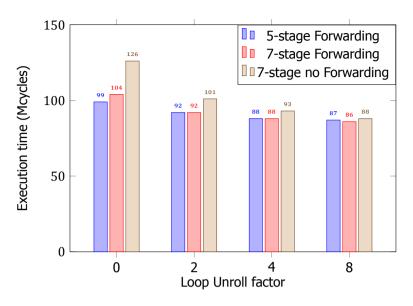

| 5  | 5.1<br>5.2                                                                                            | Iuating auto-adaptation methodsIntroductionApproach5.2.1 Target processor5.2.2 Proposed auto-adapting method                                                                                                                                                                                                                                                                 | 77<br>77<br>78                                                             |

|    | 5.3                                                                                                   | Implementation5.3.1Common5.3.2Window-based monitoring5.3.3BTCB5.3.4Phase change annotationsSupervision                                                                                                                                                                                                                                                                       | 80<br>81<br>81<br>82                                                       |

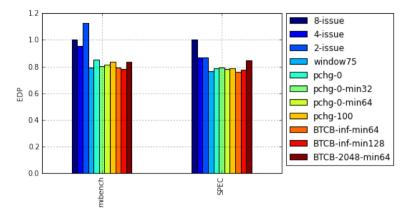

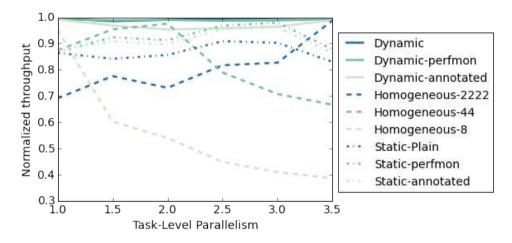

|    |                                                                                                       | Evaluation5.4.1Experimental setup5.4.2ResultsRelated work                                                                                                                                                                                                                                                                                                                    | 82<br>82                                                                   |

|    |                                                                                                       | Conclusions                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

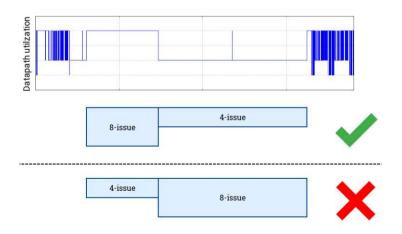

| 6  |                                                                                                       | pting to dynamic workloads                                                                                                                                                                                                                                                                                                                                                   | 87                                                                         |

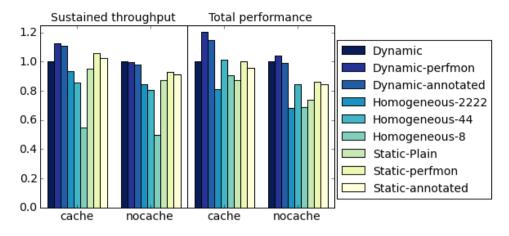

|    | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> </ul> | pring to dynamic workloadsIntroductionBackgroundThe $\rho$ -VEX polymorphic VLIW processorApproach6.4.1 On-line profiling6.4.2 Compiler annotations6.4.3 Datapath assignmentExperiments/Evaluation6.5.1 Annotation overhead and coverage6.5.2 Throughput & PerformanceRelated work6.6.1 Phase detection and workload characterization6.6.2 Polymorphic processorsConclusions | 88<br>89<br>90<br>91<br>91<br>92<br>92<br>93<br>94<br>94<br>98<br>98<br>98 |

| 7  | Eva                                                                                                   | luating real-time properties                                                                                                                                                                                                                                                                                                                                                 | 103                                                                        |

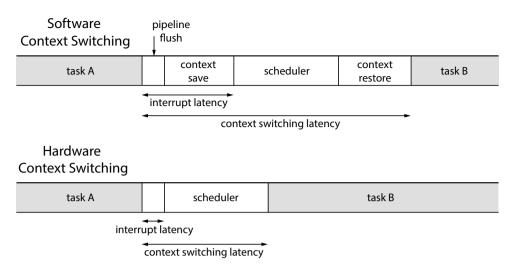

|    | 7.2<br>7.3<br>7.4<br>7.5                                                                              | Introduction                                                                                                                                                                                                                                                                                                                                                                 | 106<br>107<br>108<br>110                                                   |

|    |                                                                                                       | Conclusions                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

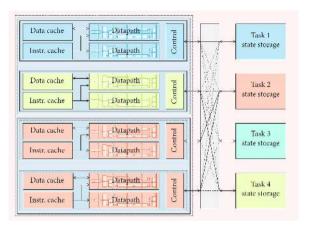

| 8  | A pl   | atform for mixed-criticality systems                     | 115 |

|----|--------|----------------------------------------------------------|-----|

|    | 8.1    | Introduction                                             | 116 |

|    |        | Background                                               |     |

|    |        | 8.2.1 Processing platform                                |     |

|    |        | 8.2.2 Scheduling methodology for dynamic processors      | 120 |

|    | 8.3    | System architecture for Mixed-criticality systems        | 122 |

|    |        | 8.3.1 Spatial isolation                                  |     |

|    |        | 8.3.2 Temporal isolation                                 |     |

|    |        | 8.3.3 Assigning unallocated cycles to non-critical tasks |     |

|    | 8.4    | Scheduling approach                                      |     |

|    |        | 8.4.1 Worst-case schedule creation                       |     |

|    |        | 8.4.2 Improving average-case performance                 |     |

|    | 8.5    | Experimental setup                                       |     |

|    | 8.6    | Results                                                  |     |

|    |        | 8.6.1 Schedulability.                                    |     |

|    |        | 8.6.2 Performance & area utilization                     |     |

|    |        | 8.6.3 Resource utilization and throughput                |     |

|    | 8.7    | Related work                                             |     |

|    | 8.8    | Conclusions                                              |     |

| 9  | Con    | clusion                                                  | 141 |

|    | 9.1    | Conclusions                                              | 141 |

|    |        | Future research directions                               |     |

| Li | st of  | Publications                                             | 145 |

| Re | fere   | nces                                                     | 147 |

| Cu | ırricı | ulum Vitæ                                                | 161 |

# Summary

Embedded systems range from very simple devices, such as a digital watch, to highly complex systems such as smartphones. In these complex devices, an increasing number of applications need to be executed on a computing platform. Moreover, the number of applications (or programs) usually exceeds the number of processors found on such platforms. This creates the need for scheduling. Furthermore, each program exhibits different characteristics and their interaction with the (real-life) environmentment leads to real-time requirements. Consequently, the set of programs, called workload, exhibits highly dynamic behavior. Workloads can be dynamic in intensity (i.e., the number of concurrent tasks), characteristics (amount and type of parallelism), and requirements (real-time constraints, power budgets, performance). We argue that dynamic workloads require a dynamic computing platform and propose to use one that comprises the  $\rho$ -VEX reconfigurable VLIW processor. It can dynamically adapt to the workload while it is running. Adaptations can be triggered by a user, programmer, compiler, or an operating system. The latter two methods can operate fully automatic and exploring these is one of the goals of this work.

Besides dynamic workloads, a number of new classes of embedded devices are running application programs that are very static, but require very high throughput. Examples are the latest generations mobile telecommunications hardware and vision-based applications (automation, surveillance, automated driving). In this case, adapting to the workload at run-time is not advantageous because there are no changes to adapt to. Optimizing for these applications is possible, but must be done before the hardware platform is manufactured (during the design phase) or by making use of Field-Programmable Gate Arrays (FPGAs).

This thesis explores the use of the proposed reconfigurable processor to target the full spectrum of embedded workloads. First, design-time reconfigurability is employed to optimize a hardware platform for a static, streaming image processing workload. Second, we explore the run-time reconfigurable processor for dynamic workloads. This is achieved by adapting to a single program to optimize energy efficiency, followed by adapting to a generated set of programs optimizing for throughput. Third, the real-time characteristics of the processor are evaluated and it is shown to have better schedulability compared to static processors. The VLIW architecture results in good timing-predictability, which allows finding tight bounds on the worst-case execution time. Last, we show that the processor is able to assign more parallel execution resources to a static program that is added into the workload, while still guaranteeing time-safety for critical tasks.

# Samenvatting

Er bestaan vele vormen van embedded (geïntegreerde) systemen, van simpele apparaten, zoals digitale horloges, tot veel complexere, zoals een smartphone. De complexere systemen worden geacht steeds meer en in toenemende mate diverse applicaties te kunnen uitvoeren op hun embedded processor. Het draaien van al deze verschillende programma's, allen met hun eigen karakteristieken, gecombineerd met de interactie met de omgeving (waardoor veel embedded systemen real-time restricties hebben), resulteert in een werklast die zeer dvnamisch is. Een werklast kan dynamisch zijn qua intensiteit (i.e., het aantal gelijktijdig actieve taken), karakteristieken (hoeveelheid en type parallelisme), en restricties (real-time, vermogen budgets, prestatie-eisen). Om dit type werklast efficient uit te voeren, stellen we voor om gebruik te maken van een dynamisch computerplatform in de vorm van de  $\rho$ -VEX herconfigureerbare VLIW processor. Deze processor kan zich aanpassen aan de werklast terwijl hij draait. Aanpassingen kunnen handmatig in gang gezet worden door de gebruiker, de programmeur, de ontwerper, of automatisch door een compiler of besturingssysteem. Een van de doelstellingen van dit werk is om de automatische methodes te onderzoeken.

Behalve dynamische werklasten ontstaan er ook nieuwe elektronische systemen die programma's uitvoeren die zeer statisch zijn, maar wel zeer hoge rekensnelheid vereisen. Voorbeelden hiervan zijn de laatste generaties mobiele telecomapparatuur en applicaties die werken met beeldherkenning (zoals diverse automatiseringstoepassingen, (camera)toezicht, zelfrijdende auto's). In dit geval heeft het geen zin om tijdens het uitvoeren van de applicatie de processor aan te passen, omdat er geen veranderingen zijn. Een hardwareplatform kan nog steeds voor deze applicaties worden geoptimaliseerd, maar het moet gebeuren tijdens de ontwerpfase of door gebruik te maken van Field-Programmable Gate Arrays (FPGA).

Dit proefschrift onderzoekt het gebruik van een herconfigureerbare processor voor het uitvoeren van het gehele spectrum van embedded software. Eerst maken we gebruik van configureerbaarheid tijdens de ontwerpfase om een hardwareplatform te optimaliseren voor een statische, streaming beeldverwerkingsapplicatie. Vervolgens onderzoeken we de run-time herconfigureerbare processor voor dynamisch werklasten. Dit doen we door eerst de processor aan te passen aan een enkel programma om de energie-efficiëntie te optimaliseren, gevolgd door het onderzoeken van aanpassingen aan een gegenereerde verzameling van programma's om de totale rekensnelheid te optimaliseren. Hierna evalueren we de real-time eigenschappen van de processor, en laten we zien dat we er real-time schedules voor kunnen maken die niet mogelijk zijn op vergelijkbare statische processoren. Ten slotte demonstreren we dat de processor in staat is om meer parallelle rekeneenheden toe te wijzen aan een statische taak die aan de werklast is toegevoegd, terwijl de tijd-kritische taken nog steeds aan hun real-time restricties voldoen.

# Acknowledgements

The PhD. project has been an incredible journey and I have been lucky to have been surrounded with so many wonderful people throughout the whole process. I will attempt to thank most of them here.

Stephan, under your guidance I have enjoyed the freedom in choosing a path that I felt was truly my own. Your topic is most definitely not the easiest in our field and you have always countered adversity and skepticism with optimism, creativity and perseverance (qualities that I quickly recognized as being essential in bringing a PhD. to a successful conclusion). It has been an amazing adventure and I want to thank you for everything. Zaid, traveling abroad to project meetings and conferences with you felt more like city trips with friends. Your energy and drive never seized to amaze me, and your faith in me has been deeply appreciated. Koen, I am grateful this is not an in memoriam and that you have made such an incredible recovery. I have been a part of your group for half a decade now and I felt at home right from the start.

I would like to thank my PhD. committee, Peter, Henk, Michael, Kees and Said for taking the effort to review my work and provide valuable suggestions and critique.

Sorin, you have given me the opportunity to teach some things about computer architecture to hundreds of students from all over the world for four years. It is something I am very proud of. Thank you for all the confidence you placed in me, and thanks to Thomas, Nicoleta and Jeroen for all their help.

A big thanks to the wonderful staff; Lidwina, Joyce, Arjan, and sysadmin Erik (I hope you didn't mind me occasionally making sure you weren't bored).

I have had delightful times with many colleagues from overseas, including Qi, Jian, Jintao, Shanshan, Cuong (whom I've had the pleasure of visiting in Vietnam!), Innocent, Hoang Anh, and the profoundly talented football players Lei and Joey. Our weekly matches were something I always looked forward to! Thanks to Imran, Daniel, Razvan, Motta, and the others (also from other groups, including Accel and Long). Thanks to my Dutch PhD. buddies Johan and Erik; I have enjoyed the lunches, borrels, events and discussions with you!

I have the warmest memories of our friends from UFRGS, Brazil, who I have had the pleasure of working together with (many even as office mates). Luigi, it was difficult to even picture my defense without you. But I am glad that I never have to address you as "opponent", as I feel like you have been one of my greatest supporters. Caco, I will not forget your powerful presence on the football field! Arthur and Anderson, it was really great to have you guys as office mates on more than one occasion. Thank you all, also the others (Tiago, Sebastian, Jeckson), for the wonderful times we shared in Delft and at conferences elsewhere! Participating in the ALMARVI project has taught me a lot, and I would like to thank the partners, especially the ones that we occasionally collaborated closely with, such as the guys from TUT Finland (Pekka, Timo and friends), Jiri from UTIA Czechia, and of course Rob and Steven at Philips.

Many thanks to the folks in the MEST board; Sven and Jordi, Nauman, Jan, Boyao, Fei, Chock, Hui, Augusto, Andres, and my successor Haji.

Koen & Carmina's quantum effort has rocketeered the group into a leading position in this upcoming field and sparked the creation of a whole department. Carmina, Leon, Lingling, Savvas, Xiang, Nader, Hans and the others; I feel very proud to have been your colleague and wish you all the best of luck!

There has been a large number of students working on the  $\rho$ -VEX for their Master's thesis, each contributing something to the project, the team, and even to this thesis; a big thanks to Muez, Maurice, Klaas, Hugo, Jens, Koray, Panos, Bas, Rolf, Muneeb, Angelos, Lennart, Jonathan, Jacko, Saevar, Anurag, Uttam, and Federico. In addition, I have thoroughly enjoyed having Bachelor's honour track students Tom, Piet, Luc and Matti participate in our lab!

Anthony, things have never been the same after you left and I have missed you at the lab ever since. Jeroen, you have been like a whirlwind going through our lab from the start, fixing and improving everything you saw. I cannot imagine how things would have gone without you, and I have often had to shake my head in awe about how talented and hard-working you are. The three of us felt like an unstoppable team, and I want you to know how much I loved working with you.

Carsten, our paths have never strayed far from each other from school all the way up to the PhD., and I have always considered our friendship something very special and valuable. I will miss having you so close.

To all my friends; thanks for all the fun and I hope to enjoy more of your company at bars, boats, barbecues and beaches!

Steven, Prem and Suzanne; thank you for making me feel part of your family. To my own family; Coen and Suus, I'm so proud of you and always love being around you. Dearest Mom and Dad, I am thankful for everything you have given me and for having you in my life. Over the years, I have become deeply aware of how special you are.

And at the end of the day, Olga, none of it would be worth much if you weren't here to share with. You are the sunshine of my life.

#

# Introduction

Ever since electronic devices started to use programmable embedded processors instead of dedicated circuits, more and more software that increases their functionality is being added each generation. The embedded domain, that has historically been concerned with very low-power designs running simple programs, is expanding its reach with ever increasing numbers of devices executing an ever widening spectrum of software: from washing machines to self-driving cars. This creates the need for embedded systems to be able to target applications in the entire spectrum in an efficient manner. As the applications and their requirements are so diverse, there exists no single execution platform that can execute all workloads efficiently.

This chapter introduces two sides of the spectrum of embedded workloads in Section 1.1 and 1.2, briefly introduces embedded execution platforms that are currently used to execute these workloads in Section 1.3, and discusses general workload properties in Section 1.4. Then, the problem formulation and scope of this work are presented in Section 1.5, the proposed solution is discussed in Section 1.6, and the evaluation approach is presented in Section 1.7.

## **1.1.** Dynamic workloads call for dynamic processors

We are continuously surrounded by electronic devices. Some of these just make our lives easier, while others perform crucial tasks such as operating the wings of an airplane or the brakes in our cars. In these devices, there has been a steady increase in usage of embedded processors, because of their relatively low cost compared to designing a dedicated electronic circuit for each task or device. For example, high-end cars currently have over 100 processors on board [1], and the demand for processing power may start to increase at a significantly higher pace now all competing brands have started to incorporate Advanced Driver Assistance Systems (ADAS) into their models.

The workloads that are executed on embedded processors are increasing in complexity [2]. Early embedded systems typically had only a single task to execute. To decrease costs, power consumption, and other factors such as the wiring in cars, the industry is pushing towards consolidating multiple tasks onto a single embedded processor [3]. As a result, systems have workloads consisting of multiple tasks that each have their own requirements and characteristics. Some of them will have very strict real-time requirements, others may have a performance requirement. Tasks can be multi- or single-threaded, and their execution time can be dominated by computation, control (branches), or memory accesses.

These complex workloads, combined with close interaction with the environment (e.g., responding to sensor input), lead to highly dynamic behavior. Workloads can be dynamic in intensity (i.e., the number of concurrent tasks), characteristics (amount and type of parallelism), and requirements (real-time constraints, power budgets, performance). A single program that has a high degree of Instruction-Level Parallelism (ILP) can be executed efficiently on a high-performance single-core processor. A program consisting of a large number of parallel threads should be executed on a processor with a large number of cores, in which case individual core performance is less important. Even within a program, some of these properties can change rapidly as execution passes through different phases [4]. On a workload

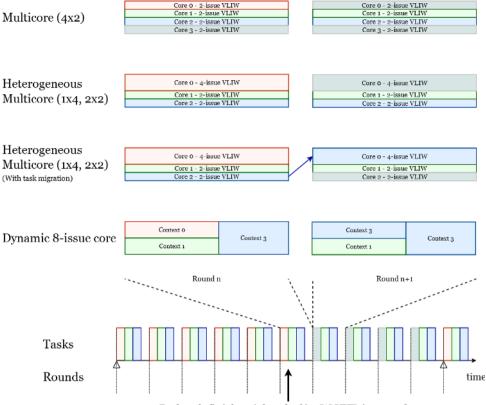

level, some programs more strict real-time requirements than others, leading to mixed-criticality systems [5]. However, contemporary embedded platforms, that are used to execute these highly dynamic workloads, are based on homogeneous or heterogeneous multi-core processors that are *static*.

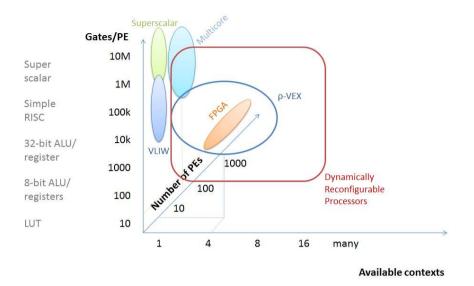

Homogeneous multi-core processors have multiple instances of a processor core on a single chip, supporting concurrent execution of multiple tasks or threads. Heterogeneous multi-core processors usually have a number of high-performance and a number of energy-efficient (but lower performance) cores. This provides some potential to match a program to a core type, depending on its requirements (how much performance does it need?) and code characteristics (some code will not run significantly faster on a high-performance processor core, because for example it is bound by the performance of the memory system). This approach limits the accuracy of this match, because the number of core types is fixed and finite (current heterogeneous processors such as ARM big.LITTLE provide only two options). Additionally, it limits resource utilization, because if a program is running on one core, all the others are idle. A final drawback is that there is a penalty involved when migrating a task from one core to another. These observations have inspired architects from industry and academia to propose dynamically reconfigurable processors.

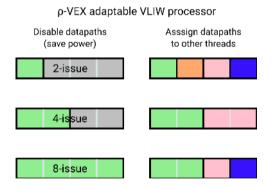

Dynamic (or 'polymorphic') processors adapt to the workload. Typically, they can split cores to run multiple programs at the same time (providing high total throughput), or merge them to provide high single-thread performance. Several designs have been described in literature [6] [7] [8], and a theoretical foundation for their potential performance advantage has been given by Hill and Marty [9]. One such design is the  $\rho$ -VEX polymorphic VLIW (Very Long Instruction Word) processor, which is the focus of this dissertation. It is discussed in more detail in Section 1.6.

Having a processor that is able to adapt to the workload is not enough. It is still necessary to analyze the currently executing workload and evaluate what the best processor configuration is. Without such functionality, it is up to the user to trigger processor adaptations manually during run-time, up to the designer to trigger them according to a certain rule set devised at design-time (this can for example be based on environmental observations such as battery level), or to the programmer to profile and annotate his code during compile-time. Our goal is to perform these steps fully automatically in hardware, during run-time.

# **1.2.** Leveraging design-time customization for highly static workloads

On the other side of the spectrum of embedded workloads, applications exist that continuously performs a fixed set of operations of a stream of input data. For example, a currently rising class of applications uses some form of computer vision. Most notably, this includes automation (e.g., vision-guided robotics), surveillance, automotive and medical industries. A necessary step for these systems is to retrieve input from a sensor and to perform some form of signal processing. For some applications this step can be very simple, others need to perform a large number of complex steps on the input data under strict real-time constraints.

These applications can be highly complex and computationally demanding, but their behavior is static. In this case, adaptations during run-time are not advantageous, because there is no dynamic behavior to adapt to. A processor can still be optimized for these workloads, but the optimization must be performed at designtime as opposed to run-time. This is possible because we know that the application will not change. Optimization may be necessary because the application can have very high performance requirements at limited power budgets, preventing the usage of Commercial Off-The-Shelf (COTS) processing systems.

## **1.3.** Embedded execution platforms

This section briefly presents some background knowledge about processing platforms in embedded systems past and present.

#### **1.3.1.** General-purpose

Classic embedded devices used dedicated electronic circuits to perform a certain function. At some point, these circuits were replaced by general-purpose processors, that could be used in any embedded systems and programmed to perform any function. However, the complexity of embedded systems grew from a digital watch or a washing machine (that only need to perform a single, simple function) into complex devices such as smartphones and tablets. These require more powerful embedded processors to provide the performance for, for example, high-quality video en/decoding and baseband communications.

To provide more performance at acceptable power utilization, manufacturers started creating multicore platforms. These processing systems can be homogeneous, meaning that each core is identical, or heterogeneous, where there are different types of cores. These differences can be transparent to a program, such as clock frequency, cache sizes and other factors that impact performance. These systems are called *single-ISA* (Instruction Set Architecture) heterogeneous multicore processors. They are utilized by smartphone manufacturers to provide both high performance when the users requests it, and long battery life when the device is not in use. The different core types can execute the same code, but it will require more power and less time on one core compared to the next.

In addition to single-ISA heterogeneous cores, cores can be completely different and highly specialized for a certain task. For example, a processor could have a general-purpose core, a DSP (Digital Signal Processor), and an AES (Advanced Encryption Standard) accelerator. These processors are designed specifically for their application, and need to be programmed separately.

#### 1.3.2. Application-Specific

Specialized Application-Specific Integrated circuits (ASICs) can provide orders of magnitude better performance or energy efficiency. However, specifically designing a circuit for a certain (family of) tasks requires significant investments and effort. Another approach is to start designing from a generic processor design,

Figure 1.1: Conceptual depiction of homogeneous versus heterogeneous multicore processors.

and optimize it to the application. These processors are called Application-Specific Instruction-set Processors (ASIPs). They represent a middle ground between fullcustom circuitry and general-purpose processors. By including specialized instructions for the application domain, they are still able to achieve good performance and energy efficiency. Additionally, they can still be programmed for different applications within their domain. For example, a an ASIP for a baseband modem will include instructions for operations that are common for various error correction codes. This is advantageous in, for example, telecommunications hardware where multiple highly complex communication protocols (2G, 3G, 4G) must be supported [10].

#### 1.3.3. Reconfigurable

Reconfigurable processors take the concept of optimizing for an application a step further. They are able to change their behavior after they have been manufactured. The most narrow view on this type of system is the Field-Programmable Gate Array (FPGA), which is a chip that consists of vast numbers of Configurable Logic Blocks (CLBs) and interconnects. CLBs can be configured to perform any logic function with a small number of in and outputs. For example, the Xilinx Virtex6 family uses Look-up-Tables (LUTs) with six inputs. Combined with the reconfigurable interconnects, FPGAs can implement electronic circuits including complex designs such as a complete processor. A circuit configuration can be loaded into the FPGA before starting a new application. FPGAs have been used to accelerate certain segments of a program that are very time-consuming in software but can be performed efficiently by an FPGA circuit. By using partial reconfiguration, parts of the FPGA can be reconfigured while other circuits continue to function on other parts of the FPGA. This way, the FPGA can adapt not only at the start of a program but also when a program changes to another phase in its execution.

In addition to FPGAs, there exist processing platforms that are not organized in CLBs and interconnects, but using larger (coarse-grained) blocks of logic. As the notion of what can be denoted as 'reconfigurable' is debatable, even a normal processor can be viewed as reconfiguring itself to perform a different operation

every clock cycle (depending on the instruction it is executing). In contrast to an FPGA, this type of reconfiguration can occur every clock cycle (as opposed to once when starting the application), and is concerned with an entire ALU (Arithmetic Logic Unit) that consists of several thousands of gates and can perform a multitude of operations (as opposed to individual logic blocks that are tiny in comparison).

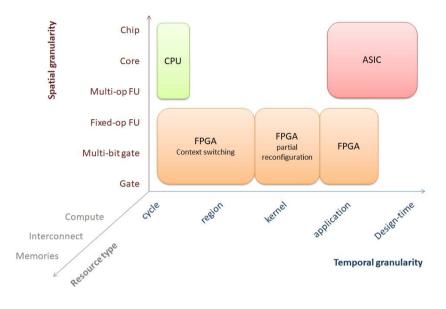

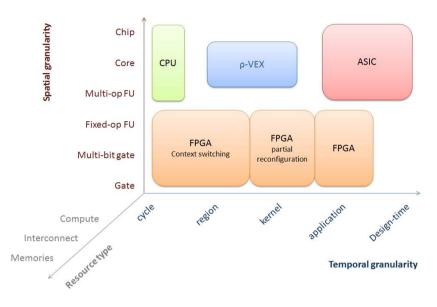

Figure 1.2: Classification of reconfigurable processors based on [11]. A processor can be reconfigurable regarding different components such as memory, compute units or connections between processors or components. Depending on the reconfiguration penalty involved, processors can be reconfigured at high frequencies (fine-grained) or, for example, per application. Similarly, the components that are reconfigurable can be very large (such as a whole core) or in case of FPGAs almost on a per-gate level.

This broad view creates a range of different reconfigurable processors, similar to the spectrum of different workload types. Figure 1.2 shows a classification, introduced by [11]. Different parts of a processor's organization can be reconfigured, most notably the memory resources (such as caches), compute resources (such as the ALU or other functional units), and the connections between them (not only between the functional units and the memory, but possibly also between functional units themselves). The spatial granularity denotes the size of the reconfigurable parts and the temporal granularity determines at which frequency these reconfigurations can be performed. Every type of reconfigurable processor has one property in common; each of them aims to adapt the hardware to the workload.

## 1.4. Workload analysis

This section discusses several requirements and characteristics that a workload can have, and the how they can be dealt with by an execution platform.

#### **1.4.1.** Requirements

An application can have several requirements that are imposed by the designer or the environment:

#### Time

In the embedded domain, timing requirements are very common. A real-time systems needs to guarantee that a result is available within a specific amount of time (the deadline), otherwise the system will fail. Often, a distinction is made between tasks where the result is useless and may result in a catastrophic failure if it is not available before the deadline (hard real-time tasks - HRTT), and tasks where the requirement is not as strict and a late result may even be of some value (soft real-time tasks - SRTT). Embedded real-time systems can have tasks that are periodic and aperiodic in nature. New instances of a periodic task will be triggered (*released*) at its specific interval (the task *period*). Aperiodic tasks are triggered when a certain event happens, such as a button being pressed. These tasks also have a deadline before which the system must have handled the event.

#### Performance

As performance is the inverse of delay, most performance requirements can also be expressed as a timing requirement. For example, a performance requirement for encoding video at a frame rate of at least 25 frames per second (FPS) seems to be a performance requirement but can also be expressed as a periodic task (encoding a video frame received from the image sensor) that should always finish within 40 ms. For applications that have less easily identifiable blocks, a performance requirement can be expressed in terms of throughput, such as for example compressing data with a minimum throughput of 1 Gibit per second.

#### Power/Energy

Embedded systems are often battery-powered, and modern high-performance embedded systems such as mobile phone Systems-on-Chip (SoC) have thermal budgets to prevent devices from overheating. Also in the server domain, energy consumption is a key component of total costs and has established itself as a critical performance metric. For datacenters, it is becoming increasingly difficult to match power provisioning and cooling capacity to the demand, as workloads can be highly variable [12]. Consequently, energy or power requirements are common in both the embedded and server domains. Methods to meet these requirements include:

- Multicore processors can be used to divide a workload over multiple processors. Subsequently, the clock frequency and voltage of the processors can be reduced to achieve the same performance. As power utilization scales linear with frequency and superlinear with voltage, this should result in lower total power utilization.

- Heterogeneous Computing is applied in two separate fashions: Single-ISA Heterogeneous Multicore Processors (HMP) [13] such as ARM big.LITTLE processors [14] can provide high performance using big processor

cores and high energy-efficiency using little cores. This concept aims to meet the contradictory requirements of mobile phone SoCs to provide high performance for cutting edge media and 3D graphics processing but also very long standby times. **Hardware accelerators** provide optimized ASIC implementations of common intensive tasks such as video coding and encryption. These can be offloaded to the accelerators, instead of executing them inefficiently on the central processor.

- **Dynamic Voltage and Frequency Scaling (DVFS)** is a common technique that changes the voltage and frequency of a processor during run-time, according to the demand for processing power.

- **Power/Clock gating** can be used to switch off parts of the processor that is not being used. In processors, this is commonly implemented as different sleep modes. Lower sleep modes conserve more power but require more time to restore to full functional state.

#### 1.4.2. Parallelism

Exploiting parallelism is one of the key mechanisms to increase the performance of a computer system [15]. This can be done by overlapping (parts of) calculations that can be performed concurrently, by assigning them to different functional units or even different processors. Depending on the application, parallelism can be present on multiple levels.

#### Task-level parallelism

The most straightforward form or parallelism is when there are multiple unrelated *tasks* assigned to a system. These tasks can be assigned to different processors available on a multicore or multiprocessor system. Increasing the number of processors in a computer system increases the number of parallel tasks it can perform, until shared resources such as memory bandwidth will become the bottleneck.

#### Thread-level parallelism

A related form of task-level parallelism is thread-level parallelism, where a single program is divided into parts, each running on a different execution *thread*. In this case, the tasks are related, which means they need to perform some form of synchronization and possibly communication of intermediate results. This overhead limits the speedup that can be achieved by distributing a task over multiple threads and assigning each thread to a separate processor. For some types of applications, the overhead is relatively small and performance can be increased by using a large number of small processors. Otherwise, a limited number of threads executing on high-performance processors is a more suitable approach.

#### Data-level parallelism

Some applications can be divided in such a way that the exact same operations are performed on subsets of the *data*. This form of parallelism can be exploited by using SIMD (Single Instruction, Multiple Data) architectures. These architectures

execute a single stream of instructions on multiple different sets of data. If the bit depth of each individual data item is relatively small, multiple data items can be calculated using a single datapath. For example, a 32-bit datapath, in SIMD mode, can execute 2 16-bit operations or 4 8-bit operations simply by decoupling the carry chain [16, Fig. 5.6]. Additionally, specialized vector datapaths can be added to a processor that are much wider than the processor's general scalar datapath. Using SIMD greatly reduces the control overhead<sup>1</sup>, communication and synchronization compared to computing the data sets on separate processors. SIMD datapaths can be very wide, supporting several parallel operations, but need to access memory in such a way that the full width can be exploited. This means that either the register file must support these wide accesses, there must be a separate vector register file, or the SIMD datapaths need to be able to directly access a cache line (which, in turn, needs to be wide enough). For example, the Hexagon VLIW [17] provides four 1024-bit wide vector datapaths, and has a dedicated vector register file that directly connects to the L2 cache. On the software side, SIMD requires compiler support in the form of automatic vectorization.

#### Instruction-level parallelism

Instead of splitting up tasks or datasets into multiple parts, a processor can also exploit parallelism on the level of individual *instructions*. It is the most transparent approach for the programmer, as it requires no manual program transformations or vectorizing compilers. Historically, exploiting ILP has been one of the key architectural driving forces behind processor performance increase. Classical approaches include pipelining and multi-issue processors, both of which are employed heavily in processor designs.

Pipelined processors divide individual instructions into several steps and overlap their execution. Pipelining has been one of the main enablers of the continuous increase in processor clock frequencies until the power density (that steadily increased with scaling down technology feature sizes) resulted in heat dissipation problems. This forced architects to search for other means to increase processor performance without increasing the frequency.<sup>2</sup> As the performance of a program is dictated by execution time =  $\frac{\text{cycles}}{\text{frequency}}$  and cycles =  $\frac{\text{instruction count}}{\text{instructions per cycle}}$ , increasing the processor clock frequency. A natural way to do this is to allow the processor to start multiple independent instructions per clock cycle: multiple-issue processors.

There are two main paradigms for designing multi-issue processors: superscalar and VLIW processors. Superscalar processors use complex circuitry to detect whether operations can be executed in parallel or not. VLIW processors move this complexity to the compiler, thereby allowing simpler processors with decreased

<sup>&</sup>lt;sup>1</sup>This includes all the circuitry needed to run the program that is not the datapaths themselves (such as branch units and pipeline control logic), but also for example the memory bandwidth required for the instruction stream.

<sup>&</sup>lt;sup>2</sup>This is not to say there were no previous efforts in this direction: indeed, the first superscalar processors have been designed in the 1960s by Cray and IBM. However, frequency scaling provided a steady performance increase with every new technology generation up to this point, after which architectural improvements were the only way forward.

power consumption to achieve similar performance *as long as the compiler can find enough parallelism in the code*. There are some fundamental limits to exploiting ILP:

- There are limits on the available ILP in code. In the general-purpose domain, between 15 and 25 % of all executed instructions are branches, which means that there will be on average between three and six instructions available before a branch [15, p. 67]. This means that a processor must be able to cross branches to find a decent amount of ILP.

- When finding ILP across branches, the processor must speculate whether these branches are taken or not. Even with highly accurate predictors, mispredictions will continue to occur occasionally. These require the processor to flush any speculatively issued instructions from the pipeline and restart execution at the resolved branch address.

- Speculation (when assumed to be imperfect) inherently reduces energy efficiency [15, p. 182].

- Some instructions have true dependencies that cannot be resolved by the processor (e.g., by using register renaming).

Even with perfect branch prediction, an infinite number of parallel datapaths and an infinite window for finding independent instructions, the number of instructions that can be executed in parallel is limited [15, Ch. 3]. In addition to the limits of finding enough ILP to efficiently utilize multiple parallel datapaths, there are some practical limits to increasing the issue width of a processor:

- The number of parallel datapaths cannot be increased indefinitely because of increasing circuit complexity<sup>3</sup>.

- Compiler techniques to increase ILP such as loop unrolling will increase binary sizes and subsequently increase the required instruction cache capacity and memory bandwidth.

- Processing multiple data items in parallel will also require more accesses to the data memory, creating the need for larger and multi-ported caches.

The limitations to both the hardware and software quickly result in diminished returns: a small increase in performance requires a large investment in circuit complexity and consequently energy consumption. Modern computing systems combine the techniques discussed in this section to exploit as much parallelism as possible: multicore superscalar processors with very deep pipelines and SIMD extensions are common even in the embedded domain.

<sup>&</sup>lt;sup>3</sup>Fully connected VLIW processors will see the circuit area of both their register file and forwarding logic increase superlinearly with their issue width. There are approaches to mitigate this effect, such as clustering [18] and using exposed datapath architectures with limited connectivity [19] [20].

#### **1.4.3.** Code characteristics

In addition to the type and amount of parallelism available in an application, an important characteristic is the instruction mix and how this influences the performance of a processor. In a very general sense, instructions from any RISC (Reduced Instruction Set Computing) processor can be divided into three families:

- **Control flow operations** change the flow of the processor through the program by jumping to a certain address. These include function calls but also conditional branches, that for example implement if/else constructs.

- **Memory operations** load or store values to and from the processor's internal registers (the register file).

- Arithmetic operations perform calculations such as additions or multiplications on values stored in the register file.

Each of the instruction type uses a different processor subsystem that can cause the processor to stall, degrading performance.

#### Control-bound

As discussed in Section 1.4.2, processors with deep pipelines rely heavily on speculation to achieve high performance. Branch prediction is arguably the most important form of speculation, and mispredictions are very expensive. Programs with a large amount of branches require more complex prediction logic to keep the misprediction rate low. VLIW processors often rely on the compiler to perform static branch prediction. The compiler analyzes the most likely control flow and restructures the code so that the common case will execute fastest. In addition, techniques exist to expose ILP across branches by combining multiple blocks of code (trace, superblock and hyperblock scheduling). However, there are limitations to these techniques and exploiting ILP in branch-heavy programs using VLIW processors remains challenging. Control-bound applications are currently most suitable to be executed on general-purpose processors with a high operating frequency and sophisticated branch prediction.

#### Memory-bound

If a program performs a relatively large number of memory operations, and few operations on the data in between accesses, the memory accesses can create a performance bottleneck. There is a large discrepancy between latency of processors and memory devices, and in modern server-grade computer systems, a main memory access costs hundreds of processor cycles to complete. As this difference has been growing over the past decades, an increasing number of cache levels have been added to the memory hierarchy (three levels is currently very common). While caches solve part of the problem for applications with enough locality, a processor should still be able to overlap the time it is waiting for outstanding main memory requests with computations on already available data. For highly regular memory access patterns, this can be accomplished by prefetching data <sup>4</sup>. This

<sup>4</sup>Where superscalar processors have hardware circuitry that tries to predict future memory accesses to fetch these values from memory, VLIW processors commonly employ explicit prefetch instructions

can allow programs with limited cache locality to still achieve high performance. For example, some streaming workloads operate on a small set of input data only once, before continuing with the next input. Afterwards, a data set is never used anymore, rendering the caches to be of little use. However, the memory access pattern of these workload types is usually very regular and can achieve high sustained memory bandwidth.

Irregular memory access patterns are more challenging. In this case, an approach to overlap memory access latency with computation is to switch to another thread when the currently executing thread encounters a long latency cache miss (Switch-on-Event or coarse-grained Multi-Threading). This requires the processor to be able to store multiple program states in internal registers to allow it to quickly switch between them.

#### Compute-bound

In contrast to memory-bound programs, some programs perform large amounts of operations per memory access. If there is enough ILP in the code, the situation can arise where there are more operations available for executions than there are functional units available to perform them. In this case, the processor does not fully utilize the available memory bandwidth. The program can execute faster if there are more execution units, for example by using a wider issue superscalar or VLIW processor.

## **1.5.** Problem formulation and scope

The industry is continuously pushing for increasingly fast time-to-market, driven by a decreasing window of competitive advantage for new technologies. At the same time, maintaining multiple processor families, along with their complete ecosystem of toolchain, libraries, operating system and application support, is becoming increasingly expensive. This raises the question whether it is possible to use a single processor family to target both sides of the spectrum – allowing run-time adaptations for dynamic workloads, design-time optimization for static workloads, and short time-to-market. This leads to the following research question:

How to target both highly static and dynamic workloads using a single processor architecture?

As discussed, there is a large spectrum of both software (workloads) and hardware (embedded reconfigurable processors). In addition, having a run-time reconfigurable processor adds the question of how to schedule these configurations. The scope of this work concerning these aspects is defined in the following sections.

#### 1.5.1. Software: Workloads

In this thesis, we will discuss three general types of workloads, each in their own embedded application domain. A workload is considered as the set of application

that can be inserted into the code by the compiler or programmer (once more reflecting the VLIW philosophy of moving complexity from hardware to the compiler).

programs that is executed on the system under consideration. Individual programs can have multiple instances (they can be restarted, for example, with a new set of input data). Not all programs are necessarily active at the same time (some can be triggered by an event, or have a dependency on the termination of another program). In increasing order of complexity, the workloads studied in this work are:

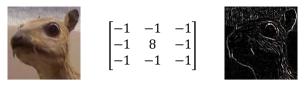

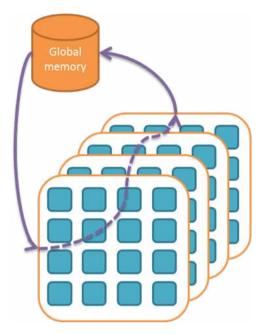

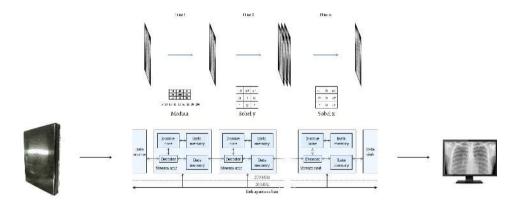

Static workloads continuously perform the same (set of) operations on an input stream. In particular, this work focuses on a medical imaging workload consisting of convolution kernel filters that are applied to input from an image sensor. The input passes through a chain<sup>5</sup> of image processing filters that aim to improve image quality by means of, for example, noise reduction and contrast enhancement. This workload has a high degree of data, thread, and instruction-level parallelism.

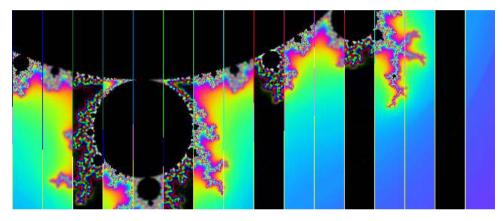

Figure 1.3: Image divided into slices, each processed on a different (set of) processors. In this still image, slices are alternating between no filters, a blurring filter, and blurring combined with an edge detection filter.

• **Dynamic workloads** consist of multiple different tasks, having different amounts of ILP. The number of concurrently executing tasks varies during the execution of the workload. Because of this, both Instruction-level and Task-Level Parallelism (TLP) are varying during the course of execution. In the time domain, this behavior occurs on both a very coarse-grained level and a fine-grained level, because 1) individual tasks typically go through numerous phases during their execution [4] and 2) some programs alternate between phases very rapidly.

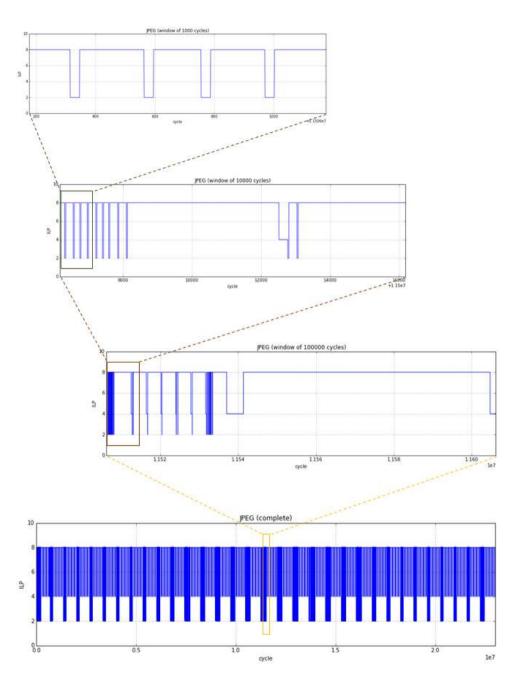

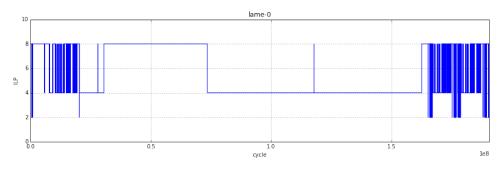

Figure 1.4 shows the phases of JPEG with different window sizes, as detected by our modified compiler. It can be seen that the program shows changing behavior on a very fine-grained level (with a phase of only 50 cycles in the top

<sup>&</sup>lt;sup>5</sup>These chains of filters are commonly referred to as a 'pipeline'. This term is also widely used to denote a processor datapath.

Figure 1.4: Graphic representation of ILP phases in JPEG as detected by a VLIW compiler. Depicted window sizes range from the full execution in the bottom figure, to 1000 cycles in the top figure. The subwindows are left-aligned at the same point exactly halfway through the full execution. These figures show changes in ILP requirements on different levels of temporal granularity.

Figure 1.5: Graphic representation of ILP phases in LAME as detected by a VLIW compiler. It has a much larger portion of long, stable phases compared to JPEG.

figure) as well as on a larger scale (with a stable phase of 60,000 cycles in the second lowest figure). In comparison, Figure 1.5 plots the full execution of MP3 encoder LAME, which shows long stable phases of tens or hundreds of millions of cycles. These two examples show that there are widely different programs regarding phase behavior.

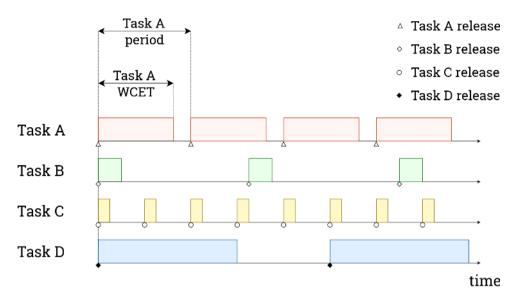

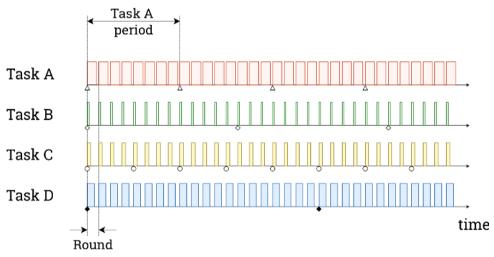

- Real-time workloads add strict timing requirements to dynamic workloads. This necessitates the execution platform to provide a guarantee to each realtime task that, every time it is activated, it will receive a number of execution cycles no less than its Worst-Case Execution Time (WCET). We will consider task sets with multiple tasks that can each have a distinct WCET and timing requirement. In this work, we use real-time workloads that contain multiple *periodic* tasks. Each task has a period after which a new instance of the task is triggered. If the previous instance has not finished execution at that time, it has missed its deadline (deadlines are *implicit*).

- Mixed-criticality systems combine real-time workloads with a static workload by adding a static program to a real-time workload. The static program does not have a timing requirement such as the real-time tasks, but should be optimized for throughput. This workload type represents the mixed-criticality systems field of research. This field originated from the need to certify avionics systems [5] that has tasks with different levels of criticality (requiring different certifications), but evolved to also include systems with critical and non-critical tasks.

The method in which we generate workloads for these different types, for use in our evaluations, is discussed in Section 1.7.5.

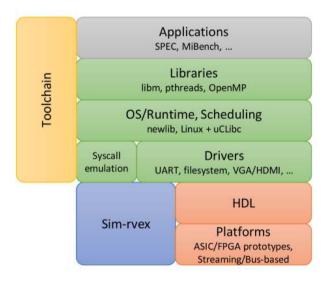

#### **1.5.2.** Hardware: Reconfigurable processors

This thesis focuses on the  $\rho$ -VEX VLIW processor that is reconfigurable on two extremes on the temporal granularity axis: static (design-time) reconfigurability (also application-level by using FPGA technology) [21], and dynamic (run-time) parameterization [22] on a region level. The use of the term parameterization

serves to distinguish the two types of reconfigurability, but also signifies that this type of reconfigurability is limited to changing a set of parameters that is fixed at design-time.

Figure 1.6: The position of the  $\rho$ -VEX dynamically reconfigurable processor in the classification of Figure 1.2 (based on [11]).

The design-time reconfigurability of the processor is used to target highly static workloads. The run-time parameterization is used for the dynamic, real-time and mixed critical workloads. The component that is parameterized is the interconnects between memories (caches and register files) and compute units (datapaths). This is discussed in more detail in Section 1.6.

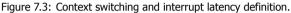

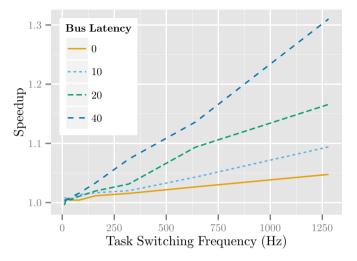

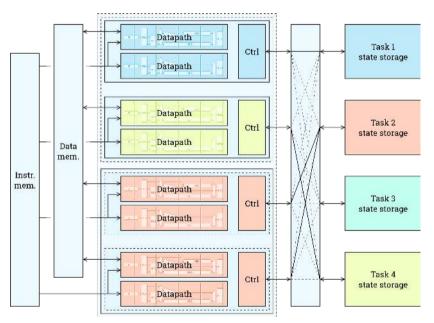

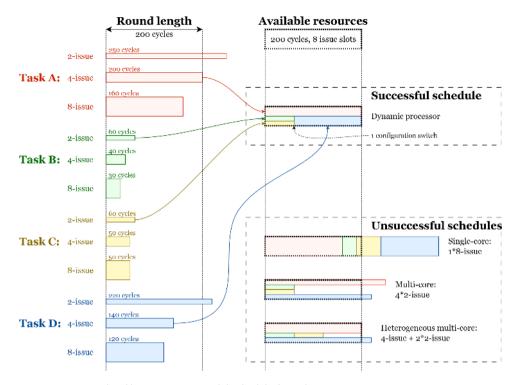

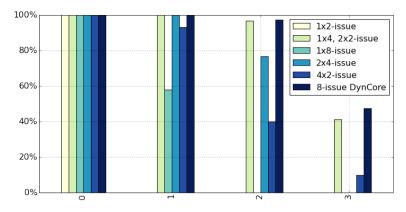

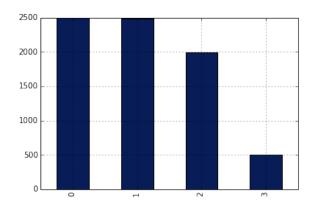

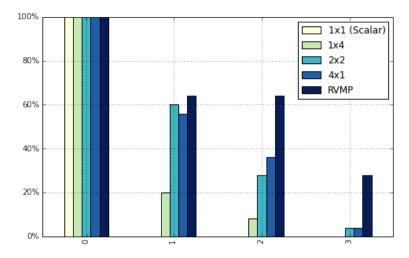

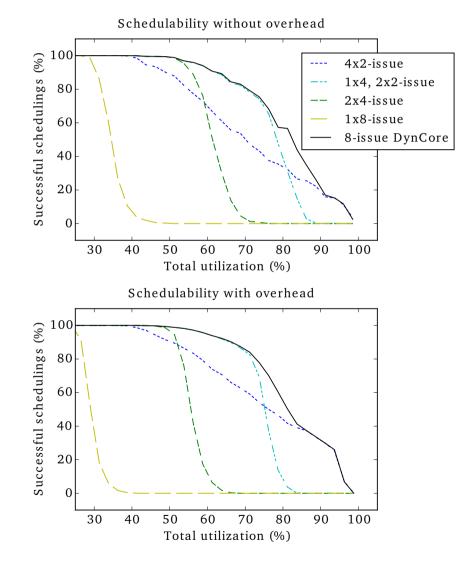

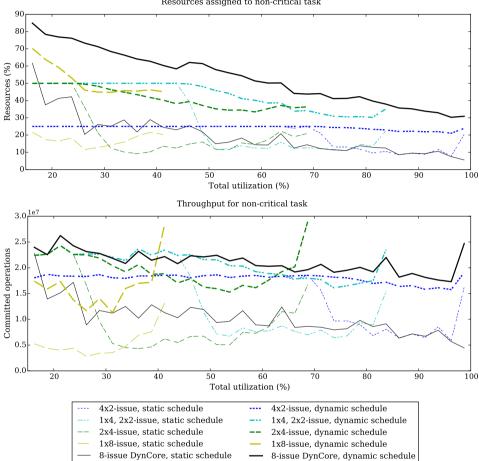

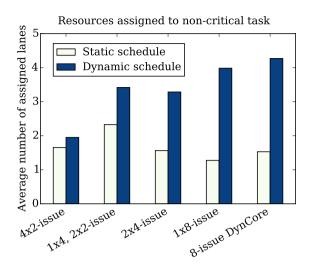

#### 1.5.3. Scheduling: Tasks and processor configurations