Marie-Anne Jaud, Pascal Scheiblin, Sébastien Martinie\*, Mikaël Cassé, Olivier Rozeau, Julien Dura,

Jérôme Mazurier, Alain Toffoli, Olivier Thomas, François Andrieu, Olivier Weber

CEA-LETI, MINATEC, 17 rue des Martyrs, 38054 Grenoble cedex 9, France

\*IM2NP-CNRS, UMR CNRS 6242, Bât. IRPHE, 49 rue Joliot Curie, BP 146, 13384 Marseille cedex 13, France Tel: +33 4 38 78 24 26, Fax: +33 4 38 78 51 40, email: marie-anne.jaud@cea.fr

Abstract—We present TCAD simulations based on advanced mobility modeling including Surface Roughness (SR) and Remote Coulomb Scattering (RCS) effects, quantum correction and short channel effects. From these calibrated models, FDSOI 6T-SRAM cells are simulated and compared to experimental data. The very good agreement achieved between simulations and electrical data on both mobility and electrical figures of merit (device and SRAM) offers major opportunities for predictive design based on TCAD simulations.

## I. INTRODUCTION

Giving the various MOSFET architectures under development (FDSOI, Ultra Thin BOx-FDSOI, nanowire, ...), it becomes necessary to have a predictive TCAD tool to assess and quantify the relevance of these different options for advanced nodes (22nm, 16nm, 13nm ...) and for small circuit applications [1-3]. Indeed, provided advanced physical models and experimental data validation, TCAD simulation tool is of great interest for i) technological support for advanced nodes development (static and dynamic performances evaluation through single device and ring oscillator, respectively) ii) design and validation of innovative small circuit architectures (typically SRAM cell) iii) providing the input necessary for the establishment of predictive modelcard for advanced nodes. In this work, FDSOI technology is studied and TCAD simulations are systematically compared to recent 300mm wafer FDSOI technology experimental data [4-5] from mobility measurements to 6T-SRAM cell static noise margins. In section II, we present the quantum correction and the improved electron and hole low field mobility introduced in TCAD simulations. Then, after calibrating short channel effects, nFDSOI and pFDSOI electrical characteristics are compared to experimental data in section III. Finally, section IV presents a comparison between TCAD and experimental results obtained on a 6T-SRAM cell, while in section V the conclusions and perspectives of this work are drawn.

## II. QUANTUM CORRECTION & MOBILITY

## A. Quantum correction

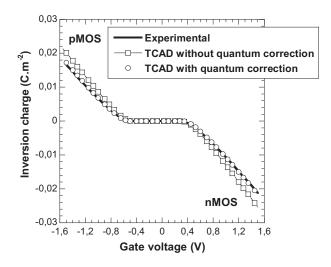

The Bohm Quantum Potential (BQP) [6-7] calibrated on self-consistent Schrödinger-Poisson simulations is used as quantum corrected potential. Inversion charge as a function of gate voltage resulting from experiments [4-5] and TCAD without and with quantum correction is plotted in Figure 1. The excellent agreement between experiments and TCAD with quantum correction shows that the inversion thickness is properly taken into account thanks to this correction.

Figure 1. Inversion charge as a function of gate volatge resulting from (line) experiments, TCAD simulations (square) without and (circle) with quantum correction.

# B. Mobility

At low electric field, the usual Lombardi mobility model [8] has been improved through Mathiessen's rule (1) by including i) usual silicon doping-dependent mobility expression and parameters (2), ii) phonon limited mobility using Takagi's expression and parameters (3) [9] that are in accordance with experimental measurements [10], iii) surface roughness limited mobility according to experimental data [10] (4), iv) Remote Coulomb Scattering (RCS) effect due to high- $k/SiO_2$  dielectric gate stack (1.2nm equivalent oxide thickness) in accordance with Kubo-Greenwood approach [11-12] (5).

This work has been supported by the French Public Authorities through the NANO 2012 program.

$$\mu_{\rm eff}^{-1} = \mu_{\rm dop}^{-1} + \mu_{\rm ph}^{-1} + \mu_{\rm sr}^{-1} + \mu_{\rm rcs}^{-1}$$

(1)

where  $\mu_{dop}$ ,  $\mu_{ph}$ ,  $\mu_{sr}$  and  $\mu_{rcs}$  are the doping-dependent mobility, the phonon scattering-dependent mobility, the surface roughness scattering-dependent mobility and the RCS mobility, respectively.

$$\mu_{dop}^{-1} = \left(\mu_{min} + \frac{\mu_{max} - \mu_{min}}{1 + (N/N_{ref})^{\theta_{imp}}}\right)^{-1}$$

(2)

(1)

(2)

(3)

$$\mu_{\rm ph}^{-1} = \left(\frac{\mu_{\rm 0ph}}{E_{\rm eff}^{\theta_{\rm ph}}}\right)$$

$$\mu_{\rm sr}^{-1} = \left(\frac{\mu_{\rm 0sr}}{E_{\rm eff}^{-\theta_{\rm sr}}}\right)^{-1} \tag{4}$$

$$\mu_{\rm rcs}^{-1} = \left(\frac{\mu_{\rm 0rcs}}{\left(\frac{E_{\rm eff}}{\gamma_1 (q.N_{\rm fix})^{\gamma_2}}\right)^{\theta_{\rm rcs}}}\right)^{-1}$$

(5)

where  $\mu_{min}$ ,  $N_{ref}$  and  $\theta_{imp}$  are the usual silicon parameters [7],  $\mu_{0ph}$  and  $\theta_{ph}$  are in accordance with [9] and experimental measurements [10],  $\mu_{0sr}$  and  $\theta_{sr}$  are in good agreement with experimental data [10],  $\mu_{0res}$ ,  $\theta_{res}$ ,  $\gamma_1$ ,  $\gamma_2$  have been calibrated to reproduce Kubo-Greenwood results [11-12],  $\mu_{max}$  and  $N_{fix}$  are fitting parameters and  $E_{eff}$  is the effective field.

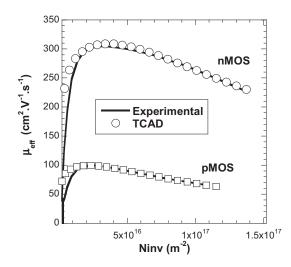

In Figure 2, low field electron and hole mobility as a function of inversion charge obtained by TCAD simulations are compared to experimental data on long and wide FDSOI devices [4-5]. The excellent agreement shows that the mobility is well described by our improved mobility model on a large range of inversion charge.

Figure 2. Low field electron and hole mobility as a function of the inversion charge resulting from (line) experiments and (symbol) TCAD simulations on long and wide device.

### III. FDSOI DEVICES

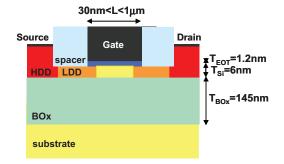

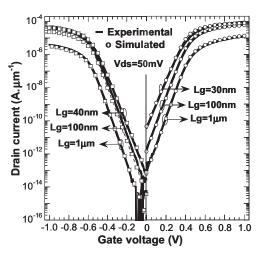

The simulated device is an undoped FDSOI MOSFET with a 6nm silicon film thickness, a  $1.2nm SiO_2$  equivalent oxide thickness and a 145nm BOx thickness as represented in Figure 3. Electrical characteristics for FDSOI nMOSFETs and pMOSFETs devices ranging from 1µm gate length down to 30nm have been simulated at Vds=50mV and Vds=1.0V.

Figure 3. Schematic of the simulated undoped FDSOI devices.

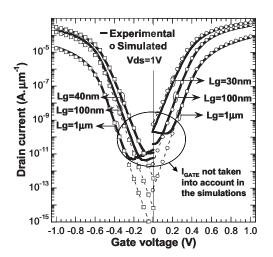

Figure 4. nMOS and pMOS  $I_{DS}$ -V<sub>GS</sub> characteristics at  $V_{DS}$ =50mV, resulting from (line) experiments and (symbol) TCAD simulations.

Figure 5. nMOS and pMOS  $I_{DS}$ - $V_{GS}$  characteristics at  $V_{DS}$ =1.0V, resulting from (line) experiments and (symbol) TCAD simulations.

Drift-diffusion with BQP correction, usual Shockley-Read-Hall generation-recombination rate and the improved low field mobility model have been used in TCAD simulations. Short channel effects (SS, DIBL) have been calibrated on experimental data by adjusting access doping levels and profiles. The simulated and experimental [4] electrical characteristics for nFDSOI and pFDSOI are plotted in Figures 4 and 5. Considering that the gate tunneling leakage current is not modeled, a very good agreement is obtained between simulations and experiments even for aggressive gate lengths (down to 30nm).

## IV. FDSOI 6T-SRAM

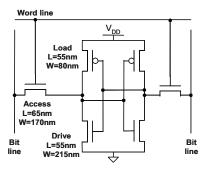

The above ingredients are used in TCAD MixedMode [7] for simulating the 6T-SRAM bit-cell represented in Figure 6.

Figure 6. 6T-SRAM cell sizing.

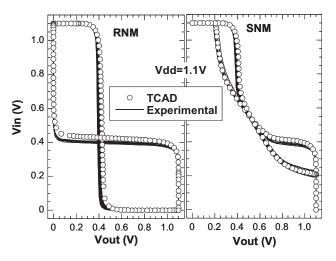

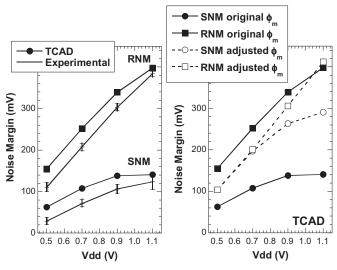

Figure 7 compares experimental and simulated Static Noise Margin (SNM) and Retention Noise Margin (RNM) butterfly obtained at Vdd=1.1V. On this same bit-cell, Figure 8 shows the extracted SNM and RNM at different supply voltage Vdd.

Figure 7. Retention Noise Magin (RNM) and Static Noise Margin (SNM) butterfly at Vdd=1.1V resulting from (line) experiments and (symbol) TCAD simulations.

We observe that simulation results present magnitude and trends consistent with experimental results especially at high Vdd. At low Vdd, discrepancy is mainly explained by a less accurate description of the moderate inversion regime for transistors with short gate length because the reduction of mobility experimentally observed for short dimensions [13] is currently not considered in simulations. Moreover, the gate tunneling current through the oxide is not taking into account in the simulation whereas it is known that this current degrades SRAM cell performances. Therefore, we have checked that on this technology (EOT=1.2nm with high-k) the gate tunneling current participates only for few per cents to the SRAM cell noise margins.

Finally, TCAD provides guidelines for the FDSOI technology to improve SRAMs characteristics trade-offs. It is found in Figure 9 that we can achieve better static noise margins by adjusting metal gate workfunctions  $\phi_m$  toward midgap.

Figure 8. RNM and SNM as a function of Vdd resulting from (line) experiments and (symbol) TCAD simulations

Figure 9. RNM and SNM as a function of Vdd resulting from (filled symbols) TCAD with same  $\phi_m$  as experiments and (open symbol) TCAD with adjusted  $\phi_m$ .

## V. CONCLUSION

A TCAD approach mainly based on improved physical mobility models including Remote Coulomb Scattering and calibrated on recent experimental data is presented. It is used to simulate FDSOI electrical characteristics and 6T-SRAM cells' noise margins. The very good agreement achieved between simulations and experimental data allows us to propose optimized SRAM cells characteristics. Moreover, this "FDSOI TCAD library" can be used to realistically extrapolate this technology to support near future node development (20nm, 16nm). Introduction of experimentally observed mobility degradation with decreasing gate length [13] and gate tunneling current in the "FDSOI TCAD library" are currently underway.

#### REFERENCES

- K. Kim et al., "Stable high-density FD/SOI SRAM with selective back-gate bias using dual bureid oxide," International SOI conference, pp. 37-38, 2008.

- [2] S. Yu et al.," The impact of line edge roughness on the stability of a FinFET SRAM," Semiconductor Science and Tehenology, vol. 24, 025005, 2009.

- [3] A. B. Sachid, G. S. Kulkarni, M. S. Baghini, D. K. Sharma and V. Ramgopal Rao, "Highly robust nanoscale planar double-gate MOSFET device and SRAM cell immunity to gate-misalignment and process variations," 2<sup>nd</sup> International Workshop on Electron Devices and Semiconductor Technology, 2009.

- [4] L. Brunet et al., "New Insight on V<sub>T</sub> Stability of HK/MG Stacks with Scaling in 30nm FDSOI Technology," VLSI 2010, in press.

- [5] F. Andrieu et al., "Low leakage and low variability ultra-thin body and bureid oxide (UT2B) SOI technology for 20nm low power CMOS and beyond," VLSI 2010, in press.

- [6] G. Iannaconne, G. Curatola, G. Fiori. "Effective Bohm Quantum Potential for device simulators basd on drift-diffusion and energy transport," SISPAD, 2004.

- [7] Silvaco Atlas and MixedMode, 2010.

- [8] C. Lombardi, Manzini, Saporito, Vanzi, "A Physically Based Mobility Model of Nonplanar Devices", IEEE Trans. CAD, vol 7, No.11, pp. 1164-1171, 1988.

- [9] S. Takagi, A. Toriumi, M. Iwase, H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part I effect of substrate impurity concentration," IEEE TED, vol.41, pp. 2357-2362, 1994

- [10] L. Thevenod et al., "Influence of TiN metal gate on Si/SiO2 surface roughness in N and PMOSFETs," Microelectronic Engineering, vol.80, pp. 11-14, 2005

- [11] S. Barraud, O. Bonno, M. Cassé, "The influence of Coulomb centers located in HfO2 /SiO2 gate stacks on the effective electron mobility," Journal of Applied Physics, vol. 104, 073725, 2008.

- [12] S. Martinie et al., "Numerical Simulation of ballistic/quasi-ballistic transport in FDSOI and Nanowire MOSFETs: analysis of CMOS inverter static performances", in Proceedings Fringe-ESSDERC, 2009.

- [13] A. Cros et al., "Unexpected mobility degradation for very short devices : A new challenge for CMOS scaling," IEDM, 2006.