Linköping Studies in Science and Technology Dissertations, No 1716

# Techniques for Efficient Implementation of FIR and Particle Filtering

Syed Asad Alam

Division of Computer Engineering Department of Electrical Engineering Linköping University SE–581 83 Linköping, Sweden Linköping 2016 Linköping Studies in Science and Technology Dissertations, No 1716

Syed Asad Alam syed.asad.alam@liu.se www.da.isy.liu.se/ Division of Computer Engineering Department of Electrical Engineering Linköping University SE-581 83 Linköping, Sweden

Copyright  $\bigodot$  2016 Syed Asad Alam, unless otherwise noted. All rights reserved.

Alam, Syed Asad Techniques for Efficient Implementation of FIR and Particle Filtering ISBN 978-91-7685-915-5

ISBN 978-91-7685-915-ISSN 0345-7524

Typeset with  $\[\]$  TeX Printed by LiU-Tryck, Linköping, Sweden 2016

To my mother and wife

# Abstract

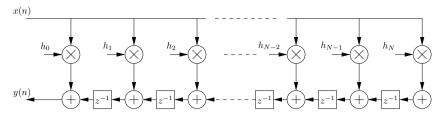

Finite-length impulse response (FIR) filters occupy a central place many signal processing applications which either alter the shape, frequency or the sampling frequency of the signal. FIR filters are used because of their stability and possibility to have linear-phase but require a high filter order to achieve the same magnitude specifications as compared to infinite impulse response (IIR) filters. Depending on the size of the required transition bandwidth the filter order can range from tens to hundreds to even thousands. Since the implementation of the filters in digital domain requires multipliers and adders, high filter orders translate to a large number of these arithmetic units for its implementation. Research towards reducing the complexity of FIR filters has been going on for decades and the techniques used can be roughly divided into two categories; reduction in the number of multipliers and simplification of the multiplier implementation.

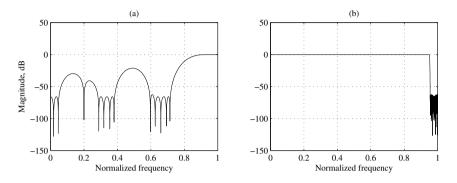

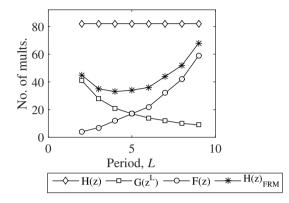

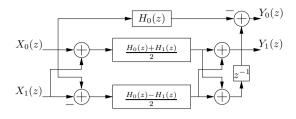

One technique to reduce the number of multipliers is to use cascaded subfilters with lower complexity to achieve the desired specification, known as frequency-response masking (FRM). One of the sub-filters is a upsampled model filter whose band edges are an integer multiple, termed as the period L, of the target filter's band edges. Other sub-filters may include complement and masking filters which filter different parts of the spectrum to achieve the desired response. From an implementation point-of-view, time-multiplexing is beneficial because generally the allowable maximum clock frequency supported by the current state-of-the-art semiconductor technology does not correspond to the application bound sample rate. A combination of these two techniques plays a significant role towards efficient implementation of FIR filters. Part of the work presented in this dissertation is architectures for time-multiplexed FRM filters that benefit from the inherent sparsity of the periodic model filters.

These time-multiplexed FRM filters not only reduce the number of multipliers but lowers the memory usage. Although the FRM technique requires a higher number delay elements, it results in fewer memories and more energy efficient memory schemes when time-multiplexed. Different memory arrangements and memory access schemes have also been discussed and compared in terms of their efficiency when using both single and dual-port memories. An efficient pipelining scheme has been proposed which reduces the number of pipelining registers while achieving similar clock frequencies. The single optimal point where the number of multiplications is minimum for non-time-multiplexed FRM filters is shown to become a function of both the period, L and time-multiplexing factor, M. This means that the minimum number of multipliers does not always correspond to the minimum number of multiplications which also increases the flexibility of implementation. These filters are shown to achieve power reduction between 23% and 68% for the considered examples.

To simplify the multiplier, alternate number systems like the logarithmic number system (LNS) have been used to implement FIR filters, which reduces the multiplications to additions. FIR filters are realized by directly designing them using integer linear programming (ILP) in the LNS domain in the minimax sense using finite word length constraints. The branch and bound algorithm, a typical algorithm to implement ILP problems, is implemented based on LNS integers and several branching strategies are proposed and evaluated. The filter coefficients thus obtained are compared with the traditional finite word length coefficients obtained in the linear domain. It is shown that LNS FIR filters provide a better approximation error compared to a standard FIR filter for a given coefficient word length.

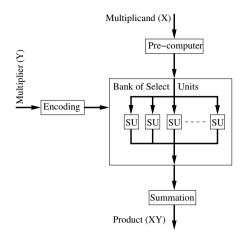

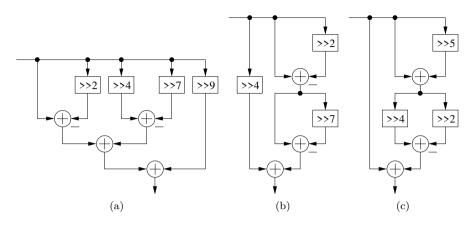

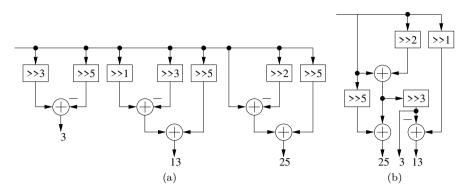

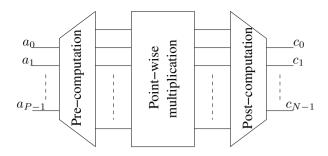

FIR filters also offer an opportunity in complexity reduction by implementing the multipliers using Booth or standard high-radix multiplication. Both of these multiplication schemes generate pre-computed multiples of the multiplicand which are then selected based on the encoded bits of the multiplier. In transposed direct form (TDF) FIR filters, one input data is multiplied with a number of coefficients and complexity can be reduced by sharing the precomputation of the multiplies of the input data for all multiplications. Part of this work includes a systematic and unified approach to the design of such computation sharing multipliers and a comparison of the two forms of multiplication. It also gives closed form expressions for the cost of different parts of multiplication and gives an overview of various ways to implement the select unit with respect to the design of multiplexers.

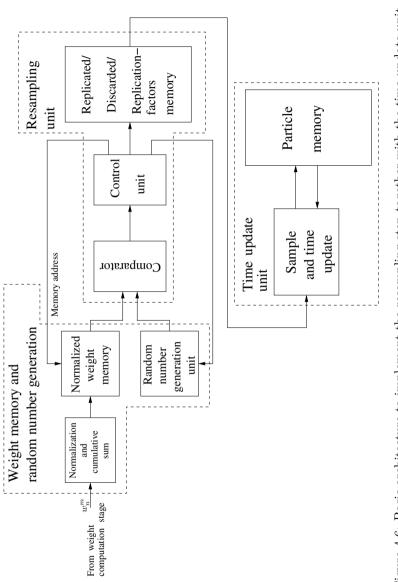

Particle filters are used to solve problems that require estimation of a system. Improved resampling schemes for reducing the latency of the resampling stage is proposed which uses a pre-fetch technique to reduce the latency between 50% to 95% dependent on the number of pre-fetches. Generalized division-free architectures and compact memory structures are also proposed that map to different resampling algorithms and also help in reducing the complexity of the multinomial resampling algorithm and reduce the number of memories required by up to 50%.

# Populärvetenskaplig Sammanfattning

Digitala filter är signalbehandlingsalgoritmer som används i många olika typer av applikationer och system. Som i de flesta fall finns det ett generellt intresse att göra saker enklare och effektivare. I denna avhandlingen studeras två olika klasser av filter och förbättringar föreslås för effektivare implementering av dessa filter.

Den första klassen av filter är så kallade FIR filter. Dessa kräver typiskt många operationer när det finns strikta krav på filtreringen. Då multiplikationer är klart mer komplexa än additioner, både var gäller area, tid och effektförbrukning, så fokuseras arbetet på dessa. Traditionellt finns det två spår för att förbättre detta: antingen minskar man antalet multiplikationer eller så förenklar man multiplikationerna. Metoder för bägge områdena föreslås i detta arbetet.

Ett effektivt sätt att konstruera FIR filter med väldigt smalt övergångsband, dvs avståndet mellan frekvenser som släpps igenom och som dämpas, är att använda frekvensmaskning. I denna typen av filter så använder man ett filter där många av multiplikationerna är noll och därmed inte behöver beräknas. Detta filter har nollorna fördelade i ett periodiskt mönster vilket leder till att beteendet i frekvensdomänen också blir periodiskt. Fördelen är att komplexiteten för att skapa ett väldigt smalt övergångsband skalar omvänt proportionellt med perioden, så ju högre period desto lägre komplexitet. Då det oftast inte är ett periodiskt filter man vill ha i slutänden så behövs det ytterligare filter som tar bort de oönskade delarna i frekvensdomänen. Dessa har typiskt högre komplexitet för högre period, så en lagom avvägning måste hittas.

Trots mycket tidigare arbete på att konstruera sådana filter har väldigt lite arbete lagts på att implementera dem effektivt. Här har vi speciellt tittat på fallet där datatakten, som bestäms av applikationen, och kretsens klockfrekvens, som bestäms av implementeringsteknologin, inte är samma. Specifikt det mest realistiska fallet att datatakten är lägre än klockfrekvensen. En arktitektur som tar hänsyn till det periodiska filtret har föreslagits och olika möjligheter har utretts i detalj. Resultaten visar att vid implementering på en FPGA så minskar mängden minne som används, tvärtemot vad man kan tro. Ett ytterligare resultat är att effekten minskar ca 80% av minskningen i antal multiplikationer. Ett alternativ för att minska komplexiteten på multiplikationerna är att använda logaritmiska talsystem (LNS). I dessa blir multiplikationerna bara en addition av exponenterna. I detta sammanhanget har för första gången optimala filter konstruerats direkt i den logaritmiska domänen med ändlig ordlängd. Att kunna konstruera optimala filter i både den linjära och logaritmiska domänen är en förutsättning för att kunna göra korrekta jämförelser mellan filter implementerade i de bägge domänerna.

Ytterligare ett alternativ för att minska komplexiteten på multiplikationerna är att använda multiplikatorer med högre radix och dela vissa delar mellan flera multiplikatorer. Vid implementering av FIR filter uppkommer ett mycket gynnsamt fall för detta. I avhandlingen föreslår vi ett enhetligt sätt att konstruera och utvärdera denna typ av multiplikatorer. På så sätt visar vi att tidigare arbeten bara var specialfall av denna generella metod. Då tidigare arbeten inte visat hur parametrar valt eller i vissa fall ej ens insett kopplingen till multiplikatorer med högre radix, kan vi visa hur man bör välja parametrar för bästa effektivitet.

Till sist behandlas en helt annan typ av digitala filter. Dessa så kallade partikelfilter används för att skatta tillstånd i dynamiska system. Den kritiska delen för effektiv implementering här är omsamplingssteget. Vi förslår tre metoder för att förbättra implementeringen av detta. En direkt implementering av omsampling bygger på att man jämför innehållet i två minnen. Varje cykel läser man från ett av minnena, vilket beroende på resultatet av tidigare jämförelse. Den förbättrade metoden bygger på att man läser in extra data från det ena minnet och kan på så sätt utföra den total jämförelsen snabbare. Med bara ett extra jämförelseblock kan man statistiskt minska den kritiska tiden med 56%. Den andra metoden löser problemet med att normalisering av värdena som jämförs, vilket normalt kräver en division. Istället används enbart multiplikationer och som en bieffekt så kan vi även skapa sekvenser av sorterade slumptal på ett nytt effektivt sätt. Till sist visar vi att upp till hälften av minnet som används för att spara sekvenserna som ska jämföras kan sparas genom att beräkna resultaten i real-tid.

## Acknowledgments

Praise be to Al-Mighty Allah, the most Compassionate, the most Merciful, who gave me an opportunity to contribute to the vast body of knowledge. Peace and blessings of Allah be upon the Holy Prophet Muhammad (Peace be upon Him), the last Prophet of Allah, who has always exhorted his followers to seek knowledge and whose life is the glorious model for the humanity.

There are a lot of people to whom I would like to express my gratitude. The following is certainly not exhaustive but an effort to thank those who had the most impact on my research and life in Linköping:

- My advisor, Dr. Oscar Gustafsson, for having confidence in me by giving me an opportunity to complete my PhD. I am greatly indebted to him for his inspiring and valuable guidance, enlightening discussions, his patience when ever I was short of his standards and constant encouragement in difficult times, kind and dynamic supervision through out and in all the phases of this thesis. Working and learning from him was always a pleasure. Thank you Oscar.

- My co-supervisor, Dr. Kent Palmkvist, for help with FPGA, VHDL and Linux related issues.

- The former and present colleagues at the old Division of Electronics Systems, Department of Electrical Engineering, Linköping University for creating a very friendly environment. They always were kind enough to do their best to help you.

- The former and present colleagues at the Division of Computer Engineering, Department of Electrical Engineering, Linköping University for making me feel welcome when I joined their division and helping out when needed.

- A special thanks to our current and past secretary Gunnel Hässler and Susanna von Sehlen for helping out in various administrative tasks.

- A special thanks to Doktorand Syed Ahmed Aamir for his support, both materialistic and spiritual, during my early days in Linköping which immensely helped me in settling in this city.

- My present and former room-mates, Dr. Fahad Qureshi, Doktorand Carl Ingemarsson and Doktorand Fahim-ul-Haque for putting up with me,

building a good working environment and having discussions on mundane and technical issues.

- Dr. Muhammad Abbas for his help and guidance at the start of my PhD studies.

- Doktorand Muhammad Touqir Pasha and Doktorand Fahim-ul-Haque for proof reading and giving valuable advice while I was writing my thesis.

- Dr. Fahad Qazi, Doktorand Muhammad Touqir Pasha, Dr. Jawad ul Hassan, Dr. Hafiz Muhammad Sohail, Dr. Nadeem Afzal, Dr. Irfan Kazim, Dr. Usman Dastageer, Dr. Muhammad Junaid and others for building a nice social circle without which it would have been hard for me and my family to live here.

- Finally a special thanks to my family

- My mother, Tanweer Alam, for her immense love, sacrifices, guidance, support and upbringing. Without her I would not be where I am. Without her life means nothing to me. It was on her encouragement that I took the decision to pursue PhD even though living so far apart was always troubling for her. Thanks Maa, because without your prayers and support, I would not have been able to complete my studies.

- My wife, Eyshaa Zehra, you have been a true life partner, bearing the load of taking care of home and children while I spent long hours in office, for always showing love, patience, affection to me and for your immense support and cooperation. You made taking a lot of tough decisions easy for me.

- A special thanks to my children, Muhammad and Arwaa, whom I am sure will read this when they grow up, for taking away all the tiredness and stress with their beautiful smiles, small giggles and playful gestures while welcoming me home.

- My whole extended family in Pakistan, Canada and the U.S.A, my in-laws, my aunts and uncles, my cousins etc., for always being there for me and for making me feel special.

- To those not listed here, I say profound thanks for bringing pleasant moments in my life.

Syed Asad Alam, January 21, 2016, Linköping Sweden.

# Abbreviations

| 2C     | Two's complement                               |

|--------|------------------------------------------------|

| ASIC   | Application specific integrated circuit        |

| ASIP   | Application specific instruction set processor |

| BILP   | Binary integer linear programming              |

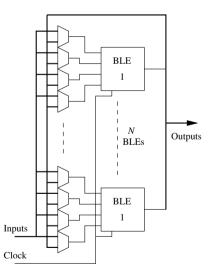

| BLE    | Basic logic element                            |

| BMI    | Brain machine interface                        |

| CFGLUT | Configurable LUT                               |

| CLB    | Configurable logic block                       |

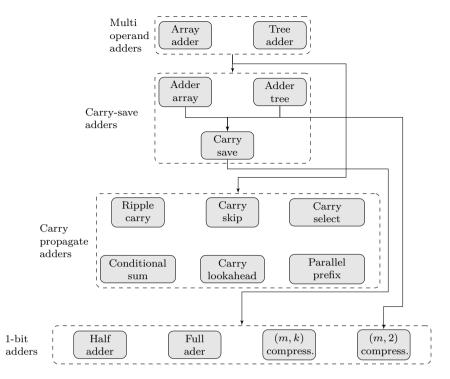

| СРА    | Carry propagate adder                          |

| CPLD   | Complex programmable logic device              |

| CPU    | Central processing unit                        |

| CSA    | Carry save adder                               |

| CSD    | Canonic signed digit                           |

| CSE    | Common subexpression elimination               |

| CU     | Control unit                                   |

| DA     | Distributed arithmetic                         |

| DAG    | Directed acyclic adder graphs                  |

| DF     | Direct form                                    |

| DFT    | Discrete fourier transform                     |

| DSP    | Digital signal processing                      |

| EEPROM | Electrically erasable programmable read only memory |

|--------|-----------------------------------------------------|

| EPROM  | Electrically programmable read only memory          |

| FF     | Flip flop                                           |

| FFA    | Fast FIR                                            |

| FFT    | Fast fourier transform                              |

| FIFO   | First in first out                                  |

| FIR    | Finite-length impulse response                      |

| FPGA   | Field programmable gate array                       |

| FRM    | Frequency-response masking                          |

| FSM    | Finite state machine                                |

| GPC    | Generalized parallel counter                        |

| GPU    | Graphical processing unit                           |

| HDL    | Hardware description language                       |

| НММ    | Hidden Markov model                                 |

| НРМ    | High performance multiplier                         |

| IC     | Integrated circuit                                  |

| ICAP   | Internal configuration access port                  |

| IDFT   | Inverse DFT                                         |

| IFIR   | Interpolated FIR                                    |

| IIR    | Infinite impulse response                           |

| ILP    | Integer linear programming                          |

| IMHA   | Independent Metropolis Hastings algorithm           |

| LNS    | Logarithmic number system                           |

| LP     | Linear programming                                  |

| LSB    | Least significant bit                               |

| LUT    | Look-up table                                       |

| MAC    | Multiply-accumulate                                 |

xii

#### Abbreviations

| мс     | Monte Carlo                                |

|--------|--------------------------------------------|

| мсм    | Multiple constant multiplication           |

| MILP   | Mixed integer linear programming           |

| MPGA   | Mask programmable gate array               |

| MSB    | Most significant bit                       |

| MSD    | Minimal signed digit                       |

| MSE    | Mean square error                          |

| NP     | Non-deterministic polynomial               |

| OPR    | Overlapped partial resampling              |

| PAL    | Programmable array logic                   |

| PAG    | Pipelined adder graph                      |

| PE     | Processing element                         |

| PLA    | Programmable logic array                   |

| PLD    | Programmable logic device                  |

| РМСМ   | Pipelined MCM                              |

| PROM   | Programmable read only memory              |

| RCA    | Ripple-carry adder                         |

| RNA    | Resampling with nonproportional allocation |

| RNS    | Residue number system                      |

| RPA    | Resampling with proportional allocation    |

| RPAG   | Reduced pipelined adder graph              |

| RSG    | Reduced slice graph                        |

| RSR    | Residual systematic resampling             |

| RTL    | Register transfer level                    |

| S-ASIC | Structured ASIC                            |

| SCM    | Single constant multiplication             |

| SD     | Signed digit                               |

| SEU  | Single-event upset                 |

|------|------------------------------------|

| SIMD | Single instruction multiple data   |

| SIS  | Sequential importance sampling     |

| SM   | Signed magnitude                   |

| SMC  | Sequential Monte Carlo             |

| SPT  | Signed power of two                |

| SRAM | Static random access memory        |

| SSF  | Single stage FIR                   |

| STM  | State transition model             |

| TDF  | Transposed direct form             |

| TID  | Total ionizing dose                |

| ulp  | Unit of least significant position |

| VLSI | Very large scale integrated        |

# Contents

| Ι        | ckground                  | 1                                                       |           |

|----------|---------------------------|---------------------------------------------------------|-----------|

| 1        | Inti                      | roduction                                               | 3         |

|          | 1.1                       | Motivation                                              | 3         |

|          |                           | 1.1.1 Reduction in Number of Multipliers                | 4         |

|          |                           | 1.1.2 Reduction in Multiplier Complexity                | 5         |

|          |                           | 1.1.3 Improved Particle Filter Resampling Architectures | 7         |

|          | 1.2                       | List of Publications                                    | 7         |

|          |                           | 1.2.1 Other Publications                                | 8         |

|          | 1.3                       | Thesis Organization                                     | 8         |

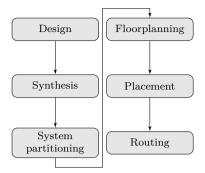

| <b>2</b> | Imp                       | elementation Aspects of DSP Algorithms                  | 11        |

|          | 2.1                       | Introduction                                            | 11        |

|          | 2.2                       | Implementation Platforms                                | 12        |

|          |                           | 2.2.1 Application Specific Integrated Circuits          | 13        |

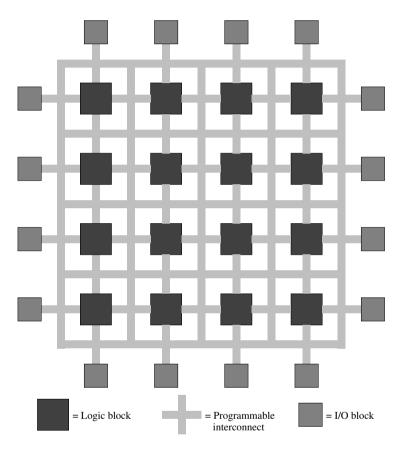

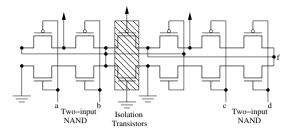

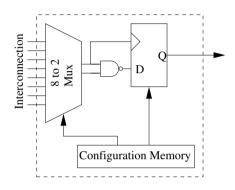

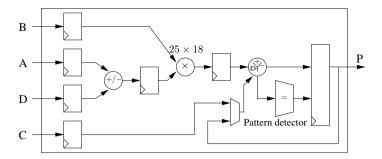

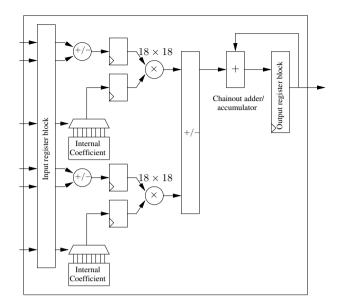

|          |                           | 2.2.2 Field Programmable Gate Arrays                    | 15        |

|          | 2.3                       | Key Arithmetic Operators in DSP Implementations         | 25        |

|          |                           | 2.3.1 Adders                                            | 25        |

|          |                           | 2.3.2 Multipliers                                       | 32        |

|          |                           | 2.3.3 Multiple Constant Multiplication                  | 38        |

|          | 2.4                       | Number Systems                                          | 43        |

| 3        | Fin                       | ite-length Impulse Response Filters                     | <b>47</b> |

|          | 3.1                       | Introduction                                            | 47        |

|          | 3.2                       | Impulse Response of FIR Filters                         | 47        |

|          | 3.3                       | Linear Phase FIR Filters                                | 48        |

|          | 3.4                       | FIR Filters: Input and Output Relationship              | 49        |

|          | 3.5                       | FIR Filter Structures                                   | 49        |

|          | 3.6 Design of FIR Filters |                                                         | 51        |

|          |                           | 3.6.1 Error Approximation                               | 52        |

|          |                           | 3.6.2 FIR Filter Design by Optimization                 | 53        |

|          |                           | 3.6.3 Remez/Park-McClellan FIR Filter Design            | 53        |

|          |                           | 3.6.4 FIR Filter Design by Linear Programming           | 53        |

|          |                                               | 3.6.5                                                                                                                                                              | FIR Filter Design by Cascade of Sub-Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                            |                                       |         | 56                                                                                                                 |

|----------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------|---------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------|

|          |                                               | 3.6.6                                                                                                                                                              | Sparse FIR Filter Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • •                                   |                            |                                       |         | 63                                                                                                                 |

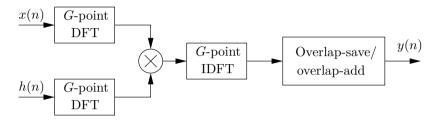

|          | 3.7                                           | Fast F                                                                                                                                                             | IR Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • •                                   |                            |                                       |         | 64                                                                                                                 |

|          | 3.8                                           | FIR F                                                                                                                                                              | ilter using Alternate Number Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |                            |                                       |         | 69                                                                                                                 |

|          |                                               | 3.8.1                                                                                                                                                              | FIR Filter using Logarithmic Number System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |                            |                                       |         | 69                                                                                                                 |

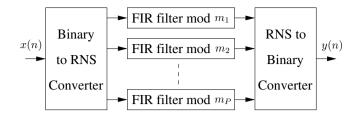

|          |                                               | 3.8.2                                                                                                                                                              | FIR Filter using Residue Number System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • •                                   |                            |                                       | •       | 70                                                                                                                 |

| 4        | Par                                           | ticle F                                                                                                                                                            | ilters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                            |                                       |         | 73                                                                                                                 |

|          | 4.1                                           | Introd                                                                                                                                                             | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                            |                                       |         | 73                                                                                                                 |

|          | 4.2                                           |                                                                                                                                                                    | ematical Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |                            |                                       |         | 74                                                                                                                 |

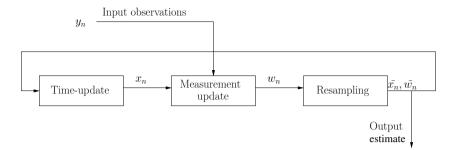

|          | 4.3                                           |                                                                                                                                                                    | le Filtering Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                            |                                       |         | 75                                                                                                                 |

|          |                                               | 4.3.1                                                                                                                                                              | Time-Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                            |                                       |         | 76                                                                                                                 |

|          |                                               | 4.3.2                                                                                                                                                              | Measurement-Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                            |                                       |         | 76                                                                                                                 |

|          |                                               | 4.3.3                                                                                                                                                              | Resampling in Particle Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |                            |                                       |         | 76                                                                                                                 |

|          |                                               |                                                                                                                                                                    | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |                            |                                       |         |                                                                                                                    |

| <b>5</b> | Sun                                           | nmary                                                                                                                                                              | and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |                            |                                       |         | 85                                                                                                                 |

|          | 5.1                                           | Summ                                                                                                                                                               | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |                            |                                       |         | 85                                                                                                                 |

|          | 5.2                                           | Future                                                                                                                                                             | e Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                            |                                       | •       | 86                                                                                                                 |

| Re       | efere                                         | nces                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |                            |                                       |         | 89                                                                                                                 |

|          |                                               |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |                            |                                       |         | 89                                                                                                                 |

|          |                                               |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••                                   | •                          | •                                     | •       | 00                                                                                                                 |

|          | nen                                           |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |                            |                                       |         |                                                                                                                    |

| TT       |                                               |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |                            |                                       | 1       |                                                                                                                    |

| II       |                                               |                                                                                                                                                                    | ations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                            |                                       | 1       | .11                                                                                                                |

|          | P<br>On                                       | ublica<br>the Im                                                                                                                                                   | ations<br>plementation of Time-Multiplexed Frequency-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ·R                                    | es                         | s <b>p</b>                            | _       |                                                                                                                    |

|          | P<br>On                                       | ublica<br>the Im<br>sking H                                                                                                                                        | ations<br>plementation of Time-Multiplexed Frequency-<br>Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |                            |                                       | on<br>1 | se<br>13                                                                                                           |

|          | P<br>On                                       | ublica<br>the Im<br>sking F<br>Introd                                                                                                                              | ations<br>plementation of Time-Multiplexed Frequency-<br>Filters<br>Juction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                            |                                       | on<br>1 | <b>se</b><br>1 <b>13</b><br>116                                                                                    |

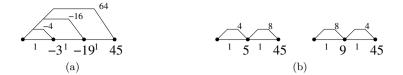

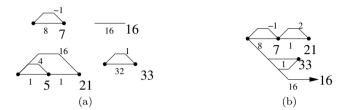

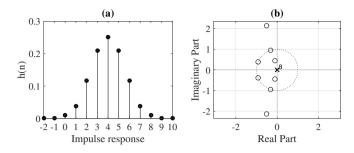

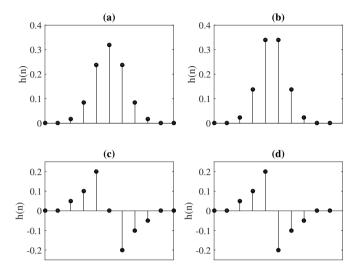

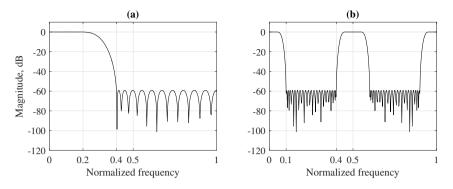

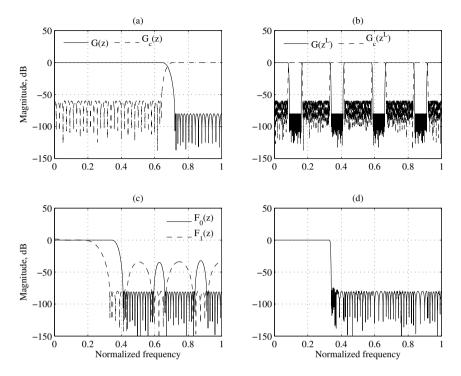

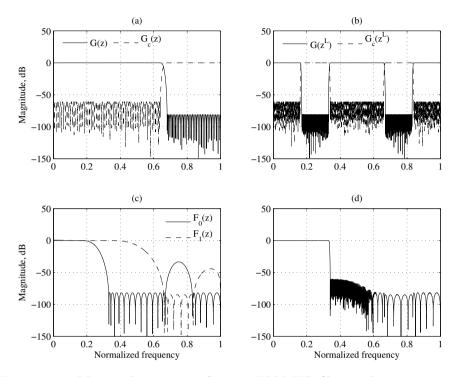

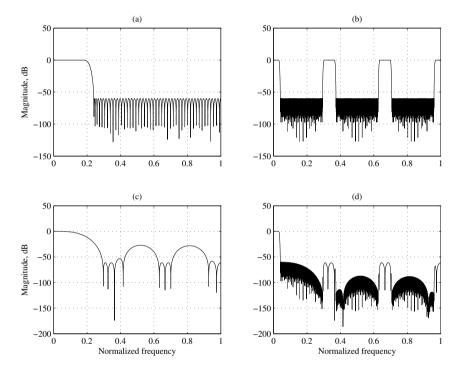

|          | <b>P</b><br><b>On</b><br><b>Mas</b><br>1<br>2 | ublica<br>the Im<br>sking H<br>Introd<br>Freque                                                                                                                    | ations plementation of Time-Multiplexed Frequency- Filters fuction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       | •                          |                                       | on<br>1 | <b>se</b><br>1 <b>13</b><br>116<br>118                                                                             |

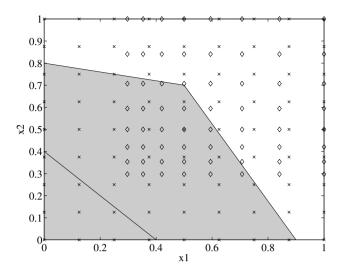

|          | P<br>On<br>Mas<br>1                           | ublica<br>the Im<br>sking H<br>Introd<br>Freque<br>Design                                                                                                          | ations plementation of Time-Multiplexed Frequency- Filters fuction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | · ·                                   |                            |                                       | on<br>1 | se<br>113<br>116<br>118<br>119                                                                                     |

|          | <b>P</b><br><b>On</b><br><b>Mas</b><br>1<br>2 | ublica<br>the Im<br>sking F<br>Introd<br>Freque<br>Design<br>Propo                                                                                                 | ations         plementation of Time-Multiplexed Frequency-         Filters         auction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <br><br>                              |                            |                                       | on<br>] | se<br>113<br>116<br>118<br>119<br>120                                                                              |

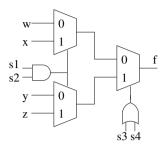

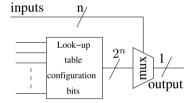

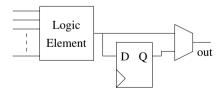

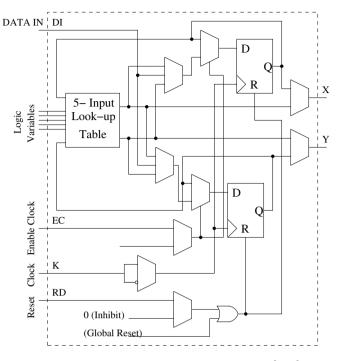

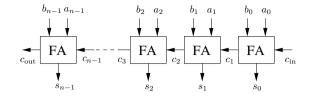

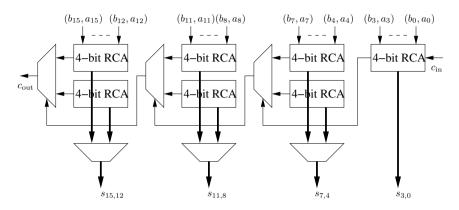

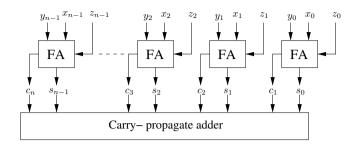

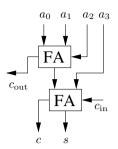

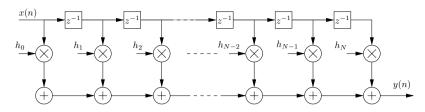

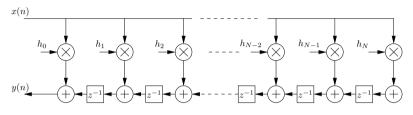

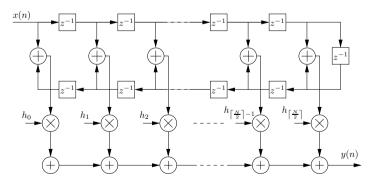

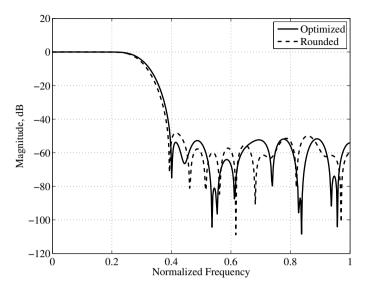

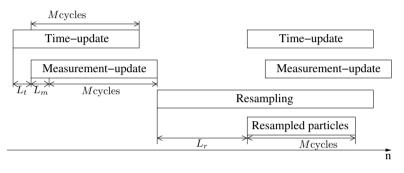

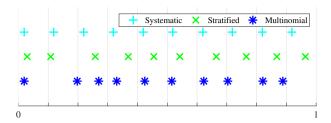

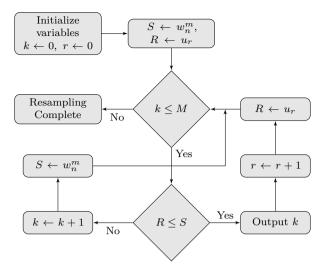

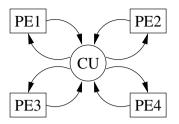

|          | <b>P</b><br><b>On</b><br>1<br>2<br>3          | ublica<br>the Im<br>sking I<br>Introd<br>Freque<br>Design<br>Propos<br>4.1                                                                                         | ations plementation of Time-Multiplexed Frequency- Filters fuction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <br><br>                              |                            |                                       | on<br>] | se<br>113<br>116<br>118<br>119<br>120                                                                              |