# Temperature-Dependent Characterization of AlGaN/GaN HEMTs: Thermal and Source/Drain Resistances

Roberto Menozzi, *Senior Member, IEEE*, Gilberto A. Umana-Membreno, *Member, IEEE*, Brett D. Nener, *Senior Member, IEEE*, Giacinta Parish, *Member, IEEE*, Giovanna Sozzi, Lorenzo Faraone, *Senior Member, IEEE*, and Umesh K. Mishra, *Fellow, IEEE*

(Invited Paper)

Abstract—This paper shows the application of simple dc techniques to the temperature-dependent characterization of AlGaN/GaN HEMTs in terms of the following: 1) thermal resistance and 2) ohmic series resistance (at low drain bias). Despite their simplicity, these measurement techniques are shown to give valuable information about the device behavior over a wide range of ambient/channel temperatures. The experimental results are validated by comparison with independent measurements and numerical simulations.

Index Terms—Gallium compounds, microwave power transistors, MODFETs, power HEMTs, semiconductor-device measurements, semiconductor-device thermal factors, wide bandgap semiconductors, III nitrides, III–V semiconductors.

#### I. INTRODUCTION

ITH UNPARALLELED output power densities such as 12 W/mm at 4 GHz (sapphire substrate) [1] or 5.1 W/mm at 18 GHz (Si substrate) [2], GaN-based HEMTs show excellent microwave power performance. High-power operation requires high power dissipation and, consequently, the need to carefully account for thermal effects when designing and modeling devices and circuits. Reliability estimates also require accurate evaluation of channel temperatures  $(T_C)$  when the accelerated life-testing data are used to extrapolate operating lifetimes.

The aim of this paper, which expands on the previous conference communications [3], [4], is to contribute to the topic of temperature characterization of AlGaN/GaN HEMTs by proposing and applying two simple dc techniques for the fast

Manuscript received November 6, 2007. This work was supported in part by the Australian Research Council Discovery Project Scheme and in part by The University of Western Australia under a Gledden Fellowship Grant.

- R. Menozzi and G. Sozzi are with the Department of Information Technology, University of Parma, 43100 Parma, Italy (e-mail: roberto.menozzi@unipr.it).

- G. A. Umana-Membreno, B. D. Nener, G. Parish, and L. Faraone are with the School of Electrical, Electronic and Computer Engineering, The University of Western Australia, Perth, WA 6009, Australia.

- U. K. Mishra is with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106 USA.

Digital Object Identifier 10.1109/TDMR.2008.918960

evaluation of the values and temperature dependence of the following: 1) the channel-to-base-plate (or ambient) thermal resistance  $R_{\rm TH}$  and 2) the low-field parasitic source/drain series resistance  $R_S+R_D$ . While the usefulness of a simple method for extracting  $T_C$  and  $R_{\rm TH}$  is obvious for both modeling and reliability estimation purposes, a quick experimental technique to evaluate  $R_S+R_D$  is advantageous, for instance, when different process options for the ohmic contacts are to be compared with the finished HEMTs rather than with TLM or other  $ad\ hoc$  test patterns. Moreover, the source/drain parasitic resistances are tightly connected with the well-known current collapse mechanism [5], which is one of the main reliability concerns for GaN-based FETs. Finally, we will show that the extraction procedure defines a simple, yet accurate, analytical model of the drain current at low drain bias.

As far as channel-temperature or thermal-resistance measurements are concerned, several papers have been published over the years, indicating how self-heating evaluation is critical for the AlGaN/GaN HEMTs. In particular, micro-Raman spectroscopy has proven to be a powerful technique [6]–[8] for measuring temperature profiles with high spatial resolution; variants were also demonstrated, which offer time-resolved measurements [9] and 3-D mapping [10], whereas a hybrid Raman/infrared (IR) approach [11] allows for the analysis of large multimaterial structures. Other studies involved liquid crystal thermography [12], photocurrent measurements [13], and scanning thermal microscopy [14]. Each of these direct techniques has its own strengths and weaknesses; generally speaking, they offer the distinctive advantage of some degree of spatial resolution (allowing, for instance, resolution of temperature differences among different gate fingers) but often require costly equipment and time-consuming measurement sessions.

Indirect electrical techniques cannot convey any spaceresolved information but are, on the other hand, simpler and cheaper than direct ones. One classical method for extracting  $T_C$  and  $R_{\rm TH}$  is by comparing temperature-dependent fast-pulsed measurements with dc measurements; examples of application to AlGaN/GaN HEMTs can be found in [15]–[17].

Pulsed techniques do not generally require simplifying assumptions and can provide some information on self-heating dynamics, but one must take care not to mistake electrical transients for thermal ones [15]; moreover, clean, nanosecond-scale, and temperature-dependent pulsed measurements are not easy to perform (particularly on high-power devices) and require *ad hoc* setups and significant measurement effort.

DC electrical techniques are obviously the simplest and cheapest, since they are often relying only on standard  $I{\text -}V$  measurements at different ambient temperatures. The main drawback with respect to pulsed methods is the need to rely sometimes on drastic simplifying assumptions [18], [19], including the independence of the thermal resistance with temperature and dissipated power. However, very few research works have been published in terms of simple dc electrical techniques for measuring  $R_{\rm TH}$ .

A variant of the method developed in [20] for LDMOSFETs is applied here for the first time to extract the  $R_{\rm TH}$  of an AlGaN/GaN HEMT. The method assumes a linear dependence of the drain current  $(I_D)$  on the channel temperature once the linear dependence of  $I_D$  on the ambient temperature  $(T_A)$  has been experimentally demonstrated. It therefore relies on the choice of suitably narrow intervals of  $T_A$  and dissipated power  $(P_D)$ , wherein the drain–current temperature dependence can be linearized with good accuracy and  $R_{\rm TH}$  can be considered constant; apart from this, no other simplifying assumption is necessary. This  $R_{\rm TH}$  extraction procedure requires only dc I-V output curves measured at different ambient temperatures, which is a distinct advantage over classical pulse-based approaches.

As far as the parasitic source/drain resistances are concerned, it is recognized that they play a significant role in limiting the performance of microwave AlGaN/GaN FETs [21]-[25], and novel design and processing concepts have been devised for reducing them [26]–[28]. Their increase is also a serious reliability concern in the current collapse effect [5]. However, measuring these parasitics on individual FETs is not a straightforward task. The estimation is typically tackled either by numerical optimization or analytical manipulation of smallsignal models [29], [30] or by relying on bias conditions that are quite far from operating conditions (e.g., the end-resistance technique [31] and its variants [32]). A disadvantage of the former approach is that it is difficult to attach a clear physical meaning to the extracted resistance values; on the other hand, the latter approach measures  $R_S$  and  $R_D$  under bias conditions where the current flow is very far from normal.

A classical technique for the measurement of compound semiconductor FET source and drain parasitic resistances at low longitudinal electric field is the one proposed by Fukui [33] for GaAs MESFETs. It rests on the assumption that the device can be divided into an intrinsic region obeying the gradual channel approximation (GCA), and therefore some simple analytical current–voltage relationship, and an extrinsic parasitic-resistance region that is not perturbed by the gate voltage. This automatically endows the extracted parasitics with a definite physical meaning;  $R_S$  and  $R_D$  measure the resistance existing between the ohmic contacts and the device region obeying the GCA (provided that one such region exists).

This paper, for the first time, applies (a modification of) Fukui's technique to the measurement of  $R_S + R_D$  of an AlGaN/GaN HEMT and its temperature dependence. The validity of the underlying assumptions is discussed and supported by independent measurements.

This paper is therefore organized as follows. Section II briefly describes the HEMT under test and the additional structures measured to support the parasitic-resistance measurements. In Section III, we illustrate the procedure to measure  $R_{\rm TH}$  and show and discuss the results it gives; Section IV does the same for the measurement of the source and drain parasitic resistances. Conclusion is given in Section V.

#### II. HEMTS UNDER TEST

The devices under test were AlGaN/GaN HEMTs grown and processed at the University of California, Santa Barbara.

They were grown on a  $325-\mu$ m-thick sapphire substrate. A 0.7- $\mu$ m Fe-doped GaN layer is followed by 50 nm of AlN, on top of which lies the 1.7- $\mu$ m-thick unintentionally doped GaN layer hosting the 2DEG; this is separated from the 29-nm Si-doped Al<sub>0.22</sub>Ga<sub>0.78</sub>N layer on top by a thin (0.6 nm) AlN interfacial layer for an improved 2DEG confinement.

The gate length is  $L_G = 0.9 \mu m$ , and the width is  $W_G = 150 \mu m$ . The source–gate and drain–gate separations are 0.7 and  $1 \mu m$ , respectively.

A long-gate HEMT with  $L_G=20~\mu\mathrm{m},~W_G=300~\mu\mathrm{m},$  and  $5+5~\mu\mathrm{m}$ -long ungated regions was also used for Hall-effect measurements of the 2DEG carrier density  $(n_S)$  and mobility  $(\mu_n)$  versus gate bias, whereas temperature-dependent low-field 2DEG mobilities were extracted on a  $40\times400~\mu\mathrm{m}$  ungated HEMT.

Although sapphire substrates are thermally outperformed by SiC and Si ones, sapphire wafers are much cheaper than SiC ones, and the growth of HEMT templates on sapphire is more mature than on silicon. It should also be noted that recent reports show how the problem of poor thermal conduction via the substrate can be overcome by using front-side cooling techniques [34], [35]. Moreover, the thermal performance of the substrate, which can be a serious problem in continuous-wave mode, tends to be less of a limiting factor when the HEMTs are operated in pulsed mode [36].

#### III. THERMAL-RESISTANCE MEASUREMENTS

### A. Method

Provided that the drain current  $I_D$ , at a fixed value of the gate–source voltage  $V_{\rm GS0}$  and for a drain–source voltage  $V_{\rm DS}$  biasing the HEMT in saturation, is experimentally observed to be a linear function of  $T_A$ , i.e.,

$$I_D(V_{GS0}, V_{DS}, T_A) = I_D(V_{GS0}, V_{DS}, T_{A0}) + h \cdot (T_A - T_{A0})$$

$$= I_{D0} + h \cdot (T_A - T_{A0}) \tag{1}$$

where  $T_{A0}$  is a reference ambient temperature, the parameter h can be measured by plotting  $I_D$  versus  $T_A$  and interpolating

with a straight line. If it exists, the observed linear dependence (1) must be due to a linear dependence of  $I_D$  on  $T_C$

$$I_D(V_{GS0}, V_{DS}, T_C) = I_{D0} + h' \cdot (T_C - T_{C0})$$

(2)

where  $T_{\rm C0}$  is the channel temperature determined by  $T_{\rm A0}$ ,  $V_{\rm GS0}$ , and  $V_{\rm DS}$ . However, by definition of the thermal resistance  $R_{\rm TH}$

$$T_C - T_{C0} = T_A - T_{A0} + R_{TH} \cdot V_{DS} \cdot (I_D - I_{D0})$$

(3)

hence substituting (3) into (2) and rearranging, one obtains

$$\frac{1}{h} = \frac{1}{h'} - R_{\rm TH} \cdot V_{\rm DS}.\tag{4}$$

By repeating this procedure at different values of  $V_{\rm DS}$  in the saturation region, 1/h can be plotted versus  $V_{\rm DS}$ . If the model is correct, the plot should be a straight line based on (4), and  $R_{\rm TH}$  can be obtained as the slope of the best fit line.

#### B. Experimental Results

The HEMTs were mounted on open TO headers, and their dc output curves (together with other characteristics recorded for monitoring purposes) were measured inside a liquid He-cooled cryostat at various temperatures starting from  $T_A = 74$  K, with 5-K temperature steps, up to 495 K. Each measurement point was taken after a 60-s delay to let the temperature settle. The gate-source voltage values were  $V_{GSO} = 0$ , -0.5, and -1 V; at lower  $V_{\mathrm{GS}}$ , self-heating is marginal, and the results become noisy. The  $T_A$  interval for  $R_{\rm TH}$  extraction was fixed at 20 K. The section of the saturated region of the output curves used here spans from  $V_{\rm DS}=4$  to 10 V. While (4) is seen to hold well enough in the entire 4-10-V  $V_{\rm DS}$  range for most of the temperatures, further restricting the  $V_{\rm DS}$  range allows for a separate  $R_{\rm TH}$  extraction in the lower (4–7 V) and upper (7–10 V)  $V_{\rm DS}$  ranges, thus yielding information on the dependence of  $R_{\rm TH}$  on  $P_D$ . Results are shown below for  $T_A \ge 200$  K. For lower temperatures, the method gives nonphysical results, probably because the thermal conductivity of sapphire changes too much with temperature [37] for  $R_{\rm TH}$  to be considered constant in a 20-K ambient temperature interval.

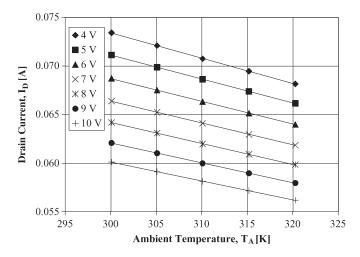

Fig. 1 shows the typical  $I_D$  versus  $T_A$  data. In all of the ambient temperature intervals probed, (1) is obeyed with good accuracy.

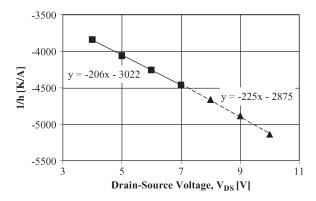

The values of 1/h obtained from the graphs similar to those in Fig. 1 have been plotted based on (4) to obtain  $R_{\rm TH}$ . Fig. 2 shows an example of such plots.

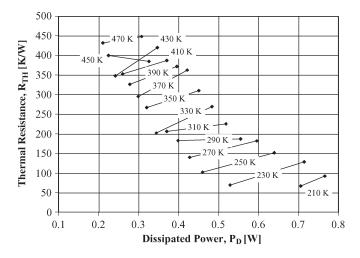

A comprehensive plot of the results obtained for  $V_{\rm GS0}=0~{\rm V}$  is shown in Fig. 3. With only one exception (the 450-K data), the results are well behaved, with  $R_{\rm TH}$  increasing as expected with ambient temperature and dissipated power. Plots corresponding to  $V_{\rm GS0}=-0.5~{\rm V}$  and  $V_{\rm GS0}=-1~{\rm V}$  look much like Fig. 3.

In order to have a comprehensive but readable chart showing the  $R_{\rm TH}$  values obtained for all of the  $V_{\rm GS0}$  values and also to check the internal consistency of the data, the thermal resistances can be used to compute the corresponding channel temperatures in each interval, and then,  $R_{\rm TH}$  can

Fig. 1. Temperature dependence of  $I_D$ . Based on (1), the best fit lines yield the h value at each  $V_{\rm DS}$  (shown in the legend).  $V_{\rm GS0}=0~{\rm V}$ .

Fig. 2. Reciprocal of the h parameter [with h extracted from  $I_D-T_A$  data based on (1)], which is plotted as a function of the drain–source voltage. Based on (4), the best fit line yields (solid line)  $R_{\rm TH}=206$  K/W for  $V_{\rm DS}=4$ –7 V and (dashed line)  $R_{\rm TH}=225$  K/W for  $V_{\rm DS}=7$ –10 V.  $V_{\rm GS0}=0$  V.

Fig. 3. Thermal resistance versus dissipated power at  $V_{\rm GS0}=0$  V. Each ambient temperature value is an average over a 20-K interval of  $T_A$ .  $P_D$  values are also averaged over the 4–7- and 7–10-V  $V_{\rm DS}$  intervals, as shown in Fig. 2.

be plotted as a function of  $T_C$ . Since the  $R_{\rm TH}$  values have been extracted independently in several different  $T_A$  and  $P_D$  intervals, a well-behaved dependence of  $R_{\rm TH}$  on  $T_C$  is not a self-fulfilling prophecy, and although it cannot be considered as

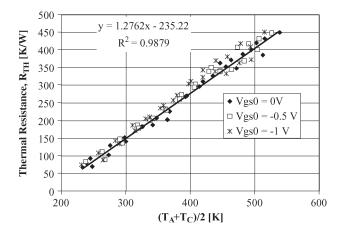

Fig. 4. Thermal resistance versus the average of ambient and channel temperature.  $T_C$  is calculated as  $T_C = T_A + R_{\mathrm{TH}} P_D$ , where  $T_A$  and  $P_D$  are the average values of each extraction interval.

an independent validity check for the method, it is a necessary condition for self-consistency.

The  $R_{\mathrm{TH}}$  versus  $T_C$  data thus obtained (not shown here) are well grouped along a straight line, indicating a good internal consistency of the method. However, the extracted  $R_{\mathrm{TH}}$  values tend to increase slightly, at each fixed channel temperature, when  $V_{\rm GS0}$  is decreased from 0 to -0.5 V and to -1 V, which reduces the correlation with  $T_C$  ( $R^2 = 0.9733$ ). A possible explanation for this behavior is the following. At lower  $V_{\rm GSO}$ , the dissipated power  $P_D$  is also lower, and each fixed value of  $T_C$  is obtained with a combination of lower  $P_D$  and higher  $T_A$  with respect to the case of higher  $V_{\rm GS0}$ . However, it must be considered that for a given channel temperature  $T_C$ , one can expect a larger or smaller  $R_{\rm TH}$  depending on the higher or lower value of the ambient (i.e., back-of-the-wafer) temperature  $T_A$  since most of the thermal resistance is caused by the sapphire substrate, which sits at an average temperature somewhere between  $T_A$  and  $T_C$ . Therefore, at the same  $T_C$ , a lower  $V_{\rm GS0}$  means a larger  $T_A$ , hence a larger  $R_{\rm TH}$ . If this explanation is correct, one should see a better correlation by plotting  $R_{\rm TH}$  versus the average of  $T_C$  and  $T_A$ . This is shown in Fig. 4. As anticipated, the correlation is better  $(R^2 = 0.9879)$ .

The excellent linear fit observed in Fig. 4 can be used to extract a compact formula to calculate the HEMT channel temperature as a function of  $T_A$  and  $P_D$ . By replacing the best fit line equation values for Fig. 4 in the formula  $T_C = T_A + R_{\rm TH} P_D$  and rearranging, in our case, one obtains

$$T_C = \frac{T_A + (0.638 \cdot T_A - 235) \cdot P_D}{1 - 0.638 \cdot P_D} \tag{5}$$

where  $P_D$  is in watts, and temperatures are in kelvin.

#### C. Simulations

In order to check the validity of our results, channel temperatures obtained from (5) have been compared with the results of 3-D numerical heat transport simulations using Synopsys Sentaurus (formerly ISE DESSIS). The temperature dependence of the thermal conductivity of sapphire has been simulated by using quadratic fits (between 200 K and 600 K)

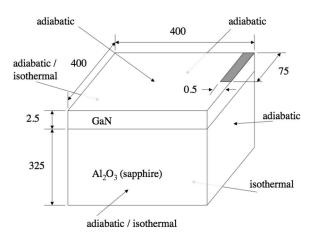

Fig. 5. Schematic view (not to scale) of the 3-D structure used in the simulations. Dimensions are expressed in micrometers. Isothermal surfaces are set at  $T=300~\rm K$ .

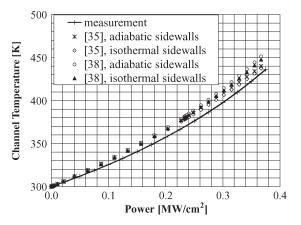

Fig. 6. Measured and simulated channel temperatures versus dissipated power density. The thermal conductivity of sapphire is taken either from [35] or [38]. Sidewalls that are not symmetry planes (see Fig. 5) are simulated either as adiabatic or isothermal (at 300 K).

to the formulas and data in [38]  $(k(\text{Al}_2\text{O}_3) = 5.21 \cdot 10^{-6} \cdot T^2 - 5.40 \cdot 10^{-3} \cdot T + 1.52 \,\text{W/cm/K}$ , where T is expressed in kelvin) and [35]  $(k(\text{Al}_2\text{O}_3) = 2.11 \cdot 10^{-6} \cdot T^2 - 2.47 \cdot 10^{-3} \cdot T + 9.12 \cdot 10^{-1} \,\text{W/cm/K}$ , where T is expressed in kelvin). The thermal conductivity of the 2.5- $\mu$ m-thick GaN is obviously much less critical; we used a quadratic fit to the formula found in [35]  $(k(\text{GaN}) = 1.54 \cdot 10^{-5} \cdot T^2 - 1.71 \cdot 10^{-2} \cdot T + 5.43 \,\text{W/cm/K}$ , where T is expressed in kelvin).

The simulated structure is schematically shown (not to scale) in Fig. 5. The HEMT has been considered as a  $150 \times 1~\mu m$  uniform surface heating element. By using symmetry, only one-fourth of the 3-D structure needs to be simulated; the two-symmetry planes are being replaced with adiabatic surfaces, as shown in Fig. 5. The top surface is also adiabatic, whereas the bottom of the wafer is isothermal  $(T=300~{\rm K})$ , i.e., it is considered to be a perfect heat sink. The remaining two surfaces have been simulated as either adiabatic or isothermal  $(T=300~{\rm K})$  to provide us with upper and lower bounds, respectively, to the channel temperature.

Fig. 6 shows the simulation results compared with the experimental ones, as approximated by (5). Equation (5) is seen to yield  $T_C$  values within 10 K (best case) to 20 K (worst

case) of the maximum lattice temperatures calculated by the simulations, over a wide range of power densities and up to  $T_C=440~\rm K$ . The agreement between measurements and simulations is remarkable, considering that, as previously described, no fitting parameter has been used in the simulations. It should also be noticed that, apart from the approximation inherent with (5), the measured temperature can be expected to represent an average over the active device region; hence, it is lower than the maximum lattice temperature given by the simulations.

#### D. Summary

Our simple dc technique yields well-behaved temperature and dissipated power dependence of the extracted thermal resistance values, which allows the definition of a simple formula whereby the thermal resistance can be calculated for every ambient temperature and dissipated power of interest. This formula gives thermal resistance values in good agreement with those calculated by a 3-D numerical heat transport simulator.

## IV. SOURCE/DRAIN PARASITIC-RESISTANCE MEASUREMENTS

#### A. Method

The method that Fukui developed for measuring  $R_S + R_D$  of GaAs MESFETs [33] rests on the assumption that the device can be divided into an intrinsic region obeying the GCA, and therefore some simple analytical current–voltage relationship, and an extrinsic parasitic-resistance region that is not perturbed by the gate voltage. Under these conditions, the total drain–source resistance of the FET in the linear region can be written as

$$R_T = \frac{V_{\rm DS}}{I_D} = R_S + R_D + R_{\rm CH} = R_S + R_D + \frac{1}{f(V_{\rm GS} - V_T)}$$

(6)

where the channel resistance  $R_{\rm CH}$  is expressed as the reciprocal of the intrinsic conductance, which is some function f of  $(V_{\rm GS}-V_T)$ . By plotting  $R_T$  as a function of  $1/f(V_{\rm GS}-V_T)$ ,  $V_T$  is used as a fitting parameter until one obtains the linear dependence expressed by (6); the sum  $R_S+R_D$  is thus determined as the intercept with the  $R_T$  axis.

In this paper, this technique will be slightly modified and applied to our HEMTs between 75 K and 400 K.

#### B. Long-Gate HEMT Characterization

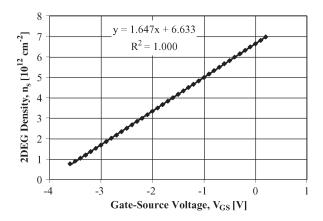

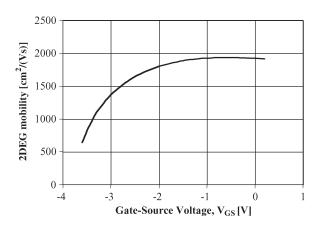

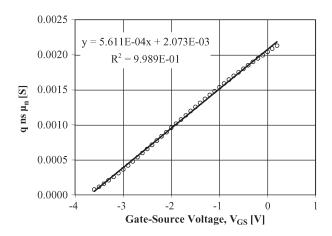

The preliminary condition for the application of this extraction procedure is the existence of an intrinsic channel region, the conductance of which can be expressed by a simple analytical function  $f(V_{\rm GS}-V_T)$ . In the case of our AlGaN/GaN HEMTs, this could be verified by using the measurement of the 2DEG carrier density  $(n_S)$  and mobility  $(\mu_n)$  carried out on long-gate  $(20\times300~\mu{\rm m})$  HEMTs. Fig. 7 shows a linear gate-voltage dependence of  $n_S$  at 300 K. The channel conductance, however, is proportional to the product  $n_S \cdot \mu_n$ . Due to the self-shielding of the 2DEG from Coulomb scattering,

Fig. 7. Measured 2DEG density versus gate–source voltage at 300 K in the long-gate HEMT (20  $\times$  300  $\mu m).$

Fig. 8. Measured 2DEG mobility versus gate–source voltage at 300 K in the long-gate HEMT (20  $\times$  300  $\mu m).$

Fig. 9. Unit-(W/L) channel conductance versus gate-source voltage at 300 K in the long-gate HEMT  $(20\times300~\mu\text{m})$ .

mobility is a nonlinear function of  $V_{\rm GS}$ , as shown in Fig. 8. However, the change in  $n_S$  is many times the change in  $\mu_n$  over the range of  $V_{\rm GS}$  used in the measurements, so that the  $n_S \cdot \mu_n$  product (as shown in Fig. 9) is, to a good approximation, linear.

The best fit line thus obtained is expressed by

$$q \cdot n_S \cdot \mu_n = 5.611 \cdot 10^{-4} \cdot (V_{GS} - V_T)$$

(7)

Fig. 10. Intrinsic channel conductance versus gate–source voltage at 300 K in the long-gate HEMT ( $20 \times 300~\mu\mathrm{m}$ ).  $V_{\mathrm{DS}} = 100~\mathrm{mV}$ .  $R_S + R_D$  is used as a fitting parameter to obtain the linear dependence entailed by (8), resulting in  $R_S + R_D = 18.5~\Omega$ .

where voltages are expressed in volts, q is in coulombs,  $n_S$  is in reciprocal square centimeters, and  $\mu_n$  is in square centimeters per volt second;  $V_T = -3.695$  V. Based on these measurements, the resistance of the intrinsic region can be expressed as

$$R_{\rm CH} = \frac{L_G}{W_G \cdot q \cdot n_S \cdot \mu_n} = \frac{L_G}{W_G \cdot 5.611 \cdot 10^{-4} \cdot (V_{\rm GS} - V_T)}$$

(8)

and by plotting  $R_T$  versus  $1/(V_{\rm GS}-V_T)$ , as previously detailed, the value of  $R_S+R_D$  can be extracted.

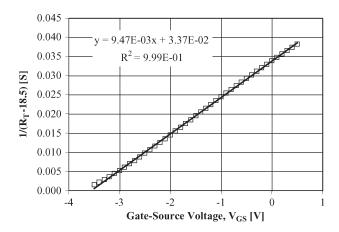

However, this approach [33] suffers from the sensitivity to the uncertainty of  $V_T$  because the intercept  $R_S + R_D$  is much smaller than the low- $V_{\rm GS}$   $R_T$  values in the plot. A better way to extract  $R_S + R_D$  is by plotting the intrinsic conductance

$$\frac{1}{R_{\rm CH}} = \frac{1}{R_T - (R_S + R_D)} \tag{9}$$

as a function of  $V_{\rm GS}$ , using  $R_S+R_D$  as a fitting parameter to obtain the expected linear dependence and extracting  $V_T$  from the intercept with the horizontal axis. This alternative approach is shown in Fig. 10. This procedure gives  $R_S+R_D=16.8\div18.5~\Omega$  and, correspondingly,  $V_T=-3.609\div-3.563~V$  (to be compared with the  $V_T=-3.695~V$  extracted from Fig. 9). The values of  $R_S+R_D$  between 16.8 and 18.5  $\Omega$  yield the same correlation coefficient of the best fit line and are therefore indistinguishable.

The slope of the best fit line of Fig. 10 is [see (8)]

$$k = \frac{W_G}{L_G} \cdot \mu_n \cdot C = \frac{W_G}{L_G} \cdot 5.611 \cdot 10^{-4} \text{ S/V}$$

(10)

where C is the AlGaN layer unit area capacitance. Therefore, from the extracted values of the slope  $(8.87 \cdot 10^{-3} \div 9.47 \cdot 10^{-3} \text{ S/V})$ , for  $W_G = 300~\mu\text{m}$ , we obtain  $L_G = 19.0 \div 17.8~\mu\text{m}$ , which is reasonably in good agreement with the  $20 \cdot \mu\text{m}$  mask value.

Fig. 11. Extracted parasitic resistances versus temperature in the short-gate HEMT (0.9  $\times$  150  $\mu$ m).  $V_{\rm DS}=40$  mV.

TABLE I

TEMPERATURE DEPENDENCE OF THE EXTRACTED PARAMETERS

| Temperature | $R_S + R_D$      | $V_{\mathrm{T}}$     | k                     |

|-------------|------------------|----------------------|-----------------------|

| [K]         | $[\Omega]$       | [V]                  | [S/V]                 |

| 74          | 8.8              | -3.147               | 5.23•10               |

| 104         | 9.1              | -3.185               | 4.21•10-1             |

| 149         | 9.7              | -3.344               | 2.60•10 <sup>-1</sup> |

| 194         | 10.7             | -3.462               | 1.39•10               |

| 255         | 12.6             | -3.583               | 6.13•10-2             |

| 300         | $14.1 \div 14.6$ | $-3.668 \div -3.614$ | 3.66•10-2             |

| 345         | 16.0 ÷ 16.6      | -3.692 ÷ -3.647      | 2.36•10 <sup>-2</sup> |

| 406         | $18.1 \div 18.9$ | -3.683 ÷ -3.648      | 1.43•10-2             |

For  $T \geq 300$  K, the entries for  $R_S + R_D$  and  $V_T$  represent a range of values yielding the same regression coefficient of the best-fit line (see Fig. 10).

Having thus gained confidence in its consistency, the extraction procedure was then applied to the short-gate HEMT.

#### C. Measurement of $R_S + R_D$ on the Short-Gate HEMT

The first problem to consider in moving to the short-gate  $(L_G=0.9~\mu\mathrm{m})$  HEMT is the possible dependence of the mobility on the longitudinal electric field, i.e., on  $V_{\mathrm{DS}}$  (this was not an issue in the long-gate HEMT, where  $V_{\mathrm{DS}}=100~\mathrm{mV}$  was applied to a device with  $L_G=20$ - $\mu\mathrm{m}$  and 10- $\mu\mathrm{m}$ -long ungated regions).

The extraction procedure was therefore applied for different values of  $V_{\rm DS}$ , namely, 10, 40, and 100 mV. For select temperature values,  $R_T$  was also extrapolated for  $V_{\rm DS} \to 0$ . The results (not shown here) indicate the following: 1) There is no significant conductance degradation up to  $V_{\rm DS} = 100$  mV; the average longitudinal electric field for  $V_{\rm DS} = 100$  mV can be estimated to be lower than 1 kV/cm, which is a value corresponding to a marginal mobility decrease at 300 K [39]; and 2) low values, such as  $V_{\rm DS} = 10$  mV, make the extraction procedure troublesome due to the disturbing effect of gate leakage at high temperatures (in spite of its impact being reduced by averaging the drain and source currents);  $V_{\rm DS} = 40$  mV was therefore chosen as the best compromise value for the extraction.

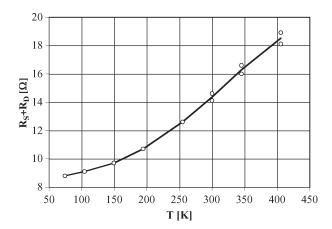

The functional dependence of (8) is verified with good fidelity over the whole temperature range, the 74-K case ( $R^2=0.996$ ) being the worst case observed. Fig. 11 shows the measured parasitic resistances versus temperature.

The complete set of extracted parameters, i.e.,  $R_S + R_D$ ,  $V_T$ , and k [see (10)], is given in Table I.

Fig. 12. Extracted (line) effective mobility versus temperature in the short-gate HEMT ( $0.9 \times 150~\mu m$ ).  $V_{\rm DS} = 40~mV$ . The (diamonds) measured low-field mobility of an ungated ( $40 \times 400~\mu m$ ) HEMT structure is also shown.

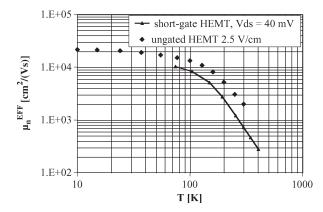

As (10) indicates, the slope k of the best fit line of plots such as Fig. 10 allows the extraction of an effective mobility  $\mu_n^{\rm EFF}$

$$\mu_n^{\text{EFF}} = \frac{k \cdot L_G}{W_G \cdot C} = \frac{k \cdot L_G \cdot t_{\text{AlGaN}}}{W_G \cdot \varepsilon_{\text{AlGaN}}}$$

(11)

where  $\varepsilon_{\text{AlGaN}}$  and  $t_{\text{AlGaN}}$  are the dielectric constant and thickness of the AlGaN layer, respectively. One must speak of an effective mobility because the true 2DEG mobility is a function of  $V_{\rm GS}$  (Fig. 8), whereas (11) returns a single mobility value, which represents an average over the  $V_{\rm GS}$  range used for the  $R_S + R_D$  extraction (e.g.,  $-3.5 \text{ V} < V_{GS} < +0.5 \text{ V}$  at 300 K). With the nominal values  $L_G = 0.9 \ \mu \text{m}$ ,  $W_G = 150 \ \mu \text{m}$ ,  $t_{\rm AlGaN} = 30$  nm, and  $\varepsilon_{\rm AlGaN} = 10.3 \cdot 8.86 \cdot 10^{-14}$  F/cm (the 0.6-nm-thick AlN layer is so thin that it can be neglected in these first-order calculations), one obtains the effective mobilities of Fig. 12 (line). The (diamonds) low-field 2DEG mobility measured on an ungated (40  $\times$  400  $\mu$ m) HEMT is also shown in Fig. 12 for comparison. The calculated  $\mu_n^{\rm EFF}$  shows the same temperature dependence as the measured low-field mobility of the ungated HEMT structure but values that are  $1.5 \div 2.8$  times lower over the 74 ÷ 406 K range. As previously discussed, this difference is unlikely to come from the effect of larger longitudinal field in the short-gate device; at  $V_{\rm DS} = 40$  mV, even a very pessimistic estimate of the average field is around 400 V/cm, which is a value where the mobility degradation is minimal [39]. On the other hand, Fig. 7 shows that at 300 K, the 2DEG mobility of the long-gate HEMT changes by a factor of 3.2 between  $V_{\rm GS} = -3.5$  and +0.5 V; thus, the effect of  $V_{\rm GS}$  can easily be responsible for most of this discrepancy, together with some uncertainty in the parameters, particularly the dielectric constant and, to a smaller extent, the thickness of the AlGaN.

#### D. Modeling Results

It is worth pointing out that the approach we followed, besides allowing the extraction of parasitic resistance values with a clear physical meaning, represents a complete and simple, yet accurate, dc drain-current model for the HEMT biased at low  $V_{\rm DS}$ .

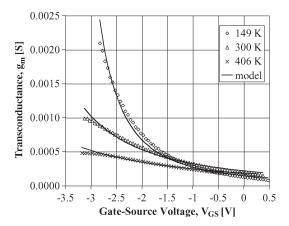

Fig. 13. HEMT transconductance measured at  $V_{\rm DS}=50$  mV and ambient temperatures of (symbols) 149 K, 300 K, and 406 K. The corresponding transconductance curves calculated by using (12) are shown by solid lines.

By using the parameter values listed in Table I, the drain current can be calculated at each temperature as

$$I_D = \frac{V_{\rm DS}}{R_T} = \frac{V_{\rm DS}}{R_S + R_D + R_{\rm CH}} = \frac{V_{\rm DS}}{R_S + R_D + \frac{1}{k(V_{\rm GS} - V_T)}}.$$

(12)

As an example, we used (12) to compute the HEMT transconductance (at  $V_{\rm DS}=50$  mV) as a function of gate-source voltage, at different ambient temperatures, and compared the model with the experimental values, as shown in Fig. 13.

The model accurately describes the temperature and  $V_{\rm GS}$  dependence of the transconductance from about 500 mV above threshold to positive gate voltage, where the lower bound is determined by the singularity of (12) for  $V_{\rm GS} \to V_T$  and the upper bound is determined by the gate leakage current.

Since the temperature dependence of the parameters in Table I is smooth and well behaved, parameter values corresponding to different temperature values can be safely interpolated.

#### E. Summary

The extraction method described in this section yields parameter values that are physically meaningful and consistent with independent measurements; for example, the extracted channel length of the long-gate HEMT (18–19  $\mu m$ ) is in good agreement with the mask length (20  $\mu m$ ). The series resistance of the short-gate (0.9  $\mu m \times 150~\mu m$ ) HEMT showed a significant increase with temperature between 74 K and 406 K, which may be correlated with the observed corresponding decrease in electron mobility. The extracted parameters define a simple analytical model of the HEMT at low drain bias that gives a good match with experimental data over bias and temperature.

#### V. CONCLUSION

This paper has shown two simple dc techniques for measuring the thermal resistance  $R_{\rm TH}$  and the low-drain-bias ohmic parasitic resistance  $R_S+R_D$  of AlGaN/GaN HEMTs. Despite

their simplicity, these methods do not require simplifying assumptions, other than those that can be verified experimentally. The devices under test were characterized over a wide range of ambient temperatures. The main results can be summarized as follows.

- 1) The thermal resistance is a strong function of ambient temperature  $T_A$  and dissipated power  $P_D$  (via the channel temperature  $T_C$ ). Since the channel-to-ambient thermal resistance is dominated by the thick sapphire substrate,  $R_{\rm TH}$  is observed to be a linear function of the average temperature  $(T_A + T_C)/2$ , varying by as much as a factor of eight between 200 K and 500 K.

- 2) The measured values of  $T_C$  can be expressed accurately enough as a function of  $T_A$  and  $P_D$  by a simple formula, and these show a satisfactory agreement (within 10–20 K, depending on the choice of literature data for the thermal conductivity of sapphire) with the numerical simulations (with no fitting involved).

- 3) For the measurement of  $R_S + R_D$ , the HEMT is modeled, at low drain bias, as an intrinsic HEMT obeying the GCA and connected with the external contacts by the bias-independent parasitic resistances. This model has been discussed and validated by using the long-gate and ungated HEMT structures.

- 4)  $R_S + R_D$  approximately doubles for ambient temperatures increasing from 75 K to 400 K, its temperature dependence mirroring that of the low-field 2DEG mobility.

- The extracted (low drain bias) model of the HEMT accurately describes the device dc behavior over temperature and gate voltage.

#### ACKNOWLEDGMENT

R. Menozzi would like to thank Prof. Faraone and the Microelectronics Research Group, The University of Western Australia for the support during his leave.

#### REFERENCES

- [1] A. Chini, D. Buttari, R. Coffie, S. Heikman, S. Keller, and U. Mishra, "12 W/mm power density AlGaN/GaN HEMTs on sapphire substrate," *Electron. Lett.*, vol. 40, no. 1, pp. 73–74, Jan. 2004.

- [2] D. Ducatteau, A. Minko, V. Hoël, E. Morvan, E. Delos, B. Grimbert, H. Lahreche, P. Bove, C. Gaquière, J. C. De Jaeger, and S. Delage, "Output power density of 5.1 W/mm at 18 GHz with an AlGaN/GaN HEMT on Si substrate," *IEEE Electron Device Lett.*, vol. 27, no. 1, pp. 7–9, Jan. 2006.

- [3] R. Menozzi, G. A. Umana-Membreno, B. D. Nener, G. Parish, G. Sozzi, L. Faraone, and U. K. Mishra, "Measurement of the thermal resistance of AlGaN/GaN HEMTs," in *Proc. 31st WOCSDICE*, Venice, Italy, May 20–23, 2007, pp. 93–96.

- [4] R. Menozzi, G. A. Umana-Membreno, B. D. Nener, G. Parish, L. Faraone, and U. K. Mishra, "Measurement of source and drain resistances of AlGaN/GaN HEMTs and their temperature dependence," in *Proc. 31st WOCSDICE*, Venice, Italy, May 20–23, 2007, pp. 229–232.

- [5] A. Koudymov, M. S. Shur, and G. Simin, "Compact model of current collapse in heterostructure field-effect transistors," *IEEE Electron Device Lett.*, vol. 28, no. 5, pp. 332–335, May 2007.

- [6] M. Kuball, S. Rajasingam, A. Sarua, M. J. Uren, T. Martin, B. T. Hughes, K. P. Hilton, and R. S. Balmer, "Measurement of temperature distribution in multifinger AlGaN/GaN heterostructure field-effect transistors using micro-Raman spectroscopy," *Appl. Phys. Lett.*, vol. 82, no. 1, pp. 124– 126, Jan. 2003.

- [7] J. Kim, J. A. Freitas, Jr., J. Mittereder, R. Fitch, B. S. Kang, S. J. Pearton, and F. Ren, "Effective temperature measurements of AlGaN/GaN-based HEMT under various load lines using micro-Raman technique," *Solid State Electron.*, vol. 50, no. 3, pp. 408–411, Mar. 2006.

- [8] I. Ahmad, V. Kasisomayajula, D. Y Song, L. Tian, J. M. Berg, and M. Holtz, "Self-heating in a GaN based heterostructure field effect transistor: Ultraviolet and visible Raman measurements and simulations," *J. Appl. Phys.*, vol. 100, no. 11, p. 113718, Dec. 2006.

- [9] M. Kuball, G. J. Riedel, J. W. Pomeroy, A. Sarua, M. J. Uren, T. Martin, K. P. Hilton, J. O. Maclean, and D. J. Wallis, "Time-resolved temperature measurement of AlGaN/GaN electronic devices using micro-Raman spectroscopy," *IEEE Electron Device Lett.*, vol. 28, no. 2, pp. 86–89, Feb. 2007.

- [10] H. Ji, M. Kuball, A. Sarua, J. Das, W. Ruythooren, M. Germain, and G. Borghs, "Three-dimensional thermal analysis of a flip-chip mounted AlGaN/GaN HFET using confocal micro-Raman spectroscopy," *IEEE Trans. Electron Devices*, vol. 53, no. 10, pp. 2658–2661, Oct. 2006.

- [11] A. Sarua, H. Ji, M. Kuball, M. J. Uren, T. Martin, K. P. Hilton, and R. S. Balmer, "Integrated micro-Raman/infrared thermography probe for monitoring of self-heating in AlGaN/GaN transistor structures," *IEEE Trans. Electron Devices*, vol. 53, no. 10, pp. 2438–2447, Oct. 2006.

- [12] J. Park, M. W. Shin, and C. C. Lee, "Thermal modeling and measurement of AlGaN-GaN HFETs built on sapphire and SiC substrates," *IEEE Trans. Electron Devices*, vol. 51, no. 11, pp. 1753–1759, Nov. 2004.

- [13] P. Regoliosi, A. Reale, A. Di Carlo, P. Romanini, M. Peroni, C. Lanzieri, A. Angelini, M. Pirola, and G. Ghione, "Experimental validation of GaN HEMTs thermal management by using photocurrent measurements," *IEEE Trans. Electron Devices*, vol. 53, no. 2, pp. 182–188, Feb. 2006.

- [14] R. Aubry, J.-C. Jacquet, J. Weaver, O. Durand, P. Dobson, G. Mills, M.-A. di Forte-Poisson, S. Cassette, and S.-L. Delage, "SThM temperature mapping and nonlinear thermal resistance evolution with bias on AlGaN/GaN HEMT devices," *IEEE Trans. Electron Devices*, vol. 54, no. 3, pp. 385–390, Mar. 2007.

- [15] E. Kohn, I. Daumiller, M. Kunze, M. Neuburger, M. Seyboth, T. J. Jenkins, J. S. Sewell, J. Van Norstand, Y. Smorchkova, and U. K. Mishra, "Transient characteristics of GaN-based heterostructure field-effect transistors," *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 2, pp. 634–642, Feb. 2003.

- [16] J. Kuzmík, S. Bychikhin, M. Neuburger, A. Dadgar, A. Krost, E. Kohn, and D. Pogany, "Transient thermal characterization of AlGaN/GaN HEMTs grown on silicon," *IEEE Trans. Electron Devices*, vol. 52, no. 8, pp. 1698–1705, Aug. 2005.

- [17] J. Kuzmík, S. Bychikhin, R. Lossy, H.-J. Würfl, M.-A. di Forte Poisson, J.-P. Teyssier, C. Gaquière, and D. Pogany, "Transient self-heating effects in multifinger AlGaN/GaN HEMTs with metal airbridges," *Solid State Flectron*, vol. 51, no. 6, pp. 969–974. Jun. 2007.

- Electron., vol. 51, no. 6, pp. 969–974, Jun. 2007.

[18] R. Gaska, A. Osinsky, J. W. Yang, and M. S. Shur, "Self-heating in high-power AlGaN-GaN HFETs," *IEEE Electron Device Lett.*, vol. 19, no. 3, pp. 89–91, Mar. 1998.

- [19] J. Kuzmík, P. Javorka, A. Alam, M. Marso, M. Heuken, and P. Kordos, "Determination of channel temperature in AlGaN/GaN HEMTs grown on sapphire and silicon substrates using DC characterization method," *IEEE Trans. Electron Devices*, vol. 49, no. 8, pp. 1496–1498, Aug. 2002.

- [20] R. Menozzi and A. C. Kingswood, "A new technique to measure the thermal resistance of LDMOS transistors," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 3, pp. 515–521, Sep. 2005.

- [21] D. W. DiSanto and C. R. Bolognesi, "Effect of gate-source access region stress on current collapse in AlGaN/GaN HFETs," *Electron. Lett.*, vol. 41, no. 8, pp. 503–504, Apr. 2005.

- [22] T. Palacios, S. Rajan, A. Chakraborty, S. Heikman, S. Keller, S. P. DenBaars, and U. K. Mishra, "Influence of the dynamic access resistance in the  $g_{\rm m}$  and  $f_T$  linearity of AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 52, no. 10, pp. 2117–2123, Oct. 2005.

- [23] R. J. Trew, Y. Liu, G. L. Bilbro, W. Kuang, R. Vetury, and J. B. Shealy, "Nonlinear source resistance in high-voltage microwave AlGaN/GaN HFETs," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 5, pp. 2061–2067, May 2006.

- [24] Nidhi, T. Palacios, A. Chakraborty, S. Keller, and U. K. Mishra, "Study of impact of access resistance on high-frequency performance of AlGaN/GaN HEMTs by measurements at low temperatures," *IEEE Electron Device Lett.*, vol. 27, no. 11, pp. 877–880, Nov. 2006.

- [25] S. Russo and A. Di Carlo, "Influence of the source-gate distance on the AlGaN/GaN HEMT performance," *IEEE Trans. Electron Devices*, vol. 54, no. 5, pp. 1071–1075, May 2007.

- [26] T. Murata, M. Hikita, Y. Hirose, Y. Uemoto, K. Inoue, T. Tanaka, and D. Ueda, "Source resistance reduction of AlGaN–GaN HFETs with novel superlattice cap layer," *IEEE Trans. Electron Devices*, vol. 52, no. 6, pp. 1042–1047, Jun. 2005.

- [27] G. Simin and Z.-J. Yang, "RF-enhanced contacts to wide-bandgap devices," *IEEE Electron Device Lett.*, vol. 28, no. 1, pp. 2–4, Jan. 2007.

- [28] V. Adivarahan, M. Gaevski, A. Koudymov, J. Yang, G. Simin, and M. A. Khan, "Selectively doped high-power AlGaN/InGaN/GaN MOS-DHFET," *IEEE Electron Device Lett.*, vol. 28, no. 3, pp. 192–194, Mar 2007

- [29] C. H. Oxley, "Method for measuring source resistance  $R_{\rm S}$  in saturation region of GaN HEMT device over bias conditions  $(V_{\rm gs}, V_{\rm ds})$ ," *Electron. Lett.*, vol. 40, no. 5, pp. 344–346, Mar. 2004.

- [30] D. W. DiSanto and C. R. Bolognesi, "At-bias extraction of access parasitic resistances in AlGaN/GaN HEMTs: Impact on device linearity and channel electron velocity," *IEEE Trans. Electron Devices*, vol. 53, no. 12, pp. 2914–2919, Dec. 2006.

- [31] L. Yang and S. I. Long, "New method to measure the source and drain resistance of the GaAs MESFET," *IEEE Electron Device Lett.*, vol. EDL-7, no. 2, pp. 75–77, Feb. 1986.

- [32] Y. Zhu, Y. Ishimaru, and M. Shimizu, "Direct determination of source, drain and channel resistances of HEMTs," *Electron. Lett.*, vol. 31, no. 4, pp. 318–320, Feb. 1995.

- [33] H. Fukui, "Determination of the basic device parameters of a GaAs MESFET," Bell Syst. Tech. J., vol. 58, no. 3, pp. 771–797, Mar. 1979.

- [34] A. Christensen, W. A. Doolittle, and S. Graham, "Heat dissipation in highpower GaN electronics on thermally resistive substrates," *IEEE Trans. Electron Devices*, vol. 52, no. 8, pp. 1683–1688, Aug. 2005.

- [35] J. Das, H. Oprins, H. Ji, A. Sarua, W. Ruythooren, J. Derluyn, M. Kuball, M. Germain, and G. Borghs, "Improved thermal performance of AlGaN/GaN HEMTs by an optimized flip-chip design," *IEEE Trans. Electron Devices*, vol. 53, no. 11, pp. 2696–2702, Nov. 2006.

- [36] Y.-R. Wu and J. Singh, "Transient study of self-heating effects in AlGaN/GaN HFETs: Consequence of carrier velocities, temperature, and device performance," J. Appl. Phys., vol. 101, no. 11, p. 113712, Jun. 2007.

- [37] M. Yamada, K. Nambu, Y. Itoh, and K. Yamamoto, "Raman microprobe study on temperature distribution during CW laser heating of silicon on sapphire," J. Appl. Phys., vol. 59, no. 4, pp. 1350–1354, Feb. 1986.

- [38] D. G. Cahill, S.-M. Lee, and T. I. Selinder, "Thermal conductivity of  $\kappa$ -Al<sub>2</sub>O<sub>3</sub> and  $\alpha$ -Al<sub>2</sub>O<sub>3</sub> wear-resistant coatings," *J. Appl. Phys.*, vol. 83, no. 11, pp. 5783–5786, Jun. 1998.

- [39] G. A. Umana-Membreno, G. Parish, B. D. Nener, D. Buttari, S. Keller, and U. K. Mishra, "Magnetotransport in AlGaN/GaN and AlGaN/AlN/GaN heterostructures," *Phys. Stat. Sol.* (B), vol. 244, no. 6, pp. 1877–1881, Jun. 2007.

**Gilberto A. Umana-Membreno** (S'93–M'06) received the B.E. (Hons.) and Ph.D. degrees in electronic engineering from The University of Western Australia, Perth, Australia, in 1997 and 2007, respectively.

He is currently a Senior Research Fellow with the Microelectronics Research Group, School of Electrical, Electronic and Computer Engineering, The University of Western Australia. His main research interests include the characterization and optimization of III-nitride-based semiconductor materials and

devices. His specific research interests include defect spectroscopy, high-energy irradiation-induced effects and their impact on AlGaN/GaN-based transistor reliability, and characterization and modeling of multiple carrier transport in semiconductor materials and devices.

**Brett D. Nener** (S'78–A'93–SM'93) received the B.E. (Hons.) and Ph.D. degrees from The University of Western Australia, Perth, Australia, in 1977 and 1987, respectively, and the M.E.Sc. degree from The University of Tokyo, Tokyo, Japan, in 1980.

He was a Visiting Professor at the U.S. Navy Space and Naval Warfare Center, San Diego, CA, from 1996 to 1998; the University of California, Santa Barbara, in 1997; and the Hong Kong Polytechnical University, Kowloon, Hong Kong, in 2003 and 2007. He is currently an Associate Professor of

electrical and electronic engineering with the School of Electrical, Electronic and Computer Engineering, The University of Western Australia. His research interest is III-nitride electronics.

Giacinta Parish (S'98–M'07) received the B.S. degree in chemistry and the B.E. and M.Eng.Sc. degrees in electronic engineering from The University of Western Australia, Perth, Australia, in 1995, 1995, and 1997, respectively, and the Ph.D. degree in electrical engineering from the University of California, Santa Barbara, in 2001.

She is currently a Senior Lecturer with the School of Electrical, Electronic and Computer Engineering, The University of Western Australia. Her main research interests include the growth and character-

ization of the III-V nitride material system. His specific research interests within this area currently include the development of processing technology, the measurement of minority carrier properties, and the transport and defect studies in electronic devices.

Roberto Menozzi (SM'08) was born in Genova, Italy, in 1963. He received the Laurea degree in electronic engineering (cum laude) from the University of Bologna, Bologna, Italy, in 1987, and the Ph.D. degree in information technology from the University of Parma, Parma, Italy, in 1994.

After serving in the army, he was in a research group with the Department of Electronics, University of Bologna. Since 1990, he has been with the Department of Information Technology, University of Parma, where he became a Research Associate

in 1993, an Associate Professor in 1998, and a Full Professor in 2006. His research activities have covered the study of latch-up in CMOS circuits, IC testing, power diode physics, modeling and characterization, and the electrical and thermal characterization, modeling, and reliability evaluation of compound semiconductor and heterostructure electron devices.

Dr. Menozzi is a committee member of the IEA-JEDEC Reliability of Compound Semiconductors Workshop and the European Symposium on Reliability of Electron Devices. Since 2007, he has been a member of the Editorial Advisory Board of *Microelectronics Reliability*.

**Giovanna Sozzi** received the Laura degree in electronic engineering (with honors) and the Ph.D. degree in information technologies from the University of Parma, Parma, Italy, in 1997 and 2002, respectively.

In 1998, she was with the FIAT, Torino, Italy. Since 2002, she has been an Assistant Professor with the Department of Information Technology, University of Parma. Her major research activities have been concerned with the electrothermal simulation and thermal modeling of high-power diodes and

silicon resistors, and semiconductor devices for microwave applications, with special emphasis on the study of hot carrier, breakdown, trap-related effects, and electrothermal behavior of compound III–V heterostructures such as FETs and HBTs.

**Lorenzo Faraone** (M'79–SM'03) was born in Italy on October 26, 1951. He received the B.E. and Ph.D. degrees from The University of Western Australia (UWA), Perth, Australia, in 1973 and 1979, respectively.

From 1979 to 1980, he was a Research Scientist with Lehigh University, Bethlehem, PA, where he was involved in studies on MOS devices. From 1980 to 1986, he was a Member of the Technical Staff with the RCA Laboratories, David Sarnoff Research Center, Princeton, NJ, working on the very large

scale integration CMOS and nonvolatile memory technologies, and space radiation effects in silicon-on-sapphire MOS integrated circuits. Since 1987, he has been with the School of Electrical, Electronic and Computer Engineering, UWA, where he was the Head of the department/school from 1999 to 2003 and has been a Professor since 1998. He is currently a holder of more than ten U.S. patents, has supervised more than 25 Ph.D. student completions, and has published more than 300 refereed technical papers in journals and conference proceedings. Since his arrival at UWA, his research interests have been in the areas of compound semiconductor materials and devices, and microelectromechanical systems (MEMS). In particular, his research interests include mercury cadmium telluride materials and device technologies for infrared (IR) detector arrays, gallium nitride technology for ultraviolet detectors and high-speed/high-power electronics, and MEMS technologies for tunable optical cavity IR detectors.

Dr. Faraone is a Fellow of the Australian Academy of Technological Sciences and Engineering and of the Australian Academy of Science. He was the recipient of the RCA Laboratories Individual Outstanding Achievement Award in 1983 and 1986 and the John de Laeter Innovation Award in 1997.

**Umesh K. Mishra** (S'80–M'83–SM'90–F'95) received the B.Tech. degree in electrical engineering from the Indian Institute of Technology, Kanpur, India, in 1979, the M.S. degree in electrical engineering from Lehigh University, Bethlehem, PA, in 1980, and the Ph.D. degree in electrical engineering from Cornell University, Ithaca, NY, in 1984.

He has been with various laboratory and academic institutions, including the Hughes Research Laboratories, Malibu, CA; the University of Michigan, Ann Arbor; and the General Electric, Syracuse, NY,

where he has made major contributions to the development of AlInAs/GaInAs HEMTs and HBTs. He is currently a Professor with the Department of Electrical and Computer Engineering and the Associate Dean of the School of Engineering, University of California, Santa Barbara. He has authored or coauthored over 450 papers in technical journals and conferences. He is the holder of nine patents. His current research interests include oxide-based III–V electronics and III–V nitride electronics and optoelectronics.

Dr. Mishra was the recipient of the Presidential Young Investigator Award from the National Science Foundation, the Hyland Patent Award presented by Hughes Aircraft, the Young Scientist Award presented at the International Symposium on GaAs and Related Compounds, and the David Sarnoff Award from the IEEE.