# **Test Pattern Generation for Multiple Stuck-at Faults**

Younès KARKOURI, El Mostapha ABOULHAMID and Eduard CERNY

Groupe de Recherche Interuniversitaire en Architecture des Ordinateurs de Haute Performance et VLSI (GRIAO) Dép. d'informatique et de recherche opérationnelle Université de Montréal, C.P. 6128, Succ. "A" Montréal, (Québec), H3C-3J7, Canada.

#### ABSTRACT

This paper presents a new method to generate test patterns for multiple stuck-at faults in combinational circuits. All multiple faults of all multiplicities are assumed present in the circuit and we do not resort to their explicit enumeration: the target fault is a single component of possibly several multiple faults. The method tries to generate test conditions that propagate the effect of the target fault to primary outputs regardless the effects of other faults which might be present in the circuit. When these conditions are fulfilled, the input vector is a test for the target fault and for all multiple faults containing the target fault as component. The method uses a branch-and-bound technique over the search space and includes several new heuristics to enhance the performance and fault detection capability. Experiments performed on the ISCAS'85 benchmark circuits show that test sets for multiple faults can be generated with high fault coverage and a reasonable increase in cost over test generation for single stuck-at faults.

Keywords: combinational circuits, stuck-at faults, multiple faults, fault analysis, test pattern generation.

Send all communications to: Prof. El Mostapha Aboulhamid at the above address. Phone: (514) 343-6288 Fax: (514) 343-2155 e-mail: aboulhamid@iro.umontreal.ca

# **1. INTRODUCTION**

The increased density of logic in digital circuits has a great impact on the complexity of testing. It is well known that the fault detection problem is NP-Complete [12, 19] even if the set of faults is restricted to the traditional single stuck-at fault model (SSF). This model is commonly used because it represents a large class of potential physical failures [28]. Therefore, a circuit of *n* lines can have up to 2n different SSFs. Due to the high density of modern circuits, a manufacturing defect may result in a fault involving more than one line, and the ability of the SSF model to represent this physical defect decreases considerably. Consequently, fault detection methods may have to deal with the multiple stuck-at fault (MSF) model. Under this model, a circuit of *n* lines can have up to  $3^n$ -1 different MSFs which makes test generation for all of them difficult in most practical cases.

Numerous fault simulation and test pattern generation methods have been developed for SSFs [2]. Experience from actual circuit testing justifies the adoption of the SSF model: First, circuits are assumed to be frequently tested so that at most one defect occurs at a time. Second, when evaluating the detection capability of MSFs by a test set developed for SSFs, a high or even complete multiple fault coverage is achieved for fanout-free circuits [16], irredundant two-level circuits [22], and internal fanout-free circuits [26]. Unfortunately, these results are only applicable to a small subset of circuits since actual designs may be redundant and may contain a large number of internal reconvergent fanouts (the cause of the NP-Completeness of the fault detection problem). These two characteristics create a phenomenon of masking between faults [10] which limits a test set derived for SSFs from detecting MSFs [4, 29].

Hughes [17] reported a simulation study on the coverage of MSFs by different SSF test sets for the 74LS181 4-bit ALU. He found that any complete test set for SSFs detects more that 99.96% of double faults, and many of the test sets detect most of the simulated triple and quadruple faults. Jacob and Biswas [18] derived a prediction algorithm for the lower bound on MSF coverage using SSF test sets. They showed that at least 99.67% of all multiple faults in any circuit are detected by a test set for SSFs if the number of observable outputs is greater or equal to three. Kubiak and Fuchs [23] recently reported a multiple-fault simulation method that determines the fault coverage of MSFs with test sets for SSFs. They confirm the results in [17] , i.e., high fault coverage is achieved for multiple faults of small multiplicities in some benchmark circuits.

We believe that the results reported by the above methods [17, 18, 23] are too high because of the chosen measure of fault coverage. Misleading conclusions can be drawn [8], and as it will be shown later, the definition of the fault coverage as given in [18] can be independent of the circuit size. Also, a complete test set for SSFs is often incomplete for MSFs [17] due to fault masking [11], and the analysis of MSFs for test generation is of great interest for achieving high reliability of VLSI circuits. This has contributed to the development of methods to analyze MSF detection in

combinational circuits for a given test set, either explicitly under certain assumptions [5, 7], or implicitly [1, 9, 30].

Bossen and Hong [5] consider stuck-at faults on checkpoints to represent the set of all MSFs. The approach to test generation establishes global equations for the circuit output functions, while considering all possibilities of faulty conditions. The manipulation of such equations is impractical in the presence of a large number of checkpoint faults or in the presence of redundancy, because masking between faults can occur before reaching primary outputs. Cha [7] considered prime faults, an equivalent class to the MSFs. He established masking relations between undetected potential faults, relative to a given test set. These relations are used to break masking cycles and add new test vectors to the initial set. This approach is not obvious in the presence of a large number of faults and reconvergent fanouts. Abramovici and Breuer [1] developed a method to identify potential faults not detected by a given test set. The method uses concepts similar to the *D*-algorithm [25], but analyzes a set of vectors rather than one vector at a time. However, it does not generate additional tests for undetected MSFs.

Other analysis methods deal with multiple faults implicitly [9, 30] and achieve a high degree of efficiency. An unavoidable pessimism is inherent in these methods because they use a conservative evaluation of the behavior of circuits under the presence of all possible MSFs. Given an initial test set, they determine the set of lines in the circuit that cannot have a particular fault (fault dropping) under the MSF model when the correct output is observed. The results obtained are not invalidated by the presence of undetected or undetectable faults: A fault is dropped only if its effect is not masked by any other fault.

Based on the conservative approach to MSF analysis [30], we present in this paper a faultoriented test pattern generation method (TPG) for MSFs in combinational networks. The method is similar to SSF TPG except that error propagation, line justification and implication consider signal ambiguity introduced by the possible presence of all faults in the circuit. No explicit enumeration of multiple faults is performed; the targeted fault is a fault component of possibly several MSFs. For each target fault, the algorithm tries to identify test conditions, from a combination of values on primary inputs, which propagate the effect of the target fault to primary outputs regardless the effects of other faults which might be present in the circuit. The generated test vector thus guarantees the detection of the target fault, and all MSFs containing this fault are implicitly detected because no fault masking can occur. Furthermore, since the propagation of fault effects is based on necessary conditions, the approach is conservative. It is thus possible that a test for a fault is not found although it exists, but the algorithm will never claim a fault as detected while in reality it is not.

The search vehicle uses techniques similar to the FAN [13] and SOCRATES [27] algorithms. Various heuristics as well as a specific fault collapsing procedure are used to reduce signal ambiguity and to find test conditions that detect a target fault. The algorithm also incorporates the efficient fault analysis method proposed in [30]. The TPG method was applied to the ISCAS'85 benchmark circuits [6], and satisfactory fault coverage was obtained. The experimental results also provided an indication of the cost of deriving good tests for multiple faults, which is about 10 times the cost of deriving tests for SSFs.

The rest of the paper is organized as follows: Section 2 presents the fault, line and gate models under the MSF model. Section 3 contains an overview of the test pattern generator for MSFs. Section 4 presents the MSF test pattern generator and the different tools and heuristics included to guide the search process. Section 5 reports the experimental results. Finally, Section 6 concludes with notes on possible directions for multiple fault test pattern generation.

## **2. THE MODELS**

Dealing with multiple faults requires a particular care when representing and propagating faulty values in the circuit. The computation of the values is conservative in order not to create optimistic conditions for fault detection that may invalidate the obtained results.

# 2.1. The Fault Model

We assume that all faults occur on circuit lines only; we refer to a single fault component of a multiple fault as a *fault*. The gates are fault free and may have up to *m* inputs ( $m \ge 1$ ) for AND, NAND, OR and NOR gates. XOR and XNOR gates have two inputs. A path from line *i* to a primary output is said *normal* if all lines along this path are normal, i.e., are faultless, but the other inputs to gates along this path may be faulty.

Fault collapsing is first performed to retain only one fault per equivalence class, and it is based on the intuitive fact that a fault effect is easier to observe if it is closer to the primary outputs. Thus, the representative fault is the closest one to the primary outputs. For example, a stuck-at-0 (s-a-0) on an input of an AND gate is removed and placed on the output. We do not consider that all inputs of an AND gate are simultaneously stuck-at-1 (s-a-1), because we assume an equivalent s-a-1 fault at the gate output.

The following faults are retained after collapsing:

- s-a-1 (s-a-0) faults on all inputs of AND/NAND (OR/NOR) gates. The multiple fault consisting of s-a-1 (s-a-0) on all inputs is not considered.

- No fault on the input of an inverter and a buffer gate, and on a fanout stem.

- Both s-a-0 and s-a-1 on primary outputs.

- Both s-a-0 and s-a-1 on each input of XOR and XNOR gates. The multiple fault consisting of s-a-1 or s-a-0 on both inputs is not considered.

Furthermore, there is at least one normal path from each faulty site to a primary output.

In a circuit consisting of *n* lines, a multiple fault is represented by a tuple with at most *n* faults and denoted by  $f = (s_i^{\alpha}, s_j^{\beta}, ...), i \neq j$ , where  $s_i^{\alpha}$  represents the *status of line i*:  $\alpha = 0$  for s-a-0,  $\alpha = 1$  for s-a-1. A line *k* not present in the tuple is not faulty in that multiple fault. According to this definition, a multiple fault *f* in the circuit under test partitions the lines into three disjoint categories, *Hidden Lines*, *Faulty Lines* and *Normal Lines*:

- Line *i* is *faulty* if  $s_i^{\alpha} \Box f$ .

- Line *j* is *normal* if  $s_j^{\alpha} \Box f$  and there is a normal path from *j* to a primary output.

- Line *k* is *hidden* if there is no normal path from *k* to a primary output.

During TPG, we assume that the circuit under test contains one multiple fault consisting of a combination faults that has not yet been dropped (detected). The effective values (real values) on hidden lines are unknown, because they are unobservable due to the multiple fault, and there is no algorithmic way to determine these values (Normal Path Theorem in [1]). We assume that *these lines carry fault free values*. As will be seen in Section 4.3, this assumption does not invalidate the generated tests.

#### 2.2. The Line Model

Various algebras have been used to describe the behavior of the fault free and the faulty circuit using D symbols [25]. We represent the fault free value of a line i by a normal value  $n_i = 0, 1$  or X (unspecified). Each line may carry a value that is different from the normal one due to propagated fault effects. A fault effect is potential (may or may not be present), since all the faults can be potentially present in the circuit.

We represent the fault effect on a line *i* using a *propagation bit*  $p_i = 0$ , 1, or X.  $p_i = 1$  if line *i* propagates a potential fault effect different from its normal value.  $p_i = 0$  if no fault effect can propagate to line *i* : Line *i* is carrying its normal value only, or is hidden or is faulty. Initially, all lines have unspecified normal values  $(n_i = X)$  and  $p_i = X$  if under the current value assignment, the lines driving i still have unspecified normal values. In the rest of the paper, the notation  $n_i / p_i$  will be used to represent the value assignment to line *i*. For example, a line carrying the value 1/1 has a normal value of 1 and may be propagating a fault effect (which can change its value to 0). Table I summarizes the possible values of a line *i*.

| LINE VALUE INTERPRETATION |            |        |  |  |  |  |  |

|---------------------------|------------|--------|--|--|--|--|--|

| $n_i/p_i$                 | Fault free | Faulty |  |  |  |  |  |

| 0 / 0                     | 0          | 0      |  |  |  |  |  |

| 0 / 1                     | 0          | 0 or 1 |  |  |  |  |  |

| 0 / X                     | 0          | Х      |  |  |  |  |  |

| 1 / 0                     | 1          | 1      |  |  |  |  |  |

| 1 / 1                     | 1          | 1 or 0 |  |  |  |  |  |

| 1 / X                     | 1          | Х      |  |  |  |  |  |

| X / 0                     | Х          | Х      |  |  |  |  |  |

| X / 1                     | Х          | Х      |  |  |  |  |  |

| X / X                     | Х          | Х      |  |  |  |  |  |

|        | TABLE I       |        |

|--------|---------------|--------|

| LINE V | ALUE INTERPRE | TATION |

|        |               |        |

The faulty value of a line is assumed unspecified when its normal value or propagation is equal to X. Primary inputs are directly controlled from the circuit environment, hence no fault effects can propagate to them.

Each line *i* is associated with its status  $s_i^{\alpha}$  which can be viewed as an atomic proposition:

- $s_i^{\alpha} = 0$  if the fault s-a- $\alpha$  is not on line *i* (e.g., has been dropped),

- $s_i \alpha = 1$  if the fault s-a- $\alpha$  is potentially present on line i.

# 2.3. The Gate Model

The gate model computes the value on the output of a gate given the status and the values of its inputs. It thus determines the normal value and the propagation of fault effects arising from a combination of fault effects and potential stuck-at faults on its inputs. Since fault effects are assumed independent, the evaluation is conservative and includes the real behavior of the circuit.

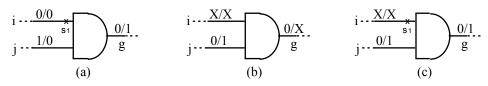

Example 1: Fig. 1 shows the computation of the value and the propagation bit for an AND gate for different input situations. In Fig. 1a, given the input values i = 0/0 and j = 1/0, the normal value on the gate output line g is  $n_g = 0$ . If line g is normal then it may propagate a fault effect issued from the combination of the fault  $s_i^1$  and the normal value  $n_i = 1$ . Hence, g carries the value 0/1.

Fig. 1. Fault effect propagation.

In Fig. 1b, we assume that both lines *i* and *j* are normal and line *j* may carry a fault effect  $(p_j = 1)$ . The propagation bit at the output *g* remains unspecified because it depends on  $n_i$  and  $p_i$ . This not the case in Fig. 1c where the fault effect on *j* may be combined with the fault  $s_i^1$  to propagate a fault effect on *g* independently of  $n_i$  and  $p_i$ . Notice that a definite value is assigned to the output only if it is guaranteed regardless the interpretation of X on the inputs.

This conservative computation of propagated values is performed using equations similar to those reported for 2-valued logic in fault analysis [30]. For TPG, these equations are extended to handle 3-valued logic for both the normal values and the propagation bits. Let a = 0,X designate that the variable *a* can take the value 0 or X (a  $\square$  {0, X}), then the equation to determine the propagation bit  $p_{out}$  on the output out of a *m*-input AND gate is the following<sup>†</sup> (*P* and *Q* are predicates; *P* is true if  $p_{out}$  can be equal to 0; *Q* is true if  $p_{out}$  can be equal to 1):

•

$$P = [\exists i, (n_i=0, X \land p_i=0, X \land s_i^1=0)] \lor [\forall i, (n_i=0, X \land p_i=0, X)] \lor [n_{out}=1 \land (\forall i, p_i=0, X)]$$

•

$$Q = [(\exists i, n_i=1, X \lor p_i=1, X) \land (\forall i, n_i=0, X \Rightarrow (p_i=1, X \lor s_i^1=1))] \lor [n_{out}=1 \land (\exists i, p_i=1, X)]$$

The value of  $p_{out}$  is then assigned as follows:

$$p_{out} = 0 \Leftrightarrow (P \land \overline{Q}); \ p_{out} = 1 \Leftrightarrow (Q \land \overline{P}); \ p_{out} = X \Leftrightarrow (P \land Q)$$

For example, no fault effect propagates to the output of the AND gate if there exists a normal input having a normal value of 0 with no possible fault effect; this input disables the propagation of any fault effect to the output. Also, the gate will not propagate a fault effect if all its inputs have a normal value of 0 and none of them is carrying a fault effect. The fault effect on the output of the gate is considered unspecified if it can be equal to 0 or 1 (i.e., P = Q = true). The equations for NAND, OR, NOR, XOR and XNOR gates are in Appendix Ia. For a fanout stem, the propagation bit is broadcast as is to all its branches. For inverters and buffers, the propagation bit is also transmitted as is to the output, because there are no faults on their inputs. As discussed in Section 4.1, the necessary conditions for sensitizing a gate to the effect of a target fault rely on assigning values (0 or 1 depending on the gate type) to its unspecified inputs that are not reachable from the target fault site.

<sup>&</sup>lt;sup>†</sup> " $\forall i$ " in all equations represents "for each input *i* of the gate, *i* = 1, ..., *m*".

# **3. SYSTEM OVERVIEW**

We consider that the circuit under test may contain a multiple fault consisting of a combination of faults remaining after collapsing. This multiple fault partitions the lines into hidden, faulty and normal lines (recall that hidden lines are assumed fault free). The goal of TPG is to generate a test set that determines as many lines as possible that cannot be faulty when the fault free response is observed. To do so, the algorithm identifies for each target fault the test conditions which allow to declare the respective line necessarily not carrying that fault. The line may in reality be either hidden or normal.

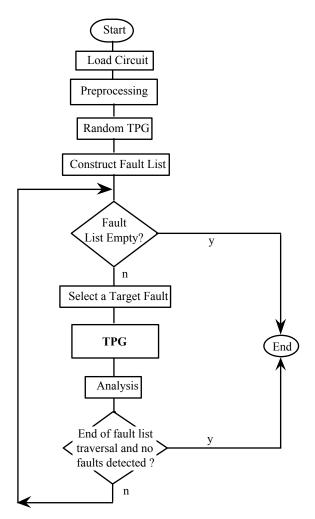

A flowchart of the TPG system is in Fig. 2. First, a preprocessing phase is performed to analyze the circuit structure, required for incorporating heuristics that guide the search part of the algorithm, including the values of controllability/observability measures [3, 15]. As commonly used in TPG systems, a random test pattern generation (RTPG) may be performed first. A non negligible number of faults are usually dropped during this phase, which accelerates the subsequent deterministic TPG. RTPG is stopped when either a maximum number of vectors has been reached or the last *n* consecutive vectors do not detect any additional fault. This phase is performed at reasonable cost since the multiple fault analyzer can manipulate 32 vectors simultaneously [20].

A target fault is arbitrarily selected from the list of remaining faults. The TPG gradually determines a set of objectives that are necessary for activating the target fault and for propagating its effect to a primary output, while taking into account the potential effects of the other faults still in the fault list. To meet these objectives in terms of a combination of values on the primary inputs, the TPG uses similar procedure as in FAN [13] and SOCRATES [27], but using our models (Section 2):

- An *implication procedure* determines as many line values as possible that are uniquely implied. Both local [13] and global implications [27] (learned during the preprocessing phase) are performed.

- A multiple backtrace procedure concurrently traces more than one path to satisfy an objective.

- A *unique sensitization procedure* is applied whenever the *S*-frontier (which is similar to the *D*-frontier in SSF TPG) consists of a single gate.

- The backtrace is stopped at *head lines*, since their justification can be done without conflicts even under the MSF model, and is then completed in the final stage of the TPG process.

Fig. 2. Flowchart of the test pattern generator.

The test conditions which activate the target fault and propagate its effect to a primary output, are characterized as follows (the justification of these conditions is presented in Section 4.3):

- C1: The effect of the target fault cannot be masked by any other fault(s), and

- C2: The effect of the target fault was propagated through a normal path, or

- C2': The effect of the target fault was propagated through all paths to primary outputs if no normal path yet exists to a primary output.

Condition C1 is maintained during the propagation of the target fault effect due to the conservative evaluation of line values (Section 2). Conditions C2 and C2' are verified during a backward deduction phase which is engaged each time the target fault effect reaches a primary output. If fulfilled, the target fault is declared as detected and is dropped from the fault list. An alternative equivalent interpretation of the detection conditions is as follows: The effect of the target fault is observable on a primary output through a fault free path (condition C2), or is not observable under any input vector because its site is hidden by another MSF (condition C2'). Because of C1, the test vector detects all multiple faults containing the target fault since the conservative evaluation guarantees that no fault masking occurs.

Multiple fault analysis is then applied, using the generated test vector with random values assigned to unspecified primary inputs. This step is similar to performing fault simulation after generating a test for a fault under the SSF model, and it allows to drop additional faults. The analysis algorithms are implemented using bit strings allowing to analyze up to 32 test vectors simultaneously [20], which results in a very efficient implementation.

Fault dropping permits gradual identification of normal paths (using the backward deduction phase) and reduces the ambiguity caused by faults when the next target is selected for TPG. Fault masking relations are not retained during TPG; therefore, each time the traversal of the target fault list is completed with some of the faults detected, it is reprocessed with the aim to detect faults that were possibly masked when targeted in the previous list traversal.

Since our TPG uses conservative value propagation and bases fault detection on necessary conditions only, the method is not a complete algorithm in that it may not always find a test for a fault at a given step in the TPG, although it may find it later when other faults will have been detected and dropped from the circuit. Given enough time to generate test patterns, the procedure will not find a test only when circular masking between faults exists. But then such a test may not exist at all if all the faults of the masking relation are present. Moreover, the method is also not complete for generating tests for all detectable multiple faults: There are situations where a multiple fault consisting of undetected faults is detectable, but the algorithm will not discover it because it is not explicitly enumerated and the individual faults are not detectable in the presence of the other faults.

# 4. MULTIPLE FAULT TPG

The TPG assumes that the circuit may contain a multiple fault, hence it takes into account all possible values of the status of the lines when generating a test for a given target fault. Consequently, the concepts of SSF TPG must be generalized to accommodate this factor.

# 4.1. Multiple Fault TPG Concepts

When the effect of the target fault is propagated to a primary output under the SSF model, the circuit lines are divided into two classes: those carrying the fault effect (*D*-drive), and those set to 0 or 1 to propagate the fault effect. With our MSF model, no distinction is made between these two classes, since fault effects may be issued from either the target and/or other faults. We thus introduce the concept of *sensibility* for implementing an equivalent notion to the *D*-drive and for distinguishing the effect of the target fault from all the other fault effects.

*Definition* 1: A line *j* is *sensible* to a target fault  $s_i^{\alpha}$  if under the current value assignments to lines, line *j* propagates the effect of  $s_i^{\alpha}$  (i.e.,  $p_j = 1$ ). The sensibility of line *j* to  $s_i^{\alpha}$  is denoted by the attribute  $w_j = 1$ .  $w_j = 0$  indicates that any fault effect on line *j* is not due to the target fault.

According to the above definition,  $s_i^{\alpha} = 1 \Box p_j = 1$ , but the fault effect on line *j* could also be due to other faults in addition to  $s_i^{\alpha}$ . Sensibility is propagated through the circuit similarly as *D* propagation for SSF TPG. A line *i* is sensible to its own fault  $s_i^{\alpha}$  whenever  $n_i = \overline{\alpha}$ . The propagation of sensibility

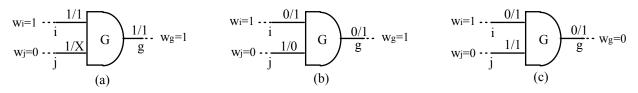

through gates depends on the gate types, the polarity of the input line(s) sensible to the target fault, and the normal values and the propagation bits of the inputs not reachable from the fault site (called *non-sensible* inputs in the rest of the paper). Fig. 3 illustrates three examples of propagation of sensibility through an AND gate, assuming that input *i* is sensible to the target fault (i.e.,  $w_i = 1$ ).

Fig. 3. Sensibility propagation through an AND gate.

In Fig. 3a, the output g is sensible to the target fault ( $w_g = 1$ ) because either line j propagates no fault effect ( $p_j = 0$ ) and the fault effect on g is due to  $p_i = 1$  (since  $n_j = 1$ ), or both i and j propagate a fault effect ( $p_j = 1$ ) in which case  $p_g = 1$  indicates that the effect of the target fault cannot be distinguished from another effect, but it is certainly present. If the sensible input has a normal value 0, then the gate output is sensible if every non-sensible input j has  $n_j = 1$  and  $p_j = 0$ . In Fig. 3b,  $p_g = 1$  is due to the effect of the target fault only, hence  $w_g = 1$ . On the other hand, if input j may carry a fault effect ( $p_j = 1$ ) (Fig. 3c), it may mask the effect of the target fault and even if  $p_g = 1$  (because of the conservative propagation of fault effects), the gate output is not declared sensible ( $w_g = 0$ ).

Sensibility to the target fault is propagated through the circuit using specific equations for each gate type (Appendix Ib). For example, for an AND gate with output *g*, the sensibility propagation is:

$$w_g = 1 \Leftrightarrow (\exists i, w_i = 1) \land [(\forall i, n_i = 1) \lor (\forall i, (n_i = 0 \land w_i = 1) \lor (w_i = 0 \land n_i = 1 \land p_i = 0))]$$

During TPG for SSFs, the propagation of the effect of the target fault consists of selecting one gate from the *D*-frontier and assigning values to its unspecified non-sensible inputs so that the gate output propagates a D or  $\overline{D}$  value. Similarly, in the case of MSFs the *S*-frontier is a set of all gates having one or more inputs sensible to the target fault, and the non-sensible ones having an unspecified normal value and/or propagation bit such that the target fault effect is not masked. For example, the inclusion of an AND gate G in the S-frontier is determined using the following expression:

$$G \Box S \text{-frontier} \Box$$

$$(\exists i, w_i=1) \land [[(\forall i, n_i=1, X) \land (\exists i, n_i=X)] \lor [(\forall i, ((n_i=0 \land w_i=1) \lor (w_i=0 \land n_i=1, X \land p_i=0, X))) \land (\exists i, n_i=X \lor p_i=X)]].$$

To illustrate the preceding concepts, consider the circuit in Fig. 1. Assuming that line *j* in Figures 1b and 1c is sensible to the target fault, the AND gate is in the *S*-frontier since its output can become sensible if 1/0 is assigned to line *i*. The required normal value on each non-sensible input *j* of the gate is always 1 (non-controlling value), and the propagation bit  $p_j$  on this input must be 0 whenever the sensible input has the normal value 0, while  $p_j$  is *X* if the sensible input has a normal value of 1. In the latter case, the presence or absence of fault effects on the non-sensible inputs does not affect the sensibility of the gate output to the target fault. Note that a gate is not included in the *S*-frontier if two of its sensible inputs have different normal value polarities. This is captured in the above inclusion expression of a gate in the *S*-frontier (see also Appendix Ic).

We summarize in Table II the required values on the non-sensible inputs in order to propagate the target fault effect through different types of gates. For a XOR or a XNOR gate, if the non-sensible input *j* has both potential  $s_j^0$  and  $s_j^1$ , the gate is not included in the *S*-frontier. The assignment to a nonsensible input *j* of a XOR or a XNOR gate in Table II assumes that either  $s_j^0$  or  $s_j^1$  was dropped in an earlier iteration of TPG, hence the assigned normal value  $n_j$  depends on the remaining fault. If both were dropped, then  $n_j$  is chosen depending on the value of the controllability measure of line *j* (Section 4.4).

| REQUIREMENTS FOR THE PROPAGATION THROUGH A GATE IN THE $S$ -frontier |                            |                                                  |                                  |  |  |  |  |  |

|----------------------------------------------------------------------|----------------------------|--------------------------------------------------|----------------------------------|--|--|--|--|--|

| Gate types                                                           | Sensible<br>input value(s) | Requirements on<br>non-sensible<br>input(s)      | Output<br>Assignment             |  |  |  |  |  |

| AND<br>(NAND)                                                        | 1 / 1                      | 1 / X                                            | 1 / 1 (0 / 1)                    |  |  |  |  |  |

|                                                                      | 0 / 1                      | 1 / 0                                            | 0/1 (1/1)                        |  |  |  |  |  |

| OR (NOR)                                                             | 0 / 1                      | 0 / X                                            | 0/1 (1/1)                        |  |  |  |  |  |

|                                                                      | 1 / 1                      | 0 / 0                                            | 1 / 1 (0 / 1)                    |  |  |  |  |  |

| XOR<br>(XNOR)                                                        | 0 / 1 or 1 / 1             | $1 / 0$ if $s_j^0 = 0$<br>$0 / 0$ if $s_i^1 = 0$ | 1 / 1 or 0 / 1<br>0 / 1 or 1 / 1 |  |  |  |  |  |

|                                                                      |                            | i i i i i i i i i i i i i i i i i i i            |                                  |  |  |  |  |  |

TABLE II

Requirements for the Propagation Through a Gate in the S-frontier

The backward justification of values assigned to the non-sensible inputs is performed by backward implication procedure in the same manner as in TPG algorithms for SSFs, except that it again takes into account the propagation bits when required to be 0.

# 4.2. Implication and Unique Sensitization

The assignments which propagate the effect of the target fault through the circuit are justified by a search over possible line values  $(n_i / p_i)$  that have a good likelihood in satisfying them. This search explores the space of possible solutions using a branch-and-bound technique [14]. The convergence to a solution is improved using heuristics and techniques, described as implication and unique sensitization, that are similar to those in FAN [13] and SOCRATES [27].

# • Implication

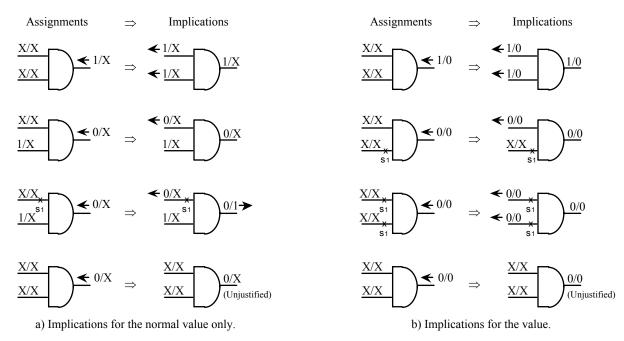

The role of the implication procedure is to identify as many line values that are uniquely determined as possible, to keep track of lines sensible to the target fault, to update the *S*-frontier, and to check for the consistency of value assignments. Line values are determined by forward and backward implications in the circuit. Forward implication consists of a simple computation of line values using the gate model defined in Section 2.3. Backward implication determines, when possible, the values on gate inputs that uniquely justify the value on the output of the gate. Both normal value and propagation bit values are determined based on the function and the propagation bit equation of the gate (Appendix Ia). The input values are left unspecified when there is no unique value assignments. Such inputs are later processed in the multiple backtrace procedure (Section 4.4). Fig. 4a shows unique normal value assignments when the propagation bit on the output of an AND gate is not specified.

Fig. 4. Uniquely determined input normal values of an AND gate.

When the propagation bit on the output of an AND gate is specified to be 0, the only two situations which are uniquely determined are:

(1) If s-a-1 faults on all its input are still possible, then all the inputs are assigned 0/0. (Recall that these s-a-1 faults cannot occur simultaneously).

(2) If there exists exactly one input *i* such that  $s_i^1 = 0$ , then this is the unique input that, when set to 0/0, disables the propagation of any fault effect to the gate output.

Fig. 4b shows unique input assignments when the propagation bit on the output of an AND gate is 0. For other gate types, the unique assignments are easily derived from their propagation bit equations (Appendix Ia).

In FAN, the backward implication procedure makes unique assignments locally from the output of each gate. In addition, global implications learned during the preprocessing phase were introduced in SOCRATES [27]. The global implications help to reduce the number of backtracks and permit early recognition of conflicts and redundancies. In our case, only normal values are determined, and thus the learning procedure is the same as in [27]. Propagation bits are not considered since invalid global implications may result in the presence of a multiple fault; they are specified by local backward implications depending on the remaining faults on the gate inputs (Fig. 4).

Before assigning a value to a line, the implication procedure checks for the consistency of the assignment. According to our line model, a conflict occurs when either a value  $\alpha$  is to be assigned to a line *i* having  $n_i = \overline{\alpha}$ , or when 0 is to be assigned to  $p_i$  which is already equal to 1. In such cases, the implication procedure signals inconsistency and is aborted.

# • Unique Sensitization

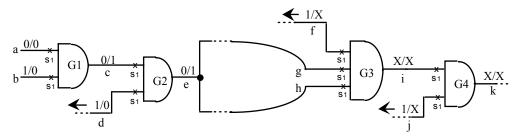

In FAN [13], when the *D*-frontier consists of a single gate, a unique sensitization procedure is used to find immediately as many unique assignments of line values as possible. These assignments decrease the number of choices and thus the number of backtracks. Fig. 5 shows an example of the application of the unique sensitization procedure using our models, when the *S*-frontier consists of a single gate.

Fig. 5. Application of the unique sensitization.

The target fault is  $s_a^1$  and the input *a* is assigned the value 0/0. The only gate in the S-frontier is G1, and every path from G1 to primary outputs passes through *c-e* and *i-k*. In order to propagate the effect of  $s_a^1$ , we have to sensitize paths *c*-*e* and *i*-*k*. To do so, non-sensible inputs of gates G1, G2, G3 and G4 have to be assigned the non-controlling normal value 1 (from Table II). Justifying a propagation bit set to 0 on a line is more difficult due to remaining faults, potentially requiring many more assignments (as illustrated in Fig. 4b). Propagation bits on these inputs are specified only if the polarity of all the paths from the fault site to the corresponding gates is the same (i.e., even or odd but not both), in order to propagate the target fault effect (to avoid its masking). Hence, we assign 1/0 to lines b and d since the polarity of the path from line a to G1 and G2 is even. For gate G3, assuming that the polarity of all the paths from a to g and to h can be either even or odd, that is, g and h may be assigned 1/1 or 0/1. Therefore, 1/X is assigned to f and has to be justified backward. The propagation bit on f will be set to 0 only if a subsequent forward implication assigns 0/1 to g and h in order to sensitize G3 to the target fault.  $p_f = 0$  has to be subsequently justified by backward implication. But, if the forward implication assigns 1/1 to g and to h, there is no need for specifying  $p_f$ , because the value 1/X on line f is sufficient to sensitize G3 to the target fault. The case for line *j* is similar. To conclude the example, the unique sensitization procedure assigns 1/0 to b and d, and 1/X to f and j and then would justify them, if possible, by backward implication.

### 4.3. Fault Detection

The lines of the circuit are hidden, faulty or normal. The goal of our TPG is to generate a test set that determines the lines that cannot be faulty (hidden or not) when the fault free response is observed. The algorithm uses the sensibility concept to propagate the effect of the target fault through the circuit, but cannot declare this fault as detected when a primary output is reached and is sensible (as done under the SSF model when a primary output is assigned a D or  $\overline{D}$  and all justifications of line values succeed). The generated test may be invalid in the presence of another fault that masks the effect of the target fault on the sensitized path only. Thus, we must establish additional test conditions

under which the target fault can be dropped (i.e., detected) assuming that the fault free response is observed. These conditions are:

- *C*1: The target fault is sensitized to a primary output through a normal path and thus the fault cannot be present if the fault free response is observed on this output.

- *C*2: No normal path has been identified from the target fault site, but all the paths to primary outputs are sensitized to the target fault. In this case, if the fault free response is observed on these primary outputs, the target fault site is either normal or hidden. Thus in both states, the target fault can be dropped.

To verify these conditions during the propagation of a target fault effect through the circuit, the algorithm must maintain a list of all the paths along which the target fault can propagate (normal paths) or must be propagated (not normal paths). This may result in an inefficient implementation since a list traversal has to be performed at each step. To remedy this inefficiency, the algorithm does not maintain such a list, but instead performs a *backward deduction phase* each time the target fault effect is propagated to a primary output and all justifications are successful. This phase verifies the presence of the test conditions that allow to drop the target fault, and at the same time it drops other faults along sensitized paths for which the test conditions *C*1 and *C*2 are fulfilled. In TPG for SSFs, this corresponds to dropping all activated faults along sensitized paths. Note that this phase is similar to the backward deduction used in fault analysis [30]. It is a linear time algorithm that performs backward sweeps from primary outputs having specified value toward primary inputs. It assumes that fault free response is observed on the primary outputs and drops fault effects on them by resetting to 0 their propagation bits. Then, for each gate feeding these outputs, it deduces the possible values that are actually carried by their inputs: The deductions may result in dropping fault effects and faults that are not masked and thus cannot be present or their sites are hidden.

A fault effect on a line is dropped by resetting to 0 its propagation bit, i.e., the line carries fault free value only. When the propagation bit on a line is reset to 0, backward deduction continues further into the driving network. Backward deduction is not performed through any gate having propagation bit on its output different from 0. Depending on the type of the gates, the propagation bits and the status of the inputs are deduced using the following deduction lemmas.

*Lemma 1:* If the propagation bit  $p_g$  on the output g of an AND/NAND gate is reset to 0, then the following are sufficient conditions for dropping the fault effect and the fault on each input *i*:

- Drop the fault effect:

$$p_i = 0 \square p_i = 1 \square [(n_i = 0 \square (\forall j \neq i, n_j = 1 \square p_j = 0)) \Delta (\forall j, n_j = 1)]$$

- Drop the fault:  $s_i^1 = 0 \square n_i = 0 \square (\forall j \neq i, n_j = 1 \square p_j = 0)$

- *Lemma 2:* If the propagation bit  $p_g$  on the output g of an OR/NOR gate is reset to 0, then the following are sufficient conditions for dropping the fault effect and the fault on each input *i*:

- Drop the fault effect:  $p_i = 0 \square p_i = 1 \square [(n_i = 1 \square (\forall j \neq i, n_j = 0 \square p_i = 0)) \Delta (\forall j, n_j = 0)]$

- Drop the fault:  $s_i^0 = 0 \square n_i = 1 \square (\forall j \neq i, n_j = 0 \square p_j = 0)$

- *Lemma 3:* If the propagation bit  $p_g$  on the output g of an XOR/XNOR gate is reset to 0, then the following are sufficient conditions for dropping the fault effect and the fault on each input *i*:

- Drop the fault effect:  $p_i = 0 \square p_i = 1 \square p_j = 0 \square [(n_j = 0 \square s_i^{-1} = 0) \Delta (n_j = 1 \square s_i^{-0} = 0)], j \neq i$

- Drop the s-a-1 fault:  $s_i^{1} = 0 \square n_i = 0 \square p_i = 0, j \neq i$

- Drop the s-a-0 fault:  $s_i^0 = 0 \square n_i = 1 \square p_i = 0, j \neq i$

Lemma 4: Let s be a fanout stem. Sufficient conditions for resetting the propagation bit  $p_s$  to 0 are:

- $\forall$  fanout branch *b* of *s*, *p*<sub>b</sub>=0, <u>or</u>

- $\exists$  fanout branch *b* of *s* such that  $p_b=0$  and *b* is normal.

The proofs of these lemmas are similar to those given for the analysis method [21, 30]. For inverters and buffers, if the propagation bit on the output is reset to zero, it is also reset to zero on the input.

A line *i* is declared normal if  $s_i^{\ 1} = 0$  and  $s_i^{\ 0} = 0$  (i.e., both faults were dropped) and there exists a normal path from *i* to a primary output (i.e., all faults along this path have also been dropped). The backward deduction phase determines such normal paths while backtracing in the circuit. The following example illustrates some of the possible deductions during the backward phase.

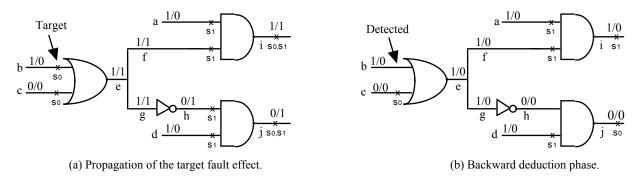

*Example* 2: Consider the circuit in Fig. 6 containing faults  $s_a^1$ ,  $s_b^0$ ,  $s_c^0$ ,  $s_d^1$ ,  $s_f^1$ ,  $s_h^1$ ,  $s_i^1$ ,  $s_j^0$ ,  $s_j^1$  and  $s_j^0$ . Any combination of these faults constitutes a multiple fault whenever there is a normal path from each of its components to at least one primary output and excluding simultaneous faults on inputs of the same gate. Let the target fault be  $s_b^0$ . The fault is activated (Fig. 6a) by assigning normal value 1 to input *b*, and  $p_b = 0$  since it is a primary input. The assignment c = 0/0 propagates the target fault effect to line *e*. Since there is no normal path from the fanout stem *e* to a primary output, the effect of the target fault must be propagated through all its branches. By setting *a* and *d* to 1/0, the outputs *i* and *j* are reached. At this stage, lines *e*, *f*, *g*, *h*, *i* and *j* are all sensible to  $s_b^0$ .

Fig. 6. Fault detection example.

The backward deduction is now executed (Fig. 6b). First, it assumes that the fault free response is observed on the primary outputs *i* and *j*, i.e.,  $p_i = p_j = 0$ . Faults  $s_i^0$  and  $s_j^1$  are detected and dropped. Backtracing on each of the AND gates feeding *i* and *j*, the propagation bits on *f* and *h* are reset to 0 according to lemma 1, i.e., these effects will be observable on *i* and *j*, unless they are hidden by  $s_i^1$  and  $s_j^0$ , respectively. The fault  $s_h^1$  is detected based on the same deductions. The fault effect on stem *e* is also reset to 0 since it was reset to 0 on all its fanout branches (*f* and *g*). Based on Lemma 2 (of an OR gate), the fault effect on *e* is due to  $s_b^0$  only, and since  $p_e = 0$  then the fault  $s_b^0$  is detected. The vector *t* = (abcd) = (1101) is thus a test for the faults  $s_b^0$ ,  $s_h^1$ ,  $s_i^0$  and  $s_j^1$ . In fact, implicitly, *t* is a test for all multiple faults containing one or more of these faults as a member. For example, the set of multiple faults containing  $s_b^0$  and detected by *t* is  $F = \{(s_b^0), (s_b^0, s_a^1), (s_b^0, s_f^1), (s_b^0, s_i^0), (s_b^0, s_d^1), (s_b^0, s$   $s_{h}^{1}, (s_{b}^{0}, s_{j}^{0}), (s_{b}^{0}, s_{j}^{1}), (s_{b}^{0}, s_{a}^{1}, s_{h}^{1}), (s_{b}^{0}, s_{a}^{1}, s_{d}^{1}), (s_{b}^{0}, s_{f}^{1}, s_{d}^{1}), (s_{b}^{0}, s_{i}^{0}, s_{d}^{1}), (s_{b}^{0}, s_{i}^{1}, s_{d}^{1}), (s_{b}^{0}, s_{j}^{1}, s_{d}^{1}), (s_{b}^{0}, s_{d}^{1}, s_$

# 4.4. TPG algorithm

The key concepts introduced in the previous sections are the propagation of sensibility  $(w_i)$ , the propagation of fault effects  $(p_i)$ , and the test conditions for fault detection. These concepts and the underlying fault, line and gate models can be incorporated in any TPG algorithm for SSFs to adapt it for multiple faults. In our case, we use a branch-and-bound technique to explore the solution space using a binary decision tree [14] with heuristics techniques to improve the performance. Fig. 7 illustrates the overall TPG procedure, based on a recursive version of FAN [2]. The procedure assumes that the target fault is supplied by the caller procedure. The Boolean variable *Test\_Found* is true if the target fault is detected; the test vector is returned when the values on the head lines are justified by the procedure *Justify\_Head\_Lines()*.

| begin<br>if Imply_and_Check() = FAILURE then return( FAILURE ); /* 1 */<br>if (error at PO and all bound lines are justified) then<br>begin<br>Justify_Head_Lines();<br>Backward_Deduction( Target_Fault ); /* 2 */<br>if Test_Found then begin<br>Analysis() ; /* 3 */<br>return( SUCCESS );<br>end;<br>end;<br>if (not error at PO and S-frontier = Ø) then return( FAILURE );<br>Add every unjustified bound line to Current_Objectives;<br>G := Select one gate from the S-frontier; /* 4 */<br>Fix_Inputs(G);<br>(line, value, propagation) = Multiple_Backtrace( Current_Objectives ); /* 5 */<br>if (line, value, propagation) is empty then return( FAILURE );<br>Assign (i=line, $n_i$ =value, $p_i$ =propagation);<br>if TPG(Target_Fault) = SUCCESS then return( SUCCESS );<br>Assign (i=line, $n_i$ =X); /* 6 */<br>if TPG(Target_Fault) = SUCCESS then return( SUCCESS );<br>Assign (i=line, $n_i$ =X, $p_i$ =X);<br>return( FAILURE ); |                                                                              |                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------|

| <pre>if Imply_and_Check() = FAILURE then return( FAILURE ); /* 1 */ if (error at PO and all bound lines are justified) then     begin         Justify_Head_Lines();         Backward_Deduction(Target_Fault); /* 2 */         if Test_Found then begin             Analysis(); /* 3 */             return( SUCCESS );         end;     end;     end;     if (not error at PO and S-frontier = Ø) then return( FAILURE );     Add every unjustified bound line to Current_Objectives;     G := Select one gate from the S-frontier; /* 4 */     Fix_Inputs(G);     (line, value, propagation) = Multiple_Backtrace( Current_Objectives ); /* 5 */     if (line, value, propagation) is empty then return( FAILURE );     Assign (i=line, n_i=value, p_i=propagation);     if TPG(Target_Fault) = SUCCESS then return( SUCCESS );     Assign (i=line, n_i=X, p_i=X);     return( FAILURE ); </pre>                                                     | <pre>procedure TPG( Target_Fault ) : return( SUCCESS, FAILURE ); begin</pre> |                                       |

| if (error at PO and all bound lines are justified) then<br>begin<br>Justify_Head_Lines();<br>Backward_Deduction(Target_Fault); /* 2 */<br>if Test_Found then begin<br>Analysis(); /* 3 */<br>return(SUCCESS);<br>end;<br>end;<br>if (not error at PO and S-frontier = Ø) then return(FAILURE);<br>Add every unjustified bound line to Current_Objectives;<br>G := Select one gate from the S-frontier; /* 4 */<br>Fix_Inputs(G);<br>(line, value, propagation) = Multiple_Backtrace(Current_Objectives); /* 5 */<br>if (line, value, propagation) = Multiple_Backtrace(Current_Objectives); /* 5 */<br>if (line, value, propagation) = Multiple_Backtrace(Success); /* 5 */<br>if (line, value, propagation) = SUCCESS then return(SUCCESS);<br>Assign (i=line, n_i = n_i, p_i = X); /* 6 */<br>if TPG(Target_Fault) = SUCCESS then return(SUCCESS);<br>Assign (i=line, n_i = X, p_i = X);<br>return(FAILURE);                                       | 0                                                                            | /* 1 */                               |

| <pre>begin     Justify_Head_Lines();     Backward_Deduction(Target_Fault); /* 2 */     if Test_Found then begin         Analysis(); /* 3 */         return(SUCCESS);     end;     end;     if (not error at PO and S-frontier = Ø) then return(FAILURE);     Add every unjustified bound line to Current_Objectives;     G := Select one gate from the S-frontier; /* 4 */     Fix_Inputs(G);     (line, value, propagation) = Multiple_Backtrace(Current_Objectives); /* 5 */     if (line, value, propagation) is empty then return(FAILURE);     Assign (i=line, n_i=value, p_i=propagation);     if TPG(Target_Fault) = SUCCESS then return(SUCCESS);     Assign (i=line, n_i=x); /* 6 */     if TPG(Target_Fault) = SUCCESS then return(SUCCESS);     Assign (i=line, n_i=X);     return(FAILURE); </pre>                                                                                                                                       |                                                                              | /* 1 */                               |

| Justify_Head_Lines();<br>Backward_Deduction(Target_Fault); /* 2 */<br>if Test_Found then begin<br>Analysis(); /* 3 */<br>return(SUCCESS);<br>end;<br>end;<br>if (not error at PO and S-frontier = Ø) then return(FAILURE);<br>Add every unjustified bound line to Current_Objectives;<br>G := Select one gate from the S-frontier; /* 4 */<br>Fix_Inputs(G);<br>(line, value, propagation) = Multiple_Backtrace(Current_Objectives); /* 5 */<br>if (line, value, propagation) is empty then return(FAILURE);<br>Assign (i=line, n_i=value, p_i=propagation);<br>if TPG(Target_Fault) = SUCCESS then return(SUCCESS);<br>Assign (i=line, n_i=X); /* 6 */<br>if TPG(Target_Fault) = SUCCESS then return(SUCCESS);<br>Assign (i=line, n_i=X);<br>return(FAILURE);                                                                                                                                                                                       |                                                                              |                                       |

| <pre>Backward_Deduction(Target_Fault); /* 2 */ Backward_Deduction(Target_Fault); /* 2 */ if Test_Found then begin Analysis(); /* 3 */ return(SUCCESS); end; end; if (not error at PO and S-frontier = Ø) then return(FAILURE); Add every unjustified bound line to Current_Objectives; G := Select one gate from the S-frontier; /* 4 */ Fix_Inputs(G); (line, value, propagation) = Multiple_Backtrace(Current_Objectives); /* 5 */ if (line, value, propagation) is empty then return(FAILURE); Assign (i=line, n<sub>i</sub>=value, p<sub>i</sub>=propagation); if TPG(Target_Fault) = SUCCESS then return(SUCCESS); Assign (i=line, n<sub>i</sub>=n<sub>i</sub>, p<sub>i</sub>=X); return(FAILURE);</pre>                                                                                                                                                                                                                                        | begin                                                                        |                                       |

| <pre>if Test_Found then begin</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Justify_Head_Lines();                                                        |                                       |

| <pre>Analysis(); /* 3 */ return( SUCCESS ); end; end; if (not error at PO and S-frontier = Ø) then return( FAILURE ); Add every unjustified bound line to Current_Objectives; G := Select one gate from the S-frontier; /* 4 */ Fix_Inputs(G); (line, value, propagation) = Multiple_Backtrace( Current_Objectives ); /* 5 */ if (line, value, propagation) is empty then return( FAILURE ); Assign (i=line, n<sub>i</sub>=value, p<sub>i</sub>=propagation); if TPG(Target_Fault) = SUCCESS then return( SUCCESS ); Assign (i=line, n<sub>i</sub>=x); /* 6 */ if TPG(Target_Fault) = SUCCESS then return( SUCCESS ); Assign (i=line, n<sub>i</sub>=X); return( FAILURE );</pre>                                                                                                                                                                                                                                                                     | Backward_Deduction( Target_Fault );                                          | /* 2 */                               |

| <pre>return( SUCCESS );<br/>end;<br/>end;<br/>if (not error at PO and S-frontier = Ø) then return( FAILURE );<br/>Add every unjustified bound line to Current_Objectives;<br/>G := Select one gate from the S-frontier; /* 4 */<br/>Fix_Inputs(G);<br/>(line, value, propagation) = Multiple_Backtrace( Current_Objectives ); /* 5 */<br/>if (line, value, propagation) is empty then return( FAILURE );<br/>Assign (i=line, n<sub>i</sub>=value, p<sub>i</sub>=propagation);<br/>if TPG(Target_Fault) = SUCCESS then return( SUCCESS );<br/>Assign (i=line, n<sub>i</sub>=n<sub>i</sub>, p<sub>i</sub>=X); /* 6 */<br/>if TPG(Target_Fault) = SUCCESS then return( SUCCESS );<br/>Assign (i=line, n<sub>i</sub>=X, p<sub>i</sub>=X);<br/>return( FAILURE );</pre>                                                                                                                                                                                   | if Test_Found then begin                                                     |                                       |

| <pre>end;<br/>end;<br/>if (not error at PO and S-frontier = Ø) then return( FAILURE );<br/>Add every unjustified bound line to Current_Objectives;<br/>G := Select one gate from the S-frontier; /* 4 */<br/>Fix_Inputs(G);<br/>(line, value, propagation) = Multiple_Backtrace( Current_Objectives ); /* 5 */<br/>if (line, value, propagation) is empty then return( FAILURE );<br/>Assign (i=line, n<sub>i</sub>=value, p<sub>i</sub>=propagation);<br/>if TPG( Target_Fault ) = SUCCESS then return( SUCCESS );<br/>Assign (i=line, n<sub>i</sub>=n<sub>i</sub>, p<sub>i</sub>=X); /* 6 */<br/>if TPG( Target_Fault ) = SUCCESS then return( SUCCESS );<br/>Assign (i=line, n<sub>i</sub>=X, p<sub>i</sub>=X);<br/>return( FAILURE );</pre>                                                                                                                                                                                                      | Analysis();                                                                  | /* 3 */                               |

| <pre>end;<br/>if (not error at PO and S-frontier = Ø) then return( FAILURE );<br/>Add every unjustified bound line to Current_Objectives;<br/>G := Select one gate from the S-frontier; /* 4 */<br/>Fix_Inputs(G);<br/>(line, value, propagation) = Multiple_Backtrace( Current_Objectives ); /* 5 */<br/>if (line, value, propagation) is empty then return( FAILURE );<br/>Assign (i=line, n<sub>i</sub>=value, p<sub>i</sub>=propagation);<br/>if TPG( Target_Fault ) = SUCCESS then return( SUCCESS );<br/>Assign (i=line, n<sub>i</sub>=n<sub>i</sub>, p<sub>i</sub>=X); /* 6 */<br/>if TPG( Target_Fault ) = SUCCESS then return( SUCCESS );<br/>Assign (i=line, n<sub>i</sub>=X, p<sub>i</sub>=X);<br/>return( FAILURE );</pre>                                                                                                                                                                                                               | return( SUCCESS );                                                           |                                       |

| <pre>if (not error at PO and S-frontier = Ø) then return( FAILURE );<br/>Add every unjustified bound line to Current_Objectives;<br/>G := Select one gate from the S-frontier; /* 4 */<br/>Fix_Inputs(G);<br/>(line, value, propagation) = Multiple_Backtrace( Current_Objectives ); /* 5 */<br/>if (line, value, propagation) is empty then return( FAILURE );<br/>Assign (i=line, n<sub>i</sub>=value, p<sub>i</sub>=propagation);<br/>if TPG( Target_Fault ) = SUCCESS then return( SUCCESS );<br/>Assign (i=line, n<sub>i</sub>=n<sub>i</sub>, p<sub>i</sub>=X); /* 6 */<br/>if TPG( Target_Fault ) = SUCCESS then return( SUCCESS );<br/>Assign (i=line, n<sub>i</sub>=X, p<sub>i</sub>=X);<br/>return( FAILURE );</pre>                                                                                                                                                                                                                        | end;                                                                         |                                       |

| Add every unjustified bound line to <i>Current_Objectives</i> ;<br>G := Select one gate from the <i>S</i> -frontier; /* 4 */<br><i>Fix_Inputs(G)</i> ;<br>( <i>line, value, propagation</i> ) = <i>Multiple_Backtrace(Current_Objectives</i> ); /* 5 */<br><b>if</b> ( <i>line, value, propagation</i> ) is empty <b>then return</b> (FAILURE);<br><i>Assign</i> ( <i>i=line, n<sub>i</sub>=value, p<sub>i</sub>=propagation</i> );<br><b>if</b> <i>TPG(Target_Fault</i> ) = SUCCESS <b>then return</b> (SUCCESS);<br><i>Assign</i> ( <i>i=line, n<sub>i</sub>=n<sub>i</sub>, p<sub>i</sub>=X</i> ); /* 6 */<br><b>if</b> <i>TPG(Target_Fault</i> ) = SUCCESS <b>then return</b> (SUCCESS);<br><i>Assign</i> ( <i>i=line, n<sub>i</sub>=X, p<sub>i</sub>=X</i> );<br><b>return</b> (FAILURE);                                                                                                                                                        | end;                                                                         |                                       |

| G := Select one gate from the S-frontier; /* 4 */<br>$Fix\_Inputs(G);$<br>$(line, value, propagation) = Multiple\_Backtrace(Current\_Objectives); /* 5 */$<br>if (line, value, propagation) is empty then return(FAILURE);<br>$Assign (i=line, n_i=value, p_i=propagation);$<br>if $TPG(Target\_Fault) = \text{SUCCESS then return}(SUCCESS);$<br>$Assign (i=line, n_i=n_i, p_i=X); /* 6 */$<br>if $TPG(Target\_Fault) = \text{SUCCESS then return}(SUCCESS);$<br>$Assign (i=line, n_i=X, p_i=X); /* 6 */$<br>if $TPG(Target\_Fault) = \text{SUCCESS then return}(SUCCESS);$<br>$Assign (i=line, n_i=X, p_i=X);$<br>return(FAILURE);                                                                                                                                                                                                                                                                                                                 | if (not error at PO and S-frontier = $\emptyset$ ) then return(FAILURE       | );                                    |

| Fix_Inputs(G);(line, value, propagation) = Multiple_Backtrace(Current_Objectives);/* 5 */if (line, value, propagation) is empty then return( FAILURE );Assign (i=line, $n_i$ =value, $p_i$ =propagation);if TPG(Target_Fault) = SUCCESS then return(SUCCESS);Assign (i=line, $n_i$ = $n_i$ , $p_i$ =X);/* 6 */if TPG(Target_Fault) = SUCCESS then return(SUCCESS);Assign (i=line, $n_i$ = $n_i$ , $p_i$ =X);return(FAILURE);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Add every unjustified bound line to Current Objectives;                      |                                       |

| $(line, value, propagation) = Multiple_Backtrace(Current_Objectives); /* 5 */$<br>if (line, value, propagation) is empty then return(FAILURE);<br>Assign (i=line, n <sub>i</sub> =value, p <sub>i</sub> =propagation);<br>if TPG(Target_Fault) = SUCCESS then return(SUCCESS);<br>Assign (i=line, n <sub>i</sub> =n <sub>i</sub> , p <sub>i</sub> =X); /* 6 */<br>if TPG(Target_Fault) = SUCCESS then return(SUCCESS);<br>Assign (i=line, n <sub>i</sub> =X, p <sub>i</sub> =X);<br>return(FAILURE);                                                                                                                                                                                                                                                                                                                                                                                                                                                 | G := Select one gate from the S-frontier;                                    | /* 4 */                               |

| if (line, value, propagation) is empty then return( FAILURE );<br>Assign (i=line, $n_i$ =value, $p_i$ =propagation);<br>if TPG( Target_Fault ) = SUCCESS then return( SUCCESS );<br>Assign (i=line, $n_i$ = $n_i$ , $p_i$ =X); /* 6 */<br>if TPG( Target_Fault ) = SUCCESS then return( SUCCESS );<br>Assign (i=line, $n_i$ =X, $p_i$ =X);<br>return( FAILURE );                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Fix Inputs(G);                                                               |                                       |

| if (line, value, propagation) is empty then return( FAILURE );<br>Assign (i=line, $n_i$ =value, $p_i$ =propagation);<br>if TPG( Target_Fault ) = SUCCESS then return( SUCCESS );<br>Assign (i=line, $n_i$ = $n_i$ , $p_i$ =X); /* 6 */<br>if TPG( Target_Fault ) = SUCCESS then return( SUCCESS );<br>Assign (i=line, $n_i$ =X, $p_i$ =X);<br>return( FAILURE );                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (line, value, propagation) = Multiple Backtrace(Current Obje                 | ctives ); /* 5 */                     |

| Assign ( $i=line, n_i=n_i, p_i=X$ ); /* 6 */<br><b>if</b> TPG(Target_Fault) = SUCCESS <b>then return</b> (SUCCESS);<br>Assign ( $i=line, n_i=X, p_i=X$ );<br><b>return</b> (FAILURE);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              | · · · · · · · · · · · · · · · · · · · |

| Assign ( $i=line, n_i=X, p_i=X$ );<br>return( FAILURE );                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                              |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | return( FAILURE );                                                           |                                       |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | end;                                                                         |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ,                                                                            |                                       |

Fig. 7. Test pattern generation algorithm.

In the following, we explain the numbered lines in Fig. 7 that represent the newly introduced or extended concepts in our TPG method.

1) *Imply\_and\_Check():* This procedure is as discussed in Section 4.2. It determines as many line values as possible that are uniquely implied and updates the *S*-frontier. It performs unique sensitization whenever the *S*-frontier consists of a single gate. The procedure fails when a conflict occurs during a forward or a backward implication.

2) *Backward\_Deduction(Target\_Fault):* This procedure performs a backward sweep from primary outputs that have been assigned a value toward primary inputs. It relies on the lemmas in Section 4.3 to drop fault effects and faults on inputs of gates. The target fault is detected during this phase when conditions *C*1 and *C*2 are fulfilled (Section 4.3).

3) *Analysis():* This is the multiple fault analysis method as in [30] and recently extended to handle up to 32 input vectors in parallel [20]. The analysis is performed when the target fault is detected, in order to detect additional faults. The primary inputs left unspecified by the TPG are assigned random values.

4) The S-frontier consists of a list of gates in decreasing order of their observability measure values [3, 15]. This helps to select, at each step of the propagation of the target fault effect, the gate which is the closest to a primary output and whose error propagation is the easiest to observe. This ordering is neglected when the target fault effect is to be propagated first through a normal branch of a fanout stem. In this case, the reachable gate in the S-frontier from this normal branch is chosen first. The values are assigned to non-sensible inputs according to Table II (procedure  $Fix\_Inputs(G)$  in Fig. 7). These inputs are added to the *Current\_Objectives* to be justified by the multiple backtrace procedure.

5) *Multiple\_Backtrace()*: This procedure traces backward multiple paths to satisfy the set of *Current\_Objectives*. It is similar to the procedure in FAN, except that an objective consists of a line, a normal value and a propagation bit value. The selection of lines is performed as described in Section 4.2 when a gate output is specified but not its inputs (because of the presence of more than one input choice), and it is guided using testability measure values [3, 15]. The procedure returns the line number of a head line or a fanout stem *i* and values for  $n_i$  and  $p_i$  that have a good likelihood to satisfy the objectives. This procedure was extended to handle XOR and XNOR gates [27].

6) Backtracking: In this recursive version of the algorithm, the decision tree is identical to that of PODEM or FAN. When a value assignment on a line is rejected due to a conflict, the alternative is tried with the propagation bit set to X. It becomes 0 only if required for satisfying a subsequent objective(s).

# 4.5. A Complete TPG Example

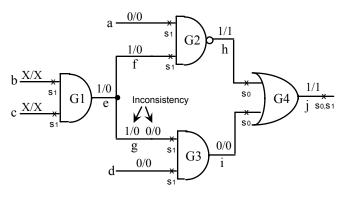

Consider the circuit in Fig. 8. After fault collapsing, all the remaining faults (shown in the figure) are assumed to be simultaneously present in the circuit, which is the initial circuit status. Lines a, e and d are head lines, b and c are free lines and f, g, h, i and j are bound lines [13]. The list of faults

in an arbitrary order is  $s_a^1$ ,  $s_f^1$ ,  $s_g^1$ ,  $s_d^1$ ,  $s_h^0$ ,  $s_i^0$ ,  $s_j^1$ ,  $s_j^0$ ,  $s_b^1$ ,  $s_c^1$ . Target faults are selected in the order of appearance.

Fig. 8. Aborted Target Fault.

Let  $s_a^{-1}$  be the first target fault. The assignment a = 0/0 activates it and implies  $w_a = 1$ , h = 1/Xand j = 1 / X. Since lines h and j dominate a, the unique sensitization procedure determines that f = 1/0and i = 0/0 are necessary to propagate the effect of  $s_a^{-1}$  to the primary output j. f = 1/0 implies e = 1/0, g = 1/0, h = 1/1,  $w_h = 1$ , and j = 1/1. i = 1/0 implies d = 0/0 and g = 0/0 (since  $s_g^{-1}$  and  $s_d^{-1}$  are still possible). At this step, the implication procedure stops because an inconsistency occurs on g - it was assigned 1/0 earlier -, as shown in Fig. 8. No backtracking is performed because all assignments were necessary and the target fault is aborted. In fact,  $s_a^{-1}$  would be detected only if  $s_d^{-1}$  is detected because the presence of  $s_d^{-1}$  masks  $s_a^{-1}$  at gate G4: if  $s_d^{-1} = 0$ , then d = 0/0 uniquely justifies i = 0/0.

Let  $s_f^1$  be the next target fault. As shown in Fig. 9a, the assignment f = 0/X activates the fault and implies  $w_f = 1$ , e = 0/X, g = 0/X, h = 1/X, i = 0/X and j = 1/1. The unique sensitization procedure determines that a = 1/0 and i = 0/0 are necessary to propagate the effect of  $s_f^1$  to primary output *j*. a = 1/0 implies h = 1/1 and  $w_h = 1$ . i = 0/0 implies g = 0/0, d = 0/0, e = 0/0, f = 0/0 and  $w_j = 1$ . At this stage, all line justifications succeed and the primary output is sensible. The justification of 0/0 on the head line *e* results in the unique assignments b = 0/0 and c = 0/0. The backward deduction procedure (Fig. 9b) then drops  $s_j^0$ ,  $s_h^0$  and  $s_f^1$ . The generated vector t = (abcd) = (1000) thus detects any MSF containing one of these faults.

a) Propagation of the target fault effect.

b) Backward deduction phase.

Fig. 9. TPG example.

Table III summarizes the TPG results for all faults in the circuit of Fig. 9. The columns indicate the selected target fault, the generated test vector, the list of dropped faults, the list of deduced normal lines during backward deduction, and the result of TPG regarding the target fault.

| COMPLETE TPG FOR THE CIRCUIT EXAMPLE |                |                        |                 |               |  |  |  |  |

|--------------------------------------|----------------|------------------------|-----------------|---------------|--|--|--|--|