# ARTICLE

# Open Access

# The ambipolar transport behavior of WSe<sub>2</sub> transistors and its analogue circuits

Zegao Wang<sup>1</sup>, Qiang Li<sup>1,2</sup>, Yuanfu Chen<sup>3</sup>, Bianxiao Cui<sup>4</sup>, Yanrong Li<sup>3</sup>, Flemming Besenbacher<sup>1</sup> and Mingdong Dong<sup>1,4</sup>

# Abstract

Tungsten diselenide (WSe<sub>2</sub>) has many excellent properties and provides superb potential in applications of valleybased electronics, spin-electronics, and optoelectronics. To facilitate the digital and analog application of WSe<sub>2</sub> in CMOS, it is essential to understand the underlying ambipolar hole and electron transport behavior. Herein, the electric field screening of WSe<sub>2</sub> with a thickness range of 1–40 layers is systemically studied by electrostatic force microscopy in combination with non-linear Thomas–Fermi theory to interpret the experimental results. The ambipolar transport behavior of 1–40 layers of WSe<sub>2</sub> transistors is systematically investigated with varied temperature from 300 to 5 K. The thickness-dependent transport properties (carrier mobility and Schottky barrier) are discussed. Furthermore, the surface potential of WSe<sub>2</sub> as a function of gate voltage is performed under Kelvin probe force microscopy to directly investigate its ambipolar behavior. The results show that the Fermi level will upshift by 100 meV when WSe<sub>2</sub> transmits from an insulator to an n-type semiconductor and downshift by 340 meV when WSe<sub>2</sub> transmits from an insulator to a p-type semiconductor. Finally, the ambipolar WSe<sub>2</sub> transistor-based analog circuit exhibits phase-control by gate voltage in an analog inverter, which demonstrates practical application in 2D communication electronics.

# Introduction

P-type and n-type transistors are the basic elements for constructing silicon-based complementary metaloxide-semiconductor (CMOS) electronics to realize digital and analog applications<sup>1</sup>. Typically, unipolar p-type and n-type transistors with high density are fabricated by various doping techniques and are integrated to build logic circuits<sup>2</sup>. The requirement of spatial separation in circuits makes the fabrication more complicated, resulting in the increase of fabrication costs. Conversely, ambipolar transistors, which can be easily switched between p-type and n-type by applying an electric field, are promising candidates to minimize circuit size with effectively simplified designs.

Correspondence: Mingdong Dong (dong@inano.au.dk)

© The Author(s) 2018

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

property, including organic/inorganic semiconductors. However, organic semiconductors are rarely applied in high-frequency logic electronics due to the relatively low carrier mobility<sup>3</sup>. Graphene's<sup>4</sup> absence of bandgap hinders its application in logic devices, even though the bandgap can be somehow tuned<sup>5,6</sup>. Although layered black phosphate has been shown to possess a unique ambipolar property<sup>7</sup>, it hardly survives after several hours of exposure in the atmosphere due to the low reactive barrier between black phosphate and oxygen/water<sup>8-10</sup>. Recently, transition metal dichalcogenides (MX<sub>2</sub>, where M = group IVB-VIIB metal and X = chalcogen) with a layered crystal structure were demonstrated to exhibit excellent semiconducting electrical properties with a large on/off ratio<sup>11–14</sup>. Among them, tungsten diselenide (WSe<sub>2</sub>), which consists of one layer of W atoms sandwiched between two layers of Se atoms, has many excellent properties providing potential applications, including valley-based electronics<sup>15,16</sup>, spin-electronics,

There are a few promising materials with the ambipolar

<sup>&</sup>lt;sup>1</sup>Interdisciplinary Nanoscience Center (iNANO), Aarhus University, DK-8000 Aarhus C, Denmark

<sup>&</sup>lt;sup>2</sup>School of Chemistry and Chemical Engineering, Shandong University, Jinan 250100 Shandong, China

Full list of author information is available at the end of the article.

and optoelectronics<sup>17,18</sup>. More significantly, different from the unipolar n-type semiconductor  $MoS_2$  with the presence of sulfur vacancy and the strong Fermi level pinning near the conduction  $band^{19-21}$ ,  $WSe_2$  as an ambipolar semiconductor has been demonstrated as having Fermi level effectively shifting between the valence band and the conduction band under application of an external field<sup>22-24</sup>.

Recently, the optical and hole dominant transport properties of exfoliated  $WSe_2$  have been explored<sup>24-27</sup>. To facilitate the potential application of WSe<sub>2</sub> in CMOS, it is essential to understand the underlying ambipolar hole and electron transport mechanisms. In this study, we obtain deep insight into the thickness-dependent electric field screening effect, and the interlayer coupling interaction is analyzed according to Thomas-Fermi theory. The thickness from 1 to 40 L and temperaturedependent ambipolar transport behavior of WSe2 transistors are studied systematically. Furthermore, the Fermi level shift of WSe<sub>2</sub> under gate voltage is investigated to understand its ambipolar behavior by Kelvin probe force microscopy. Finally, ambipolar WSe<sub>2</sub> transistors in analog circuits exhibiting gate-controlled phase change are demonstrated in practical application in two-dimensional (2D) electronics.

# Materials and methods

## **Device fabrication**

The WSe<sub>2</sub> flakes were mechanically exfoliated from a bulk crystal onto an SiO<sub>2</sub>/Si wafer using adhesive tape. The FETs were fabricated on a single wafer using electron beam lithography, simultaneously exposing all of the devices with the same processing step to ensure uniformity. The source and drain electrodes (10 nm Ti/40 nm Au) were deposited by electron beam deposition with a deposit speed of 0.2 Å/s. Before electron beam evaporation, the samples were kept overnight under the high vacuum of the electron beam deposition system. All of the devices were deposited simultaneously to ensure the same conditions. Before measurement, devices were annealed under Ar (including 10% H<sub>2</sub>) at 200 °C for 2 h.

## Measurement

The Raman spectroscopy measurements were carried out with 514-nm, 1.0-mW laser excitation and ×100 objective (Renishaw inVia Raman Spectroscope, Sweden). High-resolution transmission electron microscopy (HRTEM) imaging was conducted using an FEI Talos F200X operated at 200 kV. EFM measurements were performed with a commercial atomic force microscopy (AFM) instrument (Dimension Icon, Bruker, USA) under ambient conditions. Commercial rectangular silicon cantilever coated with a Co/Cr layer with a resonant frequency of 75 kHz and a spring constant of 2.8 N/m (MESP, Bruker, USA) was used for electrostatic force microscopy (EFM) imaging. The tip radius of the magnetic tip is ~35 nm. The tip lift height is 10 nm. A Keithley 4200SCS was employed to measure the direct current transport properties of the devices using a probe station in a vacuum chamber. The performance of the analogs circuits was measured using an oscilloscope (Agilent Infiniti Vision 3000).  $V_{\rm bias}$  and  $V_{\rm DD}$  were applied by the Keithley 4200SCS, and  $V_{\rm ac}$  was applied using a signal generator (Agilent 33120 A).

# **Results and discussion**

WSe<sub>2</sub> flakes were prepared by mechanical exfoliation, and the optical properties, including the optical contrast and Raman spectra, were characterized (see Supplementary Figures S1 and S2). As seen, the relationship between the optical contrast or Raman optical properties and thickness trends weaker and towards disorder when the layer number is higher than 4L. Furthermore, HRTEM was employed to study the atom-stacking mode of WSe<sub>2</sub> with a thickness range from 1L to 12L (see Supplementary Figures S3 and S4). The similar properties, including the distance along ( $\bar{1}010$ ) or ( $0\bar{1}10$ ) and the similar intensity profiles along the (1210), (0110), ( $\bar{1}010$ ), and ( $2\bar{1}10$ ) directions in SAD patterns, indicate the same stack mode (2H mode) of WSe<sub>2</sub>.

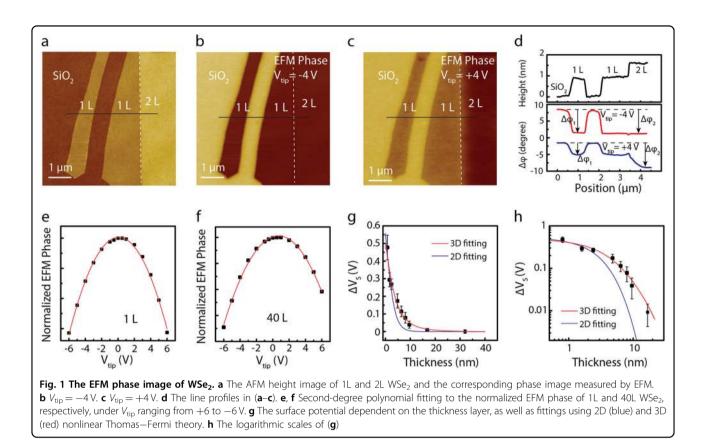

To gain a deeper insight into the dimensionality effect on the interlayer screening in WSe2 flakes, EFM was employed to probe the electric field, which is caused by the charged impurities present at the WSe<sub>2</sub>/SiO<sub>2</sub> substrate interface. In this study, the EFM measurements are conducted in a two-pass lift mode, in which a conductive AFM (c-AFM) cantilever first scanned over the WSe<sub>2</sub> flakes for topography and then was lifted a constant height to detect long-range electric interactions between the voltage applied tip and WSe<sub>2</sub> flakes. Because the EFM phase change directly relates to the unscreened charges, the observed differences in the EFM phase change indicate different field screening capabilities of WSe<sub>2</sub> flakes with different thicknesses. The typical AFM topographic image of 1L and 2L WSe<sub>2</sub> on  $SiO_2$  is shown in Fig. 1a, and the corresponding EFM images under a negative tip voltage and a positive tip voltage are shown in Fig. 1b, c. The correlated line profiles from Fig. 1a-c are shown in Fig. 1d, where one can see that the phase shift  $(\Delta \phi)$  of WSe<sub>2</sub> is always negative compared to a bare SiO<sub>2</sub> substrate. Significantly,  $\Delta \phi$  is dependent on both WSe<sub>2</sub> thickness and the tip bias. If the AFM tip and WSe<sub>2</sub> can be considered as an ideal capacitance, the EFM phase shift can be described as Eq.  $(1)^{28,29}$ , where Q and k are the Qfactor and spring constant of the cantilever, C is the local capacitance between the tip and WSe<sub>2</sub>,  $V_{\text{tip}}$  is the applied

DC voltage, and  $V_s$  is the effective surface potential.

$$\Delta \phi = \frac{Q}{2k} \frac{\partial^2 C}{\partial^2 z} \left( V_{tip} - V_s \right)^2. \tag{1}$$

Typically, a fit between  $V_{\rm tip}$  and phase can be achieved for both 1L and 40L WSe<sub>2</sub> by using a second-degree polynomial (Fig. 1e, f). The deviations of the  $V_{\rm s}$  values for the 1–40L WSe<sub>2</sub> are summarized in Fig. 1g. As seen, the effective surface potential difference decreases as thickness increases, indicating the screening effect of WSe<sub>2</sub> enhanced with the number of layers. To gain insight into the screening effect, nonlinear Thomas–Fermi theory is employed to understand the interlayer couple interaction. First, if the interlayer coupling interaction is excluded, the screening effect is parallel, following the 2D model, and then the surface potential difference can be described as Eq. (2)<sup>28,29</sup>.

$$\Delta V(D) = \frac{2\pi\hbar^2 \sigma_0}{eN_s N_v m_{||}} \sqrt{2\beta_0 d} \frac{1 - r_D}{\sqrt{1 - r_D^2}},$$

(2)

where  $r_D = 1/\cosh(D\sqrt{2\beta_0/d})$ ;  $\hbar$  is the reduced Plank constant;  $\sigma_0$  is the charge density on the SiO<sub>2</sub> substrate;  $N_s$ and  $N_v$  are the spin and valley degeneracies ( $H_s = N_v = 2$ );  $m_{||}$  is the in-plane effective mass; d is the interlayer spacing in WSe<sub>2</sub>;  $\beta_0 = e^2 N_s N_v m_{||} / 4\pi \varepsilon_0 \varepsilon \hbar^2$ ; and  $\varepsilon_0$  and  $\varepsilon$  are the vacuum permittivity and the dielectric constant of WSe<sub>2</sub> ( $\varepsilon = 7$ )<sup>30</sup>, respectively. The blue lines in Fig. 1g, h show the 2D fitting, where  $\sigma_0$  is  $1.2 \times 10^{13}$  cm<sup>-2</sup>,  $m_{||}$  is 0.01 $m_{\rm e}$  and  $m_{\rm e}$  is the electron rest mass. According to the fitting, one can see that the screening effect follows the 2D model when the thickness is less than 2.4 nm (3L WSe<sub>2</sub>), suggesting a weak interlayer coupling interaction at lower thickness. However, the 2D fitting is hardly acceptable when the thickness increases further, indicating that the interlayer coupling interaction becomes strong. The three-dimensional (3D) fitting, considering interlayer coupling interlayer coupling interlayer.

$$\Delta V(D) = \frac{1}{2} \left( \frac{6\pi^2 \hbar^3}{N_s N_v dm_{||} \sqrt{m_\perp}} \right)^{\frac{2}{3}} \left( \frac{25\beta_\perp d\sigma_0^2}{8e^2} \right)^{\frac{2}{5}} \times \frac{1 - r_D}{\left(1 - r_D^{5/2}\right)^{\frac{2}{5}}},$$

(3)

where  $m_{\perp} = \hbar^2/2t_{\perp}d^2$ ,  $t_{\perp} = 0.2eV$  ( $t_{\perp}$ : interlayer hopping parameter),  $\beta_{\perp} = (4e^2/5\varepsilon_0\varepsilon) (N_s N_\nu dm_{||}\sqrt{m_{\perp}}/6\pi^2\hbar^3)^{2/3}$ , and  $r_D$  can be numerically solved from Eq. (4):

$$\left[\frac{25\beta_{\perp}d\sigma_0^2}{8\left(1-r_D^{5/2}\right)}\right]^{-1/10} \frac{du}{r_D} \frac{du}{\left(u^{5/2}-r_D^{5/2}\right)^{1/2}} = \sqrt{\frac{2\beta_{\perp}}{d}}D.$$

(4)

The red line in Fig. 1g, h shows the 3D fitting, where  $\sigma_0 = 0.8 \times 10^{13} \text{ cm}^{-2}$  and  $m_{||} = 0.01 m_{\rm e}$ , respectively. One can see that the 3D fitting has much better consistency with the EFM results, particularly for the thicker region, indicating that WSe<sub>2</sub> is mostly in a strong coupling regime, which will apparently be reflected in the electrical transport mechanism.

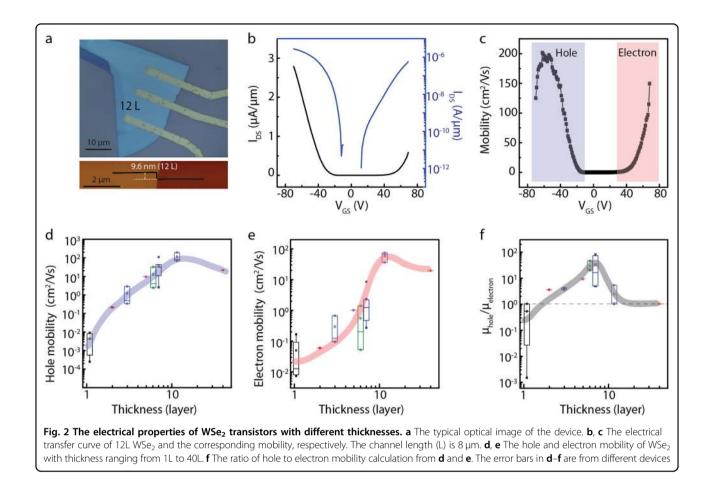

In order to explore the thickness-dependent transport behavior of WSe<sub>2</sub>, back-gated field effect WSe<sub>2</sub> transistors (FETs) were fabricated, where Ti/Au instead of traditional p-type Pd/Au or Pt/Au contacts were deposited to form ambipolar contact. Figure 2a shows the optical image of the 12L WSe<sub>2</sub> transistor. The transfer curve at room temperature (RT) is shown in Fig. 2b, indicating a typical ambipolar transport behavior, where the hole is the dominant carrier when  $V_{GS} < -15$  V and the electron is the dominant carrier when  $V_{GS} > +15$  V. The ambipolar behavior results from the shifting of the Fermi level under the electric field, which is attributed to the weak Fermilevel pinning at the metal/WSe<sub>2</sub> interface. Figure 2c shows the gate voltage-dependent field effect mobility, which is calculated by  $\mu = (L/WC_0V_{DS})(dI_{DS}/dV_{GS})$ , where  $C_0$  is the capacity and L and W are the channel length and width, respectively. The maximum hole mobility and electron mobility are 196 and 150 cm<sup>2</sup>/Vs when the gate voltage is -56 and +70 V, respectively. The balanced electron and hole transport characteristic results from the similar n-type and p-type Schottky barrier because Fermi level is closer to the middle level between the conduction band and valence band. Figure 2d, e shows the thickness-dependent results for hole mobility and electron mobility, where the mobility is extracted in both positive/negative 50-60 V ranges of gate voltages for hole mobility  $(\mu_{\rm h})$  and electron mobility  $(\mu_{\rm e})$ , respectively. With the dimensionality increase from 2D (monolayer) to 3D (12L), both hole mobility and electron mobility increase. The mobility increase should be related to both the increased density of state inducing a smaller Schottky barrier (discussed later in Fig. 3d) and the screened interfacial charged impurities inducing a weaker scattering<sup>31</sup>. Moreover, the bandgap of WSe<sub>2</sub> decreases as the thickness increases<sup>32</sup>, which is also one of the key reasons for the enhancement of electrical performance.

When the thickness is 40L, both the hole mobility and electron mobility decrease to ~20 cm<sup>2</sup>/V s, which should be caused by the increased series resistances associated with an increasing number of interlayers<sup>33</sup>. Fig. 2f shows the thickness-dependent  $\mu_{\rm h}/\mu_{\rm e}$ , which is the important

factor for evaluating the symmetric transport characteristic. The ratio of  $\mu_{\rm h}/\mu_{\rm e}$  for 1L WSe<sub>2</sub> is approximately 0.1, indicating an electron dominant transport characteristic, which implies that the hole carrier is almost suppressed by the interfacial charged impurities and has a more sensitive response than that of the electron carrier. For 2L and 3L WSe<sub>2</sub>, the ratio of  $\mu_h/\mu_e$  is approximately 3 and further increases to ~30 for 6L and 7L WSe2, which should result from the fast increase of hole mobility attributed to the screened interfacial charged impurities (Fig. 1). From 7L to 12L, the ratio of  $\mu_{\rm h}/\mu_{\rm e}$  decreases to approximately 1, corresponding to the balanced ambipolar transport behavior, which should result from the faster increase of  $\mu_{\rm e}$  (Fig. 2e) caused by the lower Schottky barrier height for the electron injection. In a 40L WSe<sub>2</sub> transistor, the ratio of  $\mu_{\rm h}/\mu_{\rm e}$  is ~1, which suggests that the transport properties for the hole and electron carriers are same. The transport behavior (n-type or p-type) is not only dependent on the interfacial state but also dependent on the work function of metal contact. For the interfacial state, in combination with the EFM results (Fig. 1), we can propose that the channel region with thinner thickness has a higher effect from the interfacial charged impurities, and thus the hole carrier is suppressed, inducing n-type behavior. As the thickness increases, the interfacial charged impurities are screened, which makes the WSe<sub>2</sub> flakes display intrinsic property. Alternately, the metal contact is also another critical role in transport. Pudasaini et al.<sup>34</sup> reported that the carrier type can evolve from ptype to ambipolar to n-type in WSe2 using Cr (the work function of Cr is 4.6 eV) contact with increasing channel thickness. In thinner WSe<sub>2</sub>, the hole conduction appears dominant because the aligned Fermi level of thinner WSe<sub>2</sub>/Cr contact is below the middle of the bandgap. In this study, the lower work function of Ti  $(\sim 4.3 \text{ eV})^{35}$  and the higher Schottky barrier height in the hole transport region can induce the preferential electron dominant conduction in thinner WSe<sub>2</sub>. This phenomenon is in line with the previous reported preferential n-type in thinner WSe2 with low-work-function metals, such as Ni, In, and Ag<sup>24,35</sup>. The requirement for real application of ambipolar semiconductor is not only the balanced hole and electron

carrier but also the higher carrier mobility. Although the ratio of  $\mu_{\rm h}/\mu_{\rm e}$  in 2L WSe<sub>2</sub> is close to 1, the electron mobility and hole mobility are relatively lower. Thus, the balanced hole and electron transport with higher mobility could be achieved in 12L WSe<sub>2</sub>, which could satisfy the requirement for practical ambipolar application.

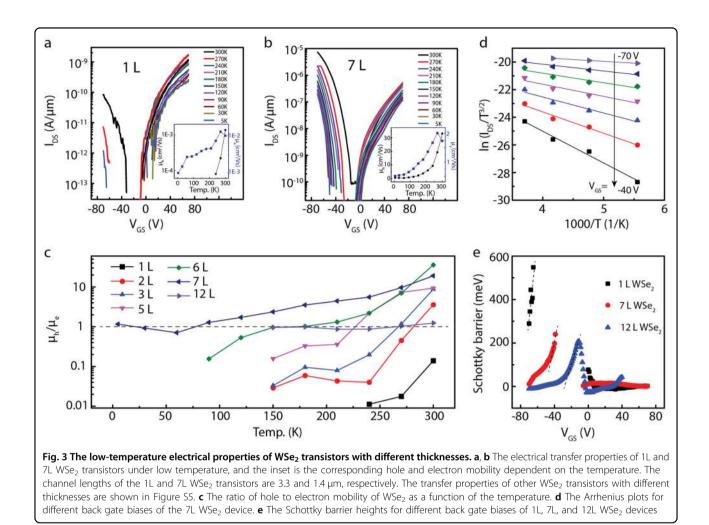

To gain insight into the ambipolar transport behavior, the electrical properties of WSe<sub>2</sub> transistors with different thicknesses are measured from RT to 5 K. The typical transfer curves of 1L and 7L WSe2 are shown in Fig. 3b (others are shown in Supplementary Figure S5). As seen in the 1L WSe<sub>2</sub> transistor, the hole branch is almost completely gone, meaning that it is an insulator when the temperature decreases to 210 K, while the electron branch still exists. Interestingly, it is 60 K when the hole branch is fully suppressed in the 2 L WSe2 transistor. Further, in the 7 L WSe<sub>2</sub> transistor, it is obviously seen that both the hole and electron branches exist until the temperature cools to 5 K. The corresponding temperature-dependent mobility is inserted, where one can see that the electron mobility slightly increases and then decreases, while the hole mobility rapidly decreases during cooling. The electron mobility shows a peak attributed to the dominant scattering switching from phonon scattering to charged impurities scattering during cooling. This phenomenon is also observed in electron-dominant back-gated MoS<sub>2</sub> transistors<sup>36</sup>. Alternately, the hole mobility is monotonously and rapidly decreasing during cooling, implying that both the phonon and charged impurities scattering strongly effect the hole carrier, which is in line with the hole-dominant graphene transistor<sup>37</sup>.

Figure 3c shows the ratio of  $\mu_{\rm h}/\mu_{\rm e}$  as the function of temperature in WSe<sub>2</sub> transistors with thickness ranging from 1L to 12L. We would simply separate the dominant transport mechanism by  $\mu_h/\mu_e = 1$  as shown by the dashed line in Fig. 3c, and thus, the dominant carrier is the hole when  $\mu_h/\mu_e > 1$ , while the dominant carrier is the electron when  $\mu_h/\mu_e < 1$ . In 1–7L WSe<sub>2</sub> transistors, the ratios of  $\mu_{\rm h}/\mu_{\rm e}$  almost decrease with temperature, which should be caused by the faster decrease of hole mobility originating from the relatively stronger scattering on the hole carrier compared to the relatively weaker scattering on the electron carrier. In detail, the ratios of  $\mu_{\rm h}/\mu_{\rm e}$  for WSe<sub>2</sub> transistors monotonously decrease across the dashed line for 2L, 3L, 5L, and 6L at 280, 267, 228, and 80 K, respectively, which means that the dominant carrier is switched from hole carrier to electron carrier during cooling. The different converted temperatures in WSe<sub>2</sub> transistors with different thicknesses are possibly attributed to their different scattering levels. Different from 1L–6L WSe<sub>2</sub> transistors, the ratio of  $\mu_{\rm h}/\mu_{\rm e}$  for the 7L  $WSe_2$  transistor decreases from ~15 at 300 K to ~1 at 80 K and then saturates to 1. The hole and electron mobility as a function of temperature is shown in the inset of Fig. 3b,

where the hole mobility decreases faster than the electron mobility. When the temperature is lower than 80 K, both the hole and electron mobility trend toward saturation, which is distinct from the evolution of hole and electron mobility in 1L-6L WSe2, where hole conduction rapidly decreases or even disappears. Therefore, from 7L WSe<sub>2</sub>, the electronic transport behavior trends toward an intrinsic property, whereby the dominant scattering is originated from the scattering center of the material rather than from interfacial charged impurity. Finally, the ratio of  $\mu_h/\mu_e$  in the 12L WSe<sub>2</sub> transistor is approximately 1, implying that the influence of scattering on the hole or electron carrier is similar. The 12L WSe<sub>2</sub> transistor with balanced ambipolar behavior originates from the bulk effect since the interfacial charged impurities are screened.

As known, the mobility behavior of a 2D material at low temperature is correlated with the contact metal but more significantly dependent on the scattering mechanism. Coulomb scattering originating from the interfacial charged impurity is one of the key scattering mechanisms. Although the interfacial charged impurity can be screened by introducing high-k dielectric, ion-gel, and  $BN^{23,27,36,38}$ , the complex fabrication and higher cost need to be taken into consideration. Interestingly, the hole branch in the 1L WSe<sub>2</sub> transistor disappears, suggesting that the effect of interfacial charged impurities on the hole carrier is much stronger than that on the electron carrier, while the interfacial charged impurity is screened in the 7L WSe<sub>2</sub> transistor and leads to a similar effect on hole mobility and electron mobility.

Even for the samples that have be held in high vacuum overnight before electron beam evaporation, the  $\text{TiO}_x$  buffer layer between Ti/Au contact and WSe<sub>2</sub> may also be formed<sup>39,40</sup>, which will induce the formation of dipoles and further tune the Schottky barrier height. Thus, the transport property cannot be predicted by simple band offset, and, therefore, it is worth estimating the Schottky barrier to further reveal the thickness-dependent band profile. To evaluate the Schottky barrier height between metal and WSe<sub>2</sub>,  $I_{DS}$  could be defined by 2D thermionic emission (Eq. (5)) due to its sufficiently thin channel<sup>41</sup>.

$$I_{DS} = A_{2D}^* T^{3/2} exp\left(\frac{\phi_B}{k_B T}\right) \left[1 - exp\left(\frac{eV_{DS}}{k_B T}\right)\right],\tag{5}$$

where  $A_{2D}^*$  is the 2D equivalent Richardson constant, *T* is the absolute temperature,  $k_{\rm B}$  is the Boltzmann constant, and  $\phi_{\rm B}$  is the effective Schottky barrier. The temperature dependence of the  $I_{\rm DS}-V_{\rm BG}$  curve could be re-plotted with Arrhenius formation  $(ln(I_{DS}/T^{3/2}) \sim 1000/T)$  as shown in Fig. 3d (7L WSe<sub>2</sub>). The effective Schottky barrier could be obtained from the slope of the Arrhenius plot. Figure 3e shows the effective Schottky barrier as a

function of the gate voltage of 1L, 7L, and 12L WSe<sub>2</sub> devices. A peak between -10 and 0 V in the 7L WSe<sub>2</sub> device is attributed to the opposite polarities of Schottky contact, which could be tuned based upon the gate voltage<sup>41</sup>. As seen, the effective Schottky barrier for the hole carrier is strongly dependent on the gate voltage compared to that for the electron carrier. Knowingly, the effective Schottky barrier for the hole is obviously reduced as the WSe<sub>2</sub> thickness increases, while there is no noticeable change in the electron carrier. The above study demonstrates that 12L WSe<sub>2</sub> exhibits good ambipolar behavior with balanced carrier mobility in a broad temperature range from RT to low temperature.

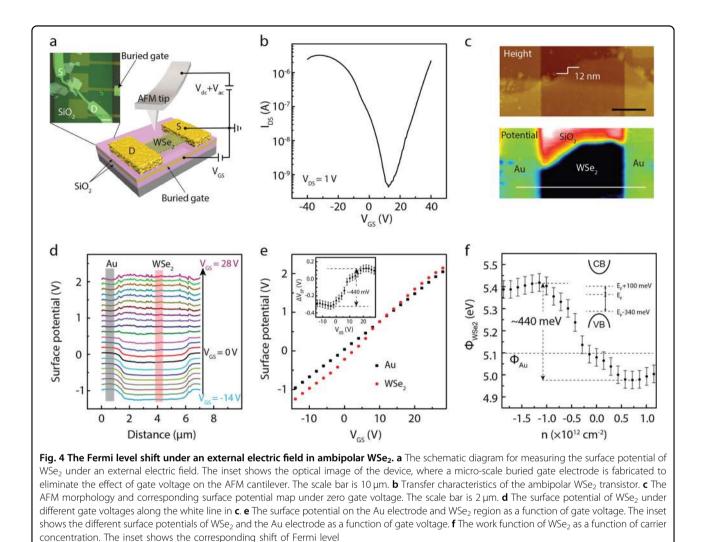

The above study reveals that the carrier of  $WSe_2$  can be effectively switched between electron and hole by a tunneling external electric field, corresponding to exhibit ntype and p-type behaviors, respectively. To reveal the ambipolar behavior of  $WSe_2$ , the work function change and Fermi level shift of  $WSe_2$  are studied under different gate voltages. Here, in situ Kelvin probe force microscopy (KPFM) is employed to measure the contact potential difference between the tip and the sample,  $V_{CPD}$ , which is referred to as the surface potential  $(V_{SP})^{42}$ . To reduce the unscreened effect of gate voltage on the AFM cantilever, the gate electrode with a size of 20 µm is buried under the SiO<sub>2</sub> layer. The WSe<sub>2</sub> flake is transferred on the surface, and then source/drain electrodes are fabricated by electron beam lithography, as shown in Supplementary Figure S6. Figure 4a shows the schematic diagram of the setup for surface potential measurement, where the electrostatic force between the cantilever and sample is nullified by applying a DC bias.

Figure 4b shows the transfer characteristic of the  $WSe_2$  device exhibiting typical ambipolar behavior. The charge neutrality point is located at 12 V, which is due to the interfacial state between  $WSe_2$  and sputtered SiO<sub>2</sub>. The height and corresponding surface potential of the device are shown in Fig. 4c. The line profiles under

different gate voltages along the white line in Fig. 4c are shown in Fig. 4d. As seen, the shift of the background is due to the unscreened electrostatic interaction between the AFM cantilever and the buried gate voltage<sup>43</sup>. It has been reported that the gate voltage will not influence the surface potential of a metallic electrode; therefore, the background signal could be subtracted to obtain the relative surface potential change of WSe<sub>2</sub>, as shown in Fig. 4e. The surface potential difference  $\Delta V_{SP}$  between WSe2 and the Au electrode can be calculated by  $\Delta V_{SP} = V_{SP\_WSe_2} - V_{SP\_Au}$ , where  $V_{SP\_WSe_2}$  and  $V_{SP\_Au}$ are the surface potentials of WSe<sub>2</sub> and Au, respectively. As seen in Fig. 4e,  $\Delta V_{\rm SP}$  changes from ~-0.330 to ~0.100 V when the gate voltage varies from -14 to 28 V. A sudden change of  $\Delta V_{\rm SP}$  (Fig. 4e) is observed at the charge neutrality point  $(V_D)$ , where the gate voltage is 12 V. The rapid change of  $\Delta V_{\rm SP}$  is also reported in graphene, which may be related to the different electronic structures of the valance band and conductive band<sup>43</sup>. As known, the surface potential recorded by the KPFM could be formatted by  $eV_{SP} = \emptyset_{tip} - \emptyset_{sample}$ , where  $\emptyset_{tip}$  and  $\emptyset_{sample}$  are the work functions of the AFM tip and sample<sup>42</sup>, respectively. Thus, the surface potential change is related to the work function:  $e\Delta V_{SP} = \emptyset_{Au} - \emptyset_{WSe_2}$ , where  $\emptyset_{Au}$  and  $\emptyset_{WSe_2}$  are the work functions of Au and WSe<sub>2</sub>, respectively. Here, we assume that the work function of Au is 5.1 eV<sup>44,45</sup>, and therefore, the work function of WSe<sub>2</sub> could be directly calculated by  $\emptyset_{WSe_2} = \emptyset_{Au} - e\Delta V_{SP}$ . Figure 4f shows the work function of WSe<sub>2</sub> ( $\emptyset_{WSe_2}$ ) as a function of carrier concentration, where the carrier concentration is calculated by  $n = C_0(V_{GS} - V_D)/e$ . For this particular device, it is seen that  $\emptyset_{WSe_2}$  could be tunneled by ~440 meV when WSe<sub>2</sub> switches between n-type and p-type transport behaviors. Namely, the Fermi level will upshift by 100 meV when the WSe<sub>2</sub> transmits from an insulator to an n-type semiconductor, as shown in the inset of Fig. 4f.

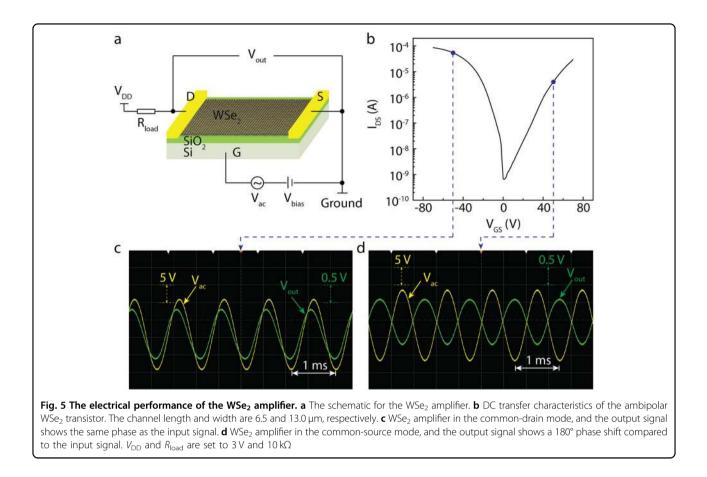

As studied above, the WSe<sub>2</sub> transistor displays typical ambipolar behavior with reasonable electron mobility and hole mobility, which has the potential for practicable use in communication<sup>7</sup>. As proof of the concept, the 12L WSe<sub>2</sub> transistor is employed to demonstrate two basic functions of analog circuits. The schematic of the WSe<sub>2</sub> amplifier is illustrated in Fig. 5a, where the supply voltage  $V_{\text{DD}}$  is set to 3 V, and the off-chip resistor  $R_{\text{load}}$  is 10 k $\Omega$ . As seen, the gate voltage ( $V_{\text{GS}}$ ) is hence equal to the sum of a fixed DC bias voltage ( $V_{\text{bias}}$ ) and a small sinusoidal AC signal ( $V_{\text{ac}}$ ,  $V_{\text{PP}} = 10$  V, f = 1 kHz). The DC transfer

curve of the WSe<sub>2</sub> transistor at RT is shown in Fig. 5b, which displays balanced electron and hole transport. The output signal  $(V_{out})$  of the WSe<sub>2</sub> amplifier is monitored on an oscilloscope as shown in Fig. 5c, d, corresponding to negative and positive  $V_{\text{bias}}$ , respectively. When a negative  $V_{\text{bias}}$  is applied to the WSe<sub>2</sub> amplifier (Fig. 5c), in the positive phase of  $V_{\rm ac}$ ,  $I_{\rm ds}$  increases/ decreases as  $V_{GS}$  decreases/increases, so the voltage drop across the off-chip resistor will increase/decrease, respectively<sup>46,47</sup>. As a consequence, the corresponding  $V_{\rm out}$  will decrease/increase, which exhibits the same phase as the input signal. This situation is called the commondrain mode. Similarly, when  $V_{\text{bias}}$  is positive in the n-type branch, the corresponding Vout will increase/decrease as V<sub>GS</sub> decreases/increases, respectively, which exhibits a phase difference of 180° compared to  $V_{\rm ac}$  (Fig. 5d). This situation is called the common-source mode. Therefore, it is clear that the working mode of the WSe<sub>2</sub> amplifier could be easily controlled by DC bias voltage. Two fundamental modes in a single WSe<sub>2</sub> transistor demonstrate that one can develop other WSe2-based complicated analog circuits for signal processing performance with simplified circuit designs.

### Conclusion

In summary, EFM is employed to investigate the electric-field screening effect of WSe2 with a thickness range of 1–40 layers. The effective surface potential as a function of thickness is investigated in combination with non-linear Thomas-Fermi theory. The results show that the dielectric screening behavior follows a 2D model when the thickness is less than 3L, while it follows a 3D model when the thickness is greater than 3L. Significantly, the electrical transport properties of WSe<sub>2</sub> transistors demonstrate that the WSe<sub>2</sub> transistor exhibits ambipolar behavior and the asymmetric transport characteristic with different layer thicknesses. By studying the thickness- and temperature-dependent transport behavior, we successfully demonstrate that 12L WSe2 exhibits balanced ambipolar behavior with higher electron and electron mobility from RT to low temperature. Furthermore, the ambipolar behavior of WSe2 is studied by in situ KPFM to reveal its work function change/Fermi level shift as a function of gate voltage. The results show that the work function/Fermi level will be tunneled by 440 meV when WSe<sub>2</sub> switches between n-type and p-type WSe<sub>2</sub>. Finally, the analog circuit composed of ambipolar 12L WSe<sub>2</sub> transistors exhibits good controlled-phase performance, demonstrating its practical communication application in 2D electronics.

#### Acknowledgements

This research was supported by grants from the Danish National Research Foundation, AUFF NOVA-project, The National Natural Science Foundation of China (Grant No. 51372033, 21528501, 21703119), Shandong Provincial Nature Science Foundation (Grant No. ZR2017MB036), the National High Technology Research and Development Program of China (Grant No. 2015AA034202), and EU H2020 RISE 2016 (MNR4SCell 734174 project). The authors would like to acknowledge Pia Bomholt Jensen for the technique support in the sputtering deposition.

#### Author details

<sup>1</sup>Interdisciplinary Nanoscience Center (iNANO), Aarhus University, DK-8000 Aarhus C, Denmark. <sup>2</sup>School of Chemistry and Chemical Engineering, Shandong University, Jinan 250100 Shandong, China. <sup>3</sup>State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu 610054, China. <sup>4</sup>Department of Chemistry, Stanford University, Stanford, CA 94305, USA

#### Conflict of interest

The authors declare that they have no conflict of interest.

#### Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information is available for this paper at https://doi.org/10.1038/s41427-018-0062-1.

Received: 10 January 2018 Revised: 18 March 2018 Accepted: 8 May 2018. Published online: 1 August 2018

#### References

- Abbott, J. et al. CMOS nanoelectrode array for all-electrical intracellular electrophysiological imaging. Nat. Nanotechnol. 12, 460–466 (2017).

- Pierre, M. et al. Single-donor ionization energies in a nanoscale Cmos channel. Nat. Nanotechnol. 5, 133–137 (2010).

- Zhao, Y., Guo, Y. & Liu, Y. 25th anniversary article: recent advances in N-type and ambipolar organic field-effect transistors. *Adv. Mater.* 25, 5372–5391 (2013).

- Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

- Wang, Z. G. et al. Synthesis, characterization and electrical properties of silicondoped graphene films. J. Mater. Chem. C 3, 6301–6306 (2015).

- Wang, X. et al. Heteroatom-doped graphene materials: syntheses, properties and applications. *Chem. Soc. Rev.* 43, 7067–7098 (2014).

- Zhu, W. et al. Flexible black phosphorus ambipolar transistors, circuits and AM demodulator. *Nano Lett.* 15, 1883–1890 (2015).

- Li, L. et al. Black phosphorus field-effect transistors. Nat. Nanotechnol. 9, 372–377 (2014).

- Kwon, H. et al. Ultrathin and flat layer black phosphorus fabricated by reactive oxygen and water rinse. ACS Nano 10, 8723–8731 (2016).

- Liu, X. et al. Scanning probe nanopatterning and layer-by-layer thinning of black phosphorus. Adv. Mater. 29, 1604121 (2017).

- Wang, Z., Li, Q., Besenbacher, F. & Dong, M. Facile synthesis of single crystal PtSe<sub>2</sub> nanosheets for nanoscale electronics. *Adv. Mater.* 28, 10224–10229 (2016).

- Zhou, L. et al. Synthesis of high-quality large-area homogenous 17' MoTe<sub>2</sub> from chemical vapor deposition. Adv. Mater. 28, 9526–9531 (2016).

- Zheng, B. et al. Vertically oriented few-layered HfS<sub>2</sub> nanosheets: growth mechanism and optical properties. 2D Mater. 3, 035024 (2016).

- Li, D. et al. Two-dimensional non-volatile programmable P–N junctions. Nat. Nanotechnol. 12, 901–906 (2017).

- Hao, K et al. Direct measurement of exciton valley coherence in monolayer WSe<sub>2</sub>. Nat. Phys. **12**, 677–682 (2016).

- Wang, Z., Shan, J. & Mak, K. F. Valley- and spin-polarized Landau levels in monolayer WSe<sub>2</sub>. *Nat. Nanotechnol.* **12**, 144–149 (2017).

- Yuan, H. et al. Generation and electric control of spin–valley-coupled circular photogalvanic current in WSe<sub>2</sub>. Nat. Nanotechnol. 9, 851–857 (2014).

- Jones, A. M. et al. Spin-layer locking effects in optical orientation of exciton spin in bilayer WSe<sub>2</sub>. *Nat. Phys.* **10**, 130–134 (2014).

- Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS<sub>2</sub> transistors. *Nat. Nanotechnol.* 6, 147–150 (2011).

- Kim, C. et al. Fermi level pinning at electrical metal contacts of monolayer molybdenum dichalcogenides. ACS Nano 11, 1588–1596 (2017).

- Gong, C., Colombo, L., Wallace, R. M. & Cho, K. The unusual mechanism of partial Fermi level pinning at metal–MoS<sub>2</sub> interfaces. *Nano Lett.* 14, 1714–1720 (2014).

- Ryder, C. R., Wood, J. D., Wells, S. A. & Hersam, M. C. Chemically tailoring semiconducting two-dimensional transition metal dichalcogenides and black phosphorus. ACS Nano 10, 3900–3917 (2016).

- Allain, A. & Kis, A. Electron and hole mobilities in single-layer WSe<sub>2</sub>. ACS Nano 8, 7180–7185 (2014).

- Zhou, C. et al. Carrier type control of WSe<sub>2</sub> field-effect transistors by thickness modulation and MoO<sub>3</sub> layer doping. *Adv. Funct. Mater.* 26, 4223–4230 (2016).

- Resta, G. V. et al. Polarity control in WSe<sub>2</sub> double-gate transistors. *Sci. Rep.* 6, 29448 (2016).

- Pradhan, N. R. et al. Hall and field-effect mobilities in few layered P-WSe<sub>2</sub> fieldeffect transistors. *Sci. Rep.* 5, 8979 (2015).

- Movva, H. C. P. et al. High-mobility holes in dual-gated WSe<sub>2</sub> field-effect transistors. ACS Nano 9, 10402–10410 (2015).

- Castellanos-Gomez, A. et al. Electric-field screening in atomically thin layers of MoS<sub>2</sub>: the role of interlayer coupling. *Adv. Mater.* 25, 899–903 (2013).

- Li, L. H. et al. Dielectric screening in atomically thin boron nitride nanosheets. Nano Lett. 15, 218–223 (2015).

- Mitioglu, A. A. et al. Optical investigation of monolayer and bulk tungsten diselenide (WSe<sub>2</sub>) in high magnetic fields. *Nano Lett.* **15**, 4387–4392 (2015).

- Schmidt, H., Giustiniano, F. & Eda, G. Electronic transport properties of transition metal dichalcogenide field-effect devices: surface and interface effects. *Chem. Soc. Rev.* 44, 7715–7736 (2015).

- Prakash, A. & Appenzeller, J. Bandgap extraction and device analysis of ionic liquid gated WSe<sub>2</sub> Schottky barrier transistors. ACS Nano 11, 1626–1632 (2017).

- Li, S.-L. et al. Thickness scaling effect on interfacial barrier and electrical contact to two-dimensional MoS<sub>2</sub> layers. ACS Nano 8, 12836–12842 (2014).

- Pudasaini, P. R. et al. High-performance multilayer WSe<sub>2</sub> field-effect transistors with carrier type control. *Nano Res.* **11**, 722–730 (2018).

- Liu, W. et al. Role of metal contacts in designing high-performance monolayer N-type WSe<sub>2</sub> field effect transistors. *Nano Lett.* **13**, 1983–1990 (2013).

- Radisavljevic, B. & Kis, A. Mobility engineering and a metal-insulator transition in monolayer MoS<sub>2</sub>. *Nat. Mater.* 12, 815–820 (2013).

- Hibino, H., Tanabe, S., Mizuno, S. & Kageshima, H. Growth and electronic transport properties of epitaxial graphene on SiC. J. Phys. D Appl. Phys. 45, 154008 (2012).

- Chuang, H.-J. et al. High mobility WSe<sub>2</sub> P- and N-type field-effect transistors contacted by highly doped graphene for low-resistance contacts. *Nano Lett.* 14, 3594–3601 (2014).

- Pudasaini, P. R. et al. High performance top-gated multilayer WSe<sub>2</sub> field effect transistors. *Nanotechnology* 28, 475202 (2017).

- McDonnell, S., Smyth, C., Hinkle, C. L. & Wallace, R. M. MoS<sub>2</sub>--titanium contact interface reactions. ACS Appl. Mater. Interfaces 8, 8289–8294 (2016).

- Chow, W. L. et al. High mobility 2D palladium diselenide field-effect transistors with tunable ambipolar characteristics. *Adv. Mater.* 29, 1602969 (2017).

- Wang, Z. et al. Synthesis of nitrogen-doped graphene by chemical vapour deposition using melamine as the sole solid source of carbon and nitrogen. J. Mater. Chem. C 2, 7396–7401 (2014).

- Yu, Y.-J. et al. Tuning the graphene work function by electric field effect. Nano Lett. 9, 3430–3434 (2009).

- Hansen, W. N. & Johnson, K. B. Work function measurements in gas ambient. Surf. Sci. 316, 373–382 (1994).

- Wang, Y. et al. Gold on graphene as a substrate for surface enhanced Raman scattering study. *Appl. Phys. Lett.* 97, 163111 (2010).

- Yang, X., Liu, G., Balandin, A. A. & Mohanram, K. Triple-mode singletransistor graphene amplifier and its applications. ACS Nano 4, 5532–5538 (2010).

- Lin, Y.-F. et al. Ambipolar MoTe<sub>2</sub> transistors and their applications in logic circuits. Adv. Mater. 26, 3263–3269 (2014).