Received 27 November 2018; revised 15 February 2019; accepted 18 February 2019. Date of publication 25 February 2019; date of current version 8 March 2019.

The review of this paper was arranged by Editor N. Collaert.

Digital Object Identifier 10.1109/JEDS.2019.2901298

# The Effect of Tungsten Volume on Residual Stress and Cell Characteristics in MONOS

YOUNG-TAEK OH<sup>®</sup> <sup>1</sup>, JAE-MIN SIM<sup>1</sup>, HISASHI KINO<sup>®</sup> <sup>2</sup> (Member, IEEE), DEOK-KEE KIM<sup>3</sup>, TETSU TANAKA<sup>4</sup> (Member, IEEE), AND YUN-HEUB SONG<sup>®</sup> <sup>1</sup> (Member, IEEE)

1 Department of Electronic Engineering, Hanyang University, Seoul 04763, South Korea 2 Frontier Research Institute for Interdisciplinary Sciences, Tohoku University, Sendai 980-8579, Japan 3 Department of Electrical Engineering, Sejong University, Seoul 05006, South Korea 4 Department of Biomedical Engineering, Tohoku University, Sendai 980-8579, Japan

CORRESPONDING AUTHOR: Y.-H. SONG (e-mail: yhsong2008@hanyang.ac.kr)

This work was supported in part by the Nano Material Technology Development Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT and Future Planning under Grant NRF-2016M3A7B4910398, and in part by the Samsung Electronics' University Research and Development Program.

**ABSTRACT** The effect of residual stress during the tungsten deposition process were investigated using metal—oxide—nitride—oxide—semiconductor (MONOS) devices. The variation of residual stress due to tungsten volume was measured under tensile and compressive stress conditions. Residual stress increased in proportion to the deposition volume. Stress influenced the Si/SiO<sub>2</sub> interface and caused deterioration of the electrical properties, which was experimentally observed during measurements of the interface trap densities and memory windows. We confirmed that residual stress led to degradation of the cell characteristics of MONOS devices, and the absolute value of stress significantly affected these issues regardless of the polarity. From our experiments results, we can predict the degradation of cell characteristics in memory devices, and confirm the need for appropriate stress control in manufacturing process.

**INDEX TERMS** Residual stress, tungsten volume, curvature method, interface trap densities, MONOS structure.

#### I. INTRODUCTION

Three dimensional (3D) NAND architecture has become mainstream in NAND flash memory markets, producing better reliability, bit-density, and cost effectiveness than comparable technologies [1]-[3]. Manufacturers are massproducing 3D NAND flash memories through bit-cost scalable (BiCS) and terabit cell array transistor (TCAT) technologies [2], [3]. However, to meet the explosive demands for data storage, residual stress issues must be resolved, which are caused by mismatches between heterogeneous materials or thermal and mechanical loads encountered during fabrication. Residual stresses can further result in stack deformation, substrate distortion, and even cracking of the film or substrate [4], [5]. In this respect, 3D NAND technologies utilizing vertically stacked memory cells, to increase bit density, were more vulnerable to stress issues [5]–[7]. Specifically, the increased metal gate volume greatly influences the residual stress in the device by contributing to wafer bending, which therefore degrades the

uniform depth of focus (DOF) required in the lithography process [1], [6], [7]. In additions, residual stress also enhances the non-uniformity in physical parameters, which is one of the causes of deterioration of device performance and reliability [4], [8]. Therefore, appropriate control of residual stress development through process condition control or structure optimization is necessary to obtain better cell characteristics. With respect to these issues, only a few studies have been undertaken.

In this work, we investigated the development of residual stress as a function of processing condition. The residual stress values were extracted using a wafer curvature method. The metal-oxide-nitride-oxide-semiconductor (MONOS) capacitor was chosen for measuring electrical properties. The memory window, gate leakage, and interface state were checked, which verified the effects of residual stress on device characteristics. From there, we provided a method based on process conditions for minimizing the influence of residual stresses on cell characteristics.

#### II. EXPERIMENTAL

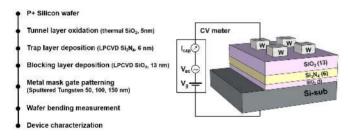

The process steps to produce the MONOS structure are shown in Fig. 1. A two-inch-diameter p-type (100) silicon wafer was prepared as a substrate, and a 5-nm-thick tunneling oxide was grown by thermal dry oxidation at 900 °C. Then, a 6-nm-thick silicon nitride trap layer was formed by low-pressure chemical vapor deposition (LPCVD) at 800 °C, followed by a 13-nm-thick LPCVD blocking oxide at 700 °C. Measurement of the deposited film thickness and wafer bending were checked with an ellipsometer (UVISEL Plus; Horiba, Longiumeau, France) and stylus surface profiler (Surfcorder ET200; Kosaka Laboratory Ltd., Tokyo, Japan), respectively. The tungsten film was formed in an ultra-high vacuum sputter system, with an operation vacuum level of  $1 \times 10^{-5}$  Pa and a 100 W RF power source. The substrate temperature was kept constant at room temperature, and Ar was used as the working gas. Meanwhile, to minimize the effects of thermal and mechanical loads on the etching process required for gate formation, metal mask patterning was performed, and the post-annealing was omitted. Through this process, we enhanced the accuracy of our analysis, excluding other causes that affect wafer bending. For evaluation of effect of stress, the main cell characteristics, including capacitance-voltage (CV) and current-voltage (IV) tests was conducted using a Keithley 4200-SCS semiconductor parameter analyzer (Keithley Instruments Inc., Cleveland, Oh, USA) and a HP 4284 LCR meter.

FIGURE 1. Key process steps and conditions for fabricating the MONOS device with varying gate thickness.

# **III. RESULTS AND DISCUSSION**

#### A. RESIDUAL STRESS EXTRACTION

When an external force over the critical point is applied to the device due to thermal or mechanical factors, exerted force remains as a residual stress and causes irreversible deformation [9]. At the wafer level, the stress generated during the thin film deposition process leads to structural deformation, known as warpage, which can be divided into tension (positive sign) and compression (negative sign) depending on the deformed shape. The film under tension will try to contract, and in response, the substrate is deformed into a concave shape. If the film has compression force, the film will try to expand, and convex shape was occurred [9], [10]. Such deformation (residual stress) can be determined numerically by the Stoney equation, which is expressed as a function of wafer curvature and elastic

parameters. The wafer curvature before and after deposition was measured. Then, the value of residual stress was calculated using the Stoney formula as follows:

$$\sigma_f = \frac{E_s}{6(1 - \nu_s)} \cdot \frac{d_s^2}{d_f} \cdot \left(\frac{1}{R_{post}} - \frac{1}{R_{pre}}\right),\tag{1}$$

where  $\sigma_f$  is the total residual stress in n stacked films,  $E_s$  and  $\nu_s$  are the Young's modulus and Poisson ratio of the substrate, respectively,  $d_s$  and  $d_f$  are the substrate thickness and film thickness (assuming  $d_f << d_s$ ), respectively, and  $R_{pre}$  and  $R_{post}$  are the radii of curvature of the substrate before and after deposition, respectively [9]. This Stoney equation can be applied to a single thin film. In a multi-layer such as oxide/nitride/oxide (O/N/O) dielectric, the superposition principle form of the Stoney equation can be used. The total residual stress in the n-stacked multi-layer was:

$$\sigma_{total} = \frac{E_s d_s^2}{6(1 - \nu_s)} \cdot \frac{1}{\sum_{i=1}^n d_{fi}} \cdot \sum_{i=1}^n \left( \frac{1}{R_{i,post}} - \frac{1}{R_{i,pre}} \right). \tag{2}$$

We calculated the value of residual stress of a single thin film and a multi-layer structure from these equations, and the detailed elastic parameters used in this study can be found in Table 1.

TABLE 1. Mechanical parameters for stress analysis.

| Material        | Young's modulus<br>[GPa] | Poisson ratio |

|-----------------|--------------------------|---------------|

| Silicon (100)   | 130                      | 0.28          |

| Silicon Oxide   | 70                       | 0.2           |

| Silicon Nitride | 270                      | 0.27          |

| Tungsten        | 410                      | 0.28          |

GPa = giga Pascal

## B. STRESS WITH VARIABLE AR PRESSURE

It is known that metal film with its large elastic modulus can be severely affected to mechanical stress, and that the stress properties may change depending on process conditions such as method of growth, temperature, and working gas conditions [11], [12].

Since the stress control is possible by changing the process conditions, it is necessary to evaluate the stress pattern according to the effect of tungsten volume in both stress conditions (tensile, compressive) for comprehensive analysis. Therefore, we checked the tensile and compressive stress conditions through the changing of working gas pressure, and then investigated the effect of tungsten volume on stress and cell characteristics under both stress conditions.

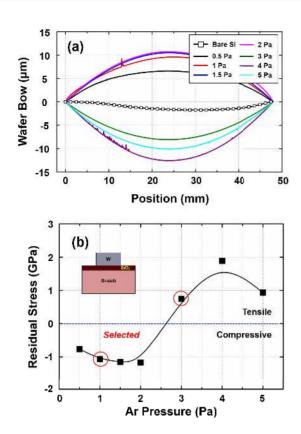

First, we calculated the residual stress of a tungsten thin film on a bare wafer to assess the properties of tungsten stress under different working gas pressures. The deposition thickness of the tungsten film was selected to be 100 nm, and the Ar pressure was varied from 0.5 to 5 Pa. Fig. 2(a) shows the wafer bow profiles utilized for the calculation of residual stresses, and the values of the residual stresses extracted from the Stoney formula can be found in Fig. 2(b). The

VOLUME 7, 2019 383

FIGURE 2. (a) Wafer bow profile for bare Si and tungsten thin film under different Ar pressure (0.5  $\sim$  5 Pa) conditions, and (b) the value of residual stress calculated from the Stoney equation. The 1 and 3 Pa Ar pressure conditions were selected as a representative condition values for each stress polarity.

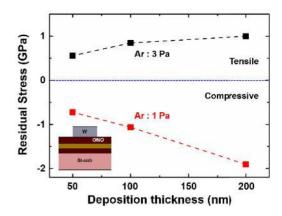

wafer bending occurs from the tungsten process draw the convex (compressive) shape in lower Ar pressure conditions, then it becomes concave (tensile) shape as the Ar pressure increases. This residual stress distribution indicates the same tendency as in previous reports and was due to a difference in momentum based on the collision probability between target atom (W) and gas molecules (Ar) [12], [13]. Utilizing this distribution, we analyzed the residual stress as a function of the change in tungsten volume under both tensile and compressive stresses, respectively. Here, 1 and 3 Pa conditions were selected as the representative values of stress polarity, and 50, 100, and 200 nm thick tungsten films were deposited with MONOS structure, as shown in Fig. 3. As deposition thickness increased, residual stress gradually increased for both tensile and compressive conditions, though the compressive stress variation with thickness was larger. Generally, the stress reached the plastic regions, the film proceeds the relaxation step through the cracking (tensile) or bucking (compressive), and maintains the maximum value of stress [9]. Thus, a distinctly different value of residual stress in 200 nm thick conditions can be regarded as the plastic point difference according to the stress polarity. Consequently, the residual stress induced on a substrate increased as the deposited film volume increased regardless of stress polarity.

FIGURE 3. Residual stress for MONOS capacitor under different Ar pressures (1, 3 Pa) and tungsten deposition thickness (50, 100, 200 nm) conditions.

# C. RELATIONSHIP BETWEEN STRESS AND INTERFACE STATE

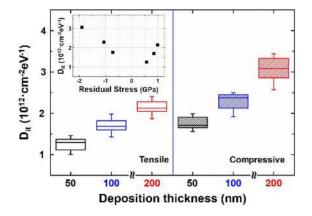

To evaluate the effect of residual stress on cell characteristics, it is necessary to consider the effect of mechanical stress on the silicon/silicon-oxide (Si/SiO<sub>2</sub>) interface state. Mechanical stress influences silicon-hydrogen bonding at the Si/SiO<sub>2</sub> interface, which changes the interface state. Normally, silicon is passivated by hydrogen molecules, which maintain a stable state. However, mechanical stress during fabrication breaks the silicon-hydrogen bonds, resulting in an unstable condition involving hydrogen desorption from the silicon molecule. Thus, dangling bonds formed where the hydrogen was removed, resulting in a trap site [14]. Finally, the interface traps increased, increasing the interface trap density (Dit) at the Si/SiO2 interface. The effect of mechanical stress on Si-H bonding has already been studied with Pb0, Pb1, and Dimer models, which considered degradation of the interface state and reliability [15], [16]. This phenomenon also occurs irrespective of the stress characteristics and the impact of them is known to be stronger under compressive stress conditions [16]. Thus, assessing the Si/SiO<sub>2</sub> interface could be an effective way to confirm the effect of residual stress on cell characteristics. We measured the value of Dit using a conductance method to assess the interface state for different stress conditions. The conductance method is considered to be an effective method for determining Dit, as it measures equivalent parallel conductance as a function of gate bias and frequency [17]. Fig. 4 shows a box plot of Dit at the midgap of 10 samples obtained using the conductance method under different stress conditions. The value of Dit of the 50-nmthick samples was less affected by deposition volume and had the smallest value among the other samples. The Dit values of the other samples gradually increased as deposition thickness increased. This tendency was observed irrespective of the stress polarity. At maximum conditions, the average  $D_{it}$  values were  $2.15 \times 10^{12}$  and  $3.07 \times 10^{12}$  eV<sup>-1</sup>cm<sup>-2</sup> for tensile and compressive stresses, respectively. In other words, the value of Dit is significantly changed by the value

384 VOLUME 7, 2019

of stress that arise from tungsten volume. In particular, the absolute value of stress has affected the value of  $D_{it}$  regardless of polarity and is supported by the results under both side conditions produced by Ar pressure control.

FIGURE 4. Interface trap densities of MONOS capacitor under different Ar pressure and tungsten deposition thickness conditions. Inset figure represents the interface trap densities as a function of residual stress under each condition.

### D. INFLUENCE ON RELIABILITY

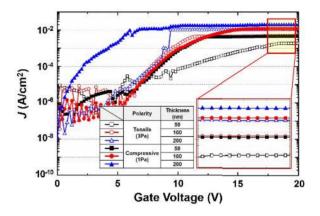

Checking the leakage characteristics has been considered as an effective way to evaluate the reliability of semiconductor devices. In metal-oxide-semiconductor (MOS) device, the increasing of gate leakage current represents the degradation of the dielectric quality, which can be a numerical parameter to indicate the device reliability. To confirm the correlation between cell reliability and Dit caused by the residual stress, we measured the gate leakage current in each condition. Fig. 5 shows the leakage current density versus gate voltage (J-V) curves in a sample for various tensile and compressive stress conditions. The J-V curve was obtained by sweeping the voltage from 0 to 20 V at a 0.1 V sweep rate. As the applied electric field becomes stronger, leakage current density increases, and saturation occurs above a certain voltage. We can determine that cells with high value of leakage current density and lower saturation points are more degraded from a reliability perspective. Meanwhile, the value of leakage current densities and saturation points exhibited significant differences depending on the stress conditions. The 50-nm-thick sample with tensile stress had the lowest Dit value with an 18 V saturation point and a  $7.51 \times 10^{-5}$  A/cm<sup>2</sup> leakage current density. However, the 200-nm-thick compressive sample with a high value of Dit showed severely degraded values of 6 V and  $7.78 \times 10^{-4}$  A/cm<sup>2</sup>, respectively. In other words, the saturation point and leakage current density (which represents cell reliability) deteriorated as Dit increased, and the distortion became stronger under compressive stress conditions compared to tensile. It is known that as the high tensile stress applied to the oxide in the MOS structure, then the bandgap narrowing, and reduction of effective thickness deteriorated

the breakdown characteristics [18], [19]. However, the reason for this difference in leakage characteristics for various stress conditions in our experiments can be considered the generation of current at the interface ( $J_{sg}$ ) and trap-assisted tunneling (TAT) [16], [20]. The current model describing the transfer mechanism in the dielectric film,  $J_{sg}$ , is the sum of electrons and holes transported through surface states, which was proportionally related to  $D_{it}$ . That's why the leakage characteristics degraded under high  $D_{it}$  conditions. In addition, TAT through a dielectric was one of the other factors that deteriorated the reliability. Thus, the tendency of  $D_{it}$  in Fig. 4 and that of the leakage characteristics in Fig. 5 were the same, and the control of residual stress and  $D_{it}$  should be ensured to preserve dielectric film quality.

FIGURE 5. The leakage current density versus gate voltage curves of the MONOS capacitor under each condition. Inset figure represents the leakage current densities at high gate voltage region.

#### E. IMPACT OF STRESS ON MEMORY CHARACTERISTICS

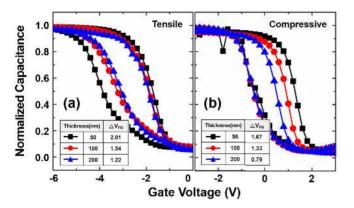

We performed CV tests to investigate the impact of stress and the interface traps generated by stress on the memory characteristics of MONOS devices. Fig. 6(a) and 6(b) display the normalized CV hysteresis for the MONOS capacitor; the measurement was performed by bidirectionally sweeping from -18 and 18V and back. The AC signal frequency and voltage sweep rate were set to 1 MHz and 0.2 V·s<sup>-1</sup>, respectively. All CV curves showed the typical accumulationdeletion-inversion properties, and the shift in flat band  $(\Delta V_{FB})$  was featured due to the trapped charge in the silicon nitride. However, our samples displayed low window memory in spite of the wide voltage sweep range. This phenomenon can be explained by the absence of post-annealing, which is effective method to eliminate the local traps and defects in dielectric layers. In addition, the difference in V<sub>FB</sub> according to stress conditions arise from difference in metal work function which may vary with chamber conditions [21]. Despite these unexpected experimental obstacles, the variation of cell characteristics with stress was confirmed. Tensile and compressive stresses showed similar effects in the CV measurement. The value of the memory window originating from the shift in

VOLUME 7, 2019 385

$V_{FB}$  was slightly larger for small stress (lower tungsten volume) conditions regardless of stress polarity, and their values gradually decreased as the residual stress increased. Considering that difference, the average memory windows of 10 samples were measured as indicated in the inset table of Fig. 6(a), and (b). As mentioned above, the highest value of  $\Delta V_{FB}$  was observed in the lower stress conditions, and their values gradually decreased as the residual stress increased for tensile or compressive stress. This shows that the memory function is considerably deteriorated under high stress conditions, and is proportional to the absolute values, regardless of stress polarity.

FIGURE 6. The normalized capacitance-voltage curves of MONOS capacitor under (a) tensile and (b) compressive stress condition. Inset table shows the memory window under each condition.

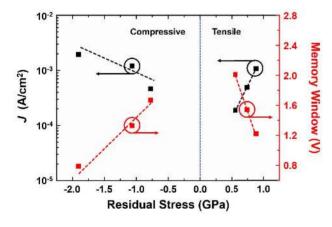

FIGURE 7. Variation of electrical properties (leakage current density and memory window) as a function of residual stress.

# F. SUMMARY

Fig. 7 presents the electrical properties, including memory windows and leakage current densities, as a function of residual stress for each condition. The blue line implies the neutral value as the starting point, the left side represents the compressive stress, and the right side represents the tensile stress condition. As the distance from the blue line (stress-free) increases in the tensile or compressive directions, the deterioration of cell characteristics is intensified, observed as the

degradation of memory window and leakage characteristics. This result proves that deterioration of cell characteristics can be prevented by minimizing residual stresses.

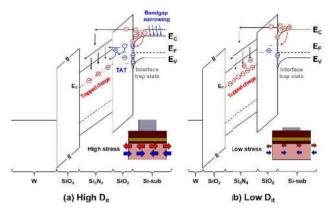

In addition, band diagram expression during charge trap operation can be helpful for understanding the experimental results, as shown in Figs. 8(a), (b). The band diagram with high D<sub>it</sub> (Fig. 8(a)) illustrates a condition with a thick tungsten gate, whereas that with a low Dit (Fig. 8(b)) represented the opposite condition. When the applied gate bias was high enough to cause Fowler-Nordheim (FN) tunneling, the charge carrier was trapped by a silicon nitride trap level. However, for a high cell Dit induced by stress, the electrons in the silicon substrate were unexpectedly caught at the interface trap site. The number of carriers reaching the trap layer was reduced, resulting in a drop in trapped charge density at the same operating conditions. In addition, it is expected that the silicon conduction band split into  $\Delta_2$  and  $\Delta_4$  valleys due to large stress will impart the reduction of conduction band energy and bandgap narrowing, resulting in the decreasing of tunneling efficiency from silicon substrate to silicon nitride trap layer [19]. Therefore, trapped charge density was reduced in high residual stress conditions, which was verified by the CV test, as can be seen in Figs. 6(a) and 6(b).

FIGURE 8. MONOS structure energy band diagram for charge trap operation with (a) high- and (b) low-stress conditions.

#### **IV. CONCLUSION**

In this paper, the effect of residual stress on the cell characteristics was investigated using a MONOS devices. We experimentally revealed that residual stress increased as the thickness of the tungsten film increases, regardless of stress property. From analyzing the Si/SiO<sub>2</sub> interface, it is confirmed that residual stress degrade the cell characteristics occurred as a result of increased interface trap density. Based on these results, we concluded that residual stress is a critical factor in cell characteristic deterioration, and the absolute value of residual stress is significantly affected by these issues regardless of stress polarity. Our results highlight the importance of stress control through physical parameter regulation to prevent the degradation of cell characteristics in memory device.

386 VOLUME 7, 2019

#### **ACKNOWLEDGMENT**

The authors would like to thank Dr. Jaegoo Lee and Dr. Junhee Lim at the Memory R&D Center, Memory Division, Samsung Electronics Co. Ltd., Hwaseong, South Korea, for their technical advice and feedback with regard to this study.

#### **REFERENCES**

- J. Lee et al., "A new ruler on the storage market: 3D-NAND flash for high-density memory and its technology evolutions and challenges on the future," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2016, pp. 11.2.1–11.2.4. doi: 10.1109/IEDM.2016.7838394.

- [2] H. Tanaka et al., "Bit cost scalable technology with punch and plug process for ultra high density flash memory," in Proc. Symp. VLSI Technol., Kyoto, Japan, Jun. 2007, pp. 14–15. doi: 10.1109/VLSIT.2007.4339708.

- [3] J. Jang et al., "Vertical cell array using TCAT (Terabit cell array transistor) technology for ultra high density NAND flash memory," in Proc. Symp. VLSI Technol., Honolulu, HI, USA, Jun. 2009, pp. 192–193.

- [4] S.-H. Lee, "Technology scaling challenges and opportunities of memory devices," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2016, pp. 1.1.1–1.1.8. doi: 10.1109/IEDM.2016.7838026.

- [5] N. Chandrasekaran, "Challenges in 3D memory manufacturing and process integration," in *IEDM Tech. Dig.*, Washington, DC, USA, Dec. 2013, pp. 13.1.1–13.1.5. doi: 10.1109/IEDM.2013.6724621.

- [6] W.-Y. Jung et al., "How to minimize CD variation and overlay degradation induced by film stress," in Proc. SPIE Adv. Lithography, San Jose, CA, USA, Apr. 2012, pp. 1–8. doi: 10.1117/12.916035.

- [7] C. Huang, M. Yang, E. Yang, T. H. Yang, and K. C. Chen, "Within-wafer CD variation induced by wafer shape," in *Proc. SPIE Adv. Lithography*, San Jose, CA, USA, Mar. 2016, pp. 1–9. doi: 10.1117/12.2216048.

- [8] Y. Nakano, T. Nomura, and T. Takenaka, "Residual stress of multilayer ceramic capacitors with Ni-electrodes (Ni-MLCCs)," *Jpn. J. Appl. Phys.*, vol. 42, no. 9B, pp. 6041–6044, Sep. 2003. doi: 10.1143/JJAP.42.6041.

- [9] J. Laconte, D. Flandre, and J.-P. Raskin, "Thin dielectric films stress extraction," in *Micromachined Thin-Film Sensors for SOI-CMOS Co-Integration*. Dordrecht, The Netherlands: Springer, 2006, pp. 47–103.

- [10] D. M. Mattox, Atomistic Film Growth and Resulting Film Properties: Residual Film Stress, Vac. Technol. Coating, Weston, CT, USA, Nov. 2001, pp. 22–23.

- [11] H. Windischmann, "Intrinsic stress in sputter-deposited thin films," Crit. Rev. Solid-State Mater. Sci., vol. 17, no. 6, pp. 547–596, Jan. 1992. doi: 10.1080/10408439208244586.

- [12] J. L. Perry, "Effect of sputter deposition parameters on stress in tantalum films with applications to chemical mechanical planarization of copper," M.S. thesis, Dept. Microelectron. Eng., Rochester Inst. Technol., Rochester, NY, USA, 2004.

- [13] G. F. Iriarte, J. G. Rodriguez, and F. Calle, "Effect of substrate-target distance and sputtering pressure in the synthesis of AlN thin films," *Microsyst. Technol.*, vol. 17, no. 3, pp. 381–386, Jan. 2011. doi: 10.1007/s00542-010-1198-2.

- [14] B. Tuttle and C. G. Van de Walle, "Structure, energetics, and vibrational properties of Si-H bond dissociation in silicon," *Phys. Rev. B, Condens. Matter*, vol. 59, no. 20, pp. 12884–12889, May 1999. doi: 10.1103/PhysRevB.59.12884.

- [15] A. Toda et al., "Impact of mechanical stress on interface trap generation in flash EEPROMs," in Proc. IEEE Int. Rel. Phys. Symp., San Jose, CA, USA, Apr. 2005, pp. 250–256. doi: 10.1109/RELPHY.2005.1493093.

- [16] Y. S. Choi, T. Nishida, and S. E. Thompson, "Impact of mechanical stress on direct and trap-assisted gate leakage currents in *p*-type silicon metal-oxide-semiconductor capacitors," *Appl. Phys. Lett.*, vol. 92, no. 17, pp. 1–3, Apr. 2008. doi: 10.1063/1.2917717.

- [17] D. K. Schroder, "Oxide and interface trapped charges, oxide thickness," in *Semiconductor Material and Device Characterization*, 3rd ed. Hoboken, NJ, USA: Wiley, 2006, pp. 347–350.

- [18] S. Jeffery, C. J. Sofield, and J. B. Pethica, "The influence of mechanical stress on the dielectric breakdown field strength of thin SiO<sub>2</sub> films," *Appl. Phys. Lett.*, vol. 73, no. 2, pp. 172–174, Jul. 1998. doi: 10.1063/1.121745.

- [19] Y. Sun, S. E. Thompson, and T. Nishida, "Physics of strain effects in semiconductors and metal-oxide-semiconductor field-effect transistors," *J. Appl. Phys.*, vol. 101, no. 10, pp. 1–22, May 2007. doi: 10.1063/1.2730561.

- [20] C.-C. Hong and J.-G. Hwu, "Degradation in metal-oxide-semiconductor structure with ultrathin gate oxide due to external compressive stress," *Appl. Phys. Lett.*, vol. 79, no. 23, pp. 3797–3799, Dec. 2001. doi: 10.1063/1.1420491.

- [21] S. A. Vitale, J. Kedzierski, P. Healey, P. W. Wyatt, and C. L. Keast, "Work-function-tuned TiN metal gate FDSOI transistors for subthreshold operation," *IEEE Trans. Electron Devices*, vol. 58, no. 2, pp. 419–426, Feb. 2011. doi: 10.1109/TED.2010.2092779.

**YOUNG-TAEK OH** received the B.S. degree in electrical computer engineering from the University of Seoul, South Korea, in 2014. He is currently pursuing the M.S. and Ph.D. degrees with Hanyang University, Seoul. His current research interests include 3-D NAND flash memory devices and mechanical stress.

**JAE-MIN SIM** received the B.S. degree in electronics engineering from the Korea National University of Transportation, Chungju, South Korea, in 2018. He is currently pursuing the M.S. and Ph.D. degrees with Hanyang University, Seoul, South Korea. His current research interests include 3-D NAND flash memory devices and 3-D simulation.

**HISASHI KINO** (M'13) received the Ph.D. degree in bioengineering and robotics from Tohoku University, Sendai, Japan, in 2012, where he is currently an Assistant Professor with the Frontier Research Institute for Interdisciplinary Sciences.

**DEOK-KEE KIM** received the B.S. degree in materials science and engineering from Seoul National University in 1993, and the Ph.D. degree in materials science and engineering from Stanford University in 2001. He was with IBM microelectronics, NY, USA, where he was involved in eDRAM integration and silicide eFUSE. He was with Samsung Electronics from 2007 to 2011, where he researched on metallic eFUSE, 3-D ReRAM, and silicon solar cells for mobile applications. Since 2011, he has been a Professor with the Electrical Engineering Department, Sejong University, Seoul, South Korea. His research interests include atomic switch for power application, reliability and characterization of oxide-based semiconductor devices, transparent electrodes for OSC, characterization of InGaAs-based devices and nano-scale material property, and stress and device performance interesticing.

**TETSU TANAKA** (M'90) received the B.S. and M.S. degrees in electronics engineering and the Ph.D. degree in machine intelligence and systems engineering from Tohoku University, Sendai, Japan, in 1987, 1990, and 2003, respectively.

In 2005, he joined Tohoku University as an Associate Professor, where he became a Professor with the Graduate School of Biomedical Engineering in 2008.

YUN-HEUB SONG (M'08) received the M.S. degree in electronic engineering from Hanyang University, Seoul, South Korea, in 1992, and the Ph.D. degree in intelligent mechanical engineering from Tohoku University, Sendai, Japan, in 1999. He is currently a Professor of electronic engineering with Hanyang University. He has researched semiconductor devices and circuit design for over 30 years in the Semiconductor Research and Development Center, Samsung Electronics Company, and Hanyang University. When he was working with Samsung, he was responsible for the device and product development of flash memory as the Vice-President, and developed 256 Mb and 512 Mb NOR flash memory from 2000 to 2003. After moving to Hanyang University in 2008, where he served as the Vice Dean of the College of Engineering, engaging in extensive international collaboration research and planning on industrial projects from 2011 to 2013. His research interests include device reliability modeling, device characterization, novel device structures and architectures for memory and logic applications, circuit design and algorithms for low-power, high-speed processing, and sensor systems based on semiconductor technology.

VOLUME 7, 2019 387