# The Effects of AlN and Copper Back Side Deposition on the Performance of Etched Back GaN/Si HEMTs

Georges Pavlidis, Samuel Kim, Idriss Abid, Malek Zegaoui, F Medjdoub, Samuel Graham

## ▶ To cite this version:

Georges Pavlidis, Samuel Kim, Idriss Abid, Malek Zegaoui, F Medjdoub, et al.. The Effects of AlN and Copper Back Side Deposition on the Performance of Etched Back GaN/Si HEMTs. IEEE Electron Device Letters, Institute of Electrical and Electronics Engineers, 2019, 40 (7), pp.1060-1063. 10.1109/LED.2019.2915984. hal-02356736

# HAL Id: hal-02356736 https://hal.archives-ouvertes.fr/hal-02356736

Submitted on 2 Dec 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# The Effects of AIN and Copper Back Side Deposition on the Performance of Etched Back GaN/Si HEMTs

Georges Pavlidis, Member, Samuel H. Kim, Idriss Abid, Malek Zegaoui, Farid Medjdoub, and Samuel Graham, Senior Member

Abstract—The breakdown voltage of GaN/Si high electron mobility transistors (HEMTs) electronics has shown to be improved by removing the silicon substrate. The drawback to this approach is the increase in the device's thermal resistance which limits the power dissipation that the device can achieve before severe degradation. This study shows the ability to improve the thermal dissipation of these devices by depositing Copper (Cu) below Aluminum Nitride (AIN) filled etched back GaN-on-Si HEMTs. The device's channel temperature is measured via Raman thermometry. The device's transient thermal dynamics is investigated via transient thermoreflectance imaging and the temperature profile across the gate metal is monitored. In addition to the device's thermal properties, residual stress analysis of the GaN channel is performed via photoluminescence. A notable decrease in the tensile residual stress is observed with the removal of the substrate and the addition of the AIN and Cu layers. Overall, the backside copper is shown to decrease the gate temperature of the etched backed AIN filled devices while maintaining a high breakdown voltage.

Index Terms— AlGaN/GaN HEMTs, self-heating, transient, Thermal Characterization, Temperature

### I. INTRODUCTION

The ability to fabricate AlGan/Gan high electron mobility transistors (HEMTs) on silicon (Si) substrates has the potential to reduce the cost of Gan HEMT power electronics [1]. For high voltage operation, large electric fields are developed across the channel making it necessary to maintain high off-state breakdown voltages with large electron densities [2], [3]. Since the electric field extends below the epi layer, the use of a Si substrate in the high electric field region limits the device's capabilities due to its weak electrical field strength [4]. To overcome this obstacle, the removal of the Si substrate has shown to increase the device's breakdown voltage up to 3000 V [5]–[7]. While removing the Si improves the device's electrical capabilities, the device's overall maximum power dissipation is limited due to excessive

Submitted paper for review.

I. Abid, M. Zegaoui, Farid Medjdoub are with CNRS-IEMN Villeneuve-d'Ascq, 59650 France

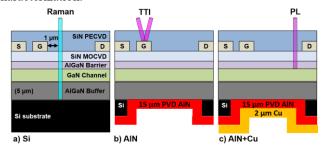

junction temperature rise [8], [9]. Recent progress to improve the performance of these etched back devices has been reported by applying backside metal processes using copper [10] or aluminum [11]. Prior to depositing copper, PVD AlN is deposited on the backside (Figure 1b) to enable higher blocking voltage capabilities as compared to the reference GaN-on-silicon devices [10]. Furthermore, the subsequent addition of 2 μm of Cu (Figure 1c) is shown to recover 85% of the maximum current density (in reference to a non-etched device) [10]. The origin of this improvement is predicted to be caused by the strong reduction in junction temperature. While the effects of these backside metal techniques on the thermal performance of etched back HEMTs has been numerically studied [12], experimental quantification has yet to be reported.

In this work, the thermal performance of etched back GaN/Si HEMTs with AlN/Cu filled trenches is assessed. To determine the effect of the additional layers, three different devices on the same wafer were prepared starting with GaN/Si HEMTs with an AlN nucleation layer and AlGaN buffer layer (shown in Figure 1). A detailed description of the processing can be found in [10]. Fabricating the devices on the same wafer reduced processing or epi variations during characterization.

Fig. 1. Stack configuration of a) GaN/Si HEMTs for power electronics with b) etched back substrate and AlN filled trench and c) further addition of Copper (Cu) backside metal deposition. The three experimental techniques employed in this study (Raman thermometry, Transient Thermoreflectance Imaging (TTI) and Photoluminescence (PL) for residual stress analysis) are depicted in the figure.

Steady state thermal analysis is conducted via Raman thermometry [13] to determine the reduction in junction temperatures caused by the addition of the Cu layer. The transient thermal dynamics of each device is also monitored by the gate metal temperature via Transient Thermoreflectance

G. Pavlidis, S. Kim and S. Graham are with The George W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology, Atlanta, GA 30332 USA (email: <a href="mailto:sgraham@gatech.edu">sgraham@gatech.edu</a>)

Imaging (TTI) [14].

In addition to assessing the device's thermal performance, the effect of the additional layers on the residual stress of the GaN channel is measured via Photoluminescence (PL) [15]. Previous studies have shown that the removal of the Si substrate can alter the residual stress in the GaN layer and ultimately impact the device performance [16]. Reducing the tensile residual stress in HEMTs can prevent the formation of large tensile strains during operation which can induce electrically active defects and mechanical damage [17].

#### II. STEADY STATE RAMAN THERMOMETRY

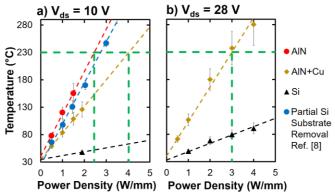

Using a 488 nm laser, Raman measurements were taken 1  $\mu$ m from the gate on the drain edge at the center of the gate width (shown in Figure 1a). The gate to drain spacing for the devices was 40  $\mu$ m. Since the GaN layer thicknesses did not change between the device structures, the two-peak method [13] was used to measure the volumetric averaged temperature rise across the GaN layer. Figure 2 shows the steady state thermal response of the devices under DC biasing for two different drain biases: 10 V and 28 V. The gate bias was adjusted to increase the power density.

Fig. 2. Comparison of device temperature measured via Raman thermometry at varying power densities for a constant drain bias of a) 10 V and b) 28 V. All measurements were taken at a constant plate temperature of 30  $^{\circ}\text{C}.$

Temperature measurements were taken at different power densities under a constant base plate temperature of 30 °C. To extrapolate the maximum power density achieved at a 200 °C temperature rise, linear regression was used. For the 10 V drain bias condition, the temperature rise is shown to decrease when transitioning from solely the AlN layer to the combination of AlN and copper. As expected, the Si device achieved a much lower junction temperature in comparison to the etched devices even after the addition of the AlN and the Copper layer.

For a constant drain bias of 10 V, a 11.6x and 7x reduction in maximum power density is observed for the AlN and AlN+Cu device respectively. Increasing the drain voltage to 28 V, the heating profile becomes more localized and the temperature measured via Raman at the gate edge becomes significantly higher [18]. The effect of this localization is confirmed when measuring the thermal performance of the AlN+Cu devices under 28 V bias (a 4.3x power reduction is estimated in contrast to an estimated 7x under 10 V drain bias).

Overall, the power reduction (proportional to the thermal

resistance) of the AlN device is shown to be greater than the power reduction reported in previous literature for a locally etched Si device without backside desposition [8] (the thermal performance of the locally etched Si device reported in [8] is plotted in Figure 2a). This increase in thermal resistance can be attributed to the full etching of the substrate below the device. In the previous scenario, the substrate was locally removed below the channel and thus resulted in a smaller increase in thermal resistance. Fully etching the substrate removes the possibility of the localized heating to be conducted via the substrate.

To compare the contribution of the thermal resistance associated with the AlN layer thickness to the overall thermal resistance, the thermal conductivity of the AlN must be measured. Time Domain Thermoreflectance (TDTR) [19] was thus used to measure the thermal conductivity of thin AlN films deposited using PVD. For thicknesses of 4-8  $\mu m$  of AlN, the thermal conductivity of AlN was measured to be 40-45 W/mK. Extracting the overall thermal resistance of the AlN device via Figure 2, the AlN layer thickness was estimated to contribute to 11% of the thermal resistance (the remainder of the contribution to the thermal resistance was predicted to be caused mainly by the thermal boundary resistance between the GaN and the AlN).

#### III. TRANSIENT THERMOREFLECTANCE IMAGING

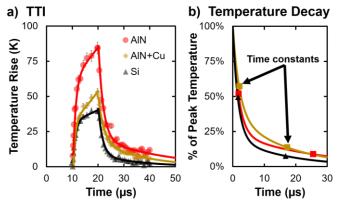

To benchmark the transient thermal performance of these devices, the temperature rise under pulsed biasing was estimated using TTI (Figure 3a). Overall, the presence of a thick SiN passivation layer made it difficult to assess the temperature distribution of the GaN channel [14]. Several LED excitation sources resulted in strong thermoreflectance signals from the GaN region but thin film interference effects caused non-uniformities in the signal [20] and resulted in large uncertainties due to low signal to noise ratios. The most consistent signal was found to be achieved from the gate metal when using a 365 nm LED source. The Cth was estimated via calibration [21] to be 1.034 x 10<sup>-4</sup> °C<sup>-1</sup>. To directly compare the transient thermal performance to the steady state Raman results, the devices were pulsed biased with a drain bias of 28 V for a 100 µs time period with a 10% duty cycle. The gate bias was adjusted for each device to match a peak current of

Fig. 3. a) Transient temperature profiles of gate metal measured via Transient Thermoreflectance Imaging (TTI) using a 365 nm LED source b) Comparison of temperature decay of gate metal when no power is dissipated. Markers indicate the time constants calculated when applying a second order exponential fitting to the temperature decays.

20 mA (5.6 W/mm). Performing a transient sweep of the three devices, the temperature rise and decay of each device can be plotted against each other (Figure 3a).

To capture the peak temperature of the device, the TTI measurements were averaged across 1 µm of the gate metal along the gate width at the center of the device. Similar to the steady state analysis, the AlN device resulted in the highest temperature rise (approximately double the temperature rise detected in the Si device). Regarding the devices' transient dynamics, second order exponential fittings were applied to each transient rise and decay curves. Since steady state conditions were not reached within the 10 µs pulse, the temperature decay fittings were used to extract time constants (Figure 3b). Due to the lower thermal spreading resistance, the silicon device is found to have the shortest time constants ( $\tau_{1,Si}$  $\approx 1.7 \text{ }\mu\text{s}$  and  $\tau_{2.\text{Si}} \approx 16.8 \text{ }\mu\text{s}$ ). Despite the AlN/Cu resulting in lower peak temperature than the AlN device, the AlN/Cu device's temperature is shown to decay slower than the AlN device within the first 20 µs. Moving beyond 20 µs, however, the AlN device is shown to decay slower than the AlN/Cu device and is calculated to have a larger time constant ( $\tau_{2,AIN} \approx$ 25.5 µs compared  $\tau_{2,AlN+Cu} \approx 17.3$  µs). This discrepancy suggests that there exists a higher thermal spreading resistance within the first few micrometers of the AlN/Cu device in comparison to the AlN device. While the higher resistance may impede the transient heat dissipation through the device, the overall temperature of the device is reduced by the addition of the Cu back metal layer.

#### IV. RESIDUAL STRESS ANALYSIS

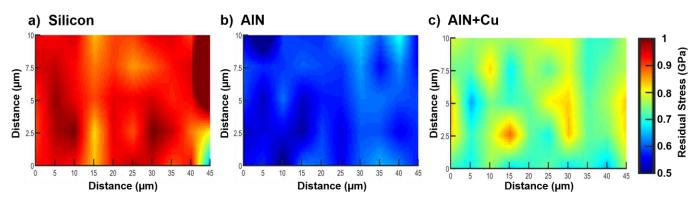

In addition to monitoring the device's thermal performance, the residual stress of the GaN layer was also measured via Photoluminescence (PL). Previous studies have shown that the residual stress in GaN is reduced when fully etching the Si substrate [8], [16]. To determine whether the addition of new materials would impact the stress relaxation, PL stress mappings were conducted across the channel between the gate and drain in 10  $\mu$ m steps along the gate width and 5  $\mu$ m steps across the channel (see Figure 4). The residual stress maps were measured using a Horiba Jobin Yvon LabRAM HR800 with a 325-nm laser as the excitation source. The reference for the band gap strain-free GaN which was used to predict the residual stress of the GaN layer was taken from [15].

The residual stress mappings for the three different devices

is plotted in Figure 4. As previously shown in literature [15], [22], the residual stress in GaN grown on Si is found to be tensile (in this study  $\approx 950$  MPa). The removal of the substrate and the addition of the PVD AlN layer demonstrates a reduction in tensile stress (580 MPa). This reduction in stress is beneficial for device reliability and highlights the ability to etch without "cracking" large area membranes for large industrial power devices. Measuring the stress distribution after the copper layer has been deposited, a slight increase in the overall average stress is observed (750 MPa).

#### V. CONCLUSION

Overall, the removal of Si substrate allows for higher breakdown voltages in the off state but prevents the excessive Joule heating during operation from being efficiently dissipated. In order to maintain a high electric field strength, the thermal performance of the etched Si can be improved by depositing a combination of materials such as AlN and Copper. The thermal profiles of these devices were assessed using steady state Raman thermometry and Transient Thermoreflectance Imaging (TTI) and the improved thermal performance by addition of these layers compared to the etched Si was quantified as a function of bias. Further residual stress analysis of the GaN channel was performed via Photoluminescence. The removal of the silicon substrate in combination with the deposition of the back layers was shown to reduce the overall tensile stress in the GaN. The relaxation of the GaN layer may potentially increase the device performance and reliability. Beyond improving the performance of lateral GaN HEMTs, the applications of these structures could also benefit the recent development of fully vertical GaN-on-Si devices with selective removal of the substrate and buffer layers [23].

#### **ACKNOWLEDGMENT**

Part of this work is supported by the French RENATECH network, the ANR and has received funding from the European Union's Horizon 2020 research and innovation program under grant agreement No 720527 (Inrel-NPower). The authors would also like to thank Dr. Luke Yates for performing TDTR measurements of the AlN samples.

Fig. 4. PL residual stress mappings of the a) GaN/Si HEMTs with b) etched back substrate and AlN filled trench and c) further addition of backside metal deposition of Copper. Stress mappings were performed between the gate and drain in 10 µm steps along the gate width and 2.5 µm steps across the channel.

## REFERENCES

- [1] H. Amano, Y. Baines, E. Beam, M. Borga, T. Bouchet, P. R. Chalker, M. Charles, K. J. Chen, N. Chowdhury, R. Chu, C. De Santi, M. M. De Souza, S. Decoutere, L. Di Cioccio, B. Eckardt, T. Egawa, P. Fay, J. J. Freedsman, L. Guido, O. Häberlen, G. Haynes, T. Heckel, D. Hemakumara, P. Houston, J. Hu, M. Hua, Q. Huang, A. Huang, S. Jiang, H. Kawai, D. Kinzer, M. Kuball, A. Kumar, K. Boon Lee, X. Li, D. Marcon, M. März, R. McCarthy, G. Meneghesso, M. Meneghini, E. Morvan, A. Nakajima, E. M. S. Narayanan, S. Oliver, T. Palacios, D. Piedra, M. Plissonnier, R. Reddy, M. Sun, I. Thayne, A. Torres, N. Trivellin, V. Unni, M. J. Uren, M. Van Hove, D. J. Wallis, J. Wang, J. Xie, S. Yagi, S. Yang, C. Youtsey, R. Yu, E. Zanoni, S. Zeltner and Y. Zhang, "The 2018 GaN power electronics roadmap," J. Phys. D. Appl. Phys., vol. 51, no. 16, p. 163001, 2018 https://doi.org/10.1088/1361-6463/aaaf9d

- [2]B. J. Baliga, "Power Semiconductor-Device Figure of Merit for High-Frequency Applications," IEEE Electron Device Lett., vol. 10, no. 10, pp. 455–457, 1989 <a href="https://doi.org/10.1109/55.43098">https://doi.org/10.1109/55.43098</a>

- [3]B. J. Baliga, "Gallium nitride devices for power electronic applications," Semicond. Sci. Technol., vol. 28, no. 7, p. 74011, 2013 https://doi.org/10.1088/0268-1242

- [4] P. Srivastava, J. Das, D. Visalli, J. Derluyn, M. Van Hove, P. E. Malinowski, D. Marcon, K. Geens, K. Cheng, S. Degroote, M. Leys, M. Germain, S. Decoutere, R. P. Mertens, and G. Borghs, "Silicon substrate removal of GaN DHFETs for enhanced (>1100 V) breakdown voltage," IEEE Electron Device Lett., vol. 31, no. 8, pp. 851–853, 2010 https://doi.org/10.1109/LED.2010.2050673

- [5]B. Lu and T. Palacios, "High Breakdown (>1500 V) AlGaN/GaN HEMTs by Substrate-Transfer Technology," IEEE Electron Device Lett., vol. 31, no. 9, pp. 951–953, 2010 <a href="https://doi.org/10.1109/LED.2010.2052587">https://doi.org/10.1109/LED.2010.2052587</a>

- [6]P. Srivastava, J. Das, D. Visalli, M. Van Hove, P. E. Malinowski, D. Marcon, S. Lenci, K. Geens, K. Cheng, M. Leys, S. Decoutere, R. P. Mertens, and G. Borghs, "Record Breakdown Voltage (2200 V) of GaN DHFETs on Si With 2-µm Buffer Thickness by Local Substrate Removal," IEEE Electron Device Lett., vol. 32, no. 1, pp. 30–32, Jan. 2011 <a href="https://doi.org/10.1109/LED.2010.2089493">https://doi.org/10.1109/LED.2010.2089493</a>

- [7] N. Herbecq, I. Roch-Jeune, N. Rolland, D. Visalli, J. Derluyn, S. Degroote, M. Germain, and F. Medjdoub, "1900V, 1.6mωcm2 AlN/GaN-on-Si power devices realized by local substrate removal," Appl. Phys. Express, vol. 7, no. 3, p. 034103, Mar. 2014 <a href="https://doi.org/10.7567/APEX.7.034103">https://doi.org/10.7567/APEX.7.034103</a>

- [8]G. Pavlidis, D. Mele, T. Cheng, F. Medjdoub, and S. Graham, "The thermal effects of substrate removal on GaN HEMTs using Raman Thermometry," in Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), 2016 15th IEEE Intersociety Conference on, 2016, pp. 1255–1260 https://doi.org/10.1109/ITHERM.2016.7517691

- [9] M. J. Tadjer, P. E. Raad, P. L. Komarov, K. D. Hobart, T. I. Feygelson, A. D. Koehler, T. J. Anderson, A. Nath, B. Pate, and F. J. Kub, "Electrothermal Evaluation of AlGaN/GaN Membrane High Electron Mobility Transistors by Transient Thermoreflectance," IEEE J. Electron Devices Soc., vol. 6, pp. 922–930, 2018 https://doi.org/10.1109/JEDS.2018.2860792

- [10] E. Dogmus, M. Zegaoui, and F. Medjdoub, "GaN-on-silicon high-electron-mobility transistor technology with ultra-low leakage up to 3000 V using local substrate removal and AlN ultra-wide bandgap," Appl. Phys. Express, vol. 11, no. 3, p. 034102, Mar. 2018 <a href="https://doi.org/10.7567/APEX.11.034102">https://doi.org/10.7567/APEX.11.034102</a>

- [11] K.-P. Hsueh, H.-Y. Wang, H.-C. Wang, H.-L. Kao, F.-T. Chien, C.-T. Chen, K.-J. Chang, and H.-C. Chiu, "Reliability Studies on AlGaN/GaN Metal-Insulator-Semiconductor High-Electron-Mobility Transistors with Through-Substrate via Technique and Backside Heat Sink Metal on Silicon-on-Insulator Substrates," ECS J. Solid State Sci. Technol., vol. 7, no. 8, pp. Q142–Q147, 2018 <a href="https://doi.org/10.1149/2.0201808jss">https://doi.org/10.1149/2.0201808jss</a>

- [12] Y.-H. Hwang, T.-S. Kang, F. Ren, and S. J. Pearton, "Novel approach to improve heat dissipation of AlGaN/GaN high electron mobility transistors with a Cu filled via under device active area," J. Vac. Sci. Technol. B, Nanotechnol. Microelectron. Mater. Process. Meas. Phenom., vol. 32, no. 6, p. 61202, 2014 <a href="https://doi.org/10.1116/1.4896593">https://doi.org/10.1116/1.4896593</a>

- [13] S. Choi, E. R. Heller, D. Dorsey, R. Vetury, and S. Graham, "Thermometry of AlGaN/GaN HEMTs using multispectral raman features," IEEE Trans. Electron Devices, vol. 60, no. 6, pp. 1898–1904, 2013 https://doi.org/10.1109/TED.2013.2255102

- [14] G. Pavlidis, E. R. Heller, D. Kendig, S. Graham, E. R. Heller, and S. Graham, "Transient thermal characterization of AlGaN/GaN HEMTs

- under pulsed biasing," IEEE Trans. Electron Devices, vol. 65, no. 5, pp. 1753–1758, 2018 <a href="https://doi.org/10.1109/TED.2018.2818621">https://doi.org/10.1109/TED.2018.2818621</a>

- [15] S. Choi, E. Heller, D. Dorsey, R. Vetury, and S. Graham, "Analysis of the residual stress distribution in AlGaN/GaN high electron mobility transistors," J. Appl. Phys., vol. 113, no. 9, p. 93510, 2013 <a href="https://doi.org/Artn.09351010.1063/1.4794009">https://doi.org/Artn.09351010.1063/1.4794009</a>

- [16] M. Azize and T. Palacios, "Effect of substrate-induced strain in the transport properties of AlGaN/GaN heterostructures," J. Appl. Phys., vol. 108, no. 2, 2010 https://doi.org/10.1063/1.3463150

- [17] J. a. del Alamo and J. Joh, "GaN HEMT reliability," Microelectron. Reliab., vol. 49, no. 9–11, pp. 1200–1206, 2009 https://doi.org/10.1016/j.microrel.2009.07.003

- [18] G. Pavlidis, S. Pavlidis, E. R. Heller, E. A. Moore, R. Vetury, and S. Graham, "Characterization of AlGaN/GaN HEMTs Using Gate Resistance Thermometry," IEEE Trans. Electron Devices, vol. 64, no. 1, pp. 78–83, 2017 https://doi.org/10.1109/Ted.2016.2625264

- [19] D. Cahill, "Analysis of heat flow in layered structures for time-domain thermoreflectance," Review of Scientific Instruments, Vol. 75, No. 12, pp. 5119-5122, 2004 <a href="https://doi.org/10.1063/1.1819431">https://doi.org/10.1063/1.1819431</a>

- [20] G. Pavlidis, D. Kendig, L. Yates, and S. Graham, "Improving the Transient Thermal Characterization of GaN HEMTs," in 2018 17th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), 2018, pp. 208–213 https://doi.org/10.1109/ITHERM.2018.8419649

- [21] K. Yazawa, D. Kendig, P. E. Raad, P. L. Komarov, and A. Shakouri, "Understanding the thermoreflectance coefficient for high resolution thermal imaging of microelectronic devices," Tech. Brief, Electron. Cool. Mag., vol. 19, no. March, pp. 10–14, 2013.

- [22] H. F. Liu, S. B. Dolmanan, L. Zhang, S. J. Chua, D. Z. Chi, M. Heuken, and S. Tripathy, "Influence of stress on structural properties of AlGaN/GaN high electron mobility transistor layers grown on 150 mm diameter Si (111) substrate," J. Appl. Phys., vol. 113, no. 2, p. 23510, 2013 https://doi.org/10.1063/1.4774288

- [23] Y. Zhang, M. Yuan, N. Chowdhury, K. Cheng, T. Palacios, "720-V/0.35-mΩ·cm² Fully Vertical GaN-on-Si Power Diodes by Selective Removal of Si Substrates and Buffer Layers," IEEE Electron Device Lett., vol. 39, no. 5, pp. 715-718, 2018 <a href="https://doi.org/10.1109/LED.2018.2819642">https://doi.org/10.1109/LED.2018.2819642</a>