# The Efficacy of Software Prefetching and Locality Optimizations on Future Memory Systems<sup>\*</sup>

Abdel-Hameed Badawy<sup>†</sup> Aneesh Aggarwal<sup>†</sup> Donald Yeung<sup>†</sup> Chau-Wen Tseng<sup>‡</sup> <sup>†</sup>Electrical and Computer Engineering Dept., <sup>‡</sup>Computer Science Dept., University of Maryland, College Park. ABSALAM@ENG.UMD.EDU ANEESH@ENG.UMD.EDU YEUNG@ENG.UMD.EDU TSENG@CS.UMD.EDU

## Abstract

Software prefetching and locality optimizations are techniques for overcoming the speed gap between processor and memory. In this paper, we provide a comprehensive summary of current software prefetching and locality optimization techniques, and evaluate the impact of memory trends on the effectiveness of these techniques for three types of applications: regular scientific codes, irregular scientific codes, and pointer-chasing codes. We find that for many applications, software prefetching outperforms locality optimizations when there is sufficient memory bandwidth, but locality optimizations outperform software prefetching under bandwidth-limited conditions. The break-even point (for 1 GHz processors) occurs at roughly 2.26 GBytes/sec on today's memory systems, and will increase on future memory systems. We also study the interactions between software prefetching and locality optimizations when applied in concert. Naively combining the techniques provides robustness to changes in memory bandwidth and latency, but does not yield additional performance gains. We propose and evaluate several algorithms to better integrate software prefetching and locality optimizations, including a modified tiling algorithm, padding for prefetching, and index prefetching. Finally, we investigate the interactions of stride-based hardware prefetching with our software techniques. We find that combining hardware and software prefetching yields similar performance to software prefetching alone, and that locality optimizations enable stride-based hardware prefetching for benchmarks that do not normally exhibit striding.

#### 1. Introduction

Current microprocessors spend a large percentage of execution time on memory access stalls, even with large on-chip caches. Since processor speeds are growing at a greater rate than memory speeds, we expect memory access costs to become even more important in the future. Computer architects have been battling this *memory wall problem* [2] by designing ever larger and more sophisticated caches. Although caches are extremely effective, they are not the complete solution. Other techniques are required to fully address the memory wall problem.

Two promising approaches for improving memory performance are *software prefetching* and *locality optimizations*. The first executes explicit prefetch instructions to begin loading data from memory to cache. As long as prefetching begins early enough and the data is not evicted prior to its use, memory access latency can be completely hidden. However, as processor throughput improves due to memory latency tolerance, memory bandwidth use is increased since prefetching increases memory traffic. In comparison, locality optimizations use compiler or run-time transformations to change the computation order and/or data layout of a program to increase the probability it

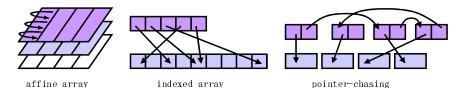

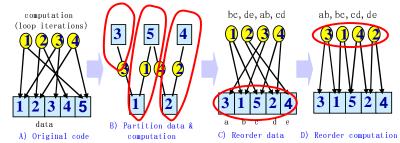

Figure 1: Examples of affine array, indexed array, and pointer-chasing memory access patterns.

accesses data already in cache. If successful, both average memory latency and bandwidth usage are reduced, since there will be fewer main memory accesses.

Both software prefetching and locality optimizations have been studied in isolation. In this paper, we examine how well each approach works for three types of data-intensive applications. Our evaluation uses a single unified environment to enable a meaningful comparison. A primary focus of our work is to compare the importance of *latency tolerance* provided by prefetching and *latency reduction* provided by locality optimizations on future high-performance memory systems. In addition, our work also investigates the interactions of software prefetching and locality optimizations when applied in concert. The contributions of this paper are as follows:

- We provide a comprehensive summary of current software prefetching and locality optimization techniques for three types of data-intensive applications: regular scientific codes, irregular scientific codes, and pointer-chasing codes.

- We compare the efficacy of software prefetching and locality optimizations for the three types of applications.

- We quantify the impact of bandwidth and latency scaling in future memory systems on the relative effectiveness of software prefetching and locality optimizations.

- We examine the performance of integrated software prefetching and locality optimizations, then propose and evaluate several enhancements to increase their combined effectiveness.

- We study the interactions of stride-based hardware prefetching with software prefetching and locality optimizations.

The rest of this paper is organized as follows. First, we describe three memory access patterns in Section 2. Then, we summarize the different techniques that have been previously developed for each access pattern. Section 3 discusses software prefetching techniques, and Section 4 discusses locality optimization techniques. Next, we present our experimental results in Section 5, and develop improved algorithms in Section 6. We also study the impact of stride-based hardware prefetchers on our results in Section 7. Finally, Section 8 discusses related work and Section 9 concludes the paper.

## 2. Memory Access Patterns

The types of software prefetching and locality optimizations which may be applied are dependent on the type of memory access pattern made by a program. We begin by presenting three important types of memory access patterns shown in Figure 1, using example codes in Figure 2.

## 2.1 Affine Array Accesses

The most basic memory access pattern is regular accesses with constant strides, such as references to elements in multidimensional arrays. The 2D Jacobi code in Figure 2 Part(A), commonly found

| // Affine Array Accesses<br>// (2D Jacobi Kernel)<br>A(N, N, N), B(N, N, N) | // Indexed Array Accesses<br>// (Molecular Dynamics)<br>X(M),X2(M),index(N) | <pre>// Pointer-Based Structures // (Linked List Traversal) struct node {val, next} *ptr;</pre> |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| do j=2, N-1                                                                 | do t = 1, time                                                              | while () {                                                                                      |

| do i=2,N-1<br>A(i,j) = 0.25 *                                               | do i = 1, N<br>d = X1(index(i))-X2(index(i))                                | ptr->next = malloc(node);<br>ptr = ptr->next;                                                   |

| (B(i-1, j)+B(i+1, j)+B(i, j-1))                                             | force = d**(-7)-d**(-4)<br>X1(index(i)) += force                            | ptr->val = ;                                                                                    |

|                                                                             | X2(index(i)) += -force                                                      | <pre>while (ptr-&gt;next) {ptr = ptr-&gt;next;;}</pre>                                          |

| Part (A)                                                                    | Part (B)                                                                    | Part (C)                                                                                        |

Figure 2: Code examples for three classes of memory access patterns.

in finite-difference or multigrid solvers for systems of partial differential equations (PDEs), is an example code that performs very regular memory accesses. The code computes the value of a point in array A as the average of values of neighbors in all dimensions of array B.

Programs exhibiting these regular memory access patterns are also called *stencil* codes because they compute values based on applying a uniform *stencil* pattern repeatedly to each point of array A to compute the desired result. Array references result in memory accesses with constant strides if array subscripts are affine (i.e., linear combinations of loop index variables with constant coefficients and additive constants). These programs are also called *regular* codes because their memory access patterns are regular and well defined.

Affine array accesses are quite common in a variety of applications, including dense-matrix linear algebra and finite-difference PDE solvers as well as image processing and scans/joins in relational databases. These programs can usually exploit long cache lines to reduce memory access costs, but may suffer poor performance due to cache conflict and capacity misses arising from the large amounts of data accessed. An important feature of codes performing affine array accesses is that memory access patterns can be identified at compile time, assuming array dimension sizes are known. This allows both software prefetching and locality transformations to be determined precisely at compile time.

#### 2.2 Indexed Array Accesses

Another memory access pattern is called indexed array accesses, because the main data array is accessed through a separate *index array* whose value is unknown at compile time. For example, consider the molecular dynamics code in Figure 2 Part(B), which calculates forces between pairs of atoms in a molecule. The index array *index* is accessed in an regular manner. In contrast, the two arrays X1 and X2 are indexed by the contents of the *index* array. The accesses are irregular due to the nature of the data stored in the index array, as shown in Figure 1. The cache performance of applications using indexed arrays can be poor since both spatial and temporal locality in such applications is typically low due to the irregularity of the access pattern.

Indexed array accesses arise in several scientific application domains where computational scientists attempt more complex simulations. In computational fluid dynamics, meshes for modeling large problems are sparse to reduce memory and computation requirements. In N-body solvers which arise in astrophysics and molecular dynamics, data structures are irregular because they model the positions of particles and their interactions. Index arrays are frequently used to store these more complicated relationships between data, since they are more efficient than pointers. Unfortunately, these irregular computations have poor temporal and spatial locality, and do not utilize processor caches efficiently. Unlike applications with affine accesses, compile-time transformations

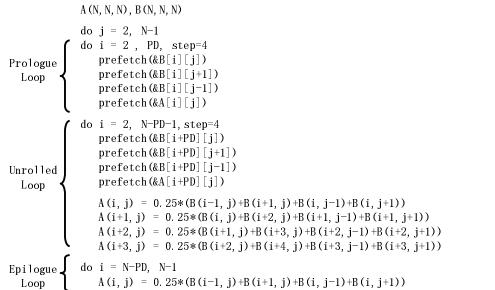

Figure 3: Example affine array prefetching for the 2D Jacobi kernel using Mowry's algorithm [3].

alone cannot improve locality because the values of the index array are not known at compile time. A combination of compile-time and run-time transformations are needed instead.

#### 2.3 Pointer-Chasing Accesses

Finally, the third class of memory accesses are *pointer-chasing* codes that dynamically allocate memory and use pointer-based data structures such as linked lists, n-ary trees, and other graph structures. Figure 2 Part(C) shows an example of creating and traversing a singly-linked list. These programs are known as *pointer-chasing* codes, because accesses to additional parts of the data structure cannot take place until the pointer to the current portion of the data structure is resolved. This property forces associated memory references to be sequentialized, and is known as the *pointer-chasing problem*.

Pointer-chasing applications usually exist in programs solving complex problems where the amount and organization of data is unknown at compile time, requiring the use of pointers to manage both dynamic storage and linkage. They may also arise from high-level programming language constructs such as object-oriented programming. Because memory is allocated and accessed dynamically, the access pattern tends to be very irregular and lack locality, resulting in poor cache performance.

Indexed array accesses share characteristics to pointer-chasing codes, since the access to the index array must be resolved before and the data values can be accessed. However, indexed arrays have only one level of indirection, allowing many data elements and index array references to occur in parallel. In comparison, pointer accesses can have arbitrarily deep levels of indirection, sequentializing the entire pointer-chasing application.

Nodes in these pointer-chasing codes are usually dynamically allocated at run time, with their total number and connection pattern unknown at the time of compilation. To traverse the list, the pointers are dereferenced one after another in a serial manner. Because of the dynamic nature of data structure creation and modification, pointer-chasing codes commonly exhibit poor spatial and temporal locality and experience poor cache behavior. Pointer-chasing memory access patterns can be detected at compile time, but cannot be directly transformed by the compiler, since the pointer values are not known statically. Instead, cache-conscious run-time memory allocation can

be used to improve locality. In comparison, prefetching is not hindered by the fact that the memory locations are not known at compile-time, but is limited by the sequentialization of memory accesses.

#### 3. Software Prefetching

Software prefetching relies on the programmer or compiler to insert explicit prefetch instructions into the application code for memory references that are likely to miss in the cache. At run time, the inserted prefetch instructions bring the data into the processor's cache in advance of its use, thus overlapping the cost of the memory access with useful work in the processor. Software prefetching has been shown to be effective in reducing memory stalls for both sequential and parallel applications, particularly for scientific programs making regular memory accesses [4, 5, 6, 3]. Recently, techniques have also been developed to apply prefetching to pointer-based data structures [7, 8, 9, 10, 11]. In this section of the paper, we present three software prefetching algorithms proposed previously in the literature for the three types of memory access patterns discussed in the previous section.

#### 3.1 Affine Array Prefetching

To perform software prefetching for affine array references commonly found in scientific codes, we follow the well-known compiler algorithm proposed by Mowry [3]. Mowry's algorithm exploits the precise access pattern information available through static analysis of affine array references to insert prefetches for only the data needed by the processor, and no more. Consequently, the algorithm is quite effective and typically provides good performance gains.

Mowry's prefetch algorithm involves three steps. To illustrate, Figure 3 shows the 2D Jacobi kernel from Figure 2 Part(A) after all the steps have been applied. First, the affine array references within inner-most loops are identified as prefetching candidates. For each candidate, locality analysis is performed to determine which dynamic instances of the static memory reference will miss in the cache, hence requiring prefetching. To permit prefetching of only the missing dynamic instances, loop unrolling is performed to create multiple static instances of each memory reference within the loop body; the degree of loop unrolling is set to the number of back-to-back memory references Co-located in the same cache block (determined via locality analysis). By unrolling the loop this number of iterations, the dynamic instances that miss in the cache are isolated-the leading static memory reference in the unrolled loop always misses, while the remaining unrolled static memory references always hit. Hence, a single prefetch for the leading memory reference can be inserted into the unrolled loop, prefetching exactly the missing dynamic instances, thus avoiding unnecessary prefetches and reducing prefetch overhead.

Figure 3 illustrates the loop unrolling and prefetch insertion transformations for the 2D Jacobi kernel. In this loop, there are five affine references, four for the *B* array, and one for the *A* array. Assuming each reference accesses 8 bytes and assuming a 32-byte cache block, the loop should be unrolled by a factor of 4. After loop unrolling, four prefetches are inserted for the five leading memory references: A(i,j), B(i-1,j), B(i+1,j), B(i,j-1), and B(i,j+1). Notice the B(i-1,j) and B(i+1,j) references lie on the same cache block, thus saving 1 prefetch.

The next step in Mowry's algorithm is to perform *prefetch scheduling*. Given the high memory latency of most modern memory systems, a single loop iteration normally contains insufficient work under which to hide the cost of memory accesses. To ensure that data arrive in time, the prefetches inserted in the first step of the algorithm must be initiated multiple iterations in advance.

The minimum number of loop iterations needed to fully overlap a memory access is known as the *prefetch distance*. Prefetch scheduling determines the prefetch distance and applies it to the inserted prefetches. Assuming the memory latency is l cycles and the work per loop iteration is w cycles, the prefetch distance, PD, is simply  $\lceil \frac{l}{w} \rceil$ . Figure 3 illustrates the indices of prefetched array elements contain a PD term, providing the early prefetch initiation required.

Finally, the last step is to "fix up" inefficiencies in prefetching created by prefetch scheduling. By modifying prefetches to initiate PD iterations in advance as illustrated in Figure 3, the first PD iterations do not get prefetched, and the last PD iterations prefetch past the end of each array. These inefficiencies can be addressed by performing loop peeling to handle the first and last PD iterations of the loop separately. The loop peeling transformation creates a *prologue loop* to execute PD prefetches for the first PD array elements, and an *epilogue loop* to execute the last PD iterations without prefetching. Figure 3 illustrates the prologue and epilogue loops created by loop peeling.

#### 3.2 Indexed Array Prefetching

Indexed array accesses, of the form A(B(i)), are common in irregular scientific codes. We use the prefetch algorithm for indexed array accesses proposed in [12] by Mowry, which is an extension to his algorithm for affine arrays described in Section 3.1. The extensions stem from three major differences between indexed and affine array accesses. First, indexed array accesses contain two array references per prefetch candidate-one for the data array and one for the index array. Affine array accesses perform only a single array reference per prefetch candidate. Second, static analysis cannot determine locality information for consecutively accessed indexed array elements since their addresses depend on the index array values known only at runtime. Finally, before a data array reference can perform, the corresponding index array reference must complete since the index value is used to index into the data array. Hence, pairs of data and index array references are serialized.

Mowry's indexed array prefetching algorithm follows the same three steps for prefetching affine arrays: loop unrolling, prefetch scheduling, and loop peeling. Each step is modified to accommodate the added complexities of indexed array accesses compared to affine array accesses. To illustrate, Figure 4 shows a simplified molecular dynamics kernel after all the steps have been performed. First, loop unrolling is applied to isolate the missing dynamic instances, as described in Section 3.1. Unfortunately, cache-miss isolation via loop unrolling succeeds only for the index array accesses. Since the location of consecutively accessed data array elements depends on the index array values at runtime, static analysis fails to provide spatial locality information for the data array references, so the compiler must be conservative and assume all data array references lie on separate cache blocks. Consequently, while a single prefetch is sufficient for all instances of the index array in the unrolled loop body, a separate prefetch is necessary for every instance of the data array. Figure 4 illustrates the unrolled loop and the inserted prefetch code. The loop unrolling degree is two to limit the size of the example code.

Next, prefetch scheduling is performed. As in affine array prefetching, the computation of the prefetch distance uses the formula,  $PD = \lceil \frac{l}{w} \rceil$ . However, the adjustment of array indices for indexed arrays must take into consideration the serialization of data array and index array references. Since data array elements cannot be prefetched until the index array values they depend on are available, prefetches for index array elements should be initiated twice as early as data array elements. This ensures that an index array value is in cache when its corresponding data array prefetch is issued. Figure 4 illustrates the indices of prefetched data array elements contain the normal PD term, but

```

X1(M), X2(M), index(N)

do t = 1, time

do i = 1, PD , step=2

prefetch(&index(i))

do i = 1, PD, step=2

Prologue

prefetch(&index(i+PD))

Loops

prefetch(&X1(index(i)))

prefetch(&X2(index(i)))

prefetch(&X1(index(i+1)))

prefetch(&X2(index(i+1)))

do i = 1, N-2*PD-1, step=2

prefetch (&index (i+2*PD))

prefetch(&X1(index(i+PD)))

prefetch(&X2(index(i+PD)))

prefetch(&X1(index(i+1+PD)))

prefetch(&X2(index(i+1+PD)))

Unrolled

Loops

= X1(index(i)) - X2(index(i))

force = d * (-7) - d * (-4)

X1(index(i)) += force

X2(index(i)) += -force

d = X1 (index (i+1)) - X2 (index (i+1))

force = d * (-7) - d * (-4)

X1(index(i+1)) += force

X2(index(i+1)) += -force

do i=N-2*PD-1, N-PD-1

prefetch(&X1(index(i+PD)))

prefetch(&X2(index(i+PD)))

d = X1(index(i)) - X2(index(i))

force = d * (-7) - d * (-4)

X1(index(i)) += force

X2(index(i)) += -force

Epilogue

+= -force

Loops

do i=N-PD-1, N

d = X1(index(i))-X2(index(i))

force = d**(-7)-d**(-4)

X1(index(i)) += force

X2(index(i)) += -force

```

Figure 4: Example indexed array prefetching

prefetched index array elements contain a 2 \* PD term to fetch them in advance of the data array prefetches.

Lastly, loop peeling is performed. As described in Section 3.1, prologue and epilogue loops are inserted to properly handle the first and last few iterations of the loop. For indexed array prefetching, two prologue loops and two epilogue loops are necessary because prefetch scheduling uses two prefetch distances, PD and 2 \* PD. The first prologue loop issues the index array prefetches for the first PD loop iterations. Then, the second prologue loop issues the index array prefetches for the next PD loop iterations as well as the data array prefetches for the first PD loop iterations. Similarly, the first epilogue loop executes the second-to-last PD loop iterations without index array prefetching. Finally, the last epilogue loop executes the last PD loop iterations without any prefetching. Figure 4 illustrates the modified loop peeling transformation.

#### 3.3 Pointer-Chasing Prefetching

Prefetching for pointer-based data structures is challenging due to the memory serialization effects associated with traversing pointer structures. The memory operations performed for array traversal can issue in parallel because individual array elements can be referenced independently. At worst, pairs of array references are serialized in the case of indexed array traversal. But even in that case, separate indexed array references can perform in parallel. In contrast, the memory operations

```

struct node {data, next, jump} *ptr, *list head, *prefetch array[PD], *history[PD];

int i, head, tail;

for (i=0; i < PD; i++)

for (i = 0; i < PD; i++)

prefetch (prefetch_array[i]); Prologue Loop

history[i] = NULL;

tail = 0:

ptr = list head;

head = PD-1;

while (ptr->next) {

prefetch (ptr->jump);

ptr = list_head;

while (ptr) {

ptr = ptr->next;...;

history[head] = ptr;

if (!history[tail])

Part A: Traversal

prefetch_array[tail] = ptr;

Pointer Prefetching -

Code.

else history[tail]->jump = ptr;

Generation Loop

head = (head+1) \% PD;

tail = (tail+1) \% PD;

ptr = ptr \rightarrow next;

```

Part B: Prefetching Pointers Creation Code.

Figure 5: Example pointer prefetching using jump pointers and prefetch arrays [7].

performed for pointer traversal must dereference a series of pointers sequentially. The memory serialization in pointer chasing prevents conventional prefetching techniques from overlapping cache misses suffered along a pointer chain, thus limiting their effectiveness.

Jump pointer prefetching [8, 11] is a promising approach for addressing the pointer-chasing problem. In jump pointer prefetching, additional pointers are inserted into a dynamic data structure to connect non-consecutive link elements. These "jump pointers" allow prefetch instructions to name link elements further down the pointer chain (*i.e.* a prefetch distance, PD, away which is computed as in Sections 3.1 and 3.2) without sequentially traversing the intermediate links. Consequently, prefetch instructions can overlap the fetch of multiple link elements simultaneously by issuing prefetches through the memory addresses stored in the jump pointers. Figure 5 Part(A) illustrates a "while" loop that has been instrumented with jump pointer prefetching.

Jump pointer prefetching, however, cannot prefetch the first PD link nodes in a linked list because there are no jump pointers that point to these early nodes. To enable prefetching of early nodes, jump pointer prefetching can be extended with *prefetch arrays* [7]. In this technique, an array of prefetch pointers is added to every linked list to point to the first PD link nodes. Hence, prefetches can be issued through the memory addresses in the prefetch arrays before traversing each linked list to cover the early nodes, much like the prologue loops in affine array and indexed array prefetching prefetch the first PD array elements. Figure 5 Part(A) illustrates the addition of a prologue loop that performs prefetching through a prefetch array.

Before prefetching can commence, the prefetch pointers must be set. Figure 5 Part(B) shows an example of prefetch pointer initialization code which uses a *history pointer array* [8] to set the prefetch pointers. The history pointer array, called "history" in Figure 5, is a circular queue that records the last PD link nodes traversed by the initialization code. Whenever a new link node is traversed, it is added to the head of the circular queue and the head is incremented. At the same time, the tail of the circular queue is tested. If the tail is NULL, then the current node is one of the first PD link nodes in the list since PD link nodes must be encountered before the circular queue fills. In this case, we set one of the "prefetch\_array" pointers to point to the node. Otherwise, the tail's jump pointer is set to point to the current link node. Since the circular queue has depth PD, all jump pointers are initialized to point PD link nodes *ahead*, thus providing the proper prefetch distance. Normally, the compiler or programmer ensures the prefetch pointer initialization code gets executed prior to prefetching, for example on the first traversal of a linked data structure. Furthermore, if the application modifies the linked data structure after the prefetch pointers have

#### EFFICACY OF SOFTWARE PREFETCHING AND LOCALITY OPTIMIZATIONS

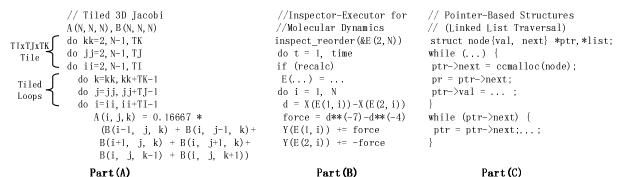

Figure 6: Example Locality optimized affine array, indexed array and pointer-chasing access codes.

CACHE (array layout avoids conflicts)

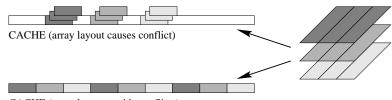

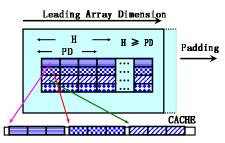

Figure 7: Example of conflict misses under two array layouts.

been initialized, it may be necessary to update the prefetch pointers either by re-executing the initialization code or by using other fix-up code.

## 4. Locality Optimizations

Software prefetching tries to hide memory latency while retaining the original program structure. Another alternative is to reduce memory accesses by changing the computation order and data layout of the program at compile and run time using *locality optimizations*. These optimizations try to improve *data locality*, the ability of an application to reuse data in the cache [13]. Reuse may be in the form of *temporal locality*, where the same cache line is accessed multiple times, or *spatial locality*, where nearby data is accessed together on the same cache line. Previous researchers have developed many locality optimizations. In this section, we consider optimizations for the three types of access patterns discussed in Section 2.

#### 4.1 Tiling for Affine Accesses

In many way, programs with affine array accesses are the easiest for compilers to apply locality optimizations, since memory access patterns can be fully analyzed at compile time. One useful program transformation is *tiling* (blocking), which combines strip-mining with loop permutation to form small tiles of loop iterations which are executed together to exploit data locality [13]. Figure 6 Part(A) demonstrates how the 3D Jacobi code can be tiled. By rearranging the loop structure so that the innermost loops can fit in cache (due to fewer iterations), tiling allows reuse to be exploited on all the tiled dimensions so that data in cache can be accessed multiple times before it is flushed.

Tiling is very effective with linear algebra codes [14, 15, 16, 17, 18], and has been been extended to handle stencil codes used in iterative PDE solvers as well [19, 20, 13]. A major problem with tiling is that limited cache associativity may cause data in a tile to be mapped onto the same cache lines, even though there is sufficient space in the cache. Conflict misses will result, causing tile data to be evicted from cache before they may be reused [16]. This effect is shown in Figure 7.

#### BADAWY, AGGARWAL, YEUNG, & TSENG

Figure 8: GPART algorithm for reordering data and computation in indexed array computations.

Previous research found *tile size selection* and *array padding* can be applied to avoid conflict misses in tiles [14, 17, 18]. Tile-size-selection algorithms carefully select tile dimensions tailored to individual array dimensions so that no conflicts occur. For 2D arrays, the Euclidean remainder algorithm may be used to quickly compute a sequence of non-conflicting tile dimensions through a simple recurrence [14, 18]. An alternative algorithm finds non-conflicting 2D tile using an greedy algorithm which expands tile dimensions while checking that no conflicts occur [16]. We can adapt this algorithm for finding non-conflicting 3D tiles by iteratively attempting to increase each tile dimension until none may be increased without introducing conflicts [19].

Tile size selection by itself may yield poor results since only small tiles may be able to avoid conflicts, particularly for array sizes near powers of two. One possible solution is to use padding to enable better tile sizes [21]. Padding increases the size of leading array dimensions, increasing the range of non-conflicting tile shapes. It has proven to be very useful for improving tiling for 2D linear algebra codes [18]. To combine padding with tile size selection for 2D arrays, we can test a small set of pads and choose the best choice. For 3D tiles, we would need to evaluate a much larger space of possible pads, so we extend the algorithm to stop searching for pad sizes when the predicted miss rate is within a small percentage of the predicted optimal [19].

#### 4.2 Reordering for Indexed Accesses

Programs with index array accesses access data in an irregular manner, depending on the values in the index array. If data is accessed in an irregular manner, spatial locality is unlikely to be obtained if the data is larger than the cache. Fortunately, recent research has demonstrated run-time data and computation transformations can improve the locality of irregular computations [22, 23, 24, 25].

Because many irregular computations typically perform *reduction* (commutative and associative) operations such as SUM and MAX, loop iterations can be safely reordered to bring accesses to the same data closer together in time. Data layout can also be transformed so that data accesses are more likely to be to the same cache line. These compiler and run-time transformations can be automated using an inspector-executor approached developed for message-passing machines [26], where the compiler identifies index accesses and inserts calls to run-time libraries to analyze and reorder data and loop iterations. Figure 6 Part(B) illustrate how a code with indexed accesses may be optimized using a combination of compile and run-time transformations. The invocation of the inspector library routine rearranges both the index array and data arrays to bring memory accesses closer in time and space, resulting in better cache performance.

Figure 8 illustrates the process by which an inspector can reorder data and computation of an index array computation at run time to improve locality. In the figure, loop iterations are represented as circles and data elements as squares. Many indexed array codes compute values based on pairs of indexed values (e.g., endpoints of a mesh segment, forces between a pair of particles). Such computations may be viewed as an undirected graph, where each loop iteration

Figure 9: CCMALLOC algorithm for improving memory allocation for pointer-chasing codes.

forms an edge connecting the pair of data elements accessed by the iteration. Each circle thus connects two squares.

In this representation, improving locality may be viewed as selecting an ordering of circles (loop iterations) and squares (data elements) so that nearby circles access identical or nearby squares. Several data and computation locality transformations exist to solve the problem of improving the locality of such graphs [22, 23, 25, 24]. Our evaluation uses a technique called GPART that relies on hierarchical clustering to improve locality [27, 28]. GPART works in three steps. First, the graph formed by the index array computation hierarchically partitioned into roughly cache-sized chunks. Second, the partitioning is then used to reorder the data to improve spatial locality. Finally, loop iterations are lexicographically sorted based on their data accesses to improve temporal locality. Experiments have shown GPART closely matches the performance of more sophisticated partitioning algorithms, with much less run-time overhead.

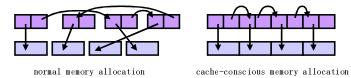

## 4.3 Memory Allocation For Pointers

Pointer-based programs frequently suffer from poor locality and are notoriously difficult to analyze and transform because of their reliance on pointers and dynamically allocated recursive data structures. Pointer-based applications are harder to optimize than indexed array codes, since pointer chasing forces link nodes to be traversed sequentially. Fortunately, researchers have developed *cache-conscious* heap allocation and transformation techniques to improve locality for pointer-based programs [29, 30, 31]. These techniques improve locality by assigning or changing the locations of dynamically allocated memory in ways designed to improve spatial locality. Examples of cacheconscious algorithms include run-time tree optimization routines that place parent nodes with child nodes for improved locality, and coloring when placing tree nodes to avoid conflict with the root.

Of particular interest is CCMALLOC, a customized memory allocator which allocates memory in a location near to a user-specified address. CCMALLOC is a heuristic that reserves space for future allocation requests when allocating new blocks of data [30]. Using this memory allocator, multiple members of a linked list are thus more likely to be in adjacent memory locations. Not only does this take advantage of hardware prefetching of long cache lines, but cache line utilization increases and fragmentation is reduced, decreasing the probability that useful cache lines will be evicted from cache.

Figure 6 Part(C) shows a simple list allocation code that uses CCMALLOC to allocate list nodes on nearby cache blocks dynamically. The code modification is quite simple: replacing MALLOC with CCMALLOC. Compiler analysis of pointer accesses can be used to determine when cache-conscious memory allocators should be used. For our experimental evaluation, we inserted calls to CCMALLOC by hand in our pointer-chasing benchmark codes. CCMALLOC for our evaluation works by taking a optional pointer argument during memory allocation, and allocating current and future nodes close to it whenever possible. To increase the probability of nearby placement, CCMALLOC reserves space for future data blocks when allocating the first node [30]. Figure 9 displays an example of cache-conscious memory allocation to improve locality for pointer-chasing codes. Note one problem with CCMALLOC is that dynamic data structures which change after allocation may not benefit from this optimization. Frequent insert and delete operations after allocation will make logically contiguous nodes physically non-contiguous after a few deletions and/or insertions. Our pointer-chasing benchmarks did not perform many deletions to linked data structures.

#### 5. Experimental Evaluation

This section evaluates the performance of software prefetching and locality optimizations, first independently, and then in concert. We describe our experimental methodology. Then, we compare software prefetching and locality optimizations under different memory bandwidths and latencies. Finally, we study their combination.

#### 5.1 Methodology

Our experimental evaluation uses the SimpleScalar tool set [32] to model a 1GHz 4-way issue dynamically-scheduled processor. The simulator models all aspects of the processor including the instruction fetch unit, the branch predictor, register renaming, the functional unit pipelines, and the reorder buffer. To enable software prefetching, we added a prefetch instruction to the ISA of the processor model. In addition, our simulator also models the memory system in detail. We assume a split 8-Kbyte direct-mapped L1 cache with 32-byte cache blocks, and a unified 256-Kbyte 4-way set-associative L2 cache with 64-byte cache blocks. Although the caches are small, they match the more modest input data sets required for simulation.

Several of our experiments study sensitivity to memory latency and memory bandwidth. To facilitate these experiments, we modified the SimpleScalar simulator to accurately model bus contention across the L2-memory bus. Then, we varied the L2-memory latency from 80 to 640 cycles, and varied the L2-memory bus bandwidth between 1-64 Gbytes/sec (note that a bandwidth of 1 Gbyte/sec is equivalent to the processor loading one byte per cycle). The lower end of both the latency and bandwidth ranges captures the trends of existing memory systems which have latencies of around 100 cycles and bandwidths of around 2-3 GBytes/sec. The mid and high end of the latency and bandwidth ranges capture the characteristics of future architectures.

For all experiments, transfers across the L1-L2 bus incur a 7-cycle latency, and we assumed the L1-L2 bus has infinite bandwidth. We also assumed an unlimited number of MSHRs to maximize concurrency in the memory system, thus exposing memory bandwidth limitations. We don't expect the infinite L1-L2 bandwidth assumption to affect our results. Our benchmarks are memory intensive with very large working sets, so they tend to be bandwidth limited at the memory sub-system level. However, the unlimited MSHRs assumption is significant. Without sufficient MSHRs, prefetching performance would degrade since the number of outstanding prefetches would be limited. We optimistically assume enough MSHRs are provided in the caches to maximize the effectiveness of prefetching.

To drive our simulations, our experimental evaluation employs nine benchmarks, representing the three classes of data-intensive applications described in Section 2. Table 1 lists the benchmarks along with their problem sizes and memory access patterns.

The first three applications in Table 1 perform affine array accesses. MM multiplies two matrices, RB performs a 3D red-black successive-over-relaxation, and JACOBI performs a 3D Jacobi relaxation. Both JACOBI and RB are frequently found in multigrid PDE solvers, such as MGRID from the SPEC/NAS benchmark suite. The next three applications perform indexed array ac-

| Application | Problem Size        | Access Pattern  |

|-------------|---------------------|-----------------|

| RB          | 200x200x8 grid      | Affine array    |

| Jacobi      | 200x200x8 grid      | Affine array    |

| MM          | 200x200 matrices    | Affine array    |

| IRREG       | 14K node mesh       | Indexed array   |

| Moldyn      | 13K molecules       | Indexed array   |

| NBF         | 144K mols           | Indexed array   |

| Health      | 5 levels, 500 iters | Pointer-chasing |

| MST         | 1024  nodes         | Pointer-chasing |

| EM3D        | 10K nodes           | Pointer-chasing |

Table 1: Benchmark summary.

| Latency | RB | Jacobi  | MM  | IRREG               | Moldyn  | NBF | Health | MST | EM3D |

|---------|----|---------|-----|---------------------|---------|-----|--------|-----|------|

| 80      | 12 | 8, 36   | 24  | 8, 20, 20, 40       | 1, 1, 2 | 2   | 31     | 3   | 2    |

| 160     | 24 | 16,68   | 44  | 12, 40, 40, 80      | 2, 2, 3 | 4   | 62     | 3   | 3    |

| 320     | 48 | 28, 136 | 88  | 24,80, $80$ , $160$ | 4, 4, 5 | 8   | 124    | 3   | 6    |

| 640     | 96 | 56, 268 | 176 | 44,160,160,319      | 7, 7, 9 | 16  | 247    | 3   | 11   |

Table 2: Prefetch distances for loops in all benchmarks versus latency in cycles.

cesses. IRREG is an iterative PDE solver for an irregular mesh, MOLDYN is abstracted from the non-bonded force calculation in CHARMM, a key molecular dynamics application used at NIH to model macromolecular systems, and NBF (Non Bonded Force kernel), is a molecular dynamics simulation. NBF is taken from the GROMOS benchmark [33].

The last three applications perform pointer-chasing accesses. HEALTH simulates the Columbian health care system, MST computes a minimum spanning tree, and EM3D simulates electromagnetic wave propagation through 3D objects. HEALTH, MST, and EM3D are all from the OLDEN benchmark suite [34].

For each application, we applied software prefetching and locality optimizations by hand, first in isolation, then in combination. We followed the algorithms described in Sections 3 and 4, applying the appropriate algorithm to each application given its memory access pattern. We then measured the performance of the optimized codes on our detailed architectural simulator.

As described in Section 3, software prefetching requires computing a prefetch distance, PD, to properly schedule prefetches. Recall that  $PD = \lceil \frac{l}{w} \rceil$ , where w is the work per loop iteration, and lis the memory latency (see Section 3.1). Hence, PD must be recomputed not only for every loop, but also for every memory latency setting. Table 2 reports the computed prefetch distances for the affine array, indexed array, and pointer-chasing benchmarks. For each benchmark, we list prefetch distances for four different memory latencies used in our experiments. In applications with multiple instrumented loops, the prefetch distance for each loop is listed separately.

| Latency | RB   | Jacobi | MM   | IRREG | Moldyn | NBF  | EM3D | Average |

|---------|------|--------|------|-------|--------|------|------|---------|

| 80      | 2.08 | 1.57   | 1.84 | 2.80  | 3.51   | N/A  | 1.75 | 2.26    |

| 160     | 2.65 | 1.89   | 2.84 | 2.93  | 2.86   | 3.37 | 1.83 | 2.62    |

| 320     | 2.94 | 2.05   | 3.82 | 3.04  | 2.99   | 3.62 | 1.87 | 2.90    |

| 640     | 3.17 | 2.10   | 4.68 | 3.20  | 3.31   | 3.81 | 1.89 | 3.20    |

Table 3: Equi-performance bandwidth in Gbytes/sec versus memory latency in cycles. The last column reports the average per latency.

Finally, as described in Section 4, locality optimizations for indexed array benchmarks reorder computations using graph partitioning techniques to improve memory performance. For our indexed array benchmarks, we apply the RCB computation reordering algorithm.

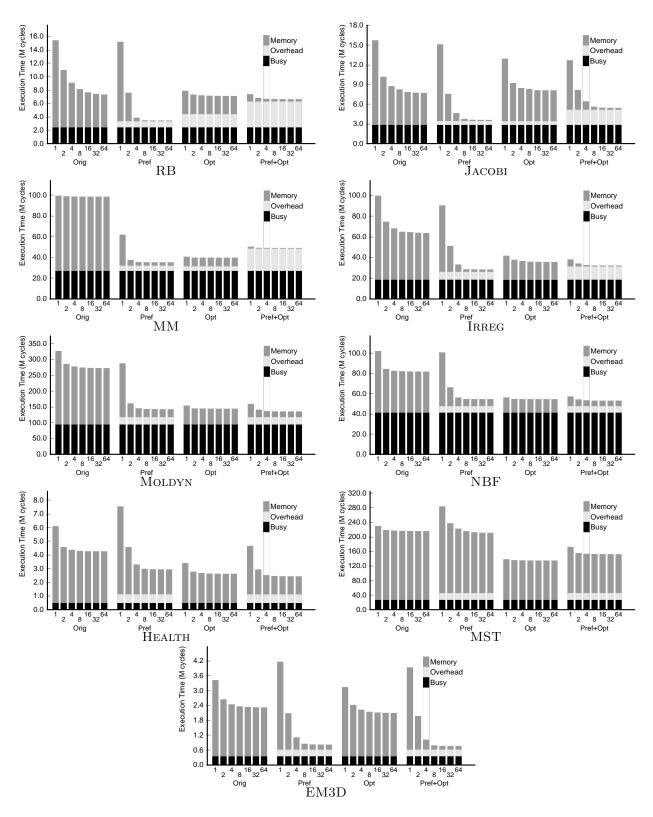

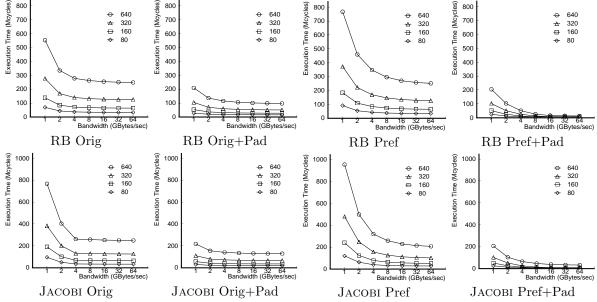

#### 5.2 Varying Memory Bandwidth

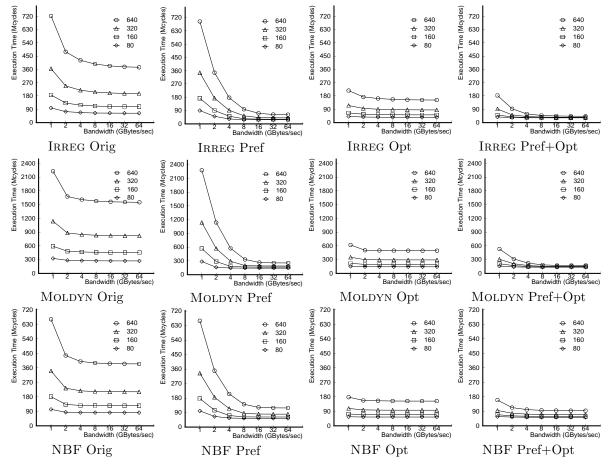

In this section, we evaluate the performance of software prefetching and locality optimizations under memory bandwidth scaling. Figure 10 plots execution time along the y-axis, and varies memory bandwidth from 1-64 Gbytes/sec along the x-axis, keeping memory latency fixed at 80 cycles. Each execution-time bar is broken down into memory stall, software overhead, and computation components. Groups of bars represent the original version of each program, and versions optimized with either software prefetching, locality optimization, or both. In this section, we focus only on applying the techniques in isolation. Later in Section 5.4, we will examine the techniques in combination.

For the affine array and indexed array benchmarks, both software prefetching and locality optimizations provide significant performance gains, improving performance by 45% on average over unoptimized codes. Comparing the techniques, we see two major differences. First, software prefetching incurs more overhead than locality optimizations. This overhead is due primarily to prefetch and related address computation instructions. In particular, loop unrolling is unable to isolate cache misses for index array accesses, as described in Section 3.2, contributing to increased runtime overhead for the indexed array benchmarks. Overall, locality optimizations exhibit very low overheads. Tiling incurs some overhead for the extra levels of loops, but this is minimal. For the indexed arrays benchmarks, the RCB algorithm has no measurable overhead since the runtime inspector is amortized over lots of computations [28].

Second, the relative effectiveness of software prefetching and locality optimizations to eliminate memory stalls depends on available memory bandwidth. At high memory bandwidths, software prefetching eliminates practically all memory stalls since the memory system can sustain the simultaneous memory requests necessary to hide all the memory latency. As memory bandwidth is reduced, memory requests must serialize, thus software prefetching loses its effectiveness. In contrast, locality optimizations reduce memory latency, and hence, memory traffic. This makes them highly effective at low bandwidths where reduced traffic pays off. However, locality optimizations cannot eliminate all memory stalls, so they achieve a lower maximum performance compared to software prefetching. Consequently, for all the array-based benchmarks except for NBF at 80 cycles of latency, software prefetching outperforms locality optimizations at high memory bandwidths, while locality optimizations outperform software prefetching at low memory bandwidths.

Table 3 reports the memory bandwidths at which software prefetching and locality optimizations achieve equal performance. Memory systems providing memory bandwidths higher than this *equi-performance bandwidth* favor software prefetching, while those providing lower memory bandwidths favor locality optimizations. For an 80-cycle memory latency corresponding to the data in Figure 10, Table 3 shows the average equi-performance bandwidth is 2.41 Gbytes/sec. (Note, NBF does not have an equi-performance bandwidth at 80 cycles of latency since locality optimization outperforms software prefetching at all memory bandwidths). Such a large equi-performance bandwidth underscores the importance of latency reduction techniques, and implies future memory systems must provide significant memory bandwidth before prefetching can outperform locality optimizations on these data-intensive applications.

Figure 10: Execution time breakdown under memory bandwidth scaling at 80 cycles of memory latency with no optimizations (Orig), with software prefetching (Pref), with locality optimization (Opt), and with combined optimizations (Pref+Opt).

In the pointer-chasing benchmarks, locality optimization outperforms software prefetching at all memory bandwidths for HEALTH and MST. This is due to three factors. First, pointer prefetching incurs high software overhead to create and manage jump pointers. Software overhead in HEALTH and MST is 131% and 70%, respectively, of the BUSY component. In contrast, CCMALLOC memory allocation incurs no measurable overhead. Second, the traversal loops in our pointer-chasing codes are short, particularly for MST, and do not provide sufficient work under which to hide memory latency. Hence, software prefetching cannot eliminate all memory stalls. Finally, pointer prefetching requires jump pointer storage that increases the cache miss rate and memory bandwidth consumption, making the optimized code even more data-intensive than the original code. As Figure 10 shows, software prefetching in HEALTH and MST (as well as EM3D) performs worse than the original code at low memory bandwidths.

In EM3D, software prefetching achieves higher performance as compared to HEALTH and MST; hence, its behavior resembles the array benchmarks rather than the other pointer-chasing benchmarks. This improved software prefetching performance is due to EM3D's primary data structure. Whereas HEALTH and MST employ linked lists that are difficult to prefetch for the reasons explained above, EM3D uses an "array of lists" data structure that is more amenable to software prefetching. Specifically, EM3D simulates alternating electric and magnetic fields characteristic of electro-magnetic wave propagation via two arrays, one for "e-nodes" and another for "h-nodes" [35]. "Edge pointers" connect e-nodes to h-nodes and vice versa to form a bipartite graph, representing a mesh over which the electro-magnetic fields are simulated [36]. Like MST, the traversal code for each edge pointer is short, potentially limiting prefetching. However, because the edge pointers are rooted inside e-node and h-node array elements (and because these arrays are both very large). jump pointers can be created to name e-nodes and h-nodes well in advance of their traversal, resulting in effective memory latency tolerance. Like the array benchmarks, software prefetching achieves better performance than CCMALLOC at high bandwidths, and worse performance than CCMALLOC at low bandwidths. Consequently, an equi-performance bandwidth exists for EM3D as shown in Table 3, and is 1.7 Gbytes/sec at 80 cycles of latency.

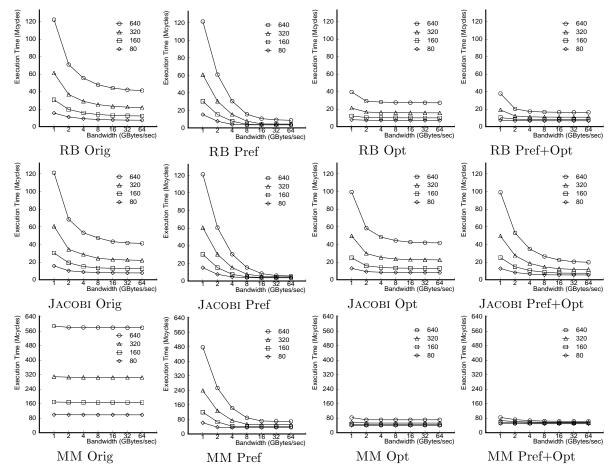

#### 5.3 Varying Memory Latency

Figures 11, 12, and 13 evaluate software prefetching and locality optimizations under memory latency scaling. Similar to Figure 10, we plot execution time versus memory bandwidth. In addition, we present results for 80, 160, 320, and 640-cycle memory latencies on separate lines in each graph. Each version of a program (original, prefetch, optimized, both) is displayed in a separate graph. Once again, we focus on applying the techniques in isolation, leaving a discussion of the combined techniques to Section 5.4.

Not surprisingly, execution time for all program versions increases as we scale memory latency. For the affine array and indexed array benchmarks, software prefetching effectively hides the increasing memory latencies given sufficient memory bandwidth. In contrast, locality optimizations suffer performance degradation as memory latencies grow; however, they still enjoy the benefit of reduced traffic at low memory bandwidths. As a result, software prefetching outperforms locality optimizations at high memory bandwidths, while locality optimizations outperform software prefetching at low memory bandwidths for all the memory latencies we simulated. Note, NBF at 80 cycles of latency is the one exception, as observed in the previous section, since locality optimization is slightly better than prefetching at all bandwidths. Table 3 shows equi-performance bandwidths generally increase with memory latency. Consequently, on future systems with high memory la-

Figure 11: Execution time under both memory bandwidth and latency scaling for affine array benchmarks with no optimizations (Orig), with software prefetching (Pref), with locality optimization (Opt), and with combined optimizations (Pref+Opt).

tencies, greater memory bandwidth will be required before software prefetching demonstrates a performance advantage over locality optimizations.

In the pointer-chasing benchmarks, locality optimization outperforms software prefetching at all memory latencies and bandwidths for HEALTH and MST. The same reasons given in Section 5.2 for the reduced effectiveness of software prefetching on pointer-based data structures explain locality optimization's performance advantage at higher memory latencies in these applications. Once again, EM3D is an exception. EM3D performance with memory latency scaling is similar to the affine array and indexed array benchmarks. The same reasons given in Section 5.2 apply. It is worth noting that since the performance of the three pointer-chasing benchmarks differs, there is still room for further research to study more pointer-chasing applications to better characterize their behavior when software prefetching and locality optimizations are applied.

#### 5.4 Combined Techniques

This section evaluates software prefetching and locality optimizations in combination. We created combined versions of our benchmarks in the following manner. For the affine array benchmarks,

Figure 12: Execution time under both memory bandwidth and latency scaling for indexed array benchmarks with no optimizations (Orig), with software prefetching (Pref), with locality optimization (Opt), and with combined optimizations (Pref+Opt).

| Latency | RB | Jacobi  | MM  | IRREG               | Moldyn  | NBF | Health | MST | EM3D |

|---------|----|---------|-----|---------------------|---------|-----|--------|-----|------|

| 80      | 9  | 8,40    | 16  | 8, 20, 20, 40       | 1, 1, 2 | 2   | 8      | 3   | 2    |

| 160     | 9  | 11, 80  | 28  | 12, 40, 40, 80      | 2, 2, 3 | 4   | 16     | 3   | 3    |

| 320     | 9  | 11, 156 | 52  | 24,80, $80$ , $160$ | 4, 4, 5 | 8   | 32     | 3   | 6    |

| 640     | 9  | 11,308  | 104 | 44, 160, 160, 319   | 7, 7, 9 | 16  | 16     | 3   | 11   |

Table 4: Prefetch distances for the combined versions for all benchmarks versus latency in cycles.

we applied software prefetching to the innermost tiled loops. For the indexed array and pointerchasing benchmarks, software prefetching and locality optimizations modify distinct parts of the code. Hence, for these programs, we simply merge the modified portions of the software prefetching and locality optimization program versions.

Table 4 reports the computed prefetch distances for the affine array, indexed array, and pointerchasing benchmarks at different memory latencies. Note that for RB, the prefetch distance is fixed at 9 since the tile size is 9x10 whereas the computed prefetch distance is larger than 9. For our combined optimizations to function properly, we must limit the prefetch distance to the minimum of the prefetch distance and the length of the tile in order to prevent prefetching beyond the current

Figure 13: Execution time under both memory bandwidth and latency scaling for pointer-chasing benchmarks with no optimizations (Orig), with software prefetching (Pref), with locality optimization (Opt), and with combined optimizations (Pref+Opt).

computation tile. This effect also occurs in one of the loops from JACOBI for latencies higher than 80 cycles.

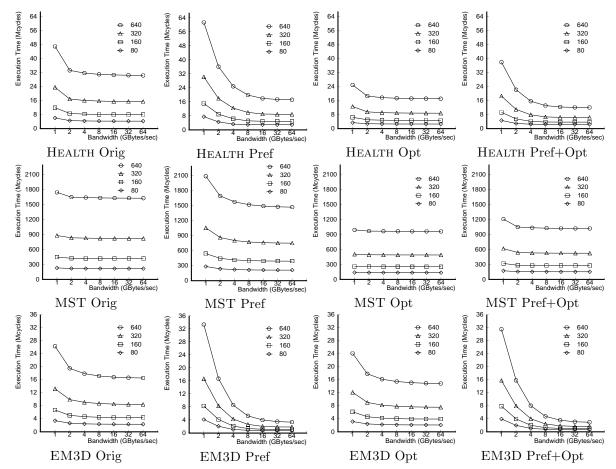

Results for the combined optimizations are reported in Figures 10, 11, 12, and 13 under "Pref+Opt." In Figure 14, we also summarize the average performance of each version of the program relative to memory bandwidth and latency. Performance is first normalized relative to the original program (with bandwidth of 1 Gbyte/sec and latency of 80 cycles), then averaged over all programs for each memory bandwidth or latency. Simulations show results vary depending on memory bandwidth and latency.

Software prefetching is very sensitive to available memory bandwidth. When bandwidth is very low, software prefetching increases overhead without reducing memory costs. The combined algorithm thus performs slightly worse than locality optimizations alone. In comparison, when memory latencies are very high, combining software prefetching and locality optimizations usually yields better performance than applying either one alone. As Figure 14 shows, combining is much better than prefetching, and only slightly better than locality optimizations.

Under certain conditions, combining techniques encounters high overhead compared to either technique alone. For the affine array benchmarks, tiling significantly reduces the number of iter-

Figure 14: Comparing average performance for different versions of programs relative to memory bandwidth and latency. Performance is normalized relative to the original program with 1 Gbyte/sec bandwidth and 80 cycle latency.

ations in the innermost loop. When prefetching is applied to these short tiled loops, the software pipeline startup overhead incurred by prefetching becomes significant, reducing the amount of memory latency hidden. This effect is apparent in the high CPU overhead in the "Pref+Opt" versions of MM and JACOBI in Figure 10. Combining also inherits the overheads from both software prefetching and tiling, further reducing its performance relative to either techniques alone. For both indexed array and pointer-chasing benchmarks, software prefetching and locality optimizations modify different parts of the benchmark code. Software prefetching modifies the computation loops themselves while locality optimizations instrument the creation code semantics, or reorders data before entering the computation loop.

For pointer-chasing benchmarks, except for EM3D, combining always under-performs CCMAL-LOC memory allocation alone at low memory bandwidths. The extra jump pointers and prefetch arrays required for pointer prefetching increase the demand for memory bandwidth, thus partially negating the reduced traffic benefits achieved by CCMALLOC memory allocation in the combined version. The combined version also underperforms CCMALLOC memory allocation at high memory bandwidths in MST. As described previously, software prefetching for the short list traversal loops in MST is ineffective; hence, combining software prefetching with CCMALLOC memory allocation only adds overhead without reducing memory stalls. For EM3D, locality optimizations performs better than any other technique at low bandwidth. At higher bandwidth, combined is the best among all the techniques. As explained in Section 5.2, software prefetching is highly effective for EM3D. When combined with CCMALLOC, the reduced memory traffic provided through better locality permits software prefetching to achieve even higher performance.

Finally, because combining exploits both latency tolerance and latency reduction, it is less sensitive to variations in memory bandwidth and latency than either technique in isolation. As shown in Figure 14, the combined version achieves the best performance on average for practically all memory bandwidths and latencies. Such robust performance is valuable when bandwidth and latency parameters on the target system are not available to the compiler, or when the compiler must produce a single optimized code for heterogeneous systems.

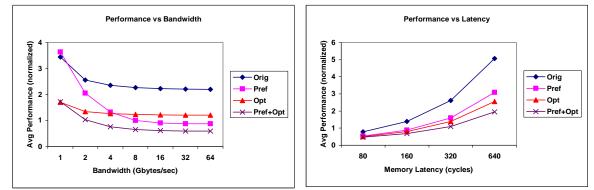

Figure 15: Comparing square tiles against tall tiles with and without prefetching.

## 6. Algorithm Enhancements

In addition to evaluating the effects of memory bandwidth and latency scaling on performance, our simulations also point out a number of ways to enhance both software prefetching and locality optimizations. This section presents several enhancements to better combine the two techniques and to enhance software prefetching for array codes in the presence of conflict misses. First, tiling is enhanced to combine more effectively with software prefetching. Then, padding which is normally used to reduce conflicts in tiling is applied to software prefetching to avoid prefetch thrashing. Finally, CCMALLOC is used to reduce overhead in software prefetching for pointer-chasing codes.

#### 6.1 Enhancing Tiling for Software Prefetching

One problem with combining tiling and software prefetching naively is the high startup overhead from prefetching short tiled loops, as described in Section 5.4. We can improve performance by modifying the original tiling algorithm. Our enhanced algorithm is identical to the one described in Section 4.1 except we select a larger innermost tile dimension size (*e.g. TI* in Figure 6). Our tiling heuristic uses the Euclidean GCD algorithm [14, 18] to generate a series of non-conflicting tile sizes. Although tiles with a square aspect ratio typically achieve the best cache utilization, we can bias the selection towards taller tiles with greater height to width aspect ratio. Such *tall*

| Application | Square         | Tall          |

|-------------|----------------|---------------|

| RB          | $9 \times 10$  | $31 \times 3$ |

| Jacobi      | $11 \times 13$ | $59 \times 3$ |

| MM          | $33 \times 23$ | $83 \times 9$ |

Table 5: Tile sizes for square and tall-tile versions of the affine array benchmarks.

| Latency | RB | Jacobi  | MM  |

|---------|----|---------|-----|

| 80      | 12 | 8, 40   | 16  |

| 160     | 20 | 12, 80  | 28  |

| 320     | 31 | 24, 156 | 52  |

| 640     | 31 | 48,308  | 104 |

Table 6: Prefetch distances for RB, JACOBI and MM with tall tiles versus latency in cycles.

tiles have more iterations in their innermost loop compared to square tiles, thus reducing startup overheads when used in combination with software prefetching. Note, however, we must take care not to choose tiles that are too tall. In the extreme case, having a tile size of  $Y \times 1$  would result in mapping the problem back to the original computation order. Thus, extremely tall tiles negate the benefits that tiling provides.

Table 5 reports both square and tall tile sizes for the three affine array benchmarks. After choosing a new tall tile size and instrumenting tiling, we then instrument software prefetching to the innermost tiled loops. Table 6 shows the prefetch distances for the new tall tile loops. If the prefetch distance computed after the instrumentation with tall tiles exceeds the length of the tile, the prefetch distance is selected to be the minimum of the tile length and the computed prefetch distance, as discussed in Section 5.4.

Figure 15 presents the tall tile results with and without prefetching for MM, JACOBI, and RB, and compares them to the corresponding square tile results from Figure 11. Notice tall tiles and square tiles alone achieve similar performance. However, when combined with software prefetching, tall tiles significantly reduce the short-loop overheads suffered at high bandwidths when using square tiles, matching the performance of software prefetching alone from Figure 11. These simulation results demonstrate that tall tiles allow us to fully exploit the benefits of software prefetching and tiling simultaneously.

In addition, the combined tall tile and software prefetching techniques retain the robustness benefit described in Section 5.4. Figure 15 shows that at low bandwidth, the performance tracks tiling performance alone, while at high bandwidth, the performance tracks software prefetching performance alone. Hence, the enhanced combined technique shows more robustness to variations in the memory system parameters since the two techniques are more synergistic when the enhancement is applied.

#### 6.2 Padding for Software Prefetching

While software prefetching can hide memory latency given sufficient memory bandwidth, conflict misses on prefetched data can degrade or even completely eliminate benefits. In our experiments, we found that prefetching for affine array codes may require array padding, particularly if the set associativity of the L2 cache is low. The problem is that for some applications and problematic data sizes, severe conflict misses may result, with all prefetched data being mapped to a small set of cache lines, as shown in the top of Figure 7. This problem is especially acute for affine accesses to arrays whose dimensions are near a multiple of the cache size since adjacent array elements will

Figure 16: Illustrating the algorithm used for the choice of array padding.

Figure 17: Execution results for padding with and without prefetching in JACOBI and RB.

conflict in cache. To alleviate the conflicts, array padding can be used to create a better mapping into the cache, as shown in the bottom half of Figure 7, allowing prefetched cache blocks to remain in cache until the processor references the data.

The appropriate amount of padding to apply to the array is computed as follows. First, the prefetch distance computed by the prefetching algorithm, as explained in Section 3 and as computed for our applications at the end of Section 5.1, is treated as the leading dimension of a tile. Second, the compiler uses the Euclidean GCD algorithm to determine whether cache conflicts will occur within a tile whose leading dimension is the prefetch distance, "PD." Padding is introduced incrementally to the leading array dimension until the Euclidean GCD algorithm gives a conflict-free tile size whose leading dimension is at least equal to or larger than "PD" [18, 19]. Figure 16 illustrates this algorithm, showing how the leading dimension of a tile "H" is related to the prefetch distance "PD," how padding is introduced along the leading array dimension, and how a group of PD prefetched array cache blocks do not conflict in the cache after padding.

For this padded problem size, prefetched cache blocks will stay in cache until they are referenced by the processor for the following reason. After issuing a prefetch, the processor will reference the prefetched cache block only after prefetch distance minus 1 (PD - 1) additional prefetches have been issued since each prefetch instruction prefetches data PD iterations in advance. So, there are at most PD prefetched cache blocks that have not been referenced by the processor at any one moment in time. For the amount of padding computed, the Euclidean GCD algorithm ensures no conflicts will occur within a tile whose leading dimension is at least equal to the prefetch distance. Hence, we are guaranteed that there are no conflicts between the PD cache blocks that have been prefetched but not yet referenced by the processor.

Figure 17 presents experiments demonstrating the utility of combining array padding with prefetching. Versions of RB and JACOBI were created with and without both padding and prefetching. We used a 2-way set-associative L2 cache in these simulations for the purpose of illustration, since 4-way caches can eliminate conflicts in both benchmarks but this would not be the case for more complicated programs. We chose a problem size of  $256 \times 256 \times 8$ . Such power-of-two problem sizes occur frequently in multigrid codes due to the need to use a series of meshes of increasing granularity. Based on the prefetch distance, our Euclidean algorithm chose to pad the array to  $313 \times 256 \times 8$  to eliminate conflicts.

The first two graphs in Figure 17 for RB and JACOBI show that padding alone applied to the original unoptimized code is capable of removing many of the conflict misses, and increases performance even with no prefetching applied. Figure 17 also shows that prefetching alone, in the graphs labeled "Pref," provides zero benefit due to the conflicts since conflicts evict prefetched cache lines before their use. In fact, performance degrades at low bandwidth due to fetching more data because of the conflicts. Once padding is applied, as shown in the graphs labeled "Pref+Pad," prefetching can improve performance beyond that achieved by padding alone. (Note, due to the change in the problem sizes for this particular enhancement, the results for ORIG and PREF for both RB and JACOBI in Figure 17 are different from those in Figure 11).

#### 6.3 CCMALLOC and Prefetching

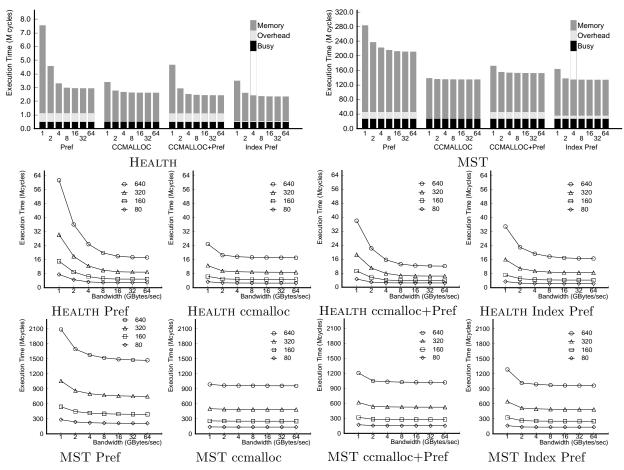

Software prefetching for pointer-chasing codes suffers high overhead to create and manage jump pointers, as described in Section 5.2. However, jump pointers may not be necessary when prefetching is combined with CCMALLOC memory allocation. Since intelligent allocation places link nodes contiguously in memory, prefetch instructions can access future link nodes by simple indexing, just as for affine array accesses. Figure 9 shows the effect of CCMALLOC on nodes linked together by pointers. From the right-hand part of the figure, it is intuitive that a compiler can insert prefetches for list nodes further down the list using the size of a node and the location of the first node. This approach, which we call *index prefetching* [1, 37], was originally proposed in [8]. With index prefetching, the jump pointers can be removed, thus eliminating all the overhead associated with jump pointer prefetching. To quantify this benefit, we created index prefetching versions for HEALTH and MST, and show the results for these benchmarks in Figure 18. (We did not create an index prefetching version for EM3D, our third pointer-chasing benchmark, since it already achieves high performance with normal software prefetching as shown in Figures 10 and 13).

The upper portion of Figure 18 compares index prefetching to the original versions with prefetch arrays and CCMALLOC allocation alone as well as in combination, assuming a memory latency of 80 cycles. The data shows index prefetching indeed eliminates most of the software overheads incurred by prefetch arrays, as we expected. As a result, index prefetching outperforms all other optimized versions at high memory bandwidths for both HEALTH and MST. Index prefetching performs slightly worse than CCMALLOC allocation alone at low bandwidth only, especially in MST, due to prefetching conditionally accessed link nodes, increasing memory bandwidth consumption.

While index prefetching reduces software overheads, it is not as effective in eliminating memory stalls as prefetch arrays for HEALTH. In HEALTH, many link nodes are deleted and re-inserted into

Figure 18: Comparing index prefetching (Index Pref) to prefetch arrays (Pref), ccmalloc memory allocation (ccmalloc), and combined optimizations (ccmalloc+Pref). Memory latency is fixed at 80 cycles in the top two graphs.

linked lists frequently. Contiguous allocation, and hence index prefetching, for such dynamic lists is useless since the layout of link nodes becomes random after a few delete and insert operations. As the upper portion of Figure 18 shows for HEALTH, index prefetching hides less memory latency than prefetch arrays due to frequent delete and insert operations. At larger memory latencies, the increased memory stalls outweigh the reduced software overheads, so combining CCMALLOC and prefetch arrays naively outperforms index prefetching.

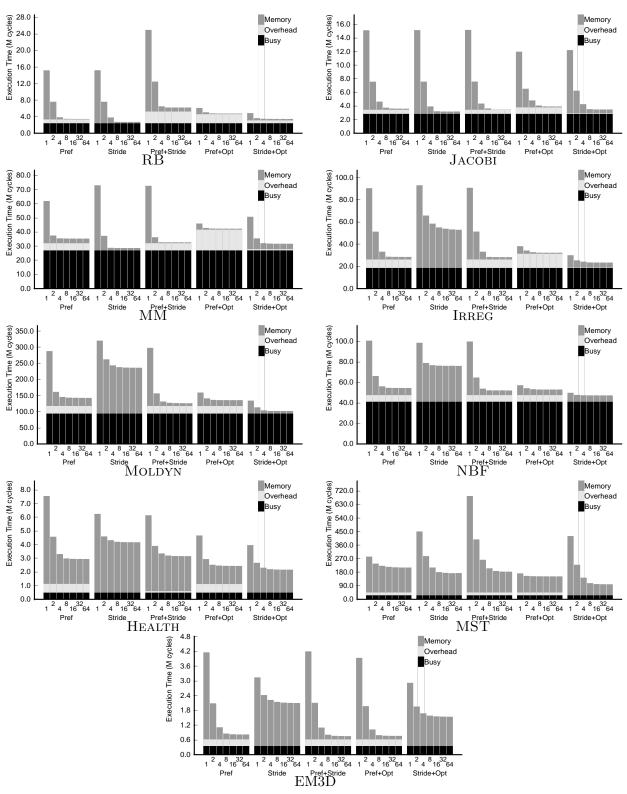

## 7. Hardware Prefetching

While our research focuses on software techniques, there also exist several hardware techniques for addressing the memory bottleneck problem. *Hardware prefetching*, in particular, is a promising hardware technique that has received significant attention. In fact, research in this area is mature enough that many recent commercial microprocessors use simple prefetchers. Specifically, the Intel Pentium 4 [38] and IBM Power 5 [39] both employ *stride-based hardware prefetchers* [40, 41]. Given that hardware prefetching is becoming commonplace in high-end CPUs, an important question is

how do our software techniques compare against hardware prefetching? Furthermore, if applied in concert, how will our software techniques interact with hardware prefetching?

To address these questions, we augmented our simulator to model a stride-based hardware prefetcher, similar to the one used in [42]. Our stride prefetcher consists of a 256-entry stride table and 8 stream buffers. The stride table observes the post-L1 miss stream to detect strides on a per-load instruction basis. When a striding load is detected, the stride table allocates a stream buffer and commences prefetching using the observed stride. The processor checks both the L1 cache and stream buffers for each memory operation, and on a stream buffer hit, the prefetched block is moved into the L1 cache. To prevent thrashing, confidence estimation is used to guide stream buffer allocation. Each stride table entry contains a saturating counter that is incremented (decremented) whenever an L1 cache miss would have been correctly (incorrectly) predicted by the stride table. Each stream buffer allocation occurs only when an inactive stream buffer is found, or when the allocating stride table entry has a higher confidence counter value than one of the active stream buffers.

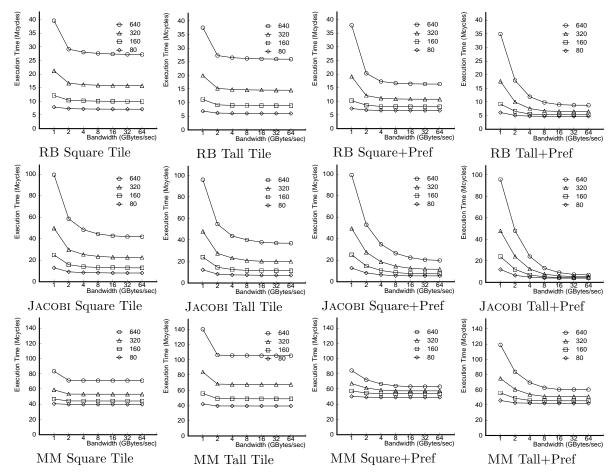

Figure 19 shows the results of our hardware prefetching study in a format similar to Figure 10. As in Figure 10, we keep the memory latency fixed at 80 cycles, and vary the memory bandwidth between 1 and 64 GBytes/sec. Groups of bars represent versions optimized using different techniques. The bars labeled "Pref" employ software prefetching alone, and are identical to the corresponding bars in Figure 10. The bars labeled "Stride" and "Pref+Stride" employ stride-based hardware prefetching alone and in combination with software prefetching, respectively. Finally, the bars labeled "Pref+Opt" and "Stride+Opt" employ locality optimization in combination with software prefetching and stride-based hardware prefetching, respectively. Note, the "Pref+Opt" and "Stride+Opt" versions of the affine array benchmarks (*e.g.* RB, JACOBI, and MM) use the tall tile approach described in Section 6.1 since basic tiling does not perform well in combination with prefetching.

Comparing the "Stride" and "Pref" bars, we see hardware prefetching outperforms software prefetching slightly at high bandwidths for RB, JACOBI, MM, and MST. These benchmarks exhibit striding, so stride prefetching effectively removes the memory stalls. Also, hardware prefetching incurs zero runtime overhead since it does not consume processor resources to issue prefetches; hence, hardware prefetching enjoys a small performance advantage roughly equal to the runtime overhead incurred by software prefetching in these benchmarks. Hardware prefetching also outperforms software prefetching at low bandwidths for HEALTH and EM3D. These benchmarks perform pointer chasing, so jump pointers and prefetch arrays must be instrumented to perform software prefetching. When memory bandwidth is scarce, fetching these extra pointers, it does not incur the additional memory traffic, allowing it to outperform software prefetching at low bandwidths.

While hardware prefetching holds a modest performance advantage in some cases, software prefetching outperforms hardware prefetching significantly in many other cases. In particular, IR-REG, MOLDYN, NBF, HEALTH, and EM3D exhibit irregular access patterns that are non-striding. Stride prefetching fails to cover a significant portion of the cache misses in these benchmarks; hence, software prefetching achieves a significant gain over hardware prefetching, particularly at high bandwidths. In MM, IRREG, MOLDYN, and MST, hardware prefetching frequently prefetches useless data, thus incurring higher memory traffic relative to software prefetching. This leads to a performance advantage for software prefetching at low bandwidths. Overall, our results indicate stride prefetching alone, as performed by hardware prefetchers in contemporary CPUs, cannot achieve the performance afforded by software prefetching on our benchmarks.

Figure 19: Execution time breakdown under memory bandwidth scaling with software prefetching (Pref), hardware prefetching (Stride), combined software prefetching and hardware prefetching (Pref+Stride), combined software prefetching and locality optimizations (Pref+Opt), and combined hardware prefetching and locality optimizations (Stride+Opt), all at 80 cycles of memory latency.

Comparing the "Pref+Stride" and "Pref" bars, we see the combination of hardware and software prefetching achieves similar performance to software prefetching alone. One exception is MST where hardware prefetching frequently fetches useless data, resulting in reduced performance at low bandwidths. However, aside from this case, the two techniques combine quite well. This result suggests compilers and programmers can apply software prefetching on systems with hardware prefetchers, and achieve good performance without worrying about their interaction. (Note, higher performance could probably be achieved if software prefetching is selectively disabled for striding memory references to reduce runtime overhead since these references can be prefetched by hardware prefetching. But evaluation of such an approach is beyond the scope of this study.)