## ಡ graph-reducer for The HDG-machine: a highly distributed transputer network\*

BURN نـ HUGH KINGDON, DAVID R. LESTER + AND GEOFFREY

GEC-Marconi Ltd, Hirst Research Centre, East Lane, Wembley, HA9 7PP

programs are immediately scalable. This paper presents some of the results of our part of Esprit 415, in which we Distributed implementations of programming languages with implicit parallelism hold out the prospect that the considered the implementation of lazy functional programming languages on distributed architectures.

specified, using Miranda.‡ Each instruction of the abstract machine was then implemented as a macro in the Transputer specification makes it possible to validate the compiler before the Transputer code is generated. The hardware currently available consists of five T800-25s, each board having 16 Mbytes of memory. Benchmark A compiler and abstract machine were designed to achieve this goal. The abstract parallel machine was formally Assembler. Although macro expansion of the code results in non-optimal code generation, use of the Miranda

timings using this hardware are given. In spite of the straightforward code-generation, the resulting system compares favourably with more sophisticated sequential implementations, such as that of LML.

Received September 1990

## 1. INTRODUCTION

of lazy functional languages is that they are slow when compared with more traditional languages such as C and Pascal. Early implementations were slow, for two reasons: implementations about Popular mythology

- they were largely interpretive; and

- that arguments to functions are not evaluated until their values are needed; thus imposing time and memory Ξ requires parallelism semantics of the languages and restricting any implementation. overheads, the lazy

Compiler technology has now advanced sufficiently so that lazy functional programs run respectably fast when compared with those written in more traditional languages, overcoming the overheads due to interpretation. An excellent collection of papers, which includes ones on implementation techniques, can be found in the April 1989 issue of this journal, the special issue on Functional Programming.

Realising that some functions needed to evaluate their arguments, so that the overheads of passing them unevaluated were unnecessary, we worked on a semantically sound technique for determining when this was the case. This resulted in the evaluation transformer model of reduction, which is able to capitalise on the information about how functions use their arguments in order to obtain more efficient sequential and parallel by solving the second problem. implementations. 8, 9, 14 began Our work

The evaluation transformer model says how the normal model of reduction can be modified in order to allow arguments to be passed to functions in a sequential implementation, and argument expressions to evaluated

using the best sequential compiler technology and placing communication (cf. the observations made for parallel prolog implements in Ref. 29 and the implementation of technology for sequential implementations can be used as a basis for an implementation using the evaluation transformer model of reduction, on both sequential and parallel machines. It can be used on a parallel machine such an implementation is best constructed it in a harness which supports task management and a combined logic and functional language on parallel evaluated in parallel in a parallel implementation. Being a modification of lazy evaluation, all the compiler machines in Ref. 4).

an abstract machine and showing how to compile functional languages to that abstract machine-see Refs abstract machine code to machine code for a real computer. In fact, the LML compiler, which produces At the time we were developing our parallel reduction model, most implementations were described by defining 2, 17, 18, 20 and 21 for example – and then compiling the compile parallel code for functional languages in terms some of the most efficient code for functional programs, works in this way. More recently, implementations have compiler technology, reflecting the growing understandsee Refs 6, 7, 26 and 27 for example. We described how the evaluation transformer information could be used to didactically convenient, and we note that the ideas can be adapted to begun to be described in terms of more conventional implementations using more standard compiler teching of the implementation of lazy functional language This was machine. 11, 12 abstract an

In functional language systems, the compiler organises for memory to be allocated to store the structures representing unevaluated arguments and data objects. Typically this information is kept in a graphical data structure, so the compiler is unable to determine when mentations include a garbage collector which periodically the allocated store should be released. Therefore implereclaims the storage occupied by data that is no longer

<sup>\*</sup> Research undertaken while the authors were employed by GEC Hirst Research Centre, and partially funded by ESPRIT Project 415: Parallel Architectures and Languages for AIP – A VLSI-Directed

<sup>†</sup> To whom all enquiries about this paper should be addressed. ‡ Miranda is a trade mark of Research Software,

Saving the state of the stack then reduces to storing the stack frame the workspace pointer, which points to the base address process. When a process is switched, its state must be To have the entire stack as part of the state is a large overhead at some ways, this is very natural on the transputer, which which therefore formed part of the state of the task switching time. Instead, we represent the stack as a linked list of stack frames, and keep a pointer to the stack concept of a workspace, the area of memory where the data for the current computation resides; and Our abstract machine specification gave each process similar solution has been adopted in.2 saved, and the state of the new process loaded. currently being used by a process. of that space. ∢ has the frame

We access to a multi-transputer system on which it could be developed. The implementation had two goals: With all these techniques in place, the time came when we had to try them out on a real parallel machine.

- to test out our ideas by providing a simple prototype

- implementation; and explore some of the issues concerning implementing functional languages in parallel on the transputer architecture.

The main purpose of this paper is to describe some of our techniques, and record some of our experiences.

Nevertheless, our implementation those that might be obtained from LML, and so there is definite hope that a results about implementation speeds would not necessrun sigimplementation, ideas could speeds comparable with our Being a simple prototype using real implementation arily be conclusive. nificantly fast. achieved

the The next two sections discuss the framework of the transputer implementation in more detail, and the rest of the paper is devoted to discussing particularities of it. In a bit more detail the evaluation transformer model of reduction, our garbage collection algorithm, and our way of handling stacks in a parallel, distributed machine. Those who are interested in a more general overview of the work of our project are April 1989 issue of this journal which a number of excellent papers on the analysis, referred to the survey article,12 and again we refer use and implementation of functional languages. Ξ. section, we describe reader to the next contains

### 2. BACKGROUND

# 2.1 The evaluation transformer model of reduction

arguments to functions is an overhead that is not present in a system which passes its arguments by value. It also restricts any parallelism in an implementation. The key points of the evaluation transformer model of reduction pass unevaluated to build data structures to are that: Having

- their evaluate 5 need definitely functions arguments; and

- the amount of evaluation that is needed of an argument expression may depend on the amount of evaluation

•

æ required of the function application of which it is subexpression. evaluate both its arguments. consider further the function append 2 + needs For example, the function

```

5

ys = x: append

ys = ys

(x:xs)

append

append

```

output of this function can request varying amounts of the result to be produced, and the amount requested affects the amount of evaluation that must be done to the argument expressions. For example, if the first element of the result must be obtained, then only the first argument needs any evaluation, and only needs its first element to be evaluated. If however, the consumer needs to evaluate all of the elements of the result list, then all which concatenates two lists together. The consumer of of the elements of both argument lists also need to evaluated

used to evaluate the argument to the required extent, before applying the function, and so saving the cost of building a data structure for the argument in the heap. The information is used in a parallel implementation by this information is creating a parallel process to evaluate the argument in parallel with the function application. sequential implementation, ಡ

or projection analysis. 13, 28 We refer the reader to these arguments can be determined using a semantically sound analysis technique, such as abstract interpretation8.9.14 and the compilation of programs using evaluation transformer further details of the model how functions information about for information. The

#### of Supporting the evaluation transformer model reduction 2.2

Downloaded from https://academic.oup.com/comjnl/article/34/4/290/368637 by guest on 21 August 2022

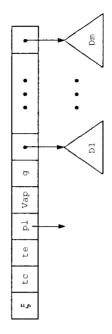

Figure 1. The Vap node for the application (g D1

Dm)

stored as graphs. The graph of the application is shown schematically in Fig. 1. It has four status fields: In our parallel implementation, function applications are

the amount of evaluation requested of the expression a task has been created to true if and only if so far, tc

te true if and only if the evaluation of the expression evaluate the expression,

has begun (although it may be temporarily suspended),

a list of tasks waiting application, a way of accessing the code for the function being applied (pictorially represented by putting g in the after the tag), and pointers to the graphs for the argument expressions (pictorially represented by pointers a function to triangles containing the name of the expression). for the evaluation of the expression to be completed the tag Vap to indicate that it is storing pl a pointer to the pending list, pox

291

complete Ref. 25. ಡ specification of the abstract machine given in and These fields are motivated in Ref. 10

# 2.3 Specifying the abstract machine

was sented the state of the machine as a tuple, and described by giving the modified state. We found be unwieldy when used for a parallel parallel much easier to write and read, compare the difference 25, and had the further advantage that it was executable. It may seem odd to talk about debugging specifications, but this is precisely the reason that we wanted an executable specification. It is possible that a formal proof of correctness for our implementation specifications for abstract machines have repreother projects, we ducked the responsibility, given, perhaps adapting the result of Ref. specification specification went for debugging the specification instead! The resultant wrote our and Ref. and instead language. the instructions this method to between Ref. 11 functional Like most machine, could be and

## A stackless implementation

languages (and indeed, any language with a function call mechanism) is to have each activation record kept on a stack, and so the stack is part of the state of a process. Such a stack, consisting of three activation records, is represented in the first part of Fig. 2. The heavy black functional The traditional way of implementing (and indeed, any

Keeping the activation records on a stack

Keeping the activation records as a linked list

Figure 2. Two different ways of keeping activation records for a process (g D1...Dm)

record. Furthermore, we make sure the Vap nodes that and the evaluation of the expression takes Lester developed an analysis technique which activation record and the start of another. In a parallel machine, it is more convenient to store the activation records in the heap, pointer to the current activation record, and each record points to the one which was activated immediately before 2). Process switches can only involves saving the pointer to its current activation are created to store a function application are big enough The only A simpler approach has been taken in Ref. 3, where a Vap node may occasionally need because saving the state of the stack activation record into a list. We keep be the activation records when that expression problem with this is determining how much space used by the Vap node. (see the second part of Fig. lines indicate the end of one gives this information. space of another. now be very fast, be extended. and link each place in the evaluated, needed. 2

### 2.5 Garbage collection

Bevan and the two Watsons independently discovered

5.30 It consisted of giving each object a reference of that object. When a pointer is copied, its weight is elegant garbage collection algorithm for distributed allocated count, and each pointer a weight; the sum of the weights of the pointers to an object is equal to the reference count copy and the original pointer (with an indirection node being introduced when the weight reaches one). Dealing with reference counts in way means that only decrement reference count are needed, removing the need for expensive increment that are used in other reference heap handle races between with languages evenly between the new oę decrement messages. mplementations to algorithms protocols messages shared

Downloaded from https://academic.oup.com/comjnl/article/34/4/290/368637 by guest on 21 August 2022 Ė portional to the number of live objects. In contrast, any asymptotic behaviour occurs even in quite small ss. <sup>19</sup> Furthermore, at least some of the efficiency of as collection takes time proheap memory size. Hartel has shown experimentally that copying scheme. Efficiency considerations therefore dictate that we choose a collector with the following properties: locally it should do copying collection, for inter-processor references algorithm takes time proportional to be attributed to the ease collectors should do weighted reference counting. ಡ garbage heap may be allocated in copying herently more efficient,1 may Unfortunately, G-machine<sup>21</sup> mark/scan which heaps. this

ester designed an algorithm which has the advantages of both algorithms.23 In his algorithm, reference counting is only used for interprocessor references. Two new node types are added to the machine:

indirections which point to non-local objects and have a weight, and Output

Input indirections which are pointed at by non-local references and point to local object; they have a reference count.

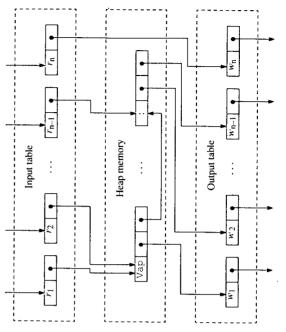

logically 3. Input indirections into three distinct parts, as shown in Figure divided IS therefore heap The

The logical structure of the heap. Figure 3.

are kept in the input table, output indirections in the output table, and all pointers in the third part of the heap, the local graph structure, are local. doing things in this way has some further advantages:

- ಡ of the remote expression when it has been uced, so that all pointers in a local store that the output indirections are a natural place to store point to the remote node share the copy; and produced,

- the local nodes and output indirection nodes can be a semi-space kept in a heap which is managed by allocator and copying collector. •

This concludes our necessarily brief overview of the higher-level details of our implementation; we now look at the details of the tasks that are used by the processors.

# 3. HDG-MACHINE TASKS

We refer to the function application illustrated in Fig. 1 as a Vap (Variable size APlication) node of the graph. It is the job of a task to evaluate a Vap node until it reaches a result – such as the integer 3. Things are slightly more because we use the evaluator to control the amount of complicated for tasks that result in data structure values, evaluation requested.

node. We store the old program counter on the old Vap node, and insert a return pointer on the newly opened Vap; this points back to the old Vap node. The One of the key ideas of the HDG-Machine is that the Vap nodes can be used to implement function calls. When a function call is attempted we open a new Vap; this points back to the old Vap n mechanism is shown in abstract form in Fig.

### 3.1 Generating tasks

nodes, we can instead create a task to perform this evaluation. We refer to this operation as the spawning of a task. This is how new tasks are generated. To provide parallelism, such tasks will be exported to processors As an alternative to the sequential evaluation of new Vap with insufficient work.

### 3.2 The task pools

When program execution begins a single task exists. As the program executes more tasks are created; these tasks are store in a task pool. The task pool is implemented as three separate task pools.

placed here. These tasks are the only candidate for migration to A newly created task is initially other processors. Migratable.

placed here. When a task is blocked it moves to the blocked task pool. When the active task pool is empty, tasks are moved from the migratable task pool. If this too is empty, tasks are requested from a neighbouring processor's migratable task pool. Active tasks may not Active. Tasks received from other processors be migrated.

Blocked. Whenever a task is blocked, because it is waiting for a result from some other task, it is placed here. When the result is available the task is placed in the active task pool.

Tasks in the migratable task pool are kept distinct from other tasks that can be executed immediately, because their state is small. This means that exporting them is not going to involve transferring an unbounded amount of state information to the remote processor.

The migratable task pool is implemented as a doubly linked-list. Tasks are exported from one end (the oldest

task is exported) and moved to the local active task pool from the other (the youngest task is moved).

The task migration strategy used is a simple one: request tasks from each of their neighbours in turn. Each neighbour either rejects the request for tasks on the a task, in this case the task requests are stopped. In order prevent tasks cycling around the machine without performing useful work, when a task is received from a remote processor, it is placed in the active task pool, thus ensuring that it will be executed on the receiving grounds that it has no tasks to donate or it passes back which do not have any executable processors processor. 2

tasks blocked task pool. There is no blocked task pool in the When the evaluation of a task has completed, the were waiting on the result of the evaluation; if this is the case the tasks are restarted by placing them in the active implementation: instead blocked tasks are referenced only from the node which caused the task to be blocked. The specification of the HDG-machine contains corresponding node is investigated to see if any task pool again.

# 3.3 Transputer details for HDG-machine tasks

are Iptr, the program counter, and Wptr, the workspace pointer. We use the first as the program counter and the other points to the current Vap node (see Subsection This gives us fast access to the contents of the node There are only two real registers on the transputer. They at the expense of: 2.4).

- some extra state on each node, and

- an awkward access pattern to global quantities.

Downloaded from https://academic.oup.com/comjnl/article/34/4/290/368637 by guest on 21 August 2022

The first of these points means that we must have two words immediately below the workspace for storing state when descheduled. The second point is only a problem because the occam linker does not permit the absolute Ideally, we would like to access the global quantity at in the transputer's memory. of code or data absolute address x by: placing

However, the value of x is not a link-time constant to the occam linker and so the above code is not permitted. When we initially implemented the machine we placed the local state of the node at negative locations from the tag position, and the S stack in the positive locations. An experiment was conducted, in which the order of items in the state was reversed. Because the loading small negative offsets is more costly than loading small positive offsets, faster register access is obtained in the modified scheme. The speed-up was 11 per cent.

consider the low-level details involved in using controlled shared memory access by concurrent processes in a transputer. We now move on to

<sup>\*</sup> In the transputer, loading and storing at locations with offsets between zero and 15 can occur in one instruction. Two instructions are required to access locations with offsets between -1 and -15.

#### Downloaded from https://academic.oup.com/comjnl/article/34/4/290/368637 by guest on 21 August 2022

# 4. TRANSPUTER PROCESSES

#### 4.1 Overview

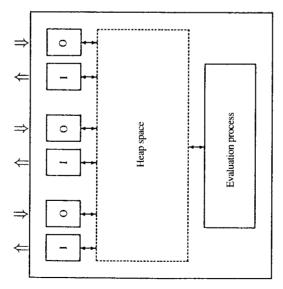

Each transputer emulates one processing element from the abstract machine. These processing elements can be thought of as consisting of three parts.

- A garbage collected heap.

- An input and an output process for each channel; there are therefore three of each on each transputer.

- An evaluation process.

The heap is used to store a number of data structures.

- Those necessary for running the evolution process, e.g. Vap nodes, integers, etc.

- The heap is also used to hold the task pools, as these are dynamic data structures, and may grow arbitrarily large. The active task pool must be shared between the reduction process and the I/O processes, as each needs to extract tasks from this data structure.

- Message queues of unsent messages.

Figure 4. An example of the state of a local processor.

require access to the heap to read and modify objects there, we must make sure that this access is controlled. That is, we would like to ensure that the heap is in a stable state when a process performs an operation on it. The natural CSP model for this would be to have a heap process, to which each I/O process and the reduction returned was a serious one - is that the reduction process spends a significant time accessing the heap. For messages. The only problem with this approach a shared and I/O messages. þe chose to have the heap as reduction then using responses to these messages would all of the processes requests resource, under strict control. send we would for us it this reason Because process using and

### 4.2 I/O processes

To ensure that messages are sent as soon as possible it is important to run the I/O processes at high priority. This further complicates the access to the heap; now we must control access from processes running at two different priorities.

Each output process has a queue of messages awaiting transmission; the queue is stored in the heap. The activation of the output process is controlled by a counting semaphore. The sequence of actions that occur when a message is sent are listed below.

- 1. When a task is evaluating an expression, the reduction process needs to send a message to another processor. This can occur when an expression pointed to by an output indirection is required evaluated by the task

- 2. The reduction process must now create a message holder which contains the type of the message, some operands to the message and the address of any expressions to be sent.

- 3. Depending on the destination, the reduction process places the message holder in one of the three output queues. A semaphore is signalled to indicate that another message has been placed on the queue.

- 4. The reduction process may be able to continue evaluation of the current task, or may have to begin evaluation of a different task.

- 5. An output process is restarted by the semaphore action. It creates an exportable version of the message, storing the result in a buffer. The message is transmitted from the buffer across the INMOS link in a single block.

- 6. The input process of the receiving transputer reads the message into an input buffer. The action of the input process depends on the type of message received, but typically it involves some access to the heap and perhaps the creation of a task.

In order to export a task we need to make exportable copies of the Vap node associated with a task. The only complication here is that we must create input indirections for each of the pointers in the Vap node. The input process of the receiving processor, creates the corresponding output indirection nodes.

# 4.3 Garbage collection and heap consistency

In this section we investigate some of the practical problems with the transputer implementation of the garbage collection algorithm from,<sup>23</sup> described in Section 2.5. There are two major problems to be overcome. Firstly we must organise the data structures, so that the problems of overflow are minimised. Secondly we must maintain a consistent heap in the presence of multiple concurrent processes, all of which share the heap as a common resource. We deal with these problems in order.

Because we have a local semi-space collector, it is possible for high-priority and low-priority allocation to occur from opposite ends of the active semi-space. This can be seen in Fig. 5. The low priority reduction process allocates from the part labelled R, the high-priority I/O processes allocate from the part labelled C. The input indirections are held in I<sub>A</sub> and I<sub>B</sub>.

Figure 5. Heap allocation in a dual-priority system.

A garbage collection is induced whenever the memory labelled R gets too close to that labelled C in Fig. 5. Because the high-priority process may have interrupted the reduction process anywhere, there may be a partially filled-in node in the heap. We must therefore resume the low-priority process before initiating a garbage collection. Fortunately, a result from Ref. 24 allows us to deduce the largest heap allocation that may be performed by the reduction machine and we can therefore place an upper bound on the uncertainty in position of the bottom of heap pointer. Provided there is room for both the largest possible allocation by the reduction process and the size of the block required by the high-priority process, the heap allocation can succeed.

process, the heap allocation can succeed.

The output indirection nodes may be placed in the heap – provided that we link them all together. This linked list is searched after the copying phase of the semi-space collector. Any output indirection nodes that have not been copied are now garbage; a decrement reference count message must therefore be sent to the relevant processor.

The input indirection table is kept in two parts, labelled I<sub>A</sub> and I<sub>B</sub> in Fig. 5, at the top of each semi-space. There is a free-list from which input indirection nodes are allocated. If this is empty, the input indirection table may be extended in the inactive semi-space (as shown in Fig. 5, where I<sub>B</sub> is shown growing downwards). Input indirection nodes are deleted when their reference count falls to zero – the locations are then chained into the free-list. After the copying phase of the garbage collector the free-list is examined in an attempt to return as much as possible of the input indirection nodes must have fixed addresses because they are referenced externally. The alternative would be to broadcast an input indirection nodes new location.

nodes new location.

The second problem is to maintain heap consistency with the above data structures. The heap must be in a stable state when a garbage collection is initiated. There are two parts to this.

- 1. There must be no nodes in the heap which are only partially filled in.

- 2. The registers of the descheduled process must be in a consistent state. To be in such a state, it must be known which machine registers are pointers.

which machine registers are pointers.

The first criterion means that a node never contains bad pointers, and that therefore we are always permitted to follow pointers in the heap. The second means that we may consistently update the pointers in the descheduled process's register set.

The use of two priority levels creates extra problems: the reduction process may be interrupted at any point, including the few actions which must be completely indivisible. These actions can only be made indivisible by also running at high priority; to achieve this a routine which changes the priority of a process is used; this is the subject of the next subsection.

# 4.4 The change-priority routines

In this subsection we will look at two ways of efficiently changing a low-priority process into a high-priority process and back again. We will consider the general solution to this problem, and then look at a faster

solution which is suitable for implementing certain kinds of critical sections.

To understand the solution, we must look at the process-scheduling methods employed by the transputer. There are two transputer scheduling instructions that we make use of: runp and stopp. The first, runp, causes a process to be added to the relevant transputer process queue. The workspace of this process is pointed to by the transputer Areg ANDed with -2, the least significant bit being used to determine the priority level (low priority is 1 and high priority is 0). The new program counter is taken from the first negative location of this new workspace. The stopp instruction stops the current process saving the program counter in the first negative location of the old workspace.

When a low-priority process is interrupted by a high-priority process, its state is preserved in locations near the bottom of memory. We can therefore recover them by loading from these locations if we desire. It is also possible to set up these locations for passing values from the high-priority process to the low-priority process, provided that we know which low-priority process is currently suspended. We now look at codes that will perform a general change of the priority of the executing process from low to high. This will work even if the high-priority process is suspended whilst waiting on communications channels.

```

instruction.*/

change

general Lo-Hi

stopp

IptrSaveLoc

WptrSaveLoc

1dnl BregSaveLoc

AregSaveLoc

KillIptr

ldnlp KillWptr

workspace

ldpi

space

-initialised

0

*

10.

(L2-L1); 1

*

... */

ldnlp

currently 11

currently 14

currently 12

currently 13

a dummy work

stnl

stnl

ldnl

code for a

into

-1;

load PC

mint;

mint;

mint;

mint;

mint;

mint;

runp

pre-

ldc

stl

ದ

11:

12:

*

```

Downloaded from https://academic.oup.com/comjnl/article/34/4/290/368637 by guest on 21 August 2022

The final two lines are optional and can be used to pass the values of the Areg and Breg from the low-priority process to the high-priority process. It relies on a pre-initialised area of memory which contains a stopp instruction, and an area in which it can put the program counter on executing this instruction. The code length and execution time for the above code are given in the following table. The extra code size and execution time are associated with the dummy workspace and the execution of a stopp instruction. The first column represents the number of transputer registers passed.

| Code length Execution time bytes) (no wait states) | 28 + 11<br>31 + 11<br>34 + 11 |

|----------------------------------------------------|-------------------------------|

| Code length (bytes)                                | 16+5<br>18+5<br>20+5          |

| Parameters                                         | 0 1 2                         |

295

```

change

runp; stopp

general Hi-Lo

adc

for a

ldlp 0;

code

```

In this case it is impossible to pass any registers to the low-priority process. The code length and execution time

| Code length Execution time (bytes) (no wait states) | 23 |

|-----------------------------------------------------|----|

| Code length<br>(bytes)                              | 4  |

| Parameter                                           | 0  |

relies on the fact that the suspended low-priority process never deschedules, then a faster solution is possible. can guarantee that the high-priority will never be executed.

```

change

ldnl BregSaveLoc

AregSaveLo

a fast Lo-Hi

ldpi

workspace

14 */

oad PC ... */

stl-1; 1dlp 0

(L2-L1);

13

currently 14

mint; ldnl //

currently

code for

into

mint;

runp

ldc

/* load

11:

122:

*

```

to pass the transputer registers from the low-priority process to the high-priority process. The code length and execution times are given in the again possible following table.

| Code length Execution time (bytes) (no wait states) | 16 | 19 | 22 |  |

|-----------------------------------------------------|----|----|----|--|

| Code length<br>(bytes)                              | 9  | ∞  | 10 |  |

| Parameters                                          | 0  | _  | 2  |  |

the nse may To change back to low priority we following code.

```

change

IptrSaveLoc

2 */

stnl AregSaveLoc

ပ

BregSaveLo

a fast Hi-Lo

ldpi

resumption PC

*

14 */

currently 13

12

(L4-L3)

stnl

stnl

currently

Currently

for

mint;

mint;

stopp

mint;

ldc

load

code

L3:

```

some of the registers The code lengths and This time it is possible to pass back to the low-priority process. execution times are:

| Code length Execution time (bytes) (no wait states) | 17<br>20<br>23 |

|-----------------------------------------------------|----------------|

| Code length<br>(bytes)                              | 5 6            |

| Code Parameters (bytes)                             | 0 1 2          |

This concludes a presentation of the low level details We are mainly interested in the associated with changing the priority levels of currently second version, as it permits interlocking, via semaphores, of processes at different priorities. executing processes.

### 4.5 Testing tags

Downloaded from https://academic.oup.com/comjnl/article/34/4/290/368637 by guest on 21 August 2022 determine types at run time, but are used to distinguish different sorts of objects of the same type. We may think programming language. In a lazy language they are also used to mark closures. Closures may be thought of as recipes that tell us how to compute a value, when we have union type in the are not tags Unlike traditional languages, r for selectors already done so. as of them not

language, because many instructions depend on the type Tag testing is a common operation in a lazy functional data that is an argument to the instruction.

programming community concerns the representation of oriented approach is required. The tag is then a pointer to a table of addresses. Each entry in the table corresponds to an operation to be performed. For One of the current debates within the functional these tags. It is common ground that some form of object example the first entry might evaluate the object, second might print it, and so on. to a table of addresses. corresponds to an operati

the least significant bit of the tag, which indicates whether a node is already evaluated.<sup>3</sup> They claim that some 70 per cent of the time that this bit is tested, the nodes are evaluated. An alternative view is that of nodes are evaluated. An alternative view is that of Peyton Jones and Salkild.26 They claim that it is easier to Augustsson and Johnsson content that one should test always jump through the tag, in a similar way to the traditional G-machine.

In theory Augustsson and Johnsson are right. Their scheme results in at most one pipe-line break and, with the right sort of hardware, it is possible than an intelligent prefetch could hide most of this penalty. In practice, on correct. This is the case even though there are always two Salkild and traditional hardware, Peyton Jones pipe-line breaks.

the and Salkild. To do so, we will give the code and timings for oę We now perform a post hoc justification of approach we took, which is that of Peyton Jones justification We now perform each approach.

```

Φ

tabl

returns

code

offset into

is unevaluated,

load tag

*jump to

which

return:

offset

item

immediately

0

the

gcall

gcall

ldnl

ldnl

ΙĘ

```

and assuming no memory fetch cycles, this code executes in 10 machine cycles. The in-line part of the code is 3 bytes lies between 0 and 16 Provided that offset

```

*

pointer

*

table

bit clear

tag

e a

to

offset

on

ìn

clears

into

jump

create

code

jumps

load

copy

bit

et

offs

4

IJ

₩

0

gcal.

ldnl

ldnl

dnp

ldc

and

adc

сj

```

\$\text{\scalars}:

/\* code as before '

The in-line code size is now 9 bytes. If the branch is taken the above executes in 9 cycles. If it is not taken the code executes in 15+4 cycles, the extra four cycles being required to return. The expected time for this code, using Augustsson's 70 per cent rule, is then 12 cycles.

Therefore, the expected time to execute is the same in both cases, although Augustsson's code is 4 bytes larger.

# 4.6 Making tag testing more efficient

In the paper specifying the parallel abstract machine, <sup>23</sup> each node in the program graph has a number of fields – an evaluator, a pending list, a task-executing flag, and a tagged object. The Vap nodes require all three extra fields. To speed up the selection of the correct operation, the evaluator and the task-executing flag are made part of the object's tag. This means there are more tag tables, for Vap nodes, but there is no need for run-time tests on these extra flags.

We also note – as discussed in the specification paper – that some of these fields are not needed on some types of objects. For example, integers do not need to have evaluators, pending lists, or a task-executing flag. The HDG-machine therefore does not have these fields for integers.

We now discuss the performance of the resulting system.

# 5. PERFORMANCE OF THE SYSTEM

After describing the hardware and software used in the benchmarking, we analyse the results obtained from the HDG-machine. The following points are to be stressed.

- There is no limit to the grain size of a task, i.e. a task can be arbitrarily small.

- can be arbitrarily small.

The only way to introduce parallelism is via annotations for evaluation transformers.

This is clearly less than optimal. For example we could re-write any of the benchmark programs so that only tasks of a reasonable size were created. It is also the case that hand annotation of the programs for parallelism would result in better performance.\*

The following restrictions on the applicability of the results should also be borne in mind.

\* The nfib benchmark - discussed later - gives a clue as to the expense involved.

- The implementation uses only four Transputers. It may be that the parallelism does not scale.

- The abstract machine is based on a slightly outdated technology (similar to the ⟨ν, G⟩-machine).<sup>3</sup> This may mean that the costs of exporting work have been understated.

- The code generation is naïve, again causing an understatement of the costs of exporting work. Better code generation will result in an increase in the relative cost of the parallelism overheads.

The first restriction is the most worrying. The ZAPP project<sup>15</sup> found that divide-and-conquer parallelism scaled to at least 40 transputers.\* The other two items are less significant, as we will hopefully be able to increase the granuality of tasks sufficiently to overcome the problem.

#### 5.1 Hardware

The hardware used was a network of T800-25 transputer boards – developed mainly for ESPRIT 1219 (PAD-MAVATI) – which had an unusually large memory size (16 Mbyte DRAM). The DRAM memory access time is three wait-states. The large size enables efficient execution of functional and symbolic applications, because the larger the heap space available, the less frequently garbage collections are required.

#### 5.2 Network

Downloaded from https://academic.oup.com/comjnl/article/34/4/290/368637 by guest on 21 August 2022

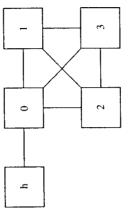

Figure 6. Network used for benchmarking.

The fully connected network of Fig. 6 was used. There were two reasons for this.

- It was readily realisable at that point in both our project and PADMAVAI.

- We were reluctant to write through-routing software for the T800. The PADMAVATI consortium was to provide fast global communication via a dynamic network (available since 1990 as Thomson's DYNET), and INMOS were rumoured to be working on their own solution (the HI).

### 5.3 Compilation

Functional programs were compiled to transputer machine code by first compiling them to parallel HDG-machine code, <sup>11,14,23</sup> and then macro-expanding this code to transputer machine code.

### 5.4 Load distribution

The load distribution mechanism was very simple

$\star$  The problem of shared data access does not figure in the ZAPP results.

it cyclically requested a task. was given from its neighbours until it when a processor had no work,

and at least one of them had not been started yet. This idea was borrowed from ZAPP.<sup>15</sup> Even though it is a fairly primitive algorithm, the theoretical results from <sup>16</sup> neighbour would send a task if it had at least two tasks, seem to show that any algorithm is within a constant fraction of an optimal distribution strategy.\* work

### 5.5 Analysis of nfib

Table 1. Timings for nfib

|                            | 4       | 0.373                   |

|----------------------------|---------|-------------------------|

| ocessors                   | 3       | 0.478                   |

| Time (in s) for processors | 7       | 0.675                   |

| Time (ir                   | _       | 1.284<br>0.996<br>0.813 |

|                            | E       | 20<br>20<br>20<br>20    |

|                            | Program | nfib<br>nfib<br>nfib    |

<sup>\*</sup> Parallel code with BSPAWN instructions deleted.

```

(n-1)

(n-2) + nfib

otherwise

n < 2

+nfib

n=1,

>nfib

>

```

The number of nfib calls per second when running on four processors is 58689. Relative to the parallel code running on a single processor the efficiency using four processors is 86 per cent and the speed-up is 3.4.

The second row in Table 1 shows what happens when is executed. The version in the third row differs from that in the second, because it is sometimes able to avoid building the parallel code without BSPAWN instructions graph.

For comparison, the purely sequential code is given in the third row. It runs in 0.813 s, giving 26926 function calls per second. Also included in this row is the same - purely sequential - run with four processors. The slight slow down is because the root transputer must respond to messages requesting work. program

used by the simple compiler; the change is that code is In Table 2 we include the result for a more sophisticated The graph operations are the same as those generated to make use of the transputer temporary registers to hold intermediate values. compiler.

g current can onr It implemented. implemented as a peephole optimizer to not was compiler

Table 2. Timings for fnfib

|                                    | Time (                      | Time (in s) for processors | ocessors |       |  |

|------------------------------------|-----------------------------|----------------------------|----------|-------|--|

| Program                            | _                           | 2                          | 3        | 4     |  |

| fnfib 20<br>fnfib 20*<br>fnfib 20† | 1.002<br>* 0.709<br>† 0.575 | 0.524                      | 0.367    | 0.294 |  |

Parallel code with BSPAWN instructions deleted

Analysis of tak 5.6

H. KINGDON, D. R. LESTER AND G. L. BURN

Table 3. Timings for tak

|                   | Time ( | Time (in s) for processors | ocessors |       |

|-------------------|--------|----------------------------|----------|-------|

| Program           | _      | 2                          | 3        | 4     |

| tak 18 12 6 5.215 | 5.215  | 2.672                      | 1.858    | 1.433 |

| >tak x y z=z,     | z=z,   | z, x<=y                    | 7        |       |

```

y)),

x (x

> N X

(x-1)

(y-1)

(z-1)

otherwise

(tak

(tak

tak

= tak

\wedge \wedge \wedge \wedge

```

can be evaluated strictly. The tak benchmark partitions very well into tasks of roughly equal size. On four We have included the tak benchmark for comparison with LISP systems. The code generated for this problem is not ideal, as the current evaluation transformer analysis is not sophisticated enough to spot that the term (z-1) processors we are therefore obtaining an efficiency of 91 per cent, and a speed-up of 3.6.

## 5.7 Analysis of queens

| =queens' n n []<br>=1   | >queens' p (n+1) b=sum [queens' p n (t:b)]<br>t < -[1p]; | safe t 1 b] | =True     | ~ = p &          | q+n = p & | q-n = p & | safe $q(n+1)$ ps |

|-------------------------|----------------------------------------------------------|-------------|-----------|------------------|-----------|-----------|------------------|

| v.                      | p(n+1)b=s1                                               |             |           | Ш                | ď         | ָם        | ŭ                |

| >queens n<br>>queens'p0 | >queens' I                                               | ٨           | >safeqn[] | >safe q n (p:ps) | ٨         | ٨         | ٨                |

This benchmark calculates the number of ways to queens on to an  $n \times n$  chessboard, such that no queen checked any other. In particular we have calculated ં values for n = 4 and n = 4place n

Table 4. Timings for queens

|                            | 4       | 0.009  |

|----------------------------|---------|--------|

| ocessors                   | 3       | 0.009  |

| Time (in s) for processors | 2       | 0.011  |

| Time (i                    | _       | 0.012  |

|                            |         | 40     |

|                            | Program | dneens |

5. Profile of function calls for queens Table

|       | 9        |        |         |      |           |      |

|-------|----------|--------|---------|------|-----------|------|

|       | dueens 6 | -      | 153     | 1043 | 1043      | 2168 |

| Calls | gueens 4 | -      | 17      | 75   | 75        | 100  |

|       | Function | dneens | dneens, | sum* | generatet | safe |

This assumes that sum is defined recursively

<sup>†</sup> Purely sequential code generated.

<sup>†</sup> Purely sequential code generated.

<sup>\*</sup> There could of course be problems with shared data structures which become distributed over the machine.

compiled for the list auxiliary function that is comprehension. The

a problem that too small. The message overhead to export a task and trieve its result is approximately 6 ms. In queens 4 this means that each task that is exported is taking about ms, and the maximum possible speed-up is achieved with three processors.\* On a more positive note we see that as soon as the problem size is expanded to queens 6 we achieve reasonable speed-ups. The speed-up on four retrieve its result is approximately 6 ms. We can clearly see the effect of having processors is 2.8

This concludes our presentation of the results; we now discuss some of the issues that we feel deserve further investigation.

## 6. FURTHER WORK

а number of features of the system that we would have liked to investigate, but had insufficient time to do so. We of In the course of the project we became aware discuss some of them in this section.

## 6.1 Caching remote graph

In the current implementation it is possible for a piece of graph to have two different input indirection nodes pointing to it. When it is copied to a remove processor via one route, the remote processor does not know that it already has the value if it is accessed by the second route.

To correct this we must implement a hashing scheme to common-up remote references. In large-scale applications this will be vital. a hashing

# 6.2 Limitations of evaluation transformers

of the we used - with only four - we are unable to compile good code for the analysis that can be performed by any abstract terpreter. In the scheme we used - with only for to the complexity are practical limits concat function. evaluators

If we need to evaluate each element in the list returned as the answer to concat xs, then will need to evaluate all of the elements in each list of xs. The problem here is that - working with a fourth-point domain - the abstract interpreter is unable to prove this fact for us. A more sophisticated abstract interpreter could solve this for us, but eventually there is a limit to what this smarter interpreter can do as well.

# 6.3 Constants on distributed machines

language is the trade-off between copying data and recreating it. This surfaces most clearly in functional languages when we consider *Constant Applicative Forms* (abbreviated CAFs). A simple example presenting an problem with the distributed implementation of any obvious choice is

K on each processor. this case we should make a copy .S CAF i slightly larger

This is the list of integers between 1 and 100. In this case is probably processor.

$$> y = [0..]$$

This is the infinite list of integers, and we would probably wish to have a single copy which is exported when required.

### 6.4 Trees vs. lists

generally do not parallelise well. The use of trees (when they are balanced) should result in a better partition of the data-structure over the distributed memory. data-structures main their as using lists Programs

## 6.5 The I/O bottleneck

access the file store, resulting in a bottleneck. If the hardware were adapted to support a number of file interface points in the network, multiple I/O operations As implemented our machine uses a single transputer to could become significantly faster.

# 6.6 Large parallel applications

Although we have shown that the techniques we used work for small problems, we have still to demonstrate that the same techniques work for 'real' applications.

Downloaded from https://academic.oup.com/comjnl/article/34/4/290/368637 by guest on 21 August 2022

## 7. CONCLUSIONS

the beginning of Section 5 – we have demonstrated that lazy functional programming can be efficiently implemented on a distributed architecture machine. This has been achieved without user annotations. This is a feature that we feel will be increasingly important as the size of parallel programs increases: at some stage it is likely to for infeasible to manually place annotations Within the constraints imposed on our project allelism.

functional language turned out to be a very important tool in developing our implementation on the transputer network. Firstly, it enabled us to debug the specification of the parallel abstract machine. Secondly, each abstract The specification of our parallel abstract machine in a as a function from one state of the machine to another; complex instructions were specified and the composition of simpler subfunctions, each of which modelled a simple involved giving a sequence of transputer instructions for each function. On reflection, the hardest part of our machine instruction was implemented in the specification action in a real implementation. Therefore, the translation from our specification to a real implementation communication system, probably because it was specified a much higher level than the rest of the abstract was implementation on the transputer network

In this paper we have given most of the building blocks for constructing an efficient implementation of lazy functional languages on a transputer network. Although

<sup>\*</sup> It is conjectured that the rather slower time for two processors is related to the particular timing sequence of task requests to the root transputer.

of transputer instructions, our experimental results have been better than expected, so much so that adopted a simplistic way of generating code, macrothey compare favourably with much better engineered implementations. This encourages us to pursue the work further. Specifically, three things need further investiinto expanding the abstract machine instructions duences gation:

- better code generation;

- structuring the system in a better way; and

- extending the system to a larger transputer network.

We briefly discuss each of these in turn.

Refs 6, 26 and 27 for example. Better code generation will therefore involve combining these techniques with some of our insights concerning the transputer architecture. Over recent years, compiling code for lazy functional languages has become a well-understood problem -

and a in an unnatural way. This also had significant affects on the speed of the system, as 'global' values could only be reliable, but it forced us to structure the implementation accessed using quite complex procedures, and further-more, required the storing of extra information on each One of the real difficulties in constructing the transnode in the graph. Hopefully these inadequacies can be assembler. Not only was the assembler puter implementation was the lack of good tools, overcome as better tools become available. suitable

implement through-routeing, which would have allowed us to use We made a deliberate decision not to

### REFERENCES

- allocation. Information Processing Letters 25 (4), 275-279 A. W. Appel, Garbage collection can be faster than stack (1987).

- L. Augustsson, Compiling lazy functional languages, Part II. Doctoral thesis, Chalmers Tekniska Högskola,

- borg, Sweden (1987). L. Augustsson and T. Johnsson, The  $\langle v, G \rangle$ -machine: An abstract machine for parallel graph reduction. In ACM Proceedings of the Functional Programming Languages and Architecture Conference 11–13 September 1989, edited D. B. MacQueen, pp. 202-213. Computer 3

- and G. Sofi, Implementation of a parallel logic + functional language. In Parallel Computers: Object-Oriented, Functional Logic, edited P. C. Treleaven, chapter 7, pp. 175-214. G. P. Balboni, P. G. Bosco, C. Cecchi, R. Melen, C. Moiso Wiley (1990). 4.

- D. I. Bevan, Distributed garbage collection using reference counting. In *PARLE Parallel Architectures and Languages Europe, Eindhoven, The Netherlands,* volume 2, edited J. W. de Bakker, A. J. Nijman and P. C. Treleaven, pp. 176–187. Lecture Notes in Computer Science [LNCS], Springer, Heidelberg (1987).

- A. Bloss, P. Hudak, and J. Young, Code optimizations for lazy evaluation. Lisp and Symbolic computation: An International Journal 1 (2), 147–164 (1988).

A. Bloss, P. Hudak, and J. Young, An optimising compiler

- for a modern functional language. The Computer Journal 32 (2), 152-161 (1989).

- Burn, Evaluation transformers A model for the lel evaluation of functional languages (extended parallel evaluation of functional languages (extended abstract). In Proceedings of the Functional Programming tember 1987, edited G. Kahn, pp. 446-470. LNCS Springer, Heidelberg. Conference, Architecture Languages and Computer G.L ∞:

- G. L. Burn, Abstract Interpretation and the Parallel Evalu-

arrived, with hardware through-routeing, we should be able to try out our ideas on larger transputer networks, Now that the HI network. scale. seeing how things bigger transputer

very encouraging. better-engineered, more general system, and being able to analyse experimental results have been ಡ look forward to developing Our

### Acknowledgements

Our colleagues at the GEC Hirst Research Centre, John Robson and Krste Asanovic, were very helpful in assisting us with our implementation on a transputer network. Their knowledge of the transputer architecture and help with various tools was most appreciated. David Bevan and Rajiv Karia also performed much valuable foundational work when they were working on this project. We would like to thank Simon Peyton Jones and the GRIP team for some very stimulating discussions on the parallel implementation of lazy functional languages.

also grateful to Bruce Cameron and Andrew Stitcher for permitting us to rewire and use PADMAVATI to run use his implementation of abstract interpretation. We are Thanks are due to Sebastian Hunt for allowing some further experiments after we have left GEC.

This work was performed whilst the authors worked for GEC Hirst Research Centre and was partially funded by ESPRIT Project 415, 'Parallel Architectures and Languages for AIP – A VLSI-Directed Approach'.

- ation of Functional Languages. Doctoral thesis, Imperial College, University of London (1987).

- G. L. Burn, Developing a distributed memory architecture for parallel graph reduction. In *Proceedings of CONPAR* 88, *Manchester*, UK. 10.

- on the evaluation transformer model of computation. In G. L. Burn, A shared memory parallel G-machine based Proceedings of the Workshop on the Implementation of Lazy Functional Languages, Aspenäs, Göteborg, Sweden, September 1988.

- G.L. Burn, Overview of a parallel reduction machine project II. In Proceedings of PARLE 89, Eindhoven, The 2

- Netherlands, volume 1, edited E. Odijk, M. Rem and J.-C. Syre, pp. 385-396. LNCS 365, Springer, Heidelberg. G. L. Burn, Using projection analysis in comfpiling lazy functional programs. In Proceedings of the 1990 ACM Lisp and Functional Programming, Nice, Conference on

- pretation and Compilation. Research Monographs in Parallel and Distributed Computing, Pitman in association Conference v., France, pp. 227-241.

G. L. Burn, Lasy Functional Languages: with MIT Press (1991) 4.

- grams on a virtual tree of processors. In Proceedings of the First Conference on Functional Programming and Computer F. W. Burton and M. R. Sleep, Executing functional pro-Architecture, Portsmouth, New Hampshire, October 1982, pp. 187-194. 15.

- Adaptive ms. IEEE Transactions on Software Engineering SE-12 (5), 662-675 distributed systems. D. L. Eager, E. D. Lazowska, and J. Zahorjan, load sharing in homogeneous 16.

- Fairbairn and S. C. Wray, Code generation techniques or functional languages. In *Proceedings 1986 ACM* for functional languages. In Proceedings 1986 Conference on Lisp and Functional Programming, bridge, Massachusetts, USA, pp. 94-104. 17.