Brigham Young University BYU ScholarsArchive

Theses and Dissertations

2005-06-16

## The Hybrid Architecture Parallel Fast Fourier Transform (HAPFFT)

Joseph M. Palmer Brigham Young University - Provo

Follow this and additional works at: https://scholarsarchive.byu.edu/etd

Part of the Electrical and Computer Engineering Commons

### **BYU ScholarsArchive Citation**

Palmer, Joseph M., "The Hybrid Architecture Parallel Fast Fourier Transform (HAPFFT)" (2005). *Theses and Dissertations*. 555. https://scholarsarchive.byu.edu/etd/555

This Thesis is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact scholarsarchive@byu.edu, ellen\_amatangelo@byu.edu.

# THE HYBRID ARCHITECTURE PARALLEL FAST FOURIER TRANSFORM (HAPFFT)

by

Joseph McRae Palmer

A thesis submitted to the faculty of

Brigham Young University

in partial fulfillment of the requirements for the degree of

Master of Science

Department of Electrical and Computer Engineering

Brigham Young University

August 2005

Copyright © 2005 Joseph McRae Palmer

All Rights Reserved

## BRIGHAM YOUNG UNIVERSITY

## GRADUATE COMMITTEE APPROVAL

of a thesis submitted by

Joseph McRae Palmer

This thesis has been read by each member of the following graduate committee and by majority vote has been found to be satisfactory.

Date

Brent E. Nelson, Chair

Date

Michael J. Wirthlin

Date

Clark N. Taylor

## BRIGHAM YOUNG UNIVERSITY

As chair of the candidate's graduate committee, I have read the thesis of Joseph McRae Palmer in its final form and have found that (1) its format, citations, and bibliographical style are consistent and acceptable and fulfill university and department style requirements; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the graduate committee and is ready for submission to the university library.

Date

Brent E. Nelson Chair, Graduate Committee

Accepted for the Department

Michael A. Jensen Graduate Coordinator

Accepted for the College

Douglas M. Chabries Dean, Ira A. Fulton College of Engineering and Technology

### ABSTRACT

# THE HYBRID ARCHITECTURE PARALLEL FAST FOURIER TRANSFORM (HAPFFT)

Joseph McRae Palmer

Department of Electrical and Computer Engineering

Master of Science

The FFT is an efficient algorithm for computing the DFT. It drastically reduces the cost of implementing the DFT on digital computing systems. Nevertheless, the FFT is still computationally intensive, and continued technological advances of computers demand larger and faster implementations of this algorithm.

Past attempts at producing high-performance, and small FFT implementations, have focused on custom hardware (ASICs and FPGAs). Ultimately, the most efficient have been single-chipped, streaming I/O, pipelined FFT architectures. These architectures increase computational concurrency through the use of hardware pipelining.

Streaming I/O, pipelined FFT architectures are capable of accepting a single data sample every clock cycle. In principle, the maximum clock frequency of such a circuit is limited only by its critical delay path. The delay of the critical path may be decreased by the addition of pipeline registers. Nevertheless this solution gives

diminishing returns. Thus, the streaming I/O, pipelined FFT is ultimately limited in the maximum performance it can provide.

Attempts have been made to map the Parallel FFT algorithm to custom hardware. Yet, the Parallel FFT was formulated and optimized to execute on a machine with multiple, *identical*, processing elements. When executed on such a machine, the FFT requires a large expense on communications. Therefore, a direct mapping of the Parallel FFT to custom hardware results in a circuit with complex control and global data movement.

This thesis proposes the Hybrid Architecture Parallel FFT (HAPFFT) as an alternative. The HAPFFT is an improved formulation for building Parallel FFT custom hardware modules. It provides improved performance, efficient resource utilization, and reduced design time.

The HAPFFT is modular in nature. It includes a custom front-end parallel processing unit which produces intermediate results. The intermediate results are sent to multiple, independent FFT modules. These independent modules form the back-end of the HAPFFT, and are generic, meaning that any prexisting FFT architecture may be used. With P back-end modules a speedup of P will be achieved, in comparison to an FFT module composed solely of a single module. Furthermore, the HAPFFT defines the front-end processing unit as a function of P. It hides the high communication costs typically seen in Parallel FFTs. Reductions in control complexity, memory demands, and logical resources, are achieved.

An extraordinary result of the HAPFFT formulation is a *sublinear area-time* growth. This phenomenon is often also called *superlinear speedup*. Sublinear area-time growth and superlinear speedup are equivalent terms. This thesis will subsequently use the term superlinear speedup to refer to the HAPFFT's outstanding speedup behavior.

A further benefit resulting from the HAPFFT formulation is reduced design time. Because the HAPFFT defines only the front-end module, and because the back-end parallel modules may be composed of any preexisting FFT modules, total design time for a HAPFFT is greatly reduced.

#### ACKNOWLEDGMENTS

I would like to express my gratitude to Dr. Brent Nelson for his advice and help throughout the course of this project. Especially for his patience in teaching a new graduate student how to correctly perform research.

Thank you also to Sandia National Laboratories for providing the funding for most of this work.

Finally, this thesis would not have been possible without the support of my wife, Betty. I'm grateful for her patience, and for her desire to see me succeed. I'm also grateful for the inspiration that she and our three children have given me.

## Contents

| Α        | ckno  | vledgments                                                | xiii |

|----------|-------|-----------------------------------------------------------|------|

| Li       | st of | Tables                                                    | xvii |

| Li       | st of | Figures                                                   | xx   |

| 1        | Intr  | oduction                                                  | 1    |

|          | 1.1   | Thesis Organization                                       | 7    |

|          | 1.2   | Related Work                                              | 8    |

| <b>2</b> | The   | Fast Fourier Transform                                    | 11   |

|          | 2.1   | Motivation for the FFT                                    | 11   |

|          |       | 2.1.1 Frequency Aliasing in the DFT                       | 12   |

|          | 2.2   | Three Common FFT Algorithms                               | 13   |

|          |       | 2.2.1 The Decimation in Time Radix-2 FFT                  | 14   |

|          |       | 2.2.2 The Decimation in Frequency Radix-2 FFT             | 21   |

|          |       | 2.2.3 The Decimation in Frequency Radix-4 FFT             | 26   |

|          | 2.3   | The Mixed-Radix FFT                                       | 30   |

| 3        | Hig   | Performance FFT Computations                              | 35   |

|          | 3.1   | Hardware Pipelined FFT Architectures                      | 36   |

|          |       | 3.1.1 A Taxonomy of FFT Architectures for Custom Hardware | 37   |

|          | 3.2   | Parallel FFT Algorithms for Software                      | 49   |

|          |       | 3.2.1 The Binary-Exchange Algorithm                       | 50   |

|          |       | 3.2.2 The Transpose Algorithm                             | 54   |

| 4               | The  | Hybrid Architecture Parallel FFT (HAPFFT)                        | 57   |  |

|-----------------|------|------------------------------------------------------------------|------|--|

|                 | 4.1  | Review of the Parallel FFT                                       | 58   |  |

|                 | 4.2  | Mapping the Parallel FFT to Custom Hardware                      | 59   |  |

|                 | 4.3  | The HAPFFT Exhibits Superlinear Speedup                          | 67   |  |

|                 | 4.4  | Experimental Results                                             | 71   |  |

| 5               | Con  | clusions                                                         | 73   |  |

|                 | 5.1  | Future Research Involving the HAPFFT                             | 74   |  |

| $\mathbf{A}$    | Imp  | lementation Details of the HAPFFT                                | 79   |  |

|                 | A.1  | The Fixed Point FFT                                              | 80   |  |

|                 |      | A.1.1 Butterfly Operation                                        | 81   |  |

|                 |      | A.1.2 Timing Behavior                                            | 82   |  |

|                 |      | A.1.3 Overflow Handling and Data-Scaling                         | 83   |  |

|                 | A.2  | Block Floating-Point FFT                                         | 83   |  |

|                 | A.3  | The HAPFFT Implementation                                        | 86   |  |

| в               | Para | allel Efficiency of the Binary-Exchange and Transpose Algorithms | s 87 |  |

| Bibliography 91 |      |                                                                  |      |  |

## List of Tables

| 3.1 | Comparison of Pipelined FFT Architectures                   | 48 |

|-----|-------------------------------------------------------------|----|

| 4.1 | HAPFFT resource requirements                                | 68 |

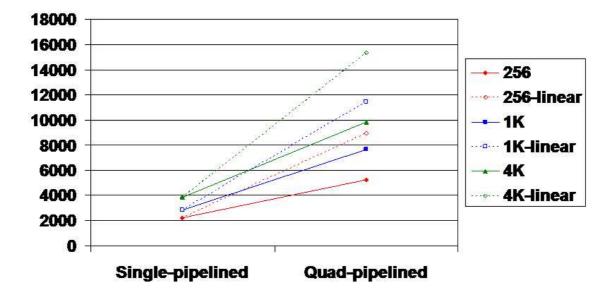

| 4.2 | Results for Fixed-point FFTs on the Xilinx XC2V6000-4 $\ .$ | 72 |

# List of Figures

| 2.1  | Radix-2 and Radix-4 Butterflies                                                    | 13 |

|------|------------------------------------------------------------------------------------|----|

| 2.2  | Simplification of radix-2 butterfly twiddle factor multiplications                 | 16 |

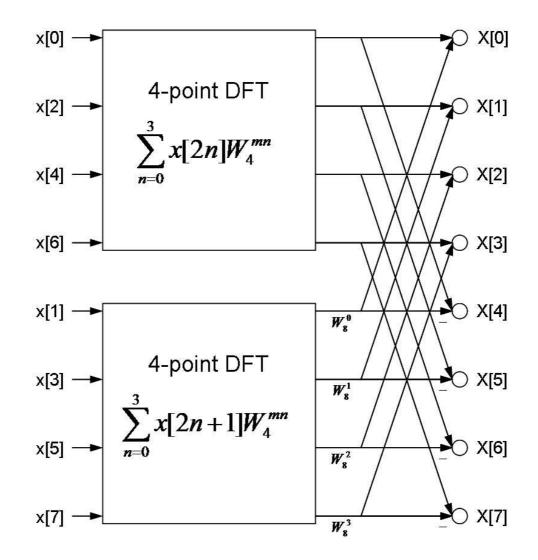

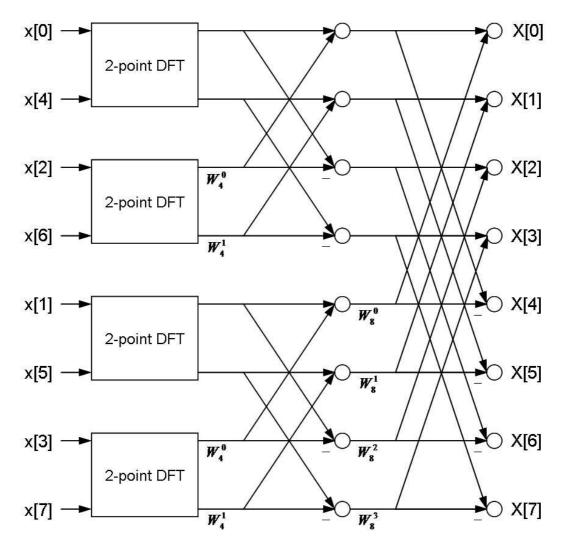

| 2.3  | Data flow graph for 8-point DFT using 4-point DFTs                                 | 17 |

| 2.4  | Data flow graph for 8-point DFT using 2-point DFTs                                 | 18 |

| 2.5  | Data flow graph for 8-point DIT FFT using radix-2 butterflies                      | 19 |

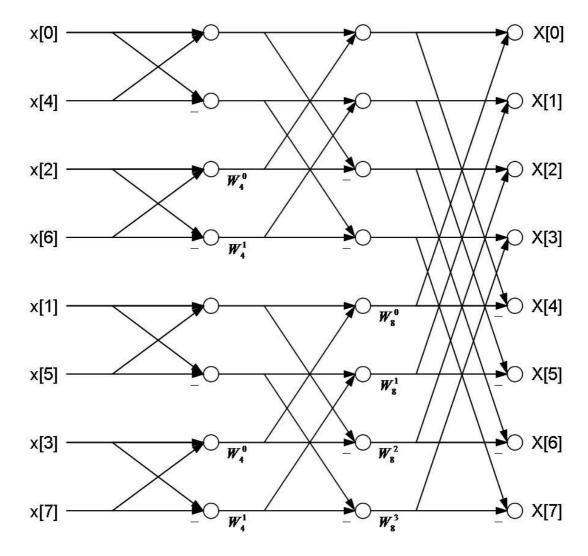

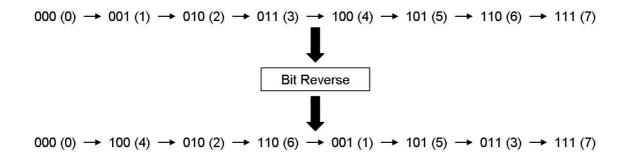

| 2.6  | Bit-reverse operation on address sequence.                                         | 20 |

| 2.7  | Pseudocode for the sequential, iterative radix-2 DIT FFT                           | 21 |

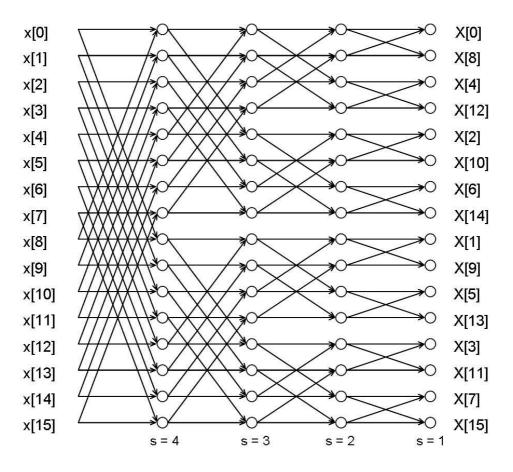

| 2.8  | Data flow graph for a 16-point DIF radix-2 FFT                                     | 24 |

| 2.9  | Pseudocode for the sequential, iterative radix-2 DIF FFT                           | 25 |

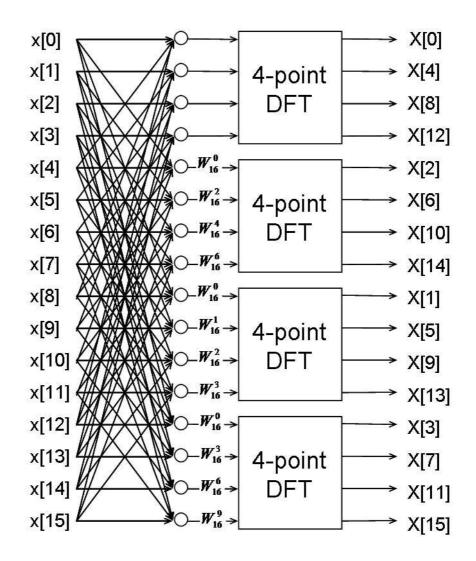

| 2.10 | Data flow graph for 16-point DFT using 4-point DFTs                                | 27 |

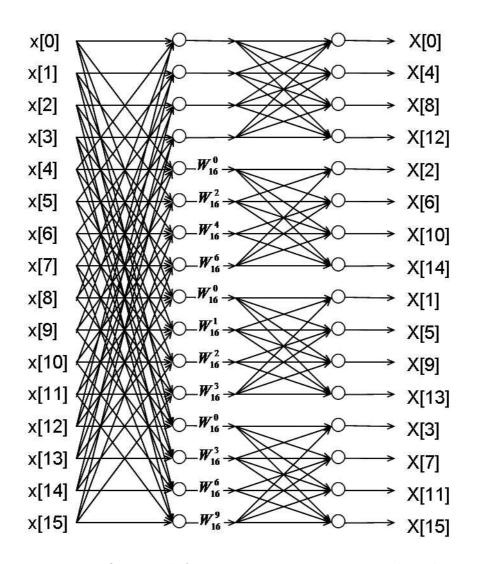

| 2.11 | Data flow graph for 16-point DIF FFT using radix-4 butterflies                     | 30 |

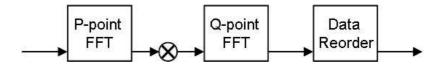

| 2.12 | An $N = PQ$ -point mixed-radix FFT                                                 | 31 |

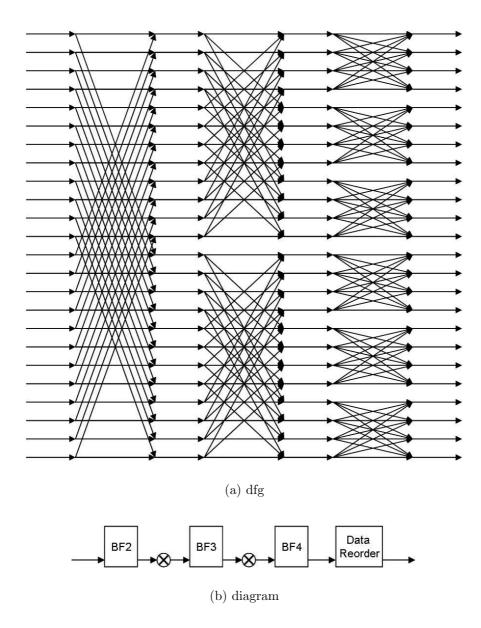

| 2.13 | Mixed-radix 24-point FFT                                                           | 32 |

| 3.1  | A typical DSP processing pipeline.                                                 | 37 |

| 3.2  | Diagram for a general in-place FFT architecture                                    | 39 |

| 3.3  | Pipelined FFT DFG for Figure 2.8                                                   | 40 |

| 3.4  | 16-point implementation of the radix-2 SDF                                         | 42 |

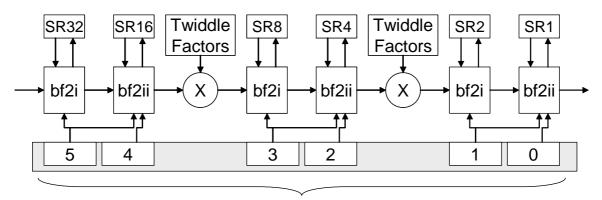

| 3.5  | Single Delay Feedback (SDF) Pipelined 64-point FFT Architectures $% \mathcal{A}$ . | 43 |

| 3.6  | 16-point implementation of the radix- $2^2$ SDF                                    | 44 |

| 3.7  | A multi-delay commutator for the R4MDC. From $[25]$                                | 45 |

| 3.8  | Single- and Multi-Delay Commutator 64-point FFTs                                   | 47 |

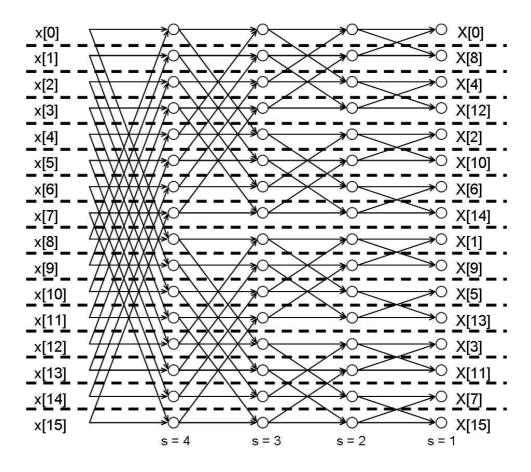

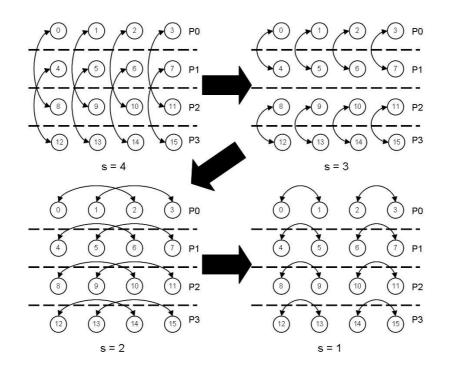

| 3.9  | 16-point FFT data-flow-graph, mapped onto 16 processors                            | 51 |

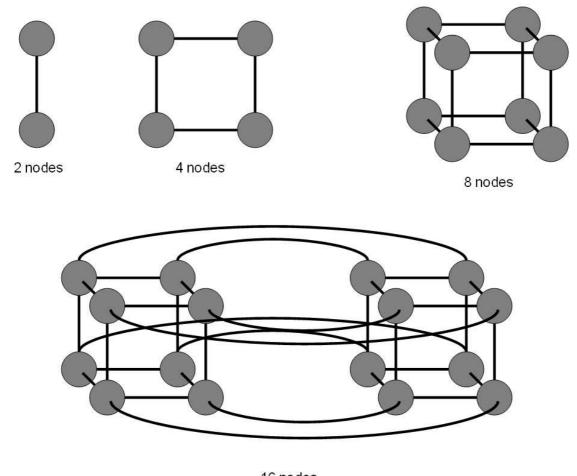

| 3.10 | Hypercube networks consisting of 2, 4, 8 and 16 nodes. $\ldots$ $\ldots$ $\ldots$  | 52 |

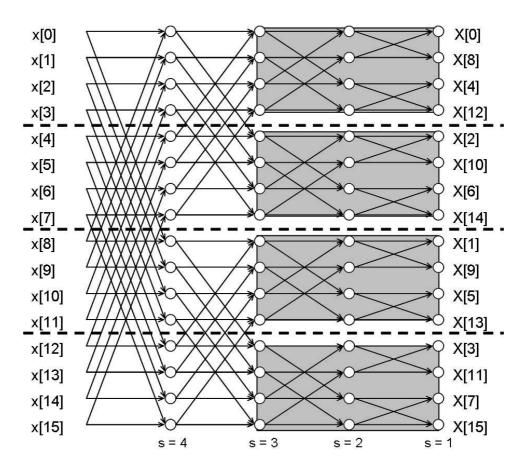

| 3.11 | 16-point FFT data-flow-graph, mapped onto 4 processors                             | 53 |

| 3.12 | Memory plan for the iterative FFT (see Figure 2.7)                                            | 54 |

|------|-----------------------------------------------------------------------------------------------|----|

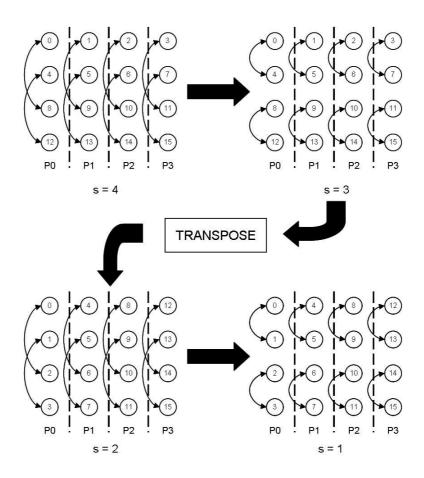

| 3.13 | Memory plan for transpose parallel-FFT algorithm                                              | 55 |

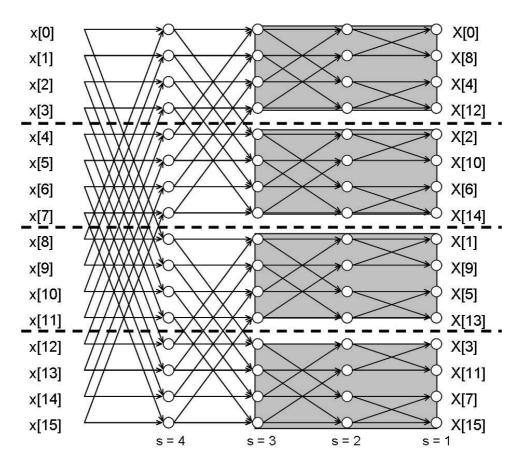

| 4.1  | 16-point FFT data-flow-graph                                                                  | 59 |

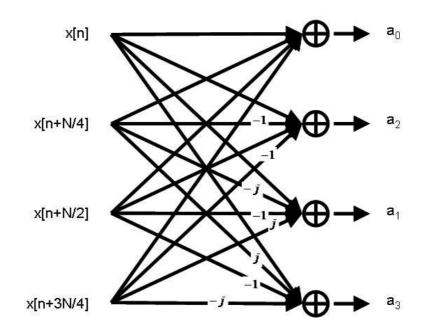

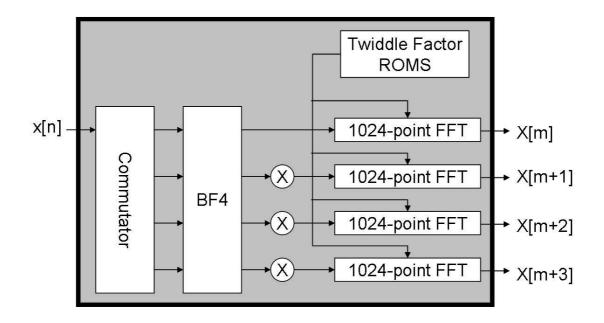

| 4.2  | Module for computing the four DFT input sequences                                             | 63 |

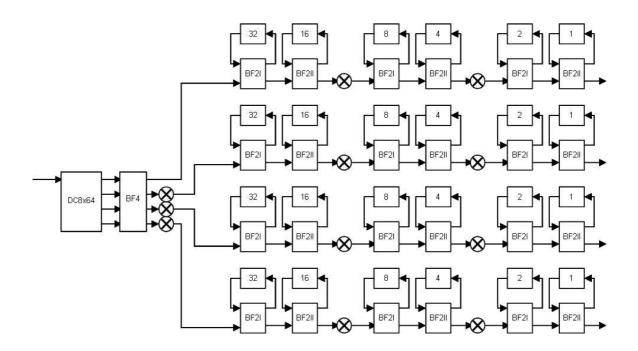

| 4.3  | 4096-point Quad-pipeline HAPFFT                                                               | 64 |

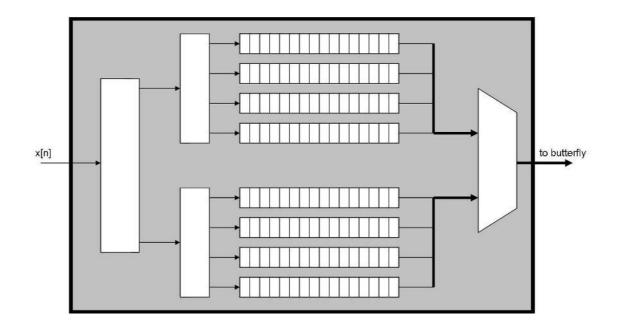

| 4.4  | Delay commutator for a 64-point HAPFFT                                                        | 65 |

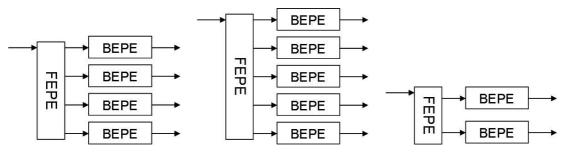

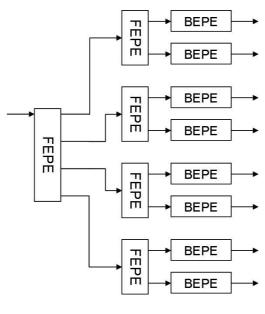

| 4.5  | Variations of the HAPFFT.                                                                     | 66 |

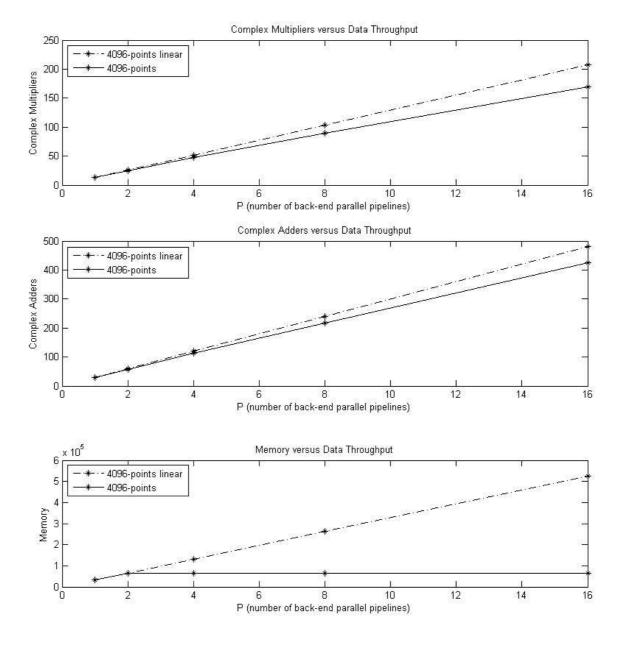

| 4.6  | Resource requirements of the HAPFFT                                                           | 69 |

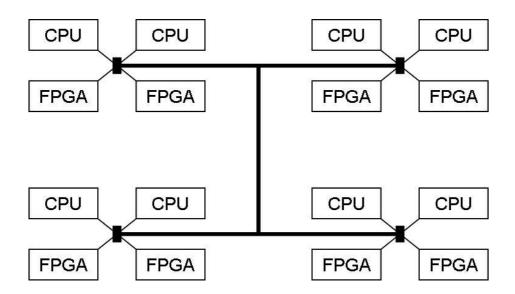

| 5.1  | Hypothetical four-node distributed memory parallel computing system.                          | 74 |

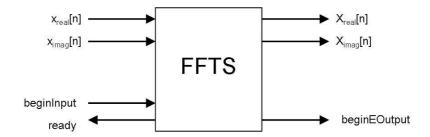

| A.1  | Pinout for fixed-point Radix- $2^2$ FFT $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 80 |

| A.2  | 64-point fixed-point Radix-2 <sup>2</sup> FFT $\ldots$                                        | 80 |

| A.3  | bf2i and bf2ii details                                                                        | 81 |

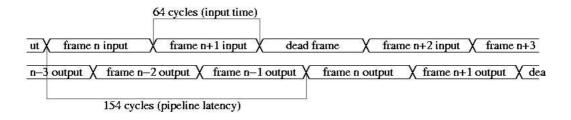

| A.4  | 64-point FFT Pipeline Latency, 18-bit data                                                    | 82 |

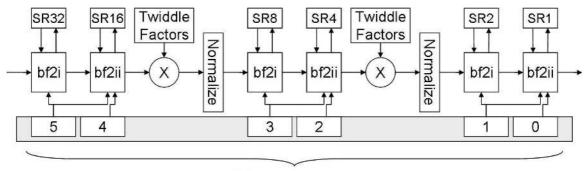

| A.5  | 64-point Single-pipeline Block Floating-point Radix-2 <sup>2</sup> FFT $\ldots$ .             | 84 |

| A.6  | 256-point Quad-pipeline fixed-point Radix-2 <sup>2</sup> HAPFFT $\ldots$                      | 85 |

## Chapter 1

## Introduction

The discrete Fourier transform (DFT) is a fundamental mathematical operations used in digital signal processing. It allows the user to analyze, modify, and synthesize signals in a digital environment. Because of this, it has found a wide range of uses in engineering and scientific applications.

The DFT is performed on a discrete numerical sequence. This is in contrast to the analog Fourier transform, which operates on continuous signals. A discrete sequence is typically a sampling in time of an analog signal, but this is not always the case. For instance, the two-dimensional DFT plays a valuable role in frequencydomain image processing. It operates on discrete data representing image pixels, sampled spatially, rather than temporally.

The DFT produces a spectral profile of the frequency components found within a sequence. In other words, it transforms the sequence from a sequence domain (for example, the time domain, or the spatial domain) to the frequency domain. The resulting transformed signal can then be analyzed, or manipulated in ways that are not possible in the sequence domain, or in a manner that would be difficult or time consuming. For example, a common application of the DFT is in digital filtering. If a noisy input is known to contain a useful signal within a known bandwidth, the DFT can be used to first produce a spectral profile of the signal. Next, one can nullify all signal components outside the target bandwidth. When the now modified frequency profile is subsequently transformed back from the frequency domain to its original domain, the undesired noise will be greatly reduced. Though this same operation can be performed outside the frequency domain, it must be done using time-domain convolution. Convolution becomes prohibitively expensive for anything but small sequences.

Prior to the introduction of the fast Fourier transform (FFT), signal processing had been mostly limited to analog methods; the DFT was seen as an academic curiosity, with few practical uses. This is because in terms of computational *time complexity*, the DFT algorithm exhibits a  $O(N^2)$  execution time.<sup>1</sup> Because it was such an expensive operation, the primitive digital computers of the time could not produce results in a manner that was timely enough for practical applications.

As an example of the computational challenges related to the DFT, in 1964 (the eve of the introduction of the FFT) the CDC 6600 was the premier supercomputer in the world, capable of sustaining 1 million floating-point operations per second (FLOPS). An important signal processing application in that era was radar range discrimination. One of the tasks of a surveillance radar is to determine the distance of a target. This is typically accomplished through some type of signal filtering. The ability of a radar to resolve targets at various distances is known as its range discrimination. Consider a hypothetical radar that can discriminate targets separated by more than 500 m in range. Such a system, if implemented using DSP techniques, would require a digital sampling rate of approximately 1 MHz. Ignoring a large number of details, if the system must detect targets up to 150 Km in distance, it might need to compile a 1024-point DFT every 1 milliseconds. Yet, in 1964, the most powerful supercomputer in the world, the CDC 6600, would have needed at least 8 seconds to complete a 1024-point DFT! Considering that this is an example of a relatively tame radar system, digital filtering techniques were obviously not a practical solution for radar engineers in 1964.

The FFT is an efficient algorithm for computing the DFT. Though variations of the FFT were invented prior to 1965, it was not until that year that the seminal paper by Cooley and Tukey [6] presented the first widely used FFT algorithm. Because the

<sup>&</sup>lt;sup>1</sup>This terminology is adopted from the field of computational theory. The notation O(Z(N)) is defined as "on the order of Z", where Z is some function of N, and N represents the problem size. Thus, the DFT exhibits an execution time "on the order of  $N^{2n}$ ". It becomes prohibitively expensive for anything but the smallest input sequences.

Cooley-Tukey FFT allowed the DFT to be efficiently computed on digital computers, it had a tremendous impact on a wide-range of fields. Using the previous radar example, if the FFT were used to compute the 1024-point DFT, then the CDC 6600 would now only require about 50 milliseconds. Though still too slow for the example system, a DSP solution is now not so far out of reach. Thus, with the adoption of the FFT, a large number of signal processing algorithms became of more than just academic interest.

Despite the tremendous advancements made in digital computers during recent decades, the impact of the FFT continues to be felt. Many technologies enjoyed by the common public would as yet not be possible without the Cooley-Tukey FFT and its derivatives. Synthetic aperture radar (SAR), a type of imaging radar, operates at sampling rates of hundreds of Mega-Hertz, or even Giga-Hertz. A 4096-point DFT might need to be computed every 800 micro-seconds. This is a tremendous computational load, even for modern digital computers. A typical general-purpose computer would be hard-pressed to sustain such a load in real-time. If implemented using the DFT, then the task would be impossible.

Though the FFT offers performance advantages over the DFT, it is nevertheless an expensive operation. This is compounded by the fact that technologies continue to appear which demand ever higher data throughput, executed on larger and larger data sets. For example, some real-time radar systems require a 4096-point DFT to be computed with a data sample rate exceeding 500 million samples per second. Such a *single* module must execute at the equivalent rate of about 40 GFLOPS, and maintain a data throughput of 32 Gbps.

This example shows that some applications of the FFT are beyond any general purpose microprocessor, and even some of the latest multiprocessing systems. Considering that some DSP algorithms require multiple DFT calculations to be executed concurrently, and on a platform that is both small and low-power, it is clear that the demand for high-performance FFT implementations has only increased with time, and will continue for the foreseeable future. There are a number of performance metrics that can be used to evaluate a given implementation of the FFT. The four most useful are data throughput, transform size, resource requirements, and power requirements. This thesis develops a high-performance, parallel FFT architecture, called the Hybrid Architecture Parallel FFT (HAPFFT). The HAPFFT is targeted for single-chip, high-performance, custom hardware applications. Transform size and data throughput were the primary design criteria, with resource requirements of secondary concern. Power was never considered, and thus will not be discussed further.

The first performance metric, data throughput, is the principal means of measuring FFT performance. The FFT is often incorporated into a signal processing pipeline. Data proceeds down this pipeline, and is processed in various ways at different stages, eventually exiting the pipeline fully processed. The rate at which the pipeline can process data is limited by its slowest component. Thus, an FFT stage must be able to provide a minimum level of throughput so that it does not become a processing bottleneck. Using DSP terminology, this minimum pipeline throughput is referred to as the data sample rate, and is measured in terms of *samples per second* (sps). For example, a DSP pipeline running at 330 Ksps must be able to process 330 thousand samples every second.

The second FFT performance metric is transform size. There are a number of reasons for demanding a large transform size. First, typically the FFT is computed on an entire block of discrete data. But, if the block is too large, it may not be possible to efficiently compute an FFT for the whole block. This could be a result of either memory or computational resources. In such a case other techniques exist for approximating a frequency profile for the data block, but the results will be inferior. Second, the *frequency resolution* of the FFT output is proportional to the size of the transform. For example, a 1024-point FFT, though computationally more expensive than a 256-point FFT, will nevertheless have four times the resolution. For applications demanding a high level of precision, it is desirable to use the largest possible FFT transform size. In fact, in some, the input sequence is zero-padded in order to produce a larger input sequence, and thus a finer output resolution. The third FFT performance metric is resource requirements. No matter how high the throughput of a given implementation, it is of little use if its hardware requirements are unrealistic. There exist FFT architectures that though slow, require very little hardware. Likewise, extremely high throughputs can be achieved by the use of massive amounts of hardware. A useful architecture must find a good balance that meets throughput requirements within the resource constraints.

Throughput, and resource requirements are related to the transform size. As discussed earlier in this section, the FFT has a time complexity of  $O(N \log N)$ . Also, its *memory complexity* is O(N). What this signifies is that, for a constant level of throughput, the computational resources grow by  $O(N \log N)$ , and the memory resources by O(N), in proportion to the transform size, N.

One means of measuring how efficient a given FFT implementation uses its resources is to quantify its hardware *utilization*. Utilization is a metric for evaluating hardware efficiency. It is the percentage of time that a given hardware resource is doing useful work.

The best way to decrease the hardware requirements of an FFT implementation, and yet maintain throughput, is to increase the hardware utilization. General purpose processors are inefficient because a large fraction of their composition is made up of functional units that are rarely used. Because of their "jack of all trades" approach, they must be able to handle not only the common case, but also any exceptional cases, no matter how rare. Thus, a significant portion of their hardware is idle at any given instant.

In contrast, custom hardware implementations of the FFT are constrained to a single, or narrow range of uses. Therefore, they can achieve much higher hardware utilization in comparison to a general-purpose processor. This will be directly translated into either lower resource requirements, or higher throughput.

Two common custom hardware FFT paradigms are in use. The first is the streaming I/O pipeline. It consists of a pipeline capable of processing a single stream of data at a constant rate of throughput. A single data sample can be accepted every

clock cycle. The other is the *bursty* pipeline. It will accept a burst of data for a short time, after which the stream must stall until the data is processed.

The streaming I/O pipelines give the best throughput, since the data stream is never stalled. Nevertheless, they are only able to process a single data point every clock cycle. Thus, the maximum performance will be limited by the maximum achievable clock frequency.

The conventional pipelined FFTs achieve high throughput by increasing the computational concurrency. This concurrency is found by pipelining the computations. But, because the clock frequency ceiling imposes limits on the maximum achievable throughput, additional concurrency must be found using other methods.

The parallel FFT has long been used in the supercomputing community [17, 2]. The parallel FFT increases concurrency by executing kernels of the FFT simultaneously in parallel. This approach is orthogonal to hardware pipelining, and thus the two approaches can be easily combined. This translates into an FFT composed of multiple, parallel pipelines. Because of the multiple pipelines, it can now accept multiple samples each clock cycle.

Many recent research efforts [13, 5, 31, 20, 30, 18, 29, 8, 11] have investigated techniques (see Section 1.2 for more details) that allow the hardware FFTs to process more than a single sample each clock cycle. Most have attempted to map the parallel FFT algorithm to hardware. While achieving their performance objectives, such a direct mapping is not efficient. The parallel FFT algorithm assumes execution is on a parallel computing machine with multiple, *identical* processors. Because of the homogeneous nature of the computing environment, data movement is global, and control is complex. A direct mapping of this algorithm to hardware does not take advantage of the flexibility of custom hardware in overcoming these performance and design obstacles.

This thesis proposes an alternative high-performance FFT architecture: the Hybrid Architecture Parallel FFT (HAPFFT). Rather than mapping the parallel FFT to hardware, the HAPFFT instead traces its roots from the custom hardware singlepipeline FFT architectures already in use. It is modular in nature, and includes a custom front-end parallel processing unit which produces intermediate results. The intermediate results are then sent to multiple, independent FFT modules. The formulation hides the Parallel FFTs communication details within the front-end processing unit. No global communication is necessary between the independent, back-end modules.

The HAPFFT's resulting control requirements are therefore simple, and the architecture is straight-forward to implement. Also, the back-end FFT modules can be implemented using the designer's architecture of choice. The HAPFFT's purpose is to enable the designer to incorporate already existing FFT modules into a parallel environment. It formulates the hardware and computations necessary for achieving this integration. Additionally, my analysis and experimental results have shown that the HAPFFT exhibits sublinear area-time growth, or alternatively, *superlinear speedup*<sup>2</sup>. The HAPFFT makes efficient use of hardware resources while achieving its performance goals.

#### 1.1 Thesis Organization

The thesis is organized as follows: Chapter 2 will cover the Fast Fourier Transform, with a focus on deriving the abstract algorithms for computing it. An understanding of these algorithms forms the basis for deriving the HAPFFT. Chapter 3 is a survey of architectural techniques for creating high-performance implementations of the FFT. It will cover pipelined FFT architectures, two common parallel FFT algorithms for parallel processing environments, and survey recent attempts to produce hardware parallel FFTs. Chapter 4 derives the HAPFFT. It gives a general formulation of the architecture, discusses some example implementations of it, and then presents and analyzes the results of my implementation experiments. Finally, Chapter 5 concludes the thesis. It will discuss future research possibilities using the HAPFFT.

<sup>&</sup>lt;sup>2</sup>Superlinear speedup is a phenomenon in which a new custom hardware implementation of some application achieves an M-times speedup (over previous implementations) with less then an M-times increase in hardware.

#### 1.2 Related Work

The fast Fourier transform has been one of the most thoroughly studied computing algorithms in the last four decades. This is both because of its importance in so many scientific and engineering fields, and because it is computationally expensive. Literally hundreds of papers have been published alone on the topic of custom hardware FFT architectures. This doesn't include the countless others which investigate its implementation in software environments, it proper usage, or algorithmic variations (two-point, Singleton three-point, Winograd 5-point, PTL 9-point, mixed-radix, convolution approach, prime-factor, etc.).

Despite the large body of research on FFT architectures, only a select few have focused on parallel FFT architectures for single-chip implementations. All have been published within the last ten years, with the papers from the last two years being the most closely related to the HAPFFT.

The first custom hardware parallel FFTs were implemented in multi-chip environments. Up until the last few years, integrated circuit technology did not provide the transistor densities necessary for implementing a useful sized parallel FFT on a single chip [31, 20, 16, 30, 18, 19, 22]. As an example of the computational complexity of the FFT, as recent as 1984, a 4096-point streaming I/O *single*-pipelined FFT required eleven printed circuit boards, and 1,380 discrete chips![24]

The HAPFFT is intended for single-chip implementations (though the formulation could be easily adapted for a multi-chip environment). The published work on multi-chip, parallel FFTs, is not closely related. Most of the implementations take a multi-processor, software implementation of the FFT, and replace the processors with ASICs. The more noteworthy are [29, 8, 5, 13, 11]. The most recent, and most interesting is COBRA[5]. It is based on a single, 64-point FFT chip. The chip is designed such that multiple chips can be configured in arrays, thereby both permitting larger transform sizes, and increasing potential concurrency.

Recent years have seen several proposals for single-chip parallel FFTs, as well as two commercial offerings. Both Pentek[19] and SiWorks[22] have released parallel FFT IP cores in the last two years. Pentek has recently published high-level details of their implementation. Their architecture implements a commutator-based streaming I/O pipeline variation based on the Radix-4 Multi-Delay Commutator (R4MDC), which will be examined in more detail in Section 3.1.1. The implementation is simple, but not very imaginative. The result is higher resource requirements, and lower clock frequencies than the HAPFFT. SiWorks has not published any details on their architecture, though they have implementation results. There implementation also requires more resources, and lower clock frequencies, in comparison to the HAPFFT.

In [18] a single-chip 4096-point FFT is developed which uses eight processing elements. But, the architecture does not take advantage of hardware pipelining, only parallel execution. Thus, the performance results are disappointing. In addition, control is very complicated, and any implementation would be difficult.

In [30], a single-chip parallel FFT is presented which makes use of the CORDIC algorithm for computing the twiddle factor multiplications. Nevertheless, the implementation is targeted for area-constrained, low-power applications, and a small transform size of 128-points. It is therefore difficult to draw a comparison with the HAPFFT.

A multi-pipelined FFT synthesis tool is presented in [20]. The authors' intent is to develop an automated FFT synthesizer to be operated in a manner similar to DISC[26]. The resulting modules obtain parallelism through the use of arrays of processing elements. The work is not complete, and the results they do post are both slow and large. Nevertheless, this may be more a result of the inadequacies of their automated synthesizer than the chosen architecture.

Except for the commercial parallel FFT offerings, the results in [31] come closest to that of the HAPFFT. This work is architecturally similar to the multi-chip FFT presented in [13], except that it is targeted for a single chip. The resulting 4096-point module implements eight parallel pipelines and exhibits good performance. But, control is complicated, and the resource requirements are excessive, requiring 1.5-4 times that of a similar sized HAPFFT.

In all the reviewed works, no architecture was found that can compete with the HAPFFT in terms of resource requirements versus throughput, or simplicity of control and communication. Additionally, the HAPFFT offers a degree of flexibility far beyond these other results. This is because the number of pipelines in the HAPFFT can be easily varied, and the parallel pipelines themselves are architecturally independent of the HAPFFT's formulation.

### Chapter 2

## The Fast Fourier Transform

In order to more fully understand the operation of high-throughput FFT architectures, one must first study the FFT algorithm. There exist numerous algorithmic variations of it, and this chapter will derive and explain the most common. In addition, insight into these particular algorithms is required to fully understand the HAPFFT.

First, I will motivate the existence of the FFT by using time complexity analysis to compare it to the DFT. Next, I will derive three different FFT algorithms that are commonly used. Finally, I will briefly cover the mixed-radix FFT.

#### 2.1 Motivation for the FFT

For the discrete sequence x[n] = x(0), x(1), ..., x(N-1) of length N, the DFT, X[m], is defined as

$$X[m] = \sum_{n=0}^{N-1} x[n] W_N^{mn}, \qquad 0 \le m < N,$$

(2.1)

where  $W_N = e^{-j2\pi/N}$ .  $W_N$  is known as the (1/N)-th root twiddle factor. Note that the index term m is unit-less. This is the primary difference between the DFT and the discrete-time Fourier transform (DTFT). The DTFT is a special case of the DFT, in which the input sequence is assumed to be defined in the time domain. The DTFT will always use the input index term t, for time.

The DFT compiles a sequence X[m] of length N. Each element of X[m] denotes the relative magnitude of a frequency component of the original sequence,

x[n]. The frequency is in terms of the sampling frequency, i.e. the inverse of the spacing between samples. A *frequency bin* of X[m] is given in terms of m as

$$f = mf_s/N, (2.2)$$

where  $f_s$  is the sample frequency, and N is the length of the sequence, with f being in units of Hertz. For example, for a sequence of length N = 256, sampled at  $f_s = 1$  KHz, the element m = 10 of the DFT would correspond to the frequency f = (10)(1000Hz)/(256) = 39.06 Hz.

Analyzing Equation 2.1, we can see that each element of X[m] requires N complex multiplications and N-1 complex additions. Thus, the time complexity of computing the DFT for a sequence of length N is  $O(N^2)$ . Though not intractable, it is nevertheless very expensive. On the other hand, the FFT produces a result identical to the DFT <sup>1</sup>, but has a time complexity of only  $O(N \log N)$ . To put this in perspective, for a sequence of 1024 elements (a common length encountered in real-world applications), the DFT is  $\frac{O(1024^2)}{O(1024 \log (1024))} = 102.4$  times more complex than the FFT. For a sequence of 16,384 elements (again, a typical size), the DFT is 1,170.3 times more complex than the FFT of the same sequence.

#### 2.1.1 Frequency Aliasing in the DFT

Before plunging into the derivation of the FFT algorithms, I will briefly discuss an issue that effects how the DFT is used.

Because the DFT operates on sampled, discrete data, a phenomenon known as frequency aliasing can occur. The Nyquist sampling theorem states that a sequence, x[n], is uniquely determined if the sampling frequency of its elements is at least twice the bandwidth of the sequence. Thus, the maximum detectable frequency of the DFT of x[n], X[m], is  $f_s/2$ . If frequency components exist above this limit, then they will still appear in the DFT output. But, they will be mislabeled as lower frequencies. In other words, the high frequency components will be aliased.

<sup>&</sup>lt;sup>1</sup>This is not entirely correct. As will be seen in Sections 2.2.1 - 2.2.3, either the output or input of the FFT is scrambled. Many applications require that it be reordered.

Because frequency aliasing can produce incorrect DFT output, one way to reduce its effect is to low-pass filter the input sequence before compiling the DFT. This will reduce the effect of unwanted, high-frequency signals. For a more detailed discussion of this topic, please refer to the relevant chapters in [15] or [12].

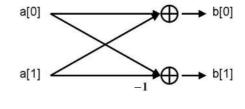

(a) BF2

Figure 2.1: Radix-2 and Radix-4 Butterflies.

#### 2.2 Three Common FFT Algorithms

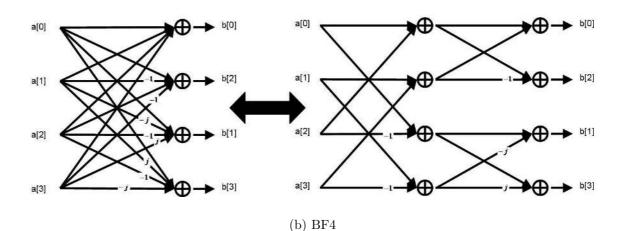

The original Cooley-Tukey FFT has also come to be known as the radix-2 decimation in frequency FFT. Over the years many derivatives of it have been introduced. I will cover three of the most common here, the radix-2 decimation in time and decimation in frequency algorithms, and the radix-4 decimation in frequency algorithm. One of the criteria that distinguishes different FFT algorithms is the FFT *radix*. The radix determines one of the atomic building block of the algorithm. I have already mentioned the radix-2 and radix-4 FFTs. These atomic units of computation are known as FFT *butterflies*. Figure 2.1 shows the radix-2 and radix-4 butterflies. They are called butterflies because of their distinctive shape. The radix-4 butterfly is also often referred to as the FFT *dragonfly*. The other FFT building block is the twiddle-factor complex multiplier.

The radix-2 butterfly is used to construct FFT algorithms for operating on sequences of a size that is a power-of-two. The radix-4 butterfly is the building block for power-of-four FFT algorithms. Though the radix-4 algorithms are more restrictive on available input sequences, they require fewer twiddle-factor multiplications. The general rule is that as the radix of the butterflies increase, fewer twiddle factor multiplications are required, but this is at the expense of less flexibility in available sizes.

What does a butterfly compute? It computes a DFT of size n, where n is the radix. So the radix-2 butterfly computes a 2-point DFT, and the radix-4 butterfly computes a 4-point DFT. There exist dozens of other FFT butterflies of varying radices, each an atomic unit that computes some n-point DFT. See Chapter 8 of [23] for more details. A knowledge of these will be useful in Section 2.3, when I discuss the mixed-radix FFT.

The following derivations will show how the radix-2 and radix-4 butterflies are incorporated into three different FFT algorithms.

#### 2.2.1 The Decimation in Time Radix-2 FFT

The decimation in time (DIT) radix-2 FFT is the most intuitive FFT algorithm, and the simplest to derive, so it will be presented first. It is also the same algorithm presented in the original Cooley and Tukey paper[6] on the FFT. The term *decimation in time* refers to the method of derivation. Given the DFT for a discrete data sequence in time,

$$X[\omega] = \sum_{t=0}^{N-1} x[t] W_N^{\omega n},$$

(2.3)

where N is the length of x[t], the DIT FFT follows by recursively splitting the DFT of x[t] into multiple, smaller DFTs of subsequences of x[t]; in other words, to decimate x[t] in time. For the radix-2 DIT FFT, x[t] will be recursively decimated into two smaller sequences of length N/2.

Given the discrete sequence  $x[n] = \{x[0], x[1], ..., x[N-1]\}$ , where N is powerof-two, the DFT of x[n], X[m], is given by (2.1). The summation of (2.1) can be split into two summations of length N/2,

$$X[m] = \sum_{n=0}^{N/2-1} x[2n] W_N^{m2n} + \sum_{n=0}^{N/2-1} x[2n+1] W_N^{m(2n+1)}$$

=

$$\sum_{n=0}^{N/2-1} x[2n] W_{N/2}^{mn} + W_N^m \sum_{n=0}^{N/2-1} x[2n+1] W_{N/2}^{mn}, \qquad (2.4)$$

where the identity  $W_N^2 = W_{N/2}$  is used.

Now observe that the upper-half of X[m] can be obtained from the bottom half, giving

$$X[m+N/2] = \sum_{n=0}^{N/2-1} x[2n] W_{N/2}^{(m+N/2)n} + W_N^{(m+N/2)} \sum_{n=0}^{N/2-1} x[2n+1] W_{N/2}^{(m+N/2)n} = \sum_{n=0}^{N/2-1} x[2n] W_{N/2}^{mn} - W_N^m \sum_{n=0}^{N/2-1} x[2n+1] W_{N/2}^{mn}.$$

(2.5)

This holds because

\_

$$W_{N/2}^{n(m+N/2)} = W_{N/2}^{nm} W_{N/2}^{nN/2} = W_{N/2}^{nm},$$

(2.6)

and

$$W_N^{m+N/2} = W_N^m W_N^{N/2} = -W_N^m. (2.7)$$

By comparing equations (2.4) and (2.5), it can be sees that X[m] and X[m + N/2], for  $0 \le m < N/2$ , only differ by a sign. Therefore, the two halves of the DFT

result can be produced by using the same operands. These operands are the two summations in (2.4) and (2.5); they are two N/2-point DFTs.

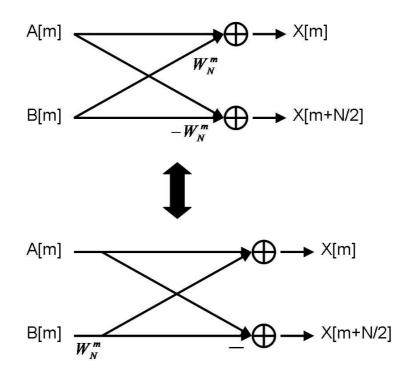

Figure 2.2: Simplification of radix-2 butterfly twiddle factor multiplications.

In addition to the sharing of the two N/2-point DFT outputs, there is a further simplification that can be made. Let us name the two N/2-point DFT outputs A[m]and B[m], respectively, of length N/2. Then (2.4) and (2.5) can be posed as

$$X[m] = A[m] + W_N^m B[m]$$

(2.8)

$$X[m + N/2] = A[m] - W_N^m B[m], (2.9)$$

where  $0 \le m < N/2$ . Observe that the *m*-th and (m + N/2)-th members of X[m] can be generated by the circuit shown at the top of Figure 2.2.

The simplification results because the circuit transformation illustrated in Figure 2.2 can be performed. Note that the converted circuit consists of a single twiddle factor multiplication on B[m], followed by a radix-2 butterfly. These circuits are equivalent, yet the transformed circuit reduces the number of twiddle factor multiplications by half.

Figure 2.3: Data flow graph for 8-point DFT using 4-point DFTs.

If the simplifications just discussed are applied to an 8-point DFT, then Figure 2.3 shows its resulting data flow graph. Note the two 4-point DFT blocks, and that the outputs of the blocks are shared as operands for the bottom and top halves of the output. X[m] is produced by executing a series of four radix-2 butterflies on the

outputs of two 4-point DFT blocks; the outputs of the DFT block corresponding to the B[m] sequence are also modified by twiddle factor multiplications.

Figure 2.4: Data flow graph for 8-point DFT using 2-point DFTs.

The computation of our transformed N-point DFT can be further simplified. The simplifications presented in the previous discussion can be recursively applied to the two N/2-point DFTs, A[m] and B[m]. For our 8-point DFT example in Figure 2.3, this will yield the data flow graph shown in Figure 2.4. The outputs of the two 4-point DFTs are now also computed with twiddle factor multiplications followed by radix-2 butterflies; the inputs to the multiplication/butterfly combo are generated from four 2-point DFTs.

Figure 2.5: Data flow graph for 8-point DIT FFT using radix-2 butterflies.

The objective of the radix-2 DIT FFT algorithm is to reduce the DFT computation to a series of radix-2 butterfly operations and twiddle factor multiplies. Each radix-2 butterfly computes a 2-point DFT. The 2-point DFT blocks in Figure 2.4 can therefore be replaced by radix-2 butterflies, finally giving Figure 2.5; this result is the complete data flow graph for an 8-point DIT FFT.

Figure 2.6: Bit-reverse operation on address sequence.

Because the input sequence, x[n], has been recursively decimated in time, the input order has been scrambled. This can be seen in Figure 2.5. For FFTs of a power of two radix, the data can be reordered by a simple *bit-reverse-copy*. This consists of copying the input sequence into a new sequence where the elements have been assigned to bit-reversed addresses. Figure 2.6 shows how the bit-reverse operation is performed on the addresses of the input sequence; after the bit-reverse copy, the data can be presented to the radix-2 DIT FFT in the correct order.

The reordering of data is a side-effect of all FFT algorithms (depending on the algorithm it can be either the input or the output that is scrambled). The scrambling effect is why it is not precise to call the FFT an equivalent operator of the DFT. But, because it is usually simple to reorder the data, most people ignore this subtle difference.

Despite the need to reorder the data, the computational savings of the FFT are considerable, compared to the DFT. In our 8-point DFT example, the resulting FFT requires 24 complex additions and 8 complex multiplications. The equivalent

```

1.

ITERATIVE_DIT_FFT(x,X) {

2.

X = x; /* copy x */

3.

n = length(x);

4.

bit_reverse(X); /* reorder X */

for(s = 1; s <= log(n); s++) { /* outer loop */</pre>

5.

6.

m = 2^{s};

7.

wm = \cos(2*pi/m)-sqrt(-1)sin(2*pi/m);

8.

for(k = 0; k < n; k += m) { /* inner loop */</pre>

w = 1; /* twiddle factor */

9.

for(j = 0; j < m/2; j++) { /* execute butterflies */

10.

11.

t = X[k+j];

u = w * X [k+j+m/2];

12.

13.

X[k+j] = t + u;

14.

X[k+j+m/2] = t - u;

15.

w = w*wm; /* compute next twiddle factor */

}

16.

17.

}

}

18.

}

19.

```

Figure 2.7: Pseudocode for the sequential, iterative radix-2 DIT FFT

DFT would require 56 complex additions and 64 complex multiplications. Except for the data shuffling, the FFT and DFT results are *identical*.

Figure 2.7 presents pseudocode describing the radix-2 DIT FFT. Though the DIT FFT was derived recursively, recursive algorithms are difficult to map to hardware. Therefore, the pseudocode describes an iterative algorithm. Note that the outer loop iterates  $\log(N)$  times, and the inner loop iterates N times. Also, lines 11-14 perform the twiddle factor multiplication and the radix-2 butterfly. Line 4 completes a bit-reverse copy of the input data sequence.

### 2.2.2 The Decimation in Frequency Radix-2 FFT

In Section 2.2.1 the FFT was derived by recursively decimating the input sequence in time. An alternative approach is to instead decimate the output sequence

in frequency. This leads us to the radix-2 decimation in frequency (DIF) FFT. The DIF FFT produces a computation that accepts the input in order, and produces a shuffled output.

The derivation of the radix-2 DIF FFT is not as intuitive in comparison to that of the DIT FFT. But, in many hardware applications of the FFT the input data is presented serially. Because of this, a full data sequence must be buffered before executing the reorder. This holds for both the DIF and DIT FFT. Nevertheless, some FFT applications can use the FFT output without reordering. Such a case would allow fewer resources to be used for the DIF FFT, since the reorder buffering would be unnecessary. Because of this, it is therefore more widely used for hardware applications.

Assume the length N of the sequence x[n] is a power of two. Its DFT, X[m], can be split into two sequences of length N/2, where one sequence contains all the even elements, and the other the odd elements. The even elements of X[m] can be computed using Equation (2.1), giving

$$X[2m] = \sum_{n=0}^{N-1} x[n] W_N^{2mn}$$

=  $\sum_{n=0}^{N/2-1} x[n] W_N^{2mn} + \sum_{n=N/2}^{N-1} x[n] W_N^{2mn}$

=  $\sum_{n=0}^{N/2-1} x[n] W_N^{2mn} + \sum_{n=0}^{N/2-1} x[n+N/2] W_N^{2m(n+N/2)}.$  (2.10)

Also, because  $W_N^{2mn}$  is periodic, the following is obtained

$$W_N^{2m(n+N/2)} = W_N^{2mn} W_N^{mN} = W_N^{2mn} = W_{N/2}^{mn}.$$

(2.11)

Using this observation, and combining the two summations of (2.10), results in

$$X[2m] = \sum_{n=0}^{N/2-1} (x[n] + x[n+N/2]) W_{N/2}^{mn}.$$

(2.12)

Equation (2.12) is the (N/2)-point DFT of the sequence obtained by performing a vector summation of the first and second halves of x[n].

The odd elements of X[m] can be obtained as follows:

$$X[2m+1] = \sum_{n=0}^{N-1} x[n] W_N^{(2m+1)n}$$

$$= \sum_{n=0}^{N/2-1} x[n] W_N^{(2m+1)n} + \sum_{n=N/2}^{N-1} x[n] W_N^{(2m+1)n}.$$

(2.13)

The second summation of (2.13) can be rearranged as

$$\sum_{n=N/2}^{N-1} x[n] W_N^{(2m+1)n} = \sum_{n=0}^{N/2-1} (x[n] + N/2) W_N^{(2m+1)(n+N/2)}$$

$$= W_N^{(2m+1)N/2} \sum_{n=0}^{N/2-1} (x[n+N/2]) W_N^{(2m+1)n}, \quad (2.14)$$

and because  $W_N^{(2m+1)N/2} = W_N^{mN} W_N^{N/2} = e^{-j2\pi m} e^{-j\pi} = -1$ , Equation (2.14) becomes

$$\sum_{n=N/2}^{N-1} x[n] W_N^{(2m+1)n} = -\sum_{n=0}^{N/2-1} (x[n+N/2]) W_N^{(2m+1)n}.$$

(2.15)

By substituting (2.15) into (2.13) and combining the summations, the odd elements of X[m] can be expressed as

$$X[2m+1] = \sum_{n=0}^{N/2-1} (x[n] - x[n+N/2]) W_N^{(2m+1)n}$$

=

$$\sum_{n=0}^{N/2-1} (x[n] - x[n+N/2]) W_{N/2}^{mn} W_N^n, \qquad (2.16)$$

since  $W_N^2 = W_{N/2}$ . Equation (2.16) is the (N/2)-point DFT of the sequence obtained by performing a vector subtraction of the second half of x[n] from the first half, and multiplying the result by  $W_N^n$ .

Just as with the DIT FFT algorithm presented in Section 2.2.1, I have obtained a simplified N-point DFT, where X[m] is formed from two N/2-point DFTs. The inputs to the DFTs are N/2-point sequences formed by vector operations on the first and second halves of x[n], and also a twiddle factor multiplication.

The same simplifications described above can be applied recursively to X[2m]and X[2m + 1]. This is done until 2-point DFTs are being computed. At this point the blocks are replaced with the radix-2 butterfly. Because the sequence is a power of two length N,  $\log_2 N$  recursions will be required.

Figure 2.8 shows the data flow diagram for a 16-point radix-2 DIF FFT. Note that there are N = 16 rows and  $\log_2 N = 4$  columns of operations. Instead of the input being scrambled, it is now the output that must be reordered. This is from

Figure 2.8: Data flow graph for a 16-point DIF radix-2 FFT.

decimating the output in frequency. Note that in Figure 2.8, there are implied twiddle factor multiplications between butterfly columns.

When implemented as a sequential program, the radix-2 FFT can be described in either a recursive or iterative algorithm. The recursive algorithm fits the preceding derivation better, but does not easily map to hardware. Figure 2.7 is the pseudocode for such an FFT algorithm. The outer loop loops logN times, and the inner loop does so N/2 times. Lines 10-13 perform the radix-2 butterfly and the twiddle factor multiplication. The bit\_reverse(X) procedure on line 18 is required for unscrambling the FFT result.

```

1.

ITERATIVE_DIF_FFT(x,X) {

2.

X = x; /* copy x */

3.

n = length(x);

for(s = log(n); s >= 1; s--) { /* outer loop */

4.

5.

m = 2^{s};

6.

wm = \cos(2*pi/m)-sqrt(-1)sin(2*pi/m);

7.

for(k = 0; k < n; k += m) { /* inner loop */</pre>

w = 1; /* twiddle factor */

8.

9.

for(j = 0; j < m/2; j++) {</pre>

t = X[k+j];

10.

11.

u = X[k+j+m/2];

12.

X[k+j] = t + u;

X[k+j+m/2] = w*(t - u);

13.

14.

w = w*wm; /* compute next twiddle factor */

}

15.

16.

}

17.

}

18.

bit_reverse(X);

19.

}

```

Figure 2.9: Pseudocode for the sequential, iterative radix-2 DIF FFT.

#### 2.2.3 The Decimation in Frequency Radix-4 FFT

In this section I will derive the radix-4 DIF FFT. I will not do so for the radix-4 DIT FFT, because the derivation is very similar to the radix-2 DIT FFT, and uses some of the same as for the radix-4 DIF FFT. It is therefore left as an exercise for the interested reader. The reason I choose to derive the radix-4 DIF FFT instead of the DIT is because the formulation of the HAPFFT is obtained in a similar manner as that for the radix-4 DIF FFT. Thus, an understanding of this section will aid in deriving the HAPFFT.

The radix-4 DIF algorithm is similar to the radix-2 DIF algorithm. The derivation uses the same approach, by decimating the DFT output in the frequency domain. They differ in that the atomic computational unit is a radix-4 butterfly, as introduced in Figure 2.1. The advantage of using the radix-4 butterfly is that it can be computed without any twiddle factor multiplications, while the total number of butterflies required is half that of the radix-2 algorithm. Thus, the total number of complex twiddle factor multiplications for a radix-4 FFT is half that of the radix-2 FFT. The disadvantage is that twice the number of complex additions are needed, and the size of the input data set is limited to a power of four length. Nevertheless, when using fixed-point computer arithmetic, because complex multiplications are very often more expensive than complex additions, a radix-4 FFT may be cheaper to implement. As an aside, in section 3.1 I will discuss the radix-2<sup>2</sup> FFT architecture. It emulates the radix-4 FFT, but can do so with fewer complex additions, resulting in a very efficient architecture.

The radix-4 DIF FFT algorithm is derived in the same manner as the DIF radix-2 algorithm. But instead of decimating the DFT output into odd and even halves, the radix-4 algorithm decimates it into quarters. For a power of four data set, x[n], of length N, I decimate its DFT, X[m], into the X[4m], X[4m+1], X[4m+2], and X[4m+3] output sequences. For the X[4m]-th quarter I get

$$X[4m] = \sum_{n=0}^{N-1} x[n] W_N^{4mn}$$

Figure 2.10: Data flow graph for 16-point DFT using 4-point DFTs.

$$= \sum_{n=0}^{N/4-1} x[n] W_N^{4mn} + \sum_{n=N/4}^{N/2-1} x[n] W_N^{4mn} + \sum_{n=N/2}^{3N/4-1} x[n] W_N^{4mn} + \sum_{n=3N/4}^{N-1} x[n] W_N^{4mn} = \sum_{n=0}^{N/4-1} x[n] W_N^{4mn} + \sum_{n=0}^{N/4-1} x[n+N/4] W_N^{4m(n+N/4)}$$

$$+\sum_{n=0}^{N/4-1} x[n+N/2] W_N^{4m(n+N/2)} +\sum_{n=0}^{N/4-1} x[n+3N/4] W_N^{4m(n+3N/4)}.$$

(2.17)

X[4m] can be further simplified by observing that

$$\begin{split} W_N^{4mn} &= W_{N/4}^{mn}, \\ W_N^{4m(n+N/4)} &= W_N^{4mn} W_N^{mN} = W_{N/4}^{mn}, \\ W_N^{4m(n+N/2)} &= W_N^{4mn} W_N^{2mN} = W_{N/4}^{mn}, \\ W_N^{4m(n+3N/4)} &= W_N^{4mn} W_N^{3mN} = W_{N/4}^{mn}. \end{split}$$

Using these twiddle factors, and combining the summations in (2.17), the result is

$$X[4m] = \sum_{n=0}^{N/4-1} (x[n] + x[n+N/4] + x[n+N/2] + x[n+3N/4]) W_{N/4}^{mn}.$$

(2.18)

The X[4m + 1]-th sequence is computed in a similar fashion, obtaining

$$X[4m+1] = \sum_{n=0}^{N-1} x[n] W_N^{(4m+1)n}$$

$$= \sum_{n=0}^{N/4-1} x[n] W_N^{(4m+1)n} + \sum_{n=N/4}^{N/2-1} x[n] W_N^{(4m+1)n}$$

$$+ \sum_{n=N/2}^{3N/4-1} x[n] W_N^{(4m+1)n} + \sum_{n=3N/4}^{N-1} x[n] W_N^{(4m+1)n}$$

$$= \sum_{n=0}^{N/4-1} x[n] W_N^{(4m+1)n}$$

$$+ \sum_{n=0}^{N/4-1} x[n+N/4] W_N^{(4m+1)(n+N/4)}$$

$$+ \sum_{n=0}^{N/4-1} x[n+N/2] W_N^{(4m+1)(n+N/2)}$$

$$+ \sum_{n=0}^{N/4-1} x[n+3N/4] W_N^{(4m+1)(n+3N/4)}. \qquad (2.19)$$

X[4m+1] can also be simplified by observing that

$$W_N^{(4m+1)n} = W_{N/4}^{mn} W_N^n,$$

$$\begin{split} W_N^{(4m+1)(n+N/4)} &= W_{N/4}^{mn} W_N^n W_N^{N/4} = -j W_{N/4}^{mn} W_N^n, \\ W_N^{(4m+1)(n+N/2)} &= W_{N/4}^{mn} W_N^{2mN} W_N^n W_N^{N/2} = -W_{N/4}^{mn} W_N^n, \\ W_N^{(4m+1)(n+3N/4)} &= W_{N/4}^{mn} W_N^{3mN} W_N^n W_N^{N/2} = j W_{N/4}^{mn} W_N^n. \end{split}$$

Thus, Equation (2.19), by combining the summations, can be rewritten as

$$X[4m+1] = \sum_{n=0}^{N/4-1} (x[n] - jx[n+N/4]) - x[n+N/2] + jx[n+3N/4]) W_{N/4}^{mn} W_N^n.$$

(2.20)

The X[4m+2]-th and X[4m+3]-th sequences can in likewise manner be found, giving us

$$X[4m+2] = \sum_{n=0}^{N/4-1} (x[n] - x[n+N/4] + x[n+N/2] - x[n+3N/4]) W_{N/4}^{mn} W_N^{2n}, \qquad (2.21)$$

$$X[4m+3] = \sum_{n=0}^{N/4-1} (x[n] + jx[n+N/4]) - x[n+N/2] - jx[n+3N/4]) W_{N/4}^{mn} W_N^{3n}.$$

(2.22)

Equations (2.18), (2.20), (2.21), and (2.22), are each N/4-point DFTs. The inputs for the DFTs are formed by computing N/4 radix-4 butterflies.

Figure 2.10 shows the dfg for a 16-point DFT after incorporating the simplifications derived above. The inputs to the DFTs are the four sequences of length N/4 = 4, computed according to Equations (2.18), (2.20), (2.21), and (2.22).

Each of the N/4-point DFTs found in (2.18), (2.20), (2.21), and (2.22) can be recursively simplified using the same methods. The recursion is executed until 4-point DFT blocks are generated. At this point the 4-point DFTs can be replaced by the equivalent radix-4 butterfly.

If these simplifications are applied to the example in in Figure 2.10, the result is found in Figure 2.11. Note that the atomic computational unit is the radix-4 butterfly. This is the complete radix-4 DIF FFT dfg for a 16-point FFT. Comparing it to the 16-point radix-2 DIF FFT in Figure 2.5, it can be sees that the total number of butterflies and twiddle factor multiplications is greatly reduced. In addition, notice

Figure 2.11: Data flow graph for 16-point DIF FFT using radix-4 butterflies.

that the output is again scrambled as a result of the frequency decimation. These can be reordered using the address bit-reverse method.

### 2.3 The Mixed-Radix FFT

All the FFT algorithms derived up to this point have been homogeneous, composed of a single type of butterfly. While this provides for simple design and algorithm derivation, it limits the size of sequences to which the FFT can be applied. They must be a power of a size, where a is the radix of the butterfly.

One may argue that this is not a problem. If a sequence is not of a proper length, then just zero-pad the sequence until it is of the proper power of *a* in length. While this is commonly done in practice, in some applications it is not desirable. The mixed-radix FFT algorithm allows an FFT of any non-prime size to be computed by factoring the FFT into a sequence of smaller FFTs.

Figure 2.12: An N = PQ-point mixed-radix FFT.

For a data set of a non-prime number size, N, if it has two factors, P and Q, then the FFT of N can be computed by instead computing a P-point FFT, and then a Q-point FFT (or vice-versa). Figure 2.12 shows this process.

Each FFT block, if it is not a prime number size, can likewise be factored into smaller blocks. This can continue until all blocks are of some prime-number in size. The radix-2 FFT algorithm is a special case of the mixed radix algorithm; it is computed using  $\log_2 N$  2-point FFTs.

Figure 2.13 shows a mixed-radix FFT example. It shows a dfg for a 24-point FFT. The FFT is factored into three stages: a 2-point FFT, then a 3-point FFT, and finally a 4-point FFT. Note that twiddle-factor multiplies are required in between each stage. These can be computed using the same techniques found in the radix-2 and radix-4 DIF derivations.

When using non-power of two sized butterflies, the data reordering becomes more complex. It is no longer just a simple case of reversing the address bits. In practice, for the mixed-radix FFT, the easiest way to reorder the data is to reorder after every FFT stage, rather than all at once at the end.

Figure 2.13: Mixed-radix 24-point FFT.

The mixed-radix FFT will be of particular importance later. It is related to the HAPFFT presented in chapter 4.

For data sequences of a prime number size there also exist FFT algorithms. The most common are grouped into a category known as the convolution-based FFT. Though much more expensive than the standard FFT, they are normally faster than explicitly computing the DFT.

## Chapter 3

# **High Performance FFT Computations**

In Chapter 2, I demonstrated that the FFT is a more computationally efficient means of computing the DFT. Despite this, the FFT is still a relatively expensive and complex operation. This is caused by the need to operate on complex numbers, access and manipulate often large blocks of memory, and control complicated movements of data.

One of the most thoroughly studied areas of FFT research has to do with techniques for increasing FFT performance. When I indicate performance I am referring to the data throughput, the average number of samples-per-second that a particular FFT implementation can consume, denoted by  $\sigma_{pipeline}$ . Other criteria may also be of equal or greater importance, such as computational latency, resource requirements, or power.

This chapter will provide background on some of the techniques used for highperformance implementations of the FFT. Some of these are architectures intended for custom hardware (such as VLSI or FPGA blocks). Others are intended for parallel computing environments. Also, in Section 1.2, I reviewed the state-of-the-art in the field of hardware parallel FFTs.

Given a particular computational algorithm and problem size, there are two ways that it can be executed faster. Either complete each algorithmic step in less time, or execute the steps concurrently. The sections in this chapter will focus on the second technique: increasing the computational concurrency of the FFT. First, Section 3.1 will discuss hardware pipelining, and then Section 3.2 will introduce the parallel FFT, and review two common algorithms for its computation.

#### 3.1 Hardware Pipelined FFT Architectures

Hardware pipelining is an important and effective technique used to increase computational concurrency. Pipelining is best illustrated by using an assembly line analogy. Using the example of an automotive assembly line, at each step in the line a given assembly step is performed. At one step the chassis is welded together, at another the engine is mounted, and a subsequent step will install the wheels. The assembly line could be split up into an arbitrary number of steps. If there are N steps involved in the assembly, and each assembly line step is always doing useful work, then it can be said that the assembly line can assemble N automobiles in parallel. This holds even though only one car exits the factory at a time.

Pipelining in custom hardware is based on a similar concept. For a given computational algorithm that requires N steps to complete, a hardware functional unit could be constructed for each step. Then, if the algorithm is suitably parallel, the pipeline can complete N times more work than an implementation that only performs a single computation at a time.

For pipelining to be effective, a few assumptions must be made: there is enough data to feed the pipeline a constant stream of data, the dependencies between data points is of a nature such that they won't interfere with the correct execution of any given pipeline stage, and there are enough hardware resources so that no stage need share functional units with another. If any of these don't hold, then the N pipeline stages may have to execute less than N computations at a time.

I will make the assumption that all pipelines discussed in this section have transitions which are *synchronous* to some clock. This means that each pipeline stage will consume and produce a datum at either the rising or falling edge of a common clock signal.

Digital signal processing tends to fit the pipelining paradigm well. Many signal processing algorithms consist of taking a block of data, and executing a number of steps on it. Often the data is a constant stream, and the execution steps are independent of each other. If hardware resources are not an issue, it is quite easy to construct a high throughput pipeline, as illustrated in Figure 3.1. For example, since

Figure 3.1: A typical DSP processing pipeline.

the DFT is a building block for many DSP algorithms, one or more FFTs may form blocks in such a pipeline.

The performance of a hardware pipeline can be quantified by using the pipeline throughput,  $\sigma_{pipeline}$ . An important parameter that determines the pipeline throughput is the *data introduction interval*, denoted as  $\delta_0$  [14]. Though having no effect on the throughput, another important parameter which places constraints on  $\delta_0$  is the *pipeline latency*. Pipeline latency is defined as the number of clock cycles that must occur after the start of a computation is begun, until a result appears. By definition,  $\delta_0 < latency$  will always hold for a pipelined circuit. If  $\delta_0 = latency$ , then a new computation is initiated only after the previous one has completed, and therefore there is no pipelining. For a pipeline with  $\delta_0 = 0$ , the data introduction interval is non-existent, and thus a computation is being initiated at every clock cycle. Such a circuit is fully pipelined, and pipelining can no longer be used for increasing computational concurrency.

Referring back to Figure 3.1, depending on a given computational step in the DSP pipeline paradigm, the step itself may be able to be further subdivided into pipeline stages. This would enable an increase in total computational concurrency. For the FFT architectures discussed in this chapter, there exist a number of methods for their pipelining. Section 3.1.1 introduces some of the more common types.

### 3.1.1 A Taxonomy of FFT Architectures for Custom Hardware

Chapter 2 introduced a number of FFT algorithms, as well as pseudocode that can be used in a practical software implementation of these algorithms. However, the FFT is often used in high-performance systems where the use of a software FFT implementation, running on a general-purpose microprocessor, is inadequate. At times this can be resolved by using a DSP processor. Alternatively, a parallel FFT algorithm (to be discussed in Section 3.2) can be implemented using a parallel computing environment.

In many applications even these approaches will not meet design requirements. Either they are too expensive in terms of power and size, or their performance may still be insufficient. In such cases a custom hardware FFT can often resolve the problem.

Hardware FFT architectures come in many flavors, depending on the criteria of the application. Some architectures provide unusually low power demands, others use almost trivial amounts of hardware, while some give exceptional data throughput. I will focus here on architectures which are targeted for high-throughput applications.

Hardware FFT modules differ in which FFT algorithm is used (radix-2 DIF, radix-4 DIT, etc.), and in how the algorithm is mapped to hardware. The architectures can be categorized into *bursty*, and *streaming* architectures.

Bursty architectures have a computational latency longer than the length of the input data set. This means that after a data set is input, a delay must be included before the next subsequent data set can be input. In other words, on average,  $\delta_0 > 0$ .

In contrast, the streaming architecture is capable of accepting one or more data points every clock cycle. Bursty architectures are used mostly for low-power and/or low-resource applications. Streaming architectures are found more often in high-throughput applications.

#### **Bursty Architectures**

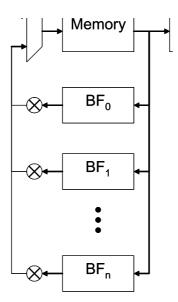

Though I shall mostly address streaming architectures, it is useful to first briefly study a common bursty architecture, called the in-place FFT architecture, shown in Figure 3.2. The purpose is to compare and contrast the bursty computational paradigm with the streaming pipeline.

Figure 3.2: Diagram for a general in-place FFT architecture.

The in-place architecture uses the most obvious mapping of the algorithms shown in Figure 2.7 and 2.9. Comparing Figure 3.2 to the algorithm presented in Figure 2.9, it can be seen that the memory block is equivalent to the X array, with the input data stream corresponding to the x array. To implement the outer and inner loops the contents of the memory block are repeatedly sent to a set of butterfly and twiddle factor multiplier functional units. Upon termination of the computation, the data is reordered, and output.

It should be apparent that performance trade-offs can be easily made. The latency, power, throughput and resource requirements can be changed by adding or subtracting to the total number of functional units.

The control of the in-place FFT architecture tends to be complicated; there is a lot of resource sharing, and the data must be carefully directed to the correct functional units. Also, though the functional units will, in general, be identical, the inputs to the twiddle factor multipliers vary from unit to unit, and from iteration to iteration. The in-place architecture can be modified to allow streaming behavior. This can be done by duplicating the memory and functional units. If enough functional units are provided, it is possible to have one core computing while the other is inputting, and vice-versa. For example, Xilinx, Inc., provides a streaming radix-4 FFT IP core based on such a scheme [28].

#### **Streaming Architectures**

While there are a number of different streaming FFT architectures [27, 7, 10, 21, 3, 4], most share a single characteristic that differentiates them from bursty architectures, namely: rather than continually reading and writing the data to the same location in memory, the data instead moves through a pipeline. Therefore, these architectures are sometimes called *pipelined FFT* architectures.

Pipelined FFTs typically have simpler control than their bursty counterparts. Nevertheless, they will also have higher resource requirements. Also, the mapping from the abstract FFT algorithms to the hardware is not quite so obvious.

Figure 3.3: Pipelined FFT DFG for Figure 2.8.

I will discuss two families of pipelined FFT architectures: the *delay feedback* and the *delay commutator* architectures. The families differ in the way that they present inputs to the butterflies. Figure 2.8 can be used to understand this difference. The input data stream will typically provide a single data point every clock cycle. Assuming that the butterflies will be executed starting at the top of the left column

of Figure 2.8, executing each butterfly from top to bottom, and then proceed with the next column of butterflies, and so on. If x[0] arrives in the first clock cycle, the first butterfly cannot be immediately executed; the other butterfly operand, x[8], will not arrive for seven more clock cycles. Likewise, for each column of our dfg, the same problem occurs as the data proceeds down the pipeline. The data must be reordered before every butterfly.

Figure 3.3 shows how the 16-point DIF FFT example could be mapped to hardware in such a way that the data is presented correctly to the butterflies. Figure 3.3 is for a radix-2 DIF algorithm, though a similar block diagram applies to other radices and algorithms.

### **Delay Feedback Pipelined Architectures**

The delay feedback architectures reorder the input by first accepting part of the data stream into the butterfly elements, but instead of computing on the block, it is redirected to a feedback delay line. By the time the data appears again at the input of the butterfly the other inputs of the butterfly will also be ready.

Figure 3.4 shows how a 16-point radix-2 DIF would be implemented using a single delay feedback for each butterfly. Looking again at Figure 2.8, each column of the dfg corresponds to one of the butterfly elements. The feedback delay,  $\lambda$ , for each butterfly is given as

$$\lambda = 2^s/2 \tag{3.1}$$

where s corresponds to the column labeling in Figure 2.8.

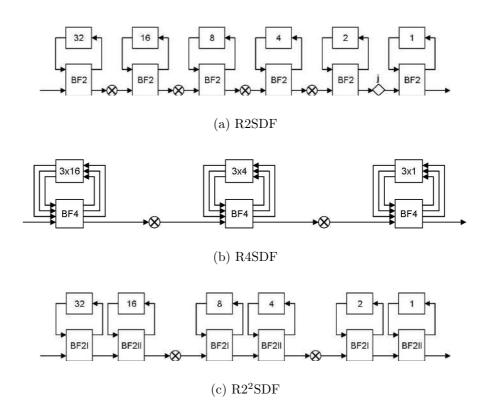

Figure 3.4 is known as the radix-2 single delay feedback (R2SDF) architecture. There are a number of variations of this same theme. The most common are described in Figure 3.5, each computing a 64-point DIF FFT.

# • R2SDF [27]

An efficient implementation of the radix-2 FFT algorithm. It Requires N-1 memory elements for the delay lines,  $2 \log_2 N$  complex additions, and  $\log_2 N-2$  complex multipliers. Control is trivial, requiring a simple binary counter; each output bit of the counter corresponds to a butterfly element.

Figure 3.4: 16-point implementation of the radix-2 SDF.

# • R4SDF [7]

By using a higher butterfly radix, a pipelined FFT can be built that needs fewer twiddle factor multiplications. The radix-4 single delay feedback (R4SDF) uses the same theme as the R2SDF, but with three delay lines per butterfly instead of one, and twice the number of complex adders. It requires N - 1 memory elements,  $4 \log_2 N$  complex adders, and  $.5 \log_2 N - 1$  complex multipliers. Control is more complex, since each butterfly must now direct four data streams.

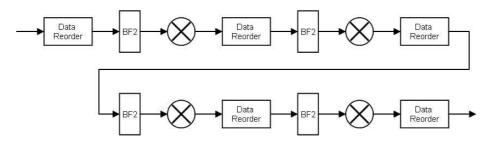

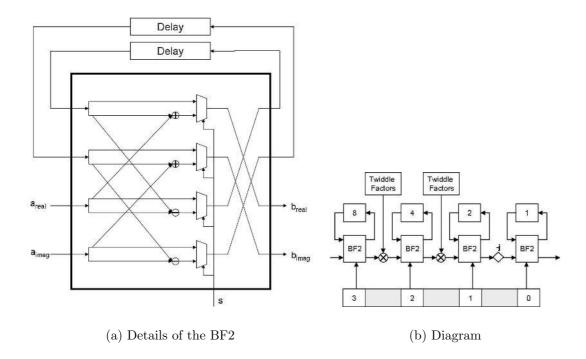

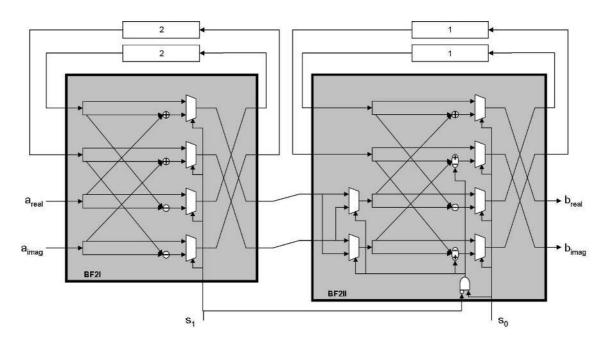

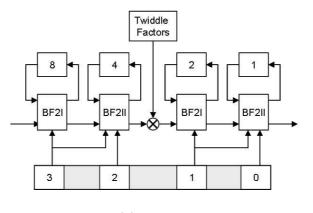

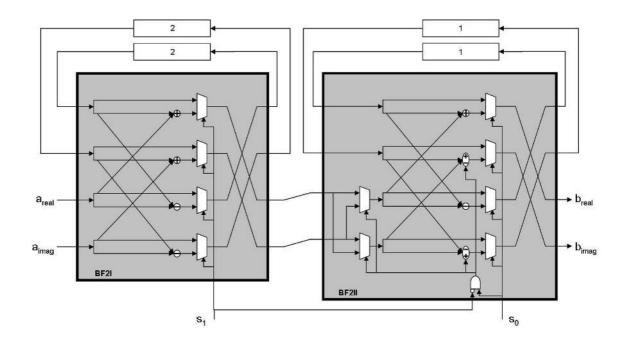

# • R2<sup>2</sup>SDF [10]

This is a recent architecture presented in [10], known as radix- $2^2$  single delay feedback (R2<sup>2</sup>SDF). The R2<sup>2</sup>SDF architecture emulates radix-4 butterfly elements by using a pair of modified radix-2 butterflies. Referring to Figure 3.5(c), the **BF2I** element is a standard **BF2**, as found in the R2SDF pipeline. The **BF2II** element is slightly modified, allowing selected inputs to be multiplied by

Figure 3.5: Single Delay Feedback (SDF) Pipelined 64-point FFT Architectures

a  $-\sqrt{-1}$ . Figure 3.6 shows how a R2<sup>2</sup>SDF pipeline is constructed, and includes details on the butterfly elements. The overall effect of the emulation is a radix-4 algorithm, but with the control and complex additions of a radix-2 algorithm. It requires N - 1 memory elements,  $2 \log_2 N$  complex adders, and  $.5 \log_2 N - 1$ complex multipliers. The control is more complex than that of the R2SDF, but still very simple.

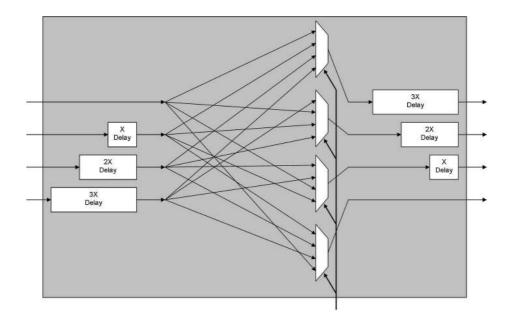

### **Delay Commutator Pipelined Architectures**

The delay commutator pipelined FFT architectures take a different approach to reordering the data. Instead of streaming it through delay feedbacks, the data is delayed and commuted (passed through a switching element) prior to arriving at the butterfly elements. For example, Figure 3.7 shows the delay commutator element

(a) Details of the BF2I and BF2II

(b) Diagram

Figure 3.6: 16-point implementation of the radix- $2^2$  SDF.

used in the radix-4 multi-delay commutator (R4MDC) architecture. After the data passes through this element, it will be presented at the inputs of the radix-4 butterfly in the correct order.

Figure 3.7: A multi-delay commutator for the R4MDC. From [25]

The delay commutator approach tends to be more complex and expensive than the delay feedback method<sup>1</sup>. Given an initial evaluation it would seem that the single-delay feedback architectures are a better choice. But an advantage of the delay commutator is that pipelining is less constrained. The delay feedback architectures are limited in the number of pipeline stages that can be added, because of the feedback delay lines. This can be understood by analyzing Figure 3.6.

Since the maximum clock frequency is limited by the critical path of the circuit, if the butterfly stages in Figure 3.6(b) contain a critical delay, this can be alleviated by the addition of pipeline registers. And for every pipeline register added, a clock

<sup>&</sup>lt;sup>1</sup>One exception is for block floating-point implementations of the FFT. The R4SDC requires slightly less memory than the  $R2^2SDF$  when implemented using block floating point arithmetic. But, the R4SDC has very complex control

delay must be removed from the feedback delay loop. This is needed so that the butterfly operands continue to be presented in the correct order. But, the final butterfly feedback loop in the pipeline has only a single clock delay. Only a single pipeline register may be included within the butterfly stage. Thus, for a SDF pipeline architecture which has been maximally pipelined, the final butterfly stage will most likely contain the critical delay path of the entire circuit. This delay cannot be further reduced using pipeline registers.

In contrast, since delay commutators contain only feed-forward paths, then the level of pipelining is limited only by the granularity of the hardware substrate. Thus, delay commutator architectures are commonly found in applications which demand very high clock frequencies [4].

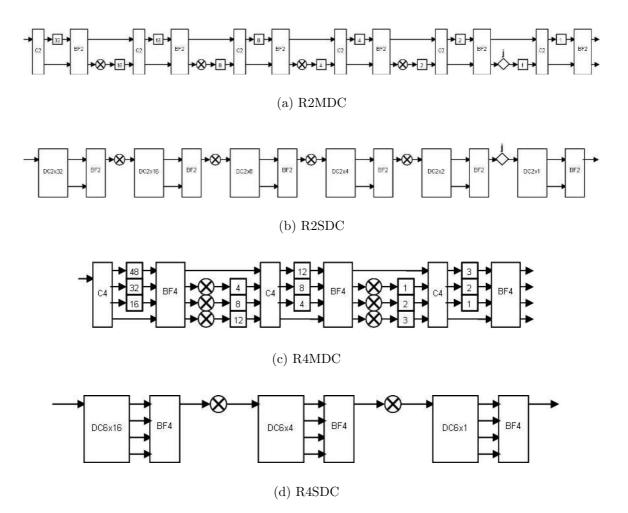

Figure 3.8 contains diagrams for four types of delay commutator FFT architectures. They all implement a 64-point DIF FFT. There are two varieties: the single-delay and multi-delay commutators. The single-delay commutators use fewer resources, but have higher control complexity.

## • R2MDC [21]