# Open access · Journal Article · DOI:10.1109/TIM.2004.834046

# The impact of combined channel mismatch effects in time-interleaved ADCs — Source link

### Christian Vogel

# Institutions: Graz University of Technology

Published on: 17 Jan 2005 - IEEE Transactions on Instrumentation and Measurement (Institute of Electrical and Electronics Engineers)

# Topics: SINAD

## Related papers:

- Time interleaved converter arrays

- · Explicit analysis of channel mismatch effects in time-interleaved ADC systems

- · Adaptive blind calibration of timing offset and gain mismatch for two-channel time-interleaved ADCs

- · Analysis of mismatch effects among A/D converters in a time-interleaved waveform digitizer

- · Blind Calibration of Timing Offsets for Four-Channel Time-Interleaved ADCs

# The Impact of Combined Channel Mismatch Effects in Time-Interleaved ADCs

Christian Vogel, Student Member, IEEE

Abstract—A time-interleaved multichannel analog-to-digital converter (ADC) achieves high sampling rates with the drawback of additional distortions caused by channel mismatches. In this paper, we consider the dependency of the signal-to-noise-and-distortion ratio (SINAD) on the combination of several different channel mismatch effects. By using either explicitly given mismatch parameters or given parameter distributions, we derive closed-form equations for calculating the explicit or the expected SINAD for an arbitrary number of channels. Furthermore, we extend the explicit SINAD by the impact of timing jitter. We clarify how channel mismatches interact and perform a worst case analysis of the explicit SINAD for individual mismatch errors. We also show that equations describing the expected SINAD of individual mismatch errors are special cases of our general formulation. We indicate how to use the expected SINAD for finding efficient optimization priorities and demonstrate the importance of worst case analyses.

*Index Terms*—Analog-to-digital converter (ADC), channel mismatch, error analysis, signal-to-noise-and-distortion ratio (SINAD), time-interleaving, timing jitter.

#### I. INTRODUCTION

**M**ODERN signal processing applications emerging in the telecommunications and instrumentation industries need high-speed analog-to-digital converters (ADCs), which can be realized by a time-interleaved architecture that can be combined with practically any ADC technology. Recent high-speed ADCs using this time-interleaved technology achieve sampling rates up to 20 GSa/s [1]; nevertheless, the time-interleaving concept is not restricted to high-speed applications but has been successfully applied to high-resolution oversampling ADCs as well [2], [3].

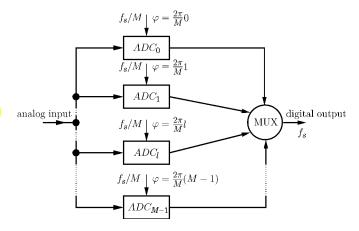

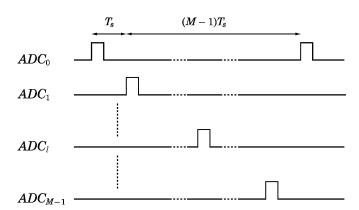

A time-interleaved ADC consists of M channel ADCs, which have the same sampling rate but different sampling phases, as if they were a single converter operating at an M times higher sampling rate [4], [5]. The time-interleaved architecture is illustrated in Fig. 1, where each channel ADC operates with a sampling frequency of  $f_s/M$ . In Fig. 2, we see the timing diagram of a time-interleaved ADC. Each time a sample is taken, a digital output is produced. Hence, each channel ADC has a sampling period of  $MT_s$ , whereas the time-interleaved system has a sampling period of  $T_s$ .

Unfortunately, it is a drawback of time-interleaved ADCs that any mismatch between the channel ADCs causes spurious com-

The author is with the Christian Doppler Laboratory for Nonlinear Signal Processing, Institute of Signal Processing and Speech Communication, Graz University of Technology, Graz, Austria (e-mail: c.vogel@ieee.org).

Fig. 1. Time-interleaved ADC with M channels.

Fig. 2. Timing diagram of a time-interleaved ADC with M channels.

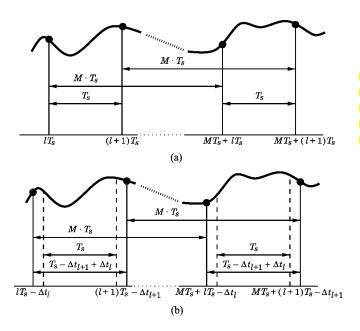

ponents in the spectrum degrading the signal-to-noise-and-distortion ratio (SINAD) [6]. Three types of mismatches result in the main degradation of the SINAD: gain, offset, and timing mismatches [7]–[10]. The timing mismatch is the deterministic deviation between the ideal and the real sampling time (Fig. 3) of each channel ADC. In contrast, timing jitter (or clock jitter) is the stochastic deviation from each ideal sampling point [11]–[14].

Many techniques were developed to compensate or reduce the errors introduced by mismatches. Adaptive compensation of gain and offset mismatches is treated in [15] and [16]. An offset compensation method utilizing randomly chopped input signals is presented in [17]. A particularly interesting approach that combines adaptive compensation of gain mismatches, chopper-based compensation of offset mismatches, and a correlation-based compensation method for timing mismatches can be found in [18]. However, the authors did not show how to extend their timing mismatch compensation concept from

Manuscript received June 15, 2003; revised June 3, 2004. This work was supported by Infineon Technologies AG.

Digital Object Identifier 10.1109/TIM.2004.834046

Fig. 3. Timing mismatch is the deterministic deviation between (a) the ideal sampling period and (b) the real sampling period. It only affects the sampling process if several channel ADCs are combined. (a) Sampling with an ideal time-interleaved ADC. (b) Sampling with a time-interleaved ADC with timing mismatches. The dashed lines indicate the ideal sampling instants.

two to M channels. Gain and offset mismatch compensation in oversampled ADCs is investigated in [19]. A time-domain identification method for timing mismatches, which utilizes statistical properties of signals with timing mismatches, is introduced in [20] and evaluated in [21] and [22]. Another possibility to improve the performance of a time-interleaved ADC is randomizing [23], [24]. Randomizing does not compensate any mismatch error but evenly distributes the mismatch error power over the frequency band. Implementation aspects of randomization algorithms can be found in [25]. The identification of timing mismatches is treated in [26], where the author uses sinusoidal input signals for the identification. While the reconstruction of signals with offset and gain errors costs only little computational complexity, the reconstruction of signals with timing mismatches, i.e., nonuniformly sampled signals, is in general, computationally expensive or inaccurate [27], [28], although new promising reconstruction methods have been introduced [29]. Another possibility used in today's high-speed ADCs are digitally adjustable delays in the clock path [1], [30].

However, in order to predict the expected TIADC performance and to choose the right compensation methods, we have to know how these combined mismatch effects interact and how much error power they produce. A lot of research on analyzing individual mismatch errors has been carried out, and the first investigations on that subject can be found in [4] and [5]. Gain and offset mismatches are extensively treated in [10], where Gaussian distributed mismatches have been assumed for the statistical analysis. The impact of gain and offset mismatches in time-interleaved oversampling converters is studied in [31]. A sound analysis of timing mismatches can be found in [9]. In addition to signals with timing mismatches, which arise in analog-to-digital conversion, the authors in [32]–[34] also investigate the digital-to-analog conversion of such signals. In [35]

the authors derive probability density functions for Gaussian distributed individual mismatch errors. In [8] and [36], the main results for individual mismatch errors are summarized. In [7], closed-form expressions for calculating the explicit SINAD for all mismatch errors together are given for the case where these errors are known deterministically, but the equations given in [7] are rather involved and difficult to extend to an arbitrary number of channels. Moreover, a statistical analysis of combined channel mismatch effects and the effect of timing jitter in combination with mismatch effects has not been considered at all. In [37], the authors provide a first analysis of nonlinearity mismatches, and in [38], some properties of nonlinearity mismatches are presented; however, a complete mathematical treatment is introduced in [39]. There, the authors show that nonlinearity mismatches can be understood as generalizations of offset and gain mismatches. Thus, individual errors are well understood, but a general deterministic analysis, which also incorporates the influence of the nondeterministic timing jitter, and a general statistical analysis of combined channel mismatches, are still missing.

This paper first develops a deterministic description of the output spectrum of a time-interleaved ADC with gain, offset, and timing mismatches. From the output spectrum description, the explicit SINAD of combined channel mismatches is calculated. Furthermore, we show how channel mismatch effects, timing jitter, and quantization noise interact and provide a worst case analysis of individual mismatch errors. After that, the expected SINAD for combined channel mismatch effects is computed. Finally, we show numerical simulation results and discuss application areas. For all derivations, we use the following notations:

| $\Omega$                                               | continuous-time angular frequency;                         |

|--------------------------------------------------------|------------------------------------------------------------|

| $\omega$                                               | discrete-time angular frequency;                           |

| M                                                      | number of channel ADCs;                                    |

| $T_s$                                                  | sampling period of the time-interleaved ADC;               |

| $g_l$                                                  | deterministic gain of the <i>l</i> th channel ADC;         |

| $o_l$                                                  | deterministic offset of the <i>l</i> th channel ADC;       |

| $r_l$                                                  | deterministic relative timing deviation of the <i>l</i> th |

|                                                        | channel ADC;                                               |

| $\Delta t_l$                                           | deterministic absolute timing deviation of the <i>l</i> th |

|                                                        | channel ADC;                                               |

| $\mu$                                                  | expected value;                                            |

| $\sigma$                                               | standard deviation;                                        |

| $\tilde{g}_l$                                          | random variable corresponding to $g_l$ ;                   |

|                                                        | random variable corresponding to $o_l$ ;                   |

| $\widetilde{	ilde{t}}_{l} \ \widetilde{	ilde{\delta}}$ | random variable corresponding to $r_l$ ;                   |

| $	ilde{\delta}$                                        | random variable for the timing jitter.                     |

|                                                        |                                                            |

#### II. THEORY

Our novel approach is based on a time-interleaved ADC model that takes offset, gain, and timing mismatches into account. First, we carry out the deterministic analysis of combined channel mismatches. Then, we derive the explicit SINAD for combined channel mismatches and extend it by timing jitter and quantization noise. After that, we perform worst case analyses of individual errors. Finally, we derive a closed-form expression to calculate the expected SINAD for arbitrary mismatch distributions.

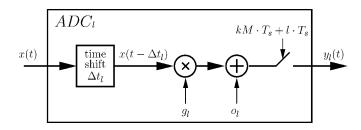

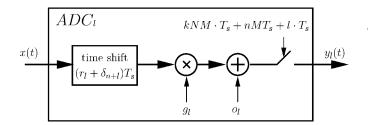

Fig. 4. Mathematical model of a channel ADC. The input signal x(t) is time-shifted by  $\Delta t_i$ , amplified by  $g_i$ , added to an offset  $o_i$ , and finally sampled with a sampling period of  $M \cdot T_s$  and a constant time shift of  $l \cdot T_s$ .

#### A. Deterministic Analysis of Time-Interleaved ADCs

The main spurious frequencies of a time-interleaved ADC system are caused by gain, offset, and timing mismatches [9], [10]. Therefore, a time-interleaved ADC model needs parameters for all three effects. These are defined as gains  $g_l$ , offsets  $o_l$ , and absolute timing deviations  $\Delta t_l$  from the ideal sampling period  $T_s$ , which can be rewritten as relative timing deviations  $r_l = \Delta t_l/T_s$  for each channel ADC. Fig. 4 shows our channel ADC model. The deviation from the ideal sampling period (i.e., the timing mismatch) is modeled as a time shift  $\Delta t_l$  of the input signal x(t), which simplifies further calculations. Additionally, each channel ADC has a gain  $g_l$  and an offset  $o_l$ . Therefore, the sampled output of one channel ADC becomes

$$y_l(t) = \sum_{k=-\infty}^{\infty} \left( g_l \cdot x(t - \Delta t_l) + o_l \right) \cdot \delta(t - kMT_s - lT_s)$$

(1)

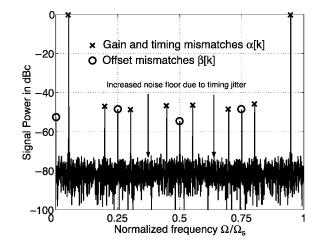

where  $\delta(t)$  is the Dirac delta function [40]. Apart from global offset and gain errors, no mismatch errors would occur if these parameters were identical for all channel ADCs in the system. However, if they differ, spurious tones appear in the spectrum as shown in Fig. 5, where a sinusoidal input signal has been coherently sampled. For such a time-interleaved ADC model, operating at an overall sampling rate of  $\Omega_s$  rad, with a sinusoidal input signal  $x(t) = A \cdot \sin(\Omega_0 t)$  and with  $\omega_0 = \Omega_0 T_s$ , the Fourier transform of the overall sampled output y(t) has the form (see Appendix A for details)

$$Y(j\Omega) = \frac{2\pi}{T_s} \sum_{k=-\infty}^{\infty} \left[ \alpha[k]\delta\left(\Omega - \Omega_0 - k\frac{\Omega_s}{M}\right) - \alpha^*[M-k]\delta\left(\Omega + \Omega_0 - k\frac{\Omega_s}{M}\right) + \beta[k]\delta\left(\Omega - k\frac{\Omega_s}{M}\right) \right]$$

(2)

where

$$\alpha[k] = \frac{A}{j2M} \sum_{l=0}^{M-1} g_l e^{-j\omega_0 r_l} e^{-jkl\frac{2\pi}{M}}$$

$$\beta[k] = \frac{1}{M} \sum_{l=0}^{M-1} o_l e^{-jkl\frac{2\pi}{M}}.$$

(3)

The symbol \* in (2) marks complex conjugation. The Fourier transform shows that some additional spurious peaks are centered at  $\pm \Omega_0 + k\Omega_s/M$  in the case of gain and timing mismatches, whereas others are centered at  $k\Omega_s/M$  in the case

Fig. 5. Output spectrum of a time-interleaved ADC. We have simulated a time-interleaved ADC with 10-bit resolution and a full-scale range (FSR) [6] of 2 consisting of four channels (M = 4) with gain ( $g = [0.994\,0.989\,1.009\,0.996]$ ), offset ( $o = [-0.002\,0.0033\,-0.0021\,-0.004]$ ), and timing mismatches ( $r = [-0.009\,-0.002\,-0.008\,0.004]$ ). Additonally, we have used Gaussian distributed timing jitter with a standard deviation of  $\sigma_{\tilde{\delta}} = 0.01$  for the simulation. Furthermore, we have applied a sinusoidal input signal with amplitude A = 0.99 and frequency  $f_0 = 107 (f_s/2048)$  (coherent sampling) from which 2048 sampling points have been taken. The normalized frequency corresponds to ( $\omega/2\pi$ ) = ( $\Omega T_s/2\pi$ ).

of offset mismatches, which is consistent with our simulations (Fig. 5) and the literature [7], [8]. We see that even the original signal component is influenced by gain and timing mismatches  $(\alpha[0], \alpha^*[M])$ . It is interesting to notice that both coefficient sets  $\alpha[k]$  and  $\beta[k]$  are discrete Fourier transforms (DFTs) of their corresponding channel parameters.

#### B. Derivation of the Explicit SINAD

In order to calculate the SINAD as defined in [6], we use the coefficients  $\alpha[k], \beta[k]$  from (3). First, we neglect quantization noise and timing jitter, and later on, we show how to add in both quantities. We see that the coefficients  $\alpha[0]$  and  $\alpha^*[M]$ represent the original sinusoidal signal, i.e., the measured signal power  $P_S^{gr}$ , whereas all other coefficients represent additional unwanted tones, i.e., the mismatch error power  $P_N^{gro}$ . It should be noted that the measured signal power  $P_S^{gr}$  itself is influenced by mismatch effects and differs from the original input signal power  $P_S$ . Nevertheless, the standard [6] uses only the measured signal for determining the SINAD, which is, regarding from a measurement point of view, quite reasonable for an ADC. The superscripts in the power symbols  $P_N$  and  $P_S$ , e.g., g and r, indicate these influences of different error sources on the power. When we substitute the measured signal power and the mismatch error power into the definition of the SINAD, we get an explicit formula, which combines all three mismatch effects

$$\begin{aligned} \text{SINAD} &= 10 \log_{10} \left( \frac{P_S^{gr}}{P_N^{gro}} \right) \\ &= 10 \log_{10} \left( 2 \left| \alpha[0] \right|^2 \right) \\ &- 10 \log_{10} \left( 2 \sum_{k=1}^{M-1} \left| \alpha[k] \right|^2 + \sum_{k=0}^{M-1} \left| \beta[k] \right|^2 \right). \end{aligned}$$

(4)

Equation (4) unifies and extends the equations found in [7]. It can handle an arbitrary number of channels and can easily be evaluated.

To get a deeper insight, we rewrite (4). The measured signal power  $P_S^{gr}$  can be written as

$$P_{S}^{gr} = 2 |\alpha[0]|^{2}$$

$$= \frac{A^{2}}{2} \left| \frac{1}{M} \sum_{l=0}^{M-1} g_{l} e^{-j\omega_{0}r_{l}} \right|^{2}$$

$$= \frac{A^{2}}{2} \left| \frac{1}{M} \sum_{l=0}^{M-1} g_{l} \cos(\omega_{0}r_{l}) - j\frac{1}{M} \sum_{l=0}^{M-1} g_{l} \sin(\omega_{0}r_{l}) \right|^{2}$$

$$= \frac{A^{2}}{2} \left( \overline{\gamma_{1}}^{2} + \overline{\gamma_{2}}^{2} \right)$$

(5)

where

$$\overline{\gamma_1} = \frac{1}{M} \sum_{l=0}^{M-1} g_l \cos(\omega_0 r_l) \tag{6}$$

$$\overline{\gamma_2} = \frac{1}{M} \sum_{l=0}^{M-1} g_l \sin(\omega_0 r_l). \tag{7}$$

The derivation explicitly shows that a global timing deviation does not influence the signal power. Hence, for determining the SINAD we can always assume that

$$\sum_{l=0}^{M-1} r_l = 0.$$

(8)

The mismatch error power  $P_N^{gro}$  consists of two terms. The gain and timing mismatch error power  $P_N^{gr} = 2\sum_{\substack{k=1\\N=1}}^{M-1} |\alpha[k]|^2$  and the offset mismatch error power  $P_N^o = \sum_{\substack{k=0\\N=1}}^{M-1} |\beta[k]|^2$ . The offset mismatch error power  $P_N^o$  can be rewritten using Parseval's theorem

$$\sum_{k=0}^{M-1} |X[k]|^2 = M \sum_{n=0}^{M-1} |x[n]|^2$$

(9)

where x[n] and X[k] are arbitrary DFT pairs, resulting in

$$P_N^o = \sum_{k=0}^{M-1} |\beta[k]|^2 = \frac{1}{M} \sum_{l=0}^{M-1} |o_l|^2 = \overline{|o|^2}.$$

(10)

The gain and timing mismatch error power  $P_N^{gr}$  can be split into  $2\sum_{k=0}^{M-1} |\alpha[k]|^2 - 2|\alpha[0]|^2$ , where we have already evaluated the second term with (5). Using again Parseval's theorem, the first term can be rewritten as

$$2\sum_{k=0}^{M-1} |\alpha[k]|^2 = \frac{A^2}{2M} \sum_{l=0}^{M-1} |g_l e^{-j\omega_0 r_l}|^2$$

$$= \frac{A^2}{2} \frac{1}{M} \sum_{l=0}^{M-1} g_l^2 = \frac{A^2}{2} \overline{g^2}.$$

(11)

Combining (5) and (11) results in

$$P_N^{gr} = \frac{A^2}{2} \left( \overline{g^2} - \left( \overline{\gamma_1}^2 + \overline{\gamma_2}^2 \right) \right). \tag{12}$$

If we combine the simplified terms (5), (10), and (12), we obtain from (4)

$$\begin{aligned} \text{SINAD} &= 10 \log_{10} \left( \frac{P_S^{gr}}{P_N^{gr} + P_N^o} \right) \\ &= 10 \log_{10} \left( \frac{A^2}{2} \left( \overline{\gamma_1}^2 + \overline{\gamma_2}^2 \right) \right) \\ &- 10 \log_{10} \left( \frac{A^2}{2} \left( \overline{g^2} - \left( \overline{\gamma_1}^2 + \overline{\gamma_2}^2 \right) \right) + \overline{|o|^2} \right) \\ &= 10 \log_{10} \left( \frac{P_S^{gr}}{\frac{A^2}{2} \overline{g^2} - P_S^{gr} + P_N^o} \right) \end{aligned}$$

(13)

which explicitly indicates how gain and timing mismatches interact.

#### C. Explicit SINAD with Timing Jitter and Quantization Noise

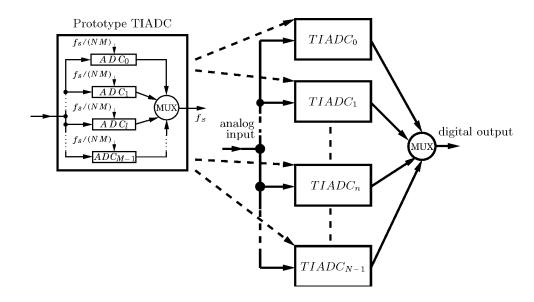

To complete our description, we investigate the influence of timing jitter and quantization noise on the SINAD. Therefore, we assume that both quantities and the mismatches are mutually independent. To derive the influence of the timing jitter, we use a special arrangement of TIADCs, illustrated in Fig. 6. On the left side, we see a prototype TIADC. With this prototype TIADC, we build a structure of N identical TIADCs, all of which sample in a time-interleaved manner. Hence, the first TIADC takes M samples, then the second one takes M samples and so forth, until the Nth TIADC takes M samples and the first TIADC starts again. Therefore, the measured signal power of such a structure can be written as

$$P_S^{gr} = \frac{A^2}{2} \left| \frac{1}{N} \sum_{n=0}^{N-1} \frac{1}{M} \sum_{l=0}^{M-1} g_l e^{-j\omega_0 r_l} \right|^2$$

(14)

where the measured signal power is, due to the repetitive structure of TIADCs, identical to the case of a single TIADC given by (5). Next, we consider a structure of N identical TIADCs, where each TIADC channel has an additional relative timing deviation  $\delta_{n+l}$  (Fig. 7) which is not repetitive but varies among all channels of the structure, which results in

$$P_{S}^{gr} = \frac{A^{2}}{2} \left| \frac{1}{N} \sum_{n=0}^{N-1} \frac{1}{M} \sum_{l=0}^{M-1} g_{l} e^{-j\omega_{0}r_{l}} e^{-j\omega_{0}\delta_{n+l}} \right|^{2}.$$

(15)

If we assume that the stochastic process underlying the additional relative timing deviations  $\delta_{n+l}$  is ergodic [41], then its time average is an unbiased estimator [42] of its expected value defined as

$$\mu_{\tilde{\delta}} = E\{\tilde{\delta}\} := \int_{-\infty}^{\infty} x f_{\tilde{\delta}}(x) dx \tag{16}$$

Fig. 6. To determine the effect of timing jitter, we build a structure of TIADCs by repeating one prototype TIADC with M channels each N times. The structure itself samples in a time-interleaved manner. Thereby, we obtain time-interleaved TIADCs (a meta TIADC with a total of  $N \cdot M$  channels). All TIADCs in the meta TIADC have the same properties (gain, offset, and timing deviation of the channel ADCs). Only an additional timing deviation (cf. Fig. 7) varies among all channels of the meta TIADC. When we let the number of TIADCs N go to infinity, we get a meta TIADC, which is identical in its behavior to the prototype TIADC, except for the additional timing deviations which model the nondeterministic timing jitter.

Fig. 7. Mathematical model of the channel ADCs used for Fig. 6. The additional timing deviation  $\delta_{n+l}T_s$  will lead us to timing jitter.

where  $f_{\delta}$  is the probability density function of the random variable  $\delta$  [41] associated with the observations  $\delta_{n+l}$ . Therefore, we can write (15) as

$$\lim_{N \to \infty} P_S^{gr} = \frac{A^2}{2} \left| \frac{1}{N} \sum_{n=0}^{N-1} \frac{1}{M} \sum_{l=0}^{M-1} g_l e^{-j\omega_0 r_l} e^{-j\omega_0 \delta_{n+l}} \right|^2$$

$$= \frac{A^2}{2} \left| E \left\{ \frac{1}{M} \sum_{l=0}^{M-1} g_l e^{-j\omega_0 r_l} e^{-j\omega_0 \tilde{\delta}} \right\} \right|^2$$

(17)

and finally obtain

$$P_{S}^{gr\delta} = \frac{A^{2}}{2} \left( \overline{\gamma_{1}}^{2} + \overline{\gamma_{2}}^{2} \right) \left| E\{e^{-j\omega_{0}\tilde{\delta}}\} \right|^{2}$$

$$= \frac{A^{2}}{2} \left( \overline{\gamma_{1}}^{2} + \overline{\gamma_{2}}^{2} \right) \left| \Phi_{\tilde{\delta}}(\omega_{0}) \right|^{2}.$$

(18)

The expression  $\Phi_{\tilde{\delta}}(\omega_0)$  is the characteristic function of the random variable  $\tilde{\delta}$  defined by  $\Phi_{\tilde{\delta}}(\omega) = E\{e^{j\omega\tilde{\delta}}\} = \int_{-\infty}^{\infty} f_{\tilde{\delta}}(x)e^{j\omega x}dx$  [41]. Thus, we have extended our structure of TIADCs to infinity, whereby each sample is taken by a different channel with a different additional timing deviation, which models the timing jitter of the system. From (13) we see that this modified signal power completely describes the TIADC. Hence, we can write for a TIADC with timing jitter

SINAD

$$= 10 \log_{10} \left( \frac{P_S^{gr\delta}}{\frac{A^2}{2} \overline{g^2} - P_S^{gr\delta} + P_N^o} \right)$$

$$= 10 \log_{10} \left( \frac{A^2}{2} \left( \overline{\gamma_1}^2 + \overline{\gamma_2}^2 \right) \left| \Phi_{\delta}(\omega_0) \right|^2 \right)$$

$$- 10 \log_{10} \left( \frac{A^2}{2} \left( \overline{g^2} - \left( \overline{\gamma_1}^2 + \overline{\gamma_2}^2 \right) \left| \Phi_{\delta}(\omega_0) \right|^2 \right) + \overline{|o|^2} \right)$$

$$= 10 \log_{10} \left( \frac{P_S^{gr\delta}}{P_N^{gr\delta} + P_N^o} \right).$$

(19)

When we assume that the quantization noise is independent from all other effects, (19) becomes

$$SINAD = 10 \log_{10} \left( \frac{P_S^{gr\delta}}{P_N^{gr\delta} + P_N^o + P_N^q} \right)$$

(20)

where  $P_N^q = \Delta^2/12$ . The symbol  $\Delta$  is the quantization step size, which is given for an N bit converter by  $\Delta = \text{FSR}/2^N$ , where FSR is the full-scale range [6]. With (20), we have derived an explicit combined mismatch description, which also takes timing jitter and quantization noise into account.

Unfortunately, the mismatch error power and the timing jitter power are coupled; nevertheless, they can be separated by using some simplifications. By assuming Gaussian distributed timing jitter, we can evaluate the characteristic function  $|\Phi_{\tilde{\delta}}(\omega_0)|^2$  to  $e^{-\omega_0^2 \sigma_{\tilde{\delta}}^2}$  [cf. (43)], where  $\sigma_{\tilde{\delta}}$  is the standard deviation of the timing jitter. The Taylor series expansion of  $e^{-\omega_0^2 \sigma_{\tilde{\delta}}^2}$  gives  $1 - \omega_0^2 \sigma_{\tilde{\delta}}^2 + (1/2)\omega_0^4 \sigma_{\tilde{\delta}}^4 - \dots$ , where we see that the higher order terms are small compared to the first two and can be neglected. Therefore, we can express (20) as

$$\begin{aligned} \text{SINAD} &= 10 \log_{10} \left( \frac{A^2}{2} \left( \overline{\gamma_1}^2 + \overline{\gamma_2}^2 \right) \left( 1 - \omega_0^2 \sigma_{\delta}^2 \right) \right) \\ &- 10 \log_{10} \left( \frac{A^2}{2} \left( \overline{g^2} - \left( \overline{\gamma_1}^2 + \overline{\gamma_2}^2 \right) \left( 1 - \omega_0^2 \sigma_{\delta}^2 \right) \right) \\ &+ \overline{|o|^2} + \frac{\Delta^2}{12} \right) \\ &= 10 \log_{10} \left( \frac{P_S^{gr} - P_N^{\delta}}{P_N^{gr} + P_N^{\delta} + P_N^{o} + P_N^{gr}} \right) \end{aligned}$$

(21)

where  $P_N^{\delta} = (A^2/2)(\overline{\gamma_1}^2 + \overline{\gamma_2}^2)(\omega_0^2 \sigma_{\delta}^2)$ . Through these simplifications, we have separated the mismatch error power from the jitter noise error power. When we neglect the mismatch effects, the result is comparable to the results in [12] and [14].

# D. Worst Case Analysis of the SINAD for Individual Mismatch Errors

To obtain the worst cases for individual mismatch errors, we set upper and lower bounds for the parameters  $x_l \in [x_{\min}, x_{\max}]$ , where  $x_l$  stands for a certain parameter  $g_l$ ,  $o_l$ , or  $r_l$ . We neglect timing jitter and quantization noise and further assume an even number of ADCs M.

We first start with the special case where timing and offset mismatches are negligible (e.g.,  $r_l = 0$  and  $o_l = 0$ ), so that we can write for (13)

$$\operatorname{SINAD} = 10 \log_{10} \left( \frac{\frac{A^2}{2} \overline{g}^2}{\frac{A^2}{2} (\overline{g^2} - \overline{g}^2)} \right).$$

(22)

With the relation

$$\sum_{l=0}^{M-1} g_l^2 - \frac{1}{M} \left( \sum_{l=0}^{M-1} g_l \right)^2 = \sum_{l=0}^{M-1} (g_l - \overline{g})^2 \qquad (23)$$

the worst case for (13) is obtained as

$$SINAD = 20 \log_{10} \left( \frac{\overline{g}}{\Delta g_{\text{max}}} \right)$$

(24)

where  $\Delta g_{\text{max}} = (g_{\text{max}} - g_{\text{min}})/2$ . Thus, the worst case occurs if all  $g_l$  are either  $g_{\text{min}}$  or  $g_{\text{max}}$  and the average  $\overline{g}$  of all  $g_l$  is  $(g_{\text{min}} + g_{\text{max}})/2$ .

Second, if gain and offset mismatches are negligible (e.g.,  $g_l = \overline{g}$  and  $o_l = 0$ ), we can express (13) as

$$\operatorname{SINAD} = 20 \log_{10} \left( \frac{\frac{A^2}{2} \overline{g}^2 \left( \overline{\phi_1}^2 + \overline{\phi_2}^2 \right)}{\frac{A^2}{2} \overline{g}^2 \left( 1 - \left( \overline{\phi_1}^2 + \overline{\phi_2}^2 \right) \right)} \right) \quad (25)$$

where

$$\overline{\phi_1} = \frac{1}{M} \sum_{l=0}^{M-1} \cos(\omega_0 r_l)$$

(26)

$$\overline{\phi_2} = \frac{1}{M} \sum_{l=0}^{M-1} \sin(\omega_0 r_l).$$

(27)

To obtain the worst case, we simplify (25) to

SINAD =

$$20 \log_{10} \left( \frac{1}{\left( \frac{1}{\left( \overline{\phi_1}^2 + \overline{\phi_2}^2 \right)} - 1 \right)} \right)$$

(28)

and recognize that we can minimize (28) by minimizing the term  $(\overline{\phi_1}^2 + \overline{\phi_2}^2)$ . Since both quantities  $\overline{\phi_1}$  and  $\overline{\phi_2}$  are squared, their smallest possible value is zero. According to (8) and the cosines in (26), the quantity  $\overline{\phi_1}$  has its minimum if all  $r_l$  are either  $r_{\text{max}}$  or  $r_{\text{min}}$ . The quantity  $\overline{\phi_2}$  is zero for  $r_l \equiv 0$ , or if the number of  $r_l = r_{\text{max}}$  equals the number of  $r_l = r_{\text{min}}$ . Therefore, the worst case for (13) reduces to

$$SINAD = 20 \log_{10} \left( \frac{1}{\omega_0 \Delta r_{\text{max}}} \right) \tag{29}$$

where  $\Delta r_{\text{max}} = (r_{\text{max}} - r_{\text{min}})/2$ . Again, the worst case occurs if all  $r_l$  are either  $r_{\text{min}}$  or  $r_{\text{max}}$  and the average  $\overline{r}$  of all  $r_l$  is  $(r_{\text{min}} + r_{\text{max}})/2$ .

Third, if gain and timing mismatches are negligible (e.g.,  $g_l = \overline{g}$  and  $r_l = 0$ ), the worst case for (13) is

$$SINAD = 20 \log_{10} \left( \frac{A\overline{g}}{\sqrt{2}\hat{o}_{\max}} \right)$$

(30)

where all  $o_l = \hat{o}_{max} = max(|o_{min}|, |o_{max}|)$ . However, from (2) we see that for this special case the energy is concentrated in  $\Omega = 0$  and is not caused by a mismatch effect. In fact, we are confronted with a global offset. Thus, we can simply filter this error energy by subtracting the arithmetic mean value from the output signal of the time-interleaved ADC. Thereby we get the reduced worst case for offset mismatches

$$SINAD = 20 \log_{10} \left( \frac{A\overline{g}}{\sqrt{2}\Delta o_{\max}} \right)$$

(31)

where  $\Delta o_{\text{max}} = (o_{\text{max}} - o_{\text{min}})/2$ , which is more consistent with the other worst cases. Hence, all  $o_l$  are either  $o_{\text{min}}$  or  $o_{\text{max}}$  and the average  $\overline{o}$  of all  $o_l$  is  $(o_{\text{min}} + o_{\text{max}})/2$ .

#### E. Derivation of the Expected SINAD

So far, we are able to calculate the SINAD of a time-interleaved ADC if the explicit parameters  $g_l$ ,  $r_l$ , and  $o_l$  of each channel ADC and its timing jitter distribution are known. However, if only the probability distributions of the mismatch parameters are known, e.g., for a particular production process, we need to derive a formula for the expected SINAD from (13). In Section II-C, we have shown how timing jitter and quantization noise power can be separated. Therefore, we only investigate the statistical behavior of the mismatches. We replace the measured signal and the mismatch error power by their expected values, as defined in (16), and substitute the explicit parameters by corresponding random variables  $\tilde{g}_l$ ,  $\tilde{r}_l$ , and  $\tilde{o}_l$ . Furthermore, we assume that all mismatch effects are mutually independent and get

$$SINAD = 10 \log_{10} \left( \frac{E \left\{ P_S^{\tilde{g}\tilde{r}} \right\}}{E \left\{ P_N^{\tilde{g}\tilde{r}\tilde{o}} \right\}} \right)$$

$$= 10 \log_{10} \left( \frac{E \left\{ P_S^{\tilde{g}\tilde{r}\tilde{o}} \right\}}{E \left\{ \frac{A^2}{2} \overline{\tilde{g}^2} - P_S^{\tilde{g}\tilde{r}} \right\} + E \left\{ P_N^{\tilde{o}} \right\}} \right). (32)$$

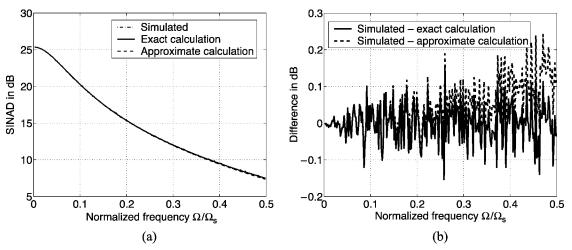

Fig. 8. Simulated time-interleaved ADC with 10-bit resolution and an FSR of 2 consisting of four channels (M=4) with gain ( $g = [1.01\ 0.95\ 1.03\ 0.97]$ ), offset ( $o = [0.01\ -0.03\ -0.04\ 0.02]$ ), and timing mismatches ( $r = [0.1\ -0.09\ 0.05\ -0.07]$ ). Additionaly, we have used Gaussian distributed timing jitter ( $\sigma_{\tilde{\sigma}} = 0.1$ ) for the simulation and have applied sinusoidal input signals with amplitude A = 0.9, where each signal has been sampled with 16 348 sampling points through coherent sampling. We see the accuracy of the exact SINAD calculation (20); however, even the approximated SINAD calculation (21), where the timing jitter power is separated from the other power sources, only slightly deviates from the simulated one. (a) Comparison between the simulated SINAD and the SINAD calculated according to (20) (exact) and (21) (approximated), respectively. (b) Difference between the simulated and the exactly calculated SINAD (solid line) and between the simulated and the approximated SINAD (dashed line).

We reduce (32) in three steps. First, we simplify the expected measured signal power  $E\{P_S^{\tilde{g}\tilde{r}}\}$ . Then, we focus on the combined gain and timing mismatch error power  $E\{(A^2/2)\overline{\tilde{g}}^2 - P_S^{\tilde{g}\tilde{r}}\}$ , and finally, we evaluate the offset mismatch error power  $E\{P_N^{\tilde{v}}\}$ .

The measured signal power can be expressed as

$$E\left\{P_{S}^{\tilde{g}\tilde{r}}\right\} = \frac{A^{2}}{2} \left|\frac{1}{M}\sum_{l=0}^{M-1} \tilde{g}_{l}e^{-j\omega_{0}\tilde{r}_{l}}\right|^{2}$$

$$= \frac{A^{2}}{2M^{2}}\sum_{l=0}^{M-1}\sum_{m=0}^{M-1} E\{\tilde{g}_{l}\tilde{g}_{m}e^{-j\omega_{0}\tilde{r}_{l}}e^{j\omega_{0}\tilde{r}_{m}}\}.$$

(33)

In order to simplify (33), we distinguish between two cases. For the first one, we set l = m, and for the second one, we set  $l \neq m$ . After evaluating both cases, we can add the results. This leads us to

$$l = m \Rightarrow \frac{A^2}{2M^2} \sum_{l=0}^{M-1} E\left\{\tilde{g}_l^2 e^{-j\omega_0(\tilde{r}_l - \tilde{r}_l)}\right\} = \frac{A^2}{2M} \left(\mu_{\tilde{g}}^2 + \sigma_{\tilde{g}}^2\right)$$

(34)

$$l \neq m \Rightarrow \frac{A^2}{2M^2} \sum_{l=0}^{M-1} \sum_{m=0, m \neq l}^{M-1} E\{\tilde{g}_l\} E\{\tilde{g}_m\} \times E\{e^{-j\omega_0 \tilde{r}_l}\} E\{e^{j\omega_0 \tilde{r}_m}\} = \frac{A^2}{2M} \left((M-1)\mu_{\tilde{g}}^2 |\Phi_{\tilde{r}}(\omega_0)|^2\right)$$

(35)

and finally results in

$$E\left\{P_{S}^{\tilde{g}\tilde{r}}\right\} = (34) + (35)$$

=  $\frac{A^{2}}{2M}\left(\mu_{\tilde{g}}^{2}\left((M-1)\left|\Phi_{\tilde{r}}(\omega_{0})\right|^{2}+1\right) + \sigma_{\tilde{g}}^{2}\right).(36)$

The symbol  $\mu_{\tilde{g}}$  denotes the mean value and the symbol  $\sigma_{\tilde{g}}$  the standard deviation of the gain mismatch variable  $\tilde{g}$ . The expression  $\Phi_{\tilde{r}}(\omega_0)$  is the characteristic function of the random variable  $\tilde{r}$ . A simplified form of the gain and timing mismatch error power in (32) can be found by

$$E\left\{\frac{A^{2}}{2}\overline{\tilde{g}^{2}} - P_{S}^{\tilde{g}\tilde{r}}\right\} = \frac{A^{2}}{2}\left(\mu_{\tilde{g}}^{2} + \sigma_{\tilde{g}}^{2}\right) - \frac{A^{2}}{2M} \\ \times \left(\mu_{\tilde{g}}^{2}\left((M-1)\left|\Phi_{\tilde{r}}(\omega_{0})\right|^{2} + 1\right) + \sigma_{\tilde{g}}^{2}\right) \\ = \frac{A^{2}}{2M}(M-1) \\ \times \left(\mu_{\tilde{g}}^{2}\left(1 - \left|\Phi_{\tilde{r}}(\omega_{0})\right|^{2}\right) + \sigma_{\tilde{g}}^{2}\right).$$

(37)

The offset mismatch error power in (32) can be reduced to

$$E\left\{P_{N}^{\tilde{o}}\right\} = \frac{1}{M} \sum_{l=0}^{M-1} E\left\{\left|\tilde{o}_{l}\right|^{2}\right\}$$

$$= \left(\mu_{\tilde{o}}^{2} + \sigma_{\tilde{o}}^{2}\right). \tag{38}$$

When we combine all three simplified parts and substitute them in (32), we obtain

$$\begin{aligned} \text{SINAD} &= 10 \log_{10} \left( \frac{E \left\{ P_{S}^{\tilde{g}\tilde{r}} \right\}}{E \left\{ P_{N}^{\tilde{g}\tilde{r}\tilde{o}} \right\}} \right) \\ &= 10 \log_{10} \\ & \left( \frac{A^{2}}{2M} \left( \mu_{\tilde{g}}^{2} \left( (M-1) \left| \Phi_{\tilde{r}}(\omega_{0}) \right|^{2} + 1 \right) + \sigma_{\tilde{g}}^{2} \right) \right) \\ &- 10 \log_{10} \\ & \left( \frac{A^{2}}{2M} (M-1) \left( \mu_{\tilde{g}}^{2} \left( 1 - \left| \Phi_{\tilde{r}}(\omega_{0}) \right|^{2} \right) + \sigma_{\tilde{g}}^{2} \right) \\ &+ \left( \mu_{\tilde{o}}^{2} + \sigma_{\tilde{o}}^{2} \right) \right). \end{aligned}$$

(39)

In order to evaluate (39), we need the expected value  $\mu_{\tilde{g}}$  and the standard deviation  $\sigma_{\tilde{g}}$  of the gain probability distribution, the expected value  $\mu_{\tilde{o}}$  and the standard deviation  $\sigma_{\tilde{o}}$  of the offset probability distribution, and the characteristic function  $\Phi_{\tilde{r}}(\omega_0)$ of the timing deviation probability distribution. Estimates of the

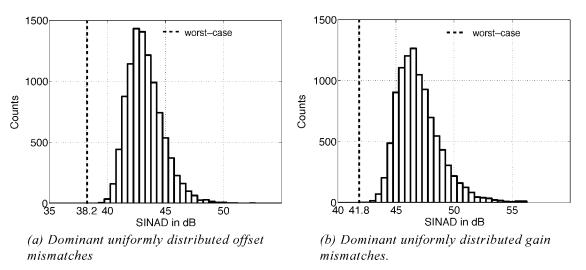

Fig. 9. Histogram plots show the SINAD of an eight channel TIADC (M=8)for 10 000 realizations with 1024 samples. The sinusoidal input signal with A = 1 has been coherently sampled with  $f_0 = (307/1024) f_s$ . In (a), we have dominant uniformly distributed offset mismatches with  $\mu_{\tilde{\sigma}} = 0$  and  $\sigma_{\tilde{\sigma}} = 0.005$ , whereas in (b), we see dominant uniformly distributed gain mismatches with  $\mu_{\tilde{g}} = 1$  and  $\sigma_{\tilde{g}} = 0.005$ . The dashed line marks the worst case for (a) according to (31) and for (b) according to (24).

expected value and the standard deviation of an unknown probability distribution can be determined by measuring an appropriate number of samples. What remains difficult is the evaluation of the characteristic function, which generally cannot be solved in closed form.

We evaluate the characteristic function for two cases of special interest where closed-forms are available. First, we assume that the timing mismatch is uniformly distributed. Therefore, the probability density function (pdf) is

$$f_{\tilde{r}}(x) = \begin{cases} \frac{1}{b-a}, & a \le x \le b\\ 0, & \text{otherwise.} \end{cases}$$

(40)

Furthermore, we use the relation  $(b-a)/2 = \sigma_{\tilde{r}}\sqrt{3}$ . Therefore, the characteristic function becomes [9]

$$|\Phi_{\tilde{r}}(\omega_0)|^2 = \left| \int_{-\infty}^{\infty} f_{\tilde{r}}(x) e^{j\omega_0 x} dx \right|^2$$

$$= \operatorname{sinc}^2 \left( \omega_0 \sigma_{\tilde{r}} \sqrt{3} \right) \tag{41}$$

where  $\operatorname{sinc}(x) = \sin(x)/x$ .

In the same way, we can carry out the calculations for Gaussian distributed timing mismatches. With the pdf of a Gaussian distribution

$$f_{\tilde{r}}(x) = \frac{1}{\sqrt{2\pi\sigma_{\tilde{r}}^2}} e^{-\frac{(x-\mu_{\tilde{r}})^2}{2\sigma_{\tilde{r}}^2}}$$

(42)

and the relation  $\int_{-\infty}^{\infty}e^{-(x^2/2)}dx=\sqrt{2\pi}$  we get the characteristic function

$$|\Phi_{\tilde{r}}(\omega_0)|^2 = \left| \int_{-\infty}^{\infty} f_{\tilde{r}}(x) e^{j\omega_0 x} dx \right|^2$$

$$= e^{-\omega_0^2 \sigma_{\tilde{r}}^2}. \tag{43}$$

## F. Derivation of the Expected SINAD for Individual Mismatch Errors

The combined description given by (39) can be used to derive the expected SINAD for individual errors. As for the com-

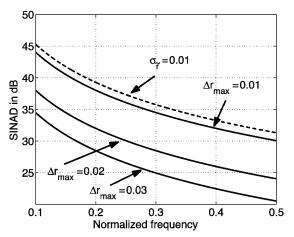

Fig. 10. Comparison of the expected SINAD and the worst case SINAD for a time-interleaved ADC consisting of four channels with dominating timing mismatches. The dashed line shows the expected SINAD for Gaussian distributed timing mismatches (45) with  $\sigma_{\tilde{\tau}} = 0.01$ . The other lines show the worst case SINAD (29) if we set the maximum deviation from the ideal sampling period to three different hard bounds ( $\Delta r_{\text{max}} = 0.01$ ,  $\Delta r_{\text{max}} = 0.02$  and  $\Delta r_{\text{max}} = 0.03$ ).

bined description, we need not know the probability distribution of the gain or the offset mismatches in order to determine their expected SINAD. It is sufficient to know the mean value and the standard deviation. Only for the timing mismatch we have to assume some kind of probability distribution. Assuming a Gaussian distribution for the timing mismatch and assuming further that  $\mu_{\tilde{o}} = 0$ , (39) reduces to

SINAD  $= 10 \log_{10} \left( \frac{A^2}{2M} \left( \mu_{\tilde{g}}^2 \left( (M-1)e^{-\omega_0^2 \sigma_{\tilde{\pi}}^2} + 1 \right) + \sigma_{\tilde{g}}^2 \right) \right) - 10 \log_{10} \left( \frac{A^2}{2M} (M-1) \left( \mu_{\tilde{g}}^2 \left( 1 - e^{-\omega_0^2 \sigma_{\tilde{\pi}}^2} \right) + \sigma_{\tilde{g}}^2 \right) + \sigma_{\tilde{\sigma}}^2 \right).$ (44)

We can show that several known equations for individual mismatch errors are special cases of (44). If  $\sigma_{\tilde{o}} = 0$  and  $\sigma_{\tilde{r}} = 0$ ,

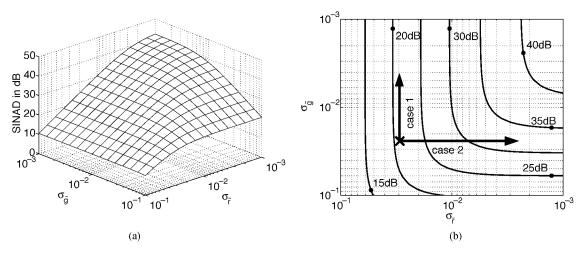

Fig. 11. Expected SINAD for Gaussian distributed gain, offset, and timing mismatch errors. A = 1, M = 8,  $f_0 = 1/2 f_s$ ,  $\mu_{\tilde{g}} = 1$ ,  $\sigma_{\tilde{s}} = 0.005$ , and  $\mu_{\tilde{s}} = 0$ . (a) Plot of the expected SINAD. (b) Isolines of the expected SINAD from Fig. (11a).

only gain mismatch errors occur, and we get (cf. [8], [10], and [36])

$$SINAD = 10 \log_{10} \left( \frac{\mu_{\tilde{g}}^2 M + \sigma_{\tilde{g}}^2}{(M-1)\sigma_{\tilde{g}}^2} \right)$$

$$\simeq 20 \log_{10} \left( \frac{\mu_{\tilde{g}}}{\sigma_{\tilde{g}}} \right) - 10 \log_{10} \left( 1 - \frac{1}{M} \right). \quad (45)$$

For  $\sigma_{\tilde{g}} = 0$  and  $\sigma_{\tilde{r}} = 0$ , we obtain an expression for offset mismatch errors exclusively (cf. [8], [10], and [36])

$$SINAD = 10 \log_{10} \left( \frac{\mu_{\tilde{g}}^2 M}{\frac{2M}{A^2} \sigma_{\delta}^2} \right)$$

$$= 20 \log_{10} \left( \frac{A \mu_{\tilde{g}}}{\sqrt{2} \sigma_{\delta}} \right).$$

(46)

For  $\sigma_{\tilde{o}} = 0$ ,  $\sigma_{\tilde{g}} = 0$ , and by using Taylor series expansion, we get, for Gaussia-distributed timing mismatch errors only (cf. [9])

$$SINAD = 10 \log_{10} \left( \frac{(M-1)e^{-\omega_0^2 \sigma_{\tilde{\tau}}^2} + 1}{(M-1)\left(1 - e^{-\omega_0^2 \sigma_{\tilde{\tau}}^2}\right)} \right)$$

$$\simeq 20 \log_{10} \left(\frac{1}{\omega_0 \sigma_{\tilde{\tau}}}\right) - 10 \log_{10} \left(1 - \frac{1}{M}\right). (47)$$

#### **III. NUMERICAL RESULTS**

Numerical time-domain simulations have been carried out to compare the results of the derived equations and the simulation results and to show their usefulness [43].

The difference between the SINAD of a simulated TIADC with 10-bit resolution, combined channel mismatches and timing jitter and the SINAD calculated according to (20) and (21) is shown in Fig. 8. We see that even for these strong mismatch errors and the strong timing jitter the calculated SINAD is, except for quantization and jitter uncertainties, identical to the simulated one. Moreover, even the approximate SINAD (21), where all error sources are separated, only slightly deviates from the simulation results.

In Fig. 9, we show the applicability of the worst case analyses for dominant uniformly distributed offset Fig. 9(a) and dominant uniformly distributed gain Fig. 9(b) mismatches. For both plots, we have generated 10 000 realizations and determined the SINAD with a coherently sampled sinusoidal input signal. We see how accurately the worst case analyses (dashed lines) determine the lower bound of the SINAD for both examples.

In Fig. 10, we compare the expected and the worst case SINAD for timing mismatches. For the expected SINAD we assume Gaussian distributed timing mismatches (47) with  $\sigma_{\tilde{r}} = 0.01$  and for the corresponding worst case SINAD (29) we set different maximum deviations from the ideal sampling period  $\Delta r_{\text{max}} = 0.01$ ,  $\Delta r_{\text{max}} = 0.02$ , and  $\Delta r_{\text{max}} = 0.03$ . This is the case when we discard all time-interleaved ADC realizations that have a channel ADC with a relative timing deviation smaller than  $r_{\text{min}}$  or greater than  $r_{\text{max}}$ . When we compare the expected SINAD and the worst case SINAD, we see that the worst cases are significantly worse. The worst cases are not very likely to occur and their probability decreases with the number of channels. However, they are the true lower bounds of the SINAD and should, therefore, be considered, too.

Next, we consider the equations for the expected SINAD. To compare it with the averaged SINAD of simulations, we have to average the measured signal power and the error power of all simulated realizations, which is

$$SINAD = 10\log_{10}\left(\frac{\overline{P_S^{gr}}}{\overline{P_N^{gro}}}\right)$$

(48)

where

and

$$\overline{P_S^{gr}} = \frac{1}{K} \sum_{k=0}^{K-1} (P_S^{gr})_k$$

$$\overline{P_N^{gro}} = \frac{1}{K} \sum_{k=0}^{K-1} \left( P_N^{gro} \right)_k.$$

The symbol K denotes the number of realizations, whereas the index k refers to one particular realization.

In Fig. 11, we illustrate the variation of the expected SINAD for the case of Gaussian distributed gain, offset, and timing mismatches (44) as a function of two independent parameters.

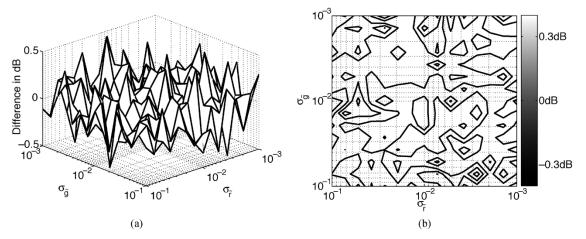

Fig. 12. Difference between the expected SINAD calculated with (44) and the SINAD of simulated time-interleaved ADCs, which have been obtained by averaging over 100 realizations determined according to (48), where for each realization we have taken 8192 samples. The time-interleaved ADC and the distribution parameters have been A = 1, M = 8,  $f_0 = 1/2 f_s$ ,  $\mu_{\tilde{g}} = 1$ ,  $\sigma_{\tilde{z}} = 0.005$ , and  $\mu_{\tilde{z}} = 0$ , hence, the same as in Fig. 11. The difference between the calculated and the simulated and averaged SINAD is less than  $\pm 0.5$  dB. (a) Difference between the expected and the simulated SINAD. (b) Isolines of the difference between the expected and the simulated SINAD from Fig. (12a).

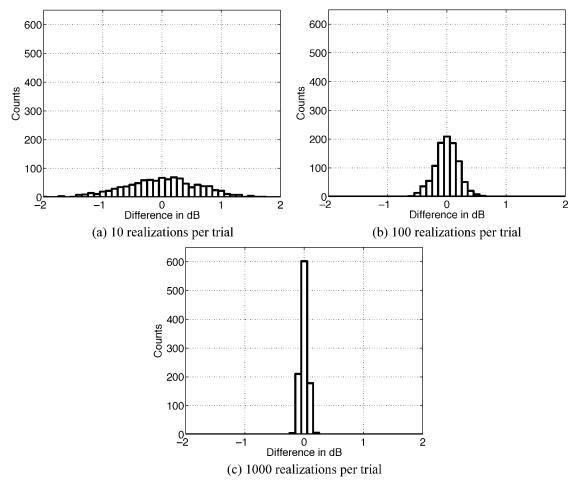

Fig. 13. Histogram plots show the distribution of the difference between the expected SINAD calculated with (44) and the averaged SINAD of simulated time-interleaved ADCs calculated with (48). For each plot 1000 trials have been carried out, but in (a), we have averaged over 10 realizations, in (b), we have averaged over 100 realizations, and in (c), we have averaged over 1000 realizations for each trial. For each realization, 4096 sampling points have been taken. We have used a time-interleaved ADC with eight channels and a sinusoidal input signal according to A = 1 and  $f_0 = (2039/4096) f_s$ . The parameters of the Gaussian distributions have been  $\mu_{\tilde{g}} = 1$  and  $\sigma_{\tilde{g}} = 0.05$  for the gain,  $\mu_{\tilde{\sigma}} = 0$  and  $\sigma_{\tilde{\sigma}} = 0.005$  for the offset, and  $\sigma_{\tilde{\tau}} = 0.03$  for the timing mismatches. The deviation from the expected SINAD becomes smaller when we average more realizations.

Fig. 11(a) shows the three-dimensional surface of the SINAD that appears when  $\sigma_{\tilde{g}}$  and  $\sigma_{\tilde{r}}$  are varied and all other parameters, especially  $\sigma_{\tilde{o}}$ , are fixed. Fig. 11(b) plots the corresponding

isolines of Fig. 11(a). The cross marks the distribution parameters for a given production process. Let us assume that in order to improve the SINAD, we could either develop some method to

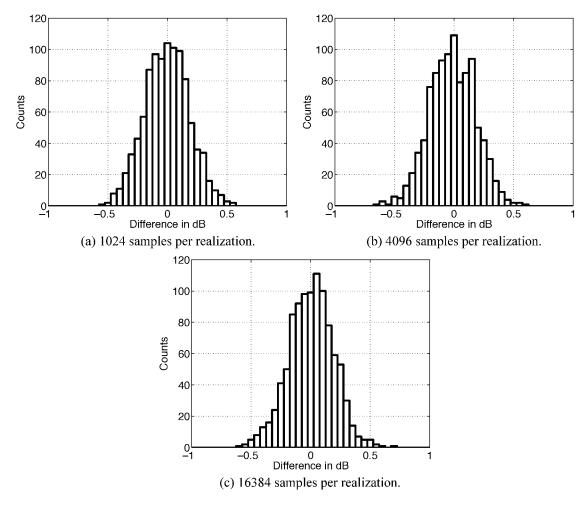

Fig. 14. Histogram plots show the distribution of the difference between the expected SINAD calculated with (44) and the averaged SINAD of simulated time-interleaved ADCs calculated with (48). For each plot, 1000 trials with 100 realizations per trial have been carried out, but in (a), we have used 1024 samples, in (b), we have used 4096 samples, and in (c), we have used 16 384 samples for each realization. Signal and distribution parameters have been identical as for Fig. 13. From (a) to (c), we recognize that the number of samples does not have an observable influence.

reduce the gain mismatch  $\sigma_{\tilde{a}}$  (case 1) or the timing mismatch  $\sigma_{\tilde{r}}$ (case 2). We see that for the first case, we only insignificantly improve the expected SINAD no matter how sophisticated our gain mismatch compensation method will be. The reason is that in our example, the timing mismatch limits the performance of the time-interleaved ADC. Thus, to improve the expected SINAD we first have to find a timing mismatch compensation method (case 2). Afterwards, it makes sense to think about a gain mismatch compensation method. To sum up, we see that the optimization of one parameter (e.g.,  $\sigma_{\tilde{q}}$ ) does not necessarily improve the SINAD if the other parameters are too large. In our example, we only consider the expected SINAD as a function of two independent parameters, since more dimensions are hard to visualize. However, in Fig. 11(b) we can also observe the influence of the parameter  $\sigma_{\tilde{o}}$ . For very small  $\sigma_{\tilde{q}}$  and  $\sigma_{\tilde{r}}$ , the surface flattens because the fixed offset mismatch  $\sigma_{\tilde{o}}$  prevents a further improvement of the expected SINAD. Hence, in order to find efficient optimization priorities, we have to consider all parameters simultaneously.

In Fig. 12, we see the difference between the calculated expected SINAD and the SINAD of simulated time-interleaved ADCs, which have been obtained by averaging over one hundred realizations. Even for this rather small number of samples, the differences between the calculation and the simulation become less than  $\pm 0.5$  dB.

To see how the deviation from the averaged SINAD to the expected SINAD develops, we illustrate the difference between these two parameters in Fig. 13 for different numbers of realizations. For each plot in Fig. 13, we have carried out 1000 trials, where in each trial we have averaged over 10 [Fig. 13(a)], 100 [Fig. 13(b)], and 1000 [Fig. 13(c)] simulated realizations according to (48) before we have determined the difference. For each realization, we have taken 4096 sampling points through coherent sampling. It can be seen that the averaged values become more accurate with an increasing number of trials.

In Fig. 14, we compare the expected and the averaged SINAD for different numbers of samples and a fixed number of simulated realizations. In particular, we have carried out 1000 trials and have averaged for each trial over 100 simulated realizations. With each realization we have taken 1024 samples [Fig. 14(a)], 4096 samples [Fig. 14(b)], and 16 384 samples [Fig. 14(c)], through coherent sampling. We see that the number of samples does not significantly influence the difference between the expected and the averaged SINAD.

#### **IV. CONCLUSION**

We have analyzed combined channel mismatch errors including timing jitter and quantization noise in time-interleaved ADCs. We have derived formulas for calculating the explicit SINAD for given parameters and the expected SINAD for given parameter distributions. Equation (4) unifies and extends the equations found in [7] for calculating the explicit SINAD. Its rearranged version (13) clarifies how offset, gain, and timing mismatches interact. Moreover, for the first time, we have introduced the concept of a meta TIADC, which allows us to consider the mutual influence of timing jitter and combined mismatch errors for an arbitrary number of channels (20). We have shown a way to separate the timing jitter power and the mismatch error power with (21). Furthermore, we have performed worst case analyses for individual errors. We have derived the worst cases for offset (31), gain (24), and timing mismatches (29). With (39), we have presented a closed-form expression for the expected SINAD, which combines arbitrarily distributed offset, gain, and timing mismatch errors. This combined error description allows us to consider the mutual dependencies of these errors, and we can determine the one error source which has the main impact on the SINAD. Thus, the equations for the expected SINAD can support engineers in finding the right optimization priorities for their time-interleaved digitizing channels.

#### APPENDIX A

In Fig. 4, we have introduced a behavioral model of one channel ADC, which can be extended to a model of a time-interleaved ADC. The time-interleaved ADC model can be described by

$$y(t) = \sum_{l=0}^{M-1} \sum_{k=-\infty}^{\infty} \underbrace{(g_l x(t - \Delta t_l) + o_l)}_{\hat{x}_l(t)} \cdot \underbrace{\delta(t - kMT_s - lT_s)}_{s_l(t)}.$$

(49)

In order to obtain the output spectrum, we have to determine the Fourier transform of  $s_l(t)$  and  $\hat{x}_l(t)$ . The Fourier transform of  $s_l(t)$  is

$$S_l(j\Omega) = \frac{2\pi}{MT_s} \sum_{k=-\infty}^{\infty} \delta\left(\Omega - k\frac{\Omega_s}{M}\right) e^{-jkl\frac{2\pi}{M}}$$

(50)

and the Fourier transform of  $\hat{x}_l(t)$  for  $x(t) = A \cdot \sin(\Omega_0 t)$  gives

$$\hat{X}_l(j\Omega) = g_l X(j\Omega) e^{-j\Omega\Delta t_l} + o_l 2\pi\delta(\Omega)$$

(51)

where

$$X(j\Omega) = \frac{A\pi}{j} \left( \delta(\Omega - \Omega_0) - \delta(\Omega + \Omega_0) \right).$$

(52)

Since the Fourier transform is a linear operation we can convolve  $S_l(t)$  with  $\hat{X}_l(j\Omega)$  for each channel and sum up the results which gives

$$Y(j\Omega) = \sum_{l=0}^{M-1} \frac{1}{2\pi} \hat{X}_{l}(j\Omega) * S_{l}(j\Omega)$$

$$= \sum_{l=0}^{M-1} \sum_{k=-\infty}^{\infty} \frac{1}{MT_{s}}$$

$$\cdot \left[ g_{l} \frac{A\pi}{j} \left( \delta \left( \Omega - \Omega_{0} - k \frac{\Omega_{s}}{M} \right) \right) - \delta \left( \Omega + \Omega_{0} - k \frac{\Omega_{s}}{M} \right) \right] e^{-j\omega_{0}r_{l}}$$

$$+ o_{l} 2\pi \delta \left( \Omega - k \frac{\Omega_{s}}{M} \right) \right] e^{-jkl\frac{2\pi}{M}}.$$

(53)

This equation can be rewritten in a more readable way as

$$Y(j\Omega) = \frac{2\pi}{T_s} \sum_{k=-\infty}^{\infty} \left[ \alpha[k]\delta\left(\Omega - \Omega_0 - k\frac{\Omega_s}{M}\right) - \alpha^*[M-k]\delta\left(\Omega + \Omega_0 - k\frac{\Omega_s}{M}\right) + \beta[k]\delta\left(\Omega - k\frac{\Omega_s}{M}\right) \right]$$

(54)

where

$$\begin{aligned} \alpha[k] &= \frac{A}{j2M} \sum_{l=0}^{M-1} g_{le}^{-j\omega_0 r_l} e^{-jkl\frac{2\pi}{M}} \\ \beta[k] &= \frac{1}{M} \sum_{l=0}^{M-1} o_l e^{-jkl\frac{2\pi}{M}}. \end{aligned}$$

(55)

#### ACKNOWLEDGMENT

The author would like to thank G. Kubin for inspiring conversations.

#### REFERENCES

- K. Poulton, R. Neff, B. Setterberg, B. Wuppermann, T. Kopley, R. Jewett, J. Pernillo, C. Tan, and A. Montijo, "A 20 GS/s 8 b ADC with a 1 MB memory in 0.18 μm CMOS," in *Proc. IEEE Int. Solid-State Circuits Conf.*, vol. 1, Feb. 2003, pp. 318–496.

- [2] R. Khoini-Poorfard and D. A. Johns, "Time-interleaved oversampling convertors," *Electron. Lett.*, vol. 29, no. 19, pp. 1673–1674, Sept. 1993.

- [3] R. Khoini-Poorfard, L. B. Lim, and D. A. Johns, "Time-interleaved oversampling A/D converters: theory and practice," *IEEE Trans. Circuits Syst. II*, vol. 44, pp. 634–645, Aug. 1997.

- [4] W. C. Black, Jr. and D. A. Hodges, "Time-interleaved converter arrays," *IEEE J. Solid State Circuits*, vol. SSC-15, pp. 1024–1029, Dec. 1980.

- [5] W. C. Black, Jr., "High Speed CMOS A/D Conversion Techniques," Ph.D. Dissertation, Univ. California, Berkeley, Nov. 1980.

- [6] IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters, IEEE Stand. 1241-2000, Jun. 2001.

- [7] N. Kurosawa, H. Kobayashi, K. Maruyama, H. Sugawara, and K. Kobayashi, "Explicit analysis of channel mismatch effects in time-interleaved ADC systems," *IEEE Trans. Circuits Syst. 1*, vol. 48, pp. 261–271, Mar. 2001.

- [8] M. Gustavsson, J. J. Wikner, and N. Tan, CMOS Data Converters for Communications. Norwell, MA: Kluwer, 2000.

- [9] Y. C. Jenq, "Digital spectra of nonuniformly sampled signals: fundamentals and high-speed waveform digitizers," *IEEE Trans. Instrum. Meas.*, vol. 37, pp. 245–251, Jun. 1988.

- [10] A. Petraglia and S. Mitra, "Analysis of mismatch effects among A/D converters in a time-interleaved waveform digitizer," *IEEE Trans. Instrum. Meas.*, vol. 40, pp. 831–835, Oct. 1991.

- [11] Y. C. Jenq, "Digital spectra of nonuniformly sampled signals: theories and applications-measuring clock/aperture jitter of an A/D system," *IEEE Trans. Instrum. Meas.*, vol. 39, pp. 969–971, Dec. 1990.

- [12] M. Shinagawa, Y. Akazawa, and T. Wakimoto, "Jitter analysis of high-speed sampling systems," *IEEE J. Solid-State Circuits*, vol. 25, pp. 220–224, Feb. 1990.

- [13] T. M. Souders, D. R. Flach, C. Hagwood, and G. L. Yang, "The effects of timing jitter in sampling systems," *IEEE Trans. Instrum. Meas.*, vol. 39, pp. 80–85, Feb. 1990.

- [14] H. Kobayashi, M. Morimura, K. Kobayashi, and Y. Onaya, "Aperture jitter effects in wideband sampling systems," in *Proc. 16th IEEE Instrum. Meas. Technol. Conf., IMTC*, vol. 2, V. Piuri and M. Savino, Eds., May 1999, pp. 880–884.

- [15] D. Fu, K. C. Dyer, S. H. Lewis, and P. J. Hurst, "A digital background calibration technique for time-interleaved analog-to-digital converters," *IEEE J. Solid-State Circuits*, vol. 33, pp. 1904–1911, Dec. 1998.

- [16] T. Ndjountche and R. Unbehauen, "Adaptive calibration techniques for time-interleaved ADCs," *Electron. Lett.*, vol. 37, pp. 412–414, Mar. 2001.

- [17] J. E. Eklund and F. Gustafsson, "Digital offset compensation of timeinterleaved ADC using random chopper sampling," in *Proc. IEEE Int. Symp. Circuits Syst., ISCAS*, vol. 3, Geneva, Switzerland, May 2000, pp. 447–450.

- [18] S. Jamal, F. Daihong, N. Chang, P. Hurst, and S. Lewis, "A 10-b 120-Msample/s time-interleaved analog-to-digital converter with digital background calibration," *IEEE J. Solid-State Circuits*, vol. 37, pp. 1618–1627, Dec. 2002.

- [19] R. D. Batten, A. Eshraghi, and T. S. Fiez, "Calibration of parallel ΔΣ ADCs," *IEEE Trans. Circuits Syst. II.*, vol. 49, pp. 390–399, Jun. 2002.

- [20] J. Elbornsson and J. Eklund, "Blind estimation of timing errors in interleaved AD converters," in *Proc. IEEE Int. Conf. Acoustics, Speech, Signal Process.*, vol. 6, May 2001, pp. 3913–3916.

- [21] J. Elbornsson, F. Gustafsson, and J. Eklund, "Amplitude and gain error influence on time error estimation algorithm for time interleaved A/D converter system," in *Proc. IEEE Int. Conf. Acoustics, Speech, Signal Process.*, vol. 2, May 2002, pp. 1281–1284.

- [22] J. Elbornsson, K. Folkesson, and J. Eklund, "Measurement verification of estimation method for time errors in a time-interleaved A/D converter system," in *Proc. IEEE Int. Symp. Circuits Syst., ISCAS*, vol. 3, May 2002, pp. 129–132.

- [23] H. Jin, E. K. F. Lee, and M. Hassoun, "Time-interleaved A/D converter with channel randomization," in *Proc. IEEE Int. Symp. Circuits Syst.*, *ISCAS*, vol. 1, Jun. 1997, pp. 425–428.

- [24] M. Tamba, A. Shimizu, H. Munakata, and T. Komuro, "A method to improve SFDR with random interleaved sampling method," in *Proc. Int. Test Conf.*, Oct. 2001, pp. 512–520.

- [25] K. El-Sankary, A. Assi, and M. Sawan, "New sampling method to improve the SFDR of time-interleaved ADCs," in *Proc. Int. Symp. Circuits Syst., ISCAS*, vol. 1, May 2003, pp. 833–836.

- [26] Y. C. Jenq, "Digital spectra of nonuniformly sampled signals: a robust sampling time offset estimation algorithm for ultra high-speed waveform digitizers using interleaving," *IEEE Trans. Instrum. Meas.*, vol. 39, pp. 71–75, Feb. 1990.

- [27] —, "Perfect reconstruction of digital spectrum from nonuniformly sampled signals," *IEEE Trans. Instrum. Meas.*, vol. 46, pp. 649–652, Jun. 1997.

- [28] H. Jin and E. K. F. Lee, "A digital-background calibration technique for minimizing timing-error effects in time-interleaved ADCs," *IEEE Trans. Circuits Syst. II*, vol. 47, pp. 603–613, Jul. 2000.

- [29] H. Johansson and P. Löwenborg, "Reconstruction of nonuniformly sampled bandlimited signals by means of digital fractional delay filters," *IEEE Trans. Signal Process.*, vol. 50, pp. 2757–2767, Nov. 2002.

- [30] K. Poulton, K. L. Knudsen, J. Kerley, J. Kang, J. Tani, E. Cornish, and M. VanGrouw, "An 8-GSa/s 8-bit ADC system," in *Proc. Symp. VLSI Circuits, Dig. Technical Papers*, Jun. 1997, pp. 23–24.

- [31] R. Khoini-Poorfard and D. A. Johns, "Mismatch effects in time-interleaved oversampling converters," in *Proc. IEEE Int. Symp. Circuits Syst.*, *ISCAS*, vol. 5, May 1994, pp. 429–432.

- [32] Y. Jenq, "Digital-to-analog (D/A) converters with nonuniformly sampled signals," *IEEE Trans. Instrum. Meas.*, vol. 45, pp. 56–59, Feb. 1996.

- [33] U. Seng-Pan, R. Martins, and J. Franca, "Design and analysis of low timing-skew clock generation for time-interleaved sampled-data systems," in *Proc. IEEE Int. Symp. Circuits Syst., ISCAS*, vol. 4, May 2002, pp. 441–444.

- [34] S.-W. Sin, S.-P. U, R. P. Martins, and J. E. Franca, "Timing-mismatch analysis in high-speed analog front-end with nonuniformly holding output," in *Proc Int. Symp. Circuits Syst., ISCAS*, vol. 1, May 2003, pp. 129–132.

- [35] G. Leger, E. Peralias, and A. Rueda, "SNR probability in time-interleaved ADCs with random channel mismatches," in *Proc. IEEE Int. Symp. Circuits Syst., ISCAS*, vol. 2, May 2002, pp. 380–383.

- [36] B. Yu and W. C. Black, Jr., "Error analysis for time-interleaved analog channels," in *Proc. IEEE Int. Symp. Circuits Syst.*, *ISCAS*, vol. 1, May 2001, pp. 468–471.

- [37] J. B. Simões, J. Landeck, and C. M. B. A. Correia, "Nonlinearity of a data-acquisition system with interleaving/multiplexing," *IEEE Trans. Instrum. Meas.*, vol. 46, pp. 1274–1279, Dec. 1997.

- [38] N. Kurosawa, H. Kobayashi, and K. Kobayashi, "Channel linearity mismatch effects in time-interleaved ADC systems," in *Proc. IEEE Int. Symp. Circuits Syst., ISCAS*, vol. 1, May 2001, pp. 420–423.

- [39] C. Vogel and G. Kubin, "Analysis and compensation of nonlinearity mismatches in time-interleaved ADC arrays," in *Proc IEEE Int. Symp. Circuits Syst., ISCAS*, vol. 1, May 2004, pp. 593–596.

- [40] E. Kreyszig, Advanced Engineering Mathematics, Eighth ed. New York: Wiley, 1998.

- [41] A. Papoulis and U. Pillai, Probability, Random Variables and Stochastic Processes, Fourth ed, ser. McGraw-Hill series in electrical engineering: Communications and signal processing. New York: McGraw-Hill, 2002.

- [42] S. M. Kay, Fundamentals of Statistical Signal Processing: Estimation Theory. Englewood Cliffs, NJ: Prentice-Hall, 1993.

- [43] C. Vogel and H. Koeppl, "Behavioral modeling of time-interleaved ADCs using MATLAB," in *Proc. Austrochip*, Oct. 2003, pp. 45–48.

**Christian Vogel** (S'02) was born in Graz, Austria, in 1975. He received the Dipl.-Ing. degree in telematics from Graz University of Technology in 2001. He has worked in the field of information security and is currently pursuing the Ph.D. degree in electrical engineering at Graz University.

His current research interests include digital compensation methods for correcting analog signal processing errors in fast ADCs.