| THE | MICROARCHITECTURE | OF FPCA-RASE | ED SOFT | Processors |

|-----|-------------------|--------------|---------|------------|

by

Peter Yiannacouras

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto

Copyright © 2005 by Peter Yiannacouras

#### Abstract

The Microarchitecture of FPGA-Based Soft Processors

#### Peter Yiannacouras

Master of Applied Science

Graduate Department of Electrical and Computer Engineering

University of Toronto

2005

As more embedded systems are built using FPGA platforms, there is an increasing need to support processors in FPGAs. One option is the *soft processor*, a processor implemented in the reconfigurable logic of the FPGA. Commercial soft processors have been widely deployed, and hence we are motivated to understand their microarchitecture. We must re-evaluate microarchitecture in the soft processor context because an FPGA platform is significantly different than an ASIC platform. This dissertation presents an infrastructure for rapidly generating RTL models of soft processors, as well as a methodology for measuring their area, performance, and power. Using the automatically-generated soft processors we explore many interesting microarchitectural axes in the trade-off space. We also compare our designs to Altera's Nios II commercial soft processors and find that our automatically generated designs span the design space while remaining very competitive.

## Contents

| Li | st of | Tables                                                  | vii          |

|----|-------|---------------------------------------------------------|--------------|

| Li | st of | Figures                                                 | ⁄ <b>iii</b> |

| 1  | Intr  | roduction                                               | 1            |

|    | 1.1   | Research Goals                                          | 3            |

|    | 1.2   | Organization                                            | 4            |

| 2  | Bac   | kground                                                 | 5            |

|    | 2.1   | Basic Processor Architecture                            | 5            |

|    | 2.2   | The MIPS-I ISA                                          | 6            |

|    | 2.3   | Application-Specific Instruction-set Processors (ASIPs) | 9            |

|    | 2.4   | FPGA Architecture                                       | 10           |

|    | 2.5   | Industrial Soft Processors                              | 12           |

|    | 2.6   | Architectural Exploration Environments                  | 14           |

|    |       | 2.6.1 Parameterized Cores                               | 15           |

|    |       | 2.6.2 ADL-based Architecture Exploration Environments   | 16           |

|    | 2.7   | Closely Related Work                                    | 17           |

|    | 2.8   | Summary                                                 | 20           |

| 3  | The   | e SPREE System                                          | <b>21</b>    |

|    | 3.1   | Input: The Architecture Description                     | 23           |

|    |       | 3.1.1 Describing the Instruction Set Architecture       | 23           |

|   |     | 3.1.2   | Describing the Datapath                     | 26 |

|---|-----|---------|---------------------------------------------|----|

|   | 3.2 | The S   | PREE Component Library                      | 27 |

|   |     | 3.2.1   | Selecting and Interchanging Components      | 27 |

|   |     | 3.2.2   | Creating and Describing Datapath Components | 28 |

|   | 3.3 | Gener   | ating a Soft Processor                      | 31 |

|   |     | 3.3.1   | Datapath Verification                       | 31 |

|   |     | 3.3.2   | Datapath Instantiation                      | 33 |

|   |     | 3.3.3   | Control Generation                          | 34 |

|   | 3.4 | Practi  | cal Issues in Component Abstraction         | 39 |

|   |     | 3.4.1   | Combinational Loops                         | 40 |

|   |     | 3.4.2   | False Paths                                 | 40 |

|   |     | 3.4.3   | Multi-cycle Paths                           | 41 |

|   | 3.5 | Summ    | ary                                         | 42 |

| 4 | Exp | erime   | ntal Framework                              | 43 |

|   | 4.1 | Proces  | ssor Verification                           | 43 |

|   | 4.2 | FPGA    | Device and CAD Tools                        | 44 |

|   |     | 4.2.1   | Determination of Confidence Across Seeds    | 45 |

|   | 4.3 | Metric  | es for Measuring Soft Processors            | 47 |

|   | 4.4 | Comp    | aring with Altera Nios II Variations        | 48 |

|   | 4.5 | Bench   | mark Applications                           | 49 |

|   |     | 4.5.1   | MiBench Benchmarks                          | 50 |

|   |     | 4.5.2   | XiRisc Benchmarks                           | 51 |

|   |     | 4.5.3   | RATES Benchmarks                            | 52 |

|   |     | 4.5.4   | Freescale Benchmark                         | 52 |

|   | 4.6 | ISA R   | eduction                                    | 53 |

|   | 4.7 | Summ    | ary                                         | 54 |

| 5 | Exp | oloring | Soft Processor Microarchitecture            | 55 |

|   |     |         |                                             |    |

|              | 5.2  | The Impact of Hardware vs Software Multiplication            | 8 |

|--------------|------|--------------------------------------------------------------|---|

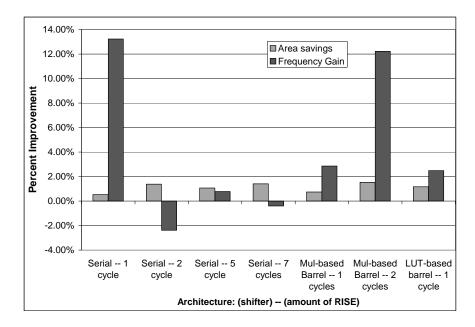

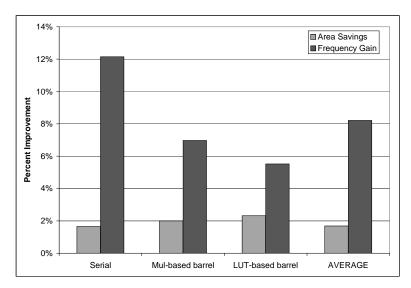

|              | 5.3  | The Impact of Shifter Implementation                         | 2 |

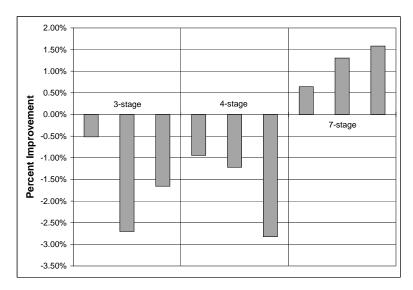

|              | 5.4  | The Impact of Pipelining                                     | 5 |

|              |      | 5.4.1 Branch Delay Slots in the 7-stage Pipeline             | 2 |

|              |      | 5.4.2 The Impact of Inter-Stage Forwarding Lines             | 5 |

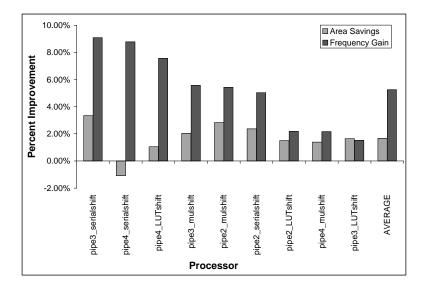

|              | 5.5  | Register Insertion for Clock Speed Enhancement               | 7 |

|              | 5.6  | Architectures that Minimize Area                             | 8 |

|              |      | 5.6.1 Fully Serialized ALU                                   | 9 |

|              |      | 5.6.2 Shared Shifting and Memory Alignment                   | 1 |

|              | 5.7  | Instruction Set Subsetting                                   | 1 |

|              | 5.8  | Optimizations                                                | 4 |

|              |      | 5.8.1 Dual Word-Size Data Memory                             | 5 |

|              |      | 5.8.2 Arithmetic Unit Result Splitting                       | 6 |

|              |      | 5.8.3 Previous Stage Decode                                  | 7 |

|              |      | 5.8.4 Instruction-Independent Enable Signals                 | 9 |

|              | 5.9  | Application Specificity of Architectural Conclusions         | 0 |

|              | 5.10 | CAD Setting Independence                                     | 3 |

|              | 5.11 | Device Independence - Stratix vs Stratix II                  | 5 |

| 6            | Con  | clusions 9                                                   | 7 |

|              | 6.1  | Contributions                                                | 8 |

|              | 6.2  | Future Work                                                  |   |

|              |      |                                                              |   |

| $\mathbf{A}$ | SPF  | TEE System Details 10                                        | 0 |

|              | A.1  | ISA Descriptions                                             | 0 |

|              | A.2  | Datapath Descriptions                                        | 7 |

|              |      | A.2.1 2-stage Pipeline with Serial Shifter                   | 8 |

|              |      | A.2.2 3-stage Pipeline with Multiplier-based Shifter         | 9 |

|              |      | A.2.3 5-stage Pipeline with LUT-based Shifter and Forwarding | 2 |

|              | Δ 3  | The Library Entry                                            | 6 |

6

| $\mathbf{B}$ | Exp  | loratio | on Result Details                                            | 131   |

|--------------|------|---------|--------------------------------------------------------------|-------|

|              | B.1  | CAD     | Settings                                                     | 131   |

|              | B.2  | Data f  | rom exploration                                              | 133   |

|              |      | B.2.1   | Shifter Implementation, Multiply Support, and Pipeline Depth | 133   |

|              |      | B.2.2   | Forwarding                                                   | . 137 |

|              |      | B.2.3   | Minimizing Area Processors                                   | 138   |

|              |      | B.2.4   | Subsetted Processors                                         | 139   |

|              |      | B.2.5   | Nios II                                                      | . 140 |

| D:           | L 12 | 1       |                                                              | 1 11  |

| Dl           | опод | raphy   |                                                              | 141   |

## List of Tables

| 2.1 | MIPS-I instructions supported                                                          |

|-----|----------------------------------------------------------------------------------------|

| 2.2 | Comparison of Nios II Variants                                                         |

| 2.3 | Comparison of ADL-based Architecture Exploration Environments                          |

| 3.1 | GENOPs used in SPREE                                                                   |

| 3.2 | Components in the SPREE Component Library                                              |

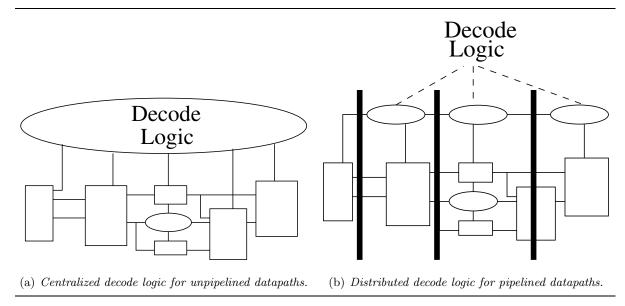

| 3.3 | Control generation for pipelined and unpipelined datapths contrasted 34                |

| 4.1 | Relative Areas of Stratix Blocks to LEs                                                |

| 4.2 | Benchmark applications evaluated                                                       |

| B.1 | Data for hardware multiply support over different shifters and pipelines 133           |

| B.2 | Data for hardware multiply support over different shifters and pipelines (cont'd). 134 |

| В.3 | Data for software multiply support over different shifters and pipelines 135           |

| B.4 | Data for software multiply support over different shifters and pipelines (cont'd) 136  |

| B.5 | Measurements of pipelines with forwarding                                              |

| B.6 | Measurements of processors which minimize area                                         |

| B.7 | ISA subsetting data on processors with full hardware multiply support 139              |

| B.8 | Area and performance of Nios II                                                        |

# List of Figures

| 2.1  | The MIPS instruction format [39]                                                            | 7  |

|------|---------------------------------------------------------------------------------------------|----|

| 2.2  | The Stratix Architecture                                                                    | 11 |

| 2.3  | Nios II vs Nios Design Space                                                                | 12 |

| 2.4  | Nios II ISA Instruction Word Format                                                         | 14 |

| 3.1  | Overview of the SPREE system                                                                | 22 |

| 3.2  | An overview of the SPREE RTL generator                                                      | 23 |

| 3.3  | The MIPS SUB instruction shown as a dependence graph of GENOPs                              | 25 |

| 3.4  | The MIPS SUB instruction described using C++ code                                           | 26 |

| 3.5  | A datapath description shown as an interconnection of components                            | 26 |

| 3.6  | The Component Interface                                                                     | 29 |

| 3.7  | Library entry format                                                                        | 30 |

| 3.8  | Sample component description for a simplified ALU                                           | 30 |

| 3.9  | Different decode logic implementations used. $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 36 |

| 3.10 | The pipeline stage model used by SPREE                                                      | 38 |

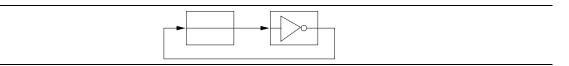

| 3.11 | A combinational loop formed between two components                                          | 40 |

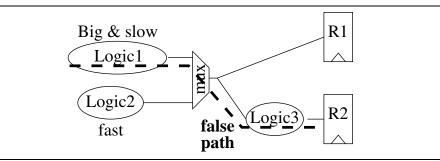

| 3.12 | A false path                                                                                | 40 |

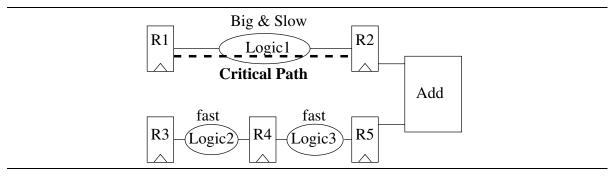

| 3.13 | A multi-cycle path                                                                          | 41 |

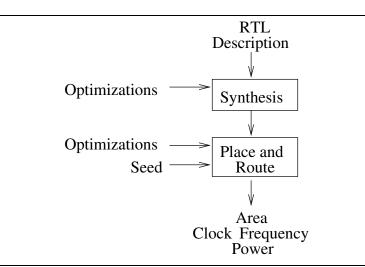

| 4.1  | CAD flow overview                                                                           | 44 |

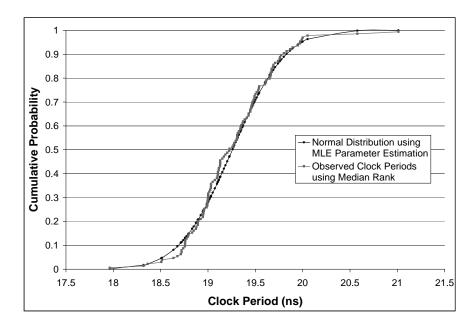

| 4.2  | Verification of Normal Distribution of Clock Frequency Measurements $\ \ldots \ \ldots$     | 46 |

| 4.3  | Accuracy versus number of seeds for three processors                                        | 47 |

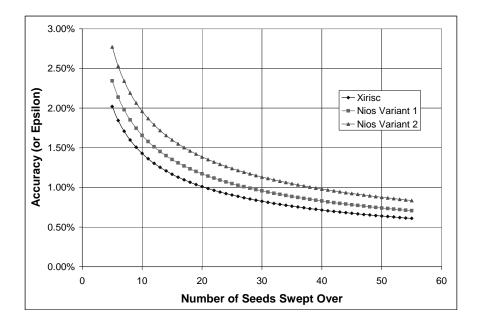

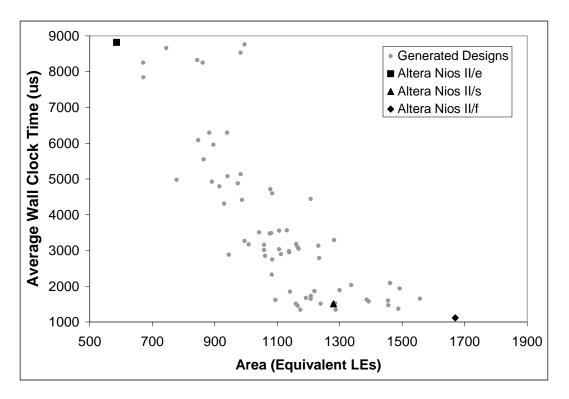

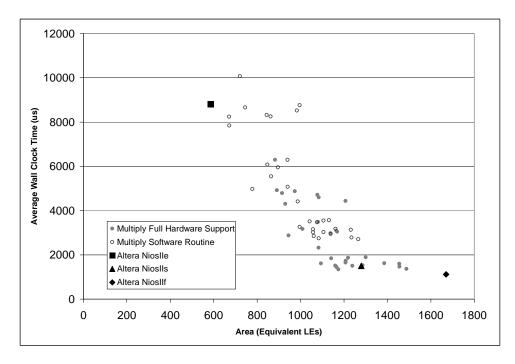

| 5.1  | Comparison of our generated designs vs the three Altera Nios II variations         | 56 |

|------|------------------------------------------------------------------------------------|----|

| 5.2  | Wall-clock-time vs area of processors with hardware multiplication support         | 60 |

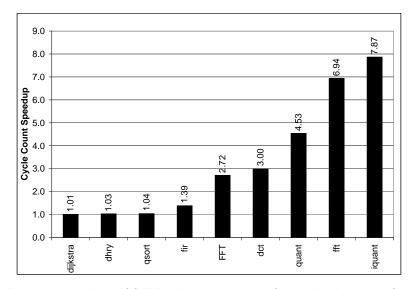

| 5.3  | Cycle count speedup of full hardware support for multiplication                    | 60 |

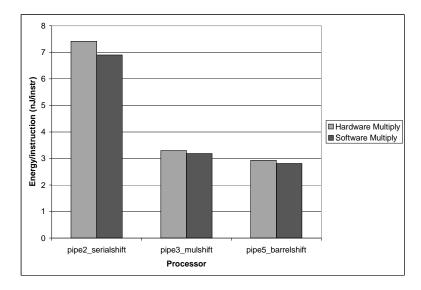

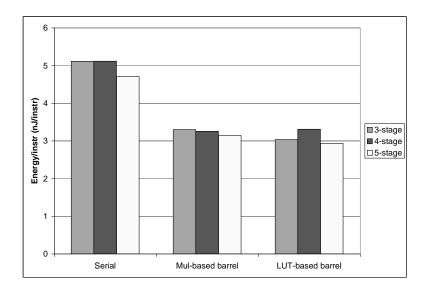

| 5.4  | Energy/instruction for hardware vs software multiplication support                 | 61 |

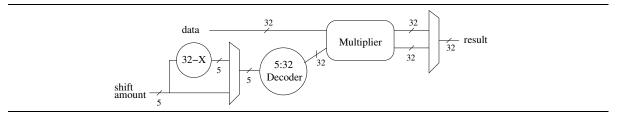

| 5.5  | A barrel shifter implemented using a multiplier                                    | 62 |

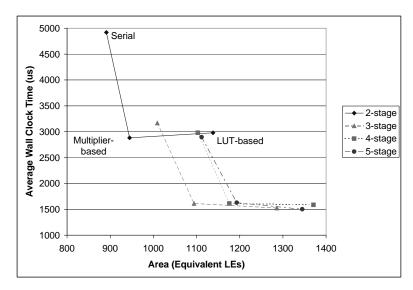

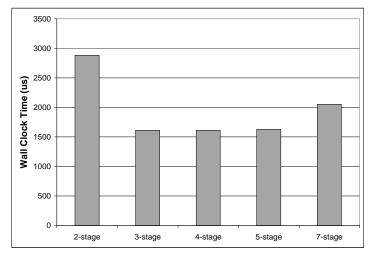

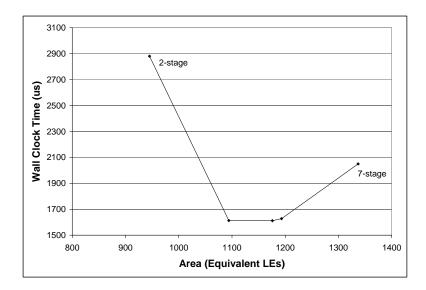

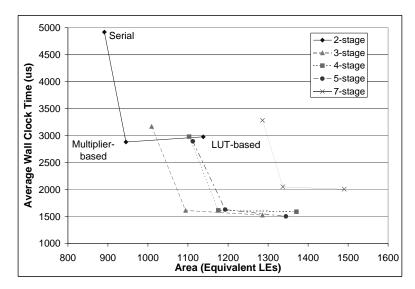

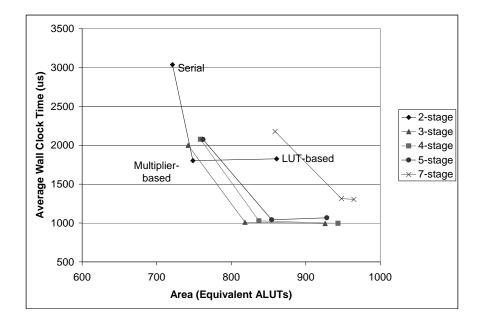

| 5.6  | Average wall-clock-time vs area for different pipeline depths                      | 63 |

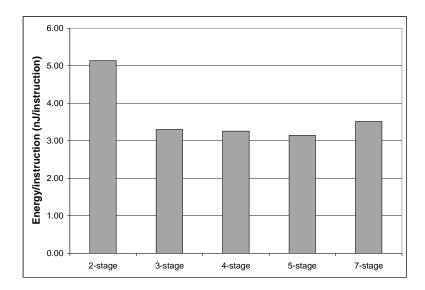

| 5.7  | Energy per instruction across different pipelines                                  | 64 |

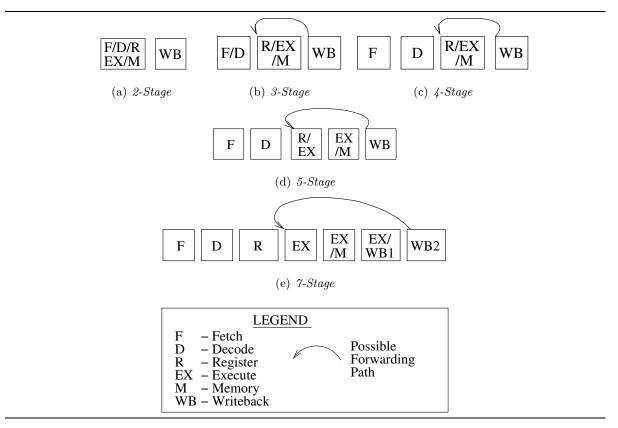

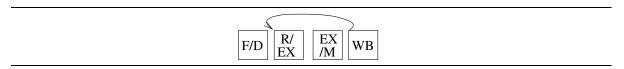

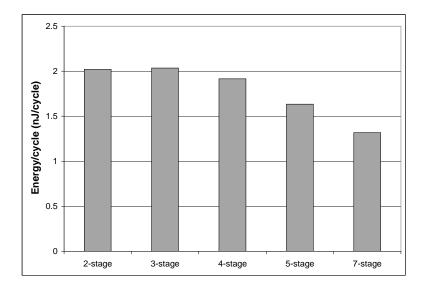

| 5.8  | Processor pipeline organizations studied                                           | 65 |

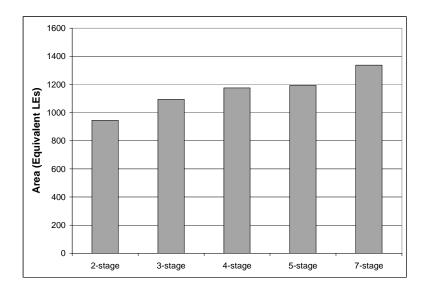

| 5.9  | Area across different pipeline depths                                              | 67 |

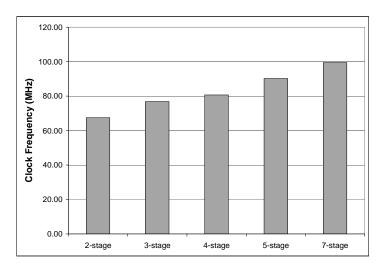

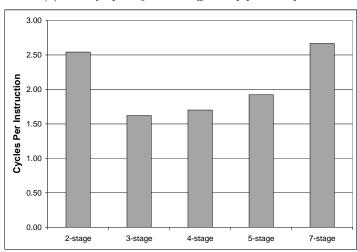

| 5.10 | Performance across different pipeline depths                                       | 68 |

| 5.11 | Wall-clock-time versus area across different pipeline depths                       | 70 |

| 5.12 | Alternative 4-stage pipeline                                                       | 70 |

| 5.13 | Energy per instruction for the different pipeline depths                           | 71 |

| 5.14 | Energy per cycle for the different pipeline depths                                 | 72 |

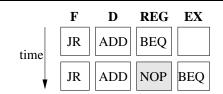

| 5.15 | Branch delay slot instruction separation                                           | 73 |

| 5.16 | Average wall-clock-time versus area space for all pipelines                        | 73 |

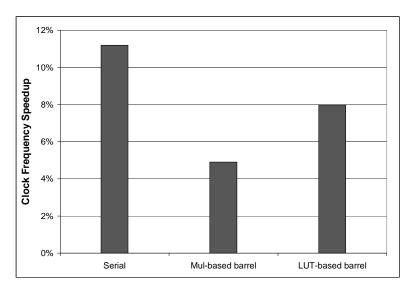

| 5.17 | Clock frequency speedup after ignoring multiple delay slots                        | 75 |

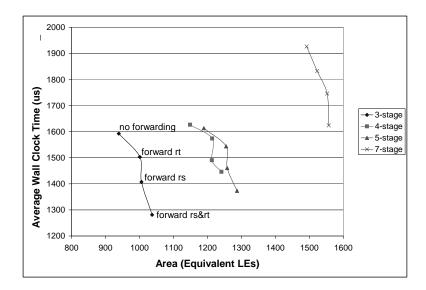

| 5.18 | Average wall-clock-time vs area for different forwarding lines                     | 76 |

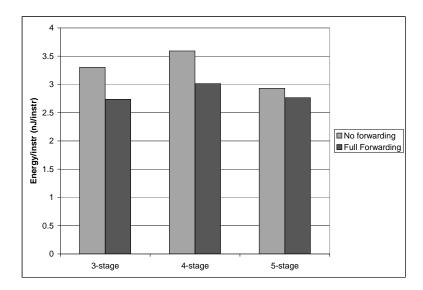

| 5.19 | Energy per instruction for three pipelines with forwarding                         | 77 |

| 5.20 | The impact of RISE on a processor across the benchmark set                         | 78 |

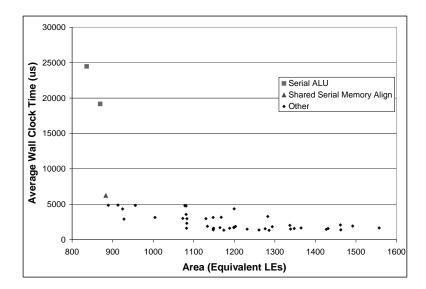

| 5.21 | Average wall-clock-time vs area space including outliers                           | 80 |

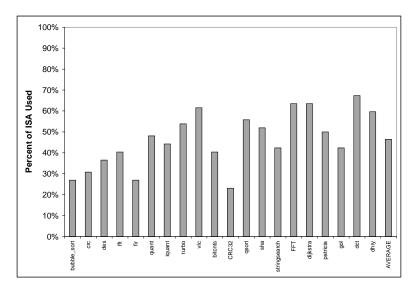

| 5.22 | ISA usage across benchmark set                                                     | 82 |

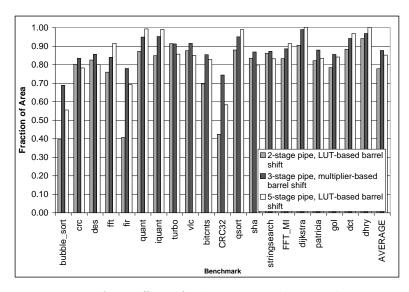

| 5.23 | Area effect of subsetting on three architectures                                   | 82 |

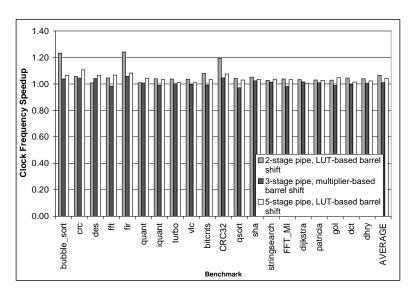

| 5.24 | Clock Speed effect of subsetting on three architectures                            | 83 |

| 5.25 | Impact of 8-bit store port on area and performance of different 2-stage pipelines. | 85 |

| 5.26 | Impact of result splitting on area and performance                                 | 86 |

| 5.27 | Impact of previous stage decode on performance                                     | 87 |

| 5.28 | Impact of instruction-independent enable signals on area and performance           | 89 |

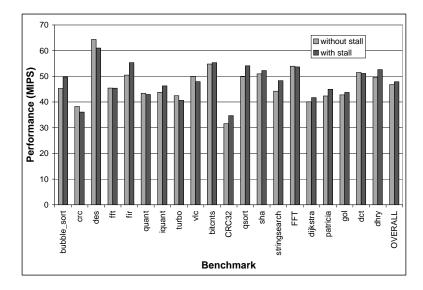

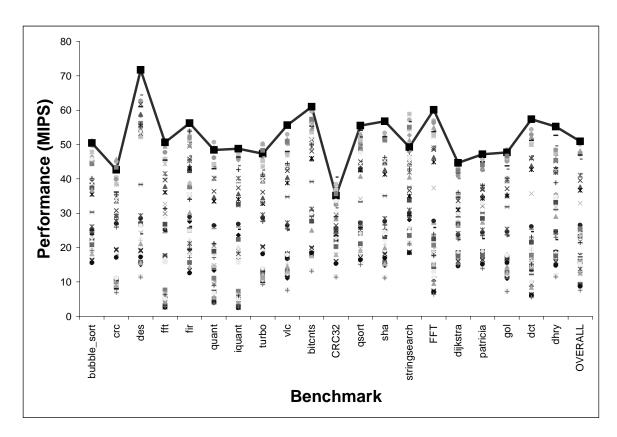

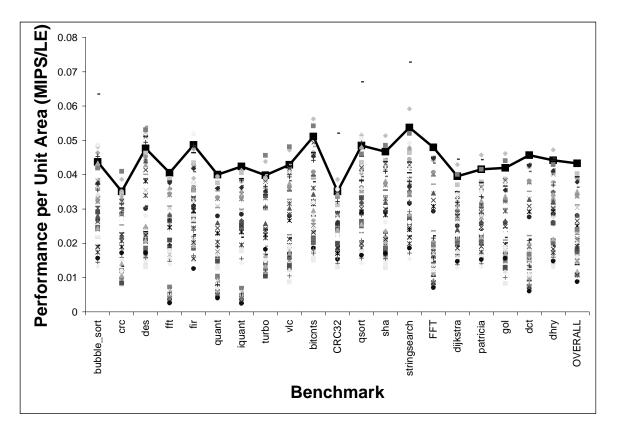

| 5.29 | Performance of all processors on each benchmark                                    | 90 |

| 5.30 | Performance per unit area of all processors on each benchmark               | 91 |

|------|-----------------------------------------------------------------------------|----|

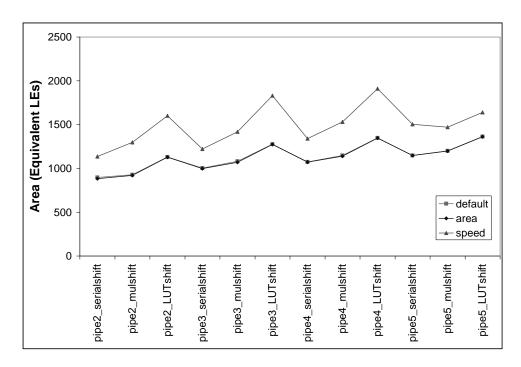

| 5.31 | Effect of three different optimization focusses on area measurement         | 93 |

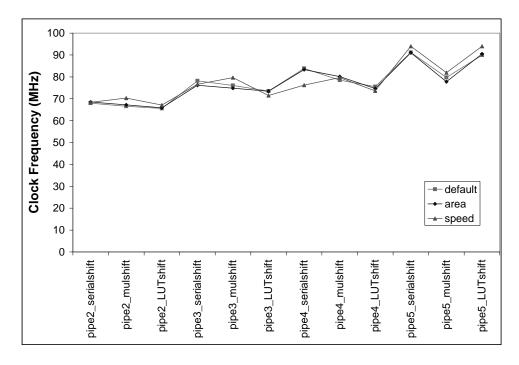

| 5.32 | Effect of three different optimization focusses on clock frequency          | 94 |

| 5.33 | Average wall-clock-time vs area for different pipeline depths on Stratix II | 95 |

|      |                                                                             |    |

| A.1  | Library entry format                                                        | 16 |

| A.2  | Sample component description for a simplified ALU                           | 16 |

## Chapter 1

### Introduction

With the rapidly rising cost and time-to-market of designing state-of-the-art ASICs, an increasing number of embedded systems are being built using Field-Programmable Gate Array (FPGA) platforms. Such systems often contain one or more embedded microprocessors which must also migrate to the FPGA platform to avoid the increased cost and latency of a multi-chip design. FPGA vendors have addressed this issue with two solutions: (i) incorporating one or more *hard processors* directly on the FPGA chip and surrounding it with FPGA fabric (eg., Xilinx's Virtex II Pro [61] and Altera's Excalibur [1]), and (ii) implementing *soft processors* which use the FPGA fabric itself (eg., Xilinx's MicroBlaze [60] and Altera's Nios [2]).

While the internal hard processors can be fast, small, and relatively cheap, they have several drawbacks. First, the number of hard processors included in the FPGA device may not match the number required by the application, leading to either too few or wasted hard processors. Second, the performance requirements of each processor in the application may not match those provided by the available FPGA-based hard processors. Third, due to the fixed location of each FPGA-based hard processor, it can be difficult to route between the processors and the custom logic. Finally, inclusion of one or more hard processors specializes the FPGA chip, impacting the resulting yield and narrowing the customer base for that product.

While a soft processor cannot easily match the performance/area/power consumption of a hard processor, soft processors do have several compelling advantages. Using a generic FPGA chip, a designer can implement the exact number of soft processors required by the application, and the FPGA CAD (computer-aided design) tools will automatically place them within the design to ease routing. Since it is implemented in configurable logic, a soft processor can be tuned by varying its implementation and complexity to match the exact requirements of an application. Finally, since no special hardware is required in the FPGA to support such processors, the FPGA remains a generic part with a large customer base. While these benefits have resulted in wide deployment of soft processors in FPGA-based embedded systems [41], the architecture of soft processors has yet to be studied in depth.

The microarchitecture of hard processors has been studied by many researchers and vendors for decades. However, the trade-offs for FPGA-based soft processors are significantly different than those implemented in full or semi-custom VLSI design flows [37, 38]: for example, on-chip memories are often faster than the clock speed of a soft processor's pipeline, and hard multipliers are area-efficient and fast compared to other functions implemented in configurable logic [5]. Because of this, the body of knowledge created by the decades of research into hard processors is not immediately transferable to soft processors, motivating us to revisit the microarchitectural design space in an FPGA context.

Furthermore, processor microarchitecture has traditionally been studied using high-level functional simulators that estimate area and performance due to the difficulty in varying designs at the logic layout level. In contrast, FPGA CAD tools allow us to quickly and accurately measure the exact speed, area, and power of the final placed and routed design for any soft processor. Hence we have the compelling opportunity to develop a complete and accurate understanding of soft processor microarchitecture.

With this knowledge, future tools could automatically navigate the soft processor design space and make intelligent application-specific architectural trade-offs based on a full understanding of soft processor microarchitecture. One can envision a tool which can take an application and a set of design constraints as inputs, and automatically generate a customized soft processor which will satisfy those design constraints. The application would also be compiled specifically for execution on this customized soft processor. A crude version of this software system may be a design space iteration over all architectures, however, with the knowledge generated by this research, the tool can make some a priori decisions and at least reduce the design space.

#### 1.1 Research Goals

The focus of this research is to develop an understanding of the soft processor microarchitectural design space. To this end, we set the following four goals:

- 1. To build a system for automatically-generating soft processors based on a simple but powerful input description.

- 2. To develop a methodology for comparing soft processor architectures.

- 3. To populate and analyze the soft processor design space and draw architectural conclusions.

- 4. To validate our results through comparison to an industrial soft processor family.

To satisfy the first goal, a system called Soft Processor Rapid Exploration Environment (SPREE) has been developed, which automatically generates an RTL (Register Transfer Level) description of a soft processor from text-based ISA (Instruction Set Architecture) and datapath descriptions. SPREE allows one to build a datapath at a high level, abstracting away from details such as component interfaces, and functional unit latencies. The user can assemble a datapath which can functionally support the given ISA, and SPREE will then automatically convert the description to an RTL form and generate the necessary control logic. FPGA CAD tools are then used to accurately measure area, clock frequency, and power of the resulting RTL designs, and RTL simulation

is used to verify correctness and measure the cycle counts of several embedded benchmark applications on these designs. The second research goal addresses issues such as accounting for area in FPGAs, choosing benchmarks, and selecting appropriate metrics for measurement. The third goal requires extensive use of the SPREE system to generate interesting processor designs and evaluate different microarchitectural axes. The fourth goal is required to achieve confidence in our architectural conclusions. By comparing the processors generated by SPREE to a family of industrial soft processors, the Altera Nios II variations, one can evaluate whether the conclusions drawn by SPREE suffer from prohibitive overheads. Through these measurements on several automatically generated processor architectures, we expect to gain a confident, complete, and accurate understanding of the soft processor architectural design space.

#### 1.2 Organization

This dissertation is organized as follows. Chapter 2 gives a background in processor microarchitecture, and FPGA architecture, as well as summarizes the relevant research fields and research projects. Chapter 3 describes our SPREE system, including its interface and various problems left for manual intervention. Chapter 4 describes the experimental framework built around SPREE in order to facilitate our architectural exploration. Chapter 5 compares our automatically generated designs against an industrial soft processor for validation and then proceeds with an architectural exploration of various architectural parameters. Chapter 6 concludes by summarizing the dissertation, naming its contributions, and listing future extensions of this work.

## Chapter 2

## Background

In this chapter we discuss relevant background required to understand this work, and also summarize the research field of processor architectural exploration. The organization is as follows: Section 2.1 discusses computer architecture fundamentals and terminology; Section 2.2 describes the MIPS-I ISA (Instruction Set Architecture) which is our selected base ISA for our exploration; Section 2.3 discusses the field of Application Specific Instruction-set Processors; Section 2.4 gives an overview of FPGA architecture and the specific device employed in this work; Section 2.5 discusses soft processors and their presence in industry; Section 2.6 summarizes existing architectural exploration approaches; finally Section 2.7 describes research which is more directly related to our work.

#### 2.1 Basic Processor Architecture

The field of processor architecture has been explored extensively for more than 40 years. Microprocessors have evolved from simple three to five stage pipelined cores to out-of-order speculative machines with intricate caching, and branch prediction schemes. In our work we do not consider such advanced topics in computer architecture, since the soft processor market currently targets only embedded applications which have much simpler architectures. Thus, we limit our exploration space to in-order issue pipelines with no caching and no branch prediction.

We now summarize basic processor architecture terminology, assuming the reader is largely familiar with basic computer architecture principles. If not, the necessary information on pipelines and computer architecture is available in Hennessy and Patterson [20]. A processor pipeline divides the execution of an instruction into steps and executes the different steps of several instructions simultaneously. Pipelining allows one to increase the clock frequency of the processor by shrinking the size of the steps, but pipelining also gives rise to data hazards. Data hazards occur when an instruction performs an operand fetch step before a preceding instruction has completed its operand write step to the same operand. The effect of this, if not guarded, would result in the read step reading an out-of-date operand value. This is referred to as a read-after-write (RAW) hazard, and the number of simultaneous steps that can potentially cause a hazard is the hazard window. To preserve program correctness, the architecture can delay the read step until the write step has completed (known as interlocking or stalling), or send the value to be written to the read step (known as forwarding). Both methods require hazard detection logic to signal the delay or the forwarding.

Pipelining also causes **branch penalties**, the penalty associated with incorrectly executing steps of instructions that should never have been fetched (which were fetched because the step which decides whether a branch is taken occurs later in the pipeline). A **branch delay slot instruction** refers to the instruction in the pipeline directly after a branch. The idea is that the branch delay slot instruction can be executed regardless of whether the branch is taken, allowing the processor to perform useful work as it computes the result of the branch condition.

#### 2.2 The MIPS-I ISA

The MIPS (Microprocessors without Interlocking Pipe Stages) ISA was developed by John Hennessy et al. in 1981[24]. The goal of MIPS was to exploit the fact that large portions of the chip were being unused as traditional architectures with shallow pipelines

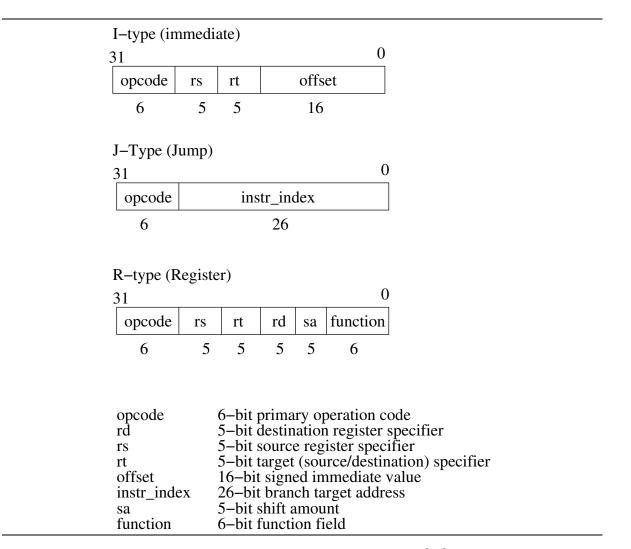

Figure 2.1: The MIPS instruction format [39]

stalled to execute complex instructions. The premise was that the stalling was hindering the pipeline from achieving faster performance. The MIPS ISA was designed ensuring all instructions can be executed in a single cycle thereby eliminating the stalls; inherently long instructions such as multiply and divide are handled specially in hardware as detailed below. Since then MIPS has become a popular instruction set widely supported by compilers and instruction simulators.

MIPS is a load-store RISC (Reduced Instruction Set Computer) instruction set with three operands, and its instruction format is shown in Figure 2.1. The operands can specify two locations in the register file for reading (rs and rt) and one for writing (usually rd, but can also be rt). There have been many revisions of MIPS since its inception named MIPS-I, MIPS-II, MIPS-III, MIPS-IV, MIPS-32/64—the newer revisions were augmented with more floating point support, trapping, and virtual memory instructions. The following properties of the MIPS ISA should be understood before proceeding.

Branch Delay Slots: MIPS has one branch delay slot instruction accompanying every branch or call instruction whether the branch is conditional or unconditional. Branch delay slots help decrease the branch penalty (the number of instructions incorrectly fetched before the processor could determine whether the branch was taken or not). This is done by imposing the rule that the instruction after the branch is always executed whether the branch is taken or not.

HI/LO registers: The MIPS multiply instruction produces a 64-bit result, which is stored in two special 32-bit registers called HI and LO storing the upper and lower halves of the 64-bit result respectively. These special registers are accessed via special instructions which can copy the values to the register file.

Nop instruction: MIPS does not contain an explicit null operation, or nop instruction. However, the instruction whose opcode is zero corresponds to a shift-left-by-zero instruction, which is effectively a null operation as it does not modify the processor state.

For this research MIPS-I was selected as our base ISA for two reasons. First, its wide support in instruction simulators and compilers avoids the time investment in having

| Type   | Instruction                                                                                                                                                  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Branch | j, jal, jr, jalr, beq, bne, blez, bgtz, bltz, bgez                                                                                                           |  |

| Memory | lb, lh, lw, lbu, lhu, sb, sh, sw                                                                                                                             |  |

| ALU    | sll, srl, sra, sllv, srlv, srav, mfhi, mflo, mult, multu, addi, addiu, slti, sltiu, andi, ori, xori, lui, add, addu, sub, subu, and, or, xor, nor, slt, sltu |  |

Table 2.1: MIPS-I instructions supported

to create one. Second, its simplicity makes it an attractive starting point. We require a simple but robust ISA with clean instruction decoding to facilitate simpler control generation. We believe MIPS in general meets this requirement, and is much better than alternatives such as x86. MIPS-I is selected over the recent MIPS revisions since this work does not explore floating-point, virtual memory, nor exceptions.

For further simplicity, a reduced version of the MIPS-I ISA is used in our exploration. Table 2.1 lists the instruction supported in our exploration. We have removed all floating point instructions, unaligned loads/stores (lwl, lwr, swl, swr), writes to the HI/LO registers (mtlo, mthi), division (div, divu), and complex branches (bgezal, bltzal)—the motivation for removing these instructions is discussed in Section 4.6.

### 2.3 Application-Specific Instruction-set Processors (ASIPs)

Although this work is generalized across a benchmark set, the future of this research is to enable intelligent application-specific architectural decisions. The majority of architectural research has been targetted toward general purpose computing—processors designed to run several different applications. In another branch of computing, the embedded processor domain, processors are usually designed to run only one application. This property allows one to consider specializing the architecture to run that specific application well (at the expense of running other applications poorly), making it an Application Specific Instruction-set Processor (ASIP). The large costs of designing and manufacturing an ASIP in the traditional ASIC flow may make this option unattractive

for designers whose application may change. With FPGAs, it is simple to replace one processor with another, as the device need only be reprogrammed. Thus, FPGAs provide the compelling advantage of allowing soft processors to become more aggressively customized to its application.

In recent years, there has been a growing interest in the architecture of ASIPs [28] and techniques for automatic customization such as compiler generation, and custom instructions [13]. Most notably, Tensilica [49] has been providing their Xtensa configurable processor commercially since 1999. The Xtensa processor can be automatically tuned by adding functional units, increasing parallelism using VLIW, and adding custom instructions (including vector operations and fused instructions). Much of this can be done automatically using AutoTIE [16], an infrastructure that automatically detects data structures in an application and creates register files for holding the data, and functional units for operating on them. These and many other techniques exist for creating application-specific processors. With the knowledge generated in this dissertation, one can more accurately apply such techniques based on a complete and accurate understanding of the design space.

#### 2.4 FPGA Architecture

The architecture of FPGAs has become increasingly complex and no longer consists of a simple array of lookup tables (LUTs) and flip flops connected by programmable routing. FPGAs now include on-chip RAM blocks, and multipliers. FPGA devices and their architectures vary across device families and across vendors. In this work we focus on Altera's Stratix [5, 32] family and hence we discuss its architecture in more detail.

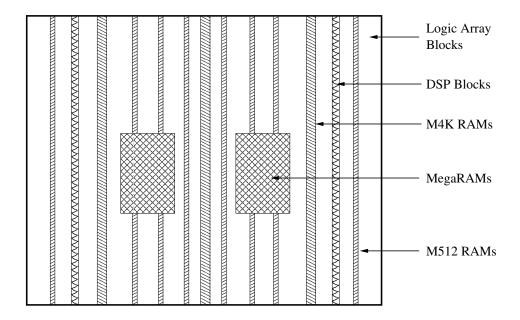

The Stratix FPGA is illustrated in Figure 2.2 and is comprised of a sea of logic elements (LEs) grouped in blocks of ten referred to as a logic array block (LAB). Each LE contains a 4-input lookup table and a flip flop. Stratix also contains fast multipliers, known as DSP blocks, which can perform 32x32 bit multiplies at 150 MHz, which is as fast

Figure 2.2: The Stratix Architecture

or faster than most soft processor designs—Altera's industrial Nios II soft processor has variations which run between 135MHz and 150 MHz. Finally, Stratix has three different sizes of block RAMs: M512 (512 bits), M4K (4096 bits), and Mega-RAM (65536 bytes). The speeds of each RAM are 320 MHz, 290 MHz, and 270 MHz respectively, making them also quite fast compared to logic. All RAMs are synchronous, meaning that they have registered inputs, and are dual ported allowing them to read/write to any two locations simultaneously. The only exception is the M512 which supports reading on one port and writing on the second port but can never do two reads or two writes simultaneously. Moreover, the ports have individually configurable data widths. More details on the architecture of Stratix can be found in the Stratix Device Handbook [5]. From the statistics above, it is clear that FPGAs are a much different platform than traditional hard processors, as highlighted by the difference in the relative speeds of logic versus multipliers and memory.

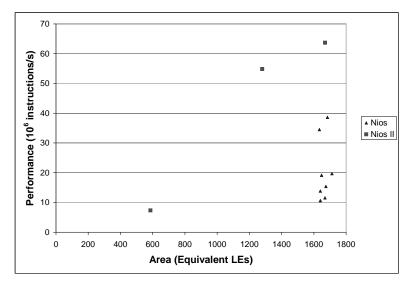

Figure 2.3: Nios II vs Nios Design Space

#### 2.5 Industrial Soft Processors

In September 2000, Altera released the first commercial soft processor the Nios [2]. Shortly after this, Xilinx released their soft processor, the Microblaze [60]. Since then the popularity of soft processors has grown immensely and now 16% of programmable logic designs contain an embedded soft processor with 50% of those designs using Nios, and 40% using Microblaze [41], the remainder mostly comprised of freely available cores [42] or a custom-made processor [59]. Both industrial soft processors have undergone several revisions and Altera has recently released its second generation soft processor the Nios II. The Nios II architecture varies greatly from the original Nios; intelligent architectural decisions enabled Altera to create three Nios II cores which dominate all Nios versions. We have measured the area and benchmarked each of the Nios II and Nios cores and plotted the performance-area space shown in Figure 2.3—which agrees with figures released by Altera [3]. The figure shows that the three Nios II cores dominate the Nios cores in both size and performance. We have selected Nios II as the industrial core to validate our exploration against, and a description of its architecture follows.

Nios II has three mostly-unparameterized architectural variations: Nios II/e, a very small unpipelined 6-CPI processor with a serial shifter and software multiplication sup-

Nios II/e Nios II/s Nios II/f Performance DMIPS/MHz 0.16 0.75 1.17 Max DMIPS 120 28 200 Clock (MHz) 150 135 135 (LEs) 600 1300 1800 Area Pipeline 5 unpiped 6 Branch Prediction static dynamic ALU Multiplier 1-cycle 3-cycle Divider optional Shifter serial 3-cycle 1-cycle

Table 2.2: Comparison of Nios II Variants

port; Nios II/s, a 5-stage pipeline with a multiplier-based barrel shifter, hardware multiplication, and an instruction cache; and Nios II/f, a large 6-stage pipeline with dynamic branch prediction, instruction and data caches, and an optional hardware divider. The three variations are contrasted in more detail in Table 2.2, which compares the three variations in terms of performance, area, and architecture. Performance is measured using the Dhrystone benchmark and is reported in DMIPS (Dhrystone Millions of Instructions per Second), and DMIPS/MHz, a clock frequency independent measurement of the same. Clearly Nios II/f outperforms the other two, however it is also largest in area as reported by the number of Stratix LEs used to implement each processor. In terms of pipelining, The Nios II/e is unpipelined, thereby requiring no branch prediction. The Nios II/s is a 5-stage pipeline with static branch prediction, while Nios II/f is a 6-stage pipeline with dynamic branch prediction. In both cases, the prediction scheme is not known. The Nios II/s uses the on-chip multipliers for performing both multiplication and shifting operations, but for both operations, the pipeline is stalled for 3 cycles. The Nios II/f also uses the on-chip multipliers for both multiplication and shifting and completes both in a single cycle. In addition, Nios II/f has the option of implementing a hardware divider unit which requires 4-66 cycles to compute its result.

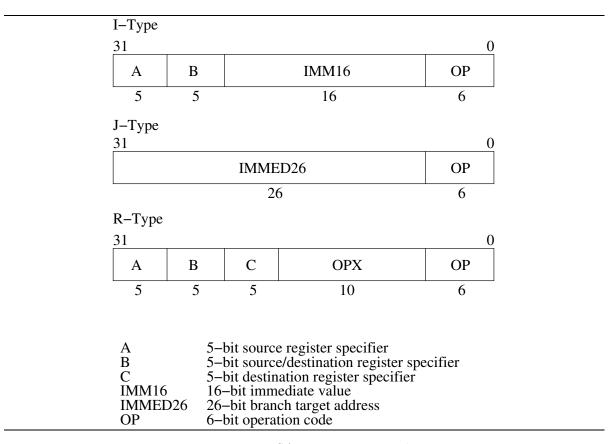

All three Nios II variants use the same ISA known as the Nios II instruction set. It is very similar to the MIPS-I ISA discussed in Section 2.2; even its instruction format shown in Figure 2.4 is nearly identical to that of the MIPS-I shown in Figure 2.1, although the

Figure 2.4: Nios II ISA Instruction Word Format

location of the fields in the instruction word have been rearranged. However it does have three significant differences: (i) Nios II does not have branch delay slot instructions; (ii) Nios II does not have HI/LO registers for multiply, instead the Nios II multiply writes its 32-bit result to the register file—separate instructions are used for calculating the upper and lower 32-bit results of a multiply; (iii) its nop instruction is implemented as an add instruction instead of a shift left instruction as in MIPS.

### 2.6 Architectural Exploration Environments

While industry architects have optimized commercial soft processors, as seen by Metzgen [37, 38], to the best of our knowledge a microarchitectural exploration of soft processors has never been conducted in the depth presented in this work. However, the architectural exploration of traditional hard processors has become a popular research

topic in recent years, and that research has produced numerous exploration environments that are primarily driven by one of two exploration methods: parameterized cores or architecture description language (ADLs). The two methods are described below.

#### 2.6.1 Parameterized Cores

A parameterized processor core is a processor designed at the RTL level (Register Transfer Level) allowing for certain aspects of the architecture to be varied. The RTL design is expressed using an HDL (Hardware Description Language) such as Verilog or VHDL (Verilog Hardware Description Language) which contains parameters that can be tuned to alter the processor architecture in a manner intended by the original designer. The functionality of the processor is guaranteed by the original designer for many combination of parameter values. The advantage of parameterized cores is that the design is at the RTL level allowing for accurate measurements of speed, area, and power impact. However, few existing parameterized cores target FPGAs specifically, and all of them narrowly constrain the potential design space because of the hard-coded parameterization. Changing the ISA, timing, or control logic requires large-scale modification to the source code of the processor, making these parameterized cores unsuitable for a rapid and broad design space exploration.

We now discuss some examples of parameterized cores: the Opencores [42] website is dedicated to providing a collection of freely available IP cores to the general public. They have many processors available, some of them which target FPGAs, and most having tunable parameters for meeting design constraints which can be explored. However this exploration space is too narrow for our needs. LEON [15] is a VHDL description of a SPARC processor which has been used by Padmanabhann [43] to conduct semi-automatic system-level explorations (caches, TLBs, etc). The research we are conducting does not include memory hierarchy and other system-level issues and the narrow microarchitectural design space afforded by the LEON core (register window size, and optional multiply/divide/multiply-accumulate units) is inadequate for the breadth of ex-

ploration we intend to conduct. The XiRisc [33] is similarly a parameterized core written in VHDL. This DLX-like [20] processor allowed for various parameterizations including 2-way VLIW, 16/32-bit datapaths, and optional shifter, multiplier, divider, and multiply-accumulate units. While these results are interesting, the core does not easily allow for further interesting exploration. Fagin [12] performed a small architectural exploration specifically for FPGA-based processors by creating an unpipelined MIPS core processor and manually adding pipelining, and then forwarding. Again this exploration space was very narrow and only the area effect on Actel FPGAs was considered. Gschwind [18] produced a MIPS-based VHDL core for exploration, but no exploration results were extracted from it.

#### 2.6.2 ADL-based Architecture Exploration Environments

An ADL (Architecture Description Language) is a language which completely specifies the architecture of the processor. A multitude of ADL-based architecture exploration environments have been proposed—a good summary of these is provided by Gries [17] and by Tomiyama [50]. The focus of these ADLs is to drive the creation of custom compilers, instruction set simulators, cycle accurate simulators, and tools for estimating area and power. Unfortunately these ADLs are often verbose and overly general, caused primarily by the need to simultaneously maintain instruction semantics (for instruction set simulation and compiler generation) and instruction behaviour (for cycle accurate simulation and RTL generation). Since we are only interested in the latter, our architecture specification can be simplified considerably. Furthermore, few ADLs provide a path to synthesis through RTL generation, and for those that do [27, 47, 56] the resulting RTL is often a very high-level description (for example, in SystemC), and therefore depends heavily on synthesis tools to optimize the design. For example, Mishra [27] provided RTL generation for the EXPRESSION ADL and discovered that the automatically generated RTL incurred 20% more area, 52% more power, and 28% slower clock frequency than an equivalent processor which was coded behaviourally for the purpose of cycle accurate

| Name         | Source       | Design focus <sup>1</sup> | Path to hardware        | Tool generation |

|--------------|--------------|---------------------------|-------------------------|-----------------|

| ASIP-Meister | [23, 29]     | micro                     | yes (generated)         | sim, comp       |

| Chess/Check  | [19]         | micro                     | yes (generated)         | $\sin, comp$    |

| CoCentric    | [48]         | $\operatorname{system}$   | yes (SystemC)           | no              |

| Expression   | [27, 40]     | micro                     | yes (generated)         | $\sin, comp$    |

| LisaTek      | [9, 46, 47]  | micro                     | SystemC or control only | $\sin$ , asm    |

| Mescal       | [45, 55, 56] | system+micro              | yes (generated)         | sim, asm        |

| PICO         | [26]         | system+ micro             | yes (generated)         | comp, sim       |

Table 2.3: Comparison of ADL-based Architecture Exploration Environments

simulation. It seems reasonable to assume that had this comparison been against a design coded for efficient synthesis, the results would likely be significantly worse. Table 2.3 summarizes some ADL-based architectural exploration environments which provide a path to hardware. In an FPGA, using different hardware resources results in large trade-offs—hence the soft processor designer needs direct control of these decisions. For this reason, the RTL generation provided by these ADL-based environments are inadequate for our purposes. In addition, availability and learning curve were also considered when rejecting the option of using ADL-based environments. For example, the LISA language is a commercial product and publications report requiring one month to learn the language and design a single processor [47].

#### 2.7 Closely Related Work

In this section, more closely related research is discussed and contrasted with the work in this dissertation. The following works are similar in theme, but for reasons detailed below remain inadequate for our purposes.

Mishra and Kejariwal augmented the EXPRESSION ADL to include RTL generation enabling synthesis-driven architectural exploration [27, 40]. The quality of these results were described above and were significantly worse than a model which was already a poor implementation of an industrial processor core—it was meant for simulation not

<sup>&</sup>lt;sup>1</sup>Micro refers to the microarchitecture of a processor, namely the machine state, register file, and execution units, while system refers to system-level issues such as memory hierarchy, I/O, and operating system support.

synthesis. A small exploration was then conducted [40] for an FFT benchmark where the number of functional units were increased from 1 to 4, the number of stages in the multiplier unit were increased from 1 to 4, and sin/cos instructions were added to the instruction set. The exploration was not complete as it did not consider the entire processor (measurements were only made for the execution stage). Moreover, this exploration was performed for traditional hard processors, without any focus on FPGA-based processors.

The UNUM [11] system automatically generates microprocessor implementations where users can seamlessly swap components without explicit changes to the control logic. In this philosophy UNUM is identical to our system. The output of the UNUM system is a processor implemented in *Bluespec* [8], a behavioural synthesis language which can be translated to RTL. The drawback to this approach is that there is overhead to using the behavioural synthesis language which also abstracts away implementation details that are essential for efficient FPGA synthesis. This system is still being developed and has yet to be used in an architectural study.

The PEAS-III/ASIPMeister project [29] focuses on ISA design and hardware software co-design, and proposes a system which generates a synthesizable RTL description of a processor from a clock-based micro-operation description of each instruction. Unfortunately the design space is very limited as PEAS-III does not support hardware interlocking (the compiler must insert null operations) and does not allow multi-cycle functional units. Moreover, a small structural change to the architecture requires changes to the description of many instructions to produce the correct control logic. It is interesting to contrast the RTL generation of the PEAS-III system to ours: PEAS-III infers the datapath from the micro-operation instruction descriptions; in our system we infer the micro-operations of each instruction from the datapath, allowing the user to carefully design the datapath. This choice reflects our desire for efficient synthesis since we believe careful design of the datapath is crucial for efficiency. PEAS-III was used [23] to conduct a synthesis-driven exploration which explored changing the multiply/divide unit to

sequential (34-cycles), and then adding a MAC (multiply-accumulate) instruction. The results were compared for their area and clock frequency as reported by the synthesis tool.

Plavec[44] designed an open-source RTL description of a processor which implemented the Altera Nios ISA. During the design process, architecture and implementation decisions were made incrementally based on bottlenecks found along the way. FPGA nuances lead naturally to a 3-stage pipeline starting point, which was then successfully increased to a 4-stage pipeline to relieve a heavily dominating critical path. Further exploration of pipeline depth was hindered by the arduousness associated with control modification. Estimates were performed by simply adding registers to the datapath to quantify upper bounds on the frequency gain, and back of the envelope calculations were used to estimate cycle count increase. The open-source RTL model was used to perform simpler self-contained architectural modifications such as register window size, and register file size.

Finally, there has recently been a surge of interest in using FPGAs as a platform for performing processor and system-level architectural studies [22]. However, the goal of such work is to overcome the long simulation times associated with cycle-accurate simulation of large and complex processors. Often the role of the FPGA is to emulate cycle-accurate details or accelerate computation, whereas the role of FPGAs in our work is to serve as the final platform for the processor. Researchers in this field of FPGA-based system emulation often focus on an architectural novelty (for example transactional parallel systems [30], caching [34], vector-thread processors [25]) and build FPGA-based emulators to explore the space. None of this work focusses on area, clock frequency, or power; a functional FPGA model is all that is desired to extract cycle-to-cycle behaviour of the systems.

#### 2.8 Summary

This chapter has defined basic computer architecture terminology as well as summarized the MIPS-I ISA and the subset of it used in our exploration. Since our research is motivated by the desire to meet stringent design constraints through application specific customizations, the field of architecting ASIPs has been briefly summarized. Since we focus on soft processors, we describe the architecture of FPGAs and our target FPGA device, as well as the industrial Nios II soft processor core we benchmark against. We have conducted a comparison of processor architecture exploration environments and have highlighted the motivations for designing a custom exploration environment. Finally, the chapter has surveyed and contrasted research which is closely related to that in this dissertation.

### Chapter 3

## The SPREE System

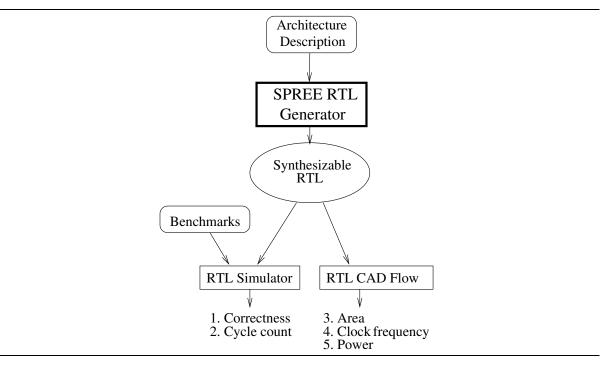

In this chapter, the Soft Processor Rapid Exploration Environment (SPREE) is described. The purpose of SPREE [62] is to facilitate the microarchitectural exploration of soft processors. Figure 3.1 depicts the role of SPREE in this research infrastructure, and provides an overview of its functionality: from an architecture description, the RTL generator emits synthesizable RTL which is used to measure area, performance, and power.

RTL generation is employed to gain very accurate measurements of a given soft processor design: FPGA CAD tools can be used to extract accurate area, clock frequency, and power measurements from an RTL description of a processor, and RTL simulators can be used to execute benchmark applications on the processor and measure exact cycle counts. We will use SPREE to rapidly generate synthesizable RTL descriptions for a wide variety of soft processor architectures, enabling us to thoroughly explore and understand the soft processor design space.

Some reduction in the breadth of our soft processor exploration was necessary to reduce the development time of SPREE. We consider simple, in-order issue processors that use only on-chip memory as main memory and hence have no cache. The memory on the FPGA is faster than a typical processor implementation eliminating the need for exploring caches. Moreover, the largest FPGA devices have more than one megabyte

Figure 3.1: Overview of the SPREE system.

of on chip memory which is adequate for many applications (in the future we plan to broaden our application base to those requiring off-chip RAM and caches). We also do not yet include support for branch prediction, exceptions, or operating systems. Finally, in this research we do not modify the ISA or the compiler, with the exception of evaluating software vs hardware support for multiplication (due to the large impact of this aspect on cycle time and area).

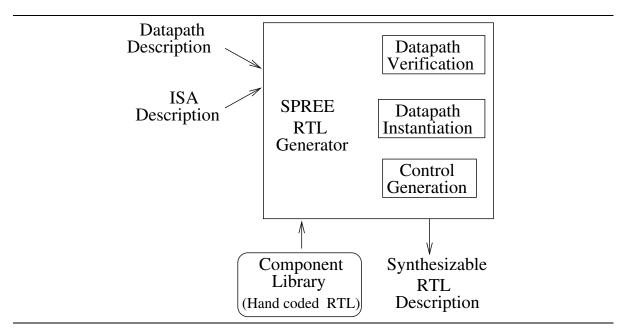

The complete SPREE system is composed of the SPREE RTL Generator, and the SPREE Component Library. Figure 3.2 depicts a block-level diagram of the SPREE RTL Generator, which takes as input a description of the target ISA and the desired datapath, verifies that the datapath supports the ISA, instantiates the datapath, and then generates the corresponding control logic. The output is a complete and synthesizable RTL description (in Verilog) of a soft processor. The SPREE Component Library is a collection of hand-implemented components used to build a datapath. As shown in Figure 3.2, the library also interfaces with the RTL Generator. The subsequent sections will describe in more detail the architecture description input, the Component Library,

Figure 3.2: An overview of the SPREE RTL generator.

and the operations of the RTL Generator.

#### 3.1 Input: The Architecture Description

The input to the SPREE system is the description of the desired processor, composed of textual descriptions of the target ISA and the processor datapath which implements that ISA. The functionality of each instruction in the ISA is described in a language which is also used to describe the functionality of components in the Component Library. The datapath is then described as an interconnection of these components. The following describes each of these in more detail.

#### 3.1.1 Describing the Instruction Set Architecture

The instruction-set of the processor is described using a set of generic operations (GENOPs) which form a common language for describing the behaviour of a component and the semantics of an instruction. A GENOP is a small unit of functionality performed inside a typical microprocessor: examples of GENOPs include subtraction (SUB), program counter write (PCWRITE), load byte from memory (LOADBYTE), and register read (REGREAD). Each

Table 3.1: GENOPs used in SPREE

| GENOP Name      | Semantics                                            | Description                               |

|-----------------|------------------------------------------------------|-------------------------------------------|

| NOP             | o0=i0                                                | Passes the input through unchanged        |

| IFETCH          | o0=opcode,o1=rs,o2=rt,o3=rd,                         | Outputs complete instruction opcode       |

| PCREAD          | o0=program counter                                   | Outputs the current PC value              |

| REGREAD         | o0=register[i0]                                      | Reads register i0 from register file      |

| HIREAD          | o0=HI                                                | Reads the MIPS HI register                |

| LOREAD          | o0=LO                                                | Reads the MIPS LO register                |

| REGWRITE        | Write i0 into i1                                     | Performs write to register file           |

| PCWRITE         | Write PC if i1 true                                  | Branch on condition i1                    |

| PCWRITEUNCOND   | Write PC                                             | Jump to target                            |

| HIWRITE         | Write HI register                                    | Writes to the MIPS HI register            |

| LOWRITE         | Write LO register                                    | Writes to the MIPS LO register            |

| CONST           | ox=x                                                 | Outputs the index on every port           |

| SIGNEXT16       | o0=sign extended i1                                  | Sign extends i1 to 32-bits                |

| BRANCHRESOLVE   | o0=eq, o1=ne, o2=lez, o4=gtz, o5=gez                 | Computes branch flags                     |

| MERGE26LO       | o0=hi 4-bits of i0,lo 26-bits of i1                  | Computes jump targets                     |

| ADD             | 00=i0+i1                                             | Performs addition                         |

| SUB             | o0=i0-i1                                             | Performs subtraction                      |

| SLT             | 00 = (i0 < i1)                                       | Compares i0 and i1                        |

| AND             | o0=i0&i1                                             | Bitwise and of i0 and i1                  |

| OR              | o0=i0 i1                                             | Bitwise or of i0 and i1                   |

| XOR             | o0=i0^i1                                             | Bitwise xor of i0 and i1                  |

| NOR             | $o0=\tilde{(i0 i1)}$                                 | Bitwise nor of i0 and i1                  |

| STOREWORD       | Store i0 in address i1                               | Performs 32-bit stores                    |

| STOREHALF       | Store i0 in address i1                               | Performs 16-bit stores                    |

| STOREBYTE       | Store i0 in address i1                               | Performs 8-bit stores                     |

| LOADWORD        | o0=data in address i1                                | Performs 32-bit loads                     |

| LOADHALF        | o0=data in address i1                                | Performs 16-bit loads                     |

| LOADBYTE        | o0=data in address i1                                | Performs 8-bit loads                      |

| SHIFTLEFT       | o0=i0< <i1< td=""><td>Performs left shift</td></i1<> | Performs left shift                       |

| SHIFTRIGHTLOGIC | o0=i0>>i1                                            | Shifts right filling with zeros           |

| SHIFTRIGHTARITH | o0=i0>>i1                                            | Shifts right filling with hi bit of i0    |

| MULT            | 00,01 = i0 * i1                                      | Outputs upper and lower halves of product |

| DIV             | 00 = i0  div  i1, 01 = i0  mod  i1                   | Returns divisor and remainder             |

GENOP has a predetermined interface using indexed input and output ports. For example, the SUB GENOP performs the subtraction function o0=i0-i1 by taking input port 0 (i0), subtracting input port 1 (i1) from it and returning the result on output port 0 (o0). Thus, the SUB GENOP uses the two input ports 0 and 1, and the output 0 to perform the subtraction. The complete set of GENOPs used in SPREE is shown in Table 3.1 using the same notation.

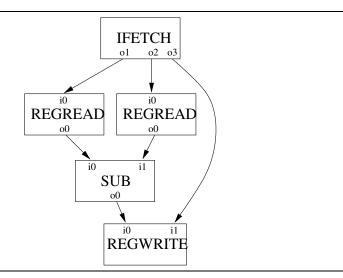

Each instruction in the processor description is described in terms of a data dependence graph of GENOPs. An example of such a graph is shown in Figure 3.3 for the MIPS subtract-signed instruction. In the graph, the nodes are GENOPs and the edges rep-

Figure 3.3: The MIPS SUB instruction (sub rd,rs,rt) shown as a dependence graph of GENOPs.

resent a flow of data from one GENOP to another. We impose the rule that no GENOP can execute until all of its inputs are ready. For a given instruction this graph shows the mandatory sequence of GENOP execution, although the datapath will determine the exact timing. From the example in Figure 3.3, the IFETCH GENOP has no inputs, and outputs the different fields of the instruction word. From the instruction word, the two source operand identifiers are passed to the register file (REGREAD) to read the source operand values. These values, are sent to the SUB GENOP and the difference, as well as the destination register from the instruction word, are connected to the register file for writing (REGWRITE).

The graph is described using C++ code as shown in Figure 3.4. New GenOp objects are created and links are made between the indexed ports of each GENOP using the add\_link function. In the example, the instruction fetch (IFETCH), the subtraction (SUB) and the two register read GENOPs (REGREAD) are first dynamically allocated. Connections are made between ports 1 and 2 of IFETCH to port 0 of both REGREADs to read the rs and rt operands respectively. Their values are connected to the ports of the subtraction operation, and the result on port 0 is connected to the writeback operation REGWRITE on port 0. Finally, the index of the destination register from port 3 of IFETCH is connected

```

GenOp * ifetch=new GenOp(GENOP_IFETCH);

GenOp * op=new GenOp(GENOP_SUB);

GenOp * rs = new GenOp(GENOP_RFREAD);

GenOp * rt = new GenOp(GENOP_RFREAD);

add_link(ifetch ,1 ,rs ,0);

add_link(rs ,0 ,op ,0);

add_link(ifetch ,2 ,rt ,0);

add_link(rt ,0 ,op ,1);

GenOp * wb = new GenOp(GENOP_RFWRITE);

add_link(op ,0 ,wb ,0);

add_link(ifetch ,3 ,wb ,1);

```

Figure 3.4: The MIPS SUB instruction described using C++ code.

Figure 3.5: A datapath description shown as an interconnection of components.

to port 1 of REGWRITE. The rest of the supported MIPS-I ISA is described similarly.

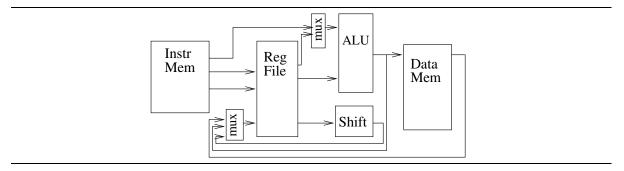

#### 3.1.2 Describing the Datapath

The datapath is described by listing the set of components and the interconnection between their physical ports. An example of a datapath is shown in Figure 3.5. In this simplified datapath, the instruction memory feeds the register file with the addresses of the two source operands to read. The register file feeds the ALU and shifting unit whose results are written back to the register file. Otherwise, the result of the ALU drives the effective address of the data memory location to read from or write to. If data memory is read, the loaded value is also written to the register file. The multiplexers shown in the datapath are optional, if not specified they will be automatically inferred when a port has multiple drivers as discussed in Section 3.3.2.

A processor architect can create any datapath that supports the specified ISA. The datapath must also include certain control components when necessary, for example:

pipeline registers, hazard detection units, and forwarding lines are available in the component library and must be used in an appropriate combination to ensure correct functionality of the processor. We hope to further automate the insertion of these components in the future.

The decision to use a structural architectural description in SPREE reflects our goal of efficient implementation. Structural descriptions provide users with the ability to manage the placement of all components including registers, and multiplexers in the datapath. This management is crucial for balancing the logic delay between registers to achieve fast clock speeds. By analyzing the critical path reported by the CAD tool, users can identify the components which limit the clock frequency and take one of three actions: (i) reducing the internal logic delay of a component, for example, making a unit complete in two cycles instead of one; (ii) moving some of the logic (such as such as multiplexers and sign-extenders) from the high delay path into neighbouring pipeline stages to reduce the amount of logic in the high delay path; (iii) adding non-pipelined registers in the high delay path causing a pipeline stall. The latter two of these actions depend critically on this ability to manually arrange the pipeline stages, referred to as retiming, which is difficult for modern synthesis tools because of the complexity in the logic for controlling the pipeline registers. Without a good ability to optimize delay we risk making incorrect conclusions based on poor implementations. For example, one might conclude that the addition of a component does not impact clock frequency because the impact is hidden by the overhead in a poorly designed pipeline. For this reason, architectural exploration in academia has traditionally neglected clock frequency considerations.

### 3.2 The SPREE Component Library

### 3.2.1 Selecting and Interchanging Components

The SPREE Component Library, which is used to build the datapath described above, stores the RTL code and interface descriptions of every available processor component.

Table 3.2: Components in the SPREE Component Library

| Component       | Description                                                                              |  |  |  |

|-----------------|------------------------------------------------------------------------------------------|--|--|--|

| Name            |                                                                                          |  |  |  |

| addersub        | An arithmetic unit used to perform add, sub, and slt instructions.                       |  |  |  |

| addersub_1      | Same but has a 1-cycle latency.                                                          |  |  |  |

| branchresolve   | Compares two register operands and computes the branch conditions.                       |  |  |  |

| const           | Outputs a constant value.                                                                |  |  |  |

| data_mem        | 1-cycle latency data memory including necessary alignment logic.                         |  |  |  |

| data_mem_reg    | Same but 2-cycle latency (a register before the alignment logic.                         |  |  |  |

| delay           | A delay register that is always enabled.                                                 |  |  |  |

| forwarding_line | A forwarding line for avoiding data hazards in a pipeline.                               |  |  |  |

| hazard_detector | A data hazard detector which stalls the pipeline.                                        |  |  |  |

| hi_reg          | The MIPS HI register.                                                                    |  |  |  |

| ifetch_unpiped  | Unpipelined instruction fetch unit including program counter.                            |  |  |  |

| ifetch_pipe     | Pipelined version of the same.                                                           |  |  |  |

| lo_reg          | The MIPS LO register.                                                                    |  |  |  |

| logic_unit      | The logic unit, capable of executing and, or, xor, and nor.                              |  |  |  |

| lui             | Shifts left by 16 to execute the MIPS load-upper-immediate instruction.                  |  |  |  |

| merge26lo       | Concatenates the 4 upper bits and 26 lower bits of two oerands.                          |  |  |  |

| mul             | performs 32-bit multiplication producing a 64-bit result.                                |  |  |  |

| mul_1, mul_2    | 1-cycle and 2-cycle latency multipliers.                                                 |  |  |  |

| mul_shift       | performs multiplication and shifting (left, right logical, right arithmetic).            |  |  |  |

| nop             | The null component, behaves as a wire.                                                   |  |  |  |

| pcadder         | A 30-bit adder used for computing branch targets.                                        |  |  |  |

| pipereg         | A pipelined register.                                                                    |  |  |  |

| pipedelayreg    | A non-pipelined register which stalls the pipeline when used.                            |  |  |  |

| reg_file        | The register file which can perform two reads and one write simultaneously.              |  |  |  |

| serialalu       | A fully serialized ALU capable of performing arithmetic, logic, and shift operations.    |  |  |  |

| shifter_LUT     | A LUT-based barrel shifter.                                                              |  |  |  |

| shifter_LUT_1   | A 1-cycle pipelined version of the same.                                                 |  |  |  |

| shifter_serial  | An variable-latency serial shifter requiring as many cycles as the amount being shifted. |  |  |  |

| shifter_serial_ | A combined serial shifter and data memory unit where the shifter is used for memory      |  |  |  |

| datamem         | alignment.                                                                               |  |  |  |

| signext16       | Sign extends the 16-bit input forming a 32-bit signed result.                            |  |  |  |

| zeroer          | A wire which either passes the input when enabled or the value 0 when not.               |  |  |  |

Examples of these include register files, shifters, and ALUs. To evaluate different options for a given part of the datapath, a user can easily interchange components and regenerate the control logic. Therefore, whether a component is pipelined, combinational, or variable in latency, the automatically-generated control logic adapts to accommodate it. A list of the components in the SPREE Component Library is given in Table 3.2.

#### 3.2.2 Creating and Describing Datapath Components

The Component Library described above can also be expanded by a user to include custom components. In this section we describe how these components are described

Figure 3.6: The Component Interface.

and imported into the Component Library. To create a datapath component, a user must perform three tasks: (i) provide the RTL description of the new component; (ii) ensure it adheres to SPREE's component interface rules; and (iii) describe its interface and functionality in a library entry. Each of these three steps will be considered in detail below.

The RTL Description The user must write the RTL description for the new component in Verilog. Since the goal is to produce an efficiently-synthesizable processor, users should consider the resources available on the target FPGA device and implement the component as efficiently as possible. The Verilog is placed in a text file where the top-level module is that specified by the component name.

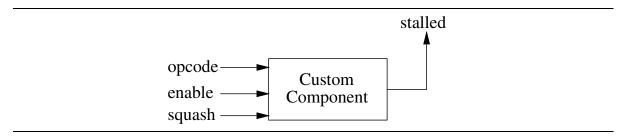

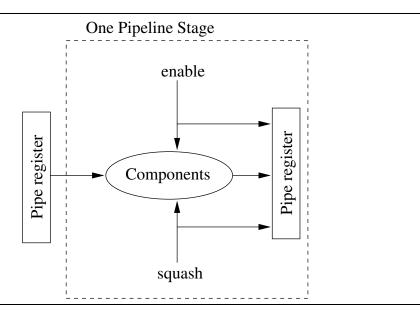

The Component Interface The control generation in SPREE can support components with a wide variety of timing interfaces including zero cycle latency (or purely combinational), pipelined, multi-cycle unpipelined, and variable cycle latency. SPREE components are constrained to using the following style of control interface by requiring the presence of the following four control signals (when appropriate): opcode, enable, squash, and stalled signals as shown in Figure 3.6. The opcode signal is used to tell the component what operation to perform and is mandatory when a component can perform more than one operation. For example, this signal will instruct the arithmetic unit to perform an add or subtract. The enable signal indicates when the component should perform its operation and is thus used for scheduling. The squash signal is used only for pipeline registers whose contents must be destroyed when the stage is squashed. The

Figure 3.7: Library entry format.

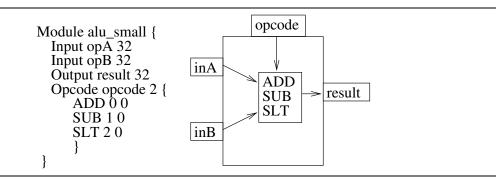

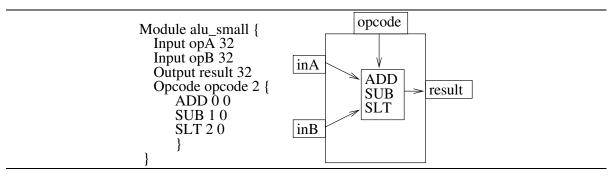

Figure 3.8: Sample component description for a simplified ALU. The ALU supports the GENOPs ADD, SUB, and SLT.

squash interface is exposed to the user to allow users to embed their own pipeline registers within a component. Finally the stalled signal is generated by variable-latency components to indicate that its operation has yet to complete. These four signal types are generic enough to accommodate a wide variety of components and must be used where appropriate when creating a custom component. The control logic generated by SPREE will drive the opcode, enable and squash signals and monitor the stalled lines; the user need only support and declare these signals. The names of each physical port in the component which connect to these signals can have arbitrary names, except for the stalled signal which must have the port name "stalled".

The Library Entry The interface and functionality of a component is communicated to SPREE through a text library entry. Figure 3.7 gives the complete format for a library entry which is detailed in Appendix A.3. Figure 3.8 shows a simplified library entry for a small ALU. The RTL interface to the component is described by the Module line, which defines the name of the Verilog module, and by the names and bit-widths of the RTL input and output ports which follow. The functionality of the component is described in the Opcode section which defines an opcode port (opcode). The fields inside the Opcode section describe the functionality of the component. Each line begins with the name of the supported operation and is proceeded by two integers: (i) the opcode port value that selects that operation, and (ii) the latency in cycles for the operation to complete (variable cycle latency is denoted with a negative latency). For example, the ADD function of the simple ALU specified in Figure 3.8 is selected by opcode 0 and has zero extra cycles of latency. The Opcode section can support an arbitrary number of GENOPs, which allows for versatile functional units, and a component can have an arbitrary number of opcode ports, which allows for parallelism within a component.

### 3.3 Generating a Soft Processor

From the above inputs (ISA description, datapath description, and Component Library), SPREE generates a complete Verilog RTL model of the desired processor. As shown in Figure 3.2 and described below, SPREE generates the processor in three phases: (i) datapath verification, (ii) datapath instantiation, and (iii) control generation.

#### 3.3.1 Datapath Verification

A consistency problem arises as there are two separate inputs that describe the processor datapath and ISA: it is possible to assemble a datapath incapable of executing the described ISA. To prevent the generation of non-functional processors, SPREE must verify that the datapath indeed supports the ISA by ensuring the flow of data through the

datapath is analogous to the flow of data imposed by the instruction descriptions. In the ISA description, each instruction has an associated graph of GENOPs describing its functionality as discussed in Section 3.1.1. The datapath is described as an interconnection of components, but the components are described in terms of GENOPs as seen in Section 3.2.2. Therefore the datapath is also a graph of GENOPs. To verify that the datapath supports the ISA, SPREE must confirm that each of the instruction graphs are subgraphs of the datapath graph.