Open access · Journal Article · DOI:10.1109/TPDS.2009.125

# The Signal Synchronous Multiclock Approach to the Design of Distributed Embedded Systems — Source link

Abdoulaye Gamatié, Thierry Gautier

Institutions: French Institute for Research in Computer Science and Automation

Published on: 01 May 2010 - IEEE Transactions on Parallel and Distributed Systems (IEEE)

Topics: Formal specification, Correctness, Asynchronous communication and Hardware architecture

#### Related papers:

- Polychrony for system design

- The synchronous languages 12 years later

- The synchronous data flow programming language LUSTRE

- Software implementation of synchronous programs

- Efficient distribution of Triggered Synchronous Block Diagrams on asynchronous platforms

## The Signal Synchronous Multiclock Approach to the Design of Distributed Embedded System

Abdoulaye Gamatié, Thierry Gautier

### ▶ To cite this version:

Abdoulaye Gamatié, Thierry Gautier. The Signal Synchronous Multiclock Approach to the Design of Distributed Embedded System. IEEE Transactions on Parallel and Distributed Systems, Institute of Electrical and Electronics Engineers, 2010, 21 (5), pp.641-657. 10.1109/TPDS.2009.125. hal-00550056

### HAL Id: hal-00550056 https://hal.archives-ouvertes.fr/hal-00550056

Submitted on 23 Dec 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# The Signal Synchronous Multi-clock Approach to the Design of Distributed Embedded Systems

Abdoulaye Gamatié and Thierry Gautier

**Abstract**—This paper presents the design of distributed embedded systems using the synchronous multi-clock model of the SIGNAL language. It proposes a methodology that ensures a correct-by-construction functional implementation of these systems from high-level models. It shows the capability of the synchronous approach to apply formal techniques and tools that guarantee the reliability of the designed systems. Such a capability is necessary and highly worthy when dealing with safety-critical systems. The proposed methodology is demonstrated through a case study consisting of a simple avionic application, which aims to pragmatically help the reader to understand the manipulated formal concepts, and to apply them easily in order to solve system correctness issues encountered in practice. The application functionality is first modeled as well as its distribution on a generic hardware architecture. This relies on the endochrony and endo-isochrony properties of SIGNAL specifications, defined previously. The considered architectures include asynchronous communication mechanisms, which are also modeled in SIGNAL and proved to achieve message exchanges correctly. Furthermore, the synchronizability of the different parts in the resulting system is addressed after its deployment on a specific execution platform with multi-rate clocks. After all these steps, a distributed code can be automatically generated.

Index Terms—Distributed embedded systems, Correct-by-construction design methodology, Safety-critical domains, Formal validation, Synchronous model, Asynchronous mechanisms, Multi-clock, SIGNAL language

#### **1** INTRODUCTION

There are various reasons to distribute embedded systems: the high performance enabled by the use of several computation units for a better response time, sometimes the geographical delocalization of the system elements, the replication of systems for fault tolerance, etc. Typical domains in which distributed embedded systems are useful are the following:

- *transportation*: the last generation of cars and aircraft increasingly combine computers and electrical linkages. This combination makes comfortable the control of the engine. This combination leads to so-called *fly-by-wire* systems, e.g., adopted in Toyota Prius automobile or in the A380.

- *telecommunication*: cell phone manufacturers and Internet highly face problems related to distributed and mobile embedded systems deployed on networks. A major issue is the compatibility between heterogeneous devices, and the robust and transparent communications in networks, while guaranteeing performance and real-time properties.

- *industrial automation*: it covers industrial robots and embedded mechatronic systems, which comprise technologies from engineering disciplines in computer software and hardware as well as in mechanics and automatic control. The issues concern the design of distributed architectures for scalable and reconfigurable mechatronic systems, and of embedded control.

The design of distributed embedded systems generally has to take into account several crucial aspects: the used communication mechanisms must be proved to be sufficiently robust, i.e. no loss of messages; for sub-systems located on different sites, the duration of communications must not alter the real-time properties of the overall system, the global functionality must be guaranteed, etc. So, the distribution of a system has to follow well-defined methodologies that offer the suitable means to clearly express its inherent concurrency and to validate its behavior w.r.t. functional and non functional requirements.

In the current study, we consider the *synchronous model* [10] for design and validation. This model offers an adequate formal basis to deal with the reliable design of embedded systems. Its basic assumption is that computation and communications are *instantaneous from the point of view of a logical time*, referred to as "*synchrony hypothesis*". This favors *deterministic* models of system behaviors for safe analysis.

#### 1.1 The synchronous multi-clock model of SIGNAL

The design of distributed systems has been extensively studied for decades [44], [19]. The asynchrony [20] inherent to these systems appears *a priori* as an obstacle to their description with the synchronous model. According to [45], a fully synchronous system is characterized by the *boundness and knowledge* of: *i*) *processing speed, ii*) *message delivery delay, iii*) *local clock rate drift, iv*) *load pattern,* and *v*) *difference among local clocks.* A fully asynchronous system assumes none of these characteristics.

Distributed embedded systems are generally implemented with GALS architectures, which are suitably abstracted with the SIGNAL synchronous multi-clock or polychronous model [37]. The multi-clock model is gaining an increasing attention from academia and industry to address the modern electronic designs [13], [24]. According to the polychronous model, the activation *clock* of a system consists of the set of instants at which its components react. This set is only partially ordered since concurrent components may have their own (independent) activation clocks. When these components do not interact, it is not necessary that their clocks be synchronized. The central question is not to agree on a global time, but to agree on the common event occurrences during the interaction of components. Contrarily to the usual monolithic approach adopted by the other synchronous languages (e.g. LUSTRE, ESTEREL until recently), which consists of compact single-clocked designs, the

This work has been partly supported by the European project IST SAFEAIR (Advanced Design Tools for Aircraft Systems and Airborne Software) - Convention  $n^{\circ}$  1 00 C 0149 00 31307 00 5.

<sup>•</sup> A. Gamatié is affiliated with CNRS/LIFL, Email: abdoulaye.gamatie@lifl.fr.

<sup>•</sup> T. Gautier is affiliated with INRIA, Email: thierry.gautier@irisa.fr.

polychronous approach aims at designing in a modular fashion systems with multiple loosely coupled clocks so as to be able to deal with the complexity of their distribution.

Compared to the synchrony/asynchrony definition of [45], the polychronous model offers an intermediate vision: while it assumes the boundness of computation and communication activities, the difference among local activation clocks is *a priori* unknown. This vision is opposed to the monolithic one, which considers the existence of a unique common clock in a system, represented by a totally ordered set of instants. The SIGNAL language relies on the polychronous model.

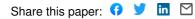

FIG. 1 illustrates the design philosophy behind polychrony: to give an adequate abstract model of a system shown in Fig. 1(b), which enables a subsequent choice towards a distributed system implemented by *globally asynchronous locally synchronous* (GALS) architectures [17] shown in Fig. 1(a), or a single-clocked system implemented by centralized architectures shown in Fig. 1(c).

Fig. 1. Distributed, polychronous and single-clocked systems.

The polychronous system, depicted in Fig. 1(b), consists of two concurrent sub-systems that receive control from events a and b and conditionally communicate via an event c or do something else (d or e). It can be refined into a single-clocked system, Fig. 1(c), by synchronizing the events a and b. It can be also refined into a distributed system, Fig. 1(a), by distributing a and b on two different locations and by implementing c by a FIFO communication channel. In general, the reliability of such channels is implicitly assumed in the polychronous model. However, in this paper, it is explicitly proved.

#### 1.2 Synchronous design of distributed systems

Among the large spectrum of literature devoted to the design of distributed systems [44], [19], we mainly concentrate below on related works that rely on the synchronous model.

As mentioned above, a major advantage of using such a model for the development of distributed embedded systems is that, on the one hand, the global correctness of systems can be trust-worthily guaranteed using the associated formal technology. It is particularly necessary when the system is used in a safety-critical domain such as automotive or avionics. This explains the numerous studies on program distribution problematics in synchronous languages. Most of these studies focus on *automatic program distribution* methods [27]: given a centralized synchronous program P and a distributed architecture A, the deployment of P on A is defined automatically, with the necessary inserted communication code, so that the resulting distributed program has the same functional behavior

as *P*. However, note that beyond these studies, automatic program distribution has been widely investigated [32].

The major contributions on this topic in the synchronous approach community could be summarized according to the main synchronous languages [10]: ESTEREL, LUSTRE and SIGNAL.

In ESTEREL, we can mention the work of Berry and Sentovich [12] on the construction of GALS systems as synchronous circuits represented by a network of communicating *codesign finite state machines*. GALS architectures [17] consist of components that execute synchronously and communicate asynchronously. Another relevant work concerns the ESTEREL specification and programming of large-scale distributed real-time systems [33].

The LUSTRE language has been also used in several studies on the design of distributed systems. Girault [26] addressed the distribution of synchronous automata within the framework of this language. Afterwards, he focused on further issues such as automatic deduction of GALS systems from centralised synchronous circuits [28], and the optimized execution of desynchronized embedded reactive programs to guarantee real-time constraints [29]. We must note the very important achievements by Caspi and his colleagues on the same topics (see [27]). They recently proposed an approach to deploy LUSTRE programs on *time-triggered architectures* [16].

In SIGNAL, there have been lots of results on program distribution, mostly from the theoretical viewpoint. The earlier work of Chéron [18] dealt with the communication of separately compiled SIGNAL programs. Then, Maffeïs [39] showed how to abstract such programs into graphs in order to define the qualitative scheduling and partitioning of these graphs. The work of Aubry [6] focused on similar problems as Girault [26] by exploring the manual and semi-automatic distribution of synchronous dataflow programs in SIGNAL. While these studies were mostly devoted to the practical side, Benveniste and Le Guernic lead several theoretical works on the distribution of SIGNAL programs [8], [9], [25], [11], [37], [41]. The approach presented in this paper shows how these theoretical results are exploited in practice to define correct-by-construction models of distributed embedded systems.

Finally, we can notice other interesting contributions such as [30] in which Grandpierre showed, with Petri nets, how one can derive a distributed implementation from a synchronous dataflow specification, e.g. in LUSTRE or SIGNAL, of a given application while minimizing the response time w.r.t. real-time requirements. The SYNDEX environment [31] aims at providing designers with such program distribution facilities.

#### 1.3 Our contribution: a seamless design methodology

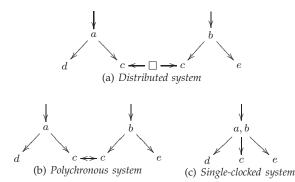

While the above studies mainly concern automatic program distribution, in this paper we focus on how to design entirely distributed embedded systems with a synchronous language by proposing a general methodology, FIG. 2, composed of four steps detailed in the following chronological order:

- 1) *System specification and manual distribution*: modeling of application functionality, distributed hardware architecture, and their association. This step is similar to the initial step in usual harware-software codesign;

- Automatic transformations: guaranteeing the global functional correctness of the distribution. These transformations exploit the endochrony and endo-isochrony properties of SIGNAL programs, presented in Section 2.2.2;

- 3) *Deployment on specific platforms*: instantiating the parts of the resulting model with components that represent

Fig. 2. Our design methodology for distributed embedded systems in SIGNAL.

specific platform mechanisms, e.g. for communication, synchronization. There are only few existing works devoted to the synchronous modeling of asynchronous mechanisms [34], [35], [23];

4) Non functional analysis and automatic code generation: checking the non functional (temporal) constraints induced by the chosen deployment and distributed code generation.

The above methodology is exposed through a case study. It is built on several complementary results obtained previously. The second step of this methodology uses an implementation of the theoretical results of [8], [9]. The third step relies on the insights gained from [21], [23] in which we have proposed a library of components consisting of synchronous models of asynchronous mechanisms for communication, synchronization or execution. Here, we consider the mechanism defined in [21] to describe the communications in the deployed system model of our case study. We also give the proof of queueing order preservation in this mechanism, which was an assumption previously. On the other hand, while the design approach presented in [23] mainly targets integrated modular avionics architectures, the current methodology aims at more general multi-processor architectures and fully makes use of the SIGNAL multi-clocked model. The fourth step uses the non functional analysis techniques proposed in [43], [36] and implements code generation approach defined in [25].

#### 1.4 Example: a Flight Warning System

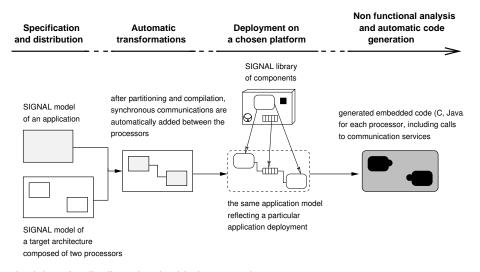

We consider a running example from the avionic domain, consisting of a Flight Warning System (FWS) to illustrate our methodology. This system is used in the Airbus A340 aircraft. It has been proposed by the Aerospatiale Company (France) as a case study in [38]. The FWS system is in charge of deciding on when and how to emit warning signals whenever there is an anomaly during the operational mode of an airplane. It is illustrated in FIG. 3 together with its implementation architecture. It consists of two cyclic concurrent processes:

- given an alarm a<sub>i</sub>, the alarm manager process confirms a<sub>i</sub> after a given period of time or removes a<sub>i</sub> from the set of confirmed alarms depending on the fact that a<sub>i</sub> is detected "present" or "absent";

- the *alarm notifier* process emits warning signals associated with confirmed alarms.

In this paper, the exact way alarms are made present or absent is supposed to be out of scope. This is achieved in another part of the aircraft.

Fig. 3. Deployment of FWS on a platform.

Even though the above two processes interact, they execute independently. So, their activation clocks are *a priori* not strongly correlated. Such a system is particularly well-suited to be described and analyzed with the polychronous model. The specific choice of executing the processes separately on different processors is one possibility among others. Here, it allows us to illustrate the possible design issues resulting from the distribution of a system functionality and how to address them with our proposed methodology.

#### 1.5 Outline

The remainder of this article is organized as follows: Section 2 introduces the synchronous language SIGNAL and its associated multi-clock semantic model. Then, the next sections present our methodology in detail through the design of FWS on a distributed platform. Section 3 is devoted to the first and second steps. It addresses the SIGNAL description of the FWS system, its associated hardware architecture and its correct distribution on the chosen architecture. Section 4 concentrates on the third step. It deals with the modeling of an asynchronous communication mechanism, represented by a FIFO queue that is proved to be correct w.r.t. its expected services. This mechanism is used for the deployment of the FWS system on a specific platform. Section 5 focuses on the last step of our methodology. It addresses clock synchronizability issues in the

deployed model of the FWS system and the automatic code generation. Finally, our proposition is discussed in Section 6 and concluding remarks are given in Section 7.

#### **2** THE SIGNAL LANGUAGE

In order to define the formal semantics of SIGNAL, we introduce the polychronous semantic model in Section 2.1. Then, we give an overview of the language in Section 2.2.

#### 2.1 The polychronous semantic model

We consider the following sets:  $\mathcal{X}$  is a countable set of variables;  $\mathcal{B} = \{ff, tt\}$  is a set of Boolean values where ff and tt respectively denote *false* and *true*;  $\mathcal{V}$  is the domain of operands (at least  $\mathcal{V} \supseteq \mathcal{B}$ ); and  $\mathbb{T}$  is a dense set equipped with a partial order relation noted  $\leq$ , and with a greatest lower bound. The elements of  $\mathbb{T}$  are called *tags*.

We now introduce the notion of observation point.

Definition 1 (observation points): A set of observation points is a set of tags  $\mathcal{T}$  such that: i)  $\mathcal{T} \subset \mathbb{T}$ ; ii)  $\mathcal{T}$  is countable; iii) each pair of tags admits a lower bound in  $\mathcal{T}$ .

The set  $\mathcal{T}$  provides a discrete time dimension that corresponds to the logical instants at which the presence/absence of events can be observed during a system execution. The set  $\mathbb{T}$  provides a continuous (physical) time dimension. So, the mapping of  $\mathcal{T}$  on  $\mathbb{T}$  allows one to move from "abstract" descriptions to "concrete" descriptions in the semantic model.

A *chain*  $C \subseteq \mathcal{T}$  is a totally ordered set which admits a lower bound. The set of chains is denoted by C. For a set of observation points  $\mathcal{T}$ , we denote by  $C_{\mathcal{T}}$  the set of all chains in  $\mathcal{T}$ . The notations min(C) and  $pred_C(t)$  respectively mean the minimum of C and the immediate predecessor of a tag  $t \in C$ .

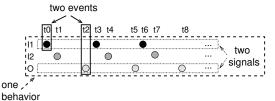

Definition 2 (events, signals and behaviors, FIG. 4):

- An event e on a given set of observation points T is a couple (t, v) ∈ T × V.

- A signal on a given set of observation points *T* is a partial function s ∈ *T* → *V*, associating values with observation points that belong to a chain C ∈ C<sub>T</sub>. The set of signals on *T* is noted S<sub>T</sub>. The domain of s is denoted by tags(s).

- For a given set of observation points  $\mathcal{T}$ , a *behavior* b on  $X \subseteq \mathcal{X}$  is a function  $b \in X \to \mathcal{S}_{\mathcal{T}}$  that associates each variable  $x \in X$  with a signal s on  $\mathcal{T}$ . We denote by  $\mathcal{B}_{\mathcal{T},X}$  the set of behaviors of domain  $X \subseteq \mathcal{X}$  on  $\mathcal{T}$ . The set  $\mathcal{B}_{\mathcal{T}}$  represents the set that contains all the behaviors defined on the union of all the sets of variables on  $\mathcal{T}$ . Finally, we write vars(b) and  $tags(b) = \bigcup_{x \in vars(b)} tags(b(x))$  to respectively denote the domain of b and its associated set of tags.  $\Box$

#### Fig. 4. Behavior, events and signals.

For any behavior *b* defined on  $X \in \mathcal{X}$ , we note  $b_{|X'}$  its projection on a set of variables  $X' \subset X$ . In other words,  $vars(b_{|X'}) = X'$  and  $\forall x \in X', b_{|X'}(x) = b(x)$ . The projection of *b* on the complementary of *X'* in *X* is denoted by  $b_{/X'}$ .

A signal can be seen, in fact, as an *elastic* with ordered *marks* (its tags). If such an elastic is *stretched*, the marks remain in the

same order but new marks may be inserted between stretched marks. If the elastic gets unstretched, the marks become closer to each other, but they still remain in the same order. The same holds for a set of elastics, i.e., a behavior.

Definition 3 (stretching): For a given set of observation points  $\mathcal{T}$ , a behavior  $b_1$  is less stretched than a behavior  $b_2$ , noted  $b_1 \leq_{\mathcal{B}_{\mathcal{T}}} b_2$ , iff there exists a bijection  $f : tags(b_1) \rightarrow tags(b_2)$  following which  $b_1$  and  $b_2$  are isomorphic:

$\begin{aligned} \forall x \in vars(b_1), & f(tags(b_1(x))) = tags(b_2(x)), \\ \forall x \in vars(b_1) \ \forall t \in tags(b_1(x)), \quad b_1(x)(t) = b_2(x)(f(t)), \\ \forall t_1, t_2 \in tags(b_1), \quad t_1 \leq t_2 \Leftrightarrow f(t_1) \leq f(t_2), \\ \text{and such that } \forall C \in \mathcal{C}_{\mathcal{T}}, \quad \forall t \in C \ t \leq f(t). \end{aligned}$

The stretching relation is a partial order on  $\mathcal{B}_{\mathcal{T}}$ . It induces an equivalence relation between behaviors.

Definition 4 (stretch-equivalence): For a given set of observation points  $\mathcal{T}$ , two behaviors  $b_1$  and  $b_2$  are stretch-equivalent, noted  $b_1 \leq b_2$ , iff there exists a behavior  $b_3$  less stretched than  $b_1$  and  $b_2$ , i.e.  $b_1 \leq b_2$  iff  $\exists b_3 \ b_3 \leq_{\mathcal{B}_{\mathcal{T}}} b_1$  and  $b_3 \leq_{\mathcal{B}_{\mathcal{T}}} b_2$ .  $\Box$

The class of equivalence of a behavior following the stretchrelation forms a semi-lattice, which admits a minimal element. We call *strict* behaviors those which are minimal for the stretchrelation on  $\mathcal{T}$ . For a given behavior *b*, the set of all behaviors that are stretch-equivalent to *b* on  $\mathcal{T}$  defines its *stretch-closure* on  $\mathcal{T}$ , noted *b*<sup>\*</sup>.

Definition 5 (stretch-closure of a behavior set): The stretchclosure of a set of behaviors p on a given set  $\mathcal{T}$  of observation points is the set  $p^*$ , which includes all behaviors resulting from the stretch-closure of each behavior  $b \in p$ , i.e.  $p^* = \bigcup_{b \in p} b^*$ .  $\Box$

The stretch-closure allows us to define the following *process* notion, which is a specific set of behaviors:

*Definition 6 (process):* For a given set of observation points  $\mathcal{T}$ , a process p is a stretch-closed set of behaviors, i.e.  $p \in \mathcal{P}(\mathcal{B})$  such that  $p = p^*$ .

We write vars(p) to denote the set of variables of a process p (we say equivalently that p is defined on vars(p)). Every non empty process contains a subset  $p_{\downarrow} \subseteq p$  of *strict* behaviors (for each  $b_1 \in p$ , there exists a unique  $b_2 \in (p)_{\downarrow}$  such that  $b_2 \leq b_1$ ).

The notions presented in this section are sufficient to express the semantics of SIGNAL basic concepts within the polychronous model [37]. In the remainder of the paper, we also use them to characterize some model properties.

#### 2.2 An overview of the language

#### 2.2.1 Basics

SIGNAL [37], [14] is a dataflow relational language that handles unbounded series of typed values  $(x_t)_{t \in \mathbb{N}}$ , called *signals*, implicitly indexed by discrete time, and denoted as x. At any logical instant  $t \in \mathbb{N}$ , a signal may be present or absent: when present, it holds some value; when absent, it holds no value and is denoted by  $\perp$  in the semantic notation. There is a particular type of signal called event. A signal of this type always holds the value true when it is present. The set of instants at which a signal x is present is referred to as its *clock*, noted  $\hat{x}$ . A process is a system of equations over signals that specifies relations between values and clocks of the signals. A program is a process. The whole SIGNAL language relies on the six primitive constructs, presented below, which define *el*ementary processes. Unlike the LUSTRE and LUCID SYNCHRONE languages in which a program expresses a functional dataflow specification, in SIGNAL, a program implicitly expresses constraints on the involved signals, that must be satisfied by their

$\square$

values on the one hand and by their clocks on the other hand (see TABLE. 1).

Instantaneous relations: y:= R(x1,...,xn) where y, x1,...,xn are signals and R is a point-wise n-ary relation/function extended canonically to signals. This construct imposes y, x1,...,xn i) to be simultaneously present, and ii) to hold values satisfying the equation y:= R(x1,...,xn) whenever they occur. Its semantics is the following set of behaviors:

$$\{ \begin{array}{ll} b \in \mathcal{B}_{|y,x_1,\dots,x_n} \mid \\ tags(b(y)) = tags(b(x_1)) = \dots = tags(b(x_n)) = C \in \mathcal{C} \setminus \emptyset \\ \forall t \in C, b(y)(t) = [R](b(x_1)(t),\dots,b(x_n)(t)) \end{array} \}$$

where  $[\![R]\!]$  is a point-wise interpretation of the relation R.

• *Delay*: y:= x \$ 1 init c where y, x are signals and c is an initialization constant. This construct imposes *i*) x and y to be simultaneously present while *ii*) y must hold the value carried by x on its previous occurrence. Its semantics is the following set of behaviors:

$$\begin{array}{ll} \{0_{|x,y}\} \ \cup \ \{ & b \in \mathcal{B}_{|x,y} \mid tags(b(y)) = tags(b(x)) = C \in \mathcal{C} \backslash \emptyset, \\ & b(y)(min(C)) = c, \\ & \forall t \in C \backslash min(C), b(y)(t) = b(x)(pred_C(t)) \end{array} \right\}$$

Undersampling: y:= x when c where y, x, c are signals and c is of Boolean type. This construct imposes *i*) y to be present only when x is present and c holds the value *true*, while *ii*) y must hold the value carried by x at those logical instants. Its semantics is the following set of behaviors:

$$\begin{cases} b \in \mathcal{B}_{|x,y,c} \\ tags(b(y)) = \{t \in tags(b(x)) \cap tags(b(c))|b(c)(t) = tt\} \\ \forall t \in tags(b(y)), b(y)(t) = b(x)(t) \end{cases}$$

• Deterministic merging: z := x default y where z, y, x are signals. This construct imposes *i*) z to be present when either x or y are present while *ii*) z must always hold the value of x uppermost, otherwise it takes the value of y. Its semantics is the following set of behaviors:  $\begin{cases} b \in \mathcal{B}_{|x|}, x_{2}, x_{3} \end{cases}$

$$\begin{array}{l} b \in \mathcal{D}_{|s_1, s_2, s_3|} \\ tags(b(s_3)) = tags(b(s_1)) \cup tags(b(s_2)) = C \in \mathcal{C} \\ \forall t \in C, \ b(s_3)(t) = b(s_1)(t) \text{ if } t \in tags(b(s_1)) \text{ else} \\ b(s_3)(t) = b(s_2)(t) \end{array}$$

- *Composition of processes:* union of the equations defined in processes, leading to the conjunction of the constraints associated with these processes. For a given set of observation points *T*, the composition on *T* of processes p<sub>1</sub> and p<sub>2</sub>, noted p<sub>1</sub> | p<sub>2</sub>, is a process p = ({b | b<sub>|vars(p<sub>1</sub>)</sub> ∈ p<sub>1</sub>, b<sub>|vars(p<sub>2</sub>)</sub> ∈ p<sub>2</sub>})\* and vars(p) = vars(p<sub>1</sub>) ∪ vars(p<sub>2</sub>).

- Restriction (or Hiding): local declarations in a process. The restriction, noted p where x (or p/x for short), of a process p defined on X ⊆ X to a process defined on X \{x}, is defined as the following set of behaviors: ({b<sub>2</sub> | ∃b<sub>1</sub> ∈ p ∧ b<sub>2</sub> = b<sub>1/{x</sub>}})\*.

These constructs are expressive enough to derive new constructs of the language for comfort and structuring.

#### 2.2.2 Clock calculus, endochrony and endo-isochrony

In SIGNAL, clocks are fundamentally the main means to express control-related properties, i.e. synchronizations between signals. They are ordered according to the following relation: a clock  $\kappa_1$  is said to be *greater than* a clock  $\kappa_2$ , which is denoted by  $\kappa_1 \ge \kappa_2$ , if  $\kappa_2$  is included in  $\kappa_1$  in terms of sets of instants. The set of clocks associated with this relation is a lattice.

**Clock calculus.** The purpose of the *clock calculus* [37] is, on the one hand, to determine the existence of a greatest clock, called *master clock*, from which all clocks of a program can be extracted, and on the other hand, to verify the consistency of synchronization relations between signals. Nonetheless, in some programs, such a unique master clock may not exist.

TABLE 1 Clock constraints in primitive constructs.

| constructs        | clock constraints                                                                                         |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| y := f(x1,,xn)    | $\hat{y} = \hat{x}_1 = \ldots = \hat{x}_n$                                                                |  |  |  |  |  |

| y := x \$1 init c | $\hat{y} = \hat{x}$                                                                                       |  |  |  |  |  |

| y := x when b     | $\hat{y} = \hat{x} \cap [b],$<br>$[b] \cup [\neg b] = \hat{b} \text{ and } [b] \cap [\neg b] = \emptyset$ |  |  |  |  |  |

| z := x default y  | $\hat{z} = \hat{x} \cup \hat{y}$                                                                          |  |  |  |  |  |

| P1 P2             | $constraints(p_1) \cap constraints(p_2)$                                                                  |  |  |  |  |  |

| p where x         | constraints(p)                                                                                            |  |  |  |  |  |

In this case, there are several local master clocks (see Section 3.1.2). TABLE. 1 gives the clock properties associated with primitive constructs of SIGNAL (here,  $[b] - \text{resp. } [\neg b] - \text{denotes}$  the set of instants where the Boolean expression b is present and *true* – resp. *false* –). Such properties are automatically inferred by the compiler from any program to be analyzed. A specific option of the compiler enables to generate a file containing these properties under the form of clock relations defined in a SIGNAL program. Clock hierarchies can therefore be extracted from such a program.

SIGNAL allows one to explicitly manipulate clocks through some derived constructs such as the following ones (the equivalent expressions are given with primitive operators):

- Sampling. y:= when b<sup>def</sup> = y := b when b. It expresses the fact that event signal y occurs whenever the signal b is true.

- Clock union. y:= x1 ^+ x2 <sup>def</sup> = y := ^x1 default ^x2. It denotes the set of instants at which at least one signal xi occurs. Clock *intersection* and *difference* are also defined.

- Synchronizer. x1 ^= x2 <sup>def</sup> ( | x := ^x1 = ^x2 |)/x. It means that x1 and x2 have the same clock or are synchronous.

Endochrony and endo-isochrony: key properties for program distribution. The safe distribution of SIGNAL programs is possible thanks to two fundamental notions, *endochrony* and *endo-isochrony*, which have been formally defined in [37], [9]. In this paper, we only recall them informally and put them to work on our case study introduced in Section 1.4.

An endochronous program p is a program that can be executed in an environment, which only provides p with the values of its inputs, without any information about their status (present or absent). p is able to reconstruct a unique synchronous behavior from any external (asynchronous) input flow of values. It is insensitive to external propagation delays. From the viewpoint of clocks, such a program holds a master clock  $\kappa$  that plays the role of its activation clock. All the other clocks of p are necessarily defined recursively from  $\kappa$ . They are smaller than  $\kappa$  following the partial order  $\geq$ . The global clock hierarchy in p therefore forms a *tree* where the root node represents the master clock of p (see Section 3.1.1). Given any SIGNAL program p, the compiler is able to check whether or not p is endochronous. An endochronous program is deterministic: for the same functional input values it yields the same functional output values whatever the external propagation delays are. The elementary processes defined by the instantaneous relations and delay primitive constructs are examples of very simple endochronous programs. All signals involved in these processes have the same clock, which is also the master clock. On the contrary, the elementary processes defined by the undersampling and merging primitive constructs are not endochronous programs since there is no master clock from which the clocks of involved signals can be inferred in such a process. A more complex example of non endochronous program is shown in Section 3.1.2.

The *isochrony* property [9] is used as a criterion under which the synchronous composition of a pair of processes  $p_1$ and  $p_2$  is equivalent to their asynchronous composition (i.e. involving "*send/receive*" like communications). It means that the order of the messages exchanged synchronously by  $p_1$ and  $p_2$  is always preserved when exchanged asynchronously. Thus,  $p_1$  and  $p_2$  can be safely deployed on GALS architectures. So, isochrony is an interesting property when one needs to describe asynchronous behavior while using the synchronous (multi-clock) model. A very similar theoretical result can be found in [41], where the authors address the functional equivalence of asynchronous composition and synchronous composition with bounded and unbounded FIFO channels, within the polychronous model. In our methodology, we rather consider a more constructive version of isochrony, called *Endo-isochrony*.

Endo-isochrony [37] requires that both  $p_1$  and  $p_2$  are endochronous each, as illustrated in Section 3.1.2; and imposes to their communicating part (i.e. the process defined by the restriction on their common variables) to be endochronous as well. Endo-isochrony is a sufficient criterion but not necessary to have a pair of isochronous processes. It is a stronger criterion. However, its advantage is that it permits to deal with the isochrony property of  $p_1$  and  $p_2$  using the compiler by checking the endochrony of the different sub-parts of the composition, hence making things more pragmatic. Endo-isochrony is illustrated in Section 3.1.2.

#### 2.2.3 A rich tool-set for validation

The SIGNAL design environment, POLYCHRONY [14], offers a compiler and a model-checker that support the trustworthy and pragmatical design approaches for safety-critical systems.

Two kinds of functional properties are distinguished about SIGNAL programs: *invariant* properties, e.g. consistency of clock constraints, endochrony of a program, and dynamical properties, e.g., reachability, liveness (see Section 4.2). The compiler itself statically addresses invariant properties. Dynamical properties are addressed by the SIGALI model checker [40], which relies on the theory of polynomial dynamical systems. Roughly speaking, a SIGNAL program is abstracted into a system of polynomial equations representing a symbolic automaton over the set  $\mathbb{Z}/_{3\mathbb{Z}} = \{-1, 0, 1\}$ . This encodes all the possible status of any Boolean signal: 1 for true, -1 for false, and 0 for  $\perp$ . For a non-Boolean signal, only the fact that this signal is present (whatever its value is) or absent is encoded. The presence is denoted by 1, and the absence by 0. It must be noted that this "translation" fully takes into account information about Boolean variables (values and clocks), whereas for non-Boolean signals, information on values are lost. Therefore, it is important that a SIGNAL program that will be analyzed by SIGALI is specified as much as possible using Boolean variables, since reasoning capabilities capture only synchronization and logic properties.

Finding a Boolean abstraction for a program is always possible. However, this abstraction may sometimes be not meaningful enough to adequately capture the properties of interest. Typically, some numerical properties require more powerful abstraction domains such as intervals [22] or polyhedra (which may lead to complex analyses). These possible extensions have been studied previously in the SIGNAL compiler in order to improve its analysis capability. Nevertheless, with SIGALI, the  $\mathbb{Z}/_{3\mathbb{Z}}$  ternary abstract encoding is necessary. In general, a good

way to obtain analyzable programs in this context consists in defining Boolean signals, usable for characterizing the relevant properties. In most cases, when such properties concern the control of a program behavior, i.e. synchronization constraints, one can easily find a direct Boolean encoding.

#### **3** SPECIFICATION AND CORRECT DISTRIBUTION

#### 3.1 Model of the FWS functionality

Given an application, its functionality is first described as a hierarchical SIGNAL process  $p = p_1 \mid ... \mid p_n$ . Here,  $p_1$  and  $p_2$  denote the alarm notifier and manager processes (Section 3.1.1) while p represents the FWS system (Section 3.1.2).

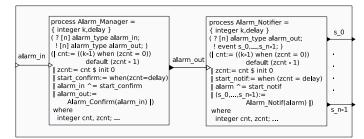

#### 3.1.1 Alarm manager and notifier processes

FIG. 5 gives an excerpt of the models of the processes composing FWS. Both are defined in a very similar way. So, we only present one of them: Alarm\_Manager. The interface signals alarm\_in and alarm\_out, at lines 3 and 4, are both declared as arrays of alarms. In SIGNAL, the input and output signals are introduced by the symbols "?" and "!" respectively. Here, their dimension is some fixed integer constant n. The type of an alarm, called alarm\_type, is a structured type with two fields: pres (resp. conf) of Boolean type that is *true* when an alarm is "present" (resp. "confirmed") and *false* when an alarm is "absent" (resp. "removed").

The body of the process is composed of five equations, from line 5 to line 11. The local signals cnt, zcnt and start\_confirm are used to specify when the process confirms alarms in equations at lines 5 to 8. The signal cnt plays the role of a *counter* of logical instants. It is set to k-1 whenever its previous value zcnt becomes zero; otherwise its previous value is decremented by one. The static parameter k at line 2 can be somehow seen as an initialization period value of cnt. The signal start\_confirm denotes the logical instants at which a confirmation begins, described by equations at lines 8 and 9. It occurs when the counter value reaches some amount of time denoted by delay within each cycle.

Note that the sub-process Alarm\_Confirm, defined at line 15 and invoked at line 10, to produce the output alarm\_out, uses a derived construct of SIGNAL, referred to as *array of processes*, that enables to describe instantaneous iterations [14].

From the above equations and according to TABLE. 1, we can deduce the following system of clock constraints associated with the process Alarm\_Manager (for a signal s, we denote by *clk\_s* its associated clock):

$$clk\_cnt = [zcnt = 0] \cup clk\_zcnt \quad (lines 5 \& 6)$$

$$clk\_zcnt = clk\_cnt \quad (line 7)$$

$$clk\_start\_confirm = [zcnt = delay] \quad (line 8) \quad (1)$$

$$clk\_alarm\_in = clk\_start\_confirm \quad (line 9)$$

$$clk\_alarm\_out = clk\_alarm\_in \quad (lines 10 \& 19)$$

After reductions of the above system (1), we obtain the following clock hierarchy:

$$[zcnt \neq delay] \quad [zcnt = delay] \equiv clk\_start\_confirm \equiv clk\_alarm\_in \equiv clk\_alarm\_out$$

We can see that the master clock is the one of cnt, which is the same for zcnt. The other clocks of the process are defined following a partitioning of the values of zcnt w.r.t. the value of delay. As a result, the process Alarm\_Manager is

```

process Alarm_Manager =

process Alarm_Notifier =

1

2

{ integer k,delay }

{ integer k,delay }

3

( ? [n] alarm_type alarm_in;

? [n] alarm_type alarm;

4

! [n] alarm_type alarm_out; )

! event s_0,...,s_n-1; )

(| cnt:= ((k-1) when (zcnt = 0))

(| cnt:= ((k-1) when (zcnt = 0))

5

default (zcnt - 1)

6

default (zcnt - 1)

7

zcnt:= cnt $ init 0

zcnt:= cnt $ init 0

start_confirm:= when(zcnt = delay)

start_notif:= when (zcnt = delay)

8

9

alarm_in ^= start_confirm

alarm ^= start_notif

(s_0,...,s_n-1):= Alarm_Notif(alarm)

10

alarm_out:= Alarm_Confirm(alarm_in)

11

)

12

where

where

13

integer cnt, zcnt;

integer cnt, zcnt;

14

event start_confirm;

event start_notif;

15

process Alarm_Confirm =

process Alarm_Notif =

16

( ? [n] alarm_type in;

( ? [n] alarm_type alarm;

17

! [n] alarm_type out; )

! event s_0,...,s_n-1; )

18

(| array i to n-1 of

(| s0:= when alarm[0].conf

19

out[i].conf := in[i].pres

. . .

20

end

s n-1:= when alarm[n-1].conf

21

);

);

22

end;

end;

```

Fig. 5. Excerpt of the SIGNAL code of alarm manager (left) and notifier processes (right).

endochronous (hence deterministic). In a similar way, we prove that the process Alarm\_Notifier is also endochronous. More generally, the SIGNAL compiler allows one to automatically check the endochrony property of a process based on this technique and to generate an associated simulation code.

#### 3.1.2 Global model of the FWS system

| 1  | process FW_System =                  |

|----|--------------------------------------|

| 2  | {    integer k1,k2,d1,d2    }        |

| 3  | ( ? [n] alarm_type alarm;            |

| 4  | ! event s_0,,s_n-1; )                |

| 5  | (  tmp:= Alarm_Manager{k1,d1}(alarm) |

| 6  | (s_0,,s_n-1):=                       |

| 7  | Alarm_Notifier{k2,d2}(tmp)           |

| 8  |                                      |

| 9  | where                                |

| 10 | <pre>[n] alarm_type tmp;</pre>       |

| 11 | process Alarm_Manager =;             |

| 12 | process Alarm_Notifier =;            |

| 13 | end;                                 |

Fig. 6. Excerpt of the SIGNAL code of FWS.

The process depicted by FIG.6 represents the FWS model. It takes as input a collection of alarms represented by alarm (line 3), and produces as outputs the signals denoted by s\_0, ..., s\_n-1. These outputs are generated by Alarm\_Notifier.

The equations from lines 5 to 7 define the interaction between the concurrent processes in the FWS system: the input of process Alarm\_Notifier are the output of process Alarm\_Manager. This transfer of data is realized via the local signal tmp. It means that the two processes must agree on the set of specific instants at which this transfer is possible.

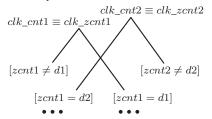

Let us analyze the clock properties induced by the definition of process FW\_System. We obtain the following two-rooted clock hierarchy:

We clearly distinguish the clock trees associated with Alarm\_Manager and Alarm\_Notifier. There is no master clock because the clocks of the sub-processes (clk\_cnt1 for Alarm\_Manager and clk\_cnt2 for Alarm\_Notifier) are included in none of each other. However, they share common instants at which the alarm transfer is done between the manager and the notifier processes. Such instants are defined only when both zcnt in Alarm\_Manager and zcnt in Alarm\_Notifier are respectively equal<sup>1</sup> to d1 and d2. Such a requirement appears under the form of a clock constraint generated by the SIGNAL compiler. The corresponding code which is automatically produced ("- force" option of the compiler) from such a model contains exception messages that are thrown whenever the clock constraints are not satisfied during code execution.

In such a situation, it means that either the environment of the two concurrent processes is able to guarantee that they can synchronize at the required specific logical instants, and the model will execute as expected; or it is not possible, and the output of the whole system model is undefined whenever the clocks of the two processes fail to agree. In SIGNAL, the special construct called assert offers the way to define assumptions in programs [14]. It could be used here to meet the requirement on the concurrent execution of Alarm\_Manager and Alarm\_Notifier processes.

On the other hand, one can think of another specification of the FW\_System model in which the confirmed alarm values tmp are transferred via a "clock-less" memory, which is made available whenever a process needs to make an access to this memory. This is obtained very easily by introducing a new equation in the body of FW\_System, which defines a local signal tmp\_mem as follows: tmp\_mem := (var tmp). Then, instead of putting tmp as input for Alarm\_Notifier at line 7 in FIG. 6, we consider tmp\_mem. The var operator allows one to memorize the value of tmp in tmp\_mem [14]. The clock of tmp\_mem is the one of the context in which it is used, i.e., the memorized value is available whenever required.

In this second version of the FW\_System model, there is

1. Note that zcnt in Alarm\_Manager and zcnt in Alarm\_Notifier are different instances; they have different clocks and evolve according to two different logical time scales.

no longer clock constraints on the specific instants at which the concurrent processes must exchange information. Their associated master clocks are completely independent, with a possible empty set of common instants. In this case, the compiler generates no clock constraints and automatically produces a code without any exception message.

A very interesting feature of the FW\_System model is that it satisfies the endo-isochrony property: first, Alarm\_Manager and Alarm\_Notifier models are both endochronous; second, their communicating part which consists of the single signal tmp (see FIG. 6) is trivially endochronous. Indeed, a single signal yields a clock hierarchy with only one clock node, which consequently forms a clock tree. The clock hierarchy associated with FW\_System typically illustrates the endo-isochrony of a pair of processes. In particular, the synchronous communication between Alarm\_Manager and Alarm\_Notifier via tmp can be equivalently replaced by an asynchronous communication while still preserving the semantics of the FW\_System model.

At this stage, some preliminary verification can be done on the FW\_System model in order to make sure that it conforms to its expected specification requirements. Typically, one may check the absence of null clocks in the defined model using the compiler. The presence of such clocks denote a possible absence of reactions during the execution of the program. This is often undesirable for reactive systems.

#### 3.2 Architecture model and manual distribution

The hardware architecture on which the previous application functionality model will be mapped is now defined. For the sake of simplicity, only processors are represented. Concretely, each processor is graphically modeled as an empty box.

Afterwards, one can proceed to the mapping of the application functionality on the hardware architecture in the POLYCHRONY graphical user interface. A SIGNAL code can be duplicated in different processor boxes; so, code replication is allowed. From this mapping, a new description of the system denoted by  $p' = p'_1 | \dots | p'_m$  is obtained, which reflects the target hardware architecture (*m* denotes the number of processors). FIG. 7 illustrates the distribution of the FWS model on a two-processors architecture, i.e. m = 2.

Fig. 7. Graphical distributed model of the FWS system.

We can notice that the sub-processes  $p'_j$  may not ne necessarily endochronous: after the mapping,  $p'_j$  can be obtained from the composition of different sub-processes  $p_i$  characterized by different clock trees without a common root clock.

#### 3.3 Automatic transformations

Let us consider the model p' resulting from the mapping of the application functionality on the processors. The main purpose

is to transform the process p' so that: *i*) p' fully preserves the functional semantics of p and *ii*) the sub-processes  $p'_j$  become endochronous and p' itself becomes endo-isochronous.

So, each process  $p'_i$  is compiled modularly in the context of p: from the clock hierarchy of p, the clock hierarchy of  $p'_i$  is transformed in such a way that it becomes a clock tree, i.e.  $p'_i$  becomes endochronous. For that, Boolean interface signals are used (each root node in a clock hierarchy of a non endochronous process is associated with a Boolean signal, and all these signals are made synchronous). On the other hand, some transformations are performed in order to render the communication part endochronous between the endochronous processes  $p'_i$ . For that, additional communicating signals are inserted between processes, which enable each process  $p'_i$  to receive all information it requires to execute. The result of these transformations is carried out automatically on the graphical representation of p' within the POLYCHRONY editor. In the obtained transformed process, denoted by p'', the information exchanges between processes are described by instantaneous communications. Here again, possible verification techniques can be applied to p'' in order to ensure that it still preserves the functional properties of *p*.

For our FWS system model, all the above transformations are not necessarily required since FW\_System is already endoisochronous as shown before. The only effect of these transformations is the automatic insertion of the communicating ports on processor boxes and the connections between these ports.

#### 4 DEPLOYMENT ON SPECIFIC PLATFORMS

In order to refine the descriptions obtained from the previous steps of the methodology, a set of predefined components is proposed, which is usable to instantiate various aspects of the system: asynchronous communication mechanisms such as the FIFO buffer modeled in this paper, execution supports (e.g., tasks and processes), system-level primitives for task management as well as for synchronization and inter-task communication services (e.g. the APEX service models [23]). These components have been modeled in SIGNAL and are grouped in a library available in the POLYCHRONY platform.

#### 4.1 Design of a library of components

We consider the FIFO queue presented in [21], to show how asynchronous communication mechanisms can be defined in SIGNAL, and proved to be correct. This queue is well adapted as mechanism to model a message buffer on which send/receive requests can be achieved by endo-isochronous processes. In addition, in the architecture level, it will be easily extended to model a bus. Compared to [21], here we give a more complete presentation of the design and analysis. A first model of FIFO queue is presented (basic\_ FIFO); then, a more constrained version (safe\_ FIFO) is defined from the first one and its key properties are checked.

#### 4.1.1 A basic FIFO queue

We call *basic* FIFO, a message queue that works as follows.

On a *write request*, the incoming message is inserted in the queue regardless of its size limit. When the queue was previously full, the oldest message is lost. The other messages are shifted forward, and the incoming one is inserted in the queue. On a *read request*, there is an outgoing message whatever the queue status is. When it was previously empty, two situations are distinguished: if there is not yet any written message,

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | <pre>process basic_FIFO = { type msg_type; integer size; msg_type def_msg; } ( ? msg_type msg_in; event access_clock;   ! msg_type msg_out; integer nbmsg; boolean OK_write, OK_read; ) (  nbmsg := ((prev_nbmsg+1) when (^msg_in) when OK_write)</pre> |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|                                                                                                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

Fig. 8. Model of the basic FIFO and an execution trace ( $msg_type$ , size and def\_msg are respectively integer, 2 and -1).

$(\forall t$

an arbitrary message called *default message* is returned; else the outgoing message is the message that has been read last. Furthermore, for simplicity we suppose that simultaneous write/read requests on the queue never occur.

The SIGNAL model corresponding to the basic FIFO is given in FIG. 8. It is defined as a SIGNAL process, represented by the keyword process (line 1). The static parameters msg\_type, size and def\_msg, declared at line 2, respectively denote the type of messages, the size limit of the queue, and the default message value. The input signals msg\_in and access\_clock (line 3), are respectively the incoming message (its presence denotes a write request), and the queue access clock (i.e. instants of read/write requests). The output signals (line 4), are msg\_out, nbmsg, OK\_write and OK\_read. They respectively represent the outgoing message, the current number of messages in the queue, and conditions for writing and reading.

Now, we can take a look at the meaning of the statements in the process body. Let us begin with the equation at line 7; it defines the local signal prev\_nbmsg, which denotes the previous number of messages in the queue. This signal is used in equations at lines 8 and 9 to define respectively when the queue can be "safely" written (the size limit is not reached), and read (there is at least one message received). This is the meaning of the signals OK\_write and OK\_read.

The statement at lines 5 and 6 expresses how the current number of messages is calculated. The previous value of this number is incremented by one on a write request when the queue was not full. It is decremented by one on a read request when the queue was not empty. Otherwise, it remains unchanged. The equation at line 14 states that the value of nbmsg is defined whenever there is a request on the queue.

The equation at line 10 defines the message queue. The signal queue is an array of dimension size that contains the size latest values of msg\_in (expressed by the window operator). The cell operator makes the signal queue available when access\_clock is present. The semantics of these derived constructs is as follows:

• Sliding windows. In y:= x window k init y\_init, the signal y is an array of size  $k \ge 1$  whose elements have the

same type as signal x; and y\_init is an array of dimension  $k' \geq k - 1$ , containing initialization values. This equation defines a sliding windows on x, of constant size k such that:

$$\geq 0) \quad \left( (t+i \geq k) \Rightarrow (y_t[i] = x_{t-k+i+1}) \lor \\ (1 \leq t+i < k) \Rightarrow (y_t[i] = y_{init}[t-k+i+2]) \right)$$

- Memory. The expression y := x cell b init c enables to *memorize* the values of the signal x. It is defined as:

- (| y := x default (y \$ 1 init c)

The signal y takes the value of x when x is present. Otherwise, when x is absent and the signal b is present and holds the value true, y memorizes the latest value of x. When b is present and *true* before the first occurrence of x, y is initialized with the constant c. The clock of y is the union of  $\hat{x}$  and [b].

Finally, the statement at lines 11 and 12 means that on a read request (i.e. at the clock ^msg\_out), the outgoing message is either the previous one if the FIFO is empty (defined at line 13), or the oldest message in the queue.

#### 4.1.2 A safe FIFO queue

In the model depicted in FIG. 9, the interface is slightly different from that of basic FIFO. The new input signal get mess denotes a read request. The signal nbmsg is local.

The statement at line 9 defines the access clock as the union of instants at which read/write requests occur. Equations at lines 10 and 11 specify the safe access to the queue in basic\_FIFO. The process call at lines 12, 13 and 14 has the local signal new\_msg\_in as input. This signal is defined only when basic\_FIFO was not full (line 10). The equation at line 11 expresses that on a read request, a message is enqueued only when basic\_FIFO was not empty. In the trace in FIG. 9, the same parameters as for basic\_FIFO are considered.

Through the above modeling approach, we observe that modularity and reusability are key features of the SIGNAL programming. They favor component-based design.

FIG. 10 shows the FWS model in which the communication between Alarm\_Manager and Alarm\_Notifier is achieved via the safe\_FIFO model. Note the modification in the Alarm\_Notifier at line 27 where the new output signal get\_msg denotes read requests on safe\_FIFO.

| 1<br>2           | <pre>process safe_FIFO = { type msg_type;</pre> |   |         |         |                   |                |                |        |   |                   |   |

|------------------|-------------------------------------------------|---|---------|---------|-------------------|----------------|----------------|--------|---|-------------------|---|

| 3                | integer size;                                   |   |         |         |                   |                |                |        |   |                   |   |

| 4                | <pre>msg_type def_msg; }</pre>                  |   |         |         |                   |                |                |        |   |                   |   |

| 5                | ( ? msg_type msg_in;                            |   |         |         |                   |                |                |        |   |                   |   |

| 6                | event get_msg;                                  |   |         |         |                   |                |                |        |   |                   |   |

| 7                | ! msg_type msg_out;                             |   |         |         |                   |                |                |        |   |                   |   |

| 8                | boolean OK_write, OK_read; )                    |   |         |         |                   |                |                |        |   |                   |   |

| 9                | (  access_clock := msg_in ^+ get_msg            |   |         |         |                   |                |                |        |   |                   |   |

| 10               | new_msg_in := msg_in when OK_write              |   |         |         |                   |                |                |        |   |                   |   |

| 11               | msg_out ^= get_msg when OK_read                 |   |         |         |                   |                |                |        |   |                   |   |

| 12               | (msg_out, nbmsg, OK_write, OK_read):=           |   |         |         |                   |                |                |        |   |                   |   |

| 13               | <pre>basic_FIFO{msg_type,size,def_msg}</pre>    |   |         |         |                   |                |                |        |   |                   |   |

| 13               |                                                 | 1 |         |         |                   |                |                |        |   |                   | ſ |

|                  | (new_msg_in,access_clock)                       |   |         |         |                   |                |                |        |   |                   |   |

| 15               | )                                               |   |         |         |                   |                |                |        |   |                   |   |

| 16               | where                                           |   |         |         |                   |                |                |        |   |                   |   |

| 17               | use basic_FIFO; event access_clock;             |   |         |         |                   |                |                |        |   |                   |   |

| 18               | integer nbmsg; msg_type new_msg_in;             |   |         |         |                   |                |                |        |   |                   |   |

| 19               | end;                                            |   |         |         |                   |                |                |        |   |                   |   |

| msg_in<br>get ms | ı :<br>sg :                                     |   | 4<br>⊥  | 6<br>   | $\frac{\perp}{t}$ | $_{t}^{\perp}$ | $_{t}^{\perp}$ | 5<br>1 | 7 | $\frac{\perp}{t}$ |   |

|                  | it :                                            |   | $\perp$ | $\perp$ | 4                 | 6              |                |        | Ţ |                   |   |

|                  | lte :                                           |   | t       | t       | f                 | t              | t              |        | t | f                 |   |

| OK rea           |                                                 | f | f       | ť       | ť                 | t              | f              | f      | ť | ť                 |   |

| 011_100          |                                                 | J | J       | ŀ       | r                 | r              | J              | J      | r | ŀ                 |   |

Fig. 9. Model of the safe FIFO with an execution trace.

```

process FW System =

1

2

{ integer k1,k2,d1,d2 }

3

( ? [n] alarm_type alarm;

4

! event s_0,...,s_n-1; )

5

(| tmp:= Alarm_Manager{k1,d1}(alarm)

(alarm_conf,OK_write,OK_read):=

6

7

safe_FIFO{[n] alarm_type,s,a_init}

8

(tmp, get_msg)

9

(get_msg, s_0,...,s_n-1):=

Alarm_Notifier{k2,d2}(alarm_conf)

10

11

)

12

where

use safe_FIFO; event get_msg;

13

14

[n] alarm_type tmp,alarm_conf;

15

boolean OK_write, OK_read;

16

constant integer s =...;

17

constant [n] alarm_type a_init =...;

18

process Alarm_Manager = ...;

process Alarm_Notifier =

19

{ integer k,delay }

20

21

( ? [n] alarm_type alarm;

22

! event get_msg, s_0,...,s_n-1; )

23

(|cnt:=((k-1) when (zcnt = 0)))

24

default (zcnt - 1)

25

zcnt:= cnt $ init 0

26

start_notif:= when (zcnt = delay)

27

get_msg := when start_notif

28

(s_0,...,s_n-1):= Alarm_Notif(alarm)

29

30

where

31

integer cnt, zcnt; event start_notif;

32

process Alarm_Notif =

33

( ? [n] alarm_type alarm;

34

! event s_0,...,s_n-1; )

35

(| s0:= when alarm[0].conf

36

. . .

37

s_n-1:= when alarm[n-1].conf

38

);

39

end;

40

end;

```

Fig. 10. Excerpt of the FWS model including safe\_FIFO.

#### 4.2 Ensuring the reliability of components

#### 4.2.1 Safety and fairness

To check the properties of the safe\_FIFO process, we consider an abstraction based on its *state variables*, i.e. signals defined by *delay* or *memory* operators in the process. These signals feature the dynamics of the system defined by the process. Here, the state variables are nbmsg, queue and prev\_msg\_out (defined in basic\_FIFO). They entirely reflect the dynamics of the equation system associated with safe\_FIFO. Let us represent the state of this system by  $\sigma$ . When the queue is full (resp. empty), the value of  $\sigma$  is noted *full* (resp. *empty*); otherwise it is equal to *none*. Let [safe\_FIFO] denote the set of behaviors associated with safe\_FIFO and *b* a behavior that belongs to this set, we address the following important properties of the safe\_FIFO in order to guarantee its robustness:

Property 1 (safe read requests): The safe\_FIFO queue never delivers an output message on a read request whenever it is empty (and its state remains unchanged):  $\forall b \in [safe_fifo],$  $\mathcal{T} = tags(b(get_msg)),$

$$t \in \mathcal{T} \land t \neq min(\mathcal{T}) \land b(\sigma)(pred_{\mathcal{T}}(t)) = empty$$

$$\Rightarrow b(\sigma)(t) = b(\sigma)(pred_{\mathcal{T}}(t)) = empty \land$$

$$t \notin tags(b(msg_out))$$

(2)

Property 2 (safe write requests): The safe\_FIFO queue never accepts an input message on a write request whenever it is full (and its state remains unchanged):  $\forall b \in [safe_fifo], T = tags(b(msg_in)),$

$$t \in \mathcal{T} \land t \neq min(\mathcal{T}) \land b(\sigma)(pred_{\mathcal{T}}(t)) = full \Rightarrow b(\sigma)(t) = b(\sigma)(pred_{\mathcal{T}}(t)) = full \land t \notin tags(b(new_msg_in))$$

(3)

We recall that the signal new\_msg\_in, which is defined in the safe\_FIFO process, at line 10, denotes incoming messages that are effectively enqueued.

Property 3 (fair read requests): A message can always be read from the safe\_FIFO queue, whenever it is not empty:  $\forall b \in [safe_fifo], T = tags(b(get_msg)),$

$$t \in \mathcal{T} \land t \neq \min(\mathcal{T}) \land b(\sigma)(pred_{\mathcal{T}}(t)) \neq empty$$

$$\Rightarrow t \in tags(b(msg_out))$$

(4)

Property 4 (fair write requests): A message can always be written in the safe\_FIFO queue, whenever it is not full:  $\forall b \in [safe_fifo], T = tags(b(msg_in)),$

$$t \in \mathcal{T} \land t \neq min(\mathcal{T}) \land b(\sigma)(pred_{\mathcal{T}}(t)) \neq full \Rightarrow t \in tags(b(new\_msg\_in))$$

(5)

The values of  $\sigma$ , the state of the system corresponding to safe\_FIFO, can be defined by considering the signals OK\_write and OK\_read. The definition of these signals is itself based on the current number of enqueued messages, represented by nbmsg. Thus,  $\sigma$  can be characterized, using nbmsg, as follows:  $\forall b \in [safe_FIFO] \forall t \in tags(b)$ ,

$$\begin{aligned} b(\sigma)(t) &= full & \Leftrightarrow & b(nb_msg)(t) = size \\ b(\sigma)(t) &= empty & \Leftrightarrow & b(nb_msg)(t) = 0 \\ b(\sigma)(t) &= none & \Leftrightarrow & 0 < b(nb_msg)(t) < size \end{aligned}$$

(6)

Since SIGALI does not address numerical properties, we must also find a Boolean encoding (or abstraction) for nbmsg.

#### 4.2.2 Abstraction and verification by model-checking

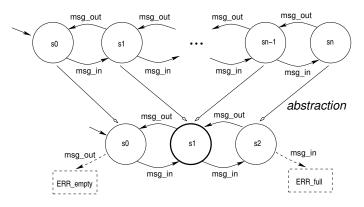

As shown in FIG. 11, a *n*-FIFO queue can be represented by an automaton with (n + 1) states, where a state denotes the current number of messages in the queue. For the sake of simplicity, we consider a 2-FIFO queue since all possible relevant configurations can be addressed. So, the result remains valid for any bounded *n*-FIFO queue where n > 2.

Fig. 11. Abstraction of a *n*-FIFO by a 2-FIFO with error states.

The automaton illustrated in FIG. 11 represents a behavior abstraction of a *n*-FIFO queue by a 2-FIFO queue. It relies on the behavioral isomorphism between both FIFO queues, which can be trivially observed. A state *sk* (represented by a circle) denotes that the queue contains *k* messages, i.e.  $\forall k \in \{0, 1, 2\}$ :

$$(nbmsg = k \Rightarrow sk = true) \land (nbmsg \neq k \Rightarrow sk = false)$$

The state *s*0 represents the initial state. Labels *msg\_in* and *msg\_out* are respectively write and read requests. Two special states (represented by rectangles) have also been added. They characterize "illegal" accesses to the queue: *ERR\_empty* is reached on an attempt to read an empty queue, and *ERR\_full* is reached when overwriting a full queue. They are also encoded by Boolean variables. Automata are very easy to specify in SIGNAL. For instance the state *s*0 and its associated transitions are defined as follows:

| 1 | ( s0:= (true when prev_s1 when (^msg_out)) |

|---|--------------------------------------------|

| 2 | default (false when prev_s0 when           |

| 3 | (msg_in ^+ msg_out)) default prev_s0       |

| 4 | prev_s0 := s0\$1 init true  )              |

All the other states are specified in a similar way. It follows the definitions of signals OK\_write and OK\_read below:

| 1 | ( OK_write:= false when (prev_err_full or |

|---|-------------------------------------------|

| 2 | prev_s2) default true                     |

| 3 | OK_read:= false when (prev_err_empty or   |

| 4 | prev_s0) default true  )                  |

The first equation means that a write request is not authorized when there are already two messages in the 2-FIFO queue (prev\_s2 is *true*), or when the queue has been overloaded previously (prev\_err\_full is *true*); otherwise it can be accepted. In a same way, the other statement specifies when a read request is legal.

The signals s0, s1, s2, ERR\_empty, ERR\_full, OK\_write and OK\_read are synchronized with access\_clock.

The reachability of "error" states (i.e. safety properties) is concretely checked with SIGALI by considering the script given in [21].

To verify properties 3 and 4, we consider *observers*, represented by Boolean state variables. We have to show that

these variables are always *true*. Let obs4 and obs3 denote respectively the observers for Properties 4 and 3.

- Property 4 is described as follows:

- On a write request (denoted by the presence of msg\_in), when the queue is either in s0 or s1; the signal obs4 carries the value *true* if the message is actually written into the queue (i.e. new\_msg\_in is present), else obs4 is *false*.

- Otherwise, obs4 keeps its previous value.

The corresponding SIGNAL code is:

```

1 (|actual_w:= true

2 when(^new_msg_in) default false

3 |obs4:= actual_w when(z_s0 or z_s1)

4 when(^msg_in) default z_obs4

5 |z_obs4 := obs4 $ 1 init true |)

```

The Boolean actual\_w denotes the fact that a message is actually inserted in the queue.

• In a similar way, Property 3 is encoded by the following SIGNAL code:

Here also, all the new variables have the same clock as the signal access\_clock. Then, the fairness properties can be checked as shown in [21].

#### 4.2.3 Queueing order preservation

1

2 3

45

We have to prove that the safe\_FIFO queue actually preserves the arrival order of enqueued messages. The idea consists in considering the flow of input messages in the call to basic\_FIFO at line 13 in FIG. 9. Such a flow corresponds to that of signal new\_msg\_in. Indeed, only the values of this signal are taken into account and read afterwards. We therefore need to verify the following property:

Property 5 (order preservation):

- (E<sub>1</sub>): the order of values present in the input flow is preserved by the definition of the message queue: ∀b ∈ [[safe\_FIFO]] ∀v, v' ∈ V s.t. ∃t, t' with v = b(new\_msg\_in)(t), v' = b(new\_msg\_in)(t') and for i, i' the respective indices of v and v' in queue<sup>2</sup>, the following holds: t ≤ t' ⇒ i ≤ i'.

- (E<sub>2</sub>): the order of values in the output flow is the same in the message queue: ∀b ∈ [safe\_FIF0] ∀v, v' ∈ V t.q. ∃t, t' with v = b(msg\_out)(t), v' = b(msg\_out)(t') and i, i' as above, the following holds: i ≤ i' ⇒ t ≤ t'.

The order preservation property is specifically related to the properties of specific SIGNAL constructs used in the FIFO queue model. A proof of this property is in Appendix Section.

#### 4.3 Use of safe\_FIFO in architecture model

We have shown that the above FW\_System model can be safely described with asynchronous communication mechanisms between its concurrent processes Alarm\_Manager and Alarm\_Notifier. Now, let us imagine a deployment of this system on a given architecture as illustrated in FIG. 3.

In this architecture, there are two processors *Processor 1* and *Processor 2* that communicate via a bus called *Bus*. The main feature of such an architecture that is taken into account in our

2. Here, the enqueued values are assumed to be inserted from right to left in the array defined with the window operator.

models is clock constraint. Each of the three components holds its own activation clock, which is different from those of others. Let us denote by  $\kappa_{p1}$ ,  $\kappa_b$  and  $\kappa_{p2}$  the clocks corresponding respectively to *Processor 1*, *Bus* and *Processor 2*.

The bus model considered here is obtained from the previous safe\_FIFO model on top of which a master clock is defined (see FIG. 12). This clock  $\kappa_b$  is represented by ^cnt in the Bus process. It enables to define the instants at which incoming and outgoing transferred data are respectively accepted and delivered by the bus. This is specified through the signal enable\_in\_out at line 11. The static parameter  $rw_per$  denotes the period at which a read/write request is accepted by the bus. Its value belongs to the interval 0..k-1 (note that k is also a static parameter in Bus).

```

process Bus =

1

2

{ type msg_type; integer size;

3

msg_type def_msg; integer k, rw_per;}

4

( ? integer msg_in;

5

event get_msg;

6

! integer msg_out;

7

boolean OK_write, OK_read;

(| cnt:= ((k-1) when (zcnt = 0))

8

9

default (zcnt - 1)

zcnt:= cnt $ init 0

10

11

enable_in_out:= when(zcnt = rw_per)

12

msg_in ^+ get_msg ^=

when enable_in_out

13

14

(msg_out, OK_write, OK_read):=

15

safe_FIFO{msg_type,size,def_msg}

16

(msg_in, get_msg)

17

18

where

19

use safe_FIFO; integer cnt, zcnt;

20

event enable_in_out;

21

end;

```

Fig. 12. A bus model in SIGNAL.

On the other hand, we assume that the Alarm\_Manager and Alarm\_Notifier processes run at the frequency of their allocated processors: the master clock of Alarm\_Manager is the same as  $\kappa_{p1}$  while the master clock of Alarm\_Notifier is the same as  $\kappa_{p2}$ . So, processor constraints are implicitly taken into account by the Alarm\_Manager and Alarm\_Notifier models, which consequently remain unchanged.

Finally, the overall model of the deployed system is close to the one shown in FIG. 10, where safe\_FIFO is replaced by Bus. Its clock analysis by the compiler exhibits the clock constraints that should be guaranteed by the program environment in order to perform functional simulation.

#### 5 ANALYSIS AND AUTOMATIC CODE GENERATION

#### 5.1 Analysis of non functional properties

There are various ways to analyze non functional properties of SIGNAL models after their deployment on a given platform. For instance, performance evaluation is possible by using a quantitative temporal interpretation of SIGNAL programs [36], [23]. On the other hand, beyond the strict clock synchronization problems that are usually solved by almost all compilers of synchronous languages, more intricate synchronization issues can arise in the design of distributed systems if one would like to be able to widely explore architecture allocation possibilities. This requires sophisticated tools to address such issues.

#### 5.1.1 Clock synchronizability issues

in

Affine clocks have been introduced in the SIGNAL clock calculus for this purpose [43], and more precisely in order to deal with synchronizability issues in a more "relaxed" way than usually in synchronous languages. Formally, an *affine transformation* of parameters  $(n, \phi, d)$  applied to a clock  $\kappa_1$  produces a clock  $\kappa_2$  by inserting (n - 1) instants between any two successive instants of  $\kappa_1$ , and then counting on this fictional set of instants each  $d^{th}$  instant, starting with the  $\phi^{th}$ . Clocks  $\kappa_1$  and  $\kappa_2$  are said to be in  $(n, \phi, d)$ -affine relation, noted as  $\kappa_1 \stackrel{(n, \phi, d)}{\longrightarrow} \kappa_2$ . The following trace depicts  $\kappa_1 \stackrel{(3,1,4)}{\longrightarrow} \kappa_2$ , where "t" denotes the presence of a clock  $\kappa_i$ :