THE SIMULATION OF MOS INTEGRATED CIRCUITS USING SPICE2

bу

Andrei Vladimirescu and Sally Liu

Memorandum No. UCB/ERL M80/7

February 1980 (Revised October 1980)

# ELECTRONICS RESEARCH LABORATORY College of Engineering University of California, Berkeley, CA 94720

### **Report Documentation Page**

Form Approved OMB No. 0704-0188

Public reporting burden for the collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington VA 22202-4302. Respondents should be aware that notwithstanding any other provision of law, no person shall be subject to a penalty for failing to comply with a collection of information if it does not display a currently valid OMB control number.

| 1. REPORT DATE OCT 1980                                                            | 2. REPORT TYPE                              | 3. DATES COVERED <b>00-00-1980 to 00-00-1980</b> |  |  |

|------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------|--|--|

| 4. TITLE AND SUBTITLE                                                              |                                             | 5a. CONTRACT NUMBER                              |  |  |

| The Simulation of MOS Integrated Cir                                               | 5b. GRANT NUMBER                            |                                                  |  |  |

|                                                                                    |                                             | 5c. PROGRAM ELEMENT NUMBER                       |  |  |

| 6. AUTHOR(S)                                                                       | 5d. PROJECT NUMBER                          |                                                  |  |  |

|                                                                                    | 5e. TASK NUMBER                             |                                                  |  |  |

|                                                                                    |                                             | 5f. WORK UNIT NUMBER                             |  |  |

| 7. PERFORMING ORGANIZATION NAME(S) AND AE University of California at Berkeley, De | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER |                                                  |  |  |

| <b>Engineering and Computer Sciences, B</b>                                        | erkeley,CA,94720                            |                                                  |  |  |

| 9. SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES)                            |                                             | 10. SPONSOR/MONITOR'S ACRONYM(S)                 |  |  |

|                                                                                    |                                             | 11. SPONSOR/MONITOR'S REPORT<br>NUMBER(S)        |  |  |

| 12. DISTRIBUTION/AVAILABILITY STATEMENT Approved for public release; distribution  | on unlimited                                |                                                  |  |  |

| 13. SUPPLEMENTARY NOTES                                                            |                                             |                                                  |  |  |

### 14. ABSTRACT

This report is addressed to all SPICE2 users involved in the design of MOS (Metal Oxide Semiconductor) IC's (Integrated circuits). The material contained herein serves as an addition to the SPICE2.G User's Guide. The device and model parameters documented refer to the SPICE2.G release versions from the University of California, Berkeley and obsolete the information contained in the "SPICE2 MOS Modeling Handbook" which is valid for the SPICE2.D release versions. The impact of MOS IC's in both analog and digital applications as well as the decreasing dimensions of the single transistors enabled by advances in processing have made it necessary to refine the models and to provide more information about each device as it appears on the circuit layout. Associated with each MOSFET is a drain and source-junction sidewall capacitance (which has a different voltage dependence than the bottom of the diffusion) and a parasitic series resistance. These are unique to a certain geometry. At the model level there are effects which become important as the channel length and width go below 10um. A thorough description of all parameters appearing on the element (device) card and model card is contained in Sec. 2. In SPICE2.G there are three different MOS models available to the user. The Level 1 model is the simple Shichman-Hodges model implemented according to Nagel's "SPICE2: A Computer Program to Simulate Semiconductor Circuits." This first order model has been found necessary for checking out the correctness of hand calculations when understanding or developing new circuits. The Level 2 model is an analytical one-dimensional model which incorporates most of the second-order effects of small-size devices. The Level 3 model is a semi-empirical model described by a set of parameters which are defined by curve-fitting rather than physical background. It is necessary for the circuit designer to know what are the equations governing the behaviour of the MOSFETs and what is the influence of the various model parameters even if hand calculations are almost impossible at this complexity. This insight of the MOS2 and MOS3 model equations is found in Sec. 3 and 4. The accuracy of the model depends heavily on the values of the input parameters. These input parameters should be related to the particular process used at each manufacturing site. The large number of parameters which describe the model require the existence of a parameter extraction system. Sec. 5 provides some detail on how to use some simple preprocessor programs for the evaluation of the SPICE2 input parameters from the measurements taken on test devices. Sec. 6 gives an example of a sample SPICE2 MOS IC input deck stressing the correlation among different model parameters and the importance of modelling various second-order effects for a good agreement with measured performance.

| 15. SUBJECT TERMS         |                             |                              |                               |                        |                                    |

|---------------------------|-----------------------------|------------------------------|-------------------------------|------------------------|------------------------------------|

| 16. SECURITY CLASSIFIC    | CATION OF:                  |                              | 17. LIMITATION OF<br>ABSTRACT | 18. NUMBER<br>OF PAGES | 19a. NAME OF<br>RESPONSIBLE PERSON |

| a. REPORT<br>unclassified | b. ABSTRACT<br>unclassified | c. THIS PAGE<br>unclassified | Same as<br>Report (SAR)       | 80                     | RESI GINSISEE I ERGGIN             |

## THE SIMULATION OF MOS INTEGRATED CIRCUITS USING SPICE2

bу

Andrei Vladimirescu and Sally Liu

Memorandum No. UCB/ERL M80/7

February 1980 (Revised October 1980)

### THE SIMULATION OF MOS INTEGRATED CIRCUITS USING SPICE2

bу

Andrei Vladimirescu and Sally Liu

Memorandum No. UCB/ERL M80/7

February 1980 (Revised October 1980)

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

### **ACKNOWLEDGEMENT**

Many people contributed to develop the new input and model equations for MOSFET's. The continuing encouragement and support of our research advisor, Professor D. O. Pederson, is greatly appreciated. Steady discussions with E. Cohen and other members of the UC Berkeley Integrated Circuits Computer-Aided Design Group are acknowledged. Discussions with Profs. W. G. Oldham, P. R. Gray, D. A. Hodges, and R. A. Newton helped in many decisions that had to be taken.

An important contribution to the development of the new model has been offered by the industrial experience gained during the Summer 1978 as a member of the MOS LSI Design Group at Tektronix Inc., in Beaverton, Oregon. The guidance of Mr. J. R. Young and stimulating discussions with Mr. D. Larsen and Dr. G. R. Boyle helped completing a good part of the work reported.

Last but not least we appreciate the discussions with Dr. R. I. Dowell from Hewlett Packard and his help in the implementation of the charge-oriented capacitance model.

This project has been supported by grants from the Army Research Office, Bell Laboratories, Signetics and Tektronix Inc.

|  | T |  |  |

|--|---|--|--|

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

### TABLE OF CONTENTS

|              |                                                       | Page |

|--------------|-------------------------------------------------------|------|

| 1.           | Introduction                                          | 1    |

| 2.           | Description of MOS Parameters                         | 2    |

| 2.1.         | Device Parameters                                     | 2    |

| 2.2.         | Model Parameters                                      | 2    |

| 3.           | Implementation of Small-Size Device                   |      |

|              | Second-Order Effects in the MOS2 Model                | 10   |

| <b>3</b> .1. | Threshold Voltage                                     | 10   |

| 3.2.         | Drain-Source Current                                  | 15   |

| 3.3.         | Operation in the Saturation Region                    | 15   |

| 3.3.1.       | Saturation due to Pinch-off;                          |      |

|              | Channel Length Modulation                             | 15   |

| 3.3.2.       | Saturation due to Scattering Limited Velocity;        |      |

|              | Channel Length Modulation                             | 16   |

| 3.4.         | Weak Inversion Conduction                             | 18   |

| 3.5.         | Temperature Dependance                                | 21   |

| 3.6.         | Charge-Oriented Model for MOSFET Capacitances         | 21   |

| 4.           | The MOS3 Model; A Semi-Empirical Model for            |      |

|              | Small-Geometry MOSFET's                               | 24   |

| 4.1.         | Threshold Voltage                                     | 24   |

| 4.2.         | Basic Current Equation                                | 27   |

| 4.3.         | Surface Mobility Modulation by the Gate Voltage       | 28   |

| 4.4.         | Velocity Saturation of Hot Electrons                  | 28   |

| 4.5.         | Saturation Voltage                                    | 28   |

| 4.6.         | Channel Length Modulation                             | 29   |

| 4.7.         | Weak Inversion Conduction                             | 29   |

| 4.8.         | Temperature Dependence                                | 31   |

| 4.9.         | Charge-Oriented Capacitance Model                     | 31   |

| 4:.10.       | Parameter Extraction for MOS3                         | 32   |

| 4.10.1.      | THETA, Mobility Modulation Parameter                  | 32   |

| 4.10.2.      | ETA, Static Feedback Parameter                        | 32   |

| 4.10.3.      | DELTA, Width Effect on Threshold                      | 34   |

| 4.10.4.      | VMAX, Limited Velocity of Hot Electrons               | 34   |

| 4.10.5.      | KAPPA, Correlation Coefficient of the Drain Fields in |      |

|              | Saturation                                            | 34   |

| 4.11.        | Performance Comparison between MOS2 and MOS3          | 35   |

| 5.           | Model Parameter Extraction                            | 36   |

| 5.1.         | VTO and NSUB Weasurement                              | 36   |

| 5.2. | Capacitance Measurements      | 37 |

|------|-------------------------------|----|

| 5.3. | Mobility Parameter Extraction | 38 |

| 5.4. | Approximation of VMAX         | 39 |

| 6.   | Simulation Example            | 41 |

|      | Appendix 1                    | 45 |

|      | Appendix 2                    | 55 |

|      | Appendix 3                    | 62 |

|      | References                    | 65 |

|      |                               |    |

### 1. INTRODUCTION

This report is addressed to all SPICE2 users involved in the design of MOS (Metal Oxide Semiconductor) IC's (Integrated circuits). The material contained herein serves as an addition to the SPICE2.G User's Guide [1].

The device and model parameters documented refer to the SPICE2.G release versions from the University of California, Berkeley and obsolete the information contained in the "SPICE2 MOS Modeling Handbook" [2] which is valid for the SPICE2.D release versions.

The impact of MOS IC's in both analog and digital applications as well as the decreasing dimensions of the single transistors enabled by advances in processing have made it necessary to refine the models and to provide more information about each device as it appears on the circuit layout. Associated with each MOSFET is a drain and source-junction sidewall capacitance (which has a different voltage dependence than the bottom of the diffusion) and a parasitic series resistance. These are unique to a certain geometry. At the model level there are effects which become important as the channel length and width go below  $10\mu m$ . A thorough description of all parameters appearing on the element (device) card and model card is contained in Sec. 2.

In SPICE2.G there are three different MOS models available to the user. The Level 1 model is the simple Shichman-Hodges model implemented according to [3]. This first order model has been found necessary for checking out the correctness of hand calculations when understanding or developing new circuits. The Level 2 model is an analytical one-dimensional model which incorporates most of the second-order effects of small-size devices. The Level 3 model is a semi-empirical model described by a set of parameters which are defined by curve-fitting rather than physical background. It is necessary for the circuit designer to know what are the equations governing the behaviour of the MOSFET's and what is the influence of the various model parameters even if hand calculations are almost impossible at this complexity. This insight of the MOS2 and MOS3 model equations is found in Sec. 3 and 4.

The accuracy of the model depends heavily on the values of the input parameters. These input parameters should be related to the particular process used at each manufacturing site. The large number of parameters which describe the model require the existence of a parameter extraction system. Sec. 5 provides some detail on how to use some simple preprocessor programs for the evaluation of the SPICE2 input parameters from the measurements taken on test devices.

Sec. 6 gives an example of a sample SPICE2 MOS IC imput deck stressing the correlation among different model parameters and the importance of modelling various second-order effects for a good agreement with measured performance.

### 2. DESCRIPTION OF MOSFET PARAMETERS

### 2.1. Device Parameters

According to the new format of the MOSFET device line [1] there are up to 8 parameters describing each geometry. With the exception of W and L (which are defaulted to 1m), all other parameters default to zero if not specified.

W and L are the channel width and length in meters as measured on the layout;

AD and AS are the drain and source area, respectively; they scale the parameters JS and CJ of the model line. If not specified they are assumed zero. When absolute values for the junction reverse current (IS) or the junction capacitances (CBD, CBS) are input on the model line the areas can be omitted. AD and AS are measured as if on a layout and thus model the bottom of the junction.

PD and PS are the perimeters of the drain and source respectively; they multiply the junction sidewall capacitance CJSW specified in F/m on the model line.

NRD and NRS are the number of squares of the parasitic series resistance of the drain and source diffusions as estimated from the layout. NRD and NRS multiply the sheet resistance RSH given on the model card. An alternate way to specify series resistances for the drain and source is to enter the total values RD and RS on the model card; these values will then be added to all devices which invoke that particular model. When RD and RS appear in the definition of a model then those devices referencing this model need no NRD or NRS.

As is seen from the above there is a close correlation between the parameters which appear on the device card and the parameters input on the model card. Since a hierarchical order of the model parameters is given in the following paragraph, only a single example is mentioned. The presence of NSUB on the model line automatically calls for the calculation of CJ. A way to strip the model of any bottom junction capacitance is to delete AD and/or AS from the device card.

### 2.2. Model Parameters

This section rather than reproducing the information contained in the User's Guide groups the 37 parameters describing the MOSFET model in a logical manner.

LEVEL indicates the program which model is desired;

LEVEL=1 invokes the Shichman-Hodges model (default);

LEVEL=2 invokes the "MOS2" model to be described in the following section;

LEVEL=3 invokes the semi-empirical model described in Sec. 4.

A first classification is to divide the input data into "Electrical" (derived) and "Processing" (primary) parameters. According to this view point, VTO and GAMMA are

electrical and NSUB and TOX are processing parameters. For all models both kinds of parameters can be entered with the general convention that the electrical data will always override the value computed from processing data if also specified. Thus if VTO, NSUB and TOX are input the threshold voltage will assume the value entered as VTO, while, e.g., GAMMA will be computed from NSUB and TOX.

The following 5 data are the Electrical (derived) parameters:

VTO is the Extrapolated Zero-Bias Threshold Voltage of a long and wide channel device. This voltage is derived at the onset of strong inversion and marks the point where the device starts conducting if the weak inversion current is neglected (see the description of the parameter NFS).

If VTO is not an input parameter and NSUB and TOX are specified, SPICE2 will evaluate the threshold from the equation

$$V_{TO} = V_{FB} + 2\varphi_F + \frac{2\sqrt{q\,\varepsilon_{SI}NSUB\,\varphi_F}}{C_{OX}}$$

(2.1)

where

$$V_{FB} = \varphi_{MS} - \frac{qNSS}{C_{OX}} \tag{2.2}$$

is the flatband voltage [4], [5] and  $\varphi_{MS}$  is the metal (poly-silicon) semiconductor work function difference. VTO will be printed out in the summary of the model parameters at the beginning of the SPICE2 output. The value VTH which is printed in the operating point information represents the threshold for given terminal voltages and for the particular device including size dependence, (see Sec. 3.1.).

KP is the Intrinsec Transconductance Parameter. If it is not specified and UO (surface mobility) and TOX are entered, it is computed by the program according to the equation

$$KP = UO \times C_{OX}$$

(2.3)

GAMMA is the Bulk Threshold Parameter and represents the proportionality factor relating the change in threshold voltage to backgate bias. It is encountered in the expression of VTO, the drain-source current  $I_{DS}$ , and saturation voltage. When it is not input and if the necessary processing parameters are given, it is derived from

$$GAMMA = \frac{\sqrt{2q \, \varepsilon_{SI} \, NS \, UB}}{C_{OX}} \tag{2.4}$$

if the necessary processing parameters are given.

PHI is the Surface Potential at strong inversion  $2\varphi_{F}$ . When not input it is computed from

$$PHI = 2\frac{kT}{q} \ln \frac{NSUB}{ni}$$

(2.5)

LAMBDA is the Channel-Length Modulation Parameter and is equivalent to the inverse of the Early voltage for the bipolar transistor and is a measure of the output conductance in saturation. By specifying this parameter the MOSFET will have a finite but constant output conductance in saturation.

If LAMBDA is not input the LEVEL=1 model will assume a zero output conductance while the LEVEL=2 model will compute a finite and voltage-dependent output conductance defined by

$$LAMBDA = \frac{\Delta L}{L \times V_{DS}} \tag{2.6}$$

where L is the channel length input on the device line less the lateral diffusions of the drain and source, LD, and  $\Delta L$  is a function of  $V_{DS}$  and  $V_{DSAT}$  as is shown later.

The above set of electrical parameters is adequate for the LEVEL=1 model.

In the following the parameters which characterize the gate and channel of the MOSFET are summarized. These parameters are further classified as oxide characteristics, charge concentrations and mobility parameters.

The characteristics of the thin oxide are listed below.

TOX is the Oxide Thickness and comes into the calculation of the conduction factor, backgate bias effect and gate-channel voltage-dependent capacitances.

If not specified, in the LEVEL=1 model TOX will be assumed infinite, i.e., VTO, KP, or GAMMA will be defaulted rather than computed if these last quantities are not entered directly. The gate capacitances,  $C_{GS}$ ,  $C_{GD}$  and  $C_{GB}$  are assumed to be the overlap capacitances, i.e., they are constant with voltage. In the LEVEL=2 and =3 model, TOX defaults to 1000A implying that the gate capacitances are always voltage-dependent.

CGSO is the Gate-Source Overlap Capacitance per meter channel width and represents the capacitance due to the lateral diffusion of the source in a silicon gate MOSFET; the input value is multiplied by the channel width. This is the constant part of the total  $C_{GS}$  capacitance which has also a contribution due to the thin oxide capacitance (the voltage-dependent charges associated with the gate and channel).

CGDO is the Gate-Drain Overlap Capacitance per meter channel width. The same considerations as above apply.

CGBO is the Gate-Bulk Overlap Capacitance per meter channel length and is, as opposed to the above capacitances, a field oxide capacitance. It is the result of the

requirement that the gate has to extend beyond the channel by a certain amount according to the specific design rules. The total  $C_{QP}$  overlap capacitance results by multiplying the above value by the channel length.

There are five parameters which describe or relate to charge concentrations.

NSUB is the Substrate Doping and is used in the derivation of most of the electrical parameters. The effect of implants can be added by specifying different VTO's and maintaining the same NSUB in the different models for the calculations, say of the junction capacitances. NSUB can be specified for a LEVEL=1 model as well and it assumes the same role.

NSS is the Effective Surface Charge Density and is used for the evaluation of VTO. In most cases it is more accurate to specify VTO as obtained from a parameter extraction system rather than NSS.

NFS is the Effective Fast Surface State Density and serves both as a flag for the evaluation of subthreshold currents and as a quantity controlling the amount of subthreshold current flowing in the device. If not specified, the MOSFET conducts only in strong inversion. This parameter is meaningless for a LEVEL=1 model.

NEFF is the Total Channel Charge (Fixed and Mobile) Coefficient. It is used as a multiplicative factor of NSUB in order to get the proper value of the output conductance in saturation. Physically it accounts for the fact that in the channel there is both mobile and fixed charge and the total amount has to be considered for computing the output conductance. NEFF has meaning only when the velocity saturation model is used (VMAX is specified) in the LEVEL=2 model.

TPG is the Type of Gate indicates whether the simulated device has a metal or polysilicon gate (and which polarity type relative to the substrate). The NGATE parameter of the older SPICE2 (D and E) versions has been deleted since the poly gate is usually heavily doped and the Fermi level is located very close to one of the band edges.

A last group of parameters characterizing the gate and channel refer to the properties of carriers in the conductive channel. The first four describe the surface mobility and its variation with the electric field.

UO is the Surface Mobility at low gate voltages. It is the only mobility parameter which has meaning for a LEVEL=1 or =3 model.

UCRIT is the Critical Field for Mobility Degradation and is the limit at which the surface mobility UO starts decreasing according to the empirical relation given below.

UEXP is the Critical Field Exponent for the empirical formula which characterizes the degradation of the surface mobility.

UTRA is the Transverse Field Coefficient for the empirical mobility degradation formula.

The above four parameters enter in the following equation of the surface mobility degradation [6]

$$\mu_{S} = UO \times \left[ \frac{UCRIT \times \varepsilon_{SI}}{C_{OX}(V_{CS} - V_{TH} - UTRA \times V_{DS})} \right]^{UEXP}$$

(2.7)

The above parameters are determined best by curve fitting as is shown in Sec. 5. In most cases UTRA can be chosen between 0.0 and 0.5.

VMAX is the Maximum Drift Velocity of Carriers and affects the drain-source saturation voltage of the MOSFET. It has been proven that for devices with channel lengths shorter than  $10\mu$  the drain current saturates before the channel pinches off because the electrons (holes) reach the scattering limited velocity in the channel. The model proposed by Baum and Beneking [7] and first used in the SHOMOS model [8] is applied in order to get  $V_{DSAT}$  from the following equation

$$VMAX = \frac{I_{DSAT}}{W \times Q_{CHAN}} \tag{2.8}$$

where  $I_{DSAT}$  and  $Q_{CHAN}$  are functions of  $V_{DSAT}$ . More details about this are given in the following section.

VMAX also acts as a flag in the LEVEL=2 model. When specified the scattering limited velocity of carriers determines  $V_{DSAT}$ ; otherwise the pinch-off approach gives  $V_{DSAT}$ . This parameter is meaningless for the LEVEL=1 model. When specified in LEVEL=2, the channel shortening effect uses the NEFF parameter as introduced above (see also Sec. 3).

A last category of parameters characterize the drain and source junctions of the MOSFET. There is some overlap among some of these parameters, e.g., the reverse current of the junction can be input either as IS (in A) or as JS (in  $A/m^2$ ). Whereas the first is an absolute value, the second is multiplied by AD and AS to give the reverse current of the drain and source junctions respectively. This methodology has been chosen since AD and AS default to zero. The same procedure applies also to the zero-bias junction capacitances CBD and CBS on one hand, and CJ on the other as is seen in the following description.

RD and RS are the Drain and Source Ohmic Resistances and are values which apply to all devices invoking the model in which they are specified. (This was the only way for the SPICE2.D and .E versions to include series resistances).

RSH is the Sheet Resistance of the Drain and Source Diffusions and is multiplied by the number of squares NRD and NRS which are entered on each device card to give the total drain and source ohmic resistance respectively, for each device. When both the total value (RD or RS) and the RSH are input the total value overrides.

CBD and CBS are Zero-Bias B-D and B-S junction capacitances and are total values for all devices which reference the model where they are specified.

CJ is the Zero-Bias B-D and B-S junction capacitance per  $m^2$  of junction area and is multiplied by the areas AD and AS entered on the device card to give total values for the B-D and B-S junction capacitances, respectively, specific to each single device. CJ is computed automatically by the program if NSUB is specified and a step junction is assumed.

When both the total value (CBD or CBS) and CJ (or NSUB) are input, the total value overrides.

MJ is the Grading Coefficient of the B-D and B-S junctions and applies to both CBD and CBS, or CJ.

The above capacitances are well suited for modeling the bottom of the junctions. It has been found experimentally that an important part of the junction capacitance is contributed by the sidewall of the diffusion which extrapolates to a different zero-bias value and grading coefficient than those pertaining to the bottom of the diffusion. The following two parameters account for this capacitance.

CJSW is the Zero-Bias Junction Sidewall Capacitance per meter of Drain and Source Perimeter. It is multiplied by PD and PS entered on the device line to give the drain and source junction sidewall capacitances, respectively.

MJSW is the Grading Coefficient of the Junction Sidewall.

All the above capacitances and grading coefficients are determined best from curve fitting of measurements taken on specially designed test chips as is outlined in Sec. 5.

The total junction capacitance can be expressed as follows: For reverse bias,  $V_{BS} < FC \times PB$  (see below for explanation of FC and PB)

$$CBS_{TOT} = CJ \frac{AS}{\left(1 - \frac{V_{BS}}{PB}\right)^{MJ}} + CJSW \frac{PS}{\left(1 - \frac{V_{BS}}{PB}\right)^{MJSW}}$$

(2.9)

For forward bias,  $V_{BS} > FC \times PB$

$$CBS_{TOT} = CJ \frac{AS}{(1 - FC)^{(1+MJ)}} \left[ 1 - FC(1+MJ) + \frac{V_{BS}}{PB} \times MJ \right] +$$

(2.10)

$$CJSW \frac{PS}{(1 - FC)^{(1+MJSW)}} \left[ 1 - FC(1+MJSW) + \frac{V_{BS}}{PB} \times MJSW \right]$$

The above equations insure a smooth transition from the reverse bias region to the forward bias region and prevent the capacitance from increasing to infinity.

IS is the Reverse Current of the Drain or Source Junctions and is a total value, the same for all the drain and source junctions of the devices which reference the model containing IS.

JS is the Reverse Current Density of the Drain or Source Junction per  $m^2$  of junction area. The total value IS results from a multiplication by AD and AS and is specific to each junction of each transistor.

If neither of the above currents are specified, the program will default IS to 1.0E-14 A. If both IS and JS are specified, IS overrides JS.

PB is the Bulk Junction Potential is used in the junction capacitance formulation.

FC is the Forward Bias Nonideal Junction Capacitance Coefficient and is used as shown above in matching the transition point and voltage characteristic of the junction capacitance when bias changes from reverse to forward. The default value of 0.5 proves satisfactory most of the time.

XJ is the Metallurgical Junction Depth.

LD is the Lateral Diffusion Coefficient in meters. The effective channel length is

$$L = L_{\mathcal{U}} - 2 \times LD \tag{2.11}$$

where  $L_{\mathbb{Z}}$  is the length on the circuit mask input on the device line. In all subsequent equations L represents the effective channel length.

LD is used for the computation of L only, whereas XJ is both a flag and parameter used in the evaluation of the short-channel effect.

The only parameters not mentioned so far are

KF is the Flicker Noise Coefficient

AF is the Flicker Noise Exponent. These two parameters are used in the small-signal AC noise analysis to determine the equivalent noise current generator connected between drain and source, the value of which is

$$I_N = \sqrt{\frac{8kTg_m}{3} + \frac{KF \times I_{DS}^{AF}}{f Cov \% L}}$$

(2.12)

In the future an improved noise model for the MOSFET is needed.

Listed below are four model parameters which are specific to the LEVEL=3 model only. For this model, the parameters LAMBDA, UCRIT, UEXP, UTRA, and NEFF are meaningless.

ETA is the Static Feedback Effect Parameter. It is the proportionality factor which multiplies the value of  $V_{DS}$  in the  $V_{TH}$  equation implemented in MOS3 to model the static drain to gate feedback effect.

DELTA is the Channel Width Factor. This is an empirical factor which adjusts the depleted bulk charge underneath the gate to be in agreement with the observed threshold voltage increase in narrow-channel devices.

THETA is the Empirical Mobility Modulation Parameter and is used to compute mobility degradation as a function of  $V_{\rm GS}$ .

KAPPA is the Field Correlation Factor. It is used to adjust the electric field across the surface depletion region of the device in saturation.

### 3. IMPLEMENTATION OF SMALL-SIZE DEVICE SECOND-ORDER EFFEECTS IN THE MOSS MODEL

This section presents the main features of the LEVEL=2 (MOS2) model and the equations which describe the various first- and second-order effects.

The following effects are modeled in MOS2:

- Backgate bias and small-size (short- and narrow-channel) effect on threshold voltage considering also the static feedback from drain to gate;

- Saturation due to the scattering limited drift velocity of carriers and finite voltagedependent output conductance;

- Surface field dependent mobility;

- Weak inversion conduction;

- Charge controlled model of regenerative effects;

- Variation of all quantities with temperature.

In the rest of this section the pertinent equations are listed with emphasis on the influence of the different input parameters.

### 3.1. Threshold Voltage

From the zero-bias threshold voltage VTO given in Sec. 2, which applies for a MOS-FET with large dimensions (W,  $L>20\mu m$ ) and with the source and buik connected together SPICE2.G readjusts this value to  $V_{TH}$  at each operating point and for each transistor according to its size.

Physically the following effects take place:

- An increase of the bulk-to-source voltage increases the depletion charge which causes  $V_{TH}$  to go up.

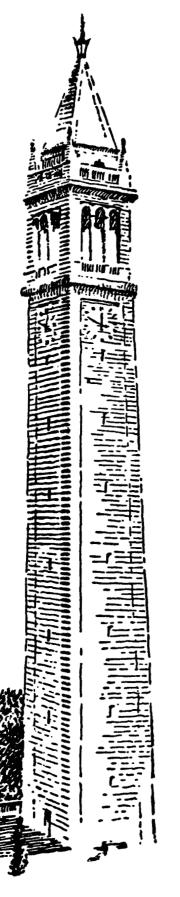

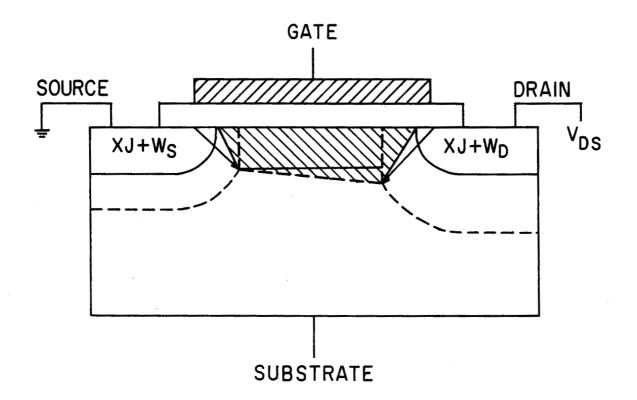

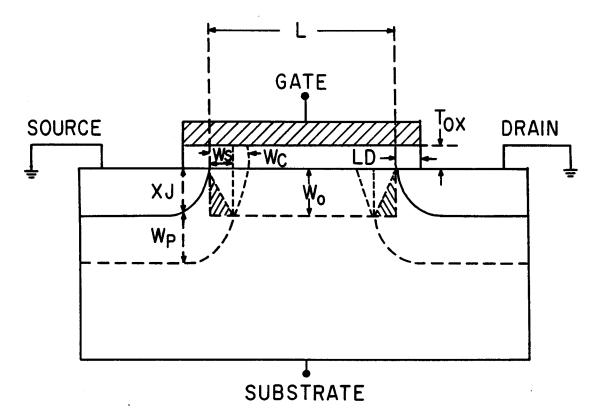

- In a short-channel device part of the depletion charge in the bulk terminates the electric field of the drain and source junctions. The electric field from gate to bulk depletes less charge and thus  $V_{TH}$  is lowered. This can be viewed by the trapezoid approach introduced by Yau [9] and which is used by SPICE2 (see Fig. 3.1.).

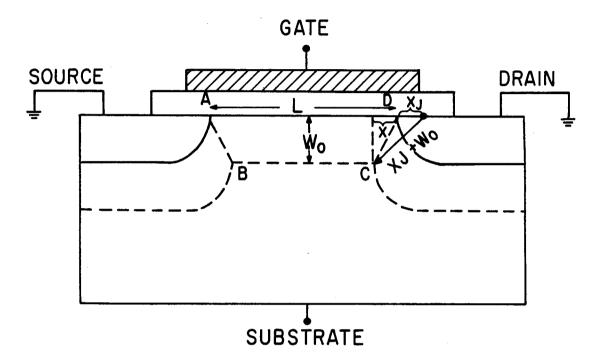

- The edge effects in a narrow channel cause the depletion charge to extend beyond the width of the channel. The gate-to-bulk field has to be increased to balance this charge; thus,  $V_{TH}$  increases (see Fig. 3.2.).

- The amount of charge underneath the gate depleted by the drain junction field rather than the gate-to-bulk field increases with  $V_{DS}$  thus lowering  $V_{TH}$ . This effect is approximated geometrically in MOS2 as shown in Fig. 3.3. and is referred to as the static drain-to-gate feedback on threshold.

An equation for  $V_{TH}$  which sums up the above features, can be expressed as

$$(X+XJ)^{2} = (XJ+W_{0})^{2} - W_{0}^{2}$$

$$X = XJ(\sqrt{1 + \frac{2W_{0}}{XJ}} - 1)$$

$$Q_{B} \propto W_{0} \times L$$

$$Q_{B}' = W_{0}[L - XJ(\sqrt{1 + \frac{2W_{0}}{XJ}})]$$

$$\frac{Q_{B}'}{Q_{B}} = [1 - \frac{XJ}{L}(\sqrt{1 + \frac{2W_{0}}{XJ}} - 1)]$$

FIG. 3.1.

FIG. 3.2.

$$V_{TH} = V_{BIN} + \gamma_S \sqrt{2\varphi_F - V_{BS}} \tag{3.1}$$

where

$$V_{BIN} = V_{BI} + DELTA \frac{\pi \varepsilon_{SI}}{4C_{OX}W} (2\varphi_F - V_{BS})$$

(3.2)

is the corrected built-in voltage for narrow channel, and

$$V_{BI} = V_{FB} + 2\varphi_F \tag{3.3}$$

$\gamma_S$  is the corrected GAMMA for short-channel with static drain-to-gate feedback (see Fig. 3.3.)

$$\gamma_S = GAMMA (1 - \alpha_S - \alpha_D) \tag{3.4}$$

where  $\alpha_D$  and  $\alpha_S$  are the correction factors for the depletion charge at the drain and source, respectively,

$$\alpha_S = \frac{1}{2} \frac{XJ}{L} \left[ \sqrt{1 + 2 \frac{W_S}{XJ}} \right]$$

(3.5)

$$\alpha_D = \frac{1}{2} \frac{XJ}{L} \left[ \sqrt{1 + 2 \frac{W_D}{XJ}} \right]$$

(3.6)

The depletion widths  $W_S$  and  $W_D$  are

$$W_S = X_D \sqrt{2\varphi_F - V_{BS}} \tag{3.7}$$

$$W_D = X_D \sqrt{2\varphi_F - V_{BS} + V_{DS}} \tag{3.8}$$

where

$$X_D = \sqrt{\frac{2\varepsilon_{SI}}{q \ NSUB}} \tag{3.9}$$

The implementation of the geometry in Fig. 3.3, represents an idealization of the actual depletion layer shape. Preliminary results show that it offers a good approximation at a minimum computational effort.

It should be noticed that the absence of XJ from the input file bypasses the correction for short channel effect.

### DASHED ZONE-BULK CHARGE DEPLETED BY GATE FIELD

FIG. 3.3

### 3.2. Drain-Source Current

In order to correct for small dimensions, the implemented drain-source current equation is slightly modified relative to previous formulations [4], [5] which include the effect of the bulk charge.

The current in strong inversion  $(V_{GS} > V_{TH})$  is given by

$$I_{DS} = \beta \left[ \left( V_{GS} - V_{BIN} - \frac{\eta V_{DS}}{2} \right) V_{DS} - \frac{2}{3} \gamma_S \left[ (2\varphi_F + V_{DS} - V_{BS})^{3/2} - (2\varphi_F - V_{BS})^{3/2} \right] \right]$$

(3.10)

where

$$\eta = 1 + DELTA \frac{\pi \varepsilon_{SI}}{4C_{OX}W}$$

$$\beta = \frac{W}{L} \mu_S C_{OX}$$

It can be seen that the narrow channel effect is included through  $V_{BIN}$  given in Eq. (3.2) and  $\eta$ . The short channel uses the corrected GAMMA,  $\gamma_S$ .  $\mu_S$  represents the degraded surface mobility. For large W and L the above equations revert to the well known forms [4], [5].

### 3.3. Operation in the Saturation Region

### 3.3.1. Saturation due to Pinch-off; Channel Length Modulation

As mentioned earlier, if VMAX is not input the program computes the saturation voltage  $V_{DSAT}$  assuming the channel pinches off at the drain limit. With the corrections for small-size effects,  $V_{DSAT}$  is

$$V_{DSAT} = \frac{(V_{GS} - V_{BIN})}{\eta} + \frac{1}{2} \left[ \frac{\gamma_S}{\eta} \right]^2 \left[ 1 - \left[ 1 + 4 \left[ \frac{\eta}{\gamma_S} \right]^2 \left[ \frac{V_{GS} - V_{BIN}}{\eta} + 2\varphi_F - V_{BS} \right] \right]^{1/2} \right]$$

(3.11)

The finite output conductance observed in saturation is due to the spread of the pinch-off region into the channel thus reducing the effective channel length,  $L_{eff} = L - \Delta L$ , and increasing the geometrical ratio of the conduction factor.

$$\frac{W}{L - \Delta L} = \frac{W}{L(1 - LAMBDA \times V_{DS})} \tag{3.12}$$

$$LAMBDA = \frac{\Delta L}{L \times V_{DS}}$$

If LAMBDA is not an input parameter, its value is computed according to Eq. (3.12) where

$$\Delta L = X_D \left[ \frac{V_{DS} - V_{DSAT}}{4} + \sqrt{1 + \left[ \frac{V_{DS} - V_{DSAT}}{4} \right]^2} \right]^{1/2}$$

(3.13)

This formulation does not include the effect of the field between gate and drain and gate and pinch-off point respectively [10], but insures the continuity of the current and its first derivative at the transition from the triode- into the saturation region (important in an iterative solution algorithm of nonlinear simultaneous equations). Another drawback of the above formulation of the channel modulation is that it overestimates the output conductance in saturation.

One problem with short channel devices is that at high  $V_{DS}$  punch-through occurs. This effect is not modeled in SPICE2. In order to prevent the channel length from going negative, Eq. (3.12) is used only when the effective channel length  $L_{eff}$  is larger than the zero-bias depletion layer width  $W_B$ ,  $(W_B = X_D \sqrt{PB})$ . When  $L_{eff}$  gets smaller than  $W_B$ , Eq. (3.12) is replaced by

$$L_{eff} = \frac{W_B}{1 + \frac{\Delta L - L_{\text{max}}}{W_B}} \tag{3.14}$$

where

$$L_{\max} = L - W_B \tag{3.15}$$

Although this equation does not model punch-through it prevents numerical non-convergence problems that have been observed.

### 3.3.2. Saturation due to Scattering Limited Velocity; Channel Length Modulation

In short-channel MOSFET's the saturation of the current occurs because the charge carriers reach their maximum scattering limited velocity before pinch-off. In other words, a lower current is expected from a short channel device as compared to a long channel device of identical geometric ratios, processing and biasing conditions.

$V_{DSAT}$  is obtained as the solution of Eq. (2.8) after substituting the expressions for  $I_{DSAT}$  and  $Q_{CHAN}$ . This leads to

$$VMAX = \frac{\mu_{S} \left[ (V_{CS} - V_{BIN} - \frac{\eta V_{DSAT}}{2}) V_{DSAT} - \frac{2}{3} \gamma_{S} (\left[ V_{DSAT} + 2\varphi_{F} - V_{BS} \right]^{\frac{3}{2}} - \left[ 2\varphi_{F} - V_{BS} \right]^{\frac{3}{2}}) \right]}{L_{eff} \left( V_{CS} - V_{BIN} - \eta V_{DSAT} - \gamma_{S} \left[ V_{DSAT} + 2\varphi_{F} - V_{BS} \right]^{1/2} \right)} (3.16)$$

A problem arises because  $Q_{CHAN}$  is defined at the point where the carriers reach their maximum velocity. This point moves towards the source as  $V_{DS}$  increases. The shortening of the channel is implemented in MOS2 as proposed by Baum [7].

$$L_{eff} = L - X_D \sqrt{\left[\frac{X_D \ VMAX}{2\mu_S}\right]^2 + (V_{DS} - V_{DSAT})} + \frac{X_D^2 \ VMAX}{2\mu_S}$$

(3.17)

In this theory on a  $V_{CS}$ =constant curve, the saturation voltage varies (decreases) as  $V_{DS}$  increases. From a numerical point of view this requires the simultaneous solution of two nonlinear equations, i.e., iterative computation which increases the computer analysis time. There is a proposal [11] which limits the solution to two iterations. However the method adopted in SPICE2.G precludes any nested iterative process based on the following assumptions:

First, define  $V_{DSAT}$  according to Eq. (3.16) with  $L_{eff} = L$  and use this value for any  $V_{DS}$  on a  $V_{CS} =$  constant characteristic. This is based on the fact that Eq. (3.17) does not provide an accurate description of the output conductance in saturation and NEFF has to be used as an empirical factor. In the expression of  $X_D$ , Eq. (3.9), NSUB is replaced by NEFF\*NSUB.

Second, good agreement of the simulated and measured I-V characteristics can be obtained by adjusting NEFF.

A closed-form solution can be obtained as follows. Eq. (3.16) can be simplified to obtain

$$v = \frac{(V_1 - \frac{V_2}{2} - \frac{x^2}{2})(x^2 - V_2) - \frac{2}{3}\gamma_S(x^3 - V_2^{\frac{3}{2}})}{V_1 - \gamma_S x - x^2}$$

(3.18)

where

$$x = \sqrt{\left[V_{DSAT} + 2\varphi_F - V_{BS}\right]}$$

$$V_1 = \frac{V_{GS} - V_{BIN}}{\eta} + 2\varphi_F - V_{DS}$$

$$V_2=2\varphi_F-V_{BS}$$

$$v = \frac{VMAX \times L_{eff}}{\mu_{S}}$$

Eq. (3.16) can be written as a quartic equation

$$x^4 + ax^3 + bx^2 + cx + d = 0 ag{3.19}$$

with

$$\alpha = \frac{4}{3} \gamma_S$$

$$b = -2(V_1 + v)$$

$$c = -2\gamma_S v$$

$$d = -V_2^2 - \frac{4}{3}\gamma_S V_2^{\frac{3}{2}} + 2V_1V_2 + 2vV_1$$

This equation can be solved by Ferrari's method. Among the 2 or 4 real roots, the smallest positive one is the valid solution; the choice is based on the fact that the equation represents the difference

$$I_{DSAT} - VMAX \times W \times Q_{CHAN}(L)$$

(3.20)

which decreases as  $V_{DSAT}$  increases.

In some cases the equation might not have a real solution. In this case the program computes  $V_{DSAT}$  based on the pinch-off approximation and prints out a message.

#### 3.4. Weak Inversion Conduction

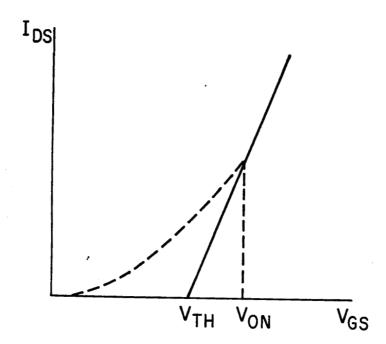

A MOSFET is not an ideal switch which starts conduction abruptly; there is current flowing in the device below the threshold voltage which marks only the onset of strong inversion. This current is known as the weak inversion or subthreshold current. The simulation of this behaviour is important for present day MOS circuits which are often designed to operate in the weak inversion region. The model implemented in SPICE2.G uses as a starting point the analysis performed by Swanson and Meindl for CMOS devices [12].

As shown in Fig. 3.4, a new threshold voltage  $V_{ON}$  is defined, above  $V_{TH}$ , which marks the transition from the weak inversion to the strong inversion characteristic;

$$V_{ON} = V_{TH} + \frac{nkT}{q} \tag{3.21}$$

where

$$n = 1 + \frac{C_{FS}}{C_{OX}} + \frac{C_D}{C_{OX}} \tag{3.22}$$

$$C_{FS} = q \times NFS \tag{3.23}$$

$$C_D = \frac{\partial Q_B}{\partial V_{BS}} = \left[ -\gamma_S \frac{d\sqrt{2\varphi_F - V_{BS}}}{dV_{BS}} - \frac{\partial \gamma_S}{\partial V_{BS}} \sqrt{2\varphi_F - V_{BS}} + DELTA \frac{\pi \varepsilon_{SI}}{4C_{OX}W} \right] C_{OX}$$

(3.24)

NFS is introduced as a parameter in the evaluation of  $V_{ON}$ . Its presence is necessary to invoke the weak inversion feature. NFS is not related to the physical nature of the subthreshold conduction, which is not determined by the fast surface state density. It is a curve-fitting parameter which can be extracted from measurements.

In the above equation it is important to notice that the quantity  $\sqrt{2\varphi_F - V_{BS}}$  which is a multiplicative factor of the depletion-charge formulation assumes that  $V_{BS}$  is negative. A more exact way to express Eq. (3.24) is to replace the square root by a  $F(V_{BS})$ . In the new MOS2 model, this function is made to decay asymptotically towards zero when  $V_{BS}$  becomes positive rather than clamp it to zero as was the case in the SPICE2.D and E versions;

$$F(V_{BS}) = \frac{\sqrt{2\varphi_F}}{1 + V_{BS}/4\varphi_F} \tag{3.25}$$

The weak inversion current equation for  $V_{CS} < V_{CN}$  is

$$I_{DS} = \beta \left[ \left( V_{ON} - V_{BIN} - \frac{\eta V_{DS}}{2} \right) V_{DS} - \frac{2}{3} \gamma_S \left[ \left( 2\varphi_F - V_{BS} + V_{DS} \right)^{\frac{3}{2}} - \left( 2\varphi_F - V_{BS} \right)^{\frac{3}{2}} \right] \right] \times e^{\frac{q}{nkT} (V_{CS} - V_{ON})}$$

(3.26)

This equation insures the continuity of the current at  $V_{ON}$  but not the continuity of the first derivative in contrast to the previous formulation [2]. This alternative has been chosen since the earlier expression suffered from introducing a negative resistance in the  $I_{DS} - V_{DS}$ ,  $V_{CS}$  =constant characteristics.

FIG. 3.4.

In order to obtain the usual aspect of the characteristics in the  $I_{DS}-V_{DS}$  plane a saturation voltage is defined at  $V_{CS}=V_{ON}$  which replaces  $V_{DS}$  in Eq. (3.26) when the latter becomes larger than the former. The role of the exponential factor is then to scale this characteristic.

### 3.5. Temperature Dependence

The MOS2 model readjusts all temperature-dependent variables in the drainsource current equation. These include

- proportionality with T of the Fermi potential  $\varphi_F$ ;

- variation with temperature of the energy gap;

- temperature dependence of the built-in voltage PB of the drain and source junctions;

- mobility variation as  $T^{-3/2}$ ;

- temperature variation of the reverse current of the diffused junctions.

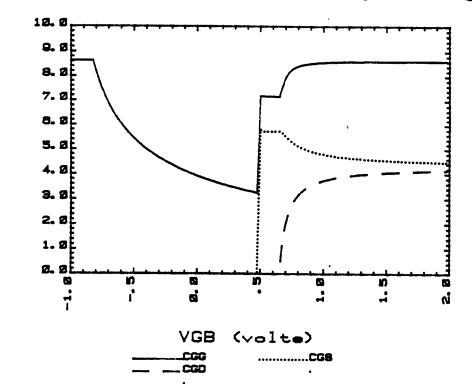

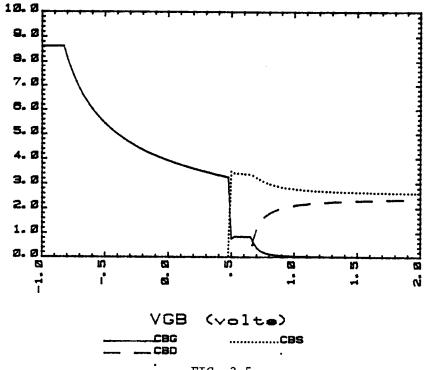

### 3.6. Charge-Oriented Model for MOSFET Capacitances

Meyer's capacitance model [13] which has been used in earlier versions of SPICE2 suffers from a fundamental weakness: it does not conserve charge. An improved formulation of the charge-oriented model proposed by Ward and Dutton [14] is used in SPICE2.G. The new model is based on the actual distribution of charge in the MOS structure and its conservation:

$$Q_{CHAN} = Q_D + Q_S = -(Q_C + Q_B) (3.27)$$

The current flowing at any terminal of a region can be related to the charge contained in that region, i.e.,

$$i_G = \frac{dQ_G}{dt}$$

$$i_B = \frac{dQ_B}{dt} \tag{3.28}$$

$$i_S + i_D = \frac{d(Q_S + Q_D)}{dt}$$

The equivalent terms of the modified nodal admittance matrix are found by using the numerical implicit integration algorithm already built into the circuit simulator for the transient analysis [15],

$$\int_{t_0}^{t_1} idt = Q(t_1) - Q(t_0)$$

(3.29)

The charges at any time point are assumed a function of only the terminal voltages at that same time point. Due to the complexity involved in finding the derivatives, a simple formulation is used for the charges [16] which is adjusted for continuity at the transitions between regions of operation. The exact formulations are the subject of a future write-up. If the trapezoidal integration formula is used, Eq. (3.29) can be rewritten as follows

$$\frac{h}{2}(i_{y1}^{1}+i_{y0})=(Q_{y1}^{0}-Q_{y0})+\sum_{x}\frac{\partial Q_{y}}{\partial V_{x}}\Big|_{V_{x1}^{0}}(V_{x1}^{1}-V_{x1}^{0})$$

(3.30)

where x stands for GB, DB and SB, and y for G, B, D and S. The subscripts indicate the time point and superscripts the iteration. Thus quantities at time point "0" are known (previous time point), quantities at time point "1" iteration "0" are also known from the solution of the last iteration at the present time point. Time "1", iteration "1" is the current iteration which, by substituting the above equation into the modified nodal system, has  $V_{21}^2$  as a solution.

Defining capacitances for the small-signal analysis

$$C_{yx} = \frac{\partial Q_y}{\partial V_x} \tag{3.31}$$

one notes that between each pair of nodes there are two capacitances, which in general are different.

Fig. 3.5. plots the voltage dependence of the various terminal capacitances associated with the  $Q_C$  and  $Q_B$  charges. Only six capacitances out of a total of twelve defined by Eq. (3.31) are independent due to the charge-conservation principle expressed by Eq. (3.27).  $Q_S$  and  $Q_D$  share equal parts of the channel charge  $Q_{CHAN}$  in the linear region. In saturation  $Q_D$  gets only  $XQC \times Q_{CHAN}$  where XQC is a model input parameter which defaults to zero;  $Q_S$  results from Eq. (3.27).

4

oapaoitanoss

<del>(</del>F

capacitanoss

### capacitances associated with bulk charge

FIG. 3.5.

### 4. THE MOSS MODEL; A SEMI-EMPIRICAL MODEL FOR SMALL GEOMETRY MOSFET'S

A small-geometry MOSFET, defined as a transistor with  $L \le 2\mu m$ , and  $W \le 2\mu m$  is characterized by the following features:

- threshold-voltage sensitivity to the length and the width of the device due to the twodimensional nature of potential distribution;

- threshold-voltage sensitivity to the drain voltage due to the drain induced barrier lowering;

- relaxed transition between linear and saturation regions, and lowered saturation voltage and saturation current due to the velocity saturation of hot electrons.

The MOS3 model has been developed to address the above features and the computational efficiency. The companion capacitance model, which conserves charge [14], is also derived and implemented.

Instead of repeating the physical explanations already presented in the previous section, the MOS3 model is described in simple terms with emphasis on the different approaches between the MOS2 and MOS3 models, followed by the parameter extraction methodology of those newly introduced parameters and the performance comparision between MOS2 and MOS3.

All the parasitic resistances, overlap and junction capacitances are described by the same parameters as in MOS2. The model parameters relating to the intrinsic MOSFET are designed to be compatible with those of MOS2. The rule of "Electrical" and "Processing" parameters also holds for MOS3. The four new parameters which are specific to MOS3 are described in Sec. 2. ETA, DELTA and KAPPA are dimensionless "Electrical" parameters, of typical values close to 1. THETA is an "Electrical" parameter of unit 1/Volt. Its typical value is approximatedly 0.1.

### 4.1. Threshold Voltage

The relationship between  $V_{TH}$ , the threshold voltage, and the substrate bias deviates from the first-order square root dependence as the device dimensions are scaled down. This is mainly because the built-in potential depends logarithmically on the substrate doping which is scaled up proportionally with the dimensions. This feature is modeled by decoupling the effects of channel length, channel width and static feedback from drain to gate. Each of these features is enabled by specifying the parameters XJ, DELTA and ETA, respectively.

The short-channel effect, the decrease of  $V_{TH}$  as the channel length is scaled down, is modelled with Dang's [17] modified trapezoidal approach, reckoning with the influence of cylindrical field distribution (see Fig. 4.1).

PHI -

$$V_{BS} = \frac{XJ^2}{X_D^2} (1 + \frac{W_C}{XJ})^2 [\ln(1 + \frac{W_C}{XJ}) - \frac{1}{2} + \frac{1}{2(1 + \frac{W_C}{XJ})}] = (\frac{W_P}{X_D})^2$$

$$\frac{W_{C}}{XJ} = d_{0} + d_{1} \frac{W_{P}}{XJ} + d_{2} (\frac{W_{P}}{XJ})^{2}$$

$$\left(\frac{W_0}{W_D + XJ}\right)^2 + \left(\frac{W_S + LD}{W_C + LD}\right)^2 = 1$$

$$W_{S} = (W_{C} + W_{D}) \left[1 - \frac{W_{0}^{2}}{(W_{P} + XJ)^{2}}\right] - LD$$

FIG. 4.1.

The narrow channel effect, the increase of  $V_{TH}$  as the channel width is scaled down, is modelled by taking into account the extra bulk charge at the edge of the channel as described in the previous section. To include other edge effects such as the existence of field implant and non-planarity due to the LOCOS process, the empirical parameter DELTA is introduced.

The static feedback effect can be explained as a consequence of the drain induced barrier lowering [18]. A term, linearly proportional to  $V_{DS}$ , is included in the  $V_{TH}$  expression. The constant of this term is inversely proportional to the oxide capacitance and the cube of the channel length [19]. The parameter ETA is introduced to allow more flexibility.

An expression for  $V_{TH}$  which sums up the above features is formulated as:

$$V_{TH} = V_{FB} + 2\varphi_F - \sigma V_{DS} + \gamma F_S \sqrt{2\varphi_F - V_{BS}} + F_N (2\varphi_F - V_{BS})$$

$$\tag{4.1}$$

where

$$\sigma = coefficient \ of \ static \ feedback$$

(4.2)

$$= ETA \frac{\Omega}{C_{OX} L^3}$$

$$\Omega = empirical\ constant$$

(4.3)

$$= 8.15 \times 10^{-22} (F \times m)$$

$$F_S = correction \ factor \ of \ short \ channel \ effect$$

(4.4)

$$=1-\frac{XJ}{L}\left[\frac{LD+W_C}{XJ}-\sqrt{1-\left(\frac{W_P/XJ}{1+W_P/XJ}\right)^2}-\frac{LD}{XJ}\right]$$

LD is the lateral diffusion length,  $W_P$  is the depletion layer width of a plane junction,  $W_C$  is the depletion layer width of a cylindrical junction and

$$\frac{W_C}{XJ} = d_0 + d_1 \frac{W_P}{XJ} + d_2 \left(\frac{W_P}{XJ}\right)^2 \tag{4.5}$$

$d_0$ ,  $d_1$  and  $d_2$  are empirical constants of values :

$$d_0 = 0.0631353$$

$$d_1 = 0.8013292$$

$$d_2 = -0.01110777$$

and

$$F_{N} = correction \ factor \ of \ narrow \ channel \ effect$$

$$= DELTA \frac{\pi \varepsilon_{SI}}{2C_{OX}W}$$

(4.6)

$$X_D = \text{coefficient of depletion layer width}$$

$$= \sqrt{\frac{2\varepsilon_{SI}}{a NSUB}}$$

(4.7)

## 4.2. Basic Drain Current Equation

The drain current can be expressed as:

$$I_{DS} = \beta \int_{0}^{V_{DS}} \left[ V_{CS} - V_{TH}(y) \right] dV_{y}$$

$$= \beta \int_{0}^{V_{DS}} \left[ V_{CS} - V_{TH} - (1 + F_{B}) V_{y} \right] dV_{y}$$

(4.8)

where

$$\beta = \frac{W}{L} \mu_{EFF} C_{OX} \tag{4.9}$$

$$F_B = \text{Taylor series expansion coefficient of bulk charge}$$

$$= \frac{\gamma F_S}{4\sqrt{2\varphi_F - V_{BS}}} + F_N$$

(4.10)

After the integration, the following equation is obtained [20]:

$$I_{DS} = \beta \left[ V_{GS} - V_{TH} - \frac{1 + F_B}{2} V_{DS} \right] V_{DS}$$

(4.11)

With such simplicity, an explicit saturation voltage expression is guaranteed. Based on the assumption that the  $V_{DS}$  dependent term in  $V_{TH}$  represents the average drain voltage influence on the channel potential, it is treated as a constant throughout the integration.

# 4.3. Surface Mobility Modulation by Gate Voltage

The simplest empirical equation is used to enhance the computational speed:

$$\mu_S = \frac{UO}{1 + THETA(V_{CS} - V_{TH})} \tag{4.12}$$

## 4.4. Velocity Saturation of Hot Electrons

The saturation of hot electron velocity lowers the conduction current in the linear region. Thus relaxes the transition between the linear and the saturation regions. In the linear region this effect is modelled by the conventional hyperbolic equation [21]:

$$\mu_{EFF} = \frac{\mu_S}{1 + \frac{\mu_S}{VMAX \times L}} V_{DS} \tag{4.13}$$

If the parameter VMAX is not specified by the user,  $\mu_{EFF}$  is set to  $\mu_S$  and this effect is not modelled.

### 4.5. Saturation Voltage

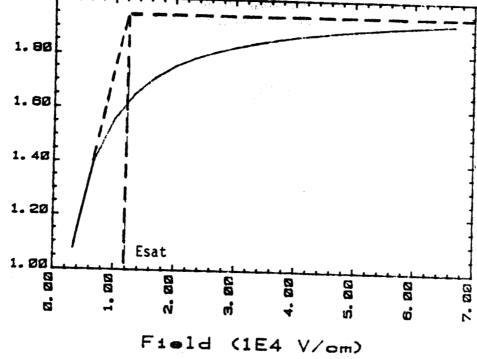

The saturation voltage of a short-channel device is the drain voltage at which the carriers asymptotically reach the maximum velocity at the drain limit (see Fig. 4.2):

$$I_{DS}^{0} = Q_{\underline{M}}(drain) VMAX (4.14)$$

After the substitution of the expressions of  $Q_{M}$  and  $I_{DS}^{0}$ , the above equation becomes :

$$\frac{W}{L}\mu_{S} C_{OX} \left[ V_{GS} - V_{TH} - \frac{1 + F_{B}}{2} V_{DSAT} \right] V_{DSAT} = W \times C_{OX} \left[ V_{GS} - V_{TH} - (1 + F_{B}) V_{DSAT} \right] VMAX$$

(4.15)

From the above equation  $V_{DSAT}$  is solved,

$$V_{DSAT} = \frac{V_{GS} - V_{TH}}{1 + F_B} + \frac{VMAX \times L}{\mu_S} - \sqrt{\frac{V_{GS} - V_{TH}}{1 + F_B}^2 + \frac{VMAX \times L}{\mu_S}^2}$$

(4.16)

$V_{DSA}$  will depend on  $V_{DS}$  if the parameter ETA is not zero. If parameter VMAX is absent from the input, the saturation voltage will be determined by the maximum of the drain current equation, corresponding to the situation of channel pinch-off:

$$V_{DSAT} = \frac{V_{GS} - V_{TH}}{1 + F_R} \tag{4.17}$$

# 4.6. Channel Length Modulation

As  $V_{DS}$  becomes greater than  $V_{DSAT}$ , the point where the carrier velocity begins to saturate moves towards the source. The channel length reduction,  $\Delta L$ , is formulated based on Baum's theory [7]:

$$\Delta L = \sqrt{\left(\frac{E_P X_D^2}{2}\right)^2 + KAPPA \times X_D^2 (V_{DS} - V_{DSAT})} - \frac{X_D^2 E_P}{2}$$

(4.18)

where

$$E_P = lateral \ field \ at \ channel \ pinch-off \ point$$

(4.19)

$$=\frac{I_{DSAT}}{G_{DSAT} \times L}$$

$I_{DSAT}$  and  $G_{DSAT}$  are the drain current and the drain conductance at saturation respectively.

It should be noted that the point where the velocity begins to saturate differs from the point where the inversion charge goes to zero, i.e., the channel pinch-off point.  $V_{DSAT}$  is the voltage at velocity saturation, while  $E_P$  is the lateral field at channel pinch-off. Thus the voltage across the depleted surface, of length  $\Delta L$ , should be less than  $(V_{DS} - V_{DSAT})$ . The parameter KAPPA is introduced to account for this effect. As  $\Delta L$  appraaches L, the same scheme as described in Sec. 3.3.1 is used to prevent a negative effective channel length.

# 4.7. Weak Inversion Conduction

The equations in the weak inversion region are the same as those used in MOS2, which provide both the continuity of the drain current, the proper bias dependence and sufficient computational efficiency. The same parameter NFS is used to turn on the weak inversion feature. For details see Sec. 3.4.

Hot Electron Velocity eaturation

2.00

FIG. 4.2.

## 4.8. Temperature Dependence

All the quantities referred to in the model equations have the same temperature dependence as in MOS2. The four newly introduced parameters are all empirical. No temperature dependence has been developed for them as yet.

# 4.9. Capacitance Model with Charge Conservation

The total amount of charge residing on the gate,  $Q_G$ , can be evaluated as:

$$Q_G = \mathcal{W} \int_0^L q_g(y) dy$$

$$= \frac{\mu_S \mathcal{W}^2}{l_{DS}} \int_0^{V_{DS}} q_g(V_y) q_c(V_y) dV_y$$

$$(4.20)$$

where

$$q_g = \text{gate charge per unit area}$$

$$= C_{OX} \left[ V_{CS} - (V_{FB} + 2\varphi_F - \sigma V_{DS}) - V_y \right]$$

(4.21)

$$q_c = channel\ charge\ per\ unit\ area$$

(4.22)

=  $-C_{OX} \left[ V_{GS} - V_{TH} - (1+F_B)\ V_y \right]$

After carrying out the integration,

$$Q_G = W \times L \times C_{OX} \left[ V_{GS} - (V_{FB} + 2\varphi_F - \sigma V_{DS}) - \frac{V_{DS}}{2} + \frac{1 + F_B}{12 F_I} V_{DS}^2 \right]$$

(4.23)

where

$$F_I = V_{GS} - V_{TH} - \frac{1 + F_B}{2} V_{DS} \tag{4.24}$$

Similarly, one can get the total bulk charge  $Q_B$  as

$$Q_{B} = -W \times L \times C_{OX} \left[ \gamma F_{S} \sqrt{2\varphi_{F} - V_{BS}} + F_{N} (2\varphi_{F} - V_{BS}) + \frac{F_{B}}{2} V_{DS} - \frac{F_{B} (1 + F_{B})}{12 F_{I}} V_{DS}^{2} \right] (4.25)$$

The total channel charge  $Q_{CHAN}$  results from the charge conservation principle,

$$Q_{CHAN} = -(Q_C + Q_B) \tag{4.26}$$

It is equally divided into the source and the drain charges in the linear region of

operation. In saturation  $Q_D$  gets a share XQC of  $Q_{CHAN}$ .

Each of these charges has three associated derivatives which are the capacitive elements in the circuit model. It should be noted that only six of these twelve capacitive components are independent.

#### 4.10. Parameter Extraction for MOS3

The characteristics of small geometry MOSFET's are sensitive to the device dimensions. The systematic parameter extraction requires measurements of several devices with different combinations of length and width, and the manipulation of the collected data. The fundamental parameters VTO, NSUB, UO and/or GAMMA and KP, which are common to both MOS2 and MOS3, should be extracted from a long and wide device, as described in next section. Only the extraction methodology of parameters relating to the second-order effects is described in the following:

## 4.10.1. THETA, Mobility Modulation Parameter

The effective surface mobility is the slope of the  $[(L \times I_{DS})/(W \times C_{OX}V_{DS})]$  versus  $V_{CS}$  plot in the linear region, at constant  $V_{DS}$  and  $V_{BS}$ , as indicated by the current equation, (4.11). Rearrange Eq. (4.12) as:

$$\frac{UO}{\mu_S} = 1 + THETA(V_{CS} - V_{TH}) \tag{4.27}$$

Clearly, parameter THETA is the slope of the  $(UO/\mu_S)$  versus  $V_{GS}$  plot. In order to isolate the gate voltage influence from the hot electron effect, the measurements of  $I_{DS}$  versus  $V_{GS}$  must be carried out at low  $V_{DS}$ , say 0.2 volts.

## 4.10.2. ETA, Static Feedback Parameter

The coefficient  $\sigma$ , the slope of the  $V_{TH}$  versus  $V_{DS}$  plot at constant  $V_{BS}$  as defined in Eq. (4.2) represents the magnitude of the static feedback effect. The determination of  $\sigma$  involves the measurement of the threshold voltage of small geometry MOSFET's at intermediate  $V_{DS}$  level. The  $V_{TH}$ 's should be determined from the  $I_{DS}$  versus  $V_{GS}$  curves at different  $V_{DS}$ , at low current levels (see Fig. 4.3).

(amp)

IDS

log

FIG. 4.3.

Other threshold voltage determination algorithms, based on either the simple saturation current equation which is proportional to the square of  $(V_{CS}-V_{TH})$  or the approximately linear current equation which is proportional to  $(V_{CS}-V_{TH}-V_{DS}/2)V_{DS}$ , does not hold because of the hot electron effect. Parameter ETA is related to  $\sigma$  by

$$ETA = \sigma \frac{C_{OX} L^3}{\Omega}$$

(4.28)

The value of the empirical constant  $\Omega$ , see Eq. (4.3), has been adjusted such that, for most practical devices, ETA assumes a value close to one.

# 4.10.3. DELTA, Width Effect on Threshold Voltage

The coefficient of the width effect on  $V_{TH}$  at constant  $V_{ES}$ , relates inversely to the channel width as indicated by Eq. (4.6). DELTA relates to  $F_N(2\varphi_F - V_{BS})W$ , the slope of  $V_{TH}$  versus 1/W plots, as:

$$DELTA = slope \frac{2 C_{OX}}{\pi \varepsilon_{SI}} \frac{1}{(2\varphi_F - V_{BS})}$$

(4.29)

Its value varies from process to process.

### 4.10.4. VMAX, Limited Velocity of Hot Electrons

The effective mobility at intermediate  $V_{DS}$  level deviates from the value at low  $V_{DS}$ ,  $\mu_S$ . The parameter VMAX can be estimated as follows: measure  $I_{DS}$  versus  $V_{CS}$  at different fixed  $V_{DS}$ 's, extract the effective mobility,  $\mu_{EFT}$ , from the collected data, and finally plot  $(1/\mu_{EFT}-1/\mu_S)$  versus  $V_{DS}/L$ . The slope of this plot is the inverse of VMAX as indicated by the rearrangement of Eq. (4.13):

$$\frac{1}{\mu_{EFF}} - \frac{1}{\mu_S} = \frac{V_{DS}}{VMAX \times L} \tag{4.30}$$

#### 4.10.5. KAPPA, Correlation Coefficient of the Drain Field in Saturation

The extraction of parameter KAPPA from measurement is not as straight forward as for the other parameters. First, one has to estimate the approximate saturation voltage and saturation current using the VMAX obtained, as above. Then the channel length reduction can be estimated as:

$$\Delta L = L(1 - \frac{I_{DS}}{I_{DSAT}}) \tag{4.31}$$

The slope of the  $\Delta L^2$  versus  $V_{DS}$  plot is approximately  $KAPPA \times X_D^2$ .

## 4.11. Performance Comparison between MOS2 and MOS3

Though MOS2 and MOS3 share most of the model parameters, different values for the same parameter must be used to produce approximately the same characteristics. For example, the parameter VMAX has no effect on the linear region characteristics of MOS2, while it lowers the effective mobility of MOS3. In order to get a match, a lower value for UO in MOS2 is required.

The  $V_{BS}$  dependence of the basic drain current equation in MOS3 is an approximation of that in MOS2. With all other parameters being properly adjusted for a specific device, say  $L=5\mu m$ ,  $NSUB=4\times10^{15}$  cm<sup>-3</sup> and  $TOX=0.1\mu m$ , this approximation only introduces about 2% deviation in the case of  $V_{CS}$  well above  $V_{TH}$ . The deviation increases to 20% when the gate voltage is only 0.5 volts above  $V_{TH}$ . However, in the latter case, the device is already approaching subthreshold conduction and the basic strong inversion theory begins to fail.

The benchmark runs with SPICE2.G indicate that, with compatible input parameters, the MOS3 model is up to 40% faster in the model computation time as compared with MOS2, depending upon the nature of the circuit and its operation.

#### 5. HODEL PARAMETER EXTRACTION of the little statement and the little st

Naturally the accuracy of the results of a MOS IC simulation depends heavily on the values of the model input parameters. The I-V characteristics predicted by the equations of the model must match very closely the measured characteristics. The complexity of the equations in Sec. 3 is such that some computer aids are required to obtain the program value of the device parameters. The best results are obtained if a characterization system is set up [22] which has as core a desk-top or a mini computer which controls the measuring instruments and does the necessary computations for finding the model parameters. The equations implemented in the parameter extraction program must be identical to those used in the circuit simulator. A data acquisition software designed for a certain model provides accurate input parameters only for that particular model. When the model is changed, the parameter extraction software has to be changed as well.

Another tool necessary for parameter extraction is a test chip which should have the following features:

- a short- and a long channel MOSFET;

- a narrow- and a wide channel device;

- diffused resistances;

- poly-silicon resistances;

- a rectangular and a meander form junction capacitor;

- a thin and a field oxide capacitor.

A desired feature of the parameter extraction software is to find the spread of the parameters for a number of wafer runs and to group the parameters according to a certain criterion, e.g., speed or power consumption, into a worst, best and nominal case input file [23].

It is the purpose of this section to illustrate the methodology and the minimum hardware software to extract the main input parameters for the MOS2 model. The reported work has been performed using a Tektronix 4051 desktop calculator, Tektronix 576 curve tracer, a C-V measuring instrument and a multimeter.

### 5.1. VTO and NSUB Measurement

The measurement is taken on a saturated transistor connected to a curve tracer. Since at this starting point few parameters are known, the saturated characteristic is approximated by a parabola rather than using the exact current equation given in Sec 3.

$$CJ = \frac{C_{J1}}{A_1}$$

where  $C_{J1}$  is the ordinate at the origin of the C-V plot and  $A_1$  is the area (known) of the rectangular capacitor. The measured results indicate that MJ is very close to 0.5.

CJSW and MJSW can be found using a linear regression through the  $(V_R, C_{J2})$  data points of the meander-form diffusion. Eq. (5.4) can be rewritten as

$$\log C_K = \log (P \times CJSW) - MJSW \times \log \left(1 + \frac{V_R}{PB}\right)$$

(5.5)

where

$$C_K = C_{J2} - A_2 \frac{CJ}{\left(1 + \frac{V_R}{PB}\right)^{1/2}}$$

(5.6)

The data processing is performed by PROGRAM1 (see Appendix 1) which in response to the point pairs  $(V_R, C_{J2})$  and other constants displays the result of the interpolation, i.e., CJSW and MJSW.

If MJ = 0.5 is not adequate, PROGRAM1 can be easily modified to perform the same linear regression as Eq. (5.5) for the large rectangular capacitor only to find MJ.

#### 5.3. Mobility Parameter Extraction

Finding the parameters which describe the mobility variation with the surface field is very important for an accurate simulation of the I-V characteristic. UO, UCRIT and UEXP which appear in the mobility degradation formula of MOS2 (see Eq. (2.7)), must be found.

The experimental setup allows independent variation of  $V_{DS}$  and  $V_{CS}$  on the curve tracer and to extract data points from the linear- (very low  $V_{DS}$ ) and triode region up to  $V_{DSAT}$ .

A straight line can be interpolated through these data points by rearranging Eq. (2.7)

$$\log\left[\frac{\mu_S}{UO}\right] = UEXP \left[\log\left(\frac{\varepsilon_{SI}}{C_{OX}}UCRIT\right) - \log\left(V_{GS} - V_{TH} - UTRA \times V_{DS}\right)\right]$$

(5.7)

where

$$-\sqrt{\frac{I_{DS}}{KP'}} = V_{CS} - V_{TH} \tag{5.1}$$

The threshold  $V_{TH}$  is taken as the intercept on the abscissa of the above linear regression through the coordinate pair  $(\sqrt{I_{DS}}, V_{GS})$ . Several  $V_{TH}$  are calculated; one for each  $V_{BS}$ .

$$V_{TH} = VTO + GAMMA(\sqrt{V_{SB} + PHI} - \sqrt{PHI})$$

(5.2)

where PHI =  $2\varphi_F$ . From another straight line interpolated in the plane  $(\sqrt{V_{SH} + PHI}, V_{TH})$ , the slope gives GAMMA and

$$NSUB = \frac{GAMMA^2}{2q \, \varepsilon_{SI}} \left( \frac{\varepsilon_{OX}}{TOX} \right)^2 \tag{5.3}$$

All the above extrapolations are performed by PROGRAM1 written in BASIC for the Tek 4051 the listing and operating instructions of which are contained in Appendix 1. The user has mainly to input only the  $(I_{DS}, V_{GS})$  point pairs and the  $V_{BS}$  stepping and the program will display VTO, GAMMA and NSUB.

These measurements should be performed on a long and wide channel MOSFET since the above values will then be corrected by the program for small-size effects. For more accuracy the extraction program could perform one more iteration once the first estimate has been found for VTO and NSUB and use the exact current equation as implemented in MOS2.

#### 5.2. Capacitance Measurements

As has been already mentioned in Sec. 2 the junction capacitance is separated into a bottom and a sidewall capacitance

$$C_{JTOT} = A \frac{CJ}{\left[1 + \frac{V_R}{PB}\right]^{MJ}} + P \frac{CJSW}{\left[1 + \frac{V_R}{PB}\right]^{MJSW}}$$

$$(5.4)$$

where A represents the plane area (on layout), P the perimeter and  $V_R$  the reverse bias applied to the junction.

CJ can be found first by assuming that the sidewall capacitance of the large rectangular capacitor is negligible. From a C-V plot, one gets

$$\frac{\mu_S}{UO} = \frac{KP_i}{KP_0} \tag{5.8}$$

with

$\mathit{KP}_i$  - conduction factor for different  $\mathit{V}_{\mathit{GS}}$

KPo - maximum value of conduction factor

UEXP and UCRIT are obtained from the above linear regression as the slope and y intercept respectively by plotting  $\log(KP_i/KP_0)$  on the y- and  $\log(V_{GS}-V_{TH}-UTRA\times V_{DS})$  on the x axis.

The data processing is performed again by PROGRAM1 by specifying  $(V_{DS}, V_{CS}, I_{DS})$  points where for different  $V_{CS}$  curves different maximum  $V_{DS}$  values are entered in order to cover each characteristic up to  $V_{DSAT}$ . PROGRAM1 computes UO, UCRIT and UEXP for each  $V_{DS}$  range and at the end displays an average for each of the three values over the whole interval.

## 5.4. Approximation of VMAX

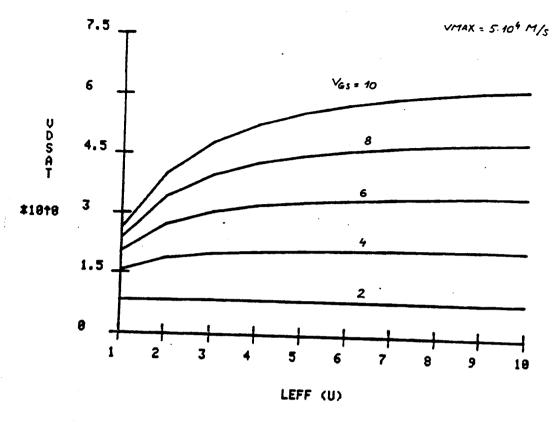

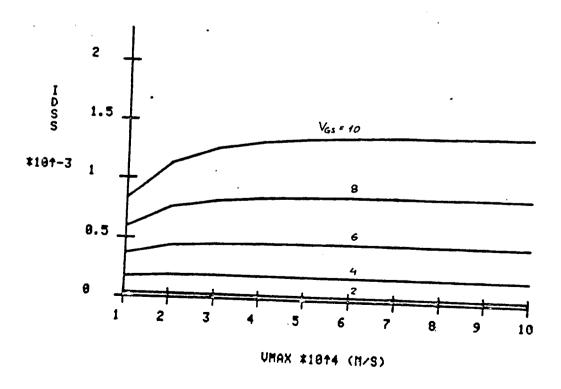

A second program written in BASIC for the Tek 4051, PROGRAM2 (see Appendix 2) helps with its two options to evaluate VMAX. The first alternative is to plot  $V_{DSAT}$  as a function of the effective channel length L with  $V_{GS}$  as a parameter. For each VMAX, one gets a different set of curves. Fig. 5.1. shows such a sample plot.

The second option plots  $I_{DSAT}$  as a function of VMAX with  $V_{GS}$  as a parameter. A different set of curves results for each L. A sample plot for this option is shown in Fig. 5.2.

Starting from the measured characteristics one defines  $V_{DSAT}$  as the voltage starting from which the I-V curve can be approximated by a straight line and the current corresponding to this point is  $I_{DSAT}$ . With these values one can get a good guess for VMAX from plots similar to those in Fig. 5.1. and 5.2. It is emphasized that PROGRAM2 uses the same equations as those implemented in SPICE2.G for  $V_{DSAT}$  (VMAX).

FIG. 5.1.

FIG. 5.2.

#### 6. SIMULATION EXAMPLE

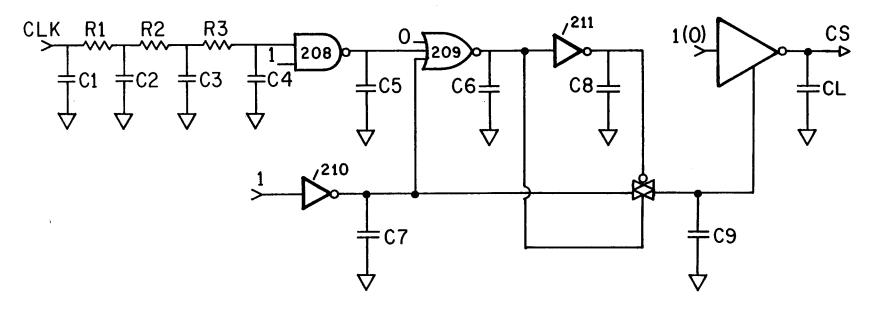

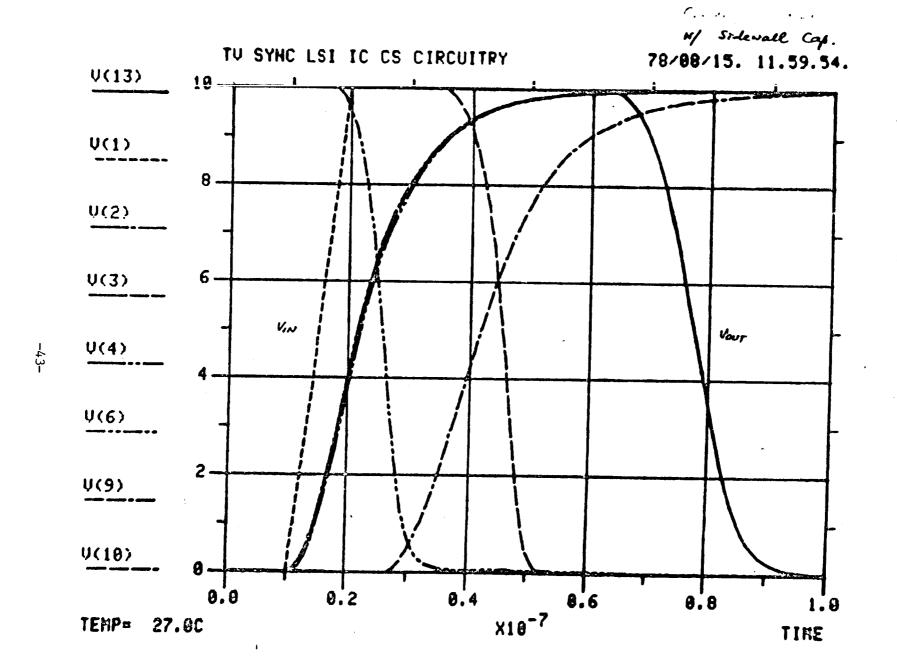

It is the purpose of this example to show the ease with which a section of a CMOS LSI circuit is accurately simulated starting from the layout and using the new device card format and model input parameter. The circuit of Fig. 6.1 represents a short path of a MOS/LSI circuit. The output signal CS generated from CLK can be measured at an output pad and compared with the simulated waveform. The input deck for SPICE2.G is given in Appendix 3.

The measured circuit chips were located on the same wafer with the test patterns from which the parameter extraction has been performed. For an accurate simulation all the parasitics of the layout must be included;  $R_1$  represents the series resistance of the input pad protection while  $R_2$  and  $R_3$  represent crossunder diffusions. Each C includes all the capacitive effects associated with that node, e.g.,  $C_1$  is contributed by Al to-Field oxide, Poly to-field, N+ and P+ junctions and thin oxide, where for each the accurate overlap area must be evaluated. Each of the gates has been modeled as a subcircuit. A load capacitance of 100pF has been used; the rest is attributed to the probe and parasitics. Fig. 6.2 shows a sample simulated output of the waveforms.

An interesting result has been obtained by performing the simulation with and without sidewall capacitance and with and without scattering-limited drift-velocity effects (VMAX). The input file given in Appendix 3 is complete in the sense that it includes series resistance, sidewall capacitance and drift velocity saturation. The devices which have no perimeter specified had a negligible sidewall compared to the area.

The results of the different simulations and the measured values are summarized in Table I. It can be noticed that the above two effects contribute a 15 to 20% accuracy improvement and the simulated results of this circuit containing 22 MOSFET's is within 5 to 10% of the results for the actual circuit.

FIG. 6.1.

FIG. 6.2.

TABLE I

|                                  |                        |          | SIMULATED    |         |             |         |

|----------------------------------|------------------------|----------|--------------|---------|-------------|---------|

| PARAMETER                        |                        | MEASURED | W/O Sidewall |         | W/ Sidewall |         |

|                                  |                        |          | W/C VMAX     | W/ VMAX | W/O VMAX    | W/ VMAX |

| Delay                            | C <sub>L</sub> = 20pF  | 64 - 75  | 49           | 51      | 60          | 62      |

| T <sub>D</sub> (N <sub>S</sub> ) | C <sub>L</sub> = 120pF | 90 - 105 | 70           | 79      | 81          | 91      |

| Fall Time                        | C <sub>L</sub> = 20pF  | 32 - 36  | 22           | 24      | 24          | 26      |

| T <sub>F</sub> (N <sub>S</sub> ) | C <sub>L</sub> = 120pF | 85 - 120 | 90           | 100     | 94          | 102     |

# Appendix 1

# User Instructions and Listing of PROGRAM1

Load the program from the tape cartridge (Tektronix 4051) by typing:

FILE n CR

# VTO, GAMMA, and NSUB Interpolation

# Calculator prompts:

TYPE OF LIN REGRESSION, DEVICE TYPE,

NO. OF POINT PAIRS, NO. OF CURVES

#### Answer

| GAMMA                                               | CR |

|-----------------------------------------------------|----|

| N (or P)                                            | CR |