# The Threshold–Voltage Model of MOSFET Devices with Localized Interface Charge

Yuh-Sheng Jean, Student Member, IEEE, and Ching-Yuan Wu, Member, IEEE

Abstract—A new analytic threshold-voltage model for a MOS-FET device with localized interface charges is presented. Dividing the damaged MOSFET device into three zones, the surface potential is obtained by solving the two-dimensional (2-D) Poisson's equation. Calculating the minimum surface potential, the analytic threshold-voltage model is derived. It is verified that the model accurately predicts the threshold voltage for not only the fresh devices but also the damaged devices. Moreover, the Drain-Induced Barrier Lowering (DIBL) and substrate bias effects are also included in this model. It is shown that the screening effects due to built-in potential and drain bias dominate the impact of the localized interface charge on the threshold voltage. Calculation results show that the extension, position and density of localized interface charge are the main issues to influence the threshold voltage of a damaged MOSFET device. Simulation results using a 2-D device simulator are used to verify the validity of this model, and quite good agreements are obtained for various cases.

# I. INTRODUCTION

T IS WELL KNOWN that the hot-carrier effect becomes a great obstacle as the dimensions of the MOSFET devices are scaled down to submicrometer or deep submicrometer level. The hot-carrier effect is mainly caused by the high electric field in the channel near the drain junction for a short channel device. This high field provides enough energy to the channel electrons which may generate electron-hole pairs through impact ionization. The generated holes are attracted to the substrate to form the substrate current and the electrons are swept toward to the drain. If the electrons get enough energy to reach the S<sub>i</sub>-S<sub>i</sub>O<sub>2</sub> interface and surmount the barrier, the gate current is resulted. This gate current more or less creates damage in the oxide or on the interface near the drain junction and device performance is degraded. Characteristics degradation of short-channel MOSFET devices due to hot-carrier injection has attracted many comprehensive studies in recent years [1]–[12]. It is known that the degradation is attributed to the interface-trap generation and electron/hole trapping in the gate oxide [1]-[4]. Due to its strong impacts on device and circuit reliability, the hot-carrier effect becomes an important research topic for submicrometer and deep submicrometer MOSFET devices.

The hot-carrier-induced degradations include transconductance  $(g_m)$  degradation, drain conductance  $(g_d)$  degradation

Manuscript received May 28, 1996; revised September 17, 1996. The review of this paper was arranged by Editor C.-Y. Lu. This work was supported by the National Science Council, Taiwan, R.O.C., under Contract NSC86-2215-E009-034.

The authors are with the Advanced Semiconductor Device Research Laboratory and Institute of Electronics, National Chiao-Tung University, Hsin-Chu, Taiwan, R.O.C.

Publisher Item Identifier S 0018-9383(97)01487-1.

and threshold–voltage shift. Many models have been proposed to describe device performance degradations [5]–[9]. Moreover, different charge pumping methods have been proposed to measure the interface trap and oxide-trapped charge [10]–[12]. Unfortunately, all of the previous analytic models [5]–[8] didn't consider the two-dimensional (2-D) effects. Furthermore, the degradations of I–V characteristic in damaged MOSFET's were comprehensively studied [6], [9] only by using the 2-D device simulator.

In this paper, we devote our efforts on the threshold-voltage shift due to the hot-carrier-induced localized interface charges. The surface potential distribution along the channel of a MOS-FET with localized interface fixed charge has been analytically derived by using proper assumptions and boundary conditions, based on solving the simplified 2-D Poisson's equation. The minimum surface potential along the channel is then used to calculate the threshold voltage. Depletion depth under the channel is also properly modified by the geometric factor using the charge sharing scheme. Consequently, the effects of drain bias and source/drain junction depth have been elegantly included. If the interface trap or oxide-trapped charge exists, it can be transformed into equivalent interface fixed charge. In addition, the effects of the extension, position and density of localized interface charges, drain bias, substrate bias on the threshold voltage are also investigated. Comparisons between the developed threshold-voltage model and the results of the 2-D numerical analysis have been made and quite good agreements have been obtained. Although our discussions are focused on n-channel MOSFET devices, similar results can be extended to p-channel MOSFET devices straightforwardly after polarity change.

# II. MODEL DESCRIPTIONS

The 2-D Poisson's equation can be written as

$$\frac{\partial^2 \phi(x,y)}{\partial x^2} + \frac{\partial^2 \phi(x,y)}{\partial y^2} \\

= \frac{q}{\epsilon_s} [N_A(y) + N_D(y) + n(x,y) + p(x,y)] \tag{1}$$

where  $N_A(y)$  and  $N_D(y)$  are the acceptor and donor concentrations in the substrate, respectively; n(x,y) and p(x,y) are the electron and hole concentrations, respectively;  $\epsilon_s$  is the dielectric permittivity of the substrate;  $\phi(x,y)$  is the electrostatic potential in the substrate; and the coordinate system is shown in Fig. 1. To a first-order approximation, the potential distribution is assumed to have the following form

$$\phi(x,y) = a_0 + a_1 y + a_2 y^2 + a_3 y^3 \tag{2}$$

where the a's may be a function of x and can be determined by the boundary conditions. Substituting (2) into (1) and integrating y from 0 to  $y_d$ , we have

$$\frac{\partial^{2} a_{0}}{\partial x^{2}} + \frac{\partial^{2} a_{1}}{\partial x^{2}} \frac{y_{d}}{2} + \frac{\partial^{2} a_{2}}{\partial x^{2}} \frac{y_{d}^{2}}{3} + \frac{\partial^{2} a_{3}}{\partial x^{2}} \frac{y_{d}^{3}}{4} + 2a_{2} + 3a_{3}y_{d}(3)$$

$$= \frac{q}{\epsilon_{s} y_{d}} \left[ \int_{0}^{y_{d}} N_{A}(y) dy + n_{s}(x) \right]$$

where  $y_d$  is the depletion depth;  $N_D(y)$  is neglected in a n-channel MOSFET device; p(x,y) is also ignored in the depletion and/or inversion region;  $n_s(x)$  is the electron concentration per unit area. The boundary conditions on the interface and depletion edges are given as

$$\begin{cases}

\phi(x,0) &= \phi_s(x) \\

\phi(x,y_d) &= V_{BS} \\

\frac{d\phi(x,y)}{dy}|_{y=0} &= \frac{C_{ox}}{\epsilon_s} [\phi_s(x) - V_{GS} + V_{FB}] \\

\frac{d\phi(x,y)}{dy}|_{y=y_d} &= 0

\end{cases}$$

(4)

where  $V_{GS}$  and  $V_{BS}$  are the gate and substrate biases, respectively;  $\phi_s(x)$  is the surface potential;  $C_{\rm ox}$  is the gate oxide capacitance per unit area;  $V_{FB}$  is the flat-band voltage. Note that if the interface fixed charge density  $N_f$  appears uniformly in this device,  $V_{FB}$  should be replaced by  $V_{FB} + \frac{qN_f}{C_{\rm ox}}$ . From (2)–(4), we can obtain

$$\phi_s''(x) - k^2 \phi_s(x) = -k^2 [V_{GS} - V_{FB} - \frac{Q_{\text{dep}}}{C_{\text{ox}}} - \frac{q n_s(x)}{C_{\text{ox}}}]$$

(5)

where

$$k^2 = 12C_{\text{ox}}/[(6\epsilon_s + C_{\text{ox}}y_d)y_d]$$

(6)

and  $Q_{\rm dep}=q\int_0^{y_d}N_A(y)dy$ . The representation of k in (6) is slightly different from that in [13], due to the fact that we integrate y from 0 to  $y_d$  in (4) to include the coupling effect of depletion charge. Actually, the terms in the bracket in the right side of (5) is the surface potential of a long channel device. While the device is operated in the depletion region, the electron concentration can be neglected. Therefore, the bracket in the right side of (5) is reduced to  $[V_{GS}-V_{FB}-\frac{qQ_{\rm dep}}{C_{\rm ox}}]$ , which is just the surface potential under depletion approximation. However, if the gate bias  $V_{GS}$  is larger than the threshold voltage  $V_T$ , it is nearly fixed at  $2\phi_B (=2\frac{kT}{q}\ln(\frac{N_A}{n_i}))$ , the approximated surface potential at strong inversion.

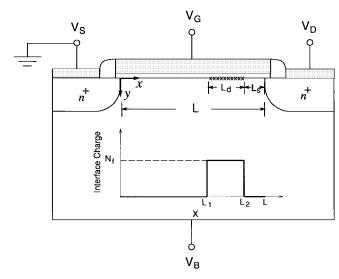

For a damaged MOSFET device shown in Fig. 1, an n-channel MOSFET device with a damaged zone  $L_d$  (where interface fixed charges are described by a step function for simplicity) is illustrated. In general, the stress-induced interface charges in an n-channel MOSFET are almost negative charges and/or acceptor-type interface trap. Therefore, the increasing gate bias turns on the damage-free zones before the damaged one. However, no matter what type of the localized interface charge is, in order to turn on this device, the damaged and damage-free zones must be considered separately.

Fig. 1. Illustration of a damaged nMOSFET.

Applying (5) to this device, we have

$$\phi_s''(x) - k^2 \phi_s(x) = \begin{cases} -k^2 \phi_1 & 0 \le x \le L - L_d - L_s \\ -k^2 \phi_2 & L - L_d - L_s \le x \le L - L_s \\ -k^2 \phi_3 & L - L_s \le x \le L \end{cases}$$

(7)

where  $\phi_1 = \phi_3 = V_{GS} - V_{FB} - \frac{Q_{\text{dep}}}{C_{\text{ox}}}$ , which represents the surface potential in the damage-free zones;  $\phi_2 = \phi_1 - \frac{qN_f}{C_{\text{ox}}}$  is the surface potential in the damaged zone. However, if  $\phi_1$ ,  $\phi_2$ , or  $\phi_3$  are larger than  $2\phi_B$ , it will be set to  $2\phi_B$ . Note that the density  $N_f$  can be negative or positive for different types of interface fixed charge. Solving (7), the solution of the surface potential is (see the Appendix)

$$\phi_{si}(x) = b_i e^{kx} + c_i e^{-kx} + \phi_i, \quad i = 1, 2, 3$$

(8)

where  $b_i$  and  $c_i$  are represented in the Appendix. In general, the threshold voltage is defined as the gate bias at which the minimum surface potential is  $2\phi_B$ . This definition is also adopted in this paper. In order to calculate the threshold voltage, the minimum potential of (8) is represented as

$$\phi_{\min,i} = 2\sqrt{b_i c_i} + \phi_i, \quad i = 1, 2, 3.$$

(9)

If the criterion  $\phi_{\min,i} = 2\phi_B$  is used, and substituting  $b_i$ ,  $c_i$  and  $\phi_i$  into (9), we can obtain the threshold voltage

$$V_T = V_{T0} + \frac{qN_f}{C}\delta(i-2) - 2\sqrt{b_i c_i}, \quad i = 1, 2, 3 \quad (10)$$

where  $V_{T0}=V_{FB}+2\phi_B+\frac{Q_{\rm dep}}{C_{\rm ox}};~\delta(i-2)$  is equal to 1 for i=2 and 0 for i=1,3, respectively. Note that even though  $b_i$  and  $c_i$  are functions of  $V_{GS}$ , (10) will reduce to the analytic form as proposed in [13] if the damaged zone is vanished. In the cases of the damaged devices, we give an initial guess of  $V_{GS}=V_{T0}$  into (10), it will converge after few iterations. Due to the three zones of the device, there are three values of  $V_T$  in (10). However, only one of them is the correct value, the others are the larger one or an unreasonable one.

Similar to [13],  $Q_{\rm dep}$  and k in (5) are modified and the depletion depth  $y_{d,\rm eff}$  (effective depletion depth) is modified as

$$y_{d,\text{eff}} = y_d \cdot f \tag{11}$$

where f is the geometric factor of the charge sharing scheme [13,] [14], which is functions of channel length L, substrate bias  $V_{BS}$ , drain bias  $V_{DS}$  and S/D junction depth  $R_j$ .

So far, we have developed the threshold–voltage model for the devices with interface fixed charge. As the interface trap appears at the  $S_i$ – $S_i$ O $_2$  interface, it is known that it will accept an electron if the trap level locates beneath the Fermi level for an acceptor-type interface trap. In this situation, it acts as negative interface fixed charge. Therefore, it can be approximated to equivalent interface fixed charge by

$$N_f = \int_{E_V}^{E_{Finv}} D_{it}(E) dE \tag{12}$$

where  $D_{it}(E)$  is the interface trap density per energy interval per area;  $E_V$  is the energy level of valence band;  $E_{Finv}$  is the Fermi level as the device is operated at threshold voltage, and can be expressed as

$$E_{Finv} = E_V + \frac{E_G}{2} + kT \ln \frac{N_A}{n_i}$$

(13)

where  $E_G$  is the bandgap of silicon. For a donor-type interface trap, (12) will be integrated from  $E_{F\mathrm{inv}}$  to  $E_C$  (energy level of conduction band) and it acts as positive interface fixed charge. However,  $E_V$  in (13) should be replaced by  $E_C$  and positive sign will be replaced by negative sign. Similarly, the oxide-trapped charge can be treated as equivalent interface fixed charge if it locates near and not far away from the  $\mathrm{S_{i}}\mathrm{-S_{i}O_{2}}$  interface. This behavior is very similar to that of interface fixed charge and can be approximated by

$$N_f = \frac{1}{qT_{\text{ox}}} \int_{-T_{\text{ox}}}^0 (T_{\text{ox}} + y) \rho_{\text{ox}}(y) dy$$

(14)

where  $\rho_{\rm ox}(y)$  is the volume oxide-trap density. In general, the localized distributions of hot-carrier-induced interface traps and oxide-trapped charge densities can be profiled by the well-known charge-pumping technique [10]–[12]. The energy distribution in the bandgap of interface traps is treated by (12) and (13), while the spatial distributions of interface-traps and oxide-trapped charge can be approximated by an equivalent step function by using the principle of charge conservation. Using these simple transformations as described above, we can extend our model to all general cases for hot-carrier-induced damages.

## III. NUMERICAL RESULTS AND COMPARISONS

In this section, a 2-D device simulator—SUMMOS [15] is used to verify the validity of the analytic model as described in the last section. The important device parameters used in this paper are listed in Table I. The channel doping of these devices is uniform to simplify the calculation. Using (10), we calculate the threshold voltage of damaged-free device. The threshold voltage of both analytic model and 2-D device

TABLE I

THE STRUCTURE PARAMETERS OF MOSFET DEVICES

USED FOR THIS MODEL AND 2-D DEVICE SIMULATOR

| Gate Oxide Thickness $T_{\text{ox}}$         | 100 Å                                       |

|----------------------------------------------|---------------------------------------------|

| Flat-band Voltage $V_{\mathrm{FB}}$          | -0.84 V                                     |

| Channel Doping $N_A$                         | $1.0 \times 10^{17} \ \mathrm{cm^{-3}}$     |

| S/D Doping $N_{\mathrm{SD}}$                 | $1.0 \times 10^{20} \ \mathrm{cm^{-3}}$     |

| S/D Junction Depth $\mathrm{R}_{\mathrm{j}}$ | $0.2~\mu\mathrm{m}$                         |

| Interface Charge Density $N_{\rm f}$         | $\pm 1.0 \times 10^{12} \ \mathrm{cm^{-2}}$ |

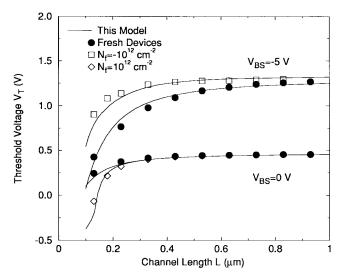

Fig. 2. Calculated threshold voltage versus channel length for both damage-free and damaged MOSFET devices, where the drain bias is 50 mV. The marks are the simulation results while the lines are the results of our model. For damaged devices, the  $L_d=0.1~\mu{\rm m}$  and  $L_s=0~\mu{\rm m}$ .

simulator are defined by the minimum surface potential equal to  $2\phi_B$ . The results are the filled circles as shown in Fig. 2, in which the drain voltage is 50 mV. It is shown that the calculation results of the analytic model fits well with the simulation results for fresh devices. These facts indicate that our analytic model is also suited to predict the short-channel effect of the MOSFET's.

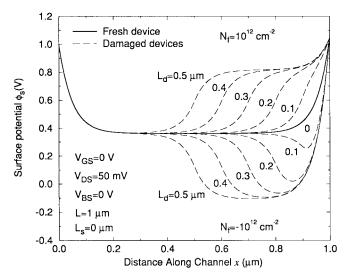

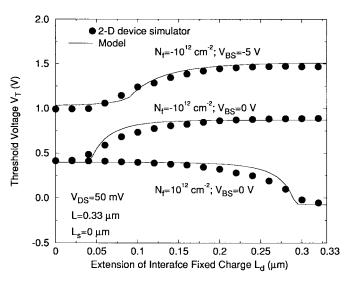

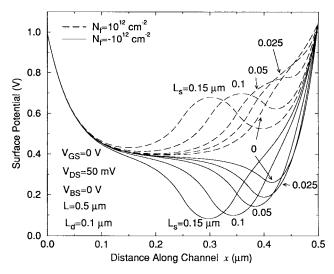

If the interface charge appears in the Si-SiO2 interface or in oxide, as shown in Fig. 1, the surface potential of this device is distorted. As the negative interface charge occurs near the drain side, the surface potential in the damaged zone is lowered. The lower curves in Fig. 3 show that the surface potential is gradually lowered by increasing the extension  $(L_d)$ of interface fixed charge but keeping the gate bias at 0 V. The minimum surface potential is therefore shifted from the source side to the damaged zone. Due to the screening effects of builtin potential and applied bias in the drain side, the lowered potential is not considerable until  $L_d$  is large. Moreover, the lowered potential becomes saturated as  $L_d$  is large enough, this phenomenon reflects to the threshold voltage shown the middle curve in Fig. 4. As  $L_d$  is small, due to the influences of built-in potential and drain bias in the drain side, the threshold voltage is only slightly increased. However, while  $L_d$  is large enough, the threshold voltage is increased drastically. Finally,

Fig. 3. Surface potential distribution for various extensions of positive (upper curves) and negative (lower curves) interface fixed charge.

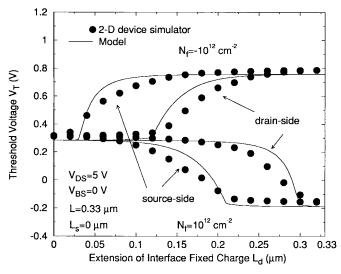

Fig. 4. Threshold-voltage variation versus extension for various conditions.

the threshold voltage is saturated to the value  $V_{T0} + \frac{qN_f}{C_{\rm ox}}$ , which is the maximum threshold voltage of a given negative interface fixed charge density. As indicated in the upper curve in Fig. 4, it shows the similar results while the substrate bias is raised to -5 V. The difference is that, it needs larger  $L_d$  to raise  $V_T$  due to the stronger screening effect as the substrate bias is raised.

For a positive interface fixed charge, the surface potential is raised, as shown in the upper curves of Fig. 3. The channel length seems to be reduced and the minimum surface potential is nearly unchanged. Nevertheless, as  $L_d$  is large enough or the channel length is short, the minimum surface potential is raised. Therefore, the threshold voltage is unchanged initially and then is lowered as  $L_d$  is large. Similar to the negative charge, it becomes saturated to the value  $V_{T0} - \frac{qN_f}{C_{\rm ox}}$ , which is the minimum threshold voltage of a given positive interface fixed charge density. The lower curve in Fig. 4 indicates these phenomena. As the channel length is shortened, the influences of the damages on the  $V_T$  become more apparent, as shown

Fig. 5. Threshold voltage variation versus extension for various conditions.

in Fig. 2. As seen from Fig. 2, the negative charge increases  $V_T$  even the channel length is long while the positive charge decreases  $V_T$  only as the channel length is very short. In either case, the  $V_T$  shift increases as the channel is shortened. It can also be easily understood from the explanations as mentioned above.

In general, the position  $(L_s)$  of damages for a stressed MOSFET device is located near the drain side, and the reason is that the gate oxide near the drain suffers the most strongest electric field and the high field-induced hot-carriers will attack this region to create permanent damages. However, the device is measured reversely(source and drain exchanged) or worked as a pass transistor, the damages may be regarded as located near the source side. If the drain bias is small, the surface potentials for the interface fixed charge in the source and drain are nearly symmetrical. The position of minimum surface potential for them may be different, but the minimum surface potential is nearly the same for those two cases. As a consequence, the variations of threshold voltage make no difference between the interface fixed charge near the source and drain sides as the drain bias is small. While the drain bias is large, in addition to the built-in potential, the damage near the drain side suffers the strongest screening effect for the drain bias, therefore its influence on  $V_T$  is reduced. On the contrary, the damage near the source side only suffers the screening effect for the built-in potential, therefore the threshold voltage raises at  $L_d \simeq 0.03 \,\mu\mathrm{m}$  while it raises at  $L_d \simeq 0.12 \,\mu\mathrm{m}$  for the damage near the drain side as shown in Fig. 5.

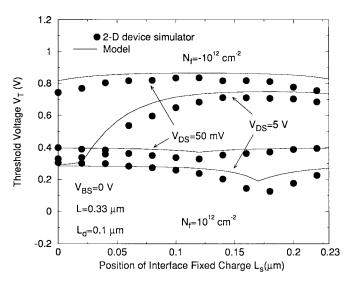

The stress-induced damage is not always located near the drain (or source) side and may be located in the channel region i.e.,  $L_s$  in Fig. 1 is not zero. For negative interface fixed charge, the screening effects for drain bias and built-in potential are gradually reduced by increasing  $L_s$ , the minimum potential is lowered as the solid curves shown in Fig. 6. This effect is apparent, especially as  $L_s$  is small or drain bias is large, because the screening effects are large in these cases. The upper curves in Fig. 7 show that the variations of the threshold voltage with the position of the negative interface fixed charge. Note that  $L_s=0~\mu\mathrm{m}$  and  $L_s=0.23~\mu\mathrm{m}$

Fig. 6. Surface potential distribution for various positions. The solid and dashed curves are with negative and positive interface fixed charges, respectively.

Fig. 7. Threshold voltage versus position for drain bias at 50 mV and 5 V. The upper and lower curves are with negative and positive interface fixed charges, respectively.

represent that the damage is located near the drain and source sides, respectively. As the drain bias is small, the variation of  $V_T$  is not apparent. It slightly increases with  $L_s$  and then decreases slightly as the interface fixed charge is shifted to the source side, which is nearly symmetrical in the drain side as the drain bias is small. A totally different aspect can be observed for a large drain bias. Because the screening effect in the drain side is much larger than that in the source side, the damage in the drain side will not cause  $V_T$  shift much until the damage is shifted toward to the source. As it reaches the source side,  $V_T$  is slightly lowered due to the weak screening effect in the source side.

For positive interface fixed charge, as the dashed curves in Fig. 6, the minimum potential is raised as  $L_s$  increases. The positive charge acts as a new source of the screening effect. If it is located in the source or drain side, its influence is not apparent as it is located in the center of channel. However,

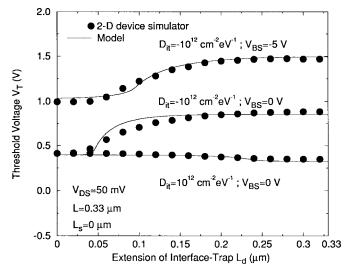

Fig. 8. Threshold voltage variation versus extension for various conditions of interface trap.

as the channel length is small or  $L_s$  is comparable to channel length, its strong screening effect is visible. As the damaged zone is gradually moving from the drain side to the center of channel, the minimum potential is located in the source side and is gradually raised as the screening effect of positive interface fixed charge. While the damaged zone is gradually moving from the center of channel to the source side, the minimum potential is located in the drain side and is gradually lowered as the screening effect of positive interface fixed charge is away. Therefore, the threshold voltage in Fig. 7 is nearly symmetrical as  $V_{DS}$  is 50 mV. Similar results are expected as  $V_{DS}$  is large, except that it is not symmetrical due to the larger screening effect in the drain side than that in the source side.

In Fig. 8, we implement uniform interface trap to 2-D device simulator, and the interface traps are distributed in the bandgap with negative (acceptor-type) and positive (donor-type)  $D_{\rm it}$  of  $10^{12} {\rm cm}^{-2} eV^{-1}$ . For acceptor-type interface trap, according to (12) and (13), the equivalent interface fixed charge is approximated to be  $-9.7 \times 10^{11} {\rm cm}^{-2}$ . On the other hand, it is  $1.5 \times 10^{11} {\rm cm}^{-2}$  for donor-type interface trap. Both of their effects on the threshold voltages are well-predicted by our model. It is worth noting that the donor-type interface trap has minor influence on nMOSFET devices unless its density is very high.

### IV. CONCLUSIONS

Based on the simplified 2-D Poisson's equation, a new analytic threshold–voltage model for a MOSFET device with localized interface charge is derived. The MOSFET device is divided into three zones and each zone has a second-order differential equation. Applying the constraints of potential and electric field continuity to solve these equations, combined with the boundary conditions in the source and drain boundaries, the surface potential is obtained. In addition, the minimum surface potential is set to  $2\phi_B$  to define the threshold voltage, the analytic threshold–voltage model is then derived and few iterations are needed to calculate it. In addition,

the interface trap and oxide-trapped charge can be treated as effective interface fixed charge. The derived threshold-voltage model is related to the extension, position, type, and density of localized interface charges, drain bias, substrate bias, and other basic structure parameters of MOSFET devices.

The typical behavior of threshold voltage for damage-free MOSFET device is easily obtained by our model. Simulation results by a 2-D device simulator are demonstrated to verify the validity of this model. The substrate-bias and DIBL effects are also well predicted. As the localized interface charge occurs, the screening effects in the source and drain sides dominate the impacts of localized interface charge on the threshold voltage. The larger drain bias make the screening effect stronger, but the damaged zone out of the influence of the screening effect dominates the threshold-voltage shift. In addition, the calculation results are verified by a 2-D numerical device simulator, and quite good agreements are obtained.

### **APPENDIX**

The continuity of surface potential and electric field in (8) must satisfy at  $x = L - L_d - L_s$  and  $x = L - L_s$ , i.e.,

$$\phi_{s1}(L - L_d - L_s) = \phi_{s2}(L - L_d - L_s)$$

(A-1)

$$\phi_{s2}(L - L_s) = \phi_{s3}(L - L_s)$$

(A-2)

$$\phi'_{s1}(L - L_d - L_s) = \phi'_{s2}(L - L_d - L_s)$$

(A-3)

$$\phi'_{s2}(L - L_s) = \phi'_{s3}(L - L_s) \tag{A-4}$$

and the boundary conditions at the source and drain edges are

$$\phi_{s1}(0) = V_{bi} \tag{A-5}$$

$$\phi_{s3}(L) = V_{bi} + V_{DS} \tag{A-6}$$

where  $V_{\rm bi}$  is the built-in potential of the source/drain junction. From (A-1) to (A-6), there are six unknown parameters and six independent equations. Therefore, we can solve the  $b_i$  and  $c_i$  as follows:

$$b_2 = \frac{d_3 d_5 - d_2 d_6}{d_1 d_5 - d_2 d_4}$$

$$c_2 = \frac{d_1 d_6 - d_3 d_4}{d_1 d_5 - d_2 d_4}$$

(A-7)

(A-8)

$$c_2 = \frac{d_1 d_6 - d_3 d_4}{d_1 d_5 - d_2 d_4} \tag{A-8}$$

$$b_1 = \frac{(V_{\text{bi}} - \phi_1)e^{-kL_1} + b_2e^{kL_1} - c_2e^{-kL_1}}{2\cosh kL_1}$$

$$c_1 = \frac{(V_{\text{bi}} - \phi_1)e^{kL_1} - b_2e^{kL_1} + c_2e^{-kL_1}}{2\cosh kL_1}$$

(A-10)

$$c_1 = \frac{(V_{\text{bi}} - \phi_1)e^{kL_1} - b_2e^{kL_1} + c_2e^{-kL_1}}{2\cosh kL_1}$$

(A-10)

$$b_3 = \frac{(V_{\text{bi}} + V_{DS} - \phi_1)e^{-kL_2} + (b_2e^{kL_2} - c_2e^{-kL_2})e^{-kL}}{2\cosh kL_s}$$

$$c_{3} = \frac{(V_{\text{bi}} + V_{DS} - \phi_{1})e^{kL_{2}} - (b_{2}e^{kL_{2}} - c_{2}e^{-kL_{2}})e^{kL}}{2\cosh kL_{s}}$$

(A-12)

where

$$d_1 = (1 - \tanh kL_1)e^{kL_1} \tag{A-13}$$

$$d_2 = (1 + \tanh kL_1)e^{-kL_1} \tag{A-14}$$

$$d_3 = \phi_1 - \phi_2 + \frac{V_{\text{bi}} - \phi_1}{\cosh k L_1}$$

(A-15)

$$d_4 = (1 + \tanh kL_s)e^{kL_2}$$

(A-16)

$$d_5 = (1 - \tanh k L_s)e^{-kL_2}$$

(A-17)

$$d_6 = \phi_1 - \phi_2 + \frac{V_{DS} - V_{bi} - \phi_1}{\cosh k L_s}$$

(A-18)

$$L_1 = L - L_d - L_s \tag{A-19}$$

$$L_2 = L - L_s. (A-20)$$

### REFERENCES

- [1] K. K. Ng and G. W. Taylor, "Effects of hot-carrier trapping in n- and p-channel MOSFET's," IEEE Trans. Electron Devices, vol. ED-30, p.

- [2] K. R. Hofmann, W. Weber, C. Werner, and G. Dorda, "Hot carrier degradation mechanism in n-MOSFET's," in IEDM Tech. Dig., 1984,

- [3] B. S. Doyle, M. Bourcerie, J. C. Marchetaux, and A. Boudou, "Interface state creation and charge trapping in the medium-to-high gate voltage  $range(V_d/2 \ge V_g \ge V_d)$  during hot-carrier stressing of n-MOS transistor," *IEEE Trans. Electron Devices*, vol. 37, p. 744, Mar. 1990.

- [4] B. S. Doyle, M. Bourcerie, C. Bergonzoni, R. Benecchi, A. Bravis, K. R. Mistry, and A. Boudou, "The generation and characterization of electron and hole traps created by hole injection during low gate voltage hotcarrier stressing of n-MOS transistors," IEEE Trans. Electron Devices, vol. 37, p. 1869, Aug. 1990.

- [5] F. C. Hsu and S. Tam, "Relationship between MOSFET degradation and hot-electron-induced interface-state generation," IEEE Electron Device Lett., vol. EDL-5, p. 50, Feb. 1984.

- H. Haddara and S. Cristoloveanu, "Two-dimensional modeling of locally damaged short-channel MOSFET's operating in the linear region," *IEEE* Trans. Electron Devices, vol. ED-34, p. 378, Feb. 1987.

- [7] S. Shabde, A. Bhattacharyya, R. S. Kao, and R. S. Muller, "Analysis of MOSFET degradation due to hot-electron stress in terms of interfacestate and fixed-charge generation," Solid State Electron., vol. 31, no. 11, p. 1603, 1988.

- I. Kurachi, N. Hwang, and L. Forbes, "Physical model of drain conductance,  $g_d$ , degradation of NMOSFET's due to interface state generation by hot carrier injection," IEEE Trans. Electron Devices, vol. 41, p. 964,

- [9] A. Schwerin, W. Hansch, and W. Weber, "The relationship between oxide charge and device degradation: A comparative study of n- and p- channel MOSFET's," IEEE Trans. Electron Devices, vol. ED-34, p. 2493, Dec. 1987.

- [10] P. Heremans, J. Witters, G. Groeseneken, and H. E. Maes, "Analysis of the charge pumping technique and its application for the evaluation of MOSFET degradation," IEEE Trans. Electron Devices, vol. 36, p. 1318, Jul. 1989

- H. H. Li, Y. L. Chu, and C. Y. Wu, "A new simplify charge-pumping current model and its model parameter extraction," IEEE Trans. Electron Devices, vol. 43, p. 1857, Nov. 1996.

- ., "A novel charge-pumping method for extracting the lateral dis-[12] tributions of interface-trap and effective oxide-trapped charge densities

- in MOSFET devices," *IEEE Trans. Electron Devices*, to be published. C. Y. Wu and S. Y. Yang, "An analytic and accurate model for the threshold voltage of short channel MOSFET's in VLSI," Solid State Electron., vol. 27, no. 7, p. 651, 1984.

- C. Y. Wu, G. S. Huang, and H. H. Chen, "An analytic threshold-voltage model for short-channel enhancement mode n-channel MOSFET's with double born channel implantation," Solid State Electron., vol. 29, no. 4, p. 387, 1986.

- [15] R. K. Perng, P. S. Lin and C. Y. Wu, "A new methodology for developing a fast two-dimensional MOSFET device simulator," Solid State Electron., vol. 34, no. 6, p. 635, 1991.

Yuh-Sheng Jean (S'90) was born in Taiwan, R.O.C., on July 5, 1968. He received the B.S. degree in electrical engineering from the National Central University, Taiwan, in 1990. He is currently pursuing the Ph.D. degree at the Institute of Electronics, National Chiao-Tung University. His research areas focus on deep-submicrometer MOS device physics and reliability issues.

Ching-Yuan Wu (M'72) was born in Taiwan, R.O.C., on March 18, 1946. He received the B.S. degree in electrical engineering from the National Taiwan University, Taiwan, in 1968, and the M.S. and Ph.D. degrees from the State University of New York (SUNY), Stony Brook, in 1970 and 1972, respectively. During the 1972–1973 academic year, he was appointed as a Lecturer in the Department of Electronical Sciences the same university. During the 1973–1975 academic years, he was a Visiting Associate Professor at the National Chiao-Tung

University, Taiwan.

In 1976, he became Full Professor in the Department of Electronics and the Institute of Electronics, National Chiao-Tung University, Hsin-Chu, Taiwan. While there, he was the Director of the Engineering Laboratories and Semiconductor Research Center from 1974 to 1980, the Director of the Institute of Electronics from 1978 to 1984, and the Dean of the College of Engineering from 1984 to 1990. He was a principal investigator of the National Electronics Mass Plan-Semiconductor Devices and Integrated-Circuit Technologies from 1976 to 1979, and had been a Coordinator of the National Microelectronics Researches and High-Level Man-Power Education Committee, National Science Council, R.O.C., from 1982 to 1988. He has been the Research Consultant of the Electronics Research and Service Organization (ERSO), ITRI, a member of the Academic Review Committee in the Ministry of education, and the chairman of the Technical Review Committee on Information and Microelectonics Technologies at the Ministry of Economic Affairs. His research activities have been in semiconductor device physics and modeling, integrated-circuit designs, and technologies. His current research areas focus on the developments of efficient 2-D and 3-D simulators for deep-submicrometer semiconductor devices, design rules and optimization techniques for deep-submicrometer CMOS devices. He has published over 180 papers in the semiconductor field and has served as a reviewer for international journals such as IEEE ELECTRON DEVICE LETTERS. IEEE TRANSACTIONS ON ELECTRON DEVICES, and Solid State Electronics.

Dr. Wu is a member of the Honorary Editorial Advisory Board of *Solid State Electronics*, and is a board member of the Chinese Engineering Society. He received the Academic Research Award in Engineering from the Ministry of Education (MOE), in 1979 and the Outstanding Scholar Award from the Chinese Educational and Cultural Foundation in 1985. He received the outstanding research Professor fellowship from the Ministry of Education and the National Science Council (NSC), Republic of China from 1982 to 1995. He received the Distinguished Engineering Professor Medal Award from the Chinese Engineering Society in 1992.