# Theory and Engineering of Scheduling Parallel Jobs

zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften

von der KIT-Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

**Dissertation**

von

**Jochen Matthias Speck**

aus Heidelberg

Tag der mündlichen Prüfung: 14.12.2017

Erster Gutachter: Prof. Dr. Peter Sanders Zweiter Gutachter: Prof. Dr. Klaus Jansen

| Hiermit versichere ich, die Arbeit selbstständig angefertigt, alle Hilfsmittel und alles, was aus Arbeiten anderer entnommen wurde, angegeben oder kenntlich gemacht zu haben. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jochen Speck                                                                                                                                                                   |

|                                                                                                                                                                                |

|                                                                                                                                                                                |

#### **Abstract**

Scheduling in the context of computer science is finding an efficient execution plan called schedule for a single job (scheduling internal tasks) or a set of jobs on a computing system. This includes assigning the used resources, for example cores or memory/cache space as well as setting other parameters like operating frequencies. Of course the found schedule should be feasible and realizable. Good schedules are important for an efficient usage of computing systems regarding different goals like high throughput, small power consumption or small makespans. Also it is important that the computation of the schedule itself does not require too much time or resources.

Nowadays computers are usually parallel machines with several concurrently working cores. Also the used applications (especially the ones with a high computation demand) are more and more parallelized today. Hence the scheduling of parallel applications is becoming an important factor of the efficiency and performance of today's computing systems.

Scheduling is a large field investigated in many different contexts and with many different approaches. For example the "Handbook of Scheduling" (edited by Joseph Y-T. Leung) has 1224 pages and references about 2000 other scientific works in the field. Even scheduling parallel jobs on parallel machines is a large field. Despite the invested effort there is a large gap between research in scheduling theory and the engineering solutions for the scheduling of parallel jobs used for experimental research or production implementations.

Our approach is to study the developments in theory as well as in practice (engineering) and to use the knowledge from both sides to produce results which might narrow the gap. One reason for the gap between theory and practice is that the scheduling models used in theory assume more knowledge about the jobs than the knowledge which is available in practice. Furthermore, some models from theory assume even a possibility for the system scheduler to change the behavior of the applications which does not exist in practice yet. But there are approaches

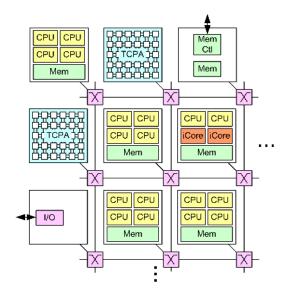

to make the applications more adaptive to changes of the system status and to provide more information for the operating system. One example of developments that aim to improve the information exchange between operating system and applications and also the adaptivity of applications is the InvasIC project. The author of this work took part in this project for four years which led to a collaboration with experts for many different parts of modern computer systems. The improved information exchange and the adaptivity of applications are engineering steps which change the system such that results from scheduling theory are better applicable. Especially the model of malleable jobs, which can adapt their resource usage during runtime, looks like a fitting counterpart to the InvasIC developments on the theoretical side.

During our work within InvasIC we were able to identify four main research directions for the scheduling of parallel computing systems (each described in its own chapter):

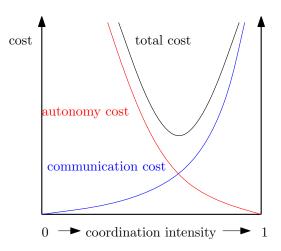

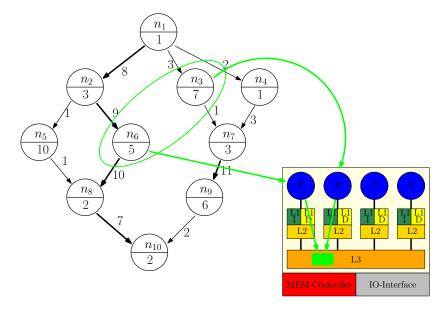

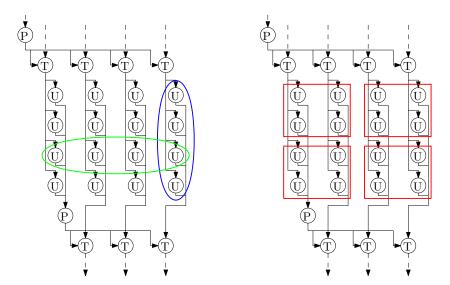

- Distribution of decisions and information among the different decision makers within the system. In modern systems different decision makers are present, for example the OS scheduler or application-internal schedulers. These schedulers need some kind of coordination to produce good results.

- Fast and efficient finding of good decisions (the classical problem researched in scheduling theory). The efficient solution of the often complex scheduling problems remains the core of every scheduling system. A large basis for this can be found in scheduling theory.

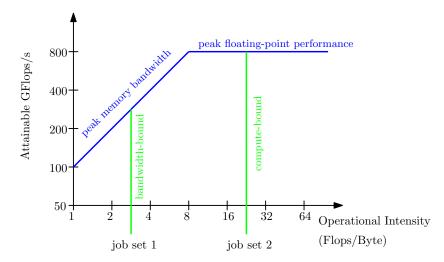

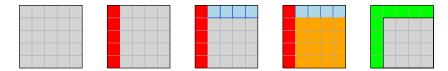

- *The efficient usage of memory and caches.* The efficient usage of the memory system is a central requirement to reach high performance and efficiency.

- The reduction of power and energy usage. Energy consumption and heat issues are a main barrier against easy performance gains through increasing clock speeds. Moreover the rise of battery-powered devices increases the importance of this area.

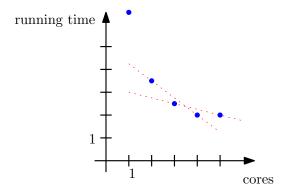

This work presents results in all of these four areas. The main result of this work is a fast scheduling algorithm for malleable jobs that finds optimal schedules given that the problem fulfills some conditions. The objective functions that are minimized by our main algorithm can be either maxima of job properties or sums of job properties. We also show that our main algorithm can be parallelized and that the parallel version finds an optimal schedule in a polylogarithmic time when the number of participating cores is at least as large as the number of jobs. This makes this algorithm the first parallel scheduling algorithm for problems with parallel jobs (to our knowledge). Some applications of the main algorithm are presented including the minimization of the energy consumption of a set of malleable jobs. To our knowledge, the application to energy minimization is the

first algorithm to optimally solve the energy minimization for a problem with malleable jobs. Besides the main result we also describe a heuristic for the fast and efficient scheduling which has proved successful in a competition.

Regarding the coordination and the information exchange between different schedulers, this work contains some general considerations from other fields and an example of a malleable application and a fitting interface.

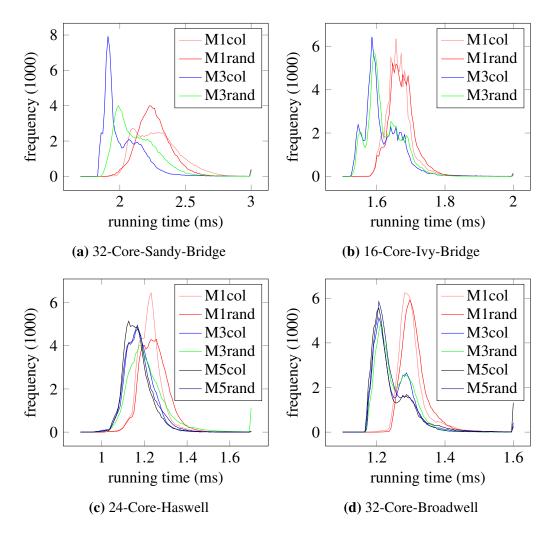

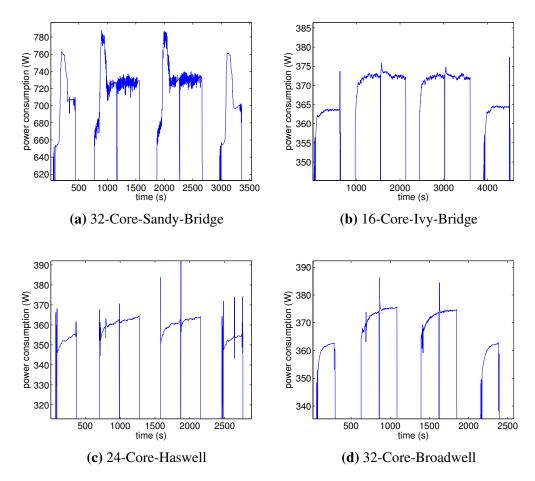

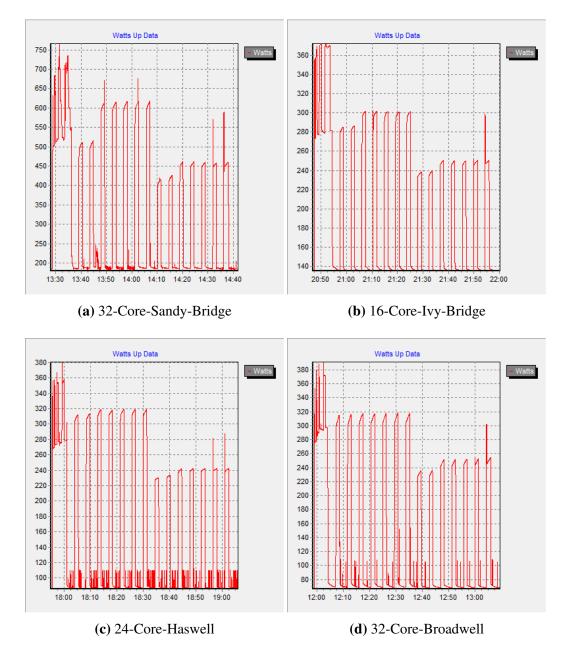

The memory and cache behavior of modern computers is investigated with extensive experiments in this work. Two case studies of memory-optimizations for real-world problems were conducted with our contributions. Their results are described following the basic experiments regarding cache and memory behavior. We also look into the power consumption of memory operations.

# Acknowledgements

There are many people I have to thank for their help and support during my way into research and during writing this thesis. As nobody will read 20 pages of acknowledgements, I have to focus on the most important ones.

First of all I wish to thank my doctoral advisor Peter Sanders for his numerous ways in supporting me. He not only introduced me into many interesting topics (especially scheduling) and helped me with his wide knowledge about computer science and research methodology but also left me a great amount of freedom. During my time in his group I had the opportunity to learn a lot from him. I also wish to thank Klaus Jansen for taking time to review my thesis and for his helpful remarks.

For their help during the writing of my thesis I would like to thank Veit Batz for his help with the thesis layout, Timo Bingmann for the discussions about properties of memory hierarchies, Marius Hillenbrand for discussions about the Linux kernel and some helpful literature suggestions in that area and Lorenz Hübschle-Schneider for proofreading parts of my thesis. I also would like to thank all my paper co-authors Felix Brandt, Patrick Flick, Tobias Maier, Peter Sanders, Raoul Steffen, Jesper Larsson Träff and Markus Völker. The collaboration with you was a pleasure. Further thanks go to my current and former colleagues at the chair of Peter Sanders especially to Veit Batz, Christian Schulz and Timo Bingmann for the interesting and instructional work-related and non-work-related discussions. The time in the research group was enjoyable and I learned a lot. In addition I would like to thank the InvasIC team for introducing me into many different parts of modern computer systems and for all discussions that helped my understanding of scheduling problems.

Special thanks go to my parents Elisabeth Speck and Wolfram Speck for their countless ways of supporting me. I would also like to thank my uncle Bernhard Westermann for introducing me to computers and programming.

# **Contents**

| Intr | oduction and Formal Basics                                   | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1  | Introduction                                                 | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.2  | Formal Descriptions and Complexity                           | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.1 3-Field Problem Classification                         | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.2 Computational Complexity                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.3 Approximations and Heuristics                          | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Scho | duling Fundamentals                                          | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1  | Importance and Cost of Large Computations                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.2  |                                                              | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.1 Reasons for Parallelization                            | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                              | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.3 Further Development                                    | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.3  | <del>_</del>                                                 | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.4  |                                                              | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.5  |                                                              | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.6  |                                                              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                              | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.7  |                                                              | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Scho | duling of Computer Systems                                   | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.1  | Developments in Theory                                       | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                              | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                              | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                              | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                              | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.1<br>1.2<br>Sche<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | 1.2 Formal Descriptions and Complexity 1.2.1 3-Field Problem Classification 1.2.2 Computational Complexity 1.2.3 Approximations and Heuristics  Scheduling Fundamentals 2.1 Importance and Cost of Large Computations 2.2 Parallel Computing Systems 2.2.1 Reasons for Parallelization 2.2.2 Build and Structure 2.2.3 Further Development 2.3 Possible Suboptimal Development Results 2.4 Parallel Computer Systems in Use 2.5 Abstraction Hierarchies and Interfaces 2.6 Algorithm Engineering and Modelling 2.6.1 Algorithm Engineering 2.6.2 Important Models 2.7 Introduction to Invasive Computing  Scheduling of Computer Systems 3.1 Developments in Theory 3.1.1 Models 3.1.2 Basic Solutions and Properties 3.1.3 Parallel Job Scheduling |

|   |      | 3.1.5   | Energy Scheduling                                           |

|---|------|---------|-------------------------------------------------------------|

|   |      | 3.1.6   | Parallel Computation of Schedules 61                        |

|   |      | 3.1.7   | Further Enhancements 62                                     |

|   | 3.2  | Develo  | opments in Scheduling Practice                              |

|   |      | 3.2.1   | Linux Completely Fair Scheduler 62                          |

|   |      | 3.2.2   | Scheduling in the Memory Hierarchy 67                       |

|   |      | 3.2.3   | Other Examples for Scheduling Practice 67                   |

|   | 3.3  | _       | etween Theory and Practice                                  |

|   | 3.4  |         | Approach                                                    |

|   |      | 3.4.1   | Development Paths                                           |

|   |      | 3.4.2   | Methodology                                                 |

|   |      | 3.4.3   | Detailed Research Directions                                |

|   |      | 3.4.4   | Results                                                     |

| 4 | Hiei | archica | al and Distributed Scheduling 77                            |

|   | 4.1  |         | ation                                                       |

|   | 4.2  |         | s in Other Areas                                            |

|   | 4.3  |         | on Distribution in Computer Science                         |

|   |      | 4.3.1   | Reasons                                                     |

|   |      | 4.3.2   | Characteristics                                             |

|   |      | 4.3.3   |                                                             |

|   |      | 4.3.4   | Problems                                                    |

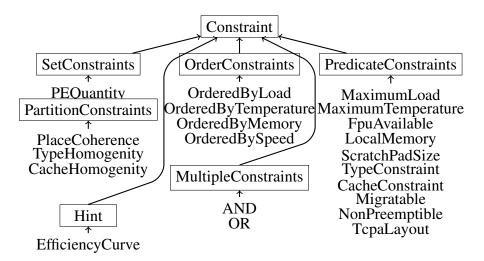

|   | 4.4  | Invasiv | ve Computing Results                                        |

|   |      | 4.4.1   | Main Ideas and Approaches 91                                |

|   |      | 4.4.2   | Development                                                 |

|   | 4.5  | Ideas f | for Improvement                                             |

|   | 4.6  |         | able Sorting                                                |

| 5 | Fact | and Ff  | ficient Schedule Computation 111                            |

| J | 5.1  |         | lexity and Justifiable Efforts                              |

|   | 5.2  | -       | ons for Malleable Jobs                                      |

|   | 3.2  | 5.2.1   | Continuous Convex Problems                                  |

|   |      | 5.2.2   | Using Continuous Domain Solutions for Discrete Problems 121 |

|   |      | 5.2.3   | Core Algorithm                                              |

|   |      | 5.2.4   | Parallelization                                             |

|   |      | 5.2.5   | Applications and Examples                                   |

|   |      | 5.2.6   | Techniques for Enhanced Problems                            |

|   | 5.3  |         | al Optimization Methods in Scheduling                       |

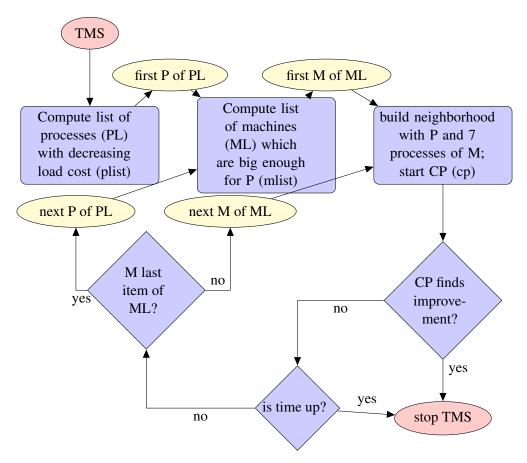

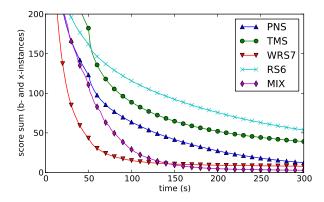

|   |      | 5.3.1   | ROADEF/EURO Challenge 2012                                  |

|   |      | 5.3.2   | Our Approach to the Challenge                               |

|   |      | 5.3.3   | Results of the Challenge                                    |

|   |      |         | 5                                                           |

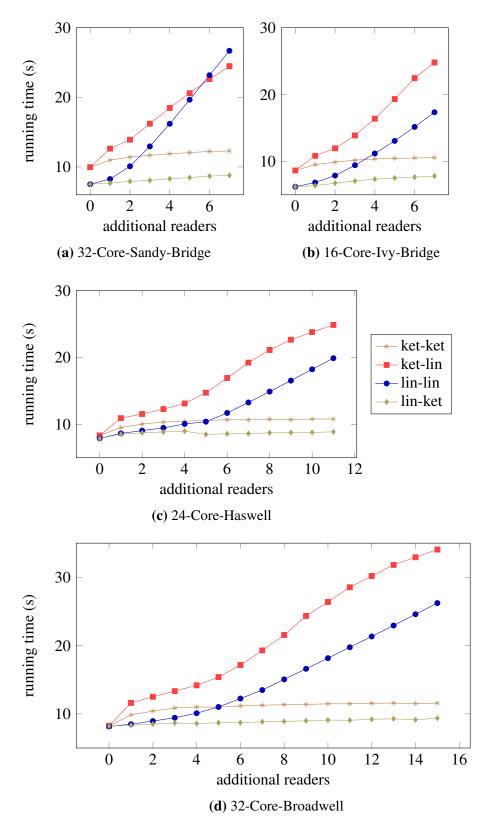

| 6  | Sch    | eduling in the Memory Hierarchy      | 195 |

|----|--------|--------------------------------------|-----|

|    | 6.1    | Properties of Memory Hierarchies     | 196 |

|    | 6.2    | Memory Scheduling                    | 209 |

|    |        | 6.2.1 Memory Bandwidth Distribution  |     |

|    |        | 6.2.2 Improvement of Cache Usage     |     |

| 7  | Pow    | er and Energy                        | 233 |

|    | 7.1    | Clock Speed                          | 234 |

|    |        | 7.1.1 Clock Speed for Malleable Jobs |     |

|    |        | 7.1.2 Enhancements                   |     |

|    | 7.2    | Memory Hierarchies                   |     |

| 8  | Con    | clusion                              | 251 |

|    | 8.1    | Summary                              | 251 |

|    | 8.2    | Outlook                              |     |

|    | 8.3    | Open Problems/Future Work            |     |

| Bi | bliog  | raphy                                | 255 |

| De | eutsch | ne Zusammenfassung                   | 269 |

# 1

## **Introduction and Formal Basics**

#### 1.1 Introduction

What is Scheduling? Given a set of jobs scheduling is making the decision when, with which worker and how to do each of these jobs. For example if a large numerical computation consisting of many small sequential jobs has to be done on a parallel computer, it has to be decided when to compute each job, which core does the computation and maybe the operating frequency of the selected core has to be determined. Of course, there might be a lot of constraints for this decision, for example job A has to be completed before job B starts, two jobs should not run on the same core at the same time or there might be an upper power limit for the computer. There are also some possible goals for a good scheduling like "completing the whole computation as fast as possible" or "using as little energy as possible". Finding a schedule has obviously also some practical constraints: finding the schedule should be fast compared to the whole computation and the schedule should not consume too much memory.

The scheduling of a large numerical computation is an example for the field of scheduling problems. Such problems can be categorized by their four main properties:

- Decision Space: What can be decided, for example which job will run on which core.

- Properties and Constraints: What are the main properties of the jobs and cores, for example the amount of work in each job. What restricts the possible decisions, for example two jobs cannot run on the same core at the same time.

- Goal: What is the goal of these decisions, for example to finish the whole computation as fast as possible.

- Information: Which properties are known by the scheduler, for example the

running time of the small jobs.

In order not to get lost in details the actual setting of a scheduling problem is usually reduced to a **model** to get rid of the unnecessary details. This also helps to find similarities between different scheduling problems.

Scheduling is a quite common part of many activities. If you want to cook a meal consisting of meat, potatoes and vegetables you have to schedule when to prepare each of the three parts and when to cook them (Baker and Trietsch [9] also use a cooking example in their introduction on page 2). Maybe each of the three parts needs a different time on the hotplate. If your goal is to get the meal ready as fast as possible a typical scheduling decision might be to prepare the part which needs the longest time on the hotplate first, so you can prepare the other parts while the first is already cooking. This description already implies a simplified model. There might be possibilities to reduce the cooking time by using a higher temperature for example, but this is not part of the described decision space.

Nobody will think about a formal schedule for a job like cooking, but scheduling (maybe without an explicit name) has a long history as some kind of time planning was probably done (even hundreds of years ago) for example while building large bridges or cathedrals. One of the first methods of planning jobs formally were Gantt charts introduced at the beginning of the 20th century (see Wilson [142]). These charts made job durations and dependencies explicit, but it remained in the responsibility of the scheduler (a real person in the first half of the 20th century) and his intuition to create a good schedule from this information.

Scheduling algorithms appeared much later. One of the first scheduling algorithms was Johnson's algorithm for finding an optimal sequence in a job shop problem, which was published in 1954 [82]. Hu's algorithm (published in 1961 [68]) for scheduling a task-DAG to parallel workers is one of the first scheduling algorithms for parallel workers. These algorithms and the introduction of computers into manufacturing planning built the basis for modern scheduling.

Scheduling is now a very big field for example the "Handbook of Scheduling" [93] one of many books about scheduling has 1224 pages and references about 2000 other scientific works in the field. Scheduling also plays an important role in many different application fields from computer science to manufacturing planning over logistics to civil engineering (a book about scheduling especially aimed at civil engineers is [69]). Scheduling is an important tool in these fields to reach several important goals or combinations of them:

- · Meet deadlines

- Speed up projects

- Increase the efficiency of workers

- Maximize throughput

- · Reduce costs

- Decide the most efficient application of resources

Hence scheduling plays an important role in the worldwide economy to provide economic wealth, to reduce resource usage and to provide on time service. More general optimization (like scheduling) is the often underestimated power that improves efficiency in all parts of society (from plant schedules to faster journey times) and hence facilitates a high standard of living.

In the first years after the invention of useful programmable computers in the 1940s **scheduling in computer science** was no important topic. Until the early 1960s most computers where specialized machines for either numerical computations or business management computations (see Tanenbaum and Bos [129, page 9] and Tanenbaum and Austin [128, page 38,39]). The programs were either run by the programmers (who reserved the machine for a certain time) or by batch processing. Especially there was at most one (sequential) program ready to run at the same time. Hence there was no decision space for a scheduler inside the computer. Thus the first schedulers inside computers appeared with the invention of multi-programming. Multi-programming was introduced in the early 1960s to use the waiting time for input in one program to run another one (see Tanenbaum and Bos [129, page 11]). Having now possibly more than one program ready to run at the same time there was a real decision to make. Since then schedulers are a typical part of operating systems.

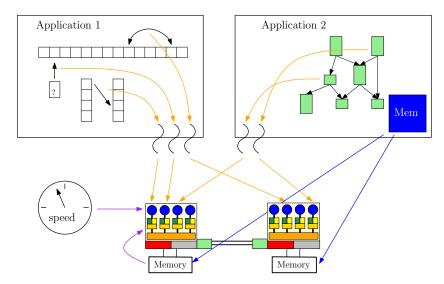

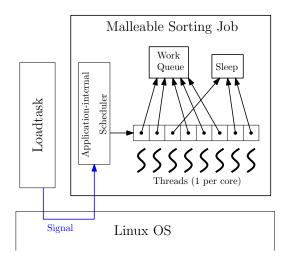

Scheduling in computer science has a lot in common with scheduling in other fields, but there are also some specialties in computer science that are important to find good schedules and scheduling algorithms. First of all scheduling in computer science is usually fully automated. There are typically a lot of decisions to make and many of them have to be fast. For example, if a job runs for an average of 5 milliseconds, then each 5 milliseconds a decision has to be made which job to run next. Hence in computer science schedules are typically computed by scheduling algorithms (and not by humans) and it is often not distinguished between scheduling and scheduling algorithms. Early computers had one sequential core which ran sequential programs, hence the main decision space was which ready program should run next. On parallel machines the decision space grows because now it is not only necessary to decide which job is next but also on which core. Also common resources like common caches and memory connections play an important role now. Parallel programs might add some more constraints or at least things to incorporate into a scheduling approach like which threads of a parallel application should run in parallel or on the same NUMA socket. Large parallel programs also often come with their own application-internal scheduler which can use application-internal knowledge to schedule internal jobs. This leads to the more complicated situation of a scheduling hierarchy with one scheduler on the operating system level responsible for the whole machine and possible application-internal schedulers for each parallel application which have the advantage of a possible better knowledge about their application. Thus changes in hard- and software have major implications on the scheduling in computer science. Also the goal of saving energy during computations becomes more and more important.

The constant changes in hard- and software lead to a constant adaption of schedulers in practice. Scheduling theory instead often focuses on more general models that might not fit all properties of modern computers. The common theoretical base of scheduling in computer science with scheduling in other fields also slows down the adaption of new hard- and software developments in scheduling theory. Also theory often assumes much knowledge about the jobs to schedule. A major example of differences between scheduling theory and computers used in practice are the memory system and caches which have a relevant influence on the performance, but current scheduling theory pays little attention to them. Scheduling in practice often has nearly no knowledge about the jobs because interfaces designed long ago prevent these schedulers from accessing relevant information. Hence these practical schedulers have no need for complex theory because without this knowledge complex scheduling algorithms are hardly useful. Thus there is a widening gap between research in scheduling theory and the scheduling that is used in practice on real computers.

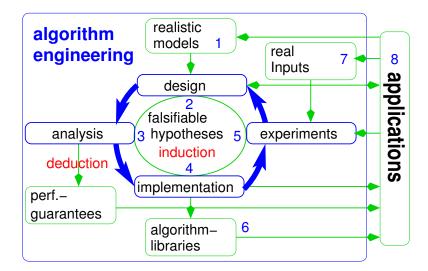

The goal of this work is to research scheduling solutions for future parallel computer systems. Another goal is reducing the gap between scheduling theory and scheduling practice in computer science. We work towards this goal by applying the methods of algorithm engineering on scheduling and by further development of the theory. On the practical side this is done by including ideas from theory and by the proposal of new interfaces which can improve efficiency. On the theory side the focus lies on the development of fast scheduling algorithms with optimal or nearly optimal results. The work also lays more stress on the efficiency gains through scheduling than on scheduling to meet deadlines. Thus it has more a systems efficiency approach than a real-time systems approach. Our published results related to this work are listed in Section 3.4.4.

**Overview of the work** In the rest of this Chapter the formal basis for the decision process of scheduling is specified in Section 1.2. Chapter 2 contains a description of the developments in computer science that are important for scheduling. The main directions of work in theoretical and practical scheduling in computer science are depicted in Chapter 3 which also contains a detailed description of our approach. Our view of the interplay of different schedulers (system-wide, application-internal) is described in Chapter 4. Our work concerning the compu-

tation of schedules (which is usually meant with the term scheduling) is described in Chapter 5. We also look into scheduling solutions for the memory hierarchy (see Chapter 6) and energy-efficiency (see Chapter 7). This work is concluded by a summary and an outlook in Chapter 8.

## 1.2 Formal Descriptions and Complexity

This section is devoted to the formal basis of scheduling. As already noted the four main properties of a scheduling problem are the decision space, the constraints, the goal and the information. For a general scheduling problem consisting of a set of jobs  $\mathscr{J}$  and a set of workers/machines  $\mathscr{M}$  we will now define these four properties:

**Decision Space** The decision space is everything that can and must be decided by the scheduler. The fixed decisions form the schedule.

- Which workers work on which jobs at which time intervals.

- What are the execution parameters for the workers and the jobs (if the problem contains such additional parameters).

- How are the additional resources distributed among the jobs (if the problem contains such resources).

If all decisions are fixed for all jobs, the schedule is complete as there are no further decisions to make. The decisions within the decision space can often be described by decision variables.

**Properties and Constraints** The properties contain the relevant information about the jobs and the workers. Not all possible combinations of decisions from the decision space lead to feasible schedules. The constraints restrict the possible combinations of decisions. The constraints also contain all other restrictions for the problem.

- The availability of the workers, possibly time dependent.

- Which workers can work on which jobs and how fast is the progress for these combinations.

- How do the additional parameters from the decision space influence progress or resource consumption.

- The circumstances under which a job becomes ready to be worked on (release time, dependencies).

- Deadlines and restrictions on additional resources.

20

It is difficult to distinguish between properties and constraints. A deadline of a job might be more a constraint than a property, but the amount of work of the job which has to be completed before the deadline is a job property but clearly restricts the possible decisions in the schedule.

**Goal/Objective** For some scheduling problems it is sufficient to find a schedule that fulfills all constraints, but more often the problem is to find a schedule that additionally optimizes a goal. In the classical scheduling theory the goal is usually a non-decreasing function of the finishing times of all jobs of the problem (for example the finishing time of the latest job  $C_{max}$  or the sum of finishing times of all jobs  $\sum_j \omega_j C_j$ ). Baker and Trietsch [9, page 13] call an objective function  $Z = f(C_1, \ldots, C_n)$  of the finishing times "regular performance measure" if Z' > Z implies that  $C_j' > C_j$  for at least one job j. Additionally/alternatively the objective function can include parts dependent on the amount of the used resources (for example used energy).

**Information** The information is the knowledge the scheduler has about the properties and constraints of the problem while making a decision. If parts of the relevant information of the scheduling problem become known to the scheduler only during the runtime of the schedule, scheduling becomes an online problem. There are two reasons for missing information: the information is generated during the scheduled process or the information is not accessible by the scheduler. Information that is not accessible by the scheduler at all is usually not part of the scheduling model.

Of course these four properties always heavily depend on the used model. The modelling of parallel computers is described in Section 2.6.2.

For the rest of the Section we look into the details of the 3-field problem classification which is widely used in scheduling theory. Finally we introduce the theory of NP-completeness and some complexity theory in order to have a basis to decide how difficult it is for certain scheduling problems to find a good schedule.

#### 1.2.1 3-Field Problem Classification

As there is such a big number of different scheduling problems there is a need to describe them in a fast and standardized way. Graham et al. [55] introduced the 3-field problem classification  $\alpha|\beta|\gamma$  to cope with this problem. The classification always describes the things which characterize the problem class. Individual problems in that class contain additional input.

The first field specifies the machine (or the workers), the second field describes the jobs and the third field the goal (or optimality criteria). To get an idea how this works we give some important descriptors for each field and some problem examples afterwards.

**Machine Field**  $\alpha$   $\alpha=1$  stands for a sequential machine,  $\alpha=P$  for a parallel machine with identical workers and  $\alpha=Pm$  means that the number of available parallel workers is fixed to m (otherwise the number of workers is part of the input). Other possible machine types are  $\alpha=Q$  which means uniform workers which only differ in their general speed independent of the job.  $\alpha=R$  means unrelated workers such that the speed of each worker might be dependent on the job. The necessary speeds for R and Q are part of the input. Hence the machine field specifies the machine properties of the scheduling problem but also a part of the decision space (number of possible workers for each job).

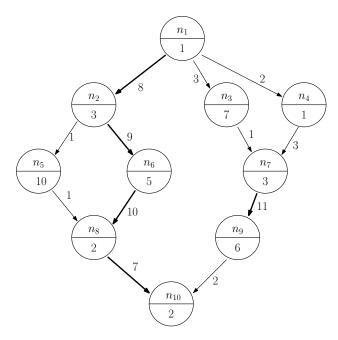

Job Field  $\beta$  If  $\beta$  contains pmtn, the jobs can be stopped and the rest of the job can be completed later (preemption), otherwise all started jobs must run without interruption.  $prec \in \beta$  denotes the existence of precedence relations between the jobs, these relations form a DAG with the jobs as nodes where a directed edge from a to b means that a has to be completed before b can start.  $d_i \in \beta$  means that the jobs have individual deadlines,  $r_i \in \beta$  analogously means that the jobs have individual release times. If prec,  $d_i$  or  $r_i$  are not present in  $\beta$ , this means respectively that there are no precedence relations, deadlines or all jobs are available from the start. In the opposite case when prec,  $r_i$  or  $d_i$  are given, concrete precedence relations, release times and deadlines for each job are part of the input. Another important part of  $\beta$  is  $p_i$  where  $p_i = 1$  means that all jobs have the same running time and  $\bar{p} \leq p_i \leq \hat{p}$  means that all running times lie in a specified interval.

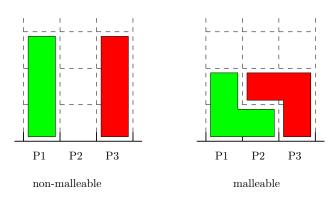

Although the 3-field notation was only intended for sequential jobs in the beginning, it was later expanded for parallel jobs (the notations for parallel jobs are taken from the "Handbook of Scheduling" [93, page 25-5]). If no indication of job parallelism is given in the  $\beta$  field, all jobs are sequential.  $size_i \in \beta$  means that there are parallel jobs with a fixed degree of parallelism which means that there is a fixed number of workers for each job which must work in parallel on this job. any is similar to size but the scheduler can decide the degree of parallelism for each job when the job starts, these jobs are called moldable. var gives the scheduler even more freedom as the degree of parallelism can be changed anytime during the execution of a job, this includes using 0 workers and thus preemption, these jobs are called malleable. For some problems a maximal degree of parallelism for each job is given through  $\delta_i \in \beta$ . When the scheduler can decide the degree

of parallelism of a job, it is of course important how the parallelism affects the job's behavior, especially the running time. If nothing is given in the  $\beta$  field about the working speed of a job with different numbers of workers, the speeds can be defined completely arbitrary in the input, for example running with 4 workers can even be slower than running with 3. If the speedup is a simple function of the number of workers, it is often given in the form  $p_i(q) = \frac{p_i}{q}$  (for a linear speedup, q is the number of workers for the job) within  $\beta$ . More complex speedup functions or function classes are usually given through an additional text outside the 3-field classification.

There are several different notations for additional resource needs depending on the nature of resources and other special conditions. A notation for discrete resources is given by Błażewicz et al. [25].

The job field can also contain some description about the information the scheduler has about the jobs. For example the Handbook of Scheduling [93, page 15-2] defines online-time and online-time-nclv. In online-time the scheduler learns about the existence of a job when it becomes ready but also gets the knowledge about the running time of the job immediately. online-time-nclv gives less information as the scheduler does not know the running time of a job until the job is finished.

Altogether the job field specifies the properties of the jobs, the constraints of the problem, the available information and parts of the decision space (degree of parallelism). In some cases the job properties are too complex to be specified in such a formal way.

Goal Field  $\gamma$  This field contains the definition of the goal of the scheduling process. It is the measurement which makes one schedule better than another. The goal of a scheduler is to minimize the function given in  $\gamma$ . The most common component of such functions are the completion times of jobs, usually denoted as  $C_i$  where i denotes the respective job. Typical goals are to minimize  $\gamma = C_{max}$ , which means the completion time of the last job, or  $\gamma = \sum \omega_i C_i$  which means the weighted sum of completion times with an individual weight for each job. Resource usage dependent goals (energy minimization) do not have a widely used standard in the 3-field notation yet.

#### **Examples**

•  $1||C_{max}|$  describes problems on a sequential machine with unrelated sequential jobs which are all available from the beginning and have no deadlines. The running times of the jobs are part of the input. The goal is to minimize the finishing time of the last job. This is one of the simplest problem classes.

- $P|pmtn|C_{max}$  describes problems on a parallel machine with unrelated sequential jobs which are all available from the beginning and have no deadlines. The jobs can be preempted. The running times of the jobs are part of the input. The goal is to minimize the finishing time of the last job.

- $P|pmtn, size_i|C_{max}$  is the same class as above but with parallel jobs instead of sequential ones. The number of workers each job needs is part of the input.

The 3-field notation is a compact and useful way to define classes of scheduling problems. Unfortunately for some problems there is no 3-field notation yet, for example for scheduling problems from the field of dynamic voltage and frequency scaling (DVFS). As the 3-field notation is the typical language of scheduling theory, it will be used as often as possible in this work.

#### 1.2.2 Computational Complexity

In order to find a solution for a scheduling problem, it is not only important to find a good schedule, it is also important that finding a good schedule is not too expensive and does not take too long. Hence we will give some basics from the big  $\mathcal{O}$  notation, NP-completeness and related subjects here in order to have the tools to describe the computational complexity of scheduling algorithms.

**Big**  $\mathcal{O}$  **Notation** A typical way to describe the computational effort of an algorithm is the big  $\mathcal{O}$  notation, which is a basic tool in many parts of computer science. As this notation is used frequently throughout this work we will recapitulate its basics here:

A function  $f : \mathbb{N} \to \mathbb{N}$  is in  $\mathcal{O}(g(n))$  if and only if there exist  $c \in \mathbb{N}$  and  $n_0 \in \mathbb{N}$  such that  $f(n) \le c \cdot g(n)$  for all  $n \ge n_0$ .

A function  $f : \mathbb{N} \to \mathbb{N}$  is in  $\Omega(g(n))$  if and only if there exist  $c \in \mathbb{N}$  and  $n_0 \in \mathbb{N}$  such that  $c \cdot f(n) \ge g(n)$  for all  $n \ge n_0$ .

A function  $f: \mathbb{N} \to \mathbb{N}$  is in  $\Theta(g(n))$  if and only if  $f(n) \in \mathcal{O}(g(n)) \cap \Omega(g(n))$ .

These notations are commonly used to give a clue about running times of an algorithm, where n denotes the size of the input in a useful way. The following definition specifies the typical way of coarsely classifying algorithms in algorithm theory.

**Definition 1.2.1.** An algorithm with running time f(n) for the worst input of size n and  $f(n) \in \mathcal{O}(g(n))$  is called

• polylogarithmic time algorithm if and only if there exists a fixed  $k \in \mathbb{N}$  such that  $g(n) = \log(n)^k$  for all n.

ullet polynomial time algorithm if and only if there exists a fixed  $k\in\mathbb{N}$  such that

$g(n) = n^k$  for all n, and it is no polylogarithmic time algorithm.

• exponential time algorithm if and only if there exists a fixed  $r \in \mathbb{R}$  with r > 1 such that  $g(n) = r^n$  for all n, and it is no polylogarithmic or polynomial time algorithm.

**NP-Completeness** A very important question for a scheduling problem is whether or not an optimal solution is computable within a reasonable amount of time. In complexity theory the common rough rule of thumb is that a polynomial time algorithm can be computed within reasonable time limits, but an exponential time algorithm can usually not be computed within a reasonable time.

There is an important class of problems called NP-complete problems which allow a solution with a polynomial time algorithm on a nondeterministic Turing machine, but it is still unknown if these problems can be solved with a polynomial time algorithm on a deterministic Turing machine (or an ordinary computer). The best-known problem in this class is called the 3-SAT problem, which is the question "Given a Boolean logic formula in conjunctive normal form with at most 3 variables per clause is it possible to find a value in {true, false} for each variable such that the outcome of the whole formula is true?". A problem in the class of NP-complete problems is called NP-complete. Traditionally the theory of NP-completeness considers only problems where for each instance the solution is just yes or no. Here we consider problems where a useful solution is computed by the algorithms.

Between all NP-complete problems there exist polynomial time algorithms (on deterministic Turing machines) such that an algorithm A that solves one NP-complete problem can solve all other NP-complete problems by adding such polynomial time algorithms before and after A. Hence a polynomial time algorithm on a deterministic Turing machine that could solve one NP-complete problem would lead to polynomial time algorithms on deterministic Turing machines for all NP-complete problems. As many important problems are in the class of NP-complete problems and no algorithm was found yet to solve any of these problems with a polynomial time algorithm on a deterministic machine, the conjecture is that it is not possible to solve NP-complete problems with polynomial time algorithms on deterministic machines.

A good introduction and reference for the theory of NP-complete problems is given by Garey and Johnson [51]. For the reason of self-containedness we also give a definition of NP-hardness and NP-completeness.

**Definition 1.2.2.** Let  $A_{SAT}$  be an algorithm to solve the 3-SAT problem. Then a problem P is called NP-hard if and only if for all algorithms  $A_P$  solving P there exist polynomial time algorithms  $A_{SP}$  and  $A_{PS}$  on deterministic machines such

that  $A_{PS}(A_P(A_{SP}(I)))$  is a solution for each 3-SAT input I. If additionally there are polynomial time algorithms  $\bar{A}_{SP}$  and  $\bar{A}_{PS}$  on deterministic machines such that  $\bar{A}_{SP}(A_{SAT}(\bar{A}_{PS}(I)))$  is a solution for each P input I, then the problem is called NP-complete.

In practice it is usually only important that a problem is NP-hard as this already yields that finding a polynomial time algorithm on a deterministic machine is highly unlikely as no NP-hard problem could be solved with a polynomial time algorithm yet.

When finding the size n of an input I of a problem P, it is usually assumed that more than one symbol is used to encode I especially the numbers in I. Hence the value of the largest number contained in I does not have to be bounded by a polynomial function of n. Let m be the maximum of n and the largest number encoded in I. Then some NP-hard problems can be solved by polynomial time algorithms with respect to m instead of n, for example PARTITION (see Garey and Johnson [51, page 90] and [51, page 60] for the NP-Completeness of this problem). If the problem restricted to the case that all numbers contained in I are bounded by a polynomial function of n is still NP-hard, then the problem is called NP-hard in the strong sense [51, page 95] or short **sNP-hard** or **sNPh** (a notation frequently used in the Handbook of Scheduling [93]).

Example:  $P2||C_{max}$  is NP-hard but not sNP-hard as it is equivalent to the PARTITION problem (as pointed out by Lenstra et al. [92]). The more general (the number of workers is part of the input)  $P|pmtn|C_{max}$  with preemption is not NP-hard as there exists a simple polynomial time algorithm called McNaughton's wrap-around rule [104] which finds the optimal solution.  $P||C_{max}$  on the other hand is sNP-hard as pointed out by Garey and Johnson [50] (reduction from 3-PARTITION).

**P-Completeness** Given big parallel machines, it is often interesting whether an input can be computed on a large machine in polylogarithmic time regarding the size of the input (and thus make the running time less size-dependent). The book by Greenlaw, Hoover and Ruzzo [57] introduces into the theory of the limits of parallel computation. For a class of problems called Nick's Class there exist algorithms which can compute solutions in polylogarithmic time with a number of processors polynomial in *n*. For some other problems such algorithms seem impossible (similar to the NP-completeness there is no real proof other than many have tried and all failed). These problems are called P-complete. Especially for scheduling of big machines it is interesting to use all processors to compute the schedule in order to complete the scheduling in polylogarithmic time. Hence it is important to investigate if a scheduling problem is P-complete. Some special scheduling problems have already been proven to be P-complete.

#### 1.2.3 Approximations and Heuristics

Algorithms which solve NP-hard problems optimally usually have an infeasible running time (exponential time). Hence one often has to use algorithms that may compute suboptimal solutions in order to get feasible (polynomial) running times. There are two different ways to get a faster algorithm: approximation and heuristic. Both ways are well-known in computer science but often differently defined. Hence we give our own definition for the reason of self-containedness.

Let I be an instance of a problem class P and  $A_{opt}$  an algorithm (not necessarily with feasible running time) which computes an optimal solution. For any algorithm A let further  $\gamma(A(I))$  be the resulting value of the objective function after A has been used on instance I. An approximation algorithm  $A_{app}$  for a problem P is an algorithm such that there exists a (useful) function f with  $\gamma(A_{app}(I)) \leq f(\gamma(A_{opt}(I)))$  for all  $I \in P$  (assuming the goal is minimization). Common functions are  $f: x \mapsto (1+\eta) \cdot x$  for an algorithm-specific  $\eta > 0$ , the respective approximation algorithms are usually called  $(1+\eta)$ -approximation and  $(1+\eta)$  is called the approximation ratio. If  $\eta$  is not too big, such an approximation might be very helpful in practice. Depending on the problem approximation algorithms can be much faster than algorithms which compute an optimal solution even for small  $\eta$ .

If it is not possible (for example because the algorithm development would be too costly) to find a reasonably fast exact or approximation algorithm, one often uses a heuristic algorithm. Heuristic algorithms are often based on general optimization ideas. There are no guarantees for the solution quality compared to an optimal solution, but there are good heuristic algorithms in practice which are fast and yield quite good results for many of the relevant instances. Hromkovič [67, chapter 6] gives a good introduction into heuristics and also reviews different possibilities to define a heuristic.

# 2

# **Scheduling Fundamentals**

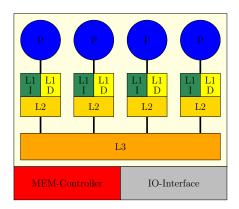

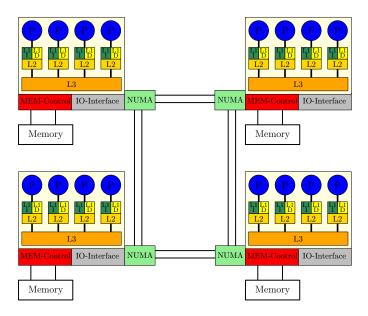

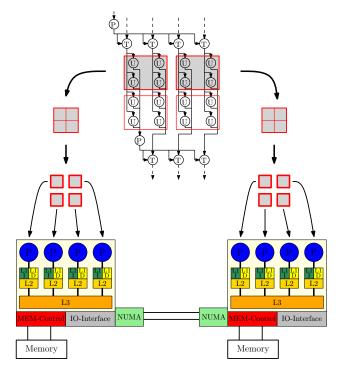

The goal of this chapter is to introduce the environment of scheduling within computer science. Section 2.1 gives some examples of areas with high computational demand today and in the future and takes a look at the cost of these computations and how scheduling might help to further reduce these costs. In order to make decisions about the use of computer systems, it is of course important to know something about their build and structure. This topic is handled in Section 2.2 in which we first go into detail why we need parallel computers in order to fulfill high resource demands (Section 2.2.1). Then the parts of modern computer systems that are relevant for scheduling are described (Section 2.2.2) and their probable future development is depicted (Section 2.2.3). An idea from economics why such development processes might lead to suboptimal results is presented in Section 2.3. Some basics about the usage of parallel computer systems are presented in Section 2.4. It is also important in which software hierarchy level (library, application, operating system, etc.) the scheduling takes place and which information is available on this level. The hierarchy and the information flow through interfaces are depicted in Section 2.5. To develop a scheduling algorithm one needs to abstract from many details of the machine and the programs, hence one needs to use a model. The modelling of parallel computers and their applications is described in Section 2.6.2. The general algorithm engineering process is introduced in Section 2.6.1, we use this methodology on scheduling (more details in Section 3.4). We also introduce the DFG-project Invasive Computing, which was the main work area of the author of this work, in Section 2.7. Our findings during Invasive Computing are described in a later Section 4.4.

# 2.1 Importance and Cost of Large Computations

To get an impression of the order of magnitude of expenses for today's computing we can just take a look at Intel's annual report [70] which reports revenues of 14 billion dollars in 2014 for the Data Center Group alone (56 billions for Intel altogether) which is only a part of the sum spent on data center hardware (computers) in 2014. Following a report of van Heddeghem et al. [138] data centers worldwide used 268 TWh of electric energy in 2012 which is nearly one half of the annual consumption of electrical energy in Germany. This spending shows the huge importance of computations in today's world.

So why do people spend that much on computation, what are the typical applications? From the early days of computation when Konrad Zuse invented the computer, computers were used for numerical calculations in engineering. As computers became more widespread, the users generated a lot more different applications of computing. Today computing intensive applications are not only used in data centers but also on PCs and even smartphones. PCs and even smartphones today are parallel computers as they normally have more than one computing core.

Hence we have a lot of different application types which require a lot of computation effort. We list some of them:

- Numerical applications are still a big consumer of computing power especially in data centers of engineering companies or research laboratories. An important property of linear algebra algorithms is whether they are for dense linear algebra or sparse linear algebra, because the former is especially dependent on the performance of the functional units of the computer system whereas the latter is more dependent on the used data structures and the memory system. In both cases the floating point units and their memory connection play an important role. These applications play an important role in the design of cars, planes and a lot of other things needed in everyday life to improve their efficiency, safety and to reduce production costs. Research in many areas like material sciences or fluid dynamics is heavily dependent on these applications.

- Optimization applications play a role across all levels of computer systems, from route and tour planning algorithms on smartphones to business optimizations on servers. The resource demand of these applications can be different as a lot of different algorithms are used. Optimization (like scheduling itself) is an important tool throughout the economy and thus an important application of computers.

- Computer knowledge generation is the kind of application where the com-

puter is used to gain knowledge out of unprepared, unstructured and somehow natural data. This ranges from speech recognition in smartphones and PCs to search engines and artificial intelligence.

Special applications like in-memory databases or applications from the computational biology also require high computational effort but are also an important service for their users.

Although there is no common special resource (floating point units, integer/logic units, cache, memory bandwidth, or others), all of these applications have in common that they have significant computation costs but also provide a high value for their users.

How can scheduling help to improve the efficiency of these applications and thus reduce costs? Let us first take a look at the three main cost factors of computation besides administration:

- 1. Hardware. The purchase cost of the hardware or the depreciation during the running time of the application.

- 2. Energy. The energy usage of the hardware due to the execution of the application. Also cooling effort, which is an often underestimated part of the energy usage.

- 3. Programming or software licences.

If programs run faster or more efficiently the applications use the hardware for a shorter time or more applications can be run on the same hardware in the same time. Scheduling can improve running time and efficiency for example through useful resource distribution (allocate resources to the program which uses them in the most efficient manner), better ordering of small tasks within programs to reduce waiting times and through balancing temporarily changing resource demands between different applications. Hence scheduling can reduce hardware cost. Scheduling can also reduce the number of cache misses, memory swaps to hard disk and the needed average core frequency. Thus scheduling can also improve the energy consumption of a computing application. The cost for software licences can be reduced in the case where licences are needed during the time a special library runs or if the licence cost is proportional to the number of computers. In these cases the software cost has the same behavior like the hardware cost (software licences are then like an additional piece of hardware). The programming effort can not be reduced directly by scheduling, but maybe in an indirect way. For applications with a high performance demand programmers often avoid the use of libraries (for example parallelization libraries) to get the most out of the machine through optimized code. If these libraries would include an efficient scheduling such that their performance comes closer to the specialized code for the situation then the programming effort for these applications could be reduced.

So scheduling can be used to improve efficiency and reduce cost. In order to reach that goal, the designer of scheduling algorithms has to know the performance relevant parts of modern parallel computers which are introduced in Section 2.2.

## 2.2 Parallel Computing Systems

#### 2.2.1 Reasons for Parallelization

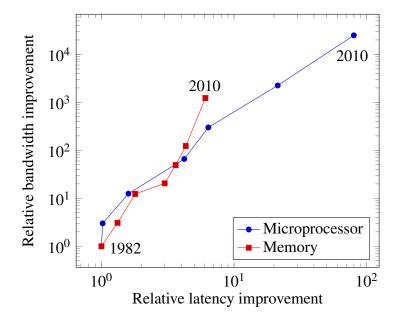

The applications described in the last Section have a high demand of computational power. The demand usually increases with the affordability of computing power. In the beginning even supercomputers were sequential computing machines. Between 2005 and 2010 personal computers became parallel devices and today even handheld devices have more than one computing core and thus are parallel computers. But what are the main reasons to move from sequential computers to the more complex parallel computers? The main reason is that the performance improvement of sequential computers was slowed by three performance walls: The Power-Wall, the ILP-Wall and the Memory-Wall (Asanovic et al. [8]).

**Power-Wall** Following the work of Borkar and Chien [15] in the 20 years before 2011 we had a typical scaling factor s = 1.4 for every technology generation. This means that for each generation the transistor dimensions are scaled by 1/s (also the capacitance), hence the area of the same logic is scaled by  $1/s^2$ . Due to the scaling the frequency could be scaled by s and the supply voltage by 1/s. Using a formula from Kogge et al. [86] we get for the power density  $P_{dens}$ , the transistor capacitance S, the transistor density S (transistors per S), the operating frequency S and the supply voltage S0.

$$P_{dens} = C \cdot d \cdot f \cdot V_{dd}^2$$

Thus the power density stayed the same when scaling by *s* without regarding the leakage power. As observed by Kogge et al. [86] in the last years the scaling of the supply voltage slowed down, this is partly due to efforts to reduce the leakage power [15]. Hence the power density is increasing if we continue scaling in the same manner. Thus the gains in operating frequency will slow down or stop totally when we have an upper limit for power density, which is indeed the case in order to have an efficient affordable cooling. This reduces further gains in sequential computing due to increased operating frequency substantially.

**ILP-Wall** More and more transistors per core were available over the last 20 years. Before the rise of parallel processors the designers used these transis-

tors to build more complex cores in order to dynamically execute instructions from a sequential program in parallel. This is called **i**nstruction **l**evel **p**arallelism (ILP), which includes techniques like pipelining, branch prediction, register renaming, alias analysis and multiple parallel functional units. According to Borkar et al. [15] there was a 1000-fold microprocessor performance increase in the two decades before 2011 of which at least one order of magnitude is due to microarchitecture improvements. The other nearly two orders of magnitude are due to operating-frequency increases. In 1991 Wall [139] studied the limits of instruction level parallelism for real programs. Even though he assumed extreme capabilities for the processors, he found the average parallelism is around 7 and the median around 5. Hence the reachable degree of instruction level parallelism is bounded. Following Hennessy and Patterson [64, page 213] the returns of even more complex architectures for increased instruction level parallelism diminished around 2005. So the industry will no longer deliver gains in instruction level parallelism because it would be too costly and inefficient.

With 10.6 billion dollars Intel had the third largest research and development spending of all companies in the world in 2013, according to Fortune [28], thus one should not expect dramatically bigger spending for processor development in the future. Hence further large gains by dramatically improved processor designs are also unlikely from this perspective.