## **UC Berkeley**

### **UC Berkeley Previously Published Works**

#### **Title**

Thermal annealing in hydrogen for 3-D profile transformation on silicon-on-insulator and sidewall roughness reduction

#### **Permalink**

https://escholarship.org/uc/item/6c41s9f0

#### **Journal**

Journal of Microelectromechanical Systems, 15(2)

#### **ISSN**

1057-7157

#### **Authors**

Lee, MCM Wu, Ming C

#### **Publication Date**

2006-04-01

Peer reviewed

# Thermal Annealing in Hydrogen for 3-D Profile Transformation on Silicon-on-Insulator and Sidewall Roughness Reduction

Ming-Chang M. Lee, Member, IEEE, and Ming C. Wu, Fellow, IEEE

Abstract—A fast, effective process using hydrogen annealing is introduced to perform profile transformation on silicon-oninsulator (SOI) and to reduce sidewall roughness on silicon surfaces. By controlling the dimensions of as-etched structures, microspheres with 1  $\mu$ m radii, submicron wires with 0.5  $\mu$ m radii, and a microdisk toroid with 0.2  $\mu$ m toroidal radius have been successfully demonstrated on SOI substrates. Utilizing this technique, we also observe the root-mean-square (rms) sidewall roughness dramatically reduced from 20 to 0.26 nm. A theoretical model is presented to analyze the profile transformation, and experimental results show this process can be engineered by several parameters including temperature, pressure, and time. [1580]

Index Terms—Annealing, surface diffusion, surface roughness.

#### I. INTRODUCTION

C IDEWALL roughness is an issue for many applications, for example, scattering loss in optical waveguides [1]–[3] and micromirrors [4]. For dry etch processes, roughness depends on the quality of photomasks, photolithography, and etching conditions. Though state-of-the-art complementary metal-oxide-semiconductor (CMOS) technologies can achieve sidewall roughness less than 5 nm [5], in many research labs, sidewall roughness is about 10-20 nm. Anisotropic wet etching such as potassium hydroxide (KOH) and tetramethylammonium hydroxide (TMAH) can form smooth sidewalls, but the geometry is limited by crystal planes. Another solution is to develop post-dry etching processes to reduce roughness. Thermal oxidation was reported to smooth the sidewall for a silicon wire fabricated on SOI [6], [7]. However, the process consumes silicon, more than ten times the surface roughness, and it induces residual stress in silicon. Therefore, it is not suitable for rough surfaces such as the sidewall scalloping resulted from the Bosh process [8]. In contrast, hydrogen annealing was reported to remove surface roughness effectively [9]-[12]. The surface mobility of silicon atoms is enhanced by heated hydrogen [13], [14] at temperatures

Manuscript received April 20, 2005; revised July 1, 2005. This work was supported in part by DARPA/CS-WDM programs (#MDA972-02-1-0019) and by the University Photonics Research Program (HR0011-04-1-0040). Subject Editor H. Zappe.

M.-C. M. Lee was with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720 USA. He is now with the Institute of Photonics Technologies and the Department of Electrical Engineering, National Tsing Hua University, Taiwan, R.O.C. (e-mail: mclee@ee.nthu.edu.tw).

M. C. Wu is with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720 USA (e-mail: wu@eecs.berkeley.edu).

Digital Object Identifier 10.1109/JMEMS.2005.859092

much lower than the melting point (1414 °C). Based on this phenomenon, migrating atoms smooth out the surface roughness to minimize the total surface energy without losing volume.

Hydrogen-induced surface migration not only changes the surface morphology but also affects the global profile if the surface migration length is comparable to or larger than structural dimensions. This effect is similar to the reflow process in glasses [15] or polymers [16], but unlike the reflow process, this mechanism only depends on surface-atom movement and the crystalline structure is preserved. Thermal annealing in hydrogen ambient has been reported to produce round corners [17] and various voids [18], [19] in bulk silicon. However, previous experiments were mostly performed on bulk Si. Microstructures on silicon-on-insulator (SOI) behave differently in hydrogen annealing because of the different boundary conditions. The bottom oxide becomes a barrier for the mass transport. In our studies, we have shown that it is possible to produce rounded three-dimensional (3-D) microstructures such as microspheres, submicron wires, and microtoroids on SOI [20], [21].

In this paper, we present a comprehensive study of the hydrogen annealing process for SOI microstructures. Detailed process characterization and modeling are described. In addition to producing various rounded 3-D structures, we will also demonstrate reduction of sidewall scalloping created after deepreactive-ion-etch (DRIE). In Section II, we examine the process parameters of hydrogen annealing and introduce a theoretical model to predict the profile transformation. Several types of profile transformation and their mechanisms are described in Section III. In Section IV, we show the ability of sidewall roughness reduction by hydrogen annealing.

#### II. PROCESS CHARACTERISTICS

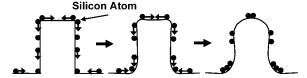

As silicon is annealed in hydrogen ambient, the surface will be terminated with hydrogen atoms [22]. Although the mass transport of silicon atoms actually depends on the atomistic nature of crystals [23] and is affected by the surface crystalline structure [24], the global profile transformation can be approximately modeled as atom motion on an isotropic continuum surface. For isotropic materials, surface diffusion and evaporation-condensation contribute to the fundamental surface mass transport mechanisms [25]. However, for annealing temperatures less than 1100 °C, surface diffusion is dominant in profile transformation [26]. In our applications, the temperature is around 1050 °C, which is compatible with typical microfabrication, and only the surface diffusion mechanism is considered. Fig. 1 shows a schematic of surface diffusion on a silicon profile.

Fig. 1. Schematic illustrating atom migration on a silicon surface during hydrogen annealing.

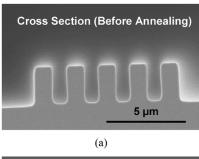

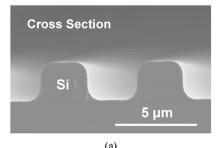

Fig. 2. The cross section of a line-and-space pattern etched on bulk silicon (a) before and (b) after hydrogen annealing ( $1100 \, ^{\circ}$ C and  $10 \, \text{torr}$  for 5 min).

Surface atoms tend to leave from convex corners and accumulate at concave corners. Based on this mechanism, initial sharp corners become rounded. Fig. 2 shows the cross-sectional scanning electron micrographs (SEM) of silicon mesas before and after hydrogen annealing (performed in ASM Episilon II single wafer epitaxial reactor). The structure was initially etched on bulk Si with 1  $\mu$ m width, 1  $\mu$ m spacing, and 2.5  $\mu$ m height. After annealed in pure hydrogen at 10 torr, 1100 °C for 5 min, both the top and bottom corners became rounded.

As shown in Fig. 1, a surface proceeding or receding along the normal direction depends on the surface atoms transferring in the transverse direction. To gain more insight to the process, we used Mullins' model to simulate the 2-D profile evolution due to surface diffusion [25]

$$\nu_n = \gamma \cdot \Omega^2 \cdot n_s \cdot \frac{D_s}{kT} \cdot \frac{\partial^2 K}{\partial s^2} \tag{1}$$

where  $\nu_n$  is the speed of the profile developing along the normal direction,  $\gamma$  is the surface tension of solid substrate,  $\Omega$  is the molecular volume,  $n_{\rm s}$  is the number of atoms per unit area,  $D_{\rm s}$  is the surface diffusion coefficient, T is the temperature, K is the surface curvature, and s is the arc length along the profile. From this equation, profile evolution dynamics are primarily determined by the material properties, the surface diffusion coefficient, and the second-order gradient of curvature. Among these factors, the surface diffusion coefficient ( $D_{\rm s}$ ) can be controlled by temperature and pressure. This process dependency was first explored by Sato  ${\it et~al.}$  on a trench evolution [12]. To gain more quantitative information on this relationship, a parametric study

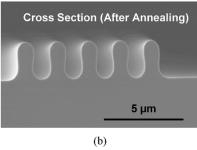

Fig. 3. Experimental surface diffusion coefficient as a function of (a) temperature and (b) pressure.

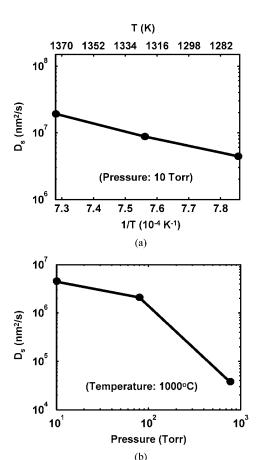

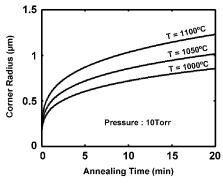

Fig. 4. The evolution of the radius of curvature on a rectangular corner at  $1000~^{\circ}\text{C}$ ,  $1050~^{\circ}\text{C}$ , and  $1100~^{\circ}\text{C}$ .

of the corner evolution was performed experimentally, and  $D_{\rm s}$  was extracted for various temperatures and pressures. As indicated in Fig. 3, the surface diffusion coefficient increases steadily with temperature, and decreases with pressure. The relation between the diffusion coefficient and temperature actually follows the Arrhenius equation. On the other hand, process pressure may affect the activation energy of the diffusion coefficient. The activation energy is estimated to be about 2.26 eV under a hydrogen pressure of 10 torr. As the pressure approaches to atmospheric pressure, the diffusion coefficient decreases more rapidly.

In (1), the profile evolution is also driven by the second-order gradient of curvature. To evaluate this characteristic, we analyzed the corner evolution on a silicon step with a rectangular profile. Fig. 4 shows the radius of curvature of a corner versus

# TABLE I EXAMPLES OF 3-D SILICON PROFILE TRANSFORMATION. THE FIGURES SHOWN IN THIS TABLE REPRESENT THE CROSS-SECTIONAL PROFILES OF SEVERAL STRUCTURES. THE PROCESS PARAMETERS ARE SET TO BE $1100\,^{\circ}$ C, $10\,^{\circ}$ C, $10\,^{\circ}$

| Features               | Before Annealing | After Annealing |

|------------------------|------------------|-----------------|

| Circular<br>Beams      | 1 μm             | 1 μm            |

| Submicron<br>Wires     | 1 µm             | < 1 μm          |

| Toroidal<br>Structures | - < 1 μm         |                 |

annealing time at 1000 °C, 1050 °C, and 1100 °C with the pressure held constant at 10 torr. As shown from these curves, the radius of curvature initially increases very rapidly due to a large gradient of curvature varying at the corner, but after a few minutes, the increase becomes much slower. The result shows the radius of curvature approximately increases with the fourth root of time. In addition, for a high annealing temperature, a large radius is easily achieved due to the large surface diffusion coefficient. This theoretical prediction provides important guidelines to optimize the process for profile engineering.

#### III. 3-D SILICON PROFILE TRANSFORMATION

Micro-structures with round profiles are difficult to be fabricated by conventional processing technologies. Although such structures have been demonstrated by a reflow technique, however, they are limited to noncrystalline materials such as glass [15] or polymers [16]. Exploiting the hydrogen-enhanced surface diffusion, we can make various round structures in monocrystalline silicon by controlling the process parameters. Profile transformation on arbitrary geometries with known parameters can be analyzed by numerical methods [27]. A simple profile evaluation can refer to the corner radius of a right angle under the same annealing process conditions, as shown in Fig. 4. If the dimensions of the structure are smaller than the annealed corner radius (ACR), the global geometry will become circular. Otherwise, only the edges will become rounded. If the devices are fabricated on SOI, the profile transformation can be performed on a released structure by removing the buried oxide. Table I lists the cross sections of different released profiles and shows the profiles are transformed into circular beams, submicron wires, and toroidal structures after hydrogen annealing. In this section, we introduce the fabrication process for each structure and demonstrate the experimental results.

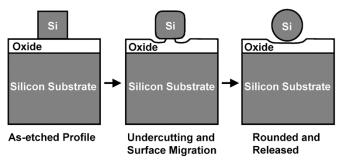

In addition to surface diffusion, hydrogen annealing also induces chemical etching at the interface of silicon and silicon dioxide [28]. Fig. 5 compares the cross sections of the annealed rectangular structures on bulk silicon and SOI. The SOI wafer was initially etched to expose the buried oxide, while the bulk Si wafer was time-etched to the same depth. Then, both wafers were annealed in pure hydrogen at 1100°C, 10 torr for 5 min. In the bulk silicon sample, the annealed profile exhibits convex

Fig. 5. Cross-sectional views of the annealed profiles on (a) bulk Si and (b) SOI ( $1100 \,^{\circ}$ C,  $10 \, \text{torr}$ , 5 min) [21].

(top) and concave (bottom) corners. However, in the SOI wafer, an undercut due to chemical etching is developed between the etched Si and the  $SiO_2$  substrate. It creates a slit at the interface with 0.1  $\mu$ m thickness. This slit exposes the bottom corners to hydrogen and makes the bottom corner convex.

#### A. Circular Cantilever Beams and Microspheres

As shown in Fig. 5, a feature profile with convex, rounded corners can be fabricated on SOI even without the aid of a releasing process. This phenomenon enables us to make circular features if the dimensions of as-etched profiles are equivalent or less than the ACR. Fig. 6 describes the transformation process. First, a structure with a square profile is fabricated on a SOI and the buried oxide is exposed. During hydrogen annealing, the bottom interface is undercut and the four corners turn rounded. If the sample is further annealed for a long time, the profile become circular and the SOI structure could be completely separated from the buried oxide, resulting in a self-released structure.

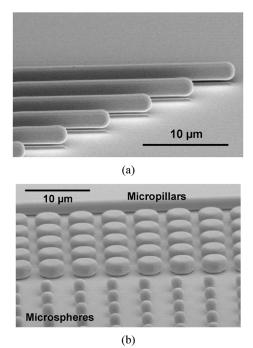

Based on this mechanism, we demonstrate circular cantilever beams and microspheres. An array of microbeams with 1  $\mu$ m

Fig. 6. A schematic process flow for self-released circular cantilever beams.

Fig. 7. SEM images of (a) circular cantilever beams and (b) microshperes. The radius of each microsphere is about 1  $\mu$ m. The radius of each circular micropillar is 2  $\mu$ m [20].

width and 1  $\mu$ m spacing were patterned by lithography. The structures were etched down to the buried oxide with vertical sidewalls on a 1.5- $\mu$ m-thick SOI film. Then, these microbeams were annealed at 1100 °C and 10 torr until they were completely released due to undercutting at the interface. Fig. 7(a) presents the result. The rectangular beams became circular with rounded tips. To avoid the structures falling on the buried oxide, the microbeam array was anchored to a large-area silicon feature, which is still unreleased. Microspheres were created using a similar process. An array of circular cylinders with 1  $\mu$ m radii were patterned by lithography. After dry-etching, the sample was annealed in pure hydrogen at 1100 °C and 10 torr. The annealing time is controlled to prevent complete release of the microspheres. Fig. 7(b) shows the SEM image of the microspheres after hydrogen annealing. The radius of each microsphere approximately equals 1  $\mu$ m. For circular cylinders with radii larger than the ACR, the annealed profiles are similar to micropillars.

#### B. Submicron Wires

For a very thin rectangular silicon structure, the profile varies significantly. Due to a large gradient of curvature changes at the edge, silicon atoms migrate rapidly from the edges to the top and bottom surfaces. This migration makes the lateral dimension

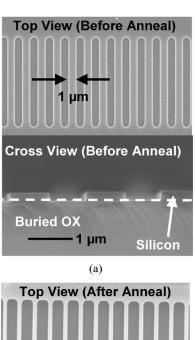

Fig. 8. SEM image of top and cross-sectional views of the microbeam array (a) before and (b) after annealing [20]. The as-etched line array is  $1-\mu m$  wide and  $0.2-\mu m$  thick for each beam. After annealing, each beam turns circular with  $0.25-\mu m$  radii. These circular beams are coated by spin-on-glass (SOG).

shrink and the vertical dimension expand. If both the thickness and width are smaller than the ACR, the initial rectangular profile eventually becomes circular after annealing. Based on this mechanism, a submicron wire can be fabricated. To demonstrate this effect, an array of 1  $\mu$ m wide strips with 1  $\mu$ m spacing was first patterned on SOI substrate with 0.2- $\mu$ m-thick Si film and  $3-\mu$ m-thick buried oxide. The top and cross-sectional views of the strips are shown in Fig. 8(a). To allow a vertical expansion and to avoid the chemical etching at Si/SiO<sub>2</sub> interface during annealing, the buried oxide underneath this array was etched by BOE. Finally, the sample was annealed in hydrogen ambient at 1100 °C, 10 torr, for 5 min. As shown in Fig. 8(b), the cross section of the Si beams was transformed from  $0.2 \times 1 \mu m^2$ rectangles to 0.25- $\mu$ m-radius circles. Note that the areas of the cross sections are conserved during the annealing process. This technique can be employed to design and fabricate submicron features without advanced lithography.

#### C. Toroidal Structures

A similar migration mechanism can be applied on a thin SOI structures with large area (lateral dimension  $\gg 1~\mu m$ ). How-

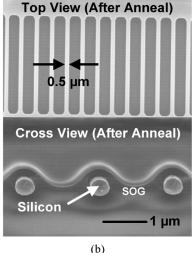

Fig. 9. The SEM image of a toroidal structure after hydrogen annealing. The inset is a close-up view of the toroidal edge. Thickness around the edge is expanded.

ever, the resultant profile transformation primarily happens at the edges. Due to the vertical expansion, a thick rim is formed on the edges of the structure. We can exploit this property to make Si microtoroids. Fig. 9 shows the SEM image of a toroidal microdisk. A circular pattern with 10  $\mu$ m radius was first created on a 0.2- $\mu$ m-thick SOI wafer. The disk was partially released in HF to form overhangs at the edges. During annealing in hydrogen, the edges of the disk were not only rounded but also expanded in the vertical direction. As a result, the microdisk was transformed into a toroidal structure with a smooth surface. The thickness varies from the edge to the center with a smooth transition. As shown in Fig. 9, the toroidal radius is estimated to be 200 nm. The microtoroid disk is attractive as an optical microresonator [29].

#### IV. SIDEWALL ROUGHNESS REDUCTION

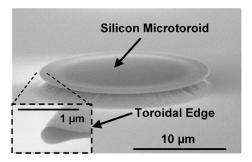

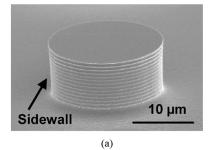

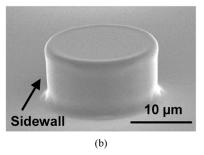

Hydrogen-enhanced surface diffusion can effectively reduce the surface roughness. If the dimensions of a structure are much greater than the ACR, the global shape remains largely unchanged while the local roughness can be smoothed out. In bulk micromachining, DRIE has been extensively used to produce high-aspect-ratio structures. However, the cyclic etching and deposition steps (Bosch Process) usually create sidewall scalloping [8]. In addition, the substrate also becomes rough after this process. Sacrificial thermal oxidation has been utilized to improve sidewall quality [30], [31]; however, the process consumes too much silicon and builds up residual stress. By employing hydrogen annealing, we demonstrate that sidewall scalloping can be dramatically reduced. Fig. 10(a) shows the SEM image of an as-etched circular mesa with a 15-µm height and a rough sidewall scalloping after DRIE process. The root-mean-square (rms) surface roughness is estimated to be 100 nm at the sidewall. The wafer was then annealed in pure hydrogen at 1100 °C, 10 torr for 10 min. As shown in Fig. 10(b), the surface roughness on both the sidewall and the substrate was dramatically reduced.

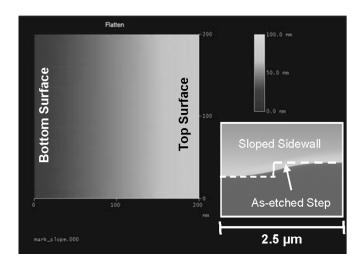

A quantitative analysis on the sidewall roughness reduction was measured by an atomic force microscope (AFM). A shallow step with 0.5- $\mu$ m depth was first etched by a conventional dry etch technique without optimization. The as-etched sidewall roughness is about 20 nm. After the sample was annealed at  $1100^{\circ}$ C, 10 torr for 10 min, the vertical sidewall became sloped. It facilitates the AFM tip to scan across the sidewall surface. Fig. 11 displays the image of a 200 nm  $\times$  200 nm scanning area on the center of the sloped sidewall. The data shows that the rms roughness of the annealed surface is only 0.26 nm.

Fig. 10. The sidewall roughness on a 15-  $\mu$ m high, 2.5-  $\mu$ m wide cylinder (a) before and (b) after annealing. The etch is done by DRIE.

Fig. 11. Atomic force microscope image of the silicon sidewall surface after hydrogen annealing. The inset is the step profile after hydrogen annealing. The scan area is 200 nm by 200 nm on the sloped sidewall. The measured data show the rms roughness is 0.26 nm.

#### V. CONCLUSION

In summary, we have reported a process using hydrogen annealing for silicon profile transformation and sidewall roughness reduction. Experimental analysis shows this process can be controlled by temperature, pressure, and time. Additionally, the transformed profile also depends on the dimensions of the structure. We have demonstrated circular cantilever beams, microspheres, submicron wires, and microtoroid structures fabricated on SOI. We also show this process can significantly reduce the sidewall scallop created by DRIE. Also, an rms sidewall roughness of 0.26 nm, which approximates the lattice constant of silicon, was achieved. This process can potentially improve the performance of several devices, including low-loss optical waveguides, vertical micromirrors and smooth microfluidic channels.

#### ACKNOWLEDGMENT

The authors thank W. Srituravanich and Professor X. Zhang for help with the AFM, and Dr. S. Mathai for helpful discussions.

#### REFERENCES

- J. P. R. Lacey and F. P. Payne, "Radiation loss from planar waveguides with random wall imperfections," *Inst. Elect. Eng. Proc.-J. Optoelec*tron., vol. 137, pp. 282–288, 1990.

- [2] F. Grillot, L. Vivien, S. Laval, D. Pascal, and E. Cassan, "Size influence on the propagation loss induced by sidewall roughness in ultrasmall SOI waveguides," *IEEE Photon. Technol. Lett.*, vol. 16, pp. 1661–1663, 2004.

- [3] W. Bogaerts, P. Bienstman, and R. Baets, "Scattering at sidewall roughness in photonic crystal slabs," Opt. Lett., vol. 28, pp. 689–691, 2003.

- [4] Y. J. Wang, X. L. Cheng, Z. L. Lin, F. Gao, and F. Zhang, "Monolithic beam splitter in silicon-on-insulator," *Opt. Express*, vol. 12, pp. 5154–5159, 2004.

- [5] S. J. McNab, N. Moll, and Y. A. Vlasov, "Ultra-low loss photonic integrated circuit with membrane-type photonic crystal waveguides," *Opt. Express*, vol. 11, no. 22, Nov. 3, 2003.

- [6] K. K. Lee, D. R. Lim, L. C. Kimerling, J. Shin, and F. Cerrina, "Fabrication of ultralow-loss Si/SiO/sub 2/waveguides by roughness reduction," Opt. Lett., vol. 26, pp. 1888–1890, 2001.

- [7] J. Arentoft, T. Sondergaard, M. Kristensen, A. Boltasseva, M. Thorhauge, and L. Frandsen, "Low-loss silicon-on-insulator photonic crystal waveguides," *Electron. Lett.*, vol. 38, pp. 274–275, 2002.

- [8] C. Chang, Y.-F. Wang, Y. Kanamori, J.-J. Shih, Y. Kawai, C.-K. Lee, K.-C. Wu, and M. Esashi, "Etching submicrometer trenches by using the Bosch process and its application to the fabrication of antireflection structures," *J. Micromech. Microeng.*, vol. 15, pp. 580–585, 2005.

- [9] N. Sato and T. Yonehara, "Hydrogen annealed silicon-on-insulator," Appl. Phys. Lett., vol. 65, pp. 1924–6, 1994.

- [10] H. Moriceau, A. M. Cartier, and B. Aspar, "Hydrogen annealing treatment used to obtain high quality SOI surfaces," presented at the IEEE Int. SOI Conf. Proc. (Cat. no. 98CH36199) IEEE 1998, New York, 1998, pp. 37–38.

- [11] J. S. Lee, Y. K. Choi, D. W. Ha, S. Balasubramanian, T. J. King, and J. Bokor, "Hydrogen annealing effect on DC and low-frequency noise characteristics in CMOS FinFETs," *IEEE Electron Device Lett.*, vol. 24, pp. 186–188, 2003.

- [12] T. Sato, K. Mitsutake, I. Mizushima, and Y. Tstrnashima, "Micro-structure transformation of silicon: A newly developed transformation technology for patterning silicon surfaces using the surface migration of silicon atoms by hydrogen annealing," *Japan. J. Appl. Phys. Part 1-Regular Papers Short Notes Rev. Papers*, vol. 39, pp. 5033–5038, 2000.

- [13] S. Jeong and A. Oshiyama, "Complex diffusion mechanisms of a silicon adatom on hydrogenated Si(100) surfaces: On terraces and near steps," *Surf. Sci.*, vol. 435, pp. 481–485, 1999.

- [14] J. Nara, T. Sasaki, and T. Ohno, "Theory of adsorption and diffusion of Si adatoms on H/Si(100) stepped surface," presented at the J. Crystal Growth, vol. 201–202, Netherlands, May 1999, pp. 77–80.

- [15] P. Jeuch, J. P. Joly, and J. M. Hode, "P-glass reflow with a tunable CO/sub 2/laser," in Laser and Electron Beam Interactions with Solids. Proc. Materials Research Society Annual Meeting. Amsterdam, The Netherlands, 1982, pp. 603–608.

- [16] H. Yang, C. Ching-Kong, W. Mau-Kuo, and L. Che-Ping, "High fill-factor microlens array mold insert fabrication using a thermal reflow process," *J. Micromech. Microeng.*, vol. 14, pp. 1197–1204, 2004.

- [17] S. Matsuda, T. Sato, H. Yoshimura, Y. Takegawa, A. Sudo, I. Mizushima, Y. Tsunashima, and Y. Toyoshima, "Novel corner rounding process for shallow trench isolation utilizing MSTS (micro-structure transformation of silicon)," presented at the Int. Electron Devices Meeting 1998. Tech. Dig. (Cat. no. 98CH36217). IEEE, Piscataway, NJ, 1998, pp. 137–140.

- [18] T. Sato, I. Mizushima, and Y. Tsunashima, "A new substrate engineering for the formation of empty space in silicon (ESS) induced by silicon surface migration," *Trans. Inst. Elect. Eng. Japan, Part C*, vol. 121-C, pp. 524–529, 2001.

- [19] H. Kuribayashi, R. Hiruta, R. Shimizu, K. Sudoh, and H. Iwasaki, "Shape transformation of silicon trenches during hydrogen annealing," *J. Vac. Sci. Technol. A-Vacuum Surfaces & Films*, vol. 21, pp. 1279–1283, 2003.

- [20] M.-C. Lee and M. C. Wu, "3D silicon transformation using hydrogen annealing," presented at the Solid-State Sensor, Actuator, Microsystem Workshop, Hilton Head, SC, 2004.

- [21] M.-C. M. Lee, J. Yao, and M. C. Wu, "Silicon profile transformation and sidewall roughness reduction using hydrogen annealing," presented at the 18th IEEE Int. Conf. Micro-Electro-Mechan.-Syst., Miami, FL, 2005.

- [22] P. Bratu, W. Brenig, A. Gross, M. Hartmann, U. Hofer, P. Kratzer, and R. Russ, "Reaction dynamics of molecular hydrogen on silicon surfaces," *Phys. Rev. B-Condensed Matter*, vol. 54, pp. 5978–5991, 1996.

- [23] K. Kitahara and O. Ueda, "Observation of atomic structure by scanning tunneling microscopy of vicinal Si(100) surface annealed in hydrogen gas," *Japan. J. Appl. Phys. Part 2-Lett.*, vol. 33, pp. L1571–3, 1994.

- [24] J. M. Bermond, J. J. Metois, X. Egea, and F. Floret, "The equilibrium shape of silicon," Surf. Sci., vol. 330, pp. 48–60, 1995.

- shape of silicon," *Surf. Sci.*, vol. 330, pp. 48–60, 1995.

[25] W. W. Mullins, "Theory of thermal grooving," *J. Appl. Phys.*, vol. 28, pp. 333–338, 1957.

- [26] K. Sudoh, H. Iwasaki, H. Kuribayashi, R. Hiruta, and R. Shimizu, "Numerical study on shape transformation of silicon trenches by high-temperature hydrogen annealing," *Japan. J. Appl. Phys. Part 1-Regular Papers Short Notes & Review Papers*, vol. 43, pp. 5937–5941, 2004.

- [27] S. Asvadurov, B. D. Coleman, R. S. Falk, and M. Moakher, "Similarity solutions in the theory of curvature driven diffusion along planar curves. I. Symmetric curves expanding in time," *Phys. D*, vol. 121, pp. 263–274, 1998.

- [28] S. T. Liu, L. Chan, and J. O. Borland, "Reaction kinetics of SiO/sub 2//Si(100) interface in H/sub 2/ambient in a reduced pressure epitaxial reactor," presented at the Proc. 10th Int. Conf. Chemical Vapor Deposition 1987. Electrochem. Soc., Pennington, NJ, 1987, pp. 428–434.

- [29] D. V. Armani, T. J. Kippenberg, S. M. Spillane, and K. J. Vahala, "Ultra-high-Q toroid microcavity on a chip," *Nature*, vol. 421, pp. 925–928, 2003.

- [30] W. H. Juan and S. W. Panga, "Controlling sidewall smoothness for micromachined Si mirrors and lenses," presented at the AIP for American Vac. Soc. J. Vacuum Science Technol. B, vol. 14, Nov.–Dec. 1996, pp. 4080–4084.

- [31] A. A. Kundig, M. Cucinelli, P. J. Uggowitzer, and A. Dommann, "Preparation of high aspect ratio surface microstructures out of a Zr-based bulk metallic glass," presented at the Elsevier Microelectronic Engineering, vol. 67–68, Netherlands, Jun. 2003, pp. 405–409.

Ming-Chang M. Lee (S'04–M'05) was born in Taiwan, R.O.C. He received the B.S. degree in control engineering from National Chiao Tung University and the M.S. degree in electrical engineering from National Taiwan University in 1994 and 1996, respectively. He received the Ph.D. degree in electrical engineering from University of California, Los Angeles, in 2005. His Ph.D. work was supervised by Prof. M. C. Wu and involved the use of microelectromechanical systems (MEMS) for tuning optical microresonators.

In 2005, he joined the faculty of the Institute of Photonics Technologies and the Department of Electrical Engineering, National Tsing Hua University, Taiwan. His research interests include optical MEMS, studies of nanophotonics, and the development of integrated photonic devices for optical communication and sensing.

Dr. Lee is a member of the OSA.

Ming C. Wu (S'82–M'83–SM'00–F'02) is received the B.S. degree from National Taiwan University, and the M.S. and Ph.D. degrees from the University of California (UC), Berkeley, in 1983, 1985, and 1988, respectively, all in electrical engineering.

He is currently Professor of Electrical Engineering and Computer Sciences at UC Berkeley, and Co-Director of Berkeley Sensors and Actuators Center (BSAC). Before joining the faculty of UC Berkeley, he was a Member of Technical Staff at AT&T Bell Laboratories, Murray Hill, NJ, from 1988 to 1992,

and Professor of Electrical Engineering at the University of California, Los Angeles (UCLA), from 1993 to 2004. His research interests include optical MEMS, optoelectronics, and biophotonics. He also held the position of Director of Nanoelectronics Research Facility and Vice Chair for Industrial Relations during his tenure at UCLA. In 1997, he cofounded OMM in San Diego, CA, to commercialize MEMS optical switches. He has published more than 400 papers, contributed five book chapters, and holds 11 U.S. patents.

Dr. Wu is a David and Lucile Packard Foundation Fellow (1992-1997). He was the founding Co-Chair of the IEEE LEOS Summer Topical Meeting on Optical MEMS (1996), the predecessor of IEEE/LEOS International Conference on Optical MEMS. He has also served in the program committees of many technical conferences, including MEMS, OFC, CLEO, LEOS, MWP, IEDM, DRC, ISSCC; and as Guest Editor of two special issues of IEEE JOURNALS on optical MEMS.