## Thermal-Diffusivity-Based Frequency References in Standard CMOS

S.M. Kashmiri

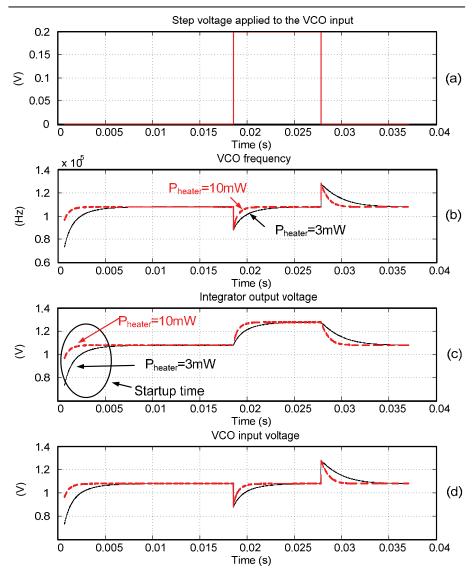

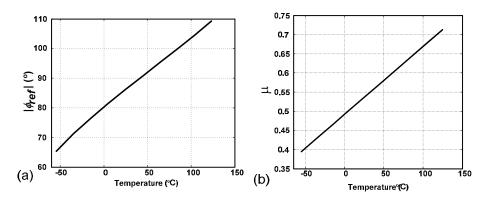

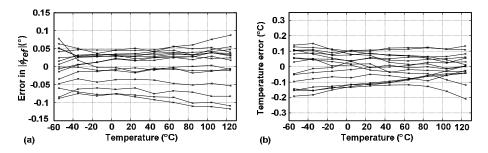

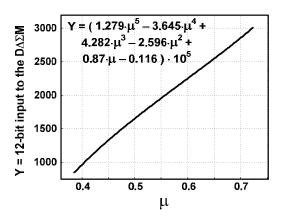

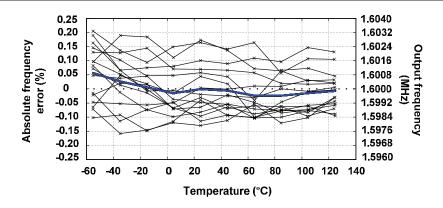

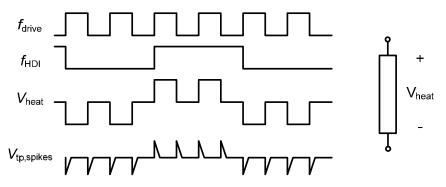

## Thermal-Diffusivity-Based Frequency References in Standard CMOS

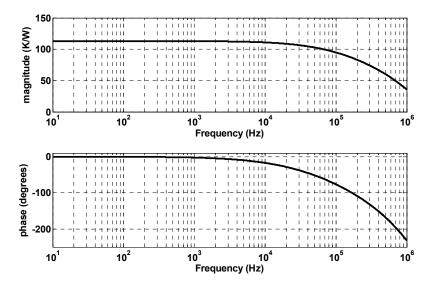

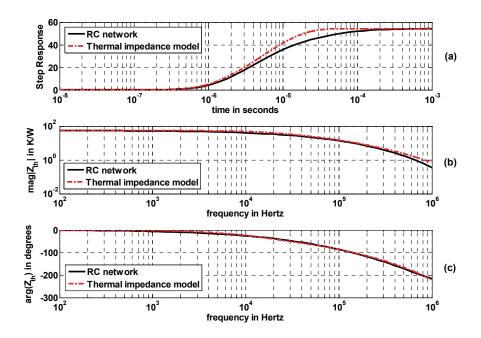

Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties,

> in het openbaar te verdedigen op woensdag 11 april 2012 om 12:30 uur

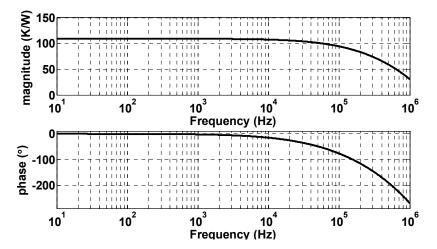

> > door

Sayyed Mahdi KASHMIRI electrotechnisch ingenieur geboren te Tehran, Iran. Dit proefschrift is goedgekeurd door de promotor: Prof.dr. K.A.A. Makinwa

Samenstelling promotiecommissie:

| Rector Magnificus,            | voorzitter                                |  |

|-------------------------------|-------------------------------------------|--|

| Prof.dr. K.A.A. Makinwa       | Technische Universiteit Delft, promotor   |  |

| Prof.dr. E. Charbon           | Technische Universiteit Delft             |  |

| Prof.dr.ir. B. Nauta          | Universiteit Twente                       |  |

| Prof.dr.ir. L.J. Breems       | Technische Universiteit Eindhoven         |  |

| Prof.dr.ir. A.J.M. van Tuijl  | Universiteit Twente                       |  |

| Dr. R.B. Staszewski           | Technische Universiteit Delft             |  |

| Dr. A. Partridge              | SiTime Corporation                        |  |

| Prof.dr.ir. A.J.P. Theuwissen | Technische Universiteit Delft, reservelid |  |

Printed by PrintPartners Ipskamp Drukkers B.V.

ISBN: 978-94-6191-219-0

Copyright © 2012 by S.M. Kashmiri

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by an information storage and retrieval system, without written permission of the author.

Printed in The Netherlands

"I believe in intuition and inspiration. Imagination is more important than knowledge. For knowledge is limited, whereas imagination embraces the entire world, stimulating progress, giving birth to evolution. It is, strictly speaking, a real factor in scientific research."

Albert Einstein, Cosmic Religion: With Other Opinions and Aphorisms, 1931, p. 97.

تقديم به خانواده ام و به اِسمِي

To my family and to Esmée

# **Contents**

| 1 Ir | ntroduction                                                     | 1  |

|------|-----------------------------------------------------------------|----|

| 1.1  | Frequency and its accuracy measures                             | 2  |

| 1.2  | Challenges of integrating frequency references                  | 5  |

| 1.3  | Frequency generation based on the thermal properties of silicon | 7  |

| 1.4  | Motivation                                                      | 10 |

| 1.5  | Challenges                                                      | 11 |

| 1.6  | Thesis organization                                             | 13 |

| 1.7  | References                                                      | 14 |

| 2 s  | ilicon-based Frequency References                               | 17 |

| 2.1  | Introduction                                                    | 17 |

| 2.2  | Silicon MEMS based oscillators                                  | 19 |

| 2.3  | LC Oscillators                                                  | 23 |

| 2.4  | RC harmonic oscillators                                         | 27 |

| 2.5  | RC relaxation oscillators                                       | 29 |

| 2.6  | Ring oscillators                                                | 34 |

|      | 2.6.1 Open-Loop Compensation                                    | 35 |

|      | 2.6.2 Closed-loop Compensation                                  | 37 |

| 2.7  | Mobility-based frequency references                             | 41 |

| 2.8  | Comparison                                                      | 44 |

| 2.9  | Conclusions                                                     | 46 |

| 2.1  | 0 References                                                    | 47 |

## 3 Frequency References Based on the Thermal Properties of Silicon 53

| 3.1  | Introdu                               | ction                                              | 54 |  |  |

|------|---------------------------------------|----------------------------------------------------|----|--|--|

| 3.2  | Thermal Properties of Silicon 55      |                                                    |    |  |  |

| 3.3  | Electro                               | thermal Filters in CMOS                            | 60 |  |  |

| 3.4  | ETF de                                | sign                                               | 64 |  |  |

|      | 3.4.1                                 | General heater considerations                      | 64 |  |  |

|      | 3.4.2                                 | General thermopile considerations                  | 65 |  |  |

|      | 3.4.3                                 | Design of a bar ETF                                | 68 |  |  |

|      | 3.4.4                                 | Design of an optimized ETF                         | 69 |  |  |

| 3.5  | Modeli                                | ng for time-domain analysis                        | 70 |  |  |

| 3.6  | Therma                                | l oscillators                                      | 72 |  |  |

| 3.7  | Electrothermal frequency-locked loops |                                                    |    |  |  |

| 3.8  | Electro                               | thermal FLL as foundation for frequency references | 79 |  |  |

| 3.9  | Dynam                                 | ics of an electrothermal FLL                       | 81 |  |  |

| 3.1( | ) FLL be                              | chavioral simulations                              | 87 |  |  |

| 3.1  | The eff                               | fect of noise on an FLL's jitter                   | 90 |  |  |

|      | 3.11.1                                | ETF noise                                          | 90 |  |  |

|      | 3.11.2                                | Implications for FLL design                        | 93 |  |  |

|      | 3.11.3                                | VCO noise                                          | 95 |  |  |

| 3.12 | <b>2</b> Challe                       | enges associated with the previous FLL's           | 96 |  |  |

| 3.13 | B Conclu                              | usions                                             | 97 |  |  |

| 3.14 | 4 References                          |                                                    |    |  |  |

### 4 A Digitally-Assisted Electrothermal Frequency-Locked Loop in Standard CMOS 101

| 4.1 | Introdu | action                            | 102 |

|-----|---------|-----------------------------------|-----|

| 4.2 | Propos  | ing a digitally-assisted FLL      | 103 |

|     | 4.2.1   | Operating principle               | 103 |

|     | 4.2.2   | DAFLL system-level specifications | 104 |

|     |         |                                   |     |

|                        | 4.2.3         | DAFLL      | realization phases                                         | 106                |

|------------------------|---------------|------------|------------------------------------------------------------|--------------------|

| 4.3                    | First te      | est chip   |                                                            | 107                |

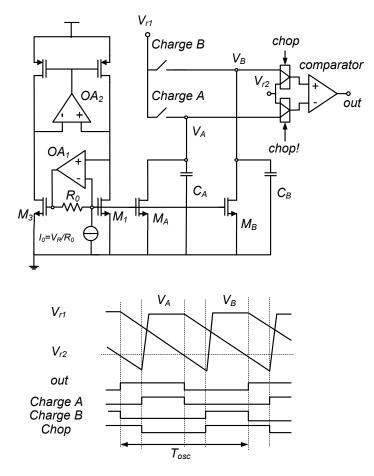

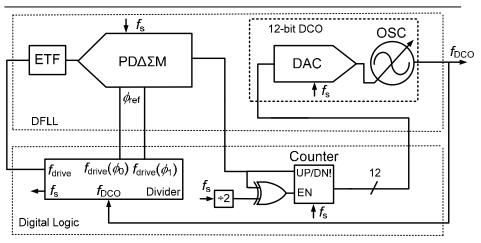

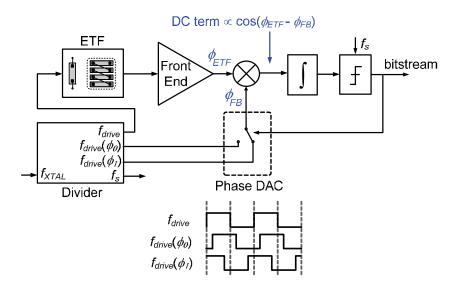

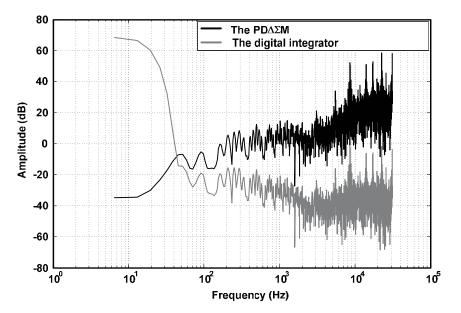

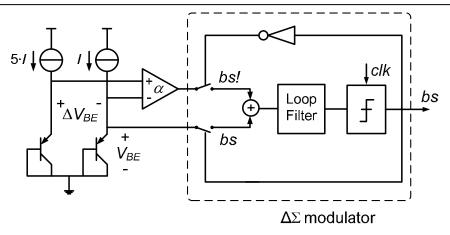

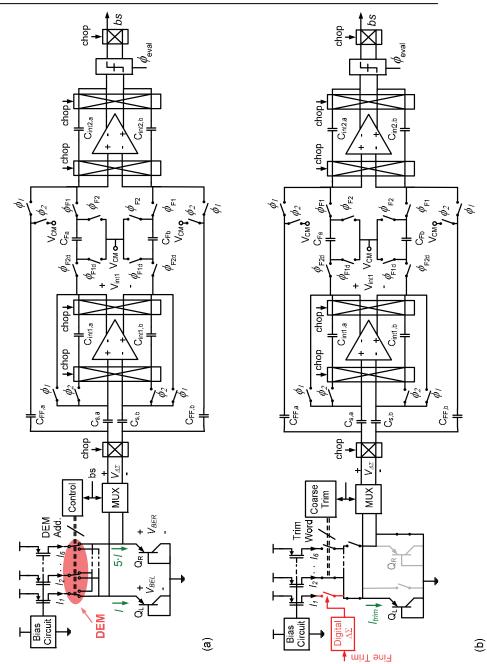

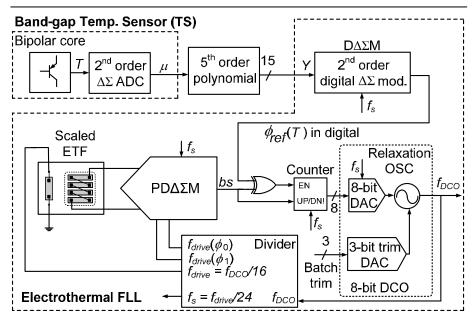

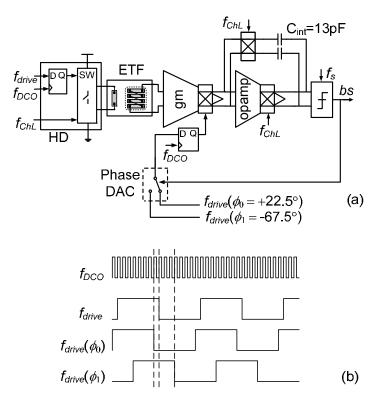

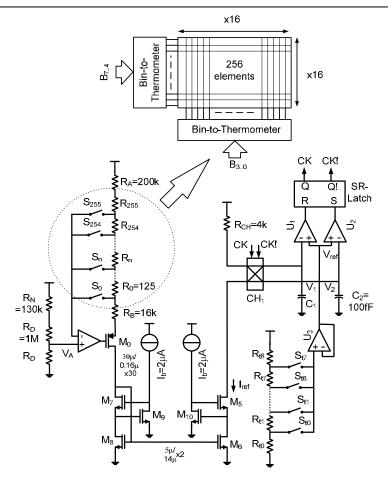

|                        | 4.3.1         | ΡΟΔΣΜ      | 1 system-level architecture                                | 107                |

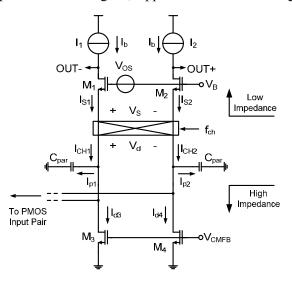

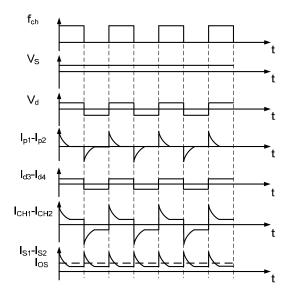

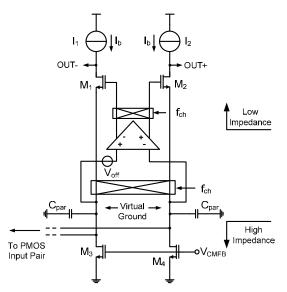

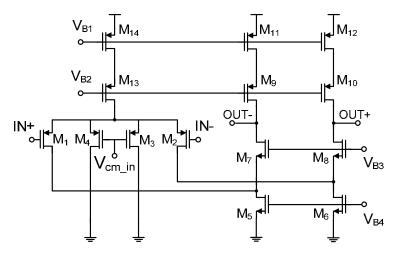

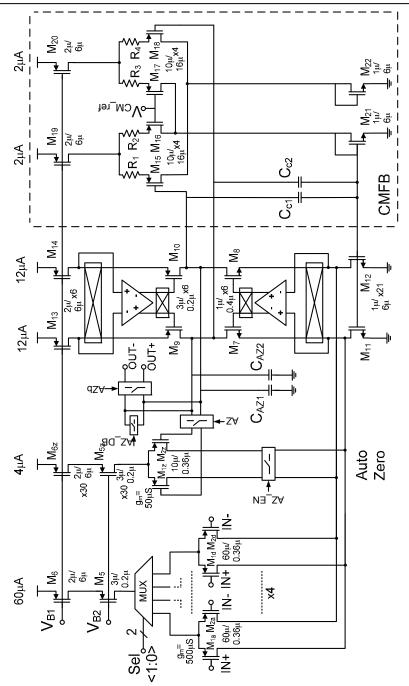

|                        | 4.3.2         | ΡΟΔΣΜ      | 1 circuit design                                           | 113                |

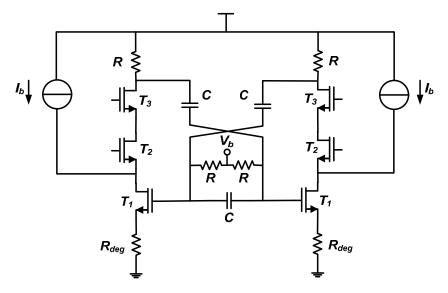

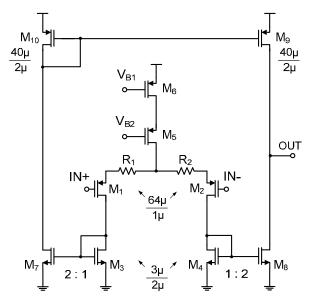

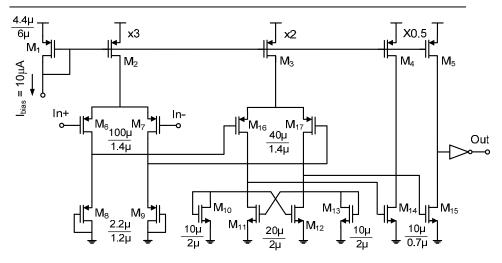

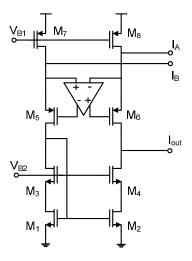

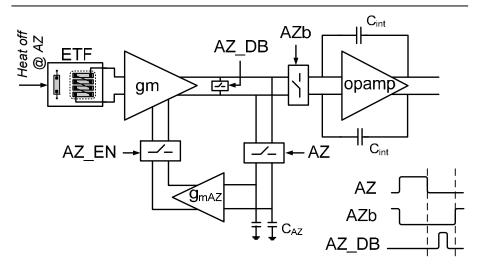

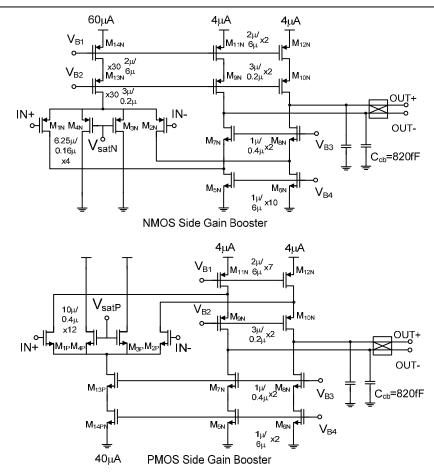

|                        |               | 4.3.2.1    | Transconductor design                                      | 114                |

|                        |               | 4.3.2.2    | Residual offset                                            | 116                |

|                        |               | 4.3.2.3    | Gain-boosting and residual offset reduction                | 118                |

|                        |               | 4.3.2.4    | Differential-to-single-ended amplifier                     | 121                |

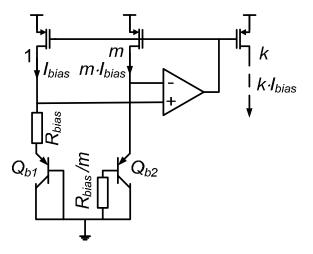

|                        |               | 4.3.2.5    | Bias circuit                                               | 122                |

|                        | 4.3.3         | First ch   | ip experimental results                                    | 123                |

|                        | 4.3.4         | Conclus    | sions from the first test chip                             | 127                |

| 4.4                    | Secon         | d test chi | p                                                          | 127                |

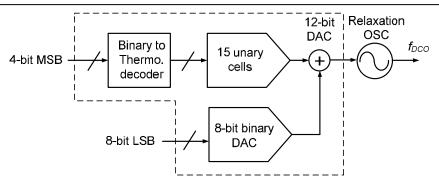

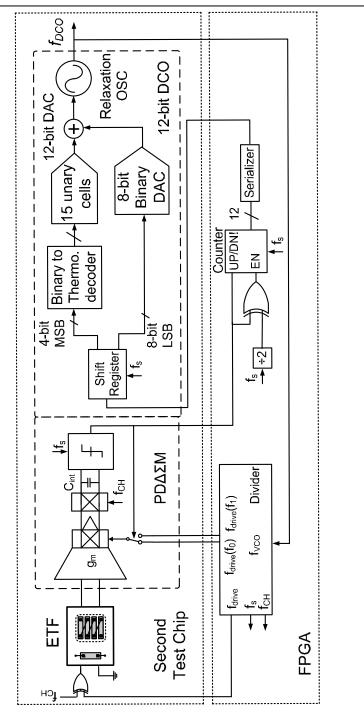

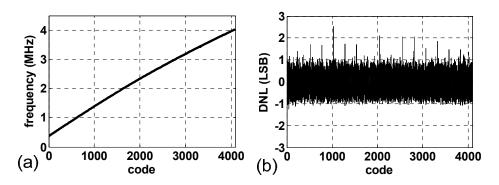

|                        | 4.4.1         | DCO sy     | stem-level architecture                                    | 127                |

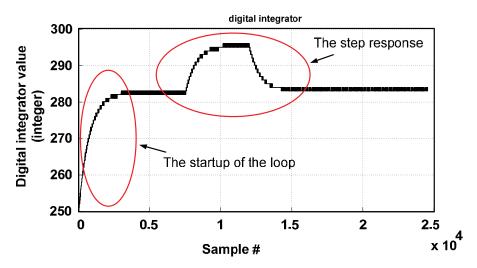

|                        | 4.4.2         | Comple     | te DAFLL system-level simulations                          | 128                |

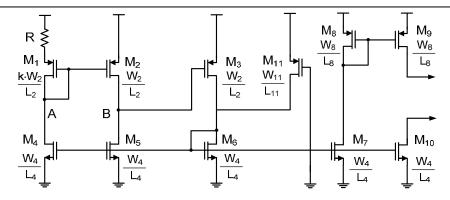

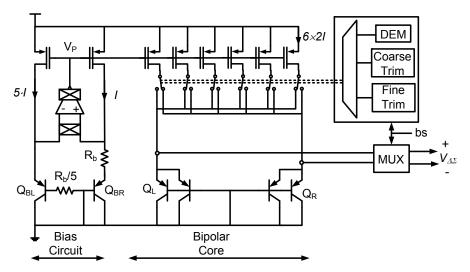

|                        | 4.4.3         | DCO ci     | rcuit design                                               | 131                |

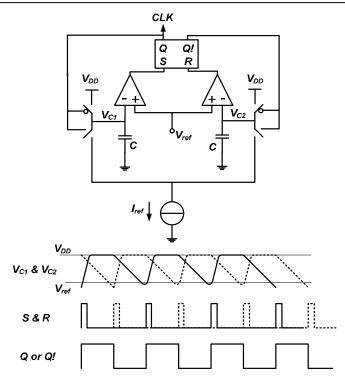

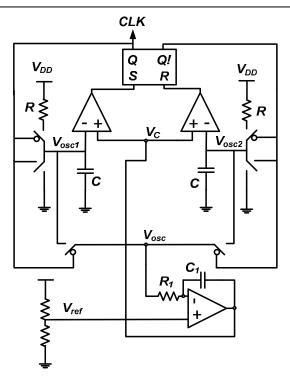

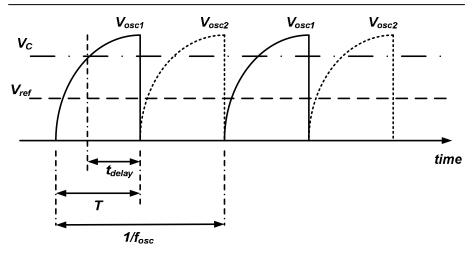

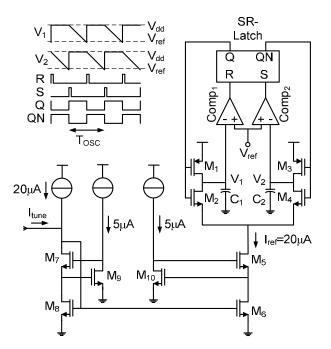

|                        |               | 4.4.3.1    | Relaxation oscillator                                      | 131                |

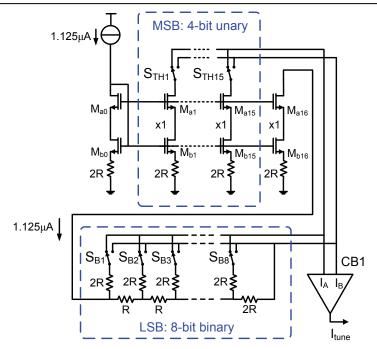

|                        |               | 4.4.3.2    | 12-bit current-steering DAC                                | 133                |

|                        | 4.4.4         | Experin    | nental results with the second test chip                   | 134                |

|                        |               |            | effective thermal-diffusivity of CMOS chips us             | ing a<br>137       |

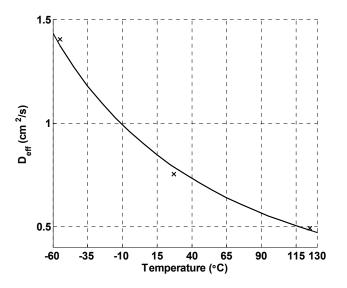

|                        | 4.5.1         | The esse   | ence of measuring $D_{\rm eff}$                            | 137                |

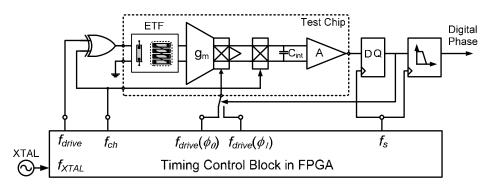

|                        | 4.5.2         | Thermal    | diffusivity measurement using CMOS ETFs                    | . 138              |

|                        | 4.5.3         | An elect   | rothermal FLL as a test vehicle in measuring $D_{\rm eff}$ | 139                |

|                        | 4.5.4         | Experim    | ental results                                              | 139                |

| <b>4.6</b> Conclusions |               |            |                                                            |                    |

| 4.7                    | Refere        | ences      |                                                            | 142                |

|                        | 4 The<br>um C |            | iffusivity Frequency Reference in Stand                    | <i>lard</i><br>145 |

| 5.1 | Introduction | <br>145 |

|-----|--------------|---------|

|     | -     | -       | compensation       |      |              |     |       |     |

|-----|-------|---------|--------------------|------|--------------|-----|-------|-----|

|     |       |         | f a TD frequen     | -    |              |     | •     |     |

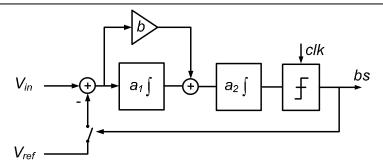

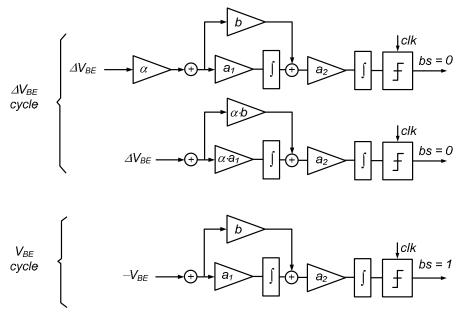

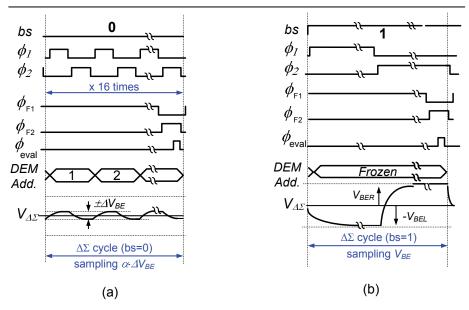

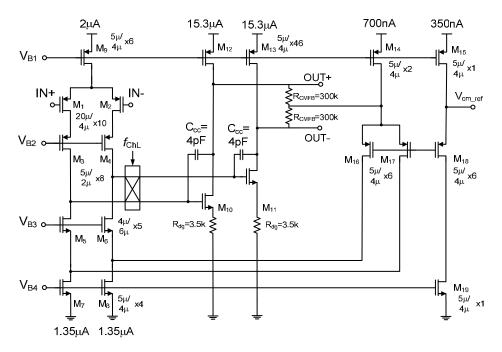

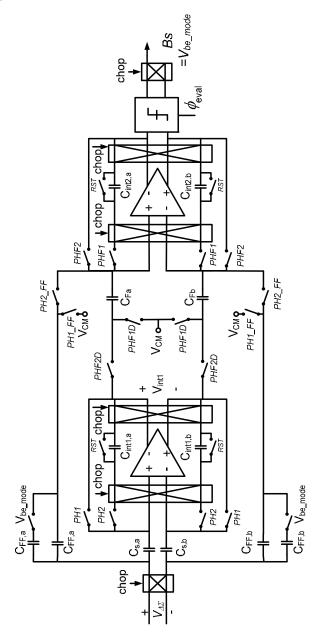

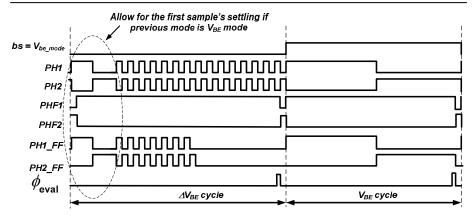

|     | 5.3.1 | System  | -level design of t | he r | eference     |     |       | 151 |

|     | 5.3.2 | The bar | nd-gap temperatu   | re s | ensor desig  | n   |       | 154 |

|     |       | 5.3.2.1 | System-level de    | sign |              |     |       | 154 |

|     |       | 5.3.2.2 | Circuit design     |      |              |     |       | 157 |

|     |       | 5.3.2.3 | Implications of    | sing | le capacitor | sam | pling | 162 |

|     | 5.3.3 | Experi  | mental results     |      |              |     |       | 163 |

| 5.4 | Conc  | lusions |                    |      |              |     |       | 168 |

| 5.5 | Refe  | rences  |                    |      |              |     |       | 169 |

## 6 A Scaled Thermal-Diffusivity Frequency Reference in Standard 0.16µm CMOS 173

| Intro | duction                                                                              |                                                                                                                                                                                                          | 174                                                                                                                                                                                                                                                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Scali | ng strate                                                                            | gy                                                                                                                                                                                                       | 175                                                                                                                                                                                                                                                                                                                                                                            |

| Syste | em-level                                                                             | design                                                                                                                                                                                                   | 180                                                                                                                                                                                                                                                                                                                                                                            |

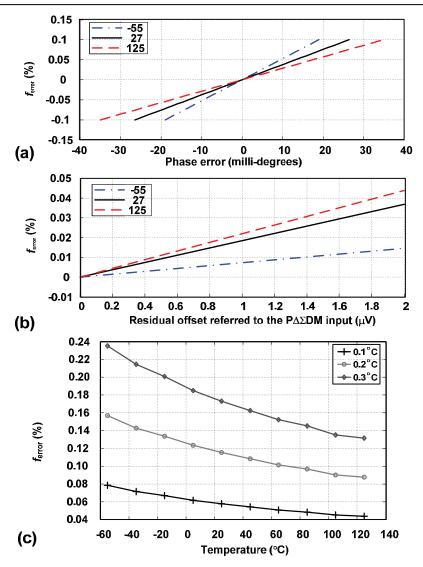

| Error | r sources                                                                            |                                                                                                                                                                                                          | 181                                                                                                                                                                                                                                                                                                                                                                            |

| Circu | uit Realiz                                                                           | zations                                                                                                                                                                                                  | 183                                                                                                                                                                                                                                                                                                                                                                            |

| 6.5.1 | ETF an                                                                               | d РДДМ                                                                                                                                                                                                   | 183                                                                                                                                                                                                                                                                                                                                                                            |

|       | 6.5.1.1                                                                              | Detailed system overview                                                                                                                                                                                 | 183                                                                                                                                                                                                                                                                                                                                                                            |

|       | 6.5.1.2                                                                              | Transconductor                                                                                                                                                                                           | 185                                                                                                                                                                                                                                                                                                                                                                            |

|       | 6.5.1.3                                                                              | Integrator Opamp                                                                                                                                                                                         | 190                                                                                                                                                                                                                                                                                                                                                                            |

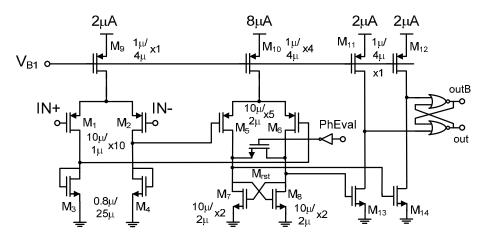

|       | 6.5.1.4                                                                              | Comparator                                                                                                                                                                                               | 191                                                                                                                                                                                                                                                                                                                                                                            |

| 6.5.2 | DCO                                                                                  |                                                                                                                                                                                                          | 192                                                                                                                                                                                                                                                                                                                                                                            |

| 6.5.3 | Tempe                                                                                | rature sensor                                                                                                                                                                                            | 194                                                                                                                                                                                                                                                                                                                                                                            |

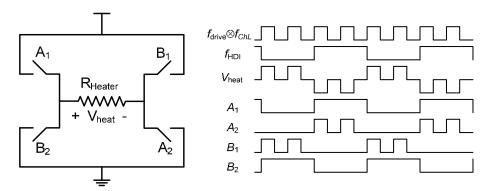

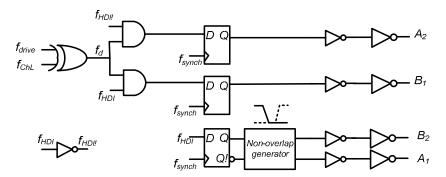

| 6.5.4 | Heater                                                                               | Drive Circuitry                                                                                                                                                                                          | 198                                                                                                                                                                                                                                                                                                                                                                            |

| Expe  | rimental                                                                             | Results                                                                                                                                                                                                  | 201                                                                                                                                                                                                                                                                                                                                                                            |

| Conc  | clusions                                                                             |                                                                                                                                                                                                          | 206                                                                                                                                                                                                                                                                                                                                                                            |

| Refe  | rences .                                                                             |                                                                                                                                                                                                          | 206                                                                                                                                                                                                                                                                                                                                                                            |

|       | Scali<br>Syste<br>Error<br>Circu<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>Expe<br>Cond | Scaling strate<br>System-level<br>Error sources<br>Circuit Realiz<br>6.5.1 ETF an<br>6.5.1.1<br>6.5.1.2<br>6.5.1.3<br>6.5.1.4<br>6.5.2 DCO<br>6.5.3 Tempe<br>6.5.4 Heater<br>Experimental<br>Conclusions | Introduction         Scaling strategy         System-level design         Error sources         Circuit Realizations <b>6.5.1</b> ETF and PDΔM <b>6.5.1.2</b> Transconductor <b>6.5.1.3</b> Integrator Opamp <b>6.5.1.4</b> Comparator <b>6.5.3</b> Temperature sensor <b>6.5.4</b> Heater Drive Circuitry         Experimental Results         Conclusions         References |

| 7 ( | Conclusions and Outlook               | 209               |

|-----|---------------------------------------|-------------------|

| 7.1 | Main findings                         | 209               |

| 7.2 | Future work                           | 211               |

| 7.3 | References                            | 212               |

| A   | Time-Domain Modeling of an Electrothe | rmal DAFLL<br>215 |

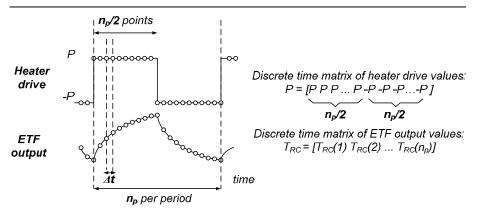

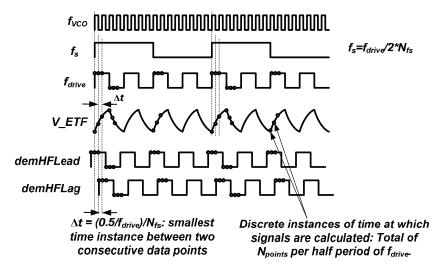

| A.1 | Time-domain simulation of an ETF      |                   |

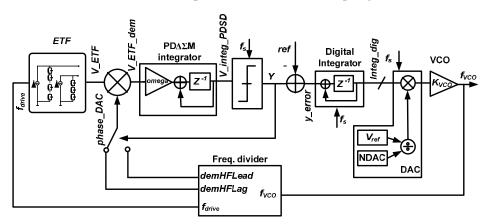

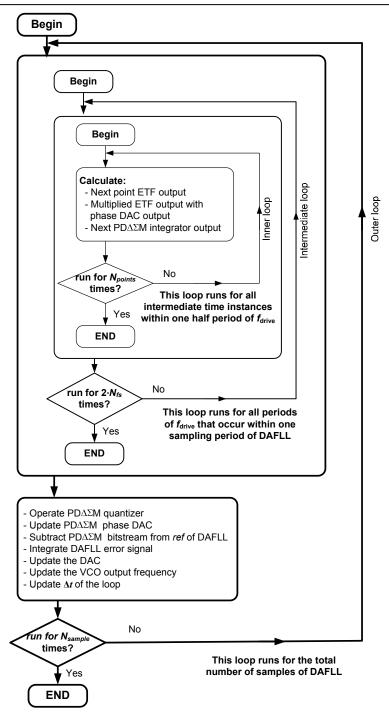

| A.2 | Time-domain simulation of the DAFLL   |                   |

| A.3 | References                            | 228               |

| Summary              | 229 |

|----------------------|-----|

| Samenvatting         | 233 |

| List of Publications | 237 |

| About the Author     | 239 |

| Acknowledgements     | 241 |

# **1** Introduction

The operation and performance of electronic systems often depends on the accuracy of the clock signals that determine their timing. For decades, these signals have been generated by quartz crystal oscillators, which dominate the 4.5 billion dollar market for frequency control components; however, due to the dedicated manufacturing process used for quartz crystals, they can not be integrated into micro-chips. For years, designers have tried to make integrated frequency references that can compete with the stability of quartz crystal oscillators. These efforts have resulted in various types of silicon-based frequency references. Some of these references combine a MEMS (Micro Electro Mechanical System) resonator with a silicon chip. Others are based on integrated elements such as resistors, capacitors, or inductors.

This thesis describes an alternative approach to the realization of integrated frequency references. Unlike other approaches, it does not rely on the accuracy of on-chip electrical components. Instead, it is based on the thermal properties of silicon. In the past, these properties have been used to build on-chip thermal delay lines intended for filter applications. The operation of such filters is governed by a physical parameter called the thermal-diffusivity. This is a measure of the rate at which heat diffuses through a silicon substrate. The thermal-diffusivity-based (TD) frequency references proposed in this thesis can be realized in a standard CMOS process, which is the mainstream technology for the high-volume production of integrated circuits. In this thesis it will be shown that output frequencies

1

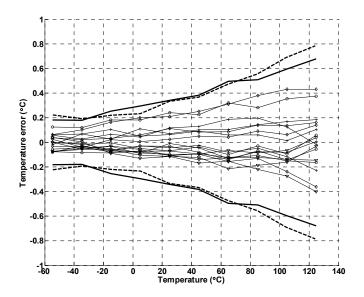

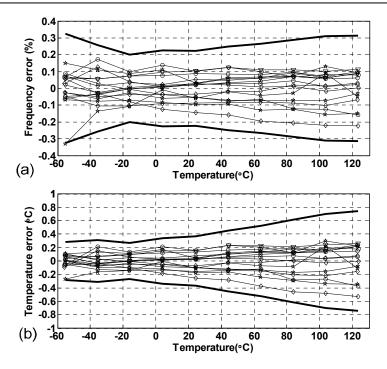

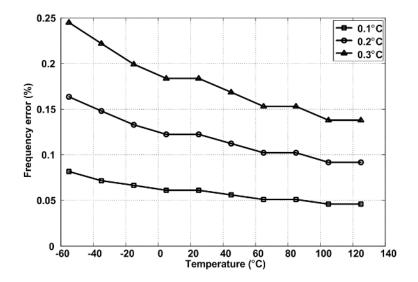

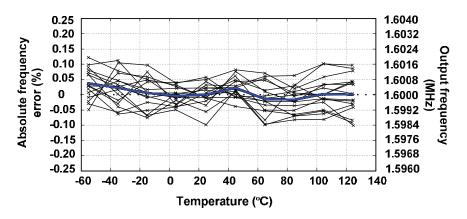

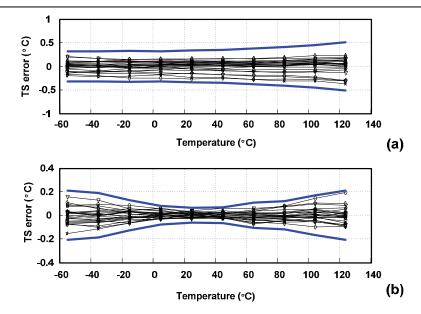

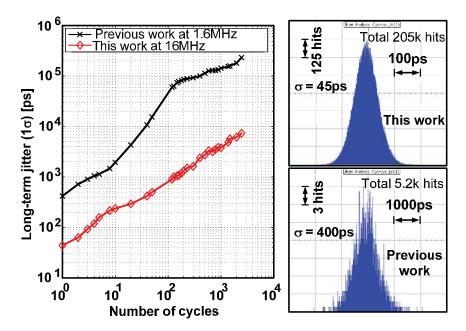

up to 16MHz and stabilities of  $\pm 0.1\%$  over the military temperature range (-55°C to 125°C) can be achieved. Furthermore, it will be demonstrated that thermal-diffusivity-based frequency references benefit from CMOS scaling.

This chapter is an introduction to the thesis. It starts with a brief discussion of various parameters related to frequency and its stability. Furthermore, an overview of quartz crystal oscillators and the efforts towards their replacement is provided. Thermal oscillators, initially meant for temperature-to-frequency conversion, are introduced as the predecessors of thermal-diffusivity-based frequency references. Further, the thermal diffusivity concept and the way it can be harnessed in a standard CMOS process is described. The chapter ends by presenting the motivations, challenges and the organization of the thesis.

#### 1.1 Frequency and its Accuracy Measures

Frequency and time are interdependent parameters. Everyone has a feeling of time, a parameter that has been measured historically by keeping track of natural phenomena such as the cycles of day, night, and seasons [1.1]. The unit of time is the second, the smallest quantity that most wristwatches can indicate. Frequency, denoted by the symbol f, is the number of occurrences of a periodic event within one second [1.2]. The unit of frequency is Hertz (Hz), meaning that a periodic event that occurs once per second has a frequency of one Hz. For instance, a violin string that produces an E musical note, vibrates 660 times in a second, corresponding to a frequency of 660Hz. Furthermore, the duration of one cycle of a repetitive event is its period, which is denoted by the symbol T. The period T is equal to the reciprocal of the frequency f.

In ancient times (thousands of years BC), the Egyptians used obelisks and sundials to keep track of time (Figure 1.1) [1.3]. Later, it was discovered that an object with a reliable periodic movement (stable frequency) could also be used to keep time. One of these early objects was the pendulum (Figure 1.1). In 1583, Galileo discovered that a pendulum swings with a nearly constant period. Later, in 1656, Huygens invented the pendulum clock. After the invention of quartz-crystal oscillators in 1918, it was possible to embed quartz crystals with oscillation frequencies of 32,768Hz into electronic wrist watches [1.1]. This specific frequency can be easily related to a 1Hz event via a binary counter that divides the oscillator frequency by 2<sup>15</sup>. Cesium atomic clocks were developed in the 50's. This invention enabled extremely accurate time (frequency) measurements, with an inaccuracy of one second in ten million years [1.1]!

Figure 1.1. (a) Sundials, (b) obelisks, (c) pendulum, (d) pendulum clock, (e) quartz crystal, and (f) Cesium atomic clock.

Most of us encounter the concept of frequency on a daily basis in the form of musical notes, radio frequencies, etc. However, these are not the only ways that frequency plays a role in our modern lives. In the current era of information, we send and receive data through our communication devices. It is because of the accurate and stable generation and detection of frequencies that we have mobile phones, wired and wireless data networks, ever faster computers, navigation systems based on the Global Positioning System (GPS), etc. In all these systems, accurate frequency sources allow data from different channels to be combined, sent through a communication medium, and successfully received at the destination.

The accuracy and stability of frequency references are crucial to the operation of any instrument that uses them. A faulty or broken tuning fork produces a resonant frequency that deviates from the desired musical tone. A music instrument tuned with that fork might then irritate a musician's sensitive ears. If the local oscillator in an FM radio has an unstable frequency that jumps around every now and then, the received signal will, accordingly, jump back and forth between the various channels. If the same oscillator has a poor noise performance, then you might hear the news in the background of your desired jazz music. If the crystal oscillators in your cell phone are too temperature dependent, your call will drop every time you step out of your warm office onto the cold snowy streets. Finally, if the frequency reference in your MP3 player does not meet the USB standard, copying an MP3 file through the USB port of your laptop might require several attempts.

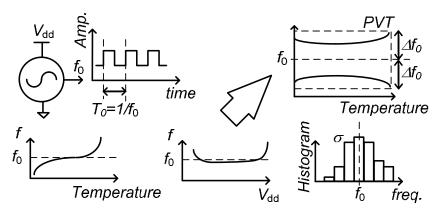

The abovementioned examples tell us that a frequency reference needs to have a certain level of accuracy, stability and noise performance [1.4]. This means that parameters should be defined to describe the quality of such a reference. In principle, an electrical frequency reference can be regarded as a circuit block that receives a supply voltage  $V_{DD}$  and produces a periodic output signal at a target frequency  $f_0$  (Figure 1.2). The stability of a frequency reference can be considered from various points of view. One

3

such view involves observing how the output frequency  $f_0$  varies as a function of environmental parameters such as ambient temperature and supply voltage  $V_{DD}$ . Furthermore, variations in the fabrication process can shift the value of  $f_0$ . The combined effect of these parameters (process, voltage, and temperature) is called the PVT tolerance of a reference.

The graphical illustrations in Figure 1.2 show how each of the PVT elements can affect the nominal frequency of a frequency reference. Over its full range of variations, each parameter causes a certain amount of deviation in the nominal value of  $f_0$ . When the effects of all parameters are added, a total deviation of  $\Delta f_0$  can be expected in the reference's frequency. This is a proportion of the nominal oscillation frequency  $f_0$ , and thus the ratio  $\Delta f_0 / f_0$  is normally denoted in percentage (%) or in parts-per-million (ppm). This is a measure of the frequency reference's stability and determines its overall level of inaccuracy.

Figure 1.2. Effects of process, voltage, and temperature variations on an oscillator's output frequency (PVT effect).

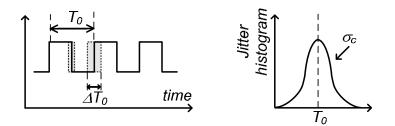

Figure 1.3. Variations in the period of oscillation due to noise and the jitter histogram.

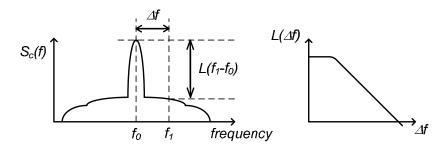

Figure 1.4. Phase noise of an oscillator.

Apart from the stability or accuracy of a frequency reference, its output also includes noise. This noise adds uncertainty to the period of oscillation. This is shown in Figure 1.3, where a few cycles of a square-wave clock are illustrated. In this figure, the period of oscillation has a random variation due to noise, which usually has a Gaussian distribution [1.5][1.6][1.7]. The average value of this distribution has a mean, which is the average period of oscillation called  $T_0 = 1/f_0$ . The standard deviation of this distribution,  $\sigma_C$ , is defined as the cycle-to-cycle jitter, which is a measure of the magnitude of period fluctuations. Jitter is normally defined as a root-mean-squared (rms) quantity.

Jitter is a time-domain means of quantifying the noise in an oscillation period, but this can also be done in the frequency domain. The associated parameter is called phase noise [1.5], and is especially important for sinewave oscillators used in telecommunication applications [1.7]. Ideally, the frequency-domain representation of a sine-wave signal has a power spectral density in the form of a peak occurring at the frequency of oscillation,  $f_0$ . Due to noise in the phase of this sinusoidal signal  $S_C(f)$ , its power spectrum will exhibit a "skirt" as shown in Figure 1.4. The amplitude of this skirt at frequencies with a certain offset with respect to  $f_0$  is an important parameter in the design of radio receivers. In such applications, the local oscillator's phase noise will affect the receiver's selectivity [1.8]. The phase noise spectrum  $L(\Delta f)$ , is defined as the attenuation in dB referenced to the value of  $S_C(f)$  at  $f_0$  and at an offset frequency  $\Delta f = f_1 - f_0$ . This is normalized to the main carrier's power and denoted in dBc/Hz (see Figure 1.4).

#### 1.2 Challenge of Integrating Frequency References

Historically, crystal oscillators have been the only frequency control components that could achieve high performance with regard to accuracy and noise [1.9]. However, due to the dedicated manufacturing process of a quartz crystal, they are nearly impossible to realize in IC technology. For years, integration has brought more reliability to electronic systems allowing

for lower prices and more functionality at smaller form factors. This is thanks to the reliable and large volume production made available by IC technologies such as the CMOS process, which have advanced with the evolution of microprocessors. To benefit from this integration trend, researchers and analog circuit designers have faced the challenge of producing frequencies as stable as those made by quartz crystal oscillators, but only through the use of on-chip circuitry [1.10].

Integrated (silicon-based) frequency references need to rely on the properties of on-chip elements in order to produce accurate time constants. Of the various methods that have been developed in the past decades, only a few have been commercialized so far. One of them is the silicon MEMS resonator-based oscillator, in which the quartz crystal is replaced by a MEMS resonating structure. The resonator is then attached to another silicon die with the circuitry that maintains the oscillation and performs the temperature compensation [1.11]. MEMS based frequency references with sub-ppm stabilities are now available commercially [1.12]. They can replace quartz crystal oscillators with packages that have exactly the same foot-print. The major difficulty with this technology is the special processing required for the fabrication of MEMS structures, which makes their integration with baseline IC technologies such as standard CMOS uneconomic. This usually leads to a solution requiring two dies within one package.

Standard CMOS compatibility of an integrated frequency reference makes it possible to combine it with larger systems-on-a-chip. Such complicated systems combine accurate analog functionalities with sophisticated digital signal processing in a single die and are normally implemented in CMOS process. Various standard-CMOS-compatible frequency references have been introduced so far, mainly relying on passive elements such as resistors, capacitors, and inductors. Among these, LC oscillators (using inductors and capacitors in a resonant circuit) [1.13] have been commercialized. These oscillators achieve accuracies in the order of a few hundred ppm by means of trimming and temperature compensation. RC oscillators dissipate less power than the LC oscillators; however, their accuracy is limited to tens of thousands of ppm [1.14]. Although, this certainly does not compete with the accuracy of quartz crystals, RC oscillators are often used in low-power applications such as biomedical implants.

Traditionally, the methods of realizing integrated frequency references make use of the generation, transfer, and processing of signals in the electrical or mechanical energy domains. RC and LC oscillators are purely electrical, while MEMS based resonators are electro-mechanical parts. The frequency generated by each of these methods depends on the manufacturing process and on the effect of temperature variations. These dependencies necessitate some means of trimming and temperature compensation in order to achieve reasonable accuracies. Sometimes, the lack of correlation among the various sources of variation requires multi-point temperature trimming, which increases the manufacturing costs.

Questions that we might ask ourselves could be: "Is there another physical property of silicon (besides the electrical-domain properties) that is stable enough and can be used as a means of producing time (frequency) references? Could this property be harnessed by means of electronic circuitry? Is this property something that can be used in any IC technology, especially within the standard CMOS process? Is it a property with reproducible behavior in response to environmental parameters such as temperature? Is a research plan for investigating the possibilities and limitations of using this property for the goal of on-chip frequency generation attractive?"

#### 1.3 Frequency Generation Based on the Thermal Properties of Silicon

Energy can be produced, processed and transferred in any of the five physical domains. These include the electrical, mechanical, chemical, thermal and electromagnetic domains. Efforts to generate stable on-chip frequency references have, so far, mainly concentrated on the electrical, mechanical and the electromagnetic domains. The *thermal-domain* properties of silicon have received much less attention.

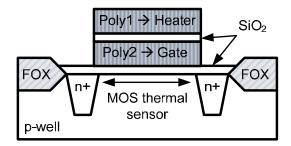

The first publications in this field date back to the 1970's, when the transport of thermal signals in microelectronic structures was investigated. In 1971, Gray and Hamilton showed [1.15] that the interactions between electrical and thermal-domain signals can be used to produce large time constants in silicon integrated circuits. Their main interest was to produce filters with very low cut-off frequencies. These efforts resulted in microstructures in which integrated heaters were fabricated close to

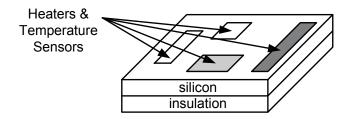

Figure 1.5. *Micro heaters and temperature sensors diffused into a silicon substrate.*

integrated thermal sensors and within a silicon substrate (see Figure 1.5). In such structures, the heat dissipated in the heater diffuses through the substrate and is sensed by the temperature sensor after a certain *thermal delay*. This delay is associated with the substrate's thermal inertia. Hamilton used this technique to realize integrated high-Q band-pass filters with bandwidths ranging from a few Hertz to a few hundred Hertz [1.16].

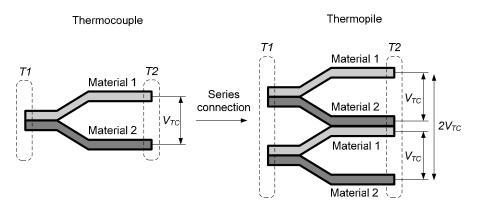

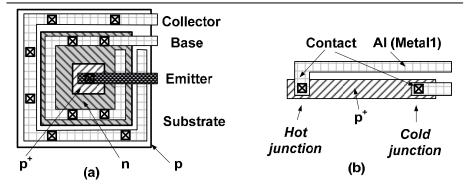

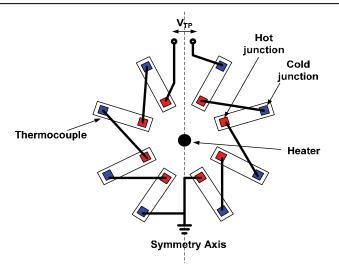

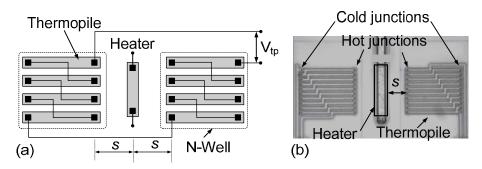

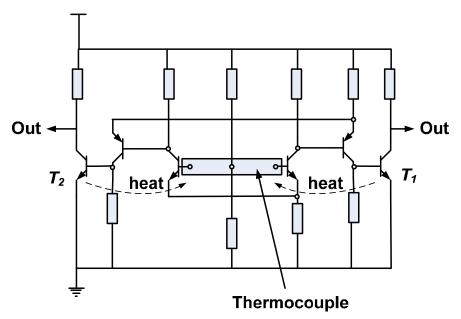

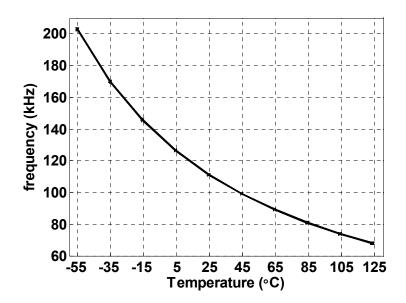

In 1972, Bosch, a researcher at Philips Research Laboratories, proposed [1.17] the use of the Seebeck (thermoelectric) effect, i.e. the direct conversion of temperature difference to electric voltage, to realize on-chip temperature sensors in the form of thermocouples [1.18]. These were made by "p" or "n" type semiconductor materials in contact with Aluminum. He considered locating a heater about 200µm apart from a thermocouple [1.18]. An amplifier fed back the output of this thermocouple to the heater, forming a thermal oscillator. Bosh reported a nominal oscillation frequency of 200 kHz, but did not publish measurement results describing the effect of process and temperature variations. Further work on thermal oscillators was published in 1995 by Szekely [1.19], in which the behavior of a thermal relaxation oscillator was investigated over temperature. This was with the special interest of studying the possibility of using thermal oscillators as temperature-to-frequency converters.

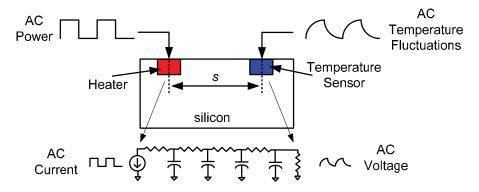

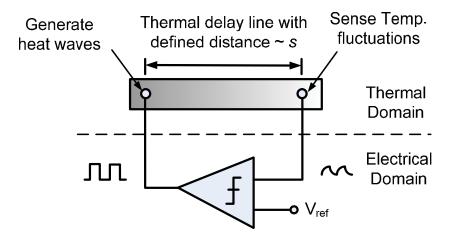

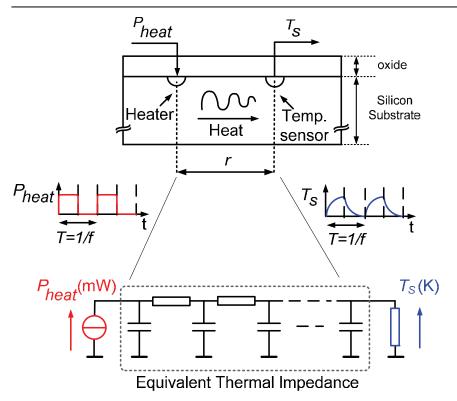

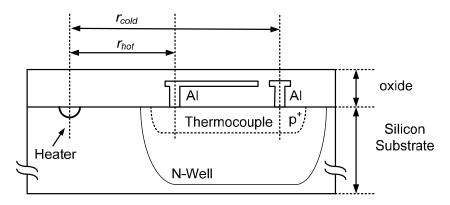

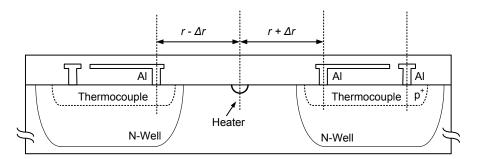

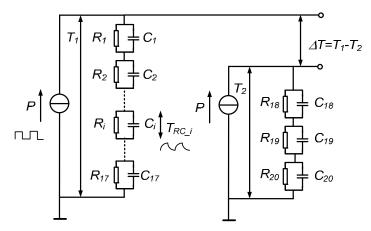

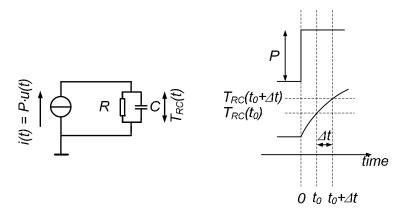

The concept of thermal oscillators builds on the well-defined thermal delays that can be realized in microstructures. Such delays involve the transfer of heat within a defined geometry, fabricated in a silicon substrate. The substrate acts as the heat transferring medium. Figure 1.6 illustrates the side view of a silicon slab, in which a diffusion heater, e.g. a resistor, is implemented in close proximity (*s* is a few tens of microns) to a relative temperature sensor, e.g. a thermopile. The heat generated in the heater diffuses through the substrate and results in a local temperature change. This

Figure 1.6. Silicon slab with a heater and a temperature sensor implemented in it at a distance s and the electrical circuit equivalent to it.

is mediated by phonons [1.20] and thus involves mechanical vibration within the silicon atoms of the lattice.

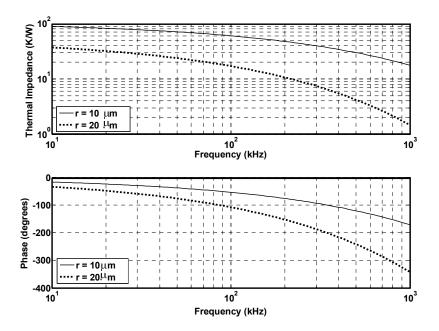

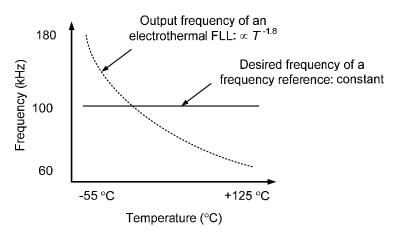

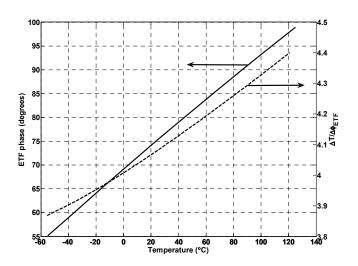

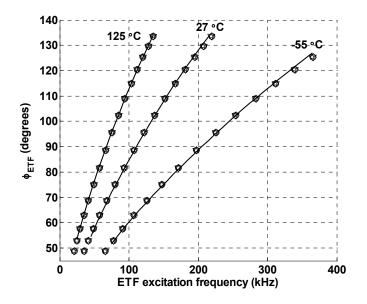

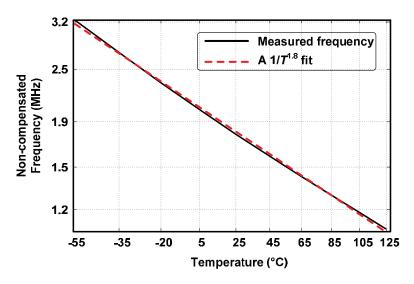

The rate at which heat diffuses through the substrate is determined by the thermal-diffusivity of silicon, D (in cm<sup>2</sup>s<sup>-1</sup>) [1.21][1.22], which is a temperature dependent parameter. This dependency is associated with the effect of temperature on the silicon lattice causing its expansion or contraction and affecting the mechanical vibration of the crystalline silicon atoms. In the past, the temperature dependence of D has been characterized over various temperature ranges. These are summarized in [1.22], indicating an approximate relation of  $T^{-1.8}$  (where T is the absolute temperature) [1.22][1.23]. This implies that the thermal delay resulting from the thermal diffusivity of silicon will also be a function of temperature.

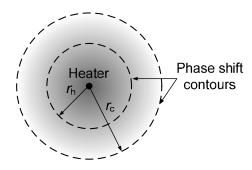

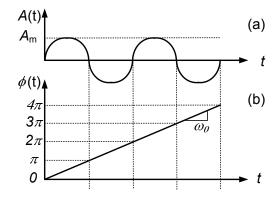

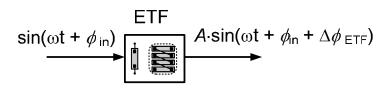

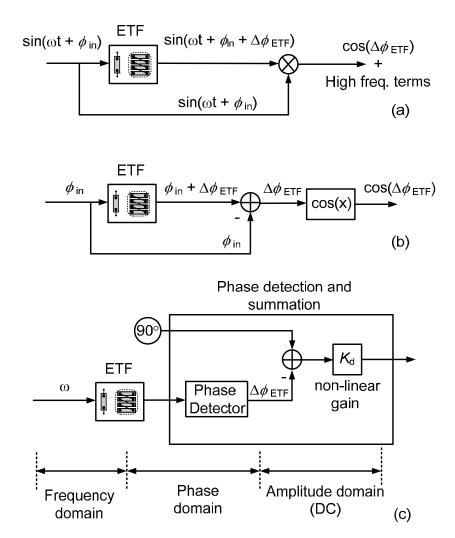

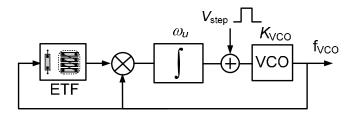

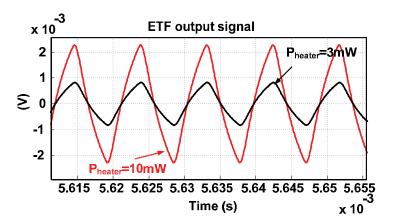

If AC power is dissipated in the structure shown in Figure 1.6, the resulting temperature fluctuations at the temperature sensor will be translated back into an AC electrical signal. However, the phase of this signal will be delayed compared to the heater's power. This delay is a function of D and s. Such a structure behaves like a low-pass filter and is therefore called an electrothermal filter (ETF). Like an electrical filter, an ETF has a defined phase vs. frequency characteristic. In principle, such a structure can be implemented in any IC process.

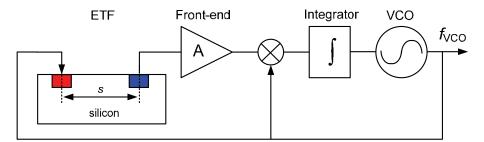

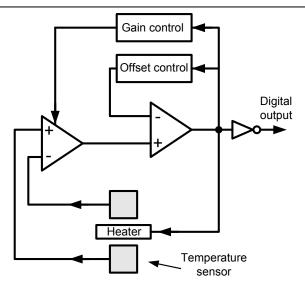

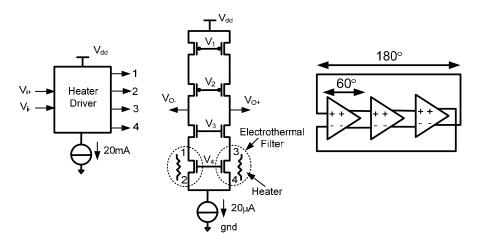

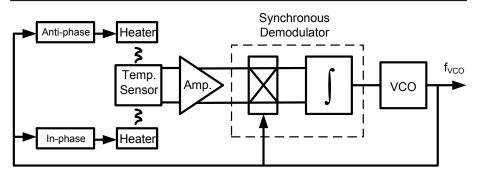

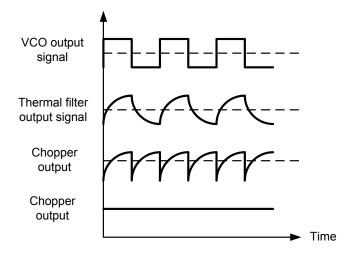

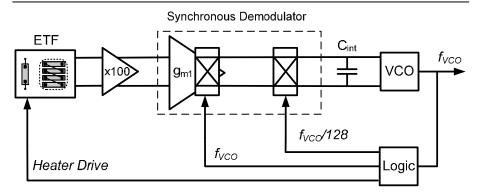

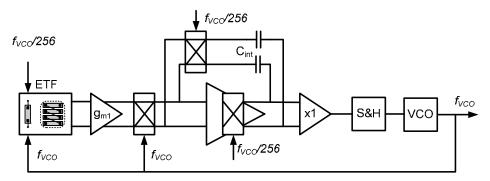

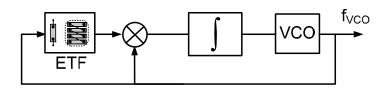

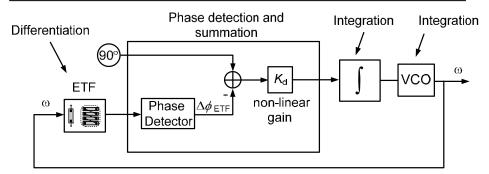

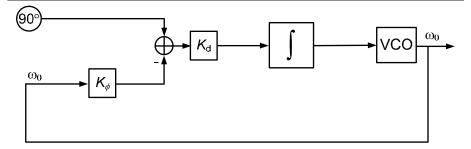

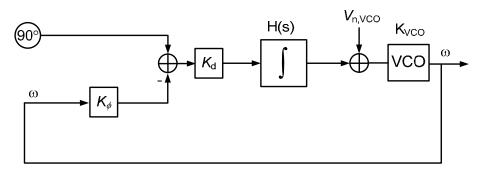

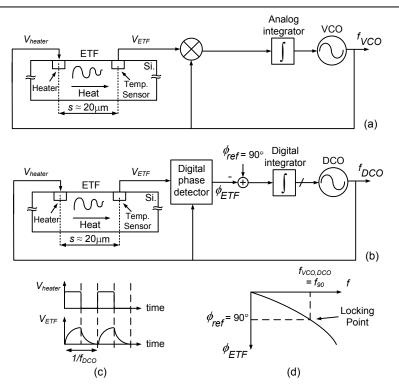

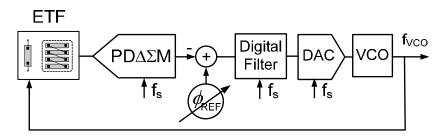

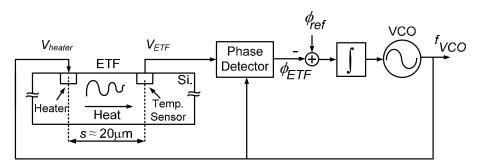

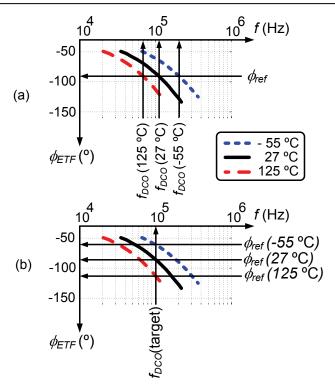

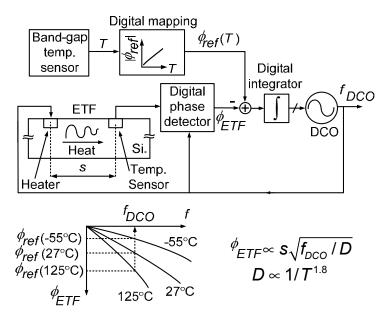

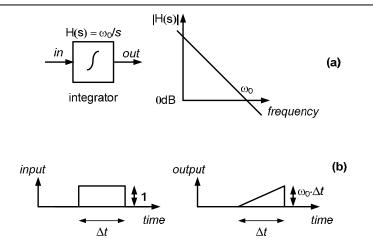

In 2006, Makinwa showed that by embedding an ETF in a frequencylocked loop (FLL), a voltage controlled oscillator (VCO) can be slaved to the thermal-diffusivity of silicon (see Figure 1.7) [1.23]. The ETF's heater is driven by the VCO output. The ETF's output signal is then demodulated by the same heater drive signal via a synchronous demodulator. The output of the demodulator is integrated and used to drive the VCO. Feedback forces the VCO to oscillate at a frequency where the output of the demodulator is zero. This corresponds to an ETF phase shift of 90 degrees. This means that ideally, the accuracy as well as the characteristics of the output frequency will be solely determined by the ETF.

Figure 1.7. *Electrothermal frequency-locked loop (FLL) with an analog integrator.*

This architecture represented a major breakthrough compared to the early thermal oscillators. This was mainly due to the use of synchronous demodulation and integration. One of the main drawbacks of the earlier thermal oscillators was their poor jitter performance. This is because silicon is a good conductor of heat and even at large heater power levels the thermopile signal is rather small. In the presence of the wideband thermal noise produced by the thermopile's resistance, the signal-to-noise ratio at the output of an ETF is quite poor. The narrow-band tracking filter employed in the electrothermal FLL of [1.23] reduces the noise bandwidth and achieves a low level of jitter. The work in [1.23] was initially aimed at developing a temperature-to-frequency converter. It demonstrated that the output frequency of an electrothermal FLL can be successfully locked to D, and thus exhibit the same temperature dependence [1.21][1.22].

In [1.23] a remarkable level of untrimmed inaccuracy, i.e. a device-todevice output frequency spread of  $\pm 0.25\%$  (3 $\sigma$ ) was reported over the industrial temperature range. This was very promising because, to first order, this is determined by the ETF's phase accuracy, which is a function of *D* and its geometry. The accuracy of the geometry is defined by the photolithography used in the CMOS process, while the value of *D* should be stable for the doping levels used for the IC-grade silicon substrates [1.23][1.24]. These results showed that perhaps the thermal-diffusivity of silicon could be a potential basis for on-chip frequency generation. However, the output frequency of the electrothermal FLL has the same temperature dependence as *D*. To build an integrated frequency reference, stability over temperature is required, and so a means of temperature compensation is necessary.

#### 1.4 Motivation

The main *practical* motivation of the work described in this thesis is to make an integrated frequency reference with no external components, which can be fabricated in standard CMOS process. As described earlier in this chapter, the elimination of quartz crystal oscillators, as the last external electrical components, has motivated a large amount of research in the past years. Many of these efforts have resulted in silicon based on-chip frequency references that either rely on the tolerance of on-chip passive elements, or require special manufacturing processes. However, only the MEMS-based and the LC-based oscillators have been commercialized.

The main *scientific* motivation of the work in this thesis is to explore the feasibility and the level of stability that can be achieved by an alternative method of on-chip frequency generation. Unlike the conventional methods, the proposed method does not rely on the accuracy of on-chip electrical

elements. Instead, the thermal-diffusivity of silicon is harnessed through standard CMOS compatible structures called electrothermal filters (ETF). The thermal diffusivity of silicon is defined by the parameter D, which is the rate at which heat diffuses through a silicon substrate. An ETF is a low-pass structure whose phase response is determined by D and by geometry. The application of ETFs in frequency-locked loops facilitates the realization of an electrical oscillator locked to D. The stability of the output frequency is then no more determined by the oscillator's own tolerances and drift, but determined by the ETF characteristics.

The work done on thermal-diffusivity-based (TD) temperature sensors has shown that ETF tolerances are in the order of 0.1% [1.23][1.25]. This is mainly determined by the purity of the silicon substrate and by the accuracy of the lithography used in the IC technology. For scaled processes, with smaller feature sizes, the lithographic accuracy improves, which implies that ETFs should benefit from Moore's law [1.27]. This agrees with the observation that the untrimmed accuracy of TD temperature sensors improves as a function of CMOS scaling [1.25][1.28]. Besides exploring the achievable levels of performance by TD frequency references, another motivation for this work is to show that such references can also benefit from process scaling.

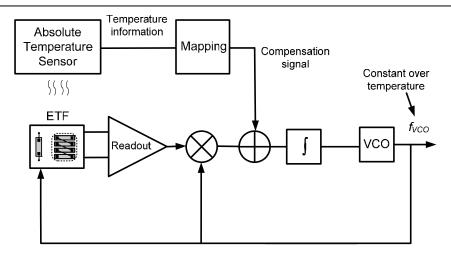

A TD frequency reference needs an accurate means of temperature compensation. This is because of the temperature dependence of D. Contrary to the multi-point temperature trims used in some silicon-based frequency references, the temperature compensation of a TD frequency reference should only require a single room-temperature trim to compensate for lithographic errors. This is crucial in reducing the extra costs associated with the test time.

The performance metrics of interest in this work are process and temperature spread and the achievable levels of output jitter. Since this method has not been explored yet, there are no specific performance targets for the, to be developed TD frequency references. From a purely scientific exploration point of view, design methodologies can be devised with the aim of discovering the limits of performance, which should then be confirmed by experimental results. This thesis thus describes a *pioneering* effort that aims to determine the possibilities and limitations of the proposed method. It represents the first steps in the evolutionary path of thermal-diffusivity based frequency references.

#### 1.5 Challenges

The design and implementation of a thermal-diffusivity-based (TD) frequency reference involves several challenges at both the system and

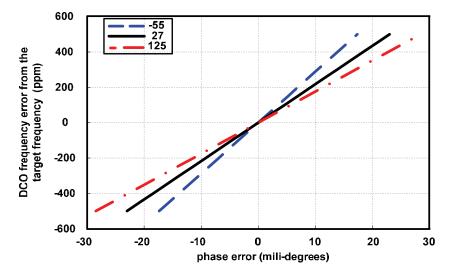

circuit levels. These mainly involve accuracy and noise related trade offs. As mentioned earlier, the expected tolerance of an electrothermal filter (ETF) is about 0.1%, which should not be altered by its interface circuitry. This means that the frequency-locked loop (FLL) in which the ETF is embedded should be able to excite it and readout its output signal accurately. The phase information contained in this signal needs to be processed with accuracies in the order of tens of milli-degrees. Precision analog circuit design techniques then need to be applied in order to suppress extra error sources such as excess electrical phase shift and residual offsets.

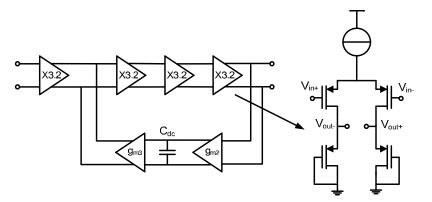

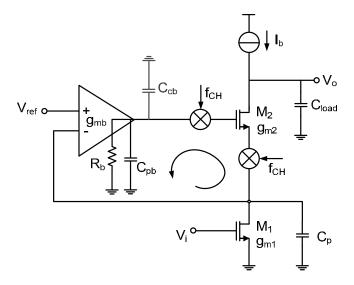

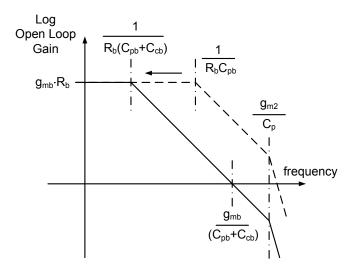

The simplified FLL shown in Figure 1.7 is based on the proposal in [1.23]. This loop involves an analog integrator that determines the loop's narrow noise-bandwidth and suppresses the ripple associated with the synchronous phase detector used to readout the ETF phase. To achieve this, an external 1µF capacitor was used in [1.23]. The elimination of this external component is a major system-level challenge. To achieve this, a new digitally-assisted FLL is proposed in this work. The narrow bandwidth is achieved through a digital loop filter whose inclusion in the loop, however, requires the addition of analog-to-digital and digital-to-analog conversions.

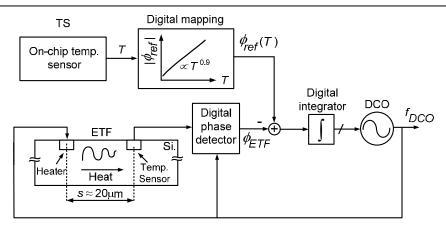

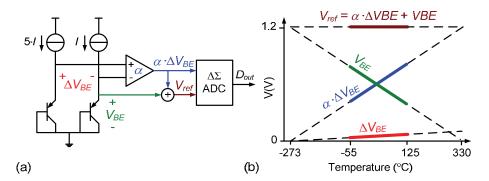

Without temperature compensation, an electrothermal FLL exhibits a temperature dependence in the order of 3000 ppm/°C (at room temperature). To guarantee 0.1% frequency accuracy, a temperature compensation scheme with a state-of-the-art inaccuracy of about 0.1°C is required. This has, so far, been achieved only by band-gap temperature sensors, which are based on the temperature dependence of bipolar transistors [1.26]. Therefore, an on-chip band-gap temperature sensor combined with a delta sigma data converter was used to measure the temperature of the die. This could then be injected into the digitally-assisted FLL through a digital mapping scheme in order to compensate the TD frequency reference.

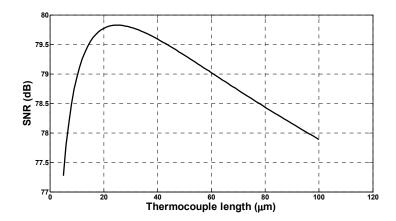

The design of a TD frequency reference involves trade-offs between accuracy, output frequency and jitter performance. An ETF's geometry determines its thermal delay. The smaller the geometry, the smaller the delay and hence the higher the output frequency of the reference can be. On the other hand, the accuracy of an ETF's phase shift determines the accuracy of the output frequency. Since this is, to first order, determined by lithographic error, reducing the geometry increases its effect. This means that the ETF's dimensions have to be increased in order to improve its intrinsic accuracy. However, silicon is a good conductor of heat, and so increasing these dimensions reduces its output signal. The lower the signal, the more will be the effect of the ETF's wideband thermal noise on the FLL's jitter. Therefore, there are trade-offs among the accuracy, output frequency and jitter of a TD frequency reference.

#### 1.6 Thesis Organization

This thesis describes an alternative method of on-chip frequency generation based on the thermal diffusivity of silicon. Apart from this introductory chapter, the second chapter provides a literature study on stateof-the-art silicon-based frequency references. For each approach, a brief introduction to the history, principles of operation, state-of-the-art realizations, performance measures, and the associated possibilities and limitations will be provided. The study covers silicon MEMS resonator based oscillators, as well as LC, RC, relaxation, ring, and electron-mobilitybased frequency references.

Chapter 3 provides an overview of the concept of on-chip frequency generation based on the thermal properties of silicon. The thermal-diffusivity of silicon, *D*, will be introduced. It will be shown how an electrothermal filter (ETF) can harness this physical property. ETFs in standard CMOS and their design parameters will be described. An overview of the earlier thermal oscillators and their limitations will be provided. Furthermore, an electrothermal frequency-locked loop (FLL) will be introduced as a system level solution to the drawbacks of early thermal oscillators. It will be shown why an FLL is a suitable foundation for building a thermal-diffusivity-based (TD) frequency reference. The dynamics of the FLL as well as the effect of the ETF thermal noise on its output jitter will be analyzed. Also, the earlier generations of CMOS FLLs and the challenges associated with their integration will be reviewed. This motivates the need for the realization of an alternative FLL.

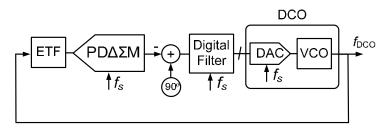

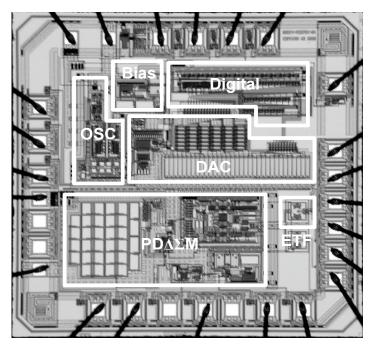

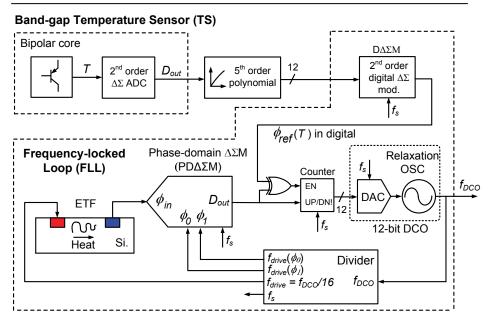

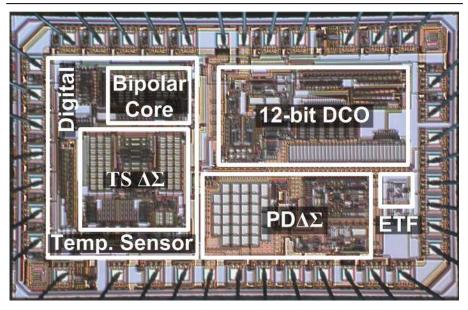

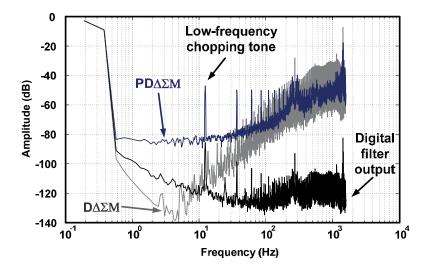

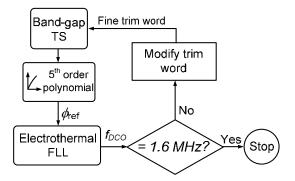

Chapter 4 describes a new architecture for electrothermal FLLs, which is more suitable for CMOS integration. The proposed digitally-assisted FLL (DAFLL) achieves the required narrow noise bandwidth by means of a digital loop filter. The proposed system-level architecture of the loop will be introduced. Furthermore, the design, implementation and characterization of the DAFLL will be covered. This includes a phase digitizer in the form of a phase-domain  $\Delta\Sigma$  modulator (PD $\Delta\Sigma$ M) and a digitally-controlled oscillator (DCO). The design and characterization of these blocks will be described in the framework of two test chips.

Chapter 5 describes the complete implementation of the first TD frequency reference in a 0.7 $\mu$ m standard CMOS process. This includes the addition of temperature compensation to the DAFLL described earlier with the help of an on-chip band-gap temperature sensor. As a result, the reference produces an output frequency of 1.6MHz and is stable to  $\pm 0.1\%$  over the military temperature range (-55°C to 125°C). The system-level considerations of the temperature compensation scheme are presented. Then

the system and circuit level design of the band-gap temperature sensor will be described in detail. Finally, the characterization results on a test chip including the complete TD frequency reference will be provided.

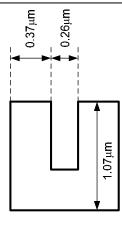

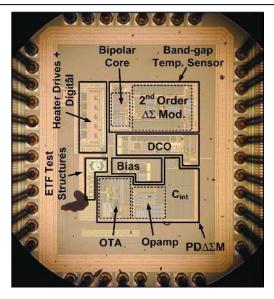

Chapter 6 describes the design and implementation of a scaled TD frequency reference in a 0.16 $\mu$ m standard CMOS process. The aim of this implementation is to demonstrate the feasibility of TD frequency references in modern CMOS process, as well as to demonstrate that such references can benefit from technology scaling. For a given accuracy, the improvements achieved by scaling include less jitter, greater output frequency, and less power consumption and chip area. The scaling strategy starting from the ETF and extending to the analog circuit design will be described. The system and circuit design as well as the experimental results on a test chip implemented in a 0.16 $\mu$ m CMOS process will be provided. The scaled reference dissipates 2.1mW from a 1.8V supply (3.7x reduction compared to the previous generation), generates a 16MHz output frequency (10x higher), and is stable to  $\pm 0.1\%$  over the military temperature range. Its 45ps rms period jitter is 7x lower and its area is 12x smaller than the previous implementation.

In chapter 7, the main conclusions of the thesis are summarized. Furthermore, possible future work on TD frequency references will be described.

#### 1.7 References

- [1.1] D. Allan et al.,"The Science of Timekeeping," *HP Application Note 1289*, 1997.

- [1.2] The Wikipedia page on frequency to be found on-line at: http://en.wikipedia.org/wiki/Frequency

- [1.3] J. Jespersen and J. Fitz-Randolph, From Sundials to Atomic Clocks: Understanding Time and Frequency, National Institute of Standards and Technology, 1999.

- [1.4] *IEEE Standard definitions of physical quantities for fundamental frequency and time metrology random instabilities*, IEEE std. 1139-1999, 1999.

- [1.5] *Clock Jitter and Phase Noise Conversion*, Application Note 3359, by Maxim, available online at: www.maxim-ic.com.

- [1.6] *Overview on Phase Noise and Jitter*, Agilent Technologies, available online at: www.agilent.com.

- [1.7] A. Hajimiri, S. Limotyrakis and T. H. Lee, "Jitter and Phase Noise in Ring Oscillators", *IEEE Journal of Solid-State Circuits*, vol. 34, pp. 790– 804, June 1999.

- [1.8] Agilent Signal Generator Spectral Purity, Application Note 388, available online at: www.agilent.com.

- [1.9] V.E. Bottom, "A History of the Quartz Crystal Industry in the USA," *IEEE Annual Frequency Control Symposium*, pp. 3–12, 1981.

- [1.10] C.S. Lam,"A review of the recent development of MEMS and crystal oscillators and their impacts on the frequency control products industry", *IEEE Ultrasonic Symposium*, pp. 694–704, 2008.

- [1.11] Wan-Thai Hsu, et al. "The New Heart Beat of Electronics Silicon MEMS Oscillators," *IEEE Electronic Components and Technology Conference*, ECTC, pp. 1895–1899, 2007.

- [1.12] SiTime's product selector sheet, available online at: http://www.sitime.com/support/product-selector

- [1.13] M.S. McCorquodale et al. "A Silicon Die as a Frequency Source," IEEE International Frequency Control Symposium, pp. 103–108, 2010.

- [1.14] V. De Smedt et al., "A 66 µW 86 ppm/°C Fully-Integrated 6 MHz Wienbridge Oscillator With a 172 dB Phase Noise FOM," *IEEE Journal* of Solid-State Circuits, vol. 44, no. 7, pp. 1990–2001, July 2009.

- [1.15] P.R. Gray and D.J. Hamilton, "Analysis of Electrothermal Integrated Circuits," *IEEE Journal of Solid-State Circuits*, vol. sc-6, no.1, pp. 8–14, February 1971.

- [1.16] M.F. Freidman and D.J. Hamilton, "An Integrated High-Q Bandpass Filter," IEEE International Solid-State Circuits Conference, pp. 162–163, February 1970.

- [1.17] G. Bosch, "A Thermal Oscillator Using the Thermo-electric (Seebeck) Effect in Silicon," *Elsevier's Solid-State Electronics*, vol. 15, pp. 849– 852, 1972.

- [1.18] Wikipedia page on the thermoelectric effect, available online at: http://en.wikipedia.org/wiki/Thermoelectric\_effect

- [1.19] V. Szekely et al, "A new monolithic temperature sensor: the thermal feedback oscillator," *in Proc. of Transducers*, pp.124–127, June 1995.

- [1.20] Wikipedia page on phonons, available online at: http://en.wikipedia.org/wiki/Phonon.

- [1.21] J. Ebrahimi, "Thermal diffusivity measurement of small silicon chips," *Journal of Physics D: Appl. Vol.*3, pp.236–239, 1970.

- [1.22] Y. S. Touloukian et al., Thermophysical Properties of Matter: Vol.10. New York: Plenum, 1998.

- [1.23] K. A. A. Makinwa and M. F. Snoeij, "A CMOS Temperature-to-Frequency Converter With an Inaccuracy of Less Than ±0.5°C (3σ) from -40°C to 105°C," *IEEE Journal of Solid-State Circuits*, vol. 41, no.12, pp. 2992–2997, Dec. 2006.

- [1.24] Y. S. Touloukian et al., Thermophysical Properties of Matter: Vol.10. New York: Plenum, 1998.

- "A Thermal-Diffusivity-Based van Vroonhoven et al., [1.25] C.P.L. Temperature Sensor with an Untrimmed Inaccuracy of  $\pm 0.2^{\circ}$ C (3 $\sigma$ ) from -55°C to 125°C," IEEE ISSCC Dig. Tech. Papers, 2010, pp. 314-315.

- [1.26] M.A.P. Pertijs and J.H. Huijsing, Precision Temperature Sensors in CMOS Technology, Springer, 2006.

- [1.27] Wikipedia page Moore's law. available online on at: http://en.wikipedia.org/wiki/Moore's law.

- [1.28] C.P.L. van Vroonhoven et al., "A CMOS Temperature to Digital Converter with an Inaccuracy of  $\pm 0.5^{\circ}$ C (3 $\sigma$ ) from -55 to  $125^{\circ}$ C," *IEEE* ISSCC Dig. Tech. Papers, 2008, pp. 576-577.

# 2 Silicon-Based Frequency References

This chapter provides an overview of silicon-based frequency references. Reduction of size and cost as well as increased reliability have been the main motivations for the realization of on-chip frequency references. However, the main limitation of such references is the effect of process, voltage, and temperature variations (PVT) on their output frequency. This chapter reviews various state-of-the-art implementations of silicon-based frequency references described in the open literature or available as products on the market. Its aim is to provide an overview of the pros and cons of the chosen approaches in order to build a comparison chart. Such an overview should help the reader to compare the approach described in this thesis, the realization of thermal-diffusivity-based (TD) frequency references, with the other available solutions.

#### 2.1 Introduction

The stability of a frequency reference is a measure of the amount of variation in its output frequency as a function of environmental parameters. These include temperature, supply voltage, process tolerances, noise, etc. It should be noted that the terms stability and accuracy will be used interchangeably throughout this thesis. This is because they both refer to the same concept as far as the level of variations in the nominal oscillation

frequency of an oscillator is concerned. If this nominal value is equal to  $f_0$ , then its level of stability (accuracy) is measured either in parts per million (ppm) or in percent [2.1]-[2.4]. If the absolute value of the deviation in the output frequency is  $\Delta f$ , then the error can be calculated as:

$$f_{error}(\%) = \frac{\Delta f}{f_0} \cdot 10^2$$

or  $f_{error}(ppm) = \frac{\Delta f}{f_0} \cdot 10^6$ . (2.1)

Various electronic systems require different levels of accuracy for their frequency reference. For instance, in some microcontroller application references stable from 0.01% (100ppm) to 1% (10000ppm) [2.5] might be required, while a wire-line data link such as USB 2.0 needs 500ppm of clock accuracy [2.6]. Wireless communication channels require tighter accuracies. For instance a cell-phone handset application might need frequencies stable to 2.5ppm [2.7], while a GPS receiver or a mobile base-station system might require sub-ppm accuracies [2.3][2.7].

For decades, crystal oscillators have been the only means of producing stable frequencies. Considering their low temperature dependency, relatively low cost and small form factor, as well as their wide commercial availability, they have a dominant share of the frequency control market (more than 90%, equivalent to more than 4.5 billion dollars) [2.3]. Quartz crystal oscillators are available with various levels of accuracy. The non-compensated (XO) and voltage compensated (VCXO) oscillators achieve stabilities in the range of 20 to 100ppm. When they are temperature compensated (TCXO), their accuracy is in the 0.1 to 5ppm range. Oven controlled (OCXO) oscillators achieve very high stabilities: in the order of 1ppb (part per billion) [2.3].

Apart from their high levels of accuracy, quartz crystal oscillators also have some drawbacks. The first of them is the space they occupy on printed circuit boards, especially when a number of frequency sources are required within one system. Another important disadvantage is their sensitivity to mechanical shock and vibration. This mainly affects the quartz crystal, which is in fact an electro-mechanical part [2.3]. Compared to electronic circuits, whose functionality is due to the movement of electrons, the crystal vibrates at the frequency of oscillation. This means that any physical motion of the crystal will change its frequency [2.3].

The abovementioned limitations have driven the search for integrated frequency references that can achieve the same level of stability as quartz crystal oscillators. Such references will be manufactured in silicon, which is why they are also referred to as silicon-based frequency references [2.8].

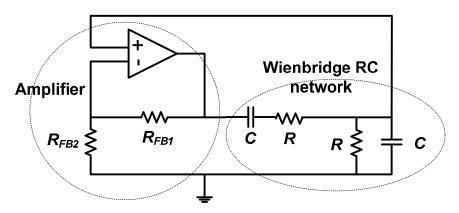

As early as 1967, the first steps towards frequency generation by means of MEMS (micro-machined silicon) structures were taken [2.9]. Around

1968, the concept of a self-referenced silicon frequency reference was illustrated with a temperature-compensated Wien-bridge RC oscillator. Later, various types of electrical oscillators such as RC, relaxation, ring, and LC oscillators have been proposed. Among these methods, MEMS-based and LC-based oscillators have been commercialized and currently achieve performance levels that can compete with crystal oscillators. In this chapter, an overview of these methods of silicon-based frequency generation will be described. State-of-the-art references will be studied in regard to their system-level architecture, their achieved level of accuracy, as well as an overview of their potential applications.

Since this thesis is about CMOS compatible frequency references, crystal oscillators will not be further discussed. Furthermore, MEMS-based oscillators, which are not truly standard CMOS compatible, will only be briefly introduced in the next section. The chapter progresses with a more detailed overview of CMOS-based LC, RC, relaxation, and ring oscillators. Furthermore, a new class of ultra-low-power frequency references based on the electron mobility of MOS transistors will be introduced. Finally, a comparison between these methods will be provided allowing for categorization of the various methods regarding crucial performance aspects such as frequency stability and power consumption.

#### 2.2 Silicon MEMS Based Oscillators

Quartz crystal resonators are excited at their resonance frequency by an electrical oscillator circuit. Their operation depends on the piezoelectric properties of a material that can not be integrated in IC technology: quartz. Over the years, a lot of research has been done on the development of silicon MEMS (Micro Electro Mechanical Systems) based resonators with the aim of replacing quartz crystals. MEMS technology involves many of the processes used by the integrated circuit technology such as lithography, deposition, etching, etc [2.10]. This technology has been applied in sensors such as accelerometers, gyroscopes, microphones, etc.

MEMS resonators are micro-machined structures that can vibrate at their resonance frequency if an external excitation is applied to them. The resonance property of such structures was first researched in 1967, when a resonant gate transistor was presented as a micro-machined integrated frequency reference [2.11]. This excitation can be of the electrostatic, piezoelectric or electromagnetic type [2.12][2.13]. The *Quality* factor of a resonator determines the stability of the frequency reference that is built around it. It is the ratio of its peak resonance frequency to the width of the peak. A MEMS resonator's shape and geometry determines this factor, which is typically between 50,000 to 300,000, a range that is comparable to quartz crystal oscillators [2.12][2.13].

MEMS resonators have faced many challenges in delivering a cost effective and reliable solution that could compete commercially with quartz crystals. The major challenges included packaging, vibration and shock sensitivity, temperature drift and long term stability [2.14]. In recent years various commercial products have been introduced by two start-up companies: Discera and SiTime. Discera was established in 2001 based on research on MEMS resonators funded by DARPA, while SiTime started in 2004 based on IP licensed through Bosch [2.3]. Today, MEMS-based frequency references produced by these companies are more compact than their quartz competitors and are more cost effective due to the mass production allowed by the use of IC technology. However, their level of jitter (phase noise) is not (yet) low enough for cell-phone applications.

Because of the special processing required by MEMS technology, a MEMS resonator has to be manufactured on a separate die from the die that holds the electronic circuitry exciting and controlling it [2.12][2.13][2.14]. Furthermore, the mass of a MEMS resonator is small, being on the order of  $10^{-14}$  kg to  $10^{-11}$  kg, which means that its resonance frequency and quality factor will be affected by any gas molecules surrounding it [2.15]. This means that silicon MEMS resonators should preferably be operated in vacuum, which is the reason why they have been fabricated within silicon cavities [2.12][2.13][2.14].

Figure 2.1. Simplified block diagram of a silicon MEMS based oscillator.

Another challenge in making MEMS-based oscillators is the temperature dependence of MEMS resonators. This is due to the temperature coefficient of the Young's modulus of silicon [2.3][2.12][2.13]. This is in the order of 20 to 40ppm/°C, which is larger than that of quartz and necessitates a means for the temperature compensation of such oscillators. There have been various structural techniques proposed to reduce or correct for the MEMS resonator's temperature coefficient. These include the combination of materials with positive and negative thermal stiffness coefficients or the application of an electric field to control the resonator's stiffness [2.16]. The approach that has been ultimately used in commercial products is to correct the temperature dependence of the oscillator through a fractional frequency synthesizer and a temperature sensor [2.17]. This technique will be described later.

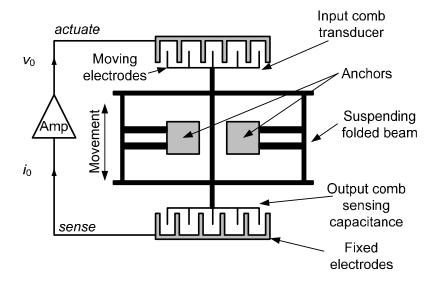

An encapsulated silicon MEMS resonator needs to be attached to an anchor on a substrate [2.14]. Figure 2.1, shows a conceptual and simplified drawing of a MEMS resonator [2.18]. Folded suspending beams are anchored to the silicon substrate at two anchor points. The suspending beams are connected to the sides of comb transducer structures. The resonator structure is biased with a DC bias source. The output transducer experiences a change in capacitance due to the movement of the suspending beam with reference to the fixed electrodes. This causes an electrical signal,  $i_0$ , which is fed to an electronic circuit that produces an excitation signal  $v_0$ , which is then applied to the input transducer. This signal will electro-statically actuate the resonator. The structure vibrates at its resonance frequency (typically in the hundreds of kHz to MHz range), which is the same frequency at which it is excited electrically. The required electrical signal is in fact the output signal of the oscillator.

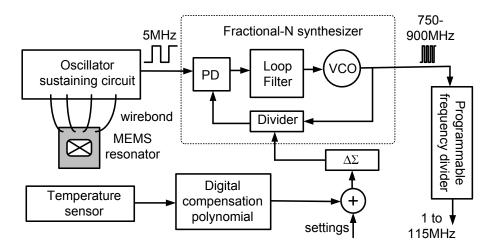

The MEMS frequency references produced by SiTime consist of a resonator element, which is wire bonded to a CMOS die that includes a sustaining circuitry, a high-resolution fractional-N frequency synthesizer [2.19], a temperature sensor and digital circuitry [2.12][2.13][2.14][2.17]. A simplified block diagram of this system [2.17] is shown in Figure 2.2. The MEMS resonator vibrates at 5MHz, which is the same frequency as that of the sustaining circuitry. This 5MHz signal is provided to the fractional-N synthesizer, which outputs a higher frequency: in the range of 750MHz to 900MHz [2.17]. This frequency can be adjusted with sub-ppm resolution over a 10% tuning range. A programmable output frequency can then be produced by dividing the output of the synthesizer. The advantage of this approach is that the same MEMS resonator can be used to provide different output frequencies. This means that the output frequency can be easily programmed into the device depending on the application.

The temperature dependence of the MEMS resonator is compensated by measuring the temperature of the CMOS die with an embedded temperature sensor. The temperature information is digitally processed through a compensation polynomial whose coefficients are stored in a non-volatile memory. The frequency reference achieves a part to part frequency stability of about 10ppm from -40°C to 85°C [2.17]. In this approach, the jitter performance of the output frequency is determined by the frequency synthesizer (that is in principle a PLL). For better jitter performance, low noise and high quality factor oscillators such as LC based resonance circuits have been combined with optimized PLLs as well as power supply regulation techniques [2.13][2.17].

One of the concerns regarding MEMS oscillators has been about their reliability in comparison to the mature quartz crystal rival. Since a MEMS resonator is a mechanical device that vibrates at millions of cycles per second, aging is one of these reliability concerns. Reliability tests published by Discera, show sub-ppm shifts in the first year of operation of such devices [2.20]. Furthermore, due to their very small dimensions (micro-meter range) and very small weight, MEMS resonators have better shock resistance than quartz crystals [2.20]. Further reliability tests such as vibration resistance, sensitivity to packaging vacuum, thermal cycling and high temperature storage life have been reported in [2.20], showing that MEMS frequency references can compete with crystal oscillators.

Figure 2.2. Simplified block-diagram of a silicon MEMS oscillator, including a MEMS resonator, a fractional-N synthesizer and a temperature compensation scheme.

Most commercial MEMS frequency references are manufactured by SiTime [2.21] and Discera [2.22]. SiTime's high performance oscillators include the SiT8208, SiT8102 and SiT9102 in standard six-pin packages ( $5.0x3.2 \text{ mm}^2$ ), which are smaller than those currently used for quartz crystals [2.13]. SiTime also introduced very thin SiT8003 oscillators with 0.25mm thick packages, mainly intended for SIM card, camera, and cell phone applications. SiTime's range of products cover output frequency stabilities from sub-ppm to 50ppm over the commercial and industrial temperature range (-40°C to  $85^{\circ}$ C). The high performance SiT8208 and SiT8209 products have sub-ps output jitter [2.23].

Discera's MEMS frequency references use the same technique of combining a MEMS resonator with a PLL [2.22]. Their range of stability is about 50ppm, at supply voltages of 1.8V to 3.3V, output frequencies of 1MHz to 150MHz and supply currents in the order of 3mA. They are available in standard packages that can be placed in crystal oscillator footprints. Their intended applications are in: mobile applications, consumer electronics, portable electronics, CCD clocks for cameras, etc.

So far, the commercially introduced MEMS frequency references show that sub-ppm frequency stabilities and programmable output frequencies are feasible. Furthermore, their small footprints make it possible to replace standard crystals with MEMS-based devices. However, they still have a few drawbacks. Their jitter performance is determined by their fractional-N synthesizer and by the temperature compensation scheme. Also, the special processing required for the MEMS resonator makes single die integration of these devices difficult. This means that the integration of such frequency references as an IP block in a system-on-chip will usually result in a twochip solution.

#### 2.3 LC Oscillators

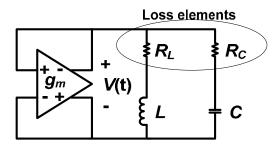

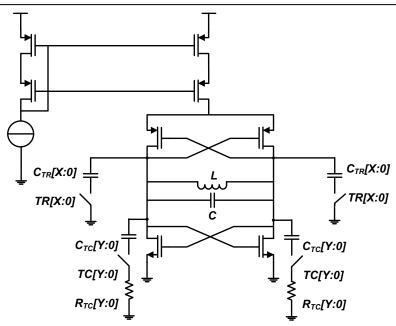

Another class of commercially available frequency references are the LC oscillators [2.24]. Such oscillators operate at the resonance frequency of an LC tank [2.25] and have been widely used in VCO's that produce RF range of frequencies [2.26]. These VCO's have been normally embedded into phase-locked loops (PLLs), with the aim of frequency synthesis from an external reference source. In order to function as a self-referenced frequency source, an LC oscillator needs to be free-running. In this case, special attention needs to be paid to its output frequency stability as a function of process, temperature and voltage variations. An LC oscillator is based on passive elements such as inductors and capacitors as well as active elements, i.e. transistors. Therefore, such an oscillator can be made in a standard CMOS process.

Figure 2.3. Simplified block diagram of an LC oscillator including the LC elements as well as their equivalent losses.

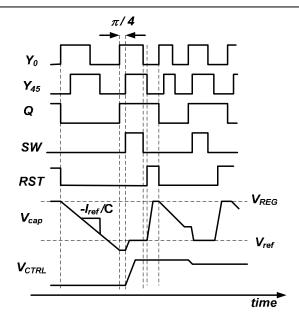

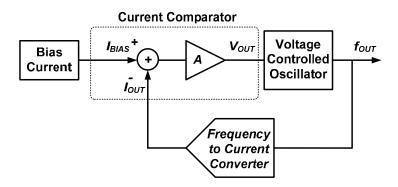

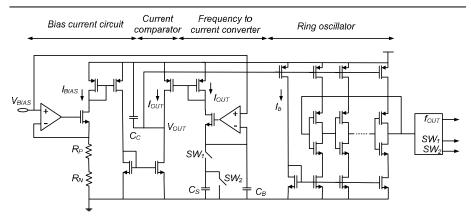

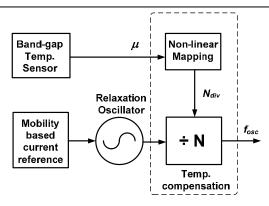

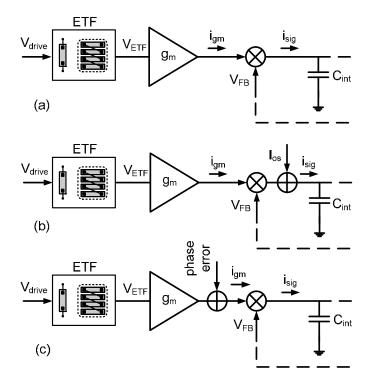

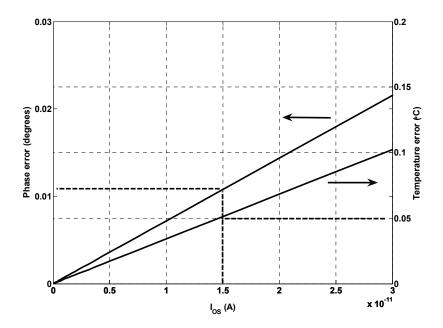

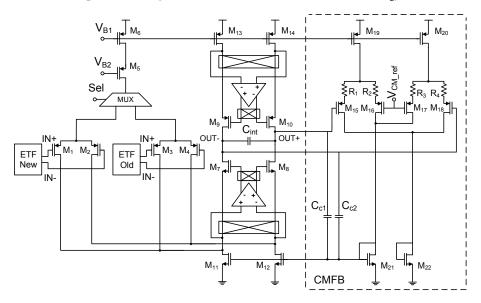

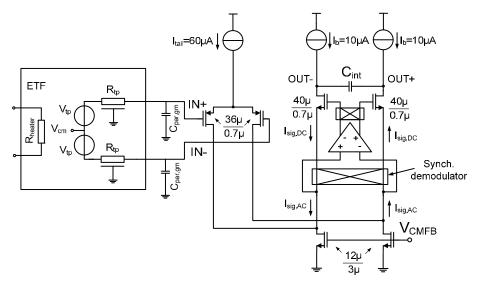

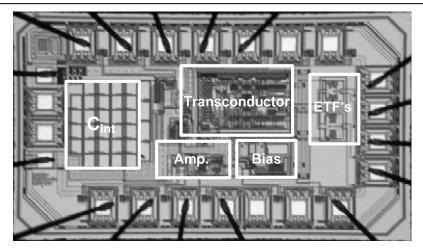

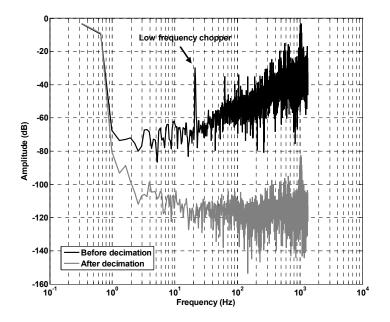

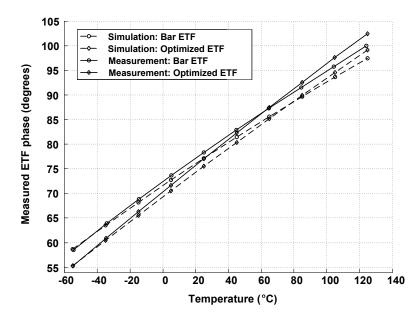

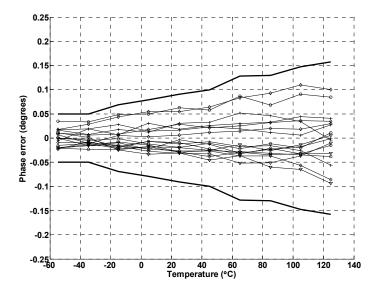

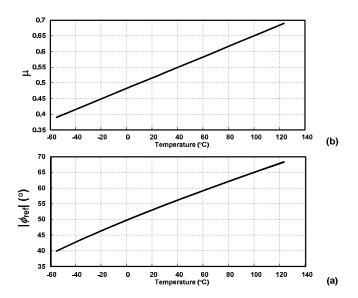

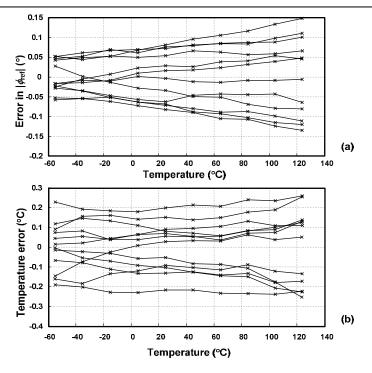

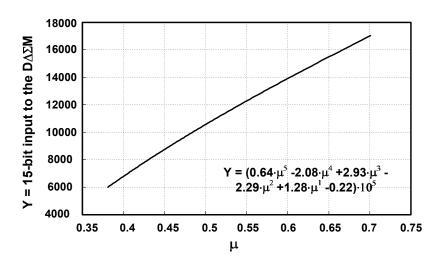

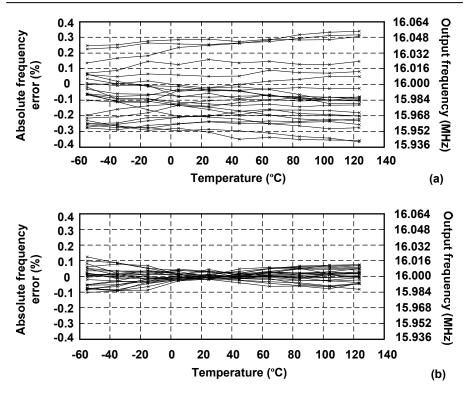

The first steps towards commercializing self-referenced LC oscillators were taken at Mobius Microsystems, a fab-less company founded in 2004 with the aim of developing all-silicon frequency sources that replace quartz crystal oscillators. The goal of Mobius Microsystems was to produce a monolithic free running RF LC oscillator that did not require the frequency synthesizers used in MEMS frequency references. This was to avoid the effect of multiplication on the output frequency jitter. These efforts resulted in oscillators with output frequency ranges from 12MHz to 25MHz and with initial target applications such as wire-line data communication, e.g. USB [2.27]-[2.32]. These solutions achieved output frequency stabilities in the order of 100ppm with period jitters in the order of 3 to 6ps (rms). In 2010, Mobius Microsystems was acquired by IDT, who has subsequently introduced LC oscillator based frequency reference to the market [2.24].