## University of Pennsylvania ScholarlyCommons

Technical Reports (CIS)

Department of Computer & Information Science

September 1987

## Three Highly Parallel Computer Architectures and Their Suitability for Three Representative Artificial Intelligence Problems

Ron Katriel *University of Pennsylvania*

Follow this and additional works at: https://repository.upenn.edu/cis\_reports

#### **Recommended Citation**

Ron Katriel, "Three Highly Parallel Computer Architectures and Their Suitability for Three Representative Artificial Intelligence Problems", . September 1987.

University of Pennsylvania Department of Computer and Information Science Technical Report No. MS-CIS-88-08.

This paper is posted at ScholarlyCommons. https://repository.upenn.edu/cis\_reports/628 For more information, please contact repository@pobox.upenn.edu.

### Three Highly Parallel Computer Architectures and Their Suitability for Three Representative Artificial Intelligence Problems

#### **Abstract**

Virtually all current Artificial Intelligence (AI) applications are designed to run on sequential (von Neumann) computer architectures. As a result, current systems do not scale up. As knowledge is added to these systems, a point is reached where their performance quickly degrades. The performance of a von Neumann machine is limited by the bandwidth between memory and processor (the *von Neumann bottleneck*). The bottleneck is avoided by distributing the processing power across the memory of the computer. In this scheme the memory becomes the processor (a "smart memory").

This paper highlights the relationship between three representative AI application domains, namely knowledge representation, rule-based expert systems, and vision, and their parallel hardware realizations. Three machines, covering a wide range of fundamental properties of parallel processors, namely module granularity, concurrency control, and communication geometry, are reviewed: the Connection Machine (a fine-grained SIMD hypercube), DADO (a medium-grained MIMD/SIMD/MSIMD tree-machine), and the Butterfly (a coarse-grained MIMD Butterflyswitch machine).

#### Comments

University of Pennsylvania Department of Computer and Information Science Technical Report No. MS-CIS-88-08.

# THREE HIGHLY PARALLEL COMPUTER ARCHITECTURES AND THEIR SUITABILITY FOR THREE REPRESENTATIVE ARTIFICIAL INTELLIGENCE PROBLEMS

**Ron Katriel**

MS-CIS-88-08 LINC LAB 97

Department of Computer and Information Science School of Engineering and Applied Science University of Pennsylvania Philadelphia, PA 19104

February 1988

**Acknowledgements:** This research was supported in part by DARPA grants NOOO14-85-K-0018, NSF-CER grant MCS-8219196 and U.S. Army grants DAA29-84-K-0061, DAA29-84-9-0027.

# Three Highly Parallel Computer Architectures and Their Suitability for

#### Three Representative Artificial Intelligence Problems

Ron Katriel

Computer and Information Science Department

University of Pennsylvania

Philadelphia, PA 19104-6389

katriel@cis.upenn.edu

September 29, 1987

#### Abstract

Virtually all current Artificial Intelligence (AI) applications are designed to run on sequential (von Neumann) computer architectures. As a result, current systems do not scale up. As knowledge is added to these systems, a point is reached where their performance quickly degrades. The performance of a von Neumann machine is limited by the bandwidth between memory and processor (the von Neumann bottleneck). The bottleneck is avoided by distributing the processing power across the memory of the computer. In this scheme the memory becomes the processor (a "smart memory").

This paper highlights the relationship between three representative AI application domains, namely knowledge representation, rule-based expert systems, and vision, and their parallel hardware realizations. Three machines, covering a wide range of fundamental properties of parallel processors, namely module granularity, concurrency control, and communication geometry, are reviewed: the Connection Machine (a fine-grained SIMD hypercube), DADO (a medium-grained MIMD/SIMD/MSIMD tree-machine), and the Butterfly (a coarse-grained MIMD Butterfly-switch machine).

#### Contents

| 1 | Introduction                    |                                                         |    |  |  |

|---|---------------------------------|---------------------------------------------------------|----|--|--|

|   | 1.1                             | The Need for Parallelism in AI                          | 5  |  |  |

|   | 1.2                             | Parallelism and NP-completeness                         | 5  |  |  |

|   | 1.3                             | Three Representative AI Domains                         | 6  |  |  |

|   |                                 | 1.3.1 Why These Domains?                                | 6  |  |  |

|   | 1.4                             | Three Representative Highly Parallel Computers          | 7  |  |  |

|   |                                 | 1.4.1 Why These Machines?                               | 7  |  |  |

|   | 1.5                             | Outline of the Paper                                    | 8  |  |  |

| 2 | Intr                            | roduction to Parallelism                                | 9  |  |  |

|   | 2.1                             | Theoretical Limitations of Parallel Computation         | 9  |  |  |

|   | 2.2                             | A Taxonomy of Parallel Processing                       | 10 |  |  |

|   | 2.3                             | Practical Architectures: Narrowing the Space            | 10 |  |  |

|   | 2.4                             | SIMD (Array) Machines                                   | 11 |  |  |

|   |                                 | 2.4.1 Organization of an Array Computer                 | 11 |  |  |

|   |                                 | 2.4.2 Interprocessor Communications in Array Processors | 13 |  |  |

|   |                                 | 2.4.3 SIMD Programming                                  | 15 |  |  |

|   | 2.5                             | MIMD Machines (Multiprocessors)                         | 15 |  |  |

|   |                                 | 2.5.1 Memory Organization in Multiprocessors            | 16 |  |  |

|   |                                 | 2.5.2 Synchronization, Scheduling, and Resource Sharing | 18 |  |  |

|   |                                 | 2.5.3 MIMD Programming                                  | 18 |  |  |

| 3 | Overview of the Chosen Machines |                                                         |    |  |  |

|   | 3.1                             | The Connection Machine                                  | 19 |  |  |

|   |                                 | 3.1.1 Introduction                                      | 19 |  |  |

|   |                                 | 3.1.2 The Connection Machine Design                     | 19 |  |  |

|   |                                 | 3.1.3 Programming the Connection Machine                | 21 |  |  |

|   | 3.2                             | DADO                                                    | 21 |  |  |

|   |                                 | 3.2.1 Introduction                                      | 21 |  |  |

|   |                                 | 3.2.2 DADO's Design Philosophy                          | 22 |  |  |

|   |                                 | 3.2.3 Programming DADO                                  | 23 |  |  |

|   | 3.3                             | The Butterfly                                           | 24 |  |  |

|   |                                 | 3.3.1 Introduction                                      | 24 |  |  |

|   |                                 | 3.3.2 Butterfly Architecture                            | 25 |  |  |

|   |                                 | 3.3.3 Programming the Butterfly Parallel Processor      | 25 |  |  |

| 4   | Parallelism in the Selected Domains |         |                                                      | <b>27</b> |

|-----|-------------------------------------|---------|------------------------------------------------------|-----------|

|     | 4.1                                 | Massiv  | ve Parallelism in Semantic Networks                  | 27        |

|     |                                     | 4.1.1   | Introduction                                         | 27        |

|     |                                     | 4.1.2   | A Taxonomy of Massively Parallel Architectures       | 29        |

|     |                                     | 4.1.3   | Shastri's Massively Parallel Representation Language | 30        |

|     | 4.2                                 | Paralle | elism in Rule-Based Expert Systems                   | 30        |

|     |                                     | 4.2.1   | Introduction                                         | 30        |

|     |                                     | 4.2.2   | Production Systems                                   | 31        |

|     |                                     | 4.2.3   | Memory-Based Reasoning                               | 34        |

|     | 4.3                                 | Parall  | elism in Vision                                      | 35        |

|     |                                     | 4.3.1   | Introduction                                         | 35        |

|     |                                     | 4.3.2   | Intermediate-Level Vision                            | 36        |

| 5   | Per                                 | formai  | nce of the Chosen Machines                           | 38        |

|     | 5.1                                 | Perfor  | mance of the Connection Machine                      | 38        |

|     |                                     | 5.1.1   | Semantic Networks                                    | 38        |

|     |                                     | 5.1.2   | Rule-Based Expert Systems                            | 39        |

|     |                                     | 5.1.3   | Intermediate-Level Vision                            | 40        |

|     |                                     | 5.1.4   | Comments on the Connection Machine                   | 40        |

|     | 5.2                                 | Perfor  | mance of the DADO Machine                            | 41        |

|     |                                     | 5.2.1   | Production Systems                                   | 41        |

|     |                                     | 5.2.2   | Intermediate-Level Vision                            | 43        |

|     |                                     | 5.2.3   | Semantic Networks                                    | 43        |

|     |                                     | 5.2.4   | Comments on DADO                                     | 44        |

|     | 5.3                                 | Perfor  | mance of the Butterfly Machine                       | 44        |

|     |                                     | 5.3.1   | Intermediate-Level Vision                            | 44        |

|     |                                     | 5.3.2   | Semantic Networks                                    | 45        |

|     |                                     | 5.3.3   | Rule Based Expert Systems                            | 46        |

|     |                                     | 5.3.4   | Comments on the Butterfly                            | 47        |

|     | 5.4                                 | Comp    | are-and-Contrast                                     | 48        |

| 6   | Arc                                 | hitect  | ures for the Selected Domains                        | 49        |

|     | 6.1                                 | Know    | ledge Representation: Semantic Networks              | 49        |

|     |                                     | 6.1.1   | Fundamental Computations                             | 49        |

|     |                                     | 6.1.2   | Architectural Issues                                 | 50        |

|     |                                     | 6.1.3   | Special Requirements                                 | 51        |

| 6.2 |                                     | Exper   | t Systems: Production Systems                        | 52        |

|    |     | 6.2.1 Fundamental Computations                                                              | 52 |

|----|-----|---------------------------------------------------------------------------------------------|----|

|    |     | 6.2.2 Architectural Issues                                                                  | 52 |

|    |     | 6.2.3 Special Requirements                                                                  | 53 |

|    | 6.3 | Vision (especially Intermediate-level)                                                      | 54 |

|    |     | 6.3.1 Fundamental Computations                                                              | 54 |

|    |     | 6.3.2 Architectural issues                                                                  | 55 |

|    |     | 6.3.3 Special Requirements                                                                  | 56 |

| 7  | Cor | nclusions                                                                                   | 57 |

|    | 7.1 | The Communication Network                                                                   | 57 |

|    | 7.2 | Shared Memory versus Message Passing                                                        | 58 |

| Τ, | ist | of Figures                                                                                  |    |

|    | 100 |                                                                                             |    |

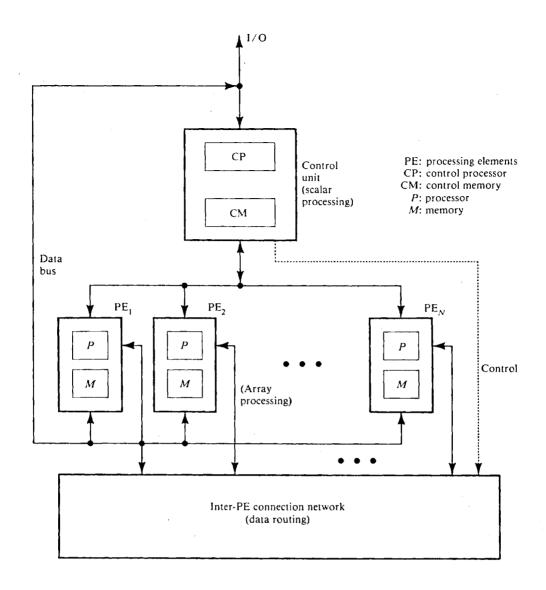

|    | 1   | Functional structure of an SIMD array processor. Source: Hwang and Briggs, "Computer        |    |

|    |     | Architecture and Parallel Processing", Page 24, McGraw-Hill, 1984                           | 12 |

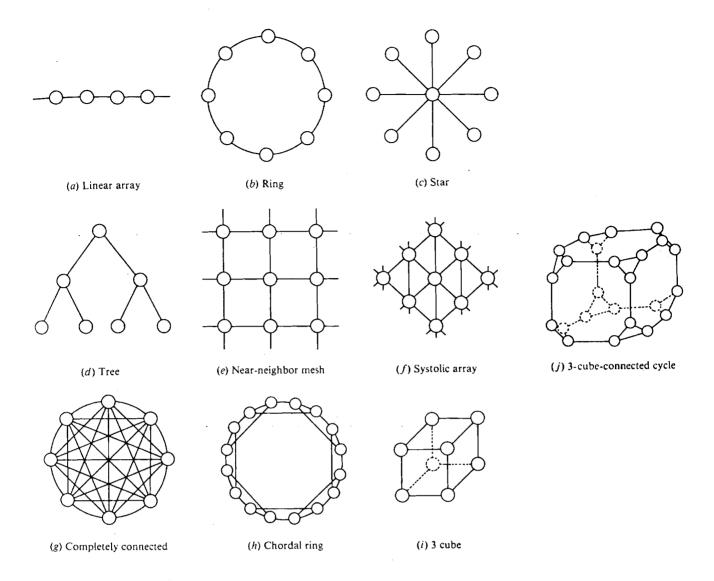

|    | 2   | Static interconnection network topologies. Source: Hwang and Briggs, "Computer Architec-    |    |

|    |     | ture and Parallel Processing", Page 335, McGraw-Hill, 1984                                  | 13 |

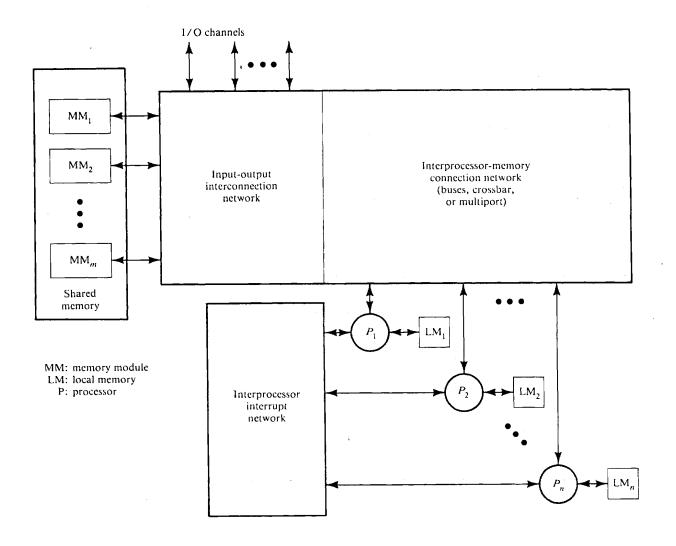

|    | 3   | Functional design of an MIMD multiprocessor system. Source: Hwang and Briggs, "Computer     |    |

|    |     | Architecture and Parallel Processing", Page 26, McGraw-Hill, 1984                           | 16 |

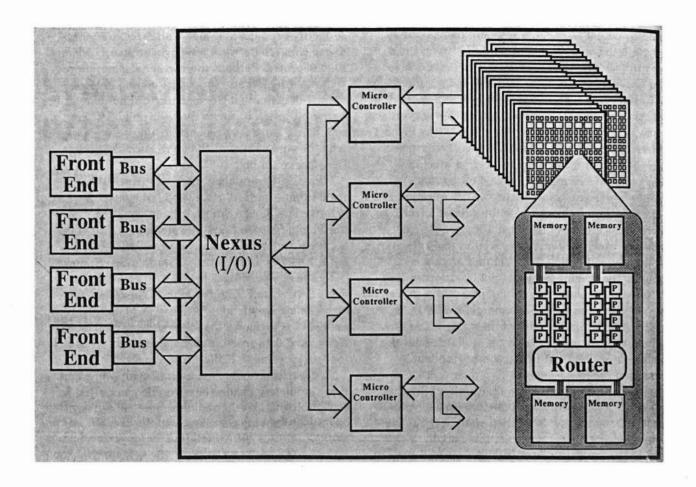

|    | 4   | Block diagram of The Connection Machine. Source: Frenkel, "Evaluating Two Massively         |    |

|    |     | Parallel Machines", CACM, Volume 29, Number 8, August 1986                                  | 20 |

|    | 5   | Functional division of the DADO tree. Source: Stolfo, "The DADO Parallel Computer",         |    |

|    |     |                                                                                             | 23 |

|    | 6   | A 16-input 16-output Butterfly switch. Source: "The Butterfly Parallel Processor Overview", |    |

|    |     | BBN Technical Report Number 6148 (Version 1), Bolt Beranek and Newman Inc., March 1986      | 26 |

|    | 7   | Example of a KL-ONE semantic inheritance network. Source: Brachman and Schmolze, "An        |    |

|    |     | Overview of the KL-ONE Knowledge Representation System", Cognitive Science, Volume 9,       |    |

|    |     | page 196, 1985                                                                              | 27 |

|    | 8   | Example OPS5 rule system. Source: Miranker, "TREAT: A Better Match Algorithm for AI         |    |

|    |     | Production Systems", AAAI87 paper draft, January 1987                                       | 32 |

|    | 9   | An example RETE match network. Source: Miranker, "TREAT: A Better Match Algorithm           |    |

|    |     | for AI Production Systems", AAAI87 paper draft, January 1987                                | 3: |

#### 1 Introduction

#### 1.1 The Need for Parallelism in AI

Virtually all current Artificial Intelligence (AI) applications are designed to run on sequential (von Neumann) computer architectures. As a result, current systems do not scale up. As knowledge is added to these systems, a point is reached where their performance quickly degrades. Thus paradoxically, programs become slower as they become smarter. As a consequence, current systems can perform "intelligently" only in limited domains and suffer from *brittleness*. Furthermore, current systems do not generally perform in real time.

Several techniques have been identified for speeding up AI programs on sequential machines. They include improved instruction set design, faster clock rates, custom VLSI hardware and the use of advanced AI language compilers. A von Neumann computer, however, does not utilize its hardware efficiently; most of the chip area is memory and only a few memory locations are accessed at a time. The performance of the machine is limited by the bandwidth between memory and processor. This is what Backus calls the *von Neumann bottleneck*. The bigger one builds machines, the worse it gets.

The von Neumann bottleneck is avoided by distributing the processing power across the memory of the computer. In this scheme the memory becomes the processor (this can be viewed as "smart memory"). Attempts to use parallelism to speed up existing AI systems have met with limited success. Often a speed-up of four times is the best that can be achieved. The major reason for this is that current AI programs (when converted to run on parallel machines) tend to have sequential bottlenecks which dominate in many cases the running time of the entire program.

#### 1.2 Parallelism and NP-completeness

In a recent interview, Richard Karp said:

"Most of the work that the theoretical computer science community has been doing on parallel computation has been concerned with making polynomial-time algorithms even faster ... [Theoreticians] may say "Focusing attention on applying parallelism to NP-Complete problems is hopeless, as you can never reduce run time from exponential to polynomial by throwing processors at a problem, unless you have an exponential number of processors. On the other hand, ..., parallelism may really help us curb combinatorial explosions." [Frenkel 86a]

Many NP-complete problems in AI are well suited to parallel computation. Most of these problems involve heuristic state-space search algorithms. Important classes of such problems are branch-and-bound algorithms (i.e., best-first search), divide-and-conquer algorithms (a.k.a. meansend analysis) and backtrack-search algorithms (e.g. depth-first search used in Prolog).

#### 1.3 Three Representative AI Domains

#### 1.3.1 Why These Domains?

This paper highlights the relationship between three representative artificial intelligence application domains and their parallel hardware realization. I have decided to focus my attention on the three important domains in artificial intelligence, namely knowledge representation (using semantic networks), rule-based expert systems (production systems), and intermediate-level vision (the Hough transform):<sup>1</sup>

- 1. Knowledge Representation: Semantic networks have received wide attention as a paradigm for knowledge representation. They have clean semantics (based on restrictions of First Order Predicate Calculus), are fairly expressive, and are ideally suited to take advantage of massively parallel architectures. Most existing knowledge representation systems are based on variations of semantic networks.

- 2. Rule-based Expert Systems: Production systems employ a restricted form of inference known as "forward and/or backward chaining" (a.k.a. modus ponens in formal logic). Rules have been used extensively in many systems to capture expert knowledge in areas such as medical diagnosis, mineral exploration, or speech understanding. Among their advantages are modularity, and naturalness.

- 3. Vision: Image processing is a mammoth information-processing task. Massively parallel computers are ideally suited for the low (iconic) level processing. Medium- and coarse-grained parallel computers are more appropriate at the higher (symbolic) levels of vision. The key to vision processing is a flow of communication and control both up and down through all representation levels.

The three domains span a wide range of data-structures and computations performed on them:

<sup>&</sup>lt;sup>1</sup>Please note that there are many other important AI domains: natural language processing, robotics, logic programming, planning, etc. The selected domains represent areas most familiar to the author of this paper.

| AI Domain                 | $Data\ Structure(s)$   | Operations                         |

|---------------------------|------------------------|------------------------------------|

| Semantic Networks         | directed acyclic graph | inheritance & categorization       |

| Production Systems        | forest of trees        | database operations (join, select) |

| Intermediate-Level Vision | mesh or tree           | statistics & pattern matching      |

#### 1.4 Three Representative Highly Parallel Computers

#### 1.4.1 Why These Machines?

Most AI-oriented machines are exploratory systems under development at universities and research labs. One can classify existing parallel computers for artificial intelligence under the following taxonomy [Hwang 87]:

- Language-Based Parallel AI Machines:

- 1. List-Processing (Lisp) Machines: Symbolics, TI Explorer

- 2. Prolog Machines: ICOT PIM, Tamura machine

- 3. Functional Programming Machines: ALICE, Rediflow

- Knowledge-Based Parallel AI Machines:

- 1. Semantic Networks: Connection Machine, NETL

- 2. Rule-Based: DADO, NON-VON

- 3. Object-Based: FAIM-1, SOAR

- 4. Neural Networks: ANZA, MARK IV

- Intelligent Interface Parallel Machines for AI-Oriented Systems:

- 1. Speech Recognition: Harpy, HEARSAY-II

- 2. Pattern Recognition/Image Processing: Pyramid, CAAPP

- 3. Computer Vision: Butterfly, WARP

The machines chosen for this paper, namely the Connection Machine, DADO, and the Butterfly, are bold-faced. They have been selected for the following reasons:

• There is a one-to-one mapping between these three machines and the three chosen AI domains

- All have been realized in hardware and extensively benchmarked and some (the Connection Machine and the Butterfly) are currently being marketed [Lim 86]

- All three machines employ conventional, off-the-shelf components for their processors and switching networks

- They have received wide attention from the AI community, and much information about their design and performance is available

- They cover a wide range of fundamental properties of parallel processors, namely module granularity, concurrency control, and communication geometry [Schwartz 83]:

- 1. Thinking Machines' Connection Machine: fine-grained SIMD hypercube

- 2. Columbia University's DADO: medium-grained SIMD/MIMD/MSIMD tree

- 3. The BBN Butterfly: coarse-grained MIMD Butterfly-switch (shuffle-exchange)

It is important to emphasize at this point that the three machines do not exhaust the space of possible parallel architectures. Due to the lack of space (and time) many other interesting machines such as Intel's Hypercube, NYU's Ultracomputer, Schlumberger's FAIM-1, TRW's MARK IV, etc., have not been covered.

#### 1.5 Outline of the Paper

This paper is organized in a breadth-first fashion. It is possible, however, to read it in a depth-first manner. This would be particularly useful for readers who are interested only in one of the machines or one of the AI domains. Basic familiarity with AI (especially semantic networks, production systems and vision) is assumed, but no background knowledge of parallel processing is needed – a brief but comprehensive overview of parallelism is presented in section 2. It describes and contrasts the salient features of SIMD, MIMD and MSIMD architectures. Section 3 is an overview of the architectures of the Connection Machine, DADO and the Butterfly. In section 4, an introduction to parallelism in semantic networks, rule-based expert systems and vision can be found. Section 5 presents an analysis of the performance of the chosen machines in each of the selected AI domains. In section 6 possible architectures for each of the domains are investigated and contrasted. Finally, section 7 contains a general discussion and conclusions. Readers familiar with certain sections or subsections are encouraged to skip them, particularly if short on time.

#### 2 Introduction to Parallelism

#### 2.1 Theoretical Limitations of Parallel Computation

At the most favorable extreme, certain problems will be totally decomposable into completely independent operations which can proceed in parallel. These can be called *constant time* concurrent algorithms. At the opposite extreme, there exist computational processes which are *completely unparallelizable*.

A general (idealized) model for parallel computation is called the *paracomputer* model: A very large number of (identical) processors share a common memory which can be read from and written to simultaneously in a single cycle (multiple writes are resolved in some way). It is useful to note that a single processor with a large enough memory can simulate an N-processor paracomputer in time O(N); thus an N-processor paracomputer can never be more than N times faster than a serial computer.

Though theoretically useful, the paracomputer model is unrealizably powerful. A more realistic model, called the *ultracomputer*, consists of a large number N of communicating processors (each with its own local memory) connected together, where each processor communicates with a fixed number k of other processors (via a favorable interconnection pattern) [Schwartz 80]. It is clear that the N-processor ultracomputer cannot compute faster than an N-processor paracomputer. Since in an ultracomputer one cannot bring more that k quantities together in one place during one cycle of computation, at least  $\log_k N$  cycles will be required. This is an attainable limit; there are many interesting  $O(\log N)$  ultracomputer algorithms. Note that a paracomputer communication cycle can be simulated by an ultracomputer in time  $O(\log N)$ .

For highest efficiency it is often important to balance processor interconnection with local processing. In many cases the "inefficiency factor"  $\log N$  can be regarded as resulting from an imbalance between the amount of work performed locally within each processor and the amount of interprocessor communication performed. One may be able to restore balance by giving each processor a larger amount of local work and only communicating "preprocessed" data. An algorithm of this sort, which uses N processors in an asymptotically efficient way, can be said to be *completely parallelizable*.

Just because an algorithm can be expressed in concurrent terms is no guarantee that it will run significantly faster on a parallel machine. The true measure of parallelism is how much faster a given program will run on n simple parallel processors compared to how fast it would run on a

single processor (and for what ranges of n this is valid). The best one can hope for is a speed-up of n; for most existing AI programs (written in traditional computer languages) this seems to be about 4 [Deering 84]. in practice, several factors can prevent realization of linear speedup. Among the most important are the need for interprocessor synchronization, poor algorithm design (not all parallelism inherent in the problem is exposed), contention among the processors for the same resource, and traditional I/O structures which cannot feed a high-performance processor fast enough to avoid processor idle time.

#### 2.2 A Taxonomy of Parallel Processing

The space of parallel processing can be divided along three dimensions, namely concurrency control, module granularity, and communication geometry [Kung 80]. As will be seen later, practical parallel architectures as embodied in existing parallel computers correspond to a small subspace of the cross product of these three dimensions. The three dimensions form a taxonomy of parallel processing<sup>2</sup>:

- 1. Module Granularity: This refers to the maximal amount of computation a typical processor can do before having to communicate with other processors. This dimension is usually divided into three: fine-, medium-, and coarse-grain. It reflects the processing power of individual processors and the size of their memory space (the two are correlated).

- 2. Concurrency Control: Enforces desired interactions among processors so that the overall execution of parallel algorithms will be correct. This dimension can be subdivided into two orthogonal subdimensions: synchronous versus asynchronous control, and centralized control, distributed control, or control via shared data.

- 3. Communication Geometry: The spectrum of possible processor-to-processor and processor-to-memory communication geometries ranges from the simplest but most limited topologies (ring, star) through tree, mesh, hypercube, and banyan, to the ideal and most complex topology (crossbar).

#### 2.3 Practical Architectures: Narrowing the Space

The interesting and useful parallel architectures correspond to a very small subspace of the cross product  $\{\text{module granularity}\} \times \{\text{concurrency control}\} \times \{\text{communication geometry}\}$ . It is useful at this point to introduce a classification of high-speed computer architectures, suggested by Flynn

<sup>&</sup>lt;sup>2</sup>The taxonomy is crude and is by no means meant to be complete.

[Flynn 72]. Flynn has shown that computer systems fall naturally into four classes, along two dimensions: parallelism within the *instruction stream* and parallelism within the *data stream*:

- 1. SISD (single-instruction stream, single-data stream): A conventional serial computer, exhibiting no parallelism.

- 2. MISD (multiple-instruction stream, single-data stream): A generally unrealistic architecture for parallel computers (no real embodiment of this class exists).

- 3. SIMD (single-instruction stream, multiple-data stream): A vector or array processor in the sense that each instruction operates on a data vector rather than a single operand.

- 4. MIMD (multiple-instruction stream, multiple-data stream): A computer (sometimes referred to as a multiprocessor) composed of N processors, each of which is a complete computer.

Only the last two classes (vector processor and multiprocessor) are of interest for parallel computation. These types of computers are vastly different in how they obtain parallelism of operation. Vector processors (SIMD machines) are synchronous lock-step computers that require central controls and tend to have small granularity. The communication geometry is of major importance. Multiprocessors (MIMD machines) consist of a set of asynchronous processors with relatively large granularities. Memory organization is of major importance, as it affects control. A hybrid class, designed to bridge the gap between these two extremes, is referred to as multiple-SIMD (MSIMD). Essentially, MSIMD computers are partitioned SIMD computers where each partition is controlled by an independent host. The host machines can be organized as an SIMD, MIMD, or even MSIMD computer. MSIMD computers are particularly useful in image processing.

#### 2.4 SIMD (Array) Machines

The central question concerning the design of array computers is how to build data access and communication facilities so that the array computer is useful for as large a variety of computations as possible (this subject area is still evolving). Most surprising, an efficient algorithm for a serial computer may lead to a relatively inefficient algorithm for a vector computer [Stone 80].

#### 2.4.1 Organization of an Array Computer

The control unit in an array computer is itself a computer. The crucial difference between this processor and others is that it can execute conditional branch instructions. Each instruction is

Figure 1: Functional structure of an SIMD array processor

either a control instruction, in which case it is executed entirely within the control unit, or it is a vector instruction and is executed in the processor array (but the instruction stream is much like a conventional serial instruction stream, with each instruction executed in sequence). The control processor has the exclusive privilege to determine which instruction to execute next. Figure 1 depicts the functional structure of an SIMD array processor. A few additional facilities can greatly enlarge the class of problems that can be done efficiently on an SIMD computer. They include masking for conditional branching, a suitable interprocessor communication network, and data skewing support.

Figure 2: Static interconnection network topologies

#### 2.4.2 Interprocessor Communications in Array Processors

The interconnection network supports data exchanges between processors in an array computer. To maximize parallelism, as much as possible of the available memory and processor bandwidths must be utilized. Data must be stored in such a way as to avoid memory-access conflicts. This calls for careful structuring of data in its storage format. Data structuring for efficient memory access frequently causes data to be fetched in such a way that operand pairs are not properly aligned for parallel manipulation. To solve this problem we must install a permutation network in the processor [Siegel 85]. Figure 2 depicts popular interconnection network patterns.

At the two extremes one finds the complete interconnection network (crossbar) and the ring network (linear array with wrap-around). A crossbar interconnection network eliminates contention for communication resources but does not eliminate contention for memory. It is the most general and flexible interconnection scheme, providing total connectivity between N processors at the prohibitive cost (for large N) of  $N^2$ . Ring networks are useful only where communications requirements are very small. They are extremely simple both logically (control) and hardware-wise.

One can retain full interconnection flexibility, with logic growth proportional to  $N \log_2 N$ , if the time to do a permutation is permitted to grow as  $\log_2 N$  instead of being constant. A better approach is to reduce the number and hence flexibility of the interconnections, while maintaining as high a speed as possible. The following topologies are examples of such networks, and are presented in order of decreasing complexity (and generality):

- Banyan Networks: A Banyan network provides complete interconnections at a cost in switching circuitry that grows as N log N. It has a unique path from each input to each output and is more general than most other cell-based networks. The binary k-cube, perfect shuffle, and tree networks are graph homomorphic images of the Banyan. They have lower hardware cost, but higher contention and reduced efficiency.

- Binary k-Cube (Hypercube): Contains a rich collection of data paths and is suitable for applications such as sorting. It is one of today's most popular designs [Wiley 87]. Each of the processors is placed at a different corner of the k-dimensional cube and is assigned a binary ID 0 ≤ p ≤ 2<sup>k</sup> − 1. Two processors are connected iff their IDs differ only in one bit. k connections per processor are required. The largest distance between any two processors is proportional to k.

- Cube-Connected Cycles (CCC): The CCC can be viewed as a simulator of the k-cube. Only a constant number of wires per processors is needed. The  $2^k$  processors are arranged in  $2^{k-r}$  rings of size  $2^r$  at the corners of a (k-r)-cube. The time complexity for divide-and-conquer is  $O(k-r) + O(2^r)$ . If k and r are chosen so that  $(r-1) + 2^{r-1} \le k \le r + 2^r$  then performance is retained while interconnection complexity is reduced [Preparata 81].

- Perfect Shuffle (shuffle-exchange): The shuffle is very similar to the CCC in its properties. It is ideally suited for algorithms having a recursive divide-and-conquer character. The shuffle-exchange performs a permutation of its input similarly to shuffling a deck of cards. First the deck is divided exactly in half, then the two halves are interleaved such that the lower half ends up taking even positions and the higher half odd positions in the newly formed deck (retaining their orders).

- Mesh (2D-array): Mesh connectivity is extensively used for image processing, matrix computations and graph algorithms, where many of the computations involve only the small neighborhood of a processor. Only four connections per processor are needed. The topology is regular and efficiently maps onto VLSI circuits. The major drawbacks of a mesh are its large delay  $(O(\sqrt{n}))$  and the fact that its highly blocking. The problem can be somewhat alleviated by adding wrap-around links (torus).

- Tree: Communication between remote leaves faces a bottleneck toward the root, but trees perform well on a rather large range of problems (sorting, matrix multiplication (in  $O(n^2)$ ), and several NP-complete problems). Tree machines can efficiently implement exhaustive search algorithms for several NP-complete problems, but exponential complexity eventually catches up either in compute time or in number of processors since speed-up is, at most, linear with the number of processors.

#### 2.4.3 SIMD Programming

The SIMD programming paradigm (which reflects the underlying architecture of an array computer) is data-level parallelism. One element of data is stored per processor and the front-end host computer executes a serial program, each step of which can involve computations in all the machine's processors. Such a solution seems far more natural and easy to construct than those typically proposed or implemented for coarse-grained (MIMD) parallel machines. An advantage of using a fine-grained (SIMD) machine is that it allows programmers to write programs which suppose a much larger number of processors that the machine. To quote Hillis, "It is very much like virtual and physical memory". As a fine-grained machine is expanded (by adding processors, memory and communication devices to an existing machine), programs can in many cases take advantage of the increase in computational power without any fundamental changes in design.

#### 2.5 MIMD Machines (Multiprocessors)

The interesting problems for these machines are quite different from those of vector computers. Multiprocessors are suitable for a much larger class of computations than array computers because multiprocessors are inherently more flexible [Stone 80]. It is relatively straightforward to fit a computation to a multiprocessor, which is not the case for vector computations on an array computer. However, to attain high-efficiency computation in a multiprocessor system, one has to solve problems of task synchronization and task scheduling. In some cases, improper synchronization or

Figure 3: Functional design of an MIMD multiprocessor system

scheduling can leads to gross inefficiency, and in extreme situations computation may cease entirely. This is in sharp contrast to array computers. Since synchronization is automatic and scheduling unnecessary (only one task at a time is performed) for array computers, they are free from the problems that surround the multiprocessor, though at the expense of flexibility.

#### 2.5.1 Memory Organization in Multiprocessors

Memory organization in multiprocessors is an important issue, as it most strongly affects the style of programming. Three classes of machines are presented, namely shared memory, message passing, and hybrid multiprocessors. Figure 3 illustrates the functional design of an MIMD multiprocessor system.

Shared Memory Machines A shared memory machine has a single global memory accessible to all processors. Each processor has some local memory (cache or registers), but the operating system usually presents the user with the view of totally shared memory (and often the user is not allowed to explicitly use the cache). Efficiency is the primary motivation for allowing shared memory at the user level. Each process can retrieve the data it requires using hardware primitives; no costly system software need be involved. Often, this approach ignores the problem of synchronization, which can dominate the cost of remote references. A key feature of shared memory systems is that the access time to a piece of data is independent of the processor making the request (barring memory contention, which is as important an issue as in uniprocessors). The aggregate memory bandwidth limits the number of processors that can be accommodated before the system's performance degrades due to contention.

Message Passing Machines Message passing systems are configured so that some memory is local to each processor, but none is globally accessible. Message-passing imposes a value-oriented semantics: processes may only communicate values, which may require the exchange of an environment in which to interpret the value (i.e., a pointer value is represented by the object to which it points). This object-oriented approach has proven quite popular for distributed systems composed of many processes. The time it takes for a processor to access data depends on its distance from the processor that currently has the data in its local memory. The design of the communication network between the processors is, therefore, a major concern in a message passing system. In contrast to the shared memory system, the performance of an algorithm will depend on how well the location of the data matches up with it use.

Hybrid Machines Hybrid systems have some of the properties of shared memory systems and some of the properties of message passing. All memory is local to a given processor, but the operating system makes the machine look like it has a single, global memory. Thus, programs are written as if for a shared memory system. However, data must be laid out as if for a message passing system if best performance is to be obtained, since access time depends on the distance between the owner of the data and the requestor (e.g., the **Butterfly**). Even though the penalties for poor data layout are often considerably smaller on hybrid systems, data layout is key to algorithm performance and the aggregate communications speed is a limit on the number of processors that can be accommodated.

#### 2.5.2 Synchronization, Scheduling, and Resource Sharing

Synchronization and interlocking can be done relatively easily using special instructions that manipulate semaphores. Each semaphore has a queue associated with it. To obtain high-efficiency utilization of processors during a computation, it is usual to remove a suspended process from a processor (placing it in an appropriate queue) and permit another process to proceed on the newly available processor. An important problem in multiprocessing is deadlock prevention. A global policy is necessary for dealing with this problem. This policy, traditionally, is enforced by the operating system.

In general, multiprocessor computer systems have all of the resource allocation problems of conventional serial computers, but processor scheduling and memory allocation tend to be the dominant problems. Recent results in the study of algorithm complexity indicate that processor scheduling and memory allocation problems may be so inherently complex that there is no hope of solving them with fast algorithms. In practice, the resource allocation problem is placed in the hands of the user to solve through his assignment of relative priorities.

#### 2.5.3 MIMD Programming

Coarse-grained parallel computers must generally be programmed by means of a method that might aptly be called control-level parallelism. This paradigm requires the programmer to divide a program into fragments, one for each of the processors in the machine [Waltz 87]. However, the fit of module memory capacity and the size of a typical data-element is not as natural as in the SIMD case, requiring special software mechanisms. Synchronization is another problem. In writing a program for a coarse-grained machine, one can adhere to concepts much like those used for programming sequential computers; the problems arise in attempting to coordinate the programs. Worse yet, it is often difficult to find parallelism in programs, let alone exactly the right amount of parallelism needed to distribute the work load equally among the (relatively small) number of available processors.

#### 3 Overview of the Chosen Machines

#### 3.1 The Connection Machine

#### 3.1.1 Introduction

The Connection Machine was designed by Daniel Hillis to concurrently manipulate knowledge stored in semantic networks [Hillis 84]. it was designed to be fast at a few very simple operations that are important for artificial intelligence, such as property lookup in a semantic inheritance network. As it turns out, the resulting machine — built by Thinking Machines, Inc. — seems to be quite general. The Connection Machine is at the "radically fine-grained" end of the spectrum of parallel machines [Waltz 87]. It is available in configurations ranging from 16,384 up to a maximum of 65,536 (for the CM-2) processor-memory units.

The design philosophy underlying the Connection Machine is that cost should be in the network, not in its many processors, and that there should be an appropriate balance between the network and processors. A well-tested technology is employed in order to achieve simplicity and reliability. The Connection Machine can operate at its peak processing rate (close to 20 GFLOPS for the CM-2) in a wide range of applications. The key to such flexibility is a communication network that enables the multiprocessors to exchange information in the pattern best suited to the problem at hand [Hillis 87]. Furthermore, Each processor can, under software control, mimic a number of virtual processors. To accomplish this, the memory of each processor is divided up so that each "virtual processor" operates on a smaller amount of memory. The speed penalty for computation has been verified as being approximately linear (up to a million virtual processors).

#### 3.1.2 The Connection Machine Design

Physically, the Connection Machine consists of 4096 chips of proprietary design, each containing 16 processors – each with a local memory of 64 Kbits (for the CM-2) – plus a hardware router (making for 512 Mbytes of total primary storage). All processors execute instructions from a single stream (i.e., in SIMD mode) generated by four microcontrollers under the direction of a conventional host (DEC VAXen or Symbolics 3600 Series Lisp Machines). Each operation can combine two bits from memory with one bit from a register, producing one bit to memory and one bit to a register. See figure 4 for a block diagram of the Connection Machine.

The processor-memory units are wired (via routers) as a boolean 12-cube with 4,096 ( $2^{12}$ ) corners, one for each chip in the Connection Machine. 24,576 bidirectional wires are used to

Figure 4: Block diagram of The Connection Machine

connect them. However, no processor is more than 12 wires away from any other. Each cube in the 12-cube has two subcubes, which may be designated 0 and 1 respectively. As a result each corner has a unique address specified by a string of 12 binary digits (bits). Each router can accept a message from one of the processors on the chip (or from a router on a different chip) and send it to either a processor on its chip or another router on a different chip. Each router can also buffer messages if there are no channels available over which to send them [Hillis 85].

Parallel channels support I/O rates of up to 2000 Mbps (for very-high speed devices such as disks and frame buffers). The CM-2 can be used with up to 8 Data-Vault parallel disk storage devices. Each of these contains  $42.5\frac{1}{4}$  inch winchesters that can be read from and written to in parallel. Each unit has a data transfer rate of 40 Mbytes/second, achieving a total transfer rate of approximately 320 Mbytes/second.

#### 3.1.3 Programming the Connection Machine

The Connection Machine programming paradigm (which reflects its underlying architecture) is data-level parallelism: one element of data is stored per processor (or virtual processor) and the front-end host computer executes a serial program, each step of which can involve computations in all the Connection Machine's processors. Programmers interact with Connection Machine through a conventional computer, known as the host. The processors of the Connection Machine are connected with the host much as a conventional memory unit would be. The Connection Machine can be programmed at the front end with C\* and \*Lisp, which are data-parallel extensions of Common-Lisp and C respectively. Programs for the Connection Machine are surprisingly similar to conventional programs [Frenkel 86b]. However, learning to write programs for parallel machines requires thinking in ways that are quite different from those demanded by sequential computers.

The basic operations of the machine operate on sets and functions rather than on numbers or pointers. Numbers are just special nodes (concepts) that are recognized by the arithmetic instructions. Four instruction groups are supported:

- 1. Set operations: Intersection, union, difference, complement, clear, etc. These require no messages to be sent.

- 2. Propagation: Projection, restriction, and inheritance. These involve message transmission.

- 3. Function manipulation: Application, modification, composition, etc. This group of operations (which support database join) gives the Connection Machine its additional power over marker propagation machines.

- 4. Arithmetic: Associative functions such as sum, multiply, min/max, and/or, etc., and asymmetric operations such as subtract.

#### 3.2 **DADO**

#### 3.2.1 Introduction

The ultimate goal of the DADO project group is the design and implementation of a cost effective, high performance, attached rule processor that is driven by a conventional host machine and is capable of rapidly executing rule-based software with very large rule sets [Stolfo 86]. The essence of their approach is to execute a very large number of pattern-matching operations on concurrent hardware. Although DADO was designed specifically for the acceleration of OPS-style production

systems, it has been found to suit a larger class of problems called almost decomposable searching problems.

#### 3.2.2 DADO's Design Philosophy

DADO is a family of special purpose highly parallel tree-structured computers in which memory and processing are extremely intermingled [Stolfo 87]. The distinction between the members of this family is granularity, the storage capacity and processor functionality at an individual processing element (PE). Each PE is a fully programmable microcomputer with a modest amount of local memory (16-20 KBytes in DADO2). A single conventional host adjacent to the root of the DADO tree controls the operation of the entire ensemble of PEs.

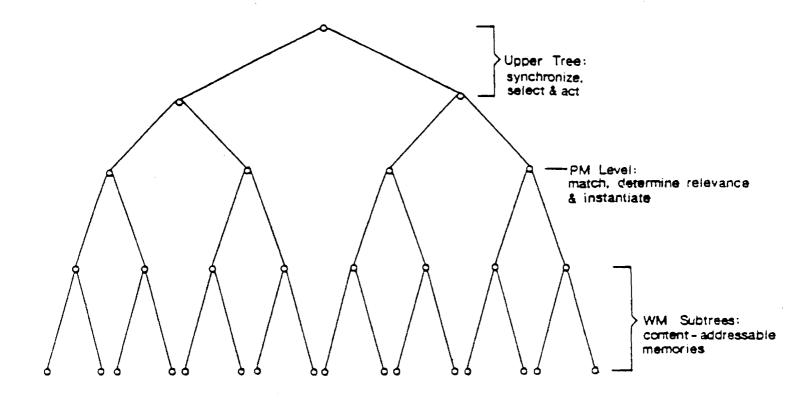

DADO's execution modes are rather unique. Each PE may operate in SIMD mode whereby instructions are executed as broadcast by some ancestor PE in the tree. Alternately, a PE may operate in MIMD mode by executing instructions from its local RAM (memory). Such a PE may, however, broadcast instructions for execution by descendant PEs operating in SIMD mode. This allows DADO to be fully partitioned into a number of distinct "sub-DADOs", each executing a distinct task. This mode is usually referred to as multiple-SIMD (MSIMD) [Siegel 81]. Figure 5 illustrates a possible configuration of DADO for production systems execution. The PM level operate in MIMD-mode while the upper tree and the WM-subtrees operate in SIMD-mode. A fourth mode, termed SPMD (for single-program, multiple-data stream), provides parallel remote procedure invocation in the style of SIMD processing. The procedures are stored locally within the PEs, operate autonomously and, therefore, may take different amounts of time to complete. Machine-level instructions are not broadcast and executed in lock-step. Rather, addresses of prestored code are broadcast to PEs for local execution.

The designers of DADO introduced a special mechanism designed to accelerate certain basic computations on the machine. The *min-resolve* circuit, as it's called, uses the combinatorial hardware in the I/O switch to select one out of all the enabled PEs in a single instruction cycle [Gupta 84a]. It can be used to calculate (in one cycle) the minimum value of a set of values distributed one to a PE. Furthermore, the PE with the minimum value is marked (ties are arbitrated in hardware according to a fixed PE ordering scheme). One use of the min-resolve circuit is to identify the maximally-rated conflict set instance from all PEs storing production rules. The mechanism should also useful in certain vision applications.

DADO1 had 15 PEs connected as a complete binary tree. DADO2, the fourth prototype in

Figure 5: Functional division of the DADO tree

the DADO series (in operation since December 1985), is a medium-grained fully populated binary tree-structured multiprocessor incorporating 1023 moderately powerful processing elements (PEs). It employs two physical tree interconnections. A specialized I/O coprocessor for a DADO2 PE was designed to accelerate inter-PE communication. This also provides a measure of fault tolerance. DADO was designed around commercially available, state-of-the-art technology. The Intel 8751 was chosen at the time (1983) as the microprocessor for the PEs (it was the only commercially available single chip microcomputer in existence that provided 4 parallel 8-bit ports). Initial performance results for OPS5 rule matchings indicate that DADO2 is 2 to 31 times faster than a VAX 11/750.

#### 3.2.3 Programming DADO

As mentioned above, DADO can be programmed efficiently for a class of problems called *almost decomposable searching problems*. The class includes Prolog-like backward chaining logic programming formalisms, relational database operations, and statistical pattern recognition. Each of these problems shares the same common programming paradigm [Stolfo 87] on DADO:

• Distribute an initial set of data to the processors

- Broadcast the data to other processors in constant time

- Match (in each processor) a query against the data

- Resolve to find the best answer in constant time

- Report the final answer to the root of DADO

Three high level parallel programming languages are available on DADO. All are straightforward extensions of (serial) conventional C, PL/M, and Portable Standard Lisp (PSL). These extensions involve adding SIMD variables to the languages (i.e., special vectors) and extending some operators to operate on them in parallel.

#### 3.3 The Butterfly

#### 3.3.1 Introduction

The Butterfly is a coarse-grained, shared-memory, expandable MIMD parallel computer built by Bolt Beranek and Newman (BBN) [BBN 86]. The computer got its name from the Butterfly switch which it uses for interprocessor communication. The switch supports a processor-to-processor bandwidth of 32 Mbits/second. One processor (Motorola MC68000) and 1 to 4 MBytes of memory are located on a single board called a Processor Node. The processor is capable of executing 500,000 instructions per second. The memory architecture, implemented by the operating system in conjunction with a micro-coded coprocessor, provides the user with the *illusion* of shared memory. Remote memory references (via the Butterfly switch) take about five times longer than local references. The speed of the processors, memories, and switch are balanced to ensure that none become a performance bottleneck.

The Butterfly's architecture scales in a flexible and cost-efficient fashion from 1 to 256 processors. When using 256 processors the computer has a raw processing power of 128 MIPS and a main memory of 256 to 1024 MBytes. For applications such as matrix multiplication, gaussian elimination, convolution, and histograms of images nearly linear speed is achieved through the entire range of processors (up to 256)<sup>3</sup>. To date, the Butterfly has been mainly used for research in image processing and computer vision. Symbolic processing and AI applications are currently being developed (object-oriented programming and rule-based expert systems).

<sup>&</sup>lt;sup>3</sup>Note that most of these applications can be efficiently computed in parallel on mesh-connected machines.

#### 3.3.2 Butterfly Architecture

Each Butterfly node contains an 8Mhz Motorola MC68000 microprocessor with 24 bit virtual addresses, at least 1 MByte of main memory, a 2901-based bit-slice microcoded co-processor called the Processor Node Controller (PNC), memory management hardware, an I/O bus, and an interface to the Butterfly switch. The PNC interprets every memory reference issued by the 68000 and is used to communicate with other nodes across the switching network. It also provides, in microcode, efficient test-and-set and queueing operations, a process scheduler, and communication synchronization mechanisms. The memory management unit is used to translate virtual addresses (used by the 68000) into physical memory addresses. As a result, the memory of all Processor Nodes, taken together, appear as a large single global memory to application software.

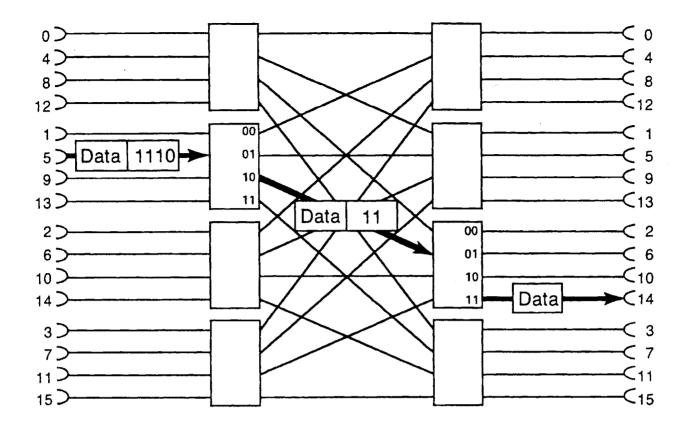

The Butterfly switch is a collection of  $4 \times 4$  switch elements (4-input 4-output crossbars) configured as a "serial decision" network, a topology similar to that of the Fast Fourier Transform Butterfly. An N-processor system uses  $(N \log_4 N)/4$  switches arranged in  $\log_4 N$  columns. Switch operation is similar to that of a packet switching network. Figure 6 illustrates a 16-input 16-output Butterfly switch. To reduce switch contention a large configuration (e.g., a 128-node Butterfly) contains extra switch nodes, used to provide alternate communication paths between processors. This also makes the switch more resilient to switching node failures. Machines are configured so that the probability of message collision within the switch is relatively low (typical contention overhead is 1% to 5%). The switch supports efficient transfer of blocks of data between any pair of Processor Nodes at full switch bandwidth. The Butterfly I/O system is distributed among the Processor Nodes. The I/O bus on each processor supports connections to a Multibus (for fast I/O devices such as disks, and external memory and processors) and serial RS-232 lines (for terminals).

#### 3.3.3 Programming the Butterfly Parallel Processor

The Butterfly Parallel Processor is programmed exclusively in high-level programming languages (C, Symbolics 3600 compatible Lisp, and Fortran). Editing, compiling and linking, downloading, running and debugging of programs are done from a UNIX front-end (VAX or Sun workstation). A window manager enables rapid switching between the front-end and the Butterfly system environments. The Chrysalis operating system contains application libraries for allocating memory, setting up processes, etc., and low-level subroutines (the kernel) callable from the user's program. The most significant application library is the Uniform System Library which creates an environment

Figure 6: A 16-input 16-output Butterfly switch

where all processors share a single common address space. It provides subroutines to efficiently allocate data structures for the problem.

Two distinct approaches to programming the Butterfly have seen widespread use: message passing and shared memory. When using the message passing paradigm the programmer decomposes the application into a moderately sized collection of loosely coupled processes which from time to time exchange control signals or data (using general communication primitives). This approach is similar to programming a multiprocess application for a uniprocessor. In the shared memory approach, a task is usually some small procedure to be applied to a subset of the shared memory. A task, therefore, can be represented simply as an index, or a range of indices, into the shared memory and an operation to be performed on that memory. This style is particularly effective for applications containing a few frequently repeated tasks (e.g., scientific computing). Memory and processor management are used to keep all memories and processors equally busy.

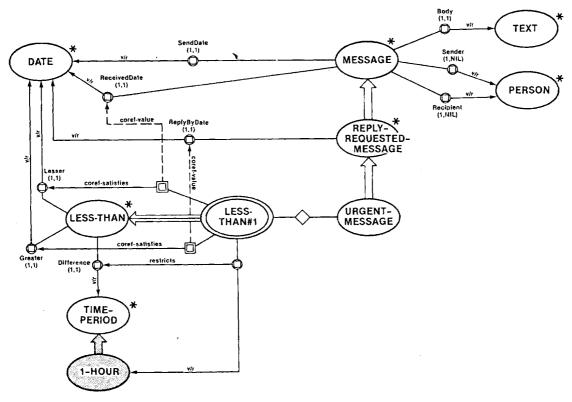

"A REPLY-REQUESTED-MESSAGE is, among other things, a MESSAGE with a ReplyByDate, which is a DATE."

Figure 7: Example of a KL-ONE semantic inheritance network

#### 4 Parallelism in the Selected Domains

#### 4.1 Massive Parallelism in Semantic Networks

#### 4.1.1 Introduction

The building block of semantic networks are *concepts*. Concepts, represented as nodes in a semantic networks, roughly correspond to the notion of concepts in natural language, but have more precise definitions. Concepts derive their meaning from the *properties* and the corresponding *property-values* they have and from their position in a subsumption hierarchy, expressed via *IS-A links*. Concepts higher in the conceptual hierarchy denote more abstract (general) concepts while concepts at the bottom of the hierarchy are usually referred to as *individual concepts* (instances). For best economy of representation, properties should be attached at the highest appropriate level of abstraction. Figure 7 illustrates a fairly complex KL-ONE semantic network.

<sup>&</sup>quot;An URGENT-MESSAGE is a REPLY-REQUESTED-MESSAGE whose ReceivedDate and ReplyByDate satisfy a LESS-THAN whose Lesser is the ReceivedDate, whose Greater is the ReplyByDate, and whose Difference is 1-HOUR."

Semantic networks support two important forms of reasoning, namely inheritance and categorization (or classification). There substantial evidence that both inheritance and classification are important forms of human reasoning and that people are very good at doing both. Inheritance allows an agent to infer ("by inheritance") properties of a concept based on the properties of its ancestors. A major problem for inheritance is the presence of exceptions and conflicting information. Categorization (or classification) is the dual of the inheritance problem. Unlike inheritance, which seeks some property value of a given concept, categorization seeks a concept that has some specified property values [Shastri 86].

Traditional representation languages include KL-ONE [Brachman 85] and its descendants, KL-TWO [Vilain 85] and NIKL [Moser 83]. They usually have two major components: a definitional language (conceptual taxonomy) and a propositional language (fact database). Semantically, they are based on restrictions of First Order Logic with Lambda Abstraction (FOL+). These restrictions trade computational power for computational tractability. The classification issues in KL-ONE have been studied extensively and are reasonably well understood. The use of a classifier ensures that the resulting knowledge base is sound, complete, and efficiently structured. Classification has been shown to be NP-complete, even for very restricted versions of KL-ONE [Brachman 84].

As an alternative to traditional representation languages, Shastri and Feldman [Shastri 85b] [Shastri 85a] have proposed to integrate evidential reasoning into semantic networks. The evidence combination rule employed in their system is a generalization of the Dempster-Shafer evidence combination rule. Traditional representation languages do not appropriately handle incompleteness, inconsistency and uncertainty. Shastri's language offers a uniform treatment of inheritance and categorization problems, including those that involve exceptions, multiple hierarchies (lattices rather than trees), and conflicting information. A major advantage of the language is that it can be implemented on a massively parallel computer. An account, accompanied by a figure, is given below.

The Need for Parallelism in Semantic Networks Knowledge Representation in AI involves more than just looking up a fact in a table. If knowledge is stored in a semantic memory, then finding the relevant information may involve searching the entire network. This can take time that is exponentially proportional to the size of the network. In 1968, Quillian [Quillian 68] proposed that information stored in a semantic network could be manipulated by concurrently propagating markers through the network. Such a system would be able to retrieve information in a time that

was essentially independent of the size of the network. The basic idea was extended considerably by Fahlman [Fahlman 82], Woods [Woods 78] and others.

The following closely follows [Shastri 86]. Ideally, each concept (node) should be allocated to a distinct processor and the interconnections between these processors should be flexible enough to represent the relations between the corresponding concepts. This requires a large number of processor elements with programmable logical connections so that the topology can be configured to suit the problem. This form of parallelism, which has been termed "massive parallelism", provides a phenomenal increase in raw computing power. Due to technological constraints, processors tend to be simple and have little local memory, and the interconnection network topology is regular. However, the memory is distributed throughout the machine and is more intelligent (can modify itself in many places simultaneously through the local processors).

#### 4.1.2 A Taxonomy of Massively Parallel Architectures

Fahlman [Fahlman 82] has proposed a division of massively parallel systems into three classes:

- 1. Marker-Passing Systems: This is the simplest family and the most limited. Communications among processing elements is in the form of single-bit markers. Each node has the capacity to store a few distinct marker bits and perform simple boolean operations on markers. Links between nodes are, in effect, dedicated private lines, so a lot of marker traffic can proceed in parallel. Fahlman's **NETL** is an example of such as system. A major problem with his architecture was its use of an external machine to control propagation, which introduces a sequential bottleneck into the system [Bic 85].

- 2. Value-Passing Systems: These systems pass around continuous quantities or numbers and perform simple arithmetic operations on these values (e.g., traditional analog computers). They never suffer from contention. Many of the iterative relaxation algorithms that have been proposed for solving low-level image processing problems and spreading-activation models of semantic processing are ideally suited to value-passing architectures. Connectionist networks also fall under this category. Their units are patterned after neurons (though they represent a gross over-simplification). For a detailed description see [Feldman 82], [Rumelhart 86], and [Fahlman 87].

- 3. Message-Passing Systems: These are the most powerful and by far the most complex systems. Such generality has a price: individual computing elements are complex, communication costs

are high, and there may be severe contention and traffic congestion problems in the network. Many message-passing systems with well-defined semantics have been proposed (e.g., KL-ONE). Also, most parallel computers fall into this category (e.g., the Connection Machine).

#### 4.1.3 Shastri's Massively Parallel Representation Language

Shastri [Shastri 85a] [Shastri 86] has successfully applied the connectionist paradigm to his theory of evidential reasoning in semantic networks. His system employs distributed control (i.e., spreading activation) and clever mechanisms to efficiently support inheritance and categorization. The system has been simulated on a conventional computer and performed as expected. The representation language uses special units to encode concepts, properties, and the relations among them. Units have only two states: active or inert. Active units produce an output that is equal to their potential. For concept nodes, the potential is graded and represents their level of activity.

Queries are presented to the semantic network via special routine networks. The query network is appropriately interfaced with the semantic network, activating the relevant units in it. Bidirectional relay nodes facilitate the computation along IS-A links (used in inheritance and categorization). At any given time, IS-A links are enabled in one direction only to eliminate the possibility of indefinite oscillation of the network. The network settles down after a period of time that is linearly proportional to the depth of the conceptual hierarchy (logarithmic in the size of the network, i.e., the number of concepts). A winner-take-all network (which is part of the query network) arbitrates among the possible candidate answers (if more than one concept is significantly active). The routine network has mechanisms to deal with conflicts and null answers.

#### 4.2 Parallelism in Rule-Based Expert Systems

#### 4.2.1 Introduction

One of the goals of AI is the creation of programs that base their "reasoning" on experience. After several decades of research in AI, rule-based production systems have emerged as one of the most important and widely employed tools for the implementation of expert systems and other AI software. A production system organization facilitates the modular, incremental growth of knowledge bases, and allows for the useful but unplanned interaction of independently-specified rules [Winston 77] [Nilsson 80]. While a few production systems have already found commercial application, their use in certain other domains (especially real-time systems) is precluded by slow

execution speeds. A detailed overview of parallelism in the OPS5 production systems follows.

While there has been some progress toward the goal of automatically generating rules of inference ([Quinlan 79]) the construction of intelligent programs has proven to be a difficult task, one that depends on the ability of a highly skilled individual to create sets of rules. Waltz [Waltz 87] believes that memories of specific events, and not rules, are the key to reasoning from experience. This paradigm has been overlooked in the past because sequential (von Neumann) computers are too slow to execute some of the necessary basic operations (like associative memory search). A brief description can be found below.

#### 4.2.2 Production Systems

In general, a production system is defined by a set of rules, or productions, that form the production memory (PM), together with a database of assertions, called the working memory (WM). Each production consists of a conjunction of pattern elements, called the left-hand-side (LHS) of the rule, along with a set of actions called the right-hand-side (RHS). The RHS specifies information that is to be added to (asserted) or removed from the WM when the LHS successfully matches against the contents of the WM. In operation, the Production System repeatedly executes a cycle of three major phases. In the match phase one determines, for each rule, whether the LHS matches the current environment of the WM. All matching instances of the rules are collected in the conflict set of rules. Next, a Select phase is initiated to choose exactly one of the matching rules according to some predefined criterion. Finally, in the Act phase, WM elements are added or deleted from WM as specified in the RHS of the selected rule, or some other operation (e.g., I/O) is performed. Typical conflict resolution techniques use recency of a matched data in WM, as well as syntactic discrimination.

The OPS5 Production System The production system language OPS was first described by Forgy and McDermott (1977). Several subsequent versions have appeared, with OPS5 being the most widely known. OPS5 has been evaluated favorably by many researchers and has been used to implement a large and successful commercial production system (McDermott's R1). Its static and dynamic characteristics have been measured on several OPS5 production systems, and even though the language was designed for sequential processing, its speed can be increased significantly by parallel execution. Miranker [Miranker 87] is actively engaged in the development of a production systems language specifically designed for parallel execution. Such a language may well prove better

| Rule:                    | Initial Working Memory: |

|--------------------------|-------------------------|

| $(P 	ext{ example-rule}$ | $(A\ 1)$                |

| (A < x >)                | $(B\ 1\ 2)$             |

| (B < x > < y >)          | $(B\ 2\ 3)$             |

| (C < y >)                | $(B\ 2\ 4)$             |

| <del>&gt;</del>          | $(C \ 3)$               |

| ;no RHS actions)         | $(C\ 2)$                |

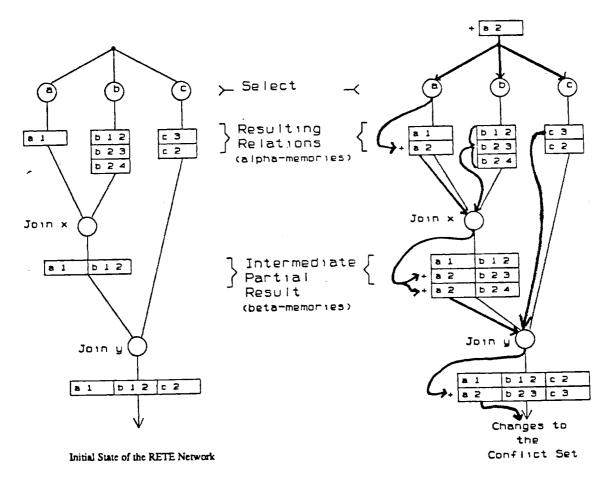

Figure 8: Example OPS5 rule system

suited to the capabilities of parallel machines. The syntax of OPS5 is very close to the description in the previous paragraph. See figure 8 for an example OPS5 rule and some relevant working memory elements.

The Development of the OPS5 Matching Algorithm Of the three steps in the production system cycle, the matching phase has proven in practice to be the most time-consuming. According to Forgy [Forgy 79], more than 90% of the execution time in a uniprocessor implementation is consumed by matching. On a sequential machine, the matching phase is an  $O(\|PM\| \|WM\|)$  process that compares the LHS of each production in the PM to every statement in the WM. Worse yet, each LHS can have a number of literals in the form of a conjunction. However, careful investigation by Forgy uncovered useful heuristics which can cut down the time spent in the matching phase. Forgy's RETE Match algorithm [Forgy 82] exploits two observations about OPS5:

- 1. Structural similarity: LHS's differ (syntactically) only slightly from each other (matching is speeded-up since changes to the WM can be easily traced to the LHS's they will affect).

- 2. Temporal redundancy: The WM changes very little from production cycle to production cycle (most matches do not have to be recomputed). Furthermore, the changes to WM have few effects on the conflict set.

Hence, a computational savings results if the LHS's of all rules in the production system are compiled into an "augmented discrimination network", or dataflow graph [Hwang 84], with state information saved at each node during execution. See figure 9 for an example RETE network (the rule and working memory elements were introduced on page 32.) The production system

Activity of the RETE Match During an Addition

Figure 9: An example RETE match network

interpreter can then incrementally compute the contents of the conflict set. A typical example is the R1 system [McDermott 82], which incrementally builds a solution to the VAX configuration problem. Production systems that search through large databases, such as ACE [Stolfo 82] or sensor-based systems, are not. McDermott, Newell and Moore conjectured (1978) that the cost of maintaining the state information exceeds the cost of comparisons that otherwise would have to be recomputed. Despite this, it is assumed that RETE is the best algorithm for production system matching.

The OPS-RETE Match Algorithm The RETE algorithm compiles the left-hand sides of production rules into a discrimination network. Changes to the working memory serve as the input to the network. The network, in turn, reports changes to the conflict set. The network contains two categories of nodes: test nodes and memory nodes. Additions or deletions to the WM are recorded

in memory nodes ( $\alpha$ -memories). A pointer to the change, called a *token*, is then replicated and passed to a number of entry points into the network. Once a token updates an  $\alpha$ -memory, it continues to propagate through the network. Following the  $\alpha$ -memories are tests nodes, called the *two-input test nodes*, which test for consistent variable bindings between two condition elements. If two tokens satisfy the test, a new token is formed at the output arc of the test node and stored in a token memory, called a  $\beta$ -memory. Tokens that propagate from terminal  $\beta$ -memories in the network (one terminal node per production) reflect changes to the conflict set.

## 4.2.3 Memory-Based Reasoning

The key operation in memory-based reasoning is weighted associative search for items in memory that are similar to a present case that one hopes to understand or act appropriately on [Waltz 87]. Once some matches have been found, they can suggest hypotheses. Other operations, which are based on statistics, test these hypotheses; to do so, they separate important features from unimportant ones. Waltz's example from the medical diagnosis domain should clarify things. It is assumed that the system has access to a large relational database of medical patient records. A memory-based reasoning program can find diagnostic hypotheses for a new patient as follows:

- 1. Load each of the processors with a database item (patient record)

- 2. Broadcast each feature of the new patient to all processors

- 3. Have each processor compute a numerical measure of closeness of its data record to each feature of the item under consideration and adding them up

- 4. Select from the database patients whose total scores are closest to that of the new patient