#### Through-Silicon-Via Inductor: Is it Real or Just A Fantasy?

Umamaheswara Rao Tida<sup>1</sup> Cheng Zhuo<sup>2</sup> Yiyu Shi<sup>1</sup>

<sup>1</sup>ECE Department, Missouri University of Science and Technology <sup>2</sup>Intel Research, Hillsboro

- Background and Motivation

- Micro-Channel Shield Technique

- Experimental Results

- Conclusions

- Background and Motivation

- Micro-Channel Shield Technique

- Experimental Results

- Conclusions

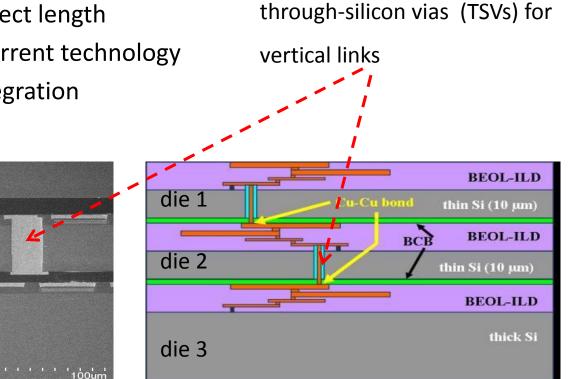

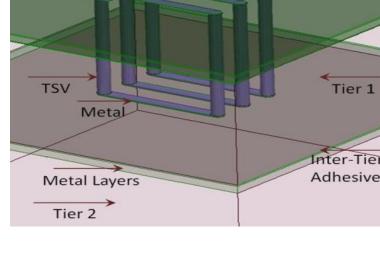

# **3D Integrated Circuits**

- 3D IC is considered one of the most promising alternatives at the limit of device scaling

- Reduced form factor

- Reduced interconnect length

- *Compatible* with current technology

- Heterogeneous integration

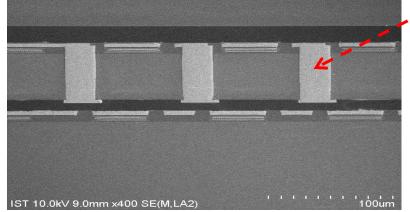

### The Curse of TSV Scaling

✓ TSV scaling limited by the wafer handling and alignment accuracy

✓ TSV diameter will not scale with logic gates

$\rightarrow$  50X diameter ratio, 2500X area ratio by 2015!

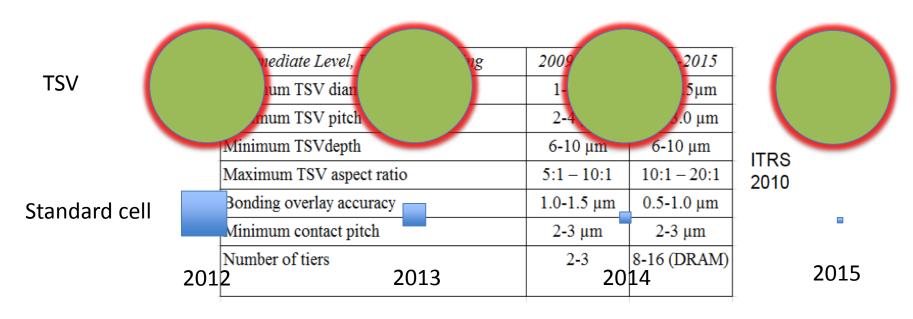

# **On-Chip Spiral Inductor**

- Low-noise amplifiers, power amplifiers

- voltage control oscillators

- voltage regulators

- DC-DC converters

- Substrate loss

- Large die area ( 78,400 um<sup>2</sup>) for practical purposes

- Consumes high routing area

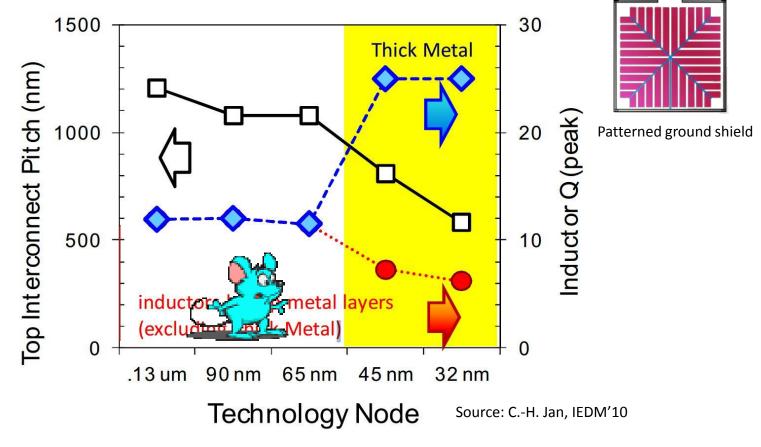

# The Curse of CMOS Scaling

Brought by scaling of the interconnect pitch and metal thickness

# How about 3D RF SOC?

- Subject to both curses?

Not necessarily!

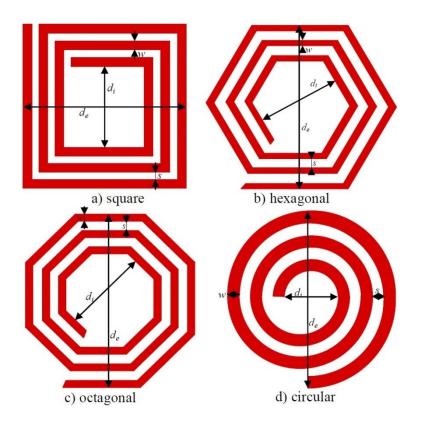

- Use dummy TSVs to make inductors

- Minimum footprint

- No special RF process

- Sounds fancy, but...

- Is it real or just a fantasy?

- New loss mechanism?

- New design freedom?

# **Prior Art and Motivation**

- The quality factor of the TSV inductor is significantly less than its 2D spiral counterpart, mainly due to the losses from the substrate.

- The entire TSV inductors is buried in the silicon substrate, which is lossy at high frequencies.

- Bontzios et al suggested that for 50 μm substrate thickness and below, TSV inductor should be used when area is the only concern.

- Is there any way that we can reduce substrate losses for TSV inductors?

# Contributions

- Novel shield technique using micro-channel.

- Experimental results states 21x and 17x increase of Q and L respectively.

- With this technique, TSV inductors can achieve up to 38x smaller area and 33% higher Q compared with spiral inductors.

- Background and Motivation

- Micro-Channel Shield Technique

- Results

- Conclusions

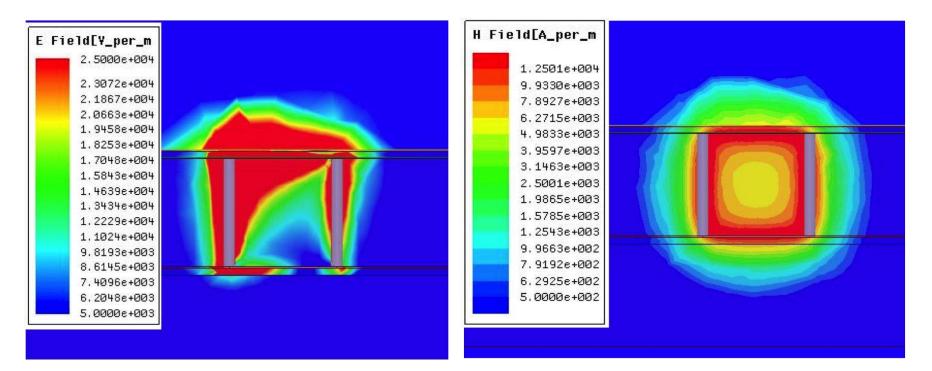

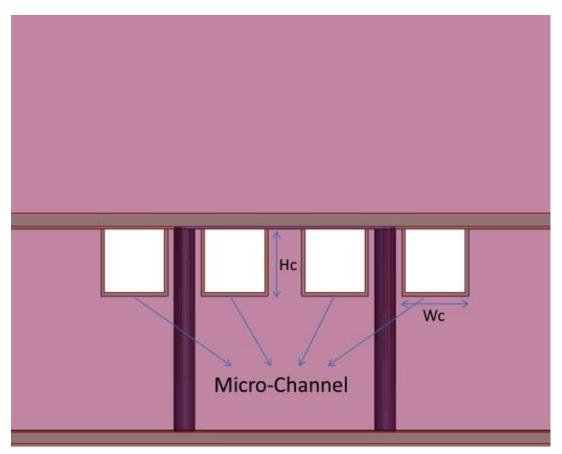

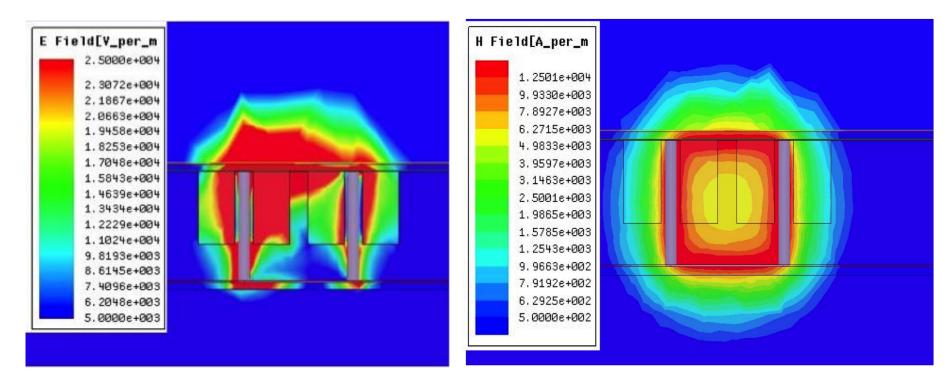

# **E Field and H Field without Shield**

- Much of the losses are near the inductor.

- Losses can be reduced if substrate near inductor is removed.

- Substrate is removed by using micro-channel technique.

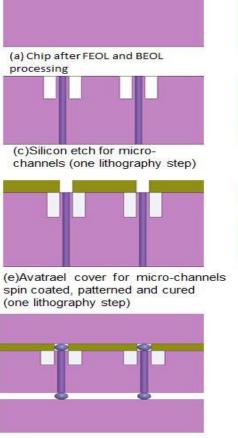

#### **Micro-Channel Fabrication Steps**

(g)Assemble chip on substrate

Adds little amount of cost due to two extra lithography steps.

(b)Electrical through via fabrication

(d)spin coat and polish a sacrificial polymer material

(f)Assemble chip on chip

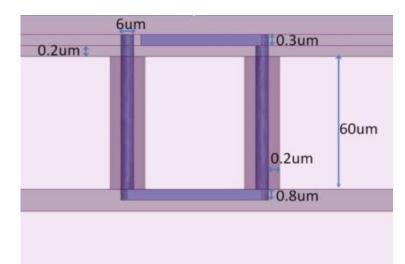

### **Micro-Channel Shields**

- 4 Micro-channels are placed 5um away from the TSV.

- When the TSV inductor is used as antenna, the micro-channels can help to cool it as well.

# E and H Field with Shield

- Losses are reduced due to the reduction of E-field in the substrate.

- Less effect on Inductance since no change in magnetic flux.

- Background and Motivation

- Introduction

- Micro-Channel Shield Technique

- Experimental Results

- Conclusions

# **Experimental Setup**

| Notation | Meaning              | Range         |

|----------|----------------------|---------------|

| Ν        | Number of turns      | 1-6           |

| Т        | Number of tiers      | 2-4           |

| P(µm)    | Loop pitch           | 13-23         |

| W(µm)    | Width of metal strip | 3-12          |

| f(GHz)   | Operating frequency  | 0.15, 1,5, 10 |

#### **Nominal Settings**

P=18um, W=6um, f=0.15, 1, 5, 10 GHz

#### voltage regulators

-

**RF** applications

----

## Improvement Using Micro-channel at Various Channel Dimensions

|                     |    | W <sub>c</sub> (um) |                |         |                 |       |       |  |  |  |

|---------------------|----|---------------------|----------------|---------|-----------------|-------|-------|--|--|--|

|                     |    |                     | Quality Factor |         | Inductance (nH) |       |       |  |  |  |

|                     |    | 10                  | 20             | 25      | 10              | 20    | 25    |  |  |  |

|                     | 10 | 6.71                | 6.92           | 7.03    | 1.396           | 1.395 | 1.394 |  |  |  |

|                     |    | (4.5%)              | (8.1%)         | (9.6%)  | 0.0%            | 0.0%  | 0.0%  |  |  |  |

| H <sub>c</sub> (um) | 20 | 7.02                | 7.29           | 7.46    | 1.393           | 1.390 | 1.390 |  |  |  |

|                     |    | (9.6%)              | (13.8%)        | (16.3%) | 0.0%            | 0.0%  | 0.0%  |  |  |  |

|                     | 30 | 7.34                | 7.34 7.76      |         | 1.391           | 1.386 | 1.384 |  |  |  |

|                     |    | (14.6%)             | (21.1%)        | (23.9%) | 0.0%            | 0.0%  | 0.0%  |  |  |  |

|                     | 40 | 7.73                | 8.28           | 8.59    | 1.388           | 1.386 | 1.382 |  |  |  |

|                     |    | (20.5%)             | (29.2%)        | (34%)   | 0.0%            | 0.0%  | 0.0%  |  |  |  |

|                     | 50 | 8.25                | 8.98           | 9.41    | 1.388           | 1.380 | 1.376 |  |  |  |

|                     |    | (28.8%)             | (40.1%)        | (46.1%) | 0.0%            | 0.0%  | 0.0%  |  |  |  |

|                     | 60 | 9.12                | 10.34          | 10.96   | 1.386           | 1.374 | 1.377 |  |  |  |

|                     |    | (42.2%)             | (61.4%)        | (71.0%) | 0.0%            | 0.0%  | 0.0%  |  |  |  |

- N=6, T=2, P=18um, W=6um and f=10 GHz

- Improvement over no shield case are shown in parenthesis.

# Maximum Q Improvement at 10 GHz

| Q |   | Т                |                   |                  |                  |  |  |  |  |  |

|---|---|------------------|-------------------|------------------|------------------|--|--|--|--|--|

|   |   | 2                | 3                 | 4                | 5                |  |  |  |  |  |

|   | 1 | 10.96<br>(5.88%) | 13.12<br>(14.5%)  | 14.53<br>(38.9%) | 14.90<br>(70.3%) |  |  |  |  |  |

|   | 2 | 11.36<br>(11.7%) | 11.31<br>(78.52%) | 7.59<br>(168%)   | 6.14<br>(359%)   |  |  |  |  |  |

| N | 3 | 11.89<br>(26.3%) | 9.15<br>(167%)    | 4.65<br>(406%)   | 2.00<br>(2034%)  |  |  |  |  |  |

|   | 4 | 11.89<br>(42.4%) | 7.46<br>(269%)    | 2.93<br>(1007%)  | 1.03<br>N/A      |  |  |  |  |  |

|   | 5 | 11.37<br>(55.3%) | 5.97<br>(371%)    | 1.87<br>N/A      | 0.19<br>N/A      |  |  |  |  |  |

|   | 6 | 10.98<br>(71%)   | 4.74<br>(483%)    | 1.01<br>N/A      | -2.08<br>N/A     |  |  |  |  |  |

- P=18um, W=6um, Wc and Hc are max

- An average of 2.5x improvement in Q

# Maximum Q Improvement at 1 GHz

|   | Q | Т              |                 |                 |                  |  |  |  |  |  |

|---|---|----------------|-----------------|-----------------|------------------|--|--|--|--|--|

|   |   | 2              | 3               | 4               | 5                |  |  |  |  |  |

|   | 1 | 4.29<br>(0.0%) | 3.74<br>(0.5%)  | 4.15<br>(1.0%)  | 4.44<br>(2.0%)   |  |  |  |  |  |

|   | 2 | 3.36<br>(0.0%) | 4.72<br>(3.2%)  | 5.37<br>(4.8%)  | 5.90<br>(9.9%)   |  |  |  |  |  |

| N | 3 | 3.76<br>(0.2%) | 5.28<br>(1.7%)  | 6.39<br>(15.8%) | 6.83<br>(36.4%)  |  |  |  |  |  |

|   | 4 | 4.02<br>(0.8%) | 6.04<br>(11.1%) | 7.11<br>(37.4%) | 7.57<br>(88.3%)  |  |  |  |  |  |

|   | 5 | 4.13<br>(0.1%) | 6.49<br>(17.8%) | 7.65<br>(67.0%) | 7.78<br>(153.0%) |  |  |  |  |  |

|   | 6 | 4.29<br>(2.7%) | 6.81<br>(26.5%) | 7.92<br>(98.5%) | 8.01<br>(235.1%) |  |  |  |  |  |

• P=18um, W=6um, Wc and Hc are max

# Maximum L Improvement at 10 GHz

| L (nH) |   |                 | Т                |                  |                  |

|--------|---|-----------------|------------------|------------------|------------------|

|        |   | 2               | 3                | 4                | 5                |

|        | 1 | 0.135<br>(0.0%) | 0.344<br>(0.0%)  | 0.577<br>(0.0%)  | 0.828<br>(1.2%)  |

|        | 2 | 0.344<br>(0.0%) | 0.958<br>(0.0%)  | 1.729<br>(0.0%)  | 2.708<br>(11.9%) |

| Ν      | 3 | 0.594<br>(0.0%) | 1.700<br>(0.0%)  | 3.523<br>(39.9%) | 5.882<br>(1615%) |

|        | 4 | 0.843<br>(0.0%) | 2.741<br>(1.0%)  | 5.959<br>(424%)  | 8.855<br>N/A     |

|        | 5 | 1.093<br>(0.0%) | 3.390<br>(2.2%)  | 8.577<br>N/A     | 3.055<br>N/A     |

|        | 6 | 1.376<br>(0.0%) | 5.206<br>(58.5%) | 10.634<br>N/A    | -3.518<br>N/A    |

- P=18um, W=6um, Wc and Hc are max

- Increased fSR brought by the shield.

# Q Factor and Area Comparison Between 2D Spiral Inductors and 3D TSV inductors

| D | Design Specs Spiral Inductor |      |          |      |      | TSV Inductor |          |                |   |   |      |      |        |        |                    |

|---|------------------------------|------|----------|------|------|--------------|----------|----------------|---|---|------|------|--------|--------|--------------------|

| # | f                            | L    | Geometry |      | А    |              | Geometry |                |   |   | Q    |      | А      |        |                    |

|   | (GHz)                        | (nH) | Т        | D    | d    | W            | Q        | (um²)          | Ν | Т | W    | Р    | w/o    | w/     | (um²)              |

|   |                              |      | (um)     | (um) | (um) | (um)         |          |                |   |   | (um) | (um) | Shield | Shield |                    |

| 1 | 1                            | 6.5  | 2        | 560  | 535  | 10           | 5.7      | 313,600<br>(1) | 6 | 2 | 7    | 20   | 4.6    | 7.6    | 8,255<br>(1/37.9x) |

| 2 | 5                            | 2.50 | 2        | 400  | 355  | 20           | 6.9      | 160,000<br>(1) | 4 | 3 | 6    | 18   | 4.3    | 10.3   | 9,358<br>(1/17.1x) |

| 3 | 10                           | 0.95 | 1        | 330  | 320  | 10           | 10.0     | 108,900<br>(1) | 2 | 3 | 6    | 18   | 5.8    | 10.1   | 4,679<br>(1/23.3x) |

- 38x area reduction.

- 33% Q improvement

- Background and Motivation

- Introduction

- Micro-Channel Shield Technique

- Experimental Results

- Conclusions

### Conclusions

- A micro-channel shield technique to drastically improve the quality factor and the inductance is proposed.

- 21x and 17x increase of Q and L respectively are observed using the technique.

- 38x smaller area and 33% higher Q compared with spiral inductors can be achieved with this technique for TSV inductors.

# Thank you!