# TiB<sub>2</sub> and ZrB<sub>2</sub> diffusion barriers in GaAs Ohmic contact technology

J. Shappirio, J. Finnegan, R. Lux, D. Fox, and J. Kwiatkowski U. S. Army Electronics Technology and Devices Laboratory, Fort Monmouth, New Jersey 07703

H. Kattelus and M. Nicolet

California Institute of Technology, Pasadena, California 91125

(Received 10 May 1985; accepted 17 June 1985)

The transition metal diboride compounds,  $ZrB_2$  and  $TiB_2$ , interposed between Ni/Ge/Au Ohmic contact metallization on *n*-type GaAs wafers and an overlying thick Au contact layer, have been investigated to evaluate their effectiveness in stabilizing the Ohmic contact by limiting the indiffusion of Au. All of the metal layers were e-beam deposited except the  $ZrB_2$  which was rf-diode sputtered. The barrier layer thicknesses were 50 and 100 nm for the  $TiB_2$  and the  $ZrB_2$ , respectively. Postdeposition alloying of the contacts was performed at 400, 425, or 450 °C. Auger electron spectroscopy depth profiling of the resultant Ohmic contacts demonstrates that the barrier layers effectively preclude penetration of Au to the Ohmic contact structure. Specific contact resistivities for such contacts are in the low  $10^{-7} \Omega \text{ cm}^2$  range; although some degradation of the contact resistivity is observed after long term annealing, the values of resistivities do not exceed  $1.5 \times 10^{-6} \Omega \text{ cm}^2$  after 92 h at 350 °C.

#### I. INTRODUCTION

A wide variety of metallization schemes have been investigated to provide reliable Ohmic contacts to III-V semiconductors in general, and to n-type GaAs specifically. The principle of these contacts is to produce a highly doped region at the surface of the GaAs in order to achieve a low contact resistance between the semiconductor and the contact metal. For n-type GaAs this is accomplished by choosing a metal composition which will alloy with the GaAs, and where one constituent of the metallization becomes a donor atom. The most widely studied and the most commonly applied Ohmic metallization consists of the eutectic Au-Ge alloy (88% Au) usually in combination with a Ni layer designed to minimize ball-up during subsequent alloying as well as to assist in the decomposition of the GaAs. Alloying of the metallization layers is required at temperatures in the range 400-500 °C for times ranging from seconds to several minutes to obtain contact resistivities on the order of  $10^{-6}$  $\Omega$  cm<sup>2</sup>. Numerous studies (cf. Braslau<sup>2</sup>) have established that the resultant contact is laterally and vertically nonhomogeneous. In addition, the thick Au overlayer normally deposited above the Ni/Ge/Au metallization in order to facilitate later device contacting provides a large reservoir of reactive material that contributes both to the increasing depth of the contact region by further in-migration of gold, as well as to contact instability during subsequent device processing and operation. Total penetration depth of such alloyed contacts may reach 200 nm. Such a depth is unacceptably high for Ohmic contacts in emerging GaAs field-effect transistor (FET) and high electron mobility transistor (HEMT) structures which may require contact depths less than 50-100 nm.

ZrB<sub>2</sub> thin films have been shown<sup>3</sup> to possess rather remarkable diffusion barrier properties when interposed between silicon and second-level aluminum metallization heat treated to temperatures of 625 °C for up to 2 h; since x-ray diffractometry indicates that as-deposited diboride films are amorphous, such films may function as diffusion barriers

owing to the absence of fast diffusion paths (grain boundaries) as suggested by Nicolet et al.<sup>4</sup> We report here, studies on the use of ZrB<sub>2</sub> and TiB<sub>2</sub> diffusion barriers between Ni/Ge/Au Ohmic contact metallization and overlying thick Au in order to evaluate their effectiveness in stabilizing Ohmic contacts by limiting the in-diffusion of gold.

### II. EXPERIMENTAL

GaAs wafers employed for this study were 560  $\mu$ m thick n-type Si-doped (100) orientation with a carrier concentration of 1-2×10<sup>18</sup>/cm<sup>3</sup>. Prior to Ni/Ge/Au Ohmic metal deposition, the wafers were washed with detergent, degreased sequentially in boiling electronic grade acetone, trichlorethylene, methanol, and acetone for 1 min each, etched in HCl to remove native oxide, and finally rinsed in deionized water. Ni/Ge/Au were sequentially e-beam evaporated in a deposition chamber prepumped to  $5 \times 10^{-8}$ Torr with Ni in contact to the GaAs and Au the final metal deposited. Total thickness of this metallization ranged from 25-100 nm; Au amounted to 85 wt. %, Ge 10.4%, and Ni 4.6% of the total metallization and the ratio of Au/Ge was selected to coincide with the eutectic alloy composition. Diffusion barrier layers of TiB<sub>2</sub> or ZrB<sub>2</sub>, 50-100 nm in thickness were next deposited. TiB2 was e-beam evaporated from a high purity, high density source material obtained from Eagle Picher in the same chamber and in the same pumpdown as the Ohmic contact metals and was followed by the e-beam deposition of 200 nm of gold without breaking vacuum. Alternatively, after Ohmic metal deposition, ZrB<sub>2</sub> was rf diode sputtered onto the samples followed by a 200 nm e-beam gold deposition.

Prior to metallization, samples were patterned for specific contact resistivity measurements by a liftoff process<sup>5</sup> starting with the deposition of CVD  $\mathrm{Si_3N_4}$  followed by spin coating of AZ1450J positive photoresist. The resist was prebaked at 90 °C and a series of various sized disks exposed on a Kasper 3000 contact aligner. To replicate the pattern in the  $\mathrm{Si_3N_4}$  film, the resist was developed and the  $\mathrm{Si_3N_4}$  was etched

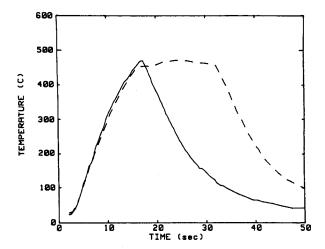

FIG. 1. Temperature-time profiles used to alloy Ohmic contacts. Solid line represents minimum alloy cycle; dashed line represents 15 s hold at alloy temperature.

in a (LFE Corp.) barrel plasma reactor using a  $CF_4/O_2$  gas mixture for 5 min at 150 W. The resist was then stripped in an  $O_2$  plasma and the wafers were recoated with AZ1450J and baked. A second contact mask with 100  $\mu$ m circular openings on 200  $\mu$ m center spacings was aligned concentrically with the previously developed disks and exposed as before. The resist was then soaked in chlorobenzene for 4 min and developed for 2.5 min in AZMF312 developer in preparation for the liftoff process. For the all e-beam evaporated metallizations, the resist was lifted off in acetone. For the sputtered  $ZrB_2$  films, the resist was soaked in acetone and then subjected to an oxygen plasma etch to fully remove the resist; this additional step was required because of damage to the polymer during the rf metal deposition.

After a preanneal nitrogen purge, both patterned and unpatterned metallized samples were alloyed to form Ohmic contacts in a Penzac furnace under flowing hydrogen gas. Peak anneal temperatures, measured by a thermocouple contacting the strip heater, were 417, 438, and 455 °C for periods up to 2 min. Reactions leading to the formation of Ohmic contacts were monitored by postanneal Auger electron spectroscopy depth profiling.

Typical annealing cycles, as shown in Fig. 1, consisted of an up-ramp to temperature followed by an immediate ramp down, or followed by a treatment at the maximum temperature for periods up to 2 min. Contact resistance was measured by a modification of the method of Cox and Strack.<sup>6</sup> Resistance was measured between five pairs of circular contacts ranging from 3 to  $50 \,\mu \text{m}$  diam with contact-to-contact spacing of  $200 \,\mu \text{m}$  deposited on  $560 \,\mu \text{m}$  thick n-GaAs. For this geometry, where the substrate thickness and contact spacing are large compared to the contact radius, and the spacing is not large compared to the thickness, the measured resistance is given by  $^7$

$$R_{\text{meas}} = \rho/2a + 2r_c/\pi a^2,\tag{1}$$

$$\pi a^2 R_{\text{meas}}/2 = \pi \rho a/4 + r_c, \tag{2}$$

where a is the contact radius,  $\rho$  is the substrate resistivity, and  $r_c$  is the specific contact resistivity. The term  $\rho/2a$  in Eq. (1) is an approximation to the spreading resistance in the GaAs. A numerical calculation of the spreading resistance using the method of Berkowitz and Lux<sup>8</sup> indicates the error of this approximation is 5% for the 50  $\mu$ m contacts and less than 1% for all others.

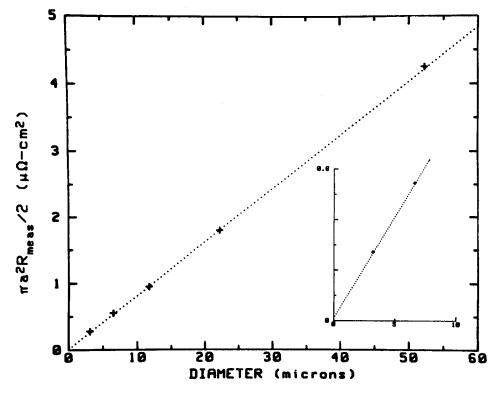

From Eq. (2), a plot of half the measured resistance times the contact area versus diameter then gives a straight line, with the y-intercept being the contact resistivity, as in Fig. 2. The major source of error is the accurate measurement of the diameter of the contact windows. To explore the effect of this error, we have artificially changed the value of all window diameters by  $+1 \mu m$ , or changed only the smallest window

FIG. 2. Typical plot of data in the form of Eq. (2) which is used to obtain the contact resistivity. The straight line is a least-squares fit to the data. The insert is an expansion of the plot near the origin.

TABLE I. Contact resistivity ( $\mu\Omega$  cm<sup>2</sup>).

| As-deposited<br>layer thicknesses(nm) | Peak temperature |       |        |

|---------------------------------------|------------------|-------|--------|

|                                       | 417 °C           | 438 ℃ | 455 °C |

| 25                                    | 0.1              | (2)   | (2)    |

| 50                                    | 0.5              | (2)   | (2)    |

| 75                                    | (1)              | 0.2   | (1)    |

| 100                                   | (1)              | 0.1   | 0.1    |

by the same amount, leaving all others fixed. The resultant recomputed contact resistivities varied at most by  $\pm 1 \times 10^{-7} \,\Omega$  cm<sup>2</sup>. In measuring the resistance, separate voltage and current probes were placed on the contact to eliminate the effect of probe resistance.

#### III. RESULTS

## A. Specific contact resistivity

Measurement of contact resistivity was made for four thicknesses of Ni/Ge/Au metallization of 25, 50, 75, and 100 nm, covered with 50 nm  ${\rm TiB_2}$  and 200 nm Au. Three alloying cycles were used consisting of a ramp up to maximum temperature and an immediate ramp down. The total alloying cycle was approximately 50 s in duration as shown in Fig. 1. The results of these measurements are shown in Table I.

For several combinations of alloying temperature and film thickness, the results did not fall on a straight line, thus precluding the determination of the contact resistivity. Two types of failures were observed: (1) failure of most or all of the 3 and 6  $\mu$ m contacts to form Ohmic contacts, and (2) anomalously high resistance in the 3 and 6  $\mu$ m contacts, well off the line extrapolated from the other contacts. Type (2) failures may be the result of incomplete removal of the resist from the contact openings.

The lowest measured contact resistivities are lower than reported in the literature. We attribute these differences to a difference in measurement techniques. It has been shown that the transmission line model (TLM) and Kelvin tech-

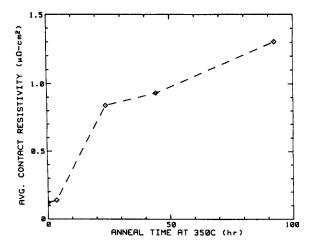

FIG. 3. Contact resistivity vs anneal time at 350 °C for contacts consisting of 100 nm Ni/Ge/Au capped by 50 nm TiB<sub>2</sub> and 200 nm Au alloyed at 450 °C with minimum ramp times.

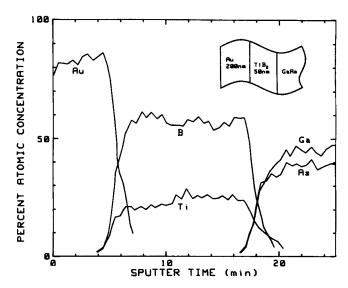

FIG. 4. Auger electron spectroscopy sputter depth profile through 200 nm of Au over 50 nm of e-beam evaporated TiB<sub>2</sub> aged at 500 °C for 3.5 h.

niques as commonly used determine an effective contact resistivity which for small resistivities can be greater than the true contact resistivity by a large factor. <sup>9,10</sup> For the present discussion of barrier layers, only the relative values of contact resistivity are significant.

## **B.** Contact aging

The deterioration of Ni/Ge/Au Ohmic contacts under long term thermal stress has been reported by Marlow et al. <sup>11</sup> To investigate this effect a group of contact patterns consisting of 100 nm of Ni/Ge/Au capped by 50 nm TiB<sub>2</sub> and 200 nm Au were alloyed at 450 °C with minimum ramp time up and down. The contacts were then annealed up to 92 h at 350 °C with periodic measurements of contact resistivity. The results, shown in Fig. 3, indicate a rapid deterioration of the contact resistivity after 3.5 h followed by a longer period of slowly increasing contact resistivity as was seen by Macksey. <sup>12</sup> The contact resistivity at 92 h did not exceed  $1.5 \times 10^{-6} \Omega$  cm<sup>2</sup>. We attribute this performance to the effectiveness of the diboride layer in blocking in-migration of Au and out-migration of Ga.

#### C. Barrier effectiveness

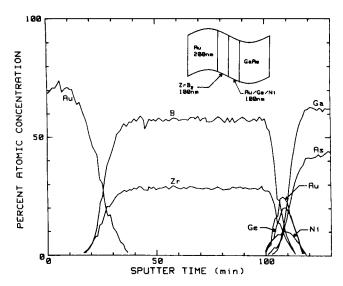

The efficiency of the "amorphous" diboride thin film diffusion barrier in preventing Au in-migration to the evolving Ohmic metallization can be estimated from the Auger data shown in Figs. 4 and 5. Figure 4 is an AES sputter depth profile through 200 nm of Au over 50 nm of TiB<sub>2</sub> e-beam evaporated onto GaAs and heat treated for 3.5 h at 500 °C. Figure 5 shows an AES profile through 200 nm Au over 100 nm of rf-diode sputtered ZrB<sub>2</sub> over 100 nm total thickness of Ni/Ge/Au on GaAs and alloyed at 450 °C for 2 min. In the case of the TiB<sub>2</sub> film shown in Fig. 4, the heat treatment conditions are far more severe than those typically employed in conventional GaAs Ohmic contact technology where temperatures are typically below 500 °C and alloy times are measured in seconds; in contrast, the conditions employed for the ZrB<sub>2</sub> example are generally consistent with standard processing. The important observation in both cases is clear,

2258

Fig. 5. Auger electron spectroscopy sputter depth profile through 200 nm of Au over rf-diode sputtered ZrB2 over 100 nm total thickness of Ni/Ge/Au on GaAs, alloyed at 450 °C for 2 min.

namely that thin film diboride diffusion barriers are extremely effective in blocking the in-migration of Au. In the absence of such a blocking layer an already established metallization structure achieved by some preselected alloying scheme could be further modified by the supply of additional, reactive gold to that interface, during either subsequent elevated device processing temperature, or by heat generated during the operation of a high power device. Furthermore, the abruptness of the Au/ZrB<sub>2</sub> and Au/TiB<sub>2</sub> interfaces which we observe suggests strongly that even thinner diffusion barrier layers, perhaps as thin as 10 nm or less, would function effectively for this purpose. The minimum thickness required for such diboride barriers is presently under investigation.

## IV. CONCLUSIONS

Ni/Ge/Au Ohmic contact metallizations at the lower limit of or thinner than those conventionally employed in the industry have been alloyed on n-type GaAs and the contact resistivity for such contacts has been measured. The contact resistivity values which we obtain, in the low  $10^{-7} \Omega \text{ cm}^2$ range, are consistent with or better than those previously reported in the literature, and are adequate for successful use in device applications. Although some degradation of contact resistivity has been observed on long term annealing, values of resistivity do not exceed  $1.5 \times 10^{-6} \Omega$  cm<sup>2</sup>. Interposed diffusion barriers of e-beam evaporated TiB2 and of rfdiode sputtered ZrB<sub>2</sub> have been shown to limit the in-migration of gold from a top contacting layer of gold, and should improve the long term stability of the contacts. Effectiveness of such barriers has been demonstrated for thicknesses down to 50 nm, and the data suggest strongly that even thinner barriers should function with equal success.

#### **ACKNOWLEDGMENTS**

The cooperation of M. Wade, D. Eckart, L. Heath, D. Troy, and T. AuCoin is appreciated.

- <sup>1</sup>R. E. Williams, Gallium Arsenide Processing Techniques (Artech House, Dedham, MA, 1984), pp. 231-233.

- <sup>2</sup>N. Braslau, in *Interfaces and Contacts*, MRS Symposium Proceedings, edited by R. Ludeke and K. Rose (North Holland, New York, 1982), p. 393.

- <sup>3</sup>J. Shappirio, J. Finnegan, R. Lux, and D. Fox, Thin Solid Films 119, 23 (1984)

- <sup>4</sup>M.-A. Nicolet, I. Suni, and M. Finetti, Solid State Technol. 25, 129 (1983). <sup>5</sup>M. Hatzakis, B. J. Canovello, and J. M. Shaw, IBM J. Res Dev. 24, 452 (1980)

- <sup>6</sup>R. H. Cox and H. Strack Solid State Electron. 10, 1213 (1967).

- <sup>7</sup>P. Severin, in Semiconductor Measurement Technology: Spreading Resistance Symposium, NBS Special Publication, edited by J. Ehrstein (U.S. GPO, Washington, D.C., 1974).

- <sup>8</sup>H. Berkowitz and R. Lux, J. Electrochem. Soc. 128, 1137 (1981).

- <sup>9</sup>H. H. Berger, Solid State Electron. 15, 145 (1972).

- <sup>10</sup>M. Finneti, A. Scorzoni, and G. Soncini, IEEE Electron Device Lett. EDL-5, 524 (1984).

- <sup>11</sup>G. S. Marlow, M. B. Das and L. Tongson, Solid State Electron. 26, 259 (1983).

- <sup>12</sup>H. M. Macksey, Inst. Phys. Conf. Ser. 33b, 254 (1977).