#### 1

# Time-encoding analog-to-digital converters: bridging the analog gap to advanced digital CMOS – Part 1: Basic principles

Georges Gielen, Luis Hernandez, Pieter Rombouts

This document is an author's draft version submitted for publication in IEEE Solid State Circuits Magazine, The actual version was published as:

Georges Gielen, Luis Hernandez and Pieter Rombouts. "Time-Encoding Analog-to-Digital Converters: Bridging the Analog Gap to Advanced Digital CMOS-Part 1: Basic Principles." IEEE Solid-State Circuits Magazine 12.2 (2020): 47-55.

#### 1

# Time-encoding analog-to-digital converters: bridging the analog gap to advanced digital CMOS – Part 1: Basic principles

Georges Gielen, Luis Hernandez, Pieter Rombouts

# I. MOTIVATION FOR TIME ENCODING

The scaling of CMOS technology deep into the nanometer range has created challenges for the design of high-performance analog integrated circuits. The shrinking supply voltage and the presence of mismatch and noise restrain the dynamic range, causing analog circuits to be large in area and have a high power consumption in spite of the process scaling. Analog circuits based on time encoding [1], [2] and hybrid analog/digital signal processing [3] have been developed to overcome these issues. Realizing analog circuit functionality with highly digital circuits results in more scalable design solutions that can achieve excellent performance. This article reviews the basic principles of time encoding, in particular applied to analog-to-digital converters (ADCs) based on Voltage-Controlled Oscillators (VCOs), one of the most successful time-encoding techniques to date. Although VCO-based ADCs have been around for a long time [4], [5] they really received a significant boost in interest after Straayer and Perrotts highly cited 2008 paper [6]. Since then, many other advancements from different research groups worldwide have been published, in application domains such as sensor readout [7]–[10], telecom [11]–[13], wideband wireless [14]–[18], Internet of Things [19], automotive [20], [21], biomedical [22]–[24], to name a few. Note that the integrating properties of VCOs have also been used to implement continuous-time filters, time to digital converters and other analog signal processing blocks [25]–[27].

This overview article is divided in two parts. This first part will introduce the basic principles of time encoding with emphasis on VCO-based ADCs, and will compare them to traditional analog circuits. The follow-up article (part 2) will describe and compare different time-encoding circuit architectures for analog-to-digital converters, and will discuss the corresponding design challenges of the building blocks. Together, they will demonstrate how time-encoding circuits can overcome many of the problems encountered when designing high-performance analog circuits that fully take advantage of advanced digital CMOS technologies, rather than suffering from it, hence bridging the analog gap to advanced CMOS.

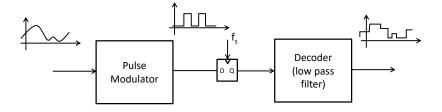

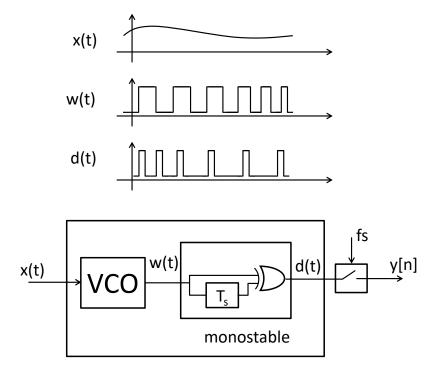

The main idea behind time encoding consists of representing an analog signal with a modulated square wave, where the signal information is encoded in the transitions instead of the instantaneous amplitude. Such a signal is easy to handle with digital circuits and is robust against noise and distortion. Representing the signal is then done through pulse modulations, known since long ago. Pulse Width Modulation (PWM) is one of the best examples, and used extensively in, for instance, power electronics. The typical block diagram of a time-encoding ADC is shown in Fig. 1. The analog input signal is applied to a pulse modulator that encodes the information in the pulse width, frequency or position of a signal (or set of signals) with two levels only. This two-level signal, which is still analog, is sampled afterwards at a sampling frequency  $f_s$ , typically much larger than the input signal bandwidth ABW. Differently from conventional ADCs, the sampler can now be a simple flip-flop, as the signal has only two values. From the sampled square wave, a decoder can reconstruct a multi-bit approximation of the analog input signal, which is typically done with a digital low-pass filter.

Although early time-encoding ADCs used PWM [1], [2], PWM may not be the best to replace analog circuits in an ADC. Indeed, PWM modulators require sawtooth generators or analog filters, still made of operational amplifiers and other highly linear circuits [28], [29]. VCO-based ADCs, on the other hand, can be implemented very efficiently with a ring oscillator,

Georges Gielen (KU Leuven), Luis Hernandez (Univ Carlos III Madrid), Pieter Rombouts (Ghent University). This work was supported by MCINN project TEC2017-82653-R, Spain and by the Fund for Scientific Research Flanders (FWO-Vlaanderen), Belgium.

Fig. 1. Principle signal operations in a time-encoding ADC.

which is a simple digital circuit [30], [31]. To be precise, VCO-based ADCs need to be modeled using a different type of pulse modulation, called Pulse Frequency Modulation (PFM). PFM exhibits first-order noise shaping when sampled directly, contrary to other pulse modulations like PWM. The hardware simplicity and digital nature of ring oscillators and the noise-shaping properties of PFM are the reasons why VCO-based ADCs have gained large popularity. We will therefore concentrate most of our discussion on VCO-based ADCs.

## II. VCO-BASED ANALOG-TO-DIGITAL CONVERSION: BASIC PRINCIPLES

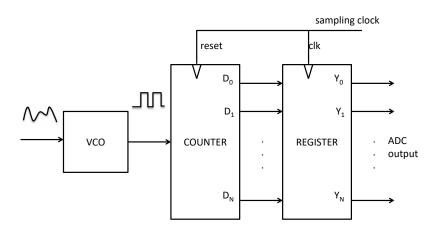

Fig. 2. Conceptual block diagram of an open-loop VCO-based ADC with counter.

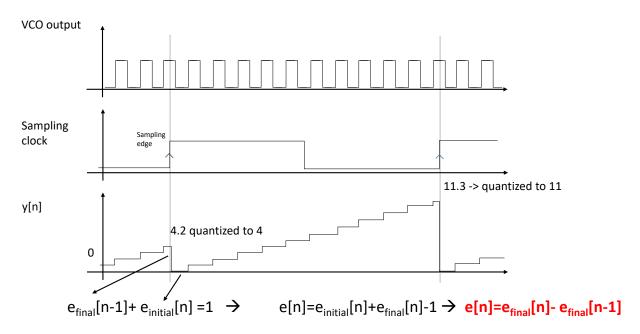

So how do VCO-based ADCs digitize an analog signal? We will give an intuitive explanation of its functioning without detailed mathematics. Fig. 2 depicts the simplest VCO-based ADC architecture, which is also one of the most used. A slowly varying input signal modulates the frequency of an oscillator (the VCO). The pulses of the oscillator are then counted with a digital counter. Assuming a sampling period  $T_s = 1/f_s$ , the number of pulses accumulated in the counter is dumped into a register every  $T_s$  seconds and the counter is reset. The value in the register is therefore a measure of the VCO frequency and hence of the analog input signal during that sample. Clearly, the higher the oscillation frequency compared to the sampling frequency, the higher the resolution that can be achieved. This defines an important design relation in VCO-based ADCs: the resolution is proportional to the oscillator frequency relative to the sampling frequency (which corresponds to the number of quantization bits in a traditional amplitude-based ADC). In addition, if the input signal is oversampled beyond Nyquist, the sampling period  $T_s$  is shorter and apparently there would be fewer counts in the counter, resulting in a lower resolution. However, the reality is the opposite: the error introduced by quantizing the frequency of the oscillator into an integer number (the count) is first-order noise shaped. Just realize that the error obtained after and before sampling in the middle of a VCO oscillator cycle always adds to one cycle. This fact is illustrated in Fig. 3, which shows that the quantization error can be written as the first-order difference of a finite-power sequence. This first-order noise shaping in combination with oversampling and digital decimation after the counter improves the signal-to-quantization-noise ratio (SQNR) much more than increasing the oscillator frequency. The following approximate equation gives the maximum SQNR of a VCO-based ADC with analog

signal bandwidth ABW, sampling frequency  $f_s$  and oscillator rest frequency  $f_0$  [32]:

$$SQNR[dB] \approx 6 \log_2\left(\frac{2f_0}{f_s}\right) - 5.17 + 9 \log_2\left(\frac{f_s}{2ABW}\right) \tag{1}$$

This equation shows that the SQNR improves with 6 dB every time the VCO frequency  $f_0$  is doubled relative to the sampling frequency  $f_s$ , as the quantization resolution is increased by one bit. If the oversampling ratio is doubled in addition to the quantization resolution, i.e. the sampling frequency  $f_s$  is doubled together with the oscillator frequency  $f_0$ , the SQNR improvement is 9 dB. An additional consequence of this dependency is that, if the sampling frequency  $f_s$  is doubled for a fixed oscillator frequency  $f_0$ , the SQNR is improved by 3 dB. Therefore, the choice of the oscillator frequency and the sampling frequency allows to optimize the SQNR.

Fig. 3. Signal behavior in the VCO-based ADC of Fig. 2 with illustration of the noise shaping. The latter is due to the fact that the error  $e_{\text{final}}$  injected at the end of a counting cycle combined with the error  $e_{\text{initial}}$  at the beginning of the next counting cycle always add up to 1 LSB.

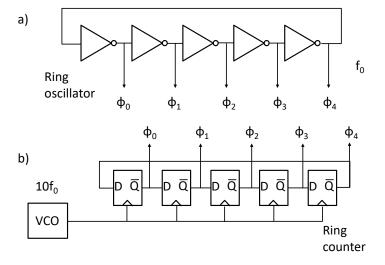

Fig. 4. Comparison of a ring oscillator with an oscillator and counter.

The typical VCO-based ADC circuit used in practice differs from the conceptual circuit of Fig. 2, although in the end it performs the same function. The difference lies in how the counter is implemented. Most VCO-based ADCs are implemented with a ring oscillator, which is a circuit that produces many similar square wave signals slightly shifted in time. Fig. 4(a) compares a 5-tap ring oscillator made of inverters and oscillating at a frequency  $f_0$  with an equifunctional circuit in Fig. 4(b) where an oscillator oscillating at  $10f_0$  is connected to a 5-tap ring counter: the outputs of both circuits are exactly the same signals. Therefore, the ring oscillator itself suffices to implement the whole system of Fig. 2 in a very compact and power-efficient way. Fortunately, as a practical implementation, the circuit of Fig. 5 allows a very easy way to measure the count increment without the need to reset the counter at every sampling clock cycle. Thanks to modulo arithmetic, this circuit encodes with minimal hardware the number of both rising and falling edges of the oscillator in a thermometric code at every clock instance. And here is the beauty of VCO-based ADCs: a many-bit, 1st-order noise-shaped sequence is obtained with only a few digital logic gates and no opamps!

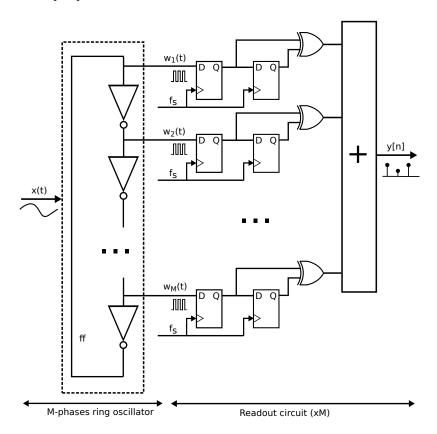

Fig. 5. Practical implementation of an open-loop ring oscillator VCO-based ADC with multi-phase readout.

Fig. 6. Phase-referenced model of a VCO-based ADC.

Since early VCO-based ADC converters were seen as alternative implementations of Delta-Sigma modulators, the explanation given for the functioning of VCO-based ADCs can also be deducted from common Delta-Sigma modulator understanding. The

block diagram of Fig. 2 can be described in terms of the oscillator phase (see Fig. 6) in a way that resembles the equations of a multi-bit first-order Delta-Sigma modulator [14], [32]. In Fig. 6, a VCO with conversion gain  $k_{VCO}$  is modulated in frequency by the input signal x(t). The phase of the VCO,  $\phi(t)$ , has a linearly growing component due to the rest angular frequency  $\omega_0$  (dotted line in Fig. 6) and a slowly varying additive component representing the integral of x(t). The physical output of the VCO, however, is a square signal (or a set of square signals in a ring oscillator); therefore only phase advancement in discrete steps can be noticed, coincident with the square signal edges. The VCO output is then sampled into a discrete sequence by a flip-flop with sampling period  $T_s$ . The quantized and sampled phase  $\phi_q[n]$  can therefore be modeled by adding a quantization noise component q[n]. The effect of the XOR gates in Fig. 5 is equivalent to computing the first-order difference of  $\phi_q[n]$ . Hence, the following equations are obtained:

$$\phi_q[n] = \omega_0 n T_s + k_{VCO} \int_{-\infty}^{nT_s} x(\tau) d\tau + q[n]$$

(2)

$$y[n] = \phi[n] - \phi[n-1] \tag{3}$$

$$= q[n] - q[n-1] + \omega_0 T_s + k_{VCO} \int_{(n-1)T_s}^{nT_s} x(\tau) d\tau$$

(4)

As can be seen, the output sequence y[n] contains the input signal x[t] averaged over each sampling period, plus the quantization noise that is indeed first-order shaped.

# III. VCO-BASED ANALOG-TO-DIGITAL CONVERSION: DIVING DEEPER

There are, however, some tricky questions that trigger a deeper dive. For instance, how does the VCO rest frequency  $f_0$  affect the quantization noise? Also, the behavior of the VCO-ADC is poorly modeled for large signals due to discrete tones in the output spectrum, similar to a 1st-order Delta-Sigma modulator. A different point of view is obtained by going back to the basics of Pulse Modulation theory [33], [34]. Fig. 7 shows how a VCO-based ADC can be expressed as the reference model of the time-encoding ADC of Fig. 1. The analog input signal x(t) modulates the frequency of the VCO that generates the square wave w(t). The signal w(t) is applied to the monostable circuit that generates the signal d(t), having a square pulse of fixed width  $T_s$  at every time instance where w(t) has an edge. According to [35], the signal d(t) is a Pulse Frequency Modulated representation of x(t). In case x(t) is a sinewave, the spectrum of d(t) can be calculated analytically. Fig. 7 also shows a possible implementation of the monostable circuit that produces d(t). It consists of the XOR operation between w(t) and itself delayed over  $T_s$  seconds. This circuit in the end is the same as used in Fig. 4, if we move the flipflops that implement the first-order difference right before the sampling operation. Fig. 7 therefore unveils how the PFM analysis is connected to the phase-referenced model.

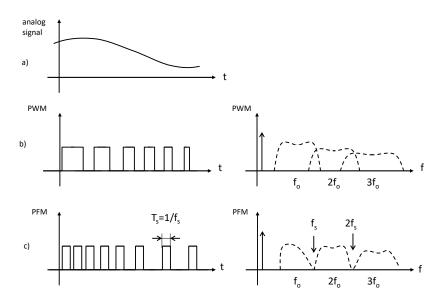

The spectrum of a pulse-modulated signal has a quite similar structure across different modulation types: it is composed of the input signal plus a modulated carrier at high frequency with modulation sidebands repeated around the harmonics of the carrier. For instance, Fig. 8(a) shows (part of) a slow sinusoidal input signal. Fig. 8(b) shows the PWM-encoded signal as a function of time (left) and the corresponding frequency spectrum (right), where the modulation sidebands have a spectrum envelope described by Bessel functions like in analog FM modulation. If the PWM signal is sampled, these modulation sidebands alias to lower frequencies in the form of quantization noise. Since VCO-based ADCs can be seen as Pulse Frequency Modulators (PFM), as described above, the frequency of the oscillator is modulated with the input and the edges are detected with the counter or an XOR function (as in Fig. 7). The carrier in this case is the rest oscillation frequency of the VCO. Pulse Frequency Modulation has a very special property: the modulation sidebands have periodic nulls in the frequency spectrum. Fig. 8(c) shows the same sinusoidal signal of Fig. 8(a) encoded with PFM in the time domain (left) and its corresponding spectrum in the frequency domain (right). The PFM time signal has many copies of the same pulse width  $T_s$ , occurring very frequently or only sparsely depending on the input signal amplitude. As long as the pulse width is always the same, signal theory predicts nulls in the periodic spectrum at frequencies corresponding to multiples of the inverse of the pulse width  $1/T_s$ . These periodic nulls arise from the sinc-shaped spectrum of the pulses composing the PFM signal. If this pulse width is forced to be the sampling period, then all carrier sidebands alias after sampling, replicating the nulls at DC, and hence creating the first-order

Fig. 7. Time-encoding equivalent of a VCO-based ADC.

noise shaping. This insight enables an accurate description of the more subtle behavior of VCO-based ADCs beyond the predictions of Delta-Sigma theory. For instance, it fully allows to understand the large-signal behavior and the occurrence of spurious baseband tones [34].

Fig. 8. Time-domain waveforms and frequency spectra of a PWM- and PFM-modulated analog signal.

# IV. CIRCUIT DESIGN GUIDELINES

With the basic principles and functioning of a VCO-based ADC explained, we can now describe the major design requirements for the circuit implementation, in particular noise and distortion, as well as the impact on the design flow.

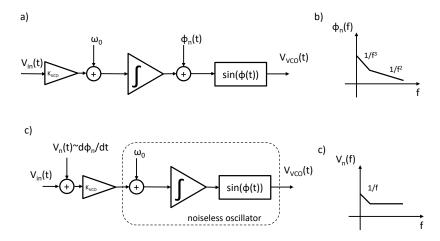

Fig. 9. Output- and input-referred modeling and corresponding spectra of phase noise in a VCO.

# A. Noise

Analog ADC designers are used to calculate the input-referred noise of an ADC and to balance it properly with the quantization noise in order to optimize the power consumption of the ADC. This balance, however, tends to be a bit more tricky in VCO-based ADCs because the dominant noise typically comes from the VCO and noise in VCOs manifests itself as (output) phase noise [36]. Phase noise is described as the random fluctuation of the phase of an oscillator. Phase noise in ring oscillators has been the subject of many publications, including [30], [36], [37]. The root cause for phase noise is the thermal and flicker noise in the resistors and transistors used in the VCO. Phase noise is displayed as an additive component  $\Phi_n(t)$  in the block diagram of Fig. 9(a) representing an oscillator modulated by a signal  $V_{in}(t)$ . Powerful simulation methods based on periodic noise analysis have been developed to predict the phase noise of an oscillator circuit, which typically has the shape of the Leeson model (see Fig. 9(b) [36]). As it is difficult to infer how such noise spectrum affects the SNR of the ADC, the VCO phase noise should be referenced to the VCO input (as in Fig. 9(c)). Referencing the VCO phase noise to the input makes the design process similar to designing any analog block [38], as the VCO's input-referred noise shows thermal and flicker noise components like any conventional analog circuit. A more straightforward approach is to use transient noise simulations, but this makes the design process very long and non-intuitive, and hence should only be done in the final design iteration [38].

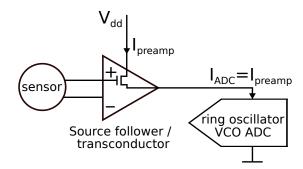

Fig. 10. VCO-based instrumentation system as application illustration.

In order to better understand the thermal noise trade-offs in the design of a VCO-based ADC system, consider as illustration the VCO-based instrumentation system shown in Fig. 10. Here, the VCO is driven by a transistor preamplifier either in current mode (by a transconductor Gm) or in voltage mode (by a source follower). Now suppose that the system is functional (with a correctly biased preamplifier, etc.), but that the noise of the system has to be reduced. This can be achieved by increasing the width of the input transistor and additionally increasing the widths of all the transistors in the ring oscillator. In this way, well established analog impedance scaling techniques are followed, sacrificing a factor of two in power for a 3 dB reduction in

circuit noise (and hence a 3 dB improvement in SNR in a circuit-noise-limited design). This is exactly the same scaling law as in conventional analog circuits, as also reflected in the typical Figure of Merit (FoM) used for ADCs<sup>1</sup>. As an additional perk of most VCO-based ADCs, the circuit of Fig. 10 shows that the main current driven by the Gm stage or the source follower is also supplying the ring oscillator, which means that the biasing current in the preamplifiers is shared by the active portion of the ADC, hence improving the power efficiency.

Flicker noise is also a major concern in low-bandwidth instrumentation applications. Detailed analysis of the noise in ring oscillators [30], [36], [37] has shown that flicker noise decreases proportionally to the number of oscillator taps. Loosely speaking, it is as if flicker noise is produced by a very large transistor, adding all areas of the inverters in the ring. Therefore, if low flicker noise is desired, many taps must be used in the ring oscillator. This, however, complicates the digital circuitry because more digital signals need to be sampled and processed. This shows how power is traded off between the analog and digital portions of the ADC. An important design option to reduce the impact of flicker noise in a sensing application is to use chopping [39], as will be discussed in part 2 of this paper.

# B. Distortion

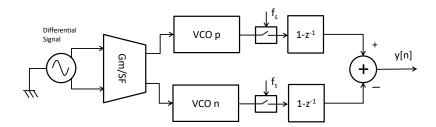

A huge challenge for VCO-based ADC design is the nonlinearity of the VCO characteristic. Differently from closed-loop feedback systems such as Delta-Sigma modulators, any nonlinearity in the voltage to frequency translation of the VCO used in a structure like Fig. 5 immediately degrades the SNDR of the ADC. Most of the different VCO-based ADC architectures that will be reviewed in part 2 of this article have as purpose to desensitize the ADC with respect to the VCO nonlinearity. If the input swing is small, in many cases a ring oscillator VCO can already be sufficiently linear. A standard practice to improve the distortion performance by removing even-order distortion, is to use a pseudo-differential VCO configuration (see Fig. 11), driving twin VCOs with differential input signals. This structure also has the benefit of achieving excellent PSRR values way above common belief [9]. Alternative solutions aim at limiting the signal swing using canceling feedforward paths or closed-loop feedback structures, as will be discussed in part 2.

Fig. 11. Pseudo-differential VCO-based ADC configuration.

# C. Design process

This takes us to a final challenge: a key problem for VCO-based ADCs is the design process itself. ADC designers usually have a background in analog circuits (e.g. capacitor-based SAR converters or Delta-Sigma modulators), and typically have little experience with ring oscillators. Phase-Locked Loop (PLL) designers might be better prepared for the job, but the kind of VCOs that they are used to design, may not be the best suited for VCO-based ADCs. A good practice is to think of the VCO as if it were an amplifier for the input signal. If one wants good noise in the ring oscillator: use large transistors [37]. If one wants improved linearity: use a differential circuit. Two oscillators with large transistors may cost power to obtain a high oscillation frequency, but then again: this is a way to save lots of biasing circuits, power-hungry opamps, capacitors and switches. ADC designers have also gotten used to minimizing the importance of digital hardware in the power budget, but in VCO-based ADCs the digital power is really significant and there may be digital logic running much faster than the sampling rate. In summary, designing time-encoding VCO-based ADCs is quite different from designing standard ADCs, and therefore requires some open-mindedness from the ADC designers.

$<sup>^{1}</sup>$ FOM = SNDR + 10 log10(BW/Power)

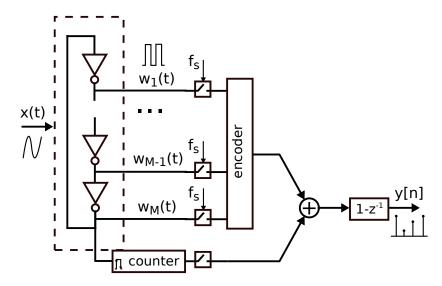

Fig. 12. Practical realization of an open-loop VCO-based ADC structure with multi-phase readout based on coarse/fine phase quantization.

# V. PRACTICAL DESIGN EXAMPLE

To illustrate the above concepts and as example of the different design methodology needed for VCO-based ADCs, we now describe the circuit shown in [9], which is intended for audio applications. It is a very simple VCO-based ADC, yet it shows the full potential of time encoding. The core of the ADC consists of two twin VCOs implemented with 11-phase ring oscillators. The VCOs are driven by a differential transconductor, that isolates the VCOs from the input, which in this case is a high-output-impedance MEMS microphone. All current used by the transconductor is at the same time powering the VCOs (see Fig. 10). The transistors in the ring oscillator have widths in the order of  $30\mu$ m. This large transistor size compared to what would be used for this frequency in a PLL, is needed to satisfy the input-referred noise requirement relative to the quantization noise of the converter (in the order of a few  $\mu$ V). The chip uses the multi-phase readout circuit shown in Fig. 12 to count the edges in the ring oscillator phases  $W_1...W_M$  with as little power as possible. The multi-phase readout circuit is implemented with a Gray counter connected to a reference phase providing a coarse quantization code, and an encoder block that refines the total edge count from samples of the ring oscillator state. The encoder block operates at the sampling clock (2.4MHz in this case), much slower than the coarse counter (approx. 50MHz). The digital and analog power consumption are each about half of the total power. The pseudo-differential architecture pays off in distortion mitigation (the peak SNDR is 70dB in 20kHz of bandwidth without feedback) and in very good power-supply rejection (which exceeds 80dB in spite of the poor inherent power-supply rejection of a single VCO channel).

# VI. TAKEAWAY POINTS

- Time-encoding VCO-based ADCs are an interesting ADC architecture in deeply scaled CMOS technologies, as they mostly

use digital circuits and frequency-encoded square wave signals rather than voltage or current linear circuits, resulting in

a small area and a good power efficiency.

- Open-loop VCO-based ADCs resemble closed-loop Delta-Sigma modulators in the sense that they behave as first-order

multi-bit Delta-Sigma modulators. The key system-level design parameters to achieve a target SQNR performance are the

rest oscillation frequency and the sampling frequency. Here, the phase-domain model (Fig. 6) and the corresponding SNR

equation (1) should be the start of your first design iteration.

- To understand more subtle system-level effects (such as overloading and spurious baseband tones), Pulse Frequency Modulation theory is needed.

- To get good distortion and PSRR performance, always a twin setup with two pseudo-differentially driven VCOs should

be used in the basic configuration. In part 2 of this paper, more complex architectures for even better performance will

be discussed.

• To design the core VCO, a PLL design style is not the best approach. Instead, it is important to think in terms of the input-referred noise of the VCO, leading to large devices in the VCO core. Designing the VCO is a mixture between traditional analog amplifier design and VCO design for PLLs. Hence, it is a craft on its own!

### REFERENCES

- [1] E. Roza, "Analog-to-digital conversion via duty-cycle modulation," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 44, no. 11, pp. 907–914, Nov 1997.

- [2] A. A. Lazar and L. T. Toth, "Perfect recovery and sensitivity analysis of time encoded bandlimited signals," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 51, no. 10, pp. 2060–2073, Oct 2004.

- [3] Y. Tsividis, "Mixed-Domain Systems and Signal Processing Based on Input Decomposition," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 53, no. 10, pp. 2145–2156, Oct 2006.

- [4] M. Hovin, A. Olsen, T. S. Lande, and C. Toumazou, "Delta-sigma modulators using frequency-modulated intermediate values," *IEEE J. Solid-State Circuits*, vol. 32, no. 1, pp. 13–22, Jan 1997.

- [5] R. Naiknaware, Haiming Tang, and T. S. Fiez, "Time-referenced single-path multi-bit /spl delta//spl sigma/ adc using a vco-based quantizer," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 47, no. 7, pp. 596–602, July 2000.

- [6] M. Z. Straayer and M. H. Perrott, "A 12-Bit, 10MHz Bandwidth, Continuous-Time Sigma-Delta ADC With a 5-Bit, 950-MS/s VCO-Based Quantizer," *IEEE J. Solid-State Circuits*, vol. 43, no. 4, pp. 805–814, April 2008.

- [7] T. Anand, K. A. A. Makinwa, and P. K. Hanumolu, "A VCO Based Highly Digital Temperature Sensor With 0.034 C/mV Supply Sensitivity," *IEEE J. Solid-State Circuits*, vol. 51, no. 11, pp. 2651–2663, Nov 2016.

- [8] C. Tu, Y. Wang, and T. Lin, "A Low-Noise Area-Efficient Chopped VCO-Based CTDSM for Sensor Applications in 40-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 52, no. 10, pp. 2523–2532, Oct 2017.

- [9] A. Quintero, C. Buffa, C. Perez, F. Cardes, D. Straeussnigg, A. Wiesbauer, and L. Hernandez, "A Coarse-Fine VCO-ADC for MEMS Microphones With Sampling Synchronization by Data Scrambling," *IEEE Solid-State Circuits Letters*, vol. 3, pp. 29–32, 2020.

- [10] J. Van Rethy, H. Danneels, V. De Smedt, W. Dehaene, and G. E. Gielen, "Supply-Noise-Resilient Design of a BBPLL-Based Force-Balanced Wheatstone Bridge Interface in 130-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 48, no. 11, pp. 2618–2627, NOV 2013.

- [11] S. Huang, N. Egan, D. Kesharwani, F. Opteynde, and M. Ashburn, "28.3 A 125MHz-BW 71.9dB-SNDR VCO-based CT SD ADC with segmented phase-domain ELD compensation in 16nm CMOS," in 2017 IEEE International Solid-State Circuits Conference (ISSCC), Feb 2017, pp. 470–471.

- [12] J. Daniels, W. Dehaene, M. Steyaert, and A. Wiesbauer, "A 0.02mm2 65nm CMOS 30MHz BW all-digital differential VCO-based ADC with 64dB SNDR," in 2010 Symposium on VLSI Circuits, June 2010, pp. 155–156.

- [13] X. Xing and G. G. E. Gielen, "A 42 fJ/Step-FoM Two-Step VCO-Based Delta-Sigma ADC in 40 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 3, pp. 714–723, March 2015.

- [14] G. Taylor and I. Galton, "A Mostly-Digital Variable-Rate Continuous-Time Delta-Sigma Modulator ADC," IEEE J. Solid-State Circuits, vol. 45, no. 12, pp. 2634–2646, Dec 2010.

- [15] F. Opteynde, "A maximally-digital radio receiver front-end," in 2010 IEEE International Solid-State Circuits Conference (ISSCC), Feb 2010, pp. 450–451.

- [16] T. Wu and M. S. Chen, "A Noise-Shaped VCO-Based Nonuniform Sampling ADC With Phase-Domain Level Crossing," IEEE J. Solid-State Circuits, vol. 54, no. 3, pp. 623–635, March 2019.

- [17] A. Mukherjee, M. Gandara, B. Xu, S. Li, L. Shen, X. Tang, D. Pan, and N. Sun, "A 1-GS/s 20 MHz-BW Capacitive-Input Continuous-Time  $\Delta\Sigma$  ADC Using a Novel Parasitic Pole-Mitigated Fully Differential VCO," *IEEE Solid-State Circuits Letters*, vol. 2, no. 1, pp. 1–4, Jan 2019.

- [18] M. Baert and W. Dehaene, "A 5-GS/s 7.2-ENOB Time-Interleaved VCO-Based ADC Achieving 30.5 fJ/cs," IEEE Journal of Solid-State Circuits, vol. 55, no. 6, pp. 1577–1587, 2019.

- [19] V. Nguyen, F. Schembari, and R. B. Staszewski, "A 0.2-V 30-MS/s 11b-ENOB Open-Loop VCO-Based ADC in 28-nm CMOS," *IEEE Solid-State Circuits Letters*, vol. 1, no. 9, pp. 190–193, Sep. 2018.

- [20] T. Watanabe, T. Mizuno, and Y. Makino, "An all-digital analog-to-digital converter with 12-uV/LSB using moving-average filtering," *IEEE J. Solid-State Circuits*, vol. 38, no. 1, pp. 120–125, Jan 2003.

- [21] S. Tajima, Y. Okuda, T. Watanabe, H. Aoyama, M. Yamamoto, and T. Uchiyama, "High-Resolution Magneto-Impedance Sensor With TAD for Low Noise Signal Processing," *IEEE Transactions on Magnetics*, vol. 50, no. 11, pp. 1–4, Nov 2014.

- [22] P. Yeon, M. S. Bakir, and M. Ghovanloo, "Towards a 1.1 mm2 free-floating wireless implantable neural recording SoC," in 2018 IEEE Custom Integrated Circuits Conference (CICC), April 2018, pp. 1–4.

- [23] W. Jiang, V. Hokhikyan, H. Chandrakumar, V. Karkare, and D. Markovic, "A ± 50-mV Linear-Input-Range VCO-Based Neural-Recording Front-End With Digital Nonlinearity Correction," *IEEE J. Solid-State Circuits*, vol. 52, no. 1, pp. 173–184, Jan 2017.

- [24] J. Huang, F. Laiwalla, J. Lee, L. Cui, V. Leung, A. Nurmikko, and P. P. Mercier, "A 0.01-mm2 Mostly Digital Capacitor-Less AFE for Distributed Autonomous Neural Sensor Nodes," *IEEE Solid-State Circuits Letters*, vol. 1, no. 7, pp. 162–165, July 2018.

- [25] L. B. Leene and T. G. Constandinou, "Time Domain Processing Techniques Using Ring Oscillator-Based Filter Structures," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, no. 12, pp. 3003–3012, Dec 2017.

- [26] B. Drost, M. Talegaonkar, and P. K. Hanumolu, "Analog Filter Design Using Ring Oscillator Integrators," IEEE J. Solid-State Circuits, vol. 47, no. 12, pp. 3120–3129, Dec 2012.

- [27] S. Tannirkulam Chandrasekaran, A. Jayaraj, M. Danesh, and A. Sanyal, "A Highly Digital Second-Order Oversampling TDC," *IEEE Solid-State Circuits Letters*, vol. 1, no. 5, pp. 114–117, May 2018.

- [28] E. Prefasi, S. Paton, and L. Hernandez, "A 7 mW 20 MHz BW Time-Encoding Oversampling Converter Implemented in a 0.08 mm<sup>2</sup>65 nm CMOS Circuit," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1562–1574, July 2011.

- [29] V. Dhanasekaran, M. Gambhir, M. M. Elsayed, E. Sanchez-Sinencio, J. Silva-Martinez, C. Mishra, L. Chen, and E. J. Pankratz, "A Continuous Time Multi-BitΔΣADC Using Time Domain Quantizer and Feedback Element," *IEEE J. Solid-State Circuits*, vol. 46, no. 3, pp. 639–650, March 2011.

- [30] A. A. Abidi, "Phase Noise and Jitter in CMOS Ring Oscillators," IEEE J. Solid-State Circuits, vol. 41, no. 8, pp. 1803-1816, Aug 2006.

- [31] B. Razavi, "The Ring Oscillator [A Circuit for All Seasons]," IEEE Solid-State Circuits Magazine, vol. 11, no. 4, pp. 10-81, Fall 2019.

- [32] J. Kim, T. K. Jang, Y. G. Yoon, and S. Cho, "Analysis and Design of Voltage-Controlled Oscillator Based Analog-to-Digital Converter," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57, no. 1, pp. 18–30, Jan 2010.

- [33] L. Hernandez and E. Gutierrez, "Analytical Evaluation of VCO-ADC Quantization Noise Spectrum Using Pulse Frequency Modulation," IEEE Signal Processing Letters, vol. 22, no. 2, pp. 249–253, Feb 2015.

- [34] E. Gutierrez, L. Hernandez, F. Cardes, and P. Rombouts, "A Pulse Frequency Modulation Interpretation of VCOs Enabling VCO-ADC Architectures With Extended Noise Shaping," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 2, pp. 444–457, Feb 2018.

- [35] E. Fitch, "The spectrum of modulated pulses," *Electrical Engineers Part IIIA: Radiocommunication, Journal of the Institution of*, vol. 94, no. 13, pp. 556–564, March 1947.

- [36] B. Razavi, "A study of phase noise in CMOS oscillators," IEEE J. Solid-State Circuits, vol. 31, no. 3, pp. 331-343, Mar 1996.

- [37] F. Pepe and P. Andreani, "An Accurate Analysis of Phase Noise in CMOS Ring Oscillators," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 66, no. 8, pp. 1292–1296, Aug 2019.

- [38] F. Cardes, A. Quintero, E. Gutierrez, C. Buffa, A. Wiesbauer, and L. Hernandez, "SNDR Limits of Oscillator-Based Sensor Readout Circuits," Sensors, vol. 18, no. 2, p. 445, Feb 2018. [Online]. Available: http://dx.doi.org/10.3390/s18020445

- [39] J. Marin, E. Sacco, J. Vergauwen, and G. Gielen, "A Robust BBPLL-Based 0.18-\mu CMOS Resistive Sensor Interface With High Drift Resilience Over a -40°C-175°C Temperature Range," *IEEE J. Solid-State Circuits*, vol. 54, no. 7, pp. 1862-1873, July 2019.