## Top-gated chemical vapor deposited MoS2 field-effect transistors on Si3N4 substrates

A. Sanne, R. Ghosh, A. Rai, H. C. P. Movva, A. Sharma, R. Rao, L. Mathew, and S. K. Banerjee

Citation: Applied Physics Letters 106, 062101 (2015); doi: 10.1063/1.4907885 View online: http://dx.doi.org/10.1063/1.4907885 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/106/6?ver=pdfcov Published by the AIP Publishing

## Articles you may be interested in

Defect-mediated transport and electronic irradiation effect in individual domains of CVD-grown monolayer MoS2 J. Vac. Sci. Technol. B 33, 02B110 (2015); 10.1116/1.4906331

Selective chemical vapor sensing with few-layer MoS2 thin-film transistors: Comparison with graphene devices Appl. Phys. Lett. 106, 023115 (2015); 10.1063/1.4905694

Growth-substrate induced performance degradation in chemically synthesized monolayer MoS2 field effect transistors

Appl. Phys. Lett. 104, 203506 (2014); 10.1063/1.4873680

Electrical performance of monolayer MoS2 field-effect transistors prepared by chemical vapor deposition Appl. Phys. Lett. 102, 193107 (2013); 10.1063/1.4804546

High mobility and high on/off ratio field-effect transistors based on chemical vapor deposited single-crystal MoS2 grains

Appl. Phys. Lett. 102, 142106 (2013); 10.1063/1.4801861

## Top-gated chemical vapor deposited MoS<sub>2</sub> field-effect transistors on Si<sub>3</sub>N<sub>4</sub> substrates

A. Sanne, R. Ghosh, A. Rai, H. C. P. Movva, A. Sharma, R. Rao, L. Mathew, and S. K. Banerjee *Microelectronics Research Center, University of Texas, Austin, Texas 78758, USA*

(Received 1 January 2015; accepted 23 January 2015; published online 9 February 2015)

We report the electrical characteristics of chemical vapor deposited (CVD) monolayer molybdenum disulfide (MoS<sub>2</sub>) top-gated field-effect transistors (FETs) on silicon nitride (Si<sub>3</sub>N<sub>4</sub>) substrates. We show that Si<sub>3</sub>N<sub>4</sub> substrates offer comparable electrical performance to thermally grown SiO<sub>2</sub> substrates for MoS<sub>2</sub> FETs, offering an attractive passivating substrate for transitionmetal dichalcogenides (TMD) with a smooth surface morphology. Single-crystal MoS<sub>2</sub> grains are grown via vapor transport process using solid precursors directly on low pressure CVD Si<sub>3</sub>N<sub>4</sub>, eliminating the need for transfer processes which degrade electrical performance. Monolayer top-gated MoS<sub>2</sub> FETs with Al<sub>2</sub>O<sub>3</sub> gate dielectric on Si<sub>3</sub>N<sub>4</sub> achieve a room temperature mobility of 24 cm<sup>2</sup>/V s with I<sub>on</sub>/I<sub>off</sub> current ratios exceeding 10<sup>7</sup>. Using HfO<sub>2</sub> as a gate dielectric, monolayer top-gated CVD MoS<sub>2</sub> FETs on Si<sub>3</sub>N<sub>4</sub> achieve current densities of 55  $\mu$ A/ $\mu$ m and a transconductance of 6.12  $\mu$ S/ $\mu$ m at V<sub>tg</sub> of -5 V and V<sub>ds</sub> of 2 V. We observe an increase in mobility at lower temperatures, indicating phonon scattering may dominate over charged impurity scattering in our devices. Our results show that Si<sub>3</sub>N<sub>4</sub> is an attractive alternative to thermally grown SiO<sub>2</sub> substrate for TMD FETs. © 2015 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4907885]

Graphene as a two-dimensional material has been thoroughly studied for its remarkable electrical, mechanical, and optical properties. However, a large roadblock to potential graphene-based CMOS devices is the absence of a bandgap, due to graphene's Dirac cone band structure. As a result, other two-dimensional (2D) materials such as transition-metal dichalcogenides (TMDs) are being studied. Of the TMDs, molybdenum disulfide (MoS<sub>2</sub>) has particularly attracted a lot of attention. MoS<sub>2</sub> is a 2D semiconductor with a bulk indirect bandgap of  $\sim 1.3 \text{ eV}$ , and a direct bandgap of  $\sim 1.8 \text{ eV}$  for single layers.<sup>1-3</sup> Its bandgap allows for high I<sub>on</sub>/I<sub>off</sub> metal-oxide semiconducting field-effect transistors (MOSFETs). In principle, the confinement of channel charge carriers to nearly atomic thicknesses (~0.65 nm) allows for improved gate control, leading to reduced short-channel effects. Top-gated FETs based on exfoliated monolayer MoS2 flakes on SiO2 have shown room temperature mobilities  $>80 \text{ cm}^2/\text{V}$  s, with  $I_{on}/I_{off}$ ratios exceeding 10<sup>8,4</sup> However, exfoliated MoS<sub>2</sub> flakes are typically small and cannot be easily scaled to large areas.

Recent studies have shown that the substrate can play a large role in the performance of  $MoS_2$  FETs. Multi-layer  $MoS_2$  back-gated FETs on 50 nm  $Al_2O_3$  substrates have shown back-gated mobilities >100 cm<sup>2</sup>/V s,<sup>5</sup> while multi-layer  $MoS_2$  FETs on 50 nm thick spin-coated poly(methyl methacrylate) (PMMA) substrates have achieved back-gated mobilities >400 cm<sup>2</sup>/V s.<sup>6</sup> Furthermore, the mobility can be engineered by applying an appropriate top gate dielectric, such as HfO<sub>2</sub>,  $Al_2O_3$ , or polymer dielectrics.<sup>7–9</sup> Applying a high-*k* dielectric as either a substrate or superstrate increases the screening of charged impurities in the MoS<sub>2</sub> layer, which may enhance the mobility.<sup>10</sup> The substrate may affect FET performance by introducing long range or short range charge disorder. It has been shown that the MoS<sub>2</sub> follows the morphology of the substrate surface, whereby a rough surface

may affect long range and short range scattering parameters.<sup>6,11</sup> Graphene was reported to have a smooth surface morphology when transferred on  $Si_3N_4$  substrates.<sup>12</sup> As a result, graphene on  $Si_3N_4$  showed comparable mobility to  $SiO_2$  due to lower long and short range scattering parameters. Additionally, various substrates can cause carrier fluctuations due to extrinsic doping, which can be a contributing factor to the mobility.

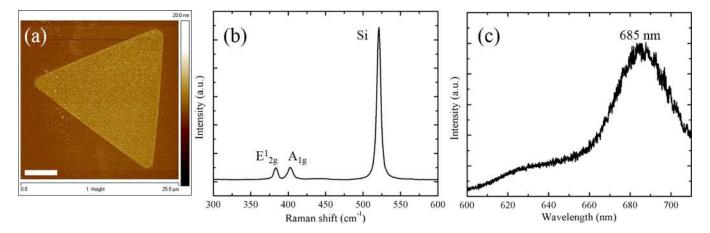

We report on the fabrication and characterization of topgated chemical vapor deposition (CVD)-grown MoS<sub>2</sub> FETs on Si<sub>3</sub>N<sub>4</sub> insulating substrates. We see comparable electrical performance of MoS<sub>2</sub> FETs on these substrates as compared to conventional thermally grown SiO<sub>2</sub>-Si substrates. Silicon nitride substrates offer superior passivating qualities over thermal oxide, such as better diffusion barriers against water molecules and ions, and a higher dielectric constant leading to increased electric field screening.<sup>13</sup> Additionally, Si<sub>3</sub>N<sub>4</sub> can function better as an etch stop layer than SiO<sub>2</sub> while etching the gate dielectric from the source/drain and other regions. Silicon nitride substrates were grown by low pressure chemical vapor deposition (LPCVD) at 800 °C on highly doped silicon. In this study, the MoS<sub>2</sub> atomic films on  $Si_3N_4$  (90 nm)/Si substrates were prepared by the sulfurization of MoO<sub>3</sub>, a process similar to those described in Refs. 14–16. The starting materials were  $MoO_3$  (15 mg) and sulfur (1 g) powder that were loaded in alumina crucibles and placed inside a quartz tube. The temperature of the furnace was raised to 850°C with temperature of sulfur end of the furnace at roughly 350 °C. The growth continues for 5 min at 850 °C, after which the heater in the furnace was turned off and the N<sub>2</sub> flow rate was set to 200 sccm for cooling down. A combination of atomic force microscopy (AFM) (Figure 1(a)), Raman spectroscopy (Figure 1(b)), and photoluminescence spectroscopy (PL) (Figure 1(c)) was used to ascertain

FIG. 1. (a) AFM image of an isolated triangular monolayer  $MoS_2$  domain on  $Si_3N_4$ . The CVD  $MoS_2$  domains were typically 0.8 nm in thickness and did not show surface contamination before any fabrication steps. (b) Raman map of the same isolated monolayer  $MoS_2$  domain with the Raman and photoluminescence spectra shown below. The  $E_{2g1}$  peak is at 383.4 cm<sup>-1</sup> with the  $A_{1g}$  at 402.9 cm<sup>-1</sup>. This corresponds to a  $\Delta$  of 19.5 cm<sup>-1</sup>. (c)The photoluminescence spectrum of the CVD  $MoS_2$  also shows a strong peak at around 685 nm (1.81 eV). The scale bar is 5  $\mu$ m.

the single-layer thickness of the isolated as-grown CVD  $MoS_2$  domains used for electrical characterization. As shown in Figure 1(a), the CVD  $MoS_2$  domains were typically 0.8 nm in thickness and did not show surface contamination before any fabrication steps. The  $E^{1}_{2g}$  peak is at 383.4 cm<sup>-1</sup> with the  $A_{1g}$  at 402.9 cm<sup>-1</sup>. This corresponds to a peak separation delta ( $\Delta$ ) of 19.5 cm<sup>-1</sup>, which is characteristic of single-layer  $MoS_2$ .<sup>17,18</sup> The full width at half maximum (FWHM) of the  $E^{1}_{2g}$  and  $A_{1g}$  peaks can indicate the quality of the film. The CVD  $MoS_2$  grown on Si<sub>3</sub>N<sub>4</sub> shows a FWHM of 6.69 cm<sup>-1</sup> for the  $A_{1g}$  peak and 5.3 cm<sup>-1</sup> for the  $E^{1}_{2g}$ peak, similar to reports of CVD  $MoS_2$  on SiO<sub>2</sub> substrates.<sup>14</sup> The PL spectrum of the CVD  $MoS_2$  also shows a strong peak at around 685 nm (1.81 eV) which is widely reported as the band gap of monolayer  $MoS_2$ .<sup>14</sup>

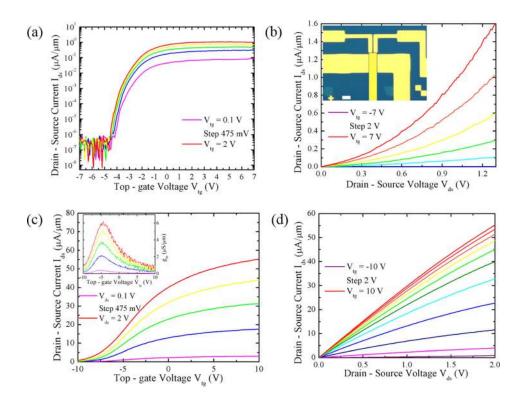

Top-gated MoS<sub>2</sub> FETs were fabricated as follows. Suitable CVD grown MoS<sub>2</sub> flakes were identified using a combination of optical contrast, Raman spectroscopy, and AFM images. Device active regions were defined using e-beam lithography. Excess MoS<sub>2</sub> was etched using Cl<sub>2</sub> plasma. Next, metal electrodes were defined with a second ebeam lithography step. A stack of Ag/Au (20 nm/30 nm) was deposited as a low-work function (4.26 eV) source/drain metal electrodes to enhance n-type conduction of the MoS<sub>2</sub> FET. Following a metal liftoff in acetone, atomic layer deposition (ALD) was used to deposit a 25 nm thick layer of  $Al_2O_3$  or  $HfO_2$  as a top gate dielectric. The top gate electrode was then defined using a final e-beam lithography step. The top gate metal was deposited as a 50 nm stack of Ni/Au. A final metal liftoff in acetone completed device fabrication. An optical image of the final device structure used for temperature dependence and mobility extraction is shown in the inset of Figure 2(b). Measurements presented in this paper were taken in vacuum ( $\sim 10^{-6}$  Torr), and in the dark. The back-gate was grounded in all top-gated measurements.

Figure 2(a) is the  $I_{ds}$ - $V_{gs}$  transfer characteristics of a MoS<sub>2</sub> transistor with a top gate dielectric of Al<sub>2</sub>O<sub>3</sub>. For all DC measurements, the device gate length (L<sub>g</sub>) is 300 nm and the widths (W) vary from 10  $\mu$ m to 25  $\mu$ m, depending on the size of the CVD MoS<sub>2</sub> domain. The top gate voltage (V<sub>tg</sub>) is swept from -7 V to 7 V with the drain voltage (V<sub>d</sub>) varying

from 0.1 V to 2.0 V. The device exhibits a threshold voltage (V<sub>th</sub>) around -4.0 V, indicating unintentional n-type doping of the MoS<sub>2</sub> during the fabrication or growth. This is common for both CVD and exfoliated MoS<sub>2</sub> devices, intrinsically caused by sulfur vacancies in the  $MoS_2$  and extrinsically by doping sources such as PMMA and acetone. With  $Al_2O_3$  as the top gate dielectric, the  $I_{on}/I_{off}$  ratios exceed  $10^7$  at a V<sub>ds</sub> of 2.0 V with off-state currents less than  $10^{-7} \mu$ A/ $\mu$ m. Using the slope of the I<sub>ds</sub>-V<sub>gs</sub> curve in the linear region, the intrinsic field-effect mobility is calculated using  $\mu_{fe} = [dI_{ds}/dV_{gs}][L/WC_{ox}V_{ds}]$ . Operating at a low-field  $V_{ds}$  of 0.1 V, we extract a maximum mobility of  $24 \text{ cm}^2/\text{V}$  s. This mobility agrees with reported values for CVD MoS<sub>2</sub> FETs on thermally grown  $SiO_2$ .<sup>19-21</sup> Figure 2(b) shows the  $I_{ds}$ - $V_{ds}$  output curves. Figure 2(c) is the  $I_{ds}$ - $V_{gs}$  transfer characteristics and Figure 2(d) is the  $I_{ds}$ - $V_{ds}$  output characteristics of a monolayer MoS<sub>2</sub> transistor with a top gate dielectric of HfO<sub>2</sub>. The current densities for HfO<sub>2</sub> are much larger than that of Al<sub>2</sub>O<sub>3</sub>, exceeding  $55 \,\mu$ A/ $\mu$ m at a V<sub>ds</sub> of 2.0 V. As shown in the inset of Figure 2(c), the devices with HfO<sub>2</sub> gate dielectric on Si<sub>3</sub>N<sub>4</sub> substrates achieve a maximum transconductance ( $g_m$ ) of 6.17  $\mu$ S/ $\mu$ m at a V<sub>ds</sub> of 2.0 V. These figures exceed previous reports of current density and transconductance in top-gated CVD grown monolayer MoS<sub>2</sub> devices with equivalent gate lengths.<sup>20,22</sup> We can see the output curves tending more towards current saturation with HfO<sub>2</sub>. Recent reports have shown that Si<sub>3</sub>N<sub>4</sub> can be used to n-type dope TMDs.<sup>23,24</sup> Positive fixed charge centers within the nitride films can act as charge transfer doping centers, which forms a possible explanation for the large V<sub>th</sub> shifts in our devices. Additionally, oxygen vacancies at the MoS<sub>2</sub> to gate dielectric interface can function as shallow charge traps, which would increase the  $I_{off}$ .<sup>25</sup> A possible source for these uncompensated atoms is improper surface temperature ramping before ALD growth. The substrate leakage for all Si<sub>3</sub>N<sub>4</sub> substrate devices is low, averaging less than 0.25 fA/cm<sup>2</sup>.

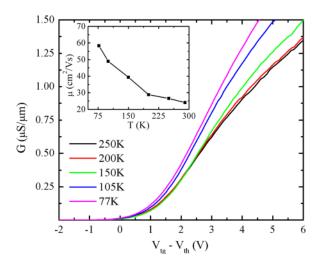

Figure 3 shows the four point conductance (G) at different temperature (T) values ranging from 300 K to 77 K. As shown in the inset of Figure 2(b), the device dimension used for this measurement was a  $L_g$  of 5  $\mu$ m and a W of 10  $\mu$ m. The MoS<sub>2</sub> FETs used for low-temperature measurements

FIG. 2. (a) Drain-to-source current Ids vs. top gate voltage Vtg for different drain voltages  $V_d$  on an  $Al_2O_3$  topgated device. The threshold voltage Vtt is around -4.0 V indicating unintentional n-type doping of the MoS<sub>2</sub>. The  $I_{on}/I_{off}$  ratio reaches  $10^7$  at  $V_d = 2.0$  V. (b) Drain-to-source current Ids vs. drain voltage V<sub>d</sub> for different top gate voltages V<sub>tg</sub>. Note the device shows negligible currents until a  $V_{tg}$  of -2V. Inset: Optical image of a top-gated MoS<sub>2</sub> FET. (c) Drain-to-source current  $I_{ds}$  vs. top gate voltage  $V_{tg}$  for different drain voltages  $V_d$  on an HfO<sub>2</sub> topgated device. With HfO<sub>2</sub> as a gate dielectric, current drives are much larger and saturation is observed. Inset: Transconductance gm vs. top gate voltage V<sub>tg</sub>. (d) Drain-to-source current I<sub>ds</sub> vs. drain voltage V<sub>d</sub> for an HfO<sub>2</sub> topgated device. The scale bar is  $5 \,\mu m$ .

were gated with Al<sub>2</sub>O<sub>3</sub>, as they possessed a higher fabrication yield over HfO<sub>2</sub> gated devices. As temperatures are reduced, the V<sub>th</sub> shifts towards higher voltages. This is because a larger bias voltage is required to overcome the larger potential barrier that less energetic electrons face at lower temperatures. To offset the V<sub>th</sub> shift, Figure 3 plots G vs. V<sub>tg</sub>-V<sub>th</sub> for different temperatures. The inset of Figure 3 shows the four point intrinsic mobility vs. temperature. The mobility increases with decreasing temperature to a value of  $58 \text{ cm}^2/\text{V}$  s at 77 K, suggesting a decrease in ionized impurity scattering in the top gate configuration. In the phononlimited region of 100 K to 300 K, the mobility vs. temperature data can be fit to  $\mu \sim T^{-\nu}$  to gain some insight into the scattering mechanisms of the device. A functional fit of the

FIG. 3. Channel conductance (G) vs.  $(V_{tg}-V_{th})$  for temperatures ranging from 250 K to 77 K. The threshold voltage  $(V_t)$  shifts to higher voltages at lower temperatures due to the temperature dependence of the surface potential. A clear increase in the slope of the conductance curve can be seen with a decrease in temperature. Inset:  $\mu$  vs. T for a top-gated MoS<sub>2</sub> device.

highest mobility device yields  $v \approx 0.65$ , which is significantly less than the predicted theoretical value (v = 1.52). This predicted theoretical value takes into account the quenching of the homopolar phonon modes of monolayer MoS<sub>2</sub>, suggesting that other temperature-dependent scattering mechanisms are involved in our devices.<sup>26</sup> Previous reports of mobility dependence on temperature have extracted a coefficient as low as v = 0.3 for top-gated MoS<sub>2</sub> with HfO<sub>2</sub> (k = 19) as a gate dielectric.<sup>27</sup> Our devices for this measurement were gated with Al<sub>2</sub>O<sub>3</sub> in a significantly lowerk top gate environment, suggesting the high-k Si<sub>3</sub>N<sub>4</sub> substrate may also contribute to screening phonons. This is also supported by the fact that Si<sub>3</sub>N<sub>4</sub> has a higher surface polar optical phonon energy than SiO<sub>2</sub>, which leads to less remote phonon scattering in the MoS<sub>2</sub> channel.<sup>28</sup>

In summary, we demonstrate top-gated CVD  $MoS_2$  FETs on  $Si_3N_4$  with comparable electrical performance to  $SiO_2$  substrates. We achieve a mobility of  $24 \text{ cm}^2/\text{V}$  s with  $I_{on}/I_{off}$  ratios exceeding  $10^7$ . Using HfO<sub>2</sub> as a top gate dielectric, devices achieve current densities of  $55 \,\mu\text{A}/\mu\text{m}$  and a max transconductance of  $6.12 \,\mu\text{S}/\mu\text{m}$ . Temperature dependence of mobility in MoS<sub>2</sub> on Si<sub>3</sub>N<sub>4</sub> shows a strong suppression of charged impurity scattering and a weaker than expected dependence on phonon scattering, suggesting the Si<sub>3</sub>N<sub>4</sub> may play a role in screening remote phonons. We show that Si<sub>3</sub>N<sub>4</sub> substrates are viable for TMD-based logic devices and potential radio frequency applications.

This work was supported by the STTR program and the NSF NASCENT ERC. The authors would like to thank the Army Research Office for partial support of this work under STTR Award No. W911NF-14-P-0030.

<sup>1</sup>G. L. Frey, S. Elani, M. Homyonfer, Y. Feldman, and R. Tenne, *Phys. Rev. B* **57**, 6666 (1998).

- <sup>2</sup>K. F. Mak, C. Lee, J. Hone, J. Shan, and T. F. Heinz, Phys. Rev. Lett. **105**, 136805 (2010).

- <sup>3</sup>T. Cao, G. Wang, W. P. Han, H. Q. Ye, C. R. Zhu, J. R. Shi, Q. Niu, P. H. Tan, E. Wang, B. L. Liu, and J. Feng, Nat. Commun. **3**, 887 (2012).

- <sup>4</sup>D. Krasnozhon, D. Lembke, C. Nyffeler, Y. Leblebici, and A. Kis, Nano. Lett. **14**, 5905 (2014).

- <sup>5</sup>S. Kim, A. Konar, W. S. Hwang, J. H. Lee, J. Lee, J. Yang, C. Jung, H. Kim, J. B. Yoo, J. Y. Choi, Y. W. Jin, S. Y. Lee, D. Jena, W. Choi, and K. Kim, Nat. Commun. **3**, 1011 (2012).

- <sup>6</sup>W. Bao, X. Cai, D. Kim, K. Sridhara, and M. S. Fuhrer, Appl. Phys. Lett. **102**, 042104 (2013).

- <sup>7</sup>B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, Nat. Nanotechnol. **6**, 147 (2011).

- <sup>8</sup>H. Liu and P. D. D. Ye, IEEE Electron Device Lett. 33, 546 (2012).

- <sup>9</sup>M. W. Lin, L. Z. Liu, Q. Lan, X. B. Tan, K. S. Dhindsa, P. Zeng, V. M. Naik, M. M. C. Cheng, and Z. X. Zhou, J. Phys. D: Appl. Phys. 45, 345102 (2012).

- <sup>10</sup>C. Jang, S. Adam, J. H. Chen, E. D. Williams, S. Das Sarma, and M. S. Fuhrer, Phys. Rev. Lett. **101**, 146805 (2008).

- <sup>11</sup>D. Sercombe, S. Schwarz, O. Del Pozo-Zamudio, F. Liu, B. J. Robinson, E. A. Chekhovich, I. I. Tartakovskii, O. Kolosov, and A. I. Tartakovskii, Sci. Rep. **3**, 3489 (2013).

- <sup>12</sup>Z. Hu, D. Sinha, J. U. Lee, and M. Liehr, J. Appl. Phys. **115**, 194507 (2014).

- <sup>13</sup>H. Pierson, Handbook of Chemical Vapor Deposition (CVD): Principles, Technology, and Applications (Noyes, New York, 1992), p. 282.

- <sup>14</sup>Y. Lee, X. Zhang, W. Zhang, M. Chang, C. Lin, K. Chang, Y. Yu, J. Wang, C. Chang, L. Li, and T. Lin, Adv. Mater. **24**, 2320 (2012).

- Appl. Phys. Lett. 106, 062101 (2015)

- <sup>15</sup>A. Zande, P. Huang, D. Chenet, T. Berkelbach, Y. You, G. Lee, T. Heinz, D. Reichman, D. Muller, and J. Hone, Nat. Mater. **12**, 554 (2013).

- <sup>16</sup>S. Najmaei, Z. Liu, W. Zhou, Z. Zou, G. Shi, S. Lei, B. Yakobson, J. Idrobo, P. Ajayan, and J. Lou, Nat. Mater. **12**, 754 (2013).

- <sup>17</sup>A. Splendiani, L. Sun, Y. Zhang, T. Li, J. Kim, C. Y. Chim, G. Galli, and F. Wang, Nano Lett. **10**, 1271 (2010).

- <sup>18</sup>H. Li, Z. Y. Yin, Q. Y. He, H. Li, X. Huang, G. Lu, D. W. H. Fam, A. I. Y. Tok, Q. Zhang, and H. Zhang, Small 8, 63 (2012).

- <sup>19</sup>M. Amani, M. Chin, A. Birdwell, T. O'Regan, S. Najmaei, Z. Liu, P. Ajayan, J. Lou, and M. Dubey, Appl. Phys. Lett. **102**, 193107 (2013).

- <sup>20</sup>H. Liu, M. Si, S. Najmaei, A. Neal, Y. Du, P. Ajayan, J. Lou, and P. Ye, Nano. Lett. **13**, 2640 (2013).

- <sup>21</sup>P. B. Shah, M. Amani, M. L. Chin, T. P. O'Regan, F. J. Crowne, and M. Dubey, Solid-State Electron. 91, 87 (2014).

- <sup>22</sup>H. Wang, L. Yu, Y. Lee, W. Fang, A. Hsu, P. Herring, M. Chin, M. Dubey, L. Li, J. Kong, and T. Palacios, IEEE Int. Electron Device Meet. **2012**, 4.6.1–4.6.4.

- <sup>23</sup>K. Chen, D. Kiriya, M. Hettick, M. Tosun, T.-J. Ha, S. R. Madhvapathy, S. Desai, A. Sachid, and A. Javey, APL Mater. 2, 092504 (2014).

- <sup>24</sup>T.-J. Ha, K. Chen, S. Chuang, K. M. Yu, D. Kiriya, and A. Javey, "Highly uniform and stable n-type carbon nanotube transistors by using positively charged silicon nitride thin films," Nano Letters 15(1), 392–397 (2015).

- <sup>25</sup>A. Valsaraj, J. Chang, L. F. Register, and S. K. Banerjee, "Theoretical investigation of monolayer MoS<sub>2</sub> on oxide," e-print arXiv:1412.7852

- <sup>26</sup>K. Kaasbjerg, K. S. Thygesen, and K. W. Jacobsen, Phys. Rev. B 85, 115317 (2012).

- <sup>27</sup>B. Radisavljevic and A. Kis, Nat. Mater. 12, 815 (2013).

- <sup>28</sup>W. Zhu, D. Neumayer, V. Perebeinos, and P. Avouris, Nano. Lett. 10, 3572 (2010).