## Purdue University Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

March 2008

## Top-gated graphene field-effect-transistors formed by decomposition of SiC

Y Q. Wu

Purdue University

P.D. Ye

Birck Nanotechnology Center and School of Electrical and Computer Engineering, Purdue University, yep@purdue.edu

Michael A. Capano

Birck Nanotechnology Center, Purdue University, capano@purdue.edu

Yi Xuan

yxuan@purdue.edu

Y Sui

Purdue Univ, Sch Elect & Comp Engn

See next page for additional authors

Follow this and additional works at: http://docs.lib.purdue.edu/nanopub

Wu, Y Q.; Ye, P. D.; Capano, Michael A.; Xuan, Yi; Sui, Y; Qi, Minghao; Cooper, James A.; Shen, T; Pandey, D; Prakash, G; and Reifenberger, R., "Top-gated graphene field-effect-transistors formed by decomposition of SiC" (2008). *Birck and NCN Publications*. Paper 182.

http://docs.lib.purdue.edu/nanopub/182

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

| Authors<br>Y Q. Wu, P. D. Ye, Michael A. Capano, Yi Xuan, Y Sui, Minghao Qi, James A. Cooper, T Shen, D Pandey, G<br>Prakash, and R. Reifenberger |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                   |

|                                                                                                                                                   |

|                                                                                                                                                   |

|                                                                                                                                                   |

|                                                                                                                                                   |

|                                                                                                                                                   |

|                                                                                                                                                   |

|                                                                                                                                                   |

|                                                                                                                                                   |

|                                                                                                                                                   |

|                                                                                                                                                   |

## Top-gated graphene field-effect-transistors formed by decomposition of SiC

Y. Q. Wu, <sup>1</sup> P. D. Ye, <sup>1,a)</sup> M. A. Capano, <sup>1,b)</sup> Y. Xuan, <sup>1</sup> Y. Sui, <sup>1</sup> M. Qi, <sup>1</sup> J. A. Cooper, <sup>1</sup> T. Shen, <sup>2</sup> D. Pandey, <sup>2</sup> G. Prakash, <sup>2</sup> and R. Reifenberger <sup>2</sup>

(Received 12 October 2007; accepted 8 February 2008; published online 3 March 2008)

Top-gated, few-layer graphene field-effect transistors (FETs) fabricated on thermally decomposed semi-insulating 4H-SiC substrates are demonstrated. Physical vapor deposited SiO<sub>2</sub> is used as the gate dielectric. A two-dimensional hexagonal arrangement of carbon atoms with the correct lattice vectors, observed by high-resolution scanning tunneling microscopy, confirms the formation of multiple graphene layers on top of the SiC substrates. The observation of n-type and p-type transition further verifies Dirac Fermions' unique transport properties in graphene layers. The measured electron and hole mobilities on these fabricated graphene FETs are as high as 5400 and  $4400 \text{ cm}^2/\text{V} \text{ s}$ , respectively, which are much larger than the corresponding values from conventional SiC or silicon. © 2008 American Institute of Physics. [DOI: 10.1063/1.2889959]

To a large extent, the success of modern microelectronics is based on the continuous miniaturization or scaling of silicon metal-oxide-semiconductor field-effect transistors (MOSFETs), which make them smaller, faster, and cheaper. However, silicon-based technology will encounter physical and technical limits within the next decade, which motivates the semiconductor industry to explore alternative device technologies such as Ge, III-Vs, and carbon nanotubes 5-5 to replace silicon as active channel materials. Graphene, a monolayer of carbon atoms tightly packed into a twodimensional (2D) hexagonal lattice, has recently been shown to be thermodynamically stable and exhibit astonishing transport properties, such as an electron mobility of  $\sim 15\,000\,\mathrm{cm^2/V}$  s and velocity of  $\sim 10^8\,\mathrm{cm/s.}^6$  High-quality monolayer graphene has been obtained in small (few micron) areas by exfoliation of highly ordered pyrolytic graphite (HOPG) and transferred onto SiO2 substrates for further device fabrication. 7,8 However, this exfoliation process cannot form the basis for a large-scale manufacturing process. Recent reports of large-area epitaxial graphene by thermal decomposition of SiC wafers have provided the missing pathway to a viable electronics technology. The advantage of epitaxially grown graphene for nanoelectronic application resides in its planar 2D structure that enables conventional topdown lithography and processing techniques.

Three-terminal MOSFETs constitute the backbone of today's silicon industry and similar device structures are envisioned for graphene. For these devices to be successful, carrier transport in the conduction channel must be controlled efficiently by the top-gate structure. Some attempts to address these issues were reported very recently, both on peeled graphene flakes<sup>10</sup> or SiC surfaces after graphitization.<sup>11</sup> In this letter, the observation of n-type and p-type transitions on epitaxially grown graphene films by top-gate bias is reported. More importantly, the measured electron and hole mobilities on fabricated top-gate graphene field-effect transistors exceeds 5400 and 4400 cm<sup>2</sup>/V s, respectively. This is one order-of-magnitude higher than earlier reported<sup>11</sup> and approaches the values obtained from exfoliated graphene films. 6-8

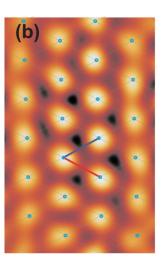

The graphene films were grown on the carbon or silicon face of semi-insulating 4H-SiC substrates in an Epigress VP508 SiC hot-wall chemical vapor deposition (CVD) reactor. The off-cut angle of the substrate is nominally 0°. Prior to growth, substrates are subjected to a hydrogen etch at 1600 °C for 5 min, followed by cooling the samples to below 700 °C. After evacuating hydrogen from the system, the growth environment is pumped to an approximate pressure of  $2 \times 10^{-7}$  mbar before temperature ramping at a rate of 10−20 °C/min up to a specified growth temperature. Growth temperatures investigated ranged 1350–1650 °C. Scanning tunneling microscopy (STM) images taken at a constant set point current of 0.5 nA with a bias of -0.5 V revealed nanometer high steps, as illustrated in Fig. 1(a), implying that graphene follows the 4H-SiC surface topography after H2 etching. The surface roughness of a plateau was measured to be  $\sim 0.2$  nm. This morphology is critical in achieving high-mobility graphene films on SiC. Atomic resolved STM images within a graphenelike domain were performed in constant height mode. Figure 1(b) shows a typical atomic-resolution STM image after denoising using a FFT filter. The image is superimposed with a triangular lattice with lattice vectors of 0.25 nm, agreeing well with the expected 0.246 nm lattice spacing of HOPG. This is far different from the 0.307 nm lattice constant of 4H SiC. The observed triangular lattice is expected from the Bernal stacking of neighboring graphene sheets, as in HOPG. 12 The formation of multiple graphene layers on SiC after high temperature decomposition is further confirmed by the similar measurement on HOPG, where a similar triangular sublattice is observed with the lattice vectors of 0.26 nm.

The device structure of the fabricated graphene FET is shown in the inset of Fig. 2(a). Device isolation of the graphene film was realized by 120 nm deep SF<sub>6</sub> based dry etching with photolithographically defined photoresist as a protection layer. Ti/Au metallization was used to form Ohmic contacts on graphene as source and drain. Physical vapor deposition (PVD) SiO<sub>2</sub> was used as top-gate dielectric. Plasma-based processing was avoided to prevent damage to

<sup>&</sup>lt;sup>1</sup>School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, USA

<sup>&</sup>lt;sup>2</sup>Department of Physics and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, USA

a)Electronic mail: yep@purdue.edu.

b) Electronic mail: capano@purdue.edu.

FIG. 1. (Color online) The graphene layer was studied using an Omicron ultrahigh-vacuum STM operating at room temperature in the low  $10^{-10}$  Torr regime. Etched W tips were used throughout. The XY piezocalibration was checked independently by imaging atoms in HOPG. (a) STM image of a graphene film formed on a carbon-face on-axis semi-insulating 4H SiC substrate. The 1.2 or 1.4 nm steps are unit steps in the basal plane of the SiC substrate. (b) Atomic resolution STM image of a triangular sublattice of carbon atoms in a graphene film. Due to the offset between two sublattices in a multiple graphene film, only every other surface atom is imaged.

the graphene films. CVD or atomic layer deposition cannot form high-quality dielectrics on the basal plane of graphene without a noncovalent functionalization layer. Finally, conventional Ni/Au metals were electron-beam evaporated, followed by liftoff to form the gate electrodes. The process requires three levels of lithography (isolation, Ohmic, and gate), all done using a contact printer.

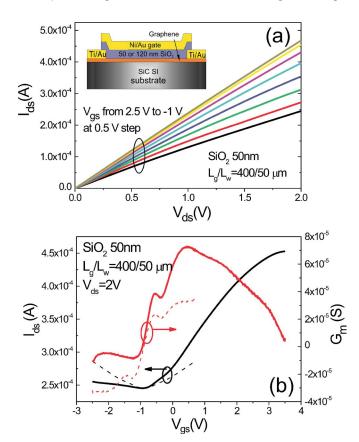

Figure 2(a) shows the dc  $I_d$ - $V_{\rm ds}$  characteristic with a gate bias from -1 to 2.5 V on a device with a fully covered gate, as shown in the inset. The measured graphene FET has a designed gate length  $(L_g)$  of 400  $\mu$ m and a gate width  $(L_w)$  of 50  $\mu$ m. The gate oxide is 50 nm SiO<sub>2</sub>. The gate leakage

FIG. 2. (Color online) (a)  $I_{\rm ds}$  vs  $V_{\rm ds}$  as a function of  $V_{\rm gs}$  on a few-layer graphene FET measured at room temperature.  $V_{\rm gs}$  changes from 2.5 V (top) to -1.0 V (bottom) in 0.5 V steps. (b) Transfer characteristics of the same device at  $V_{\rm ds}$ =2 V. The dashed lines are corrected one around Dirac point after extracting the p-n junction resistance or "odd" resistance component (see Ref. 21)

current is very low, below 10<sup>-9</sup> A under the same bias conditions, corresponding to a gate leakage current density of  $3 \times 10^{-6}$  A/cm<sup>2</sup>. The drain current can be modulated by ~50% with a few volts gate bias. A reference SiC sample without the graphitization treatment, processed at the same time, shows no current (<40 pA). Figure 2(b) illustrates the transfer characteristics of this graphene FET at  $V_{\rm ds}$ =0.2 V. The drain current or conductance exhibits a region of minimum at  $V_{gs} \sim -0.8$  V. This dip in single-graphene layer is well documented and corresponds to a minimum conductivity of  $\sim 4e^2/h$  at the charge neutrality point or Dirac point, where e and h are the electric charge and Planck's constant, respectively. It is the same physical origin here for multiple graphene films. The device cannot be turned off to zero drain current or conductance, since graphene or graphite is a semimetal with no bandgap. A finite bandgap can be created by patterning graphene into graphene nanoribbons, 16,17 but the dimensions of such ribbons press the limits of modern lithography. A finite bandgap may also be created by breaking the graphene sublattice symmetry using selective doping, 18 a vertical electric field, or interactions with the underlying substrate. With the conductance of  $1.25 \times 10^{-4}$  S in this particular device, we estimate that this few-layer graphene film could contain six to seven layers of graphene. The slope of the drain current shows that the peak extrinsic transconductance  $(G_m)$  is ~1.4 mS/mm, due to its extraordinarily large gate length. Assuming that epitaxially grown few-layer graphene on SiC has the same layer-by-layer separation of 0.335 nm as HOPG, the conduction channel of this particular device should be constrained within  $\sim$ 2.0 nm. The channel mobility can be simply estimated by  $\mu$ = $[(\Delta I_d/V_{\rm ds})/(L_w/L_g)]/C_{\rm ox}\Delta V_{\rm gs}$  using the surface-channel device formula. Here,  $C_{\text{ox}}$  is determined by  $\varepsilon_0 \varepsilon_r A/d$ , where  $\varepsilon_0$  is permittivity of free space,  $\varepsilon_r$  is 3.0 for PVD SiO<sub>2</sub> without annealing, A is unit area and d is the gate oxide thickness. The extracted electron effective mobility is as high as 5400 cm<sup>2</sup>/V s, one order of magnitude higher than the value reported in Ref. 11 and approaching values reported in exfoliated graphene films.<sup>6-8</sup> In contrast to Ref. 10, no significant degradation of mobility is observed due to the use of PVD SiO<sub>2</sub>. The device characteristics could become ambipolar such as at low charge density or near Dirac point. 14,21,22 A simple approach, proposed by Huard et al., is used to further characterize the sample by extracting the p-n junction resistance, 21 as shown by the dashed lines in Fig. 2(b). The corrected electron mobility drops 10%-30% around Dirac

Downloaded 24 Nov 2008 to 128.46.220.88. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

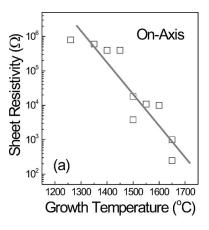

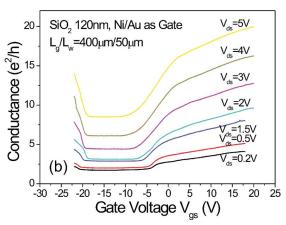

FIG. 3. (Color online) (a) Sheet resistivity of graphene films formed on SiC as a function of growth temperature. The gray line is a guide to the eye. (b) Drain conductance vs  $V_{\rm gs}$  as a function of  $V_{\rm ds}$  on a possible monolayer graphene FET measured at room temperature. The graphene film is formed on Si face of SiC. A clear n-type to p-type transition is obtained once the gate bias is strongly positive or negative.

point  $V_{\rm gs}$ =-0.8 V. Note that this correction does not have to be needed at unipolar condition or at high charge density.

To accurately control the number of graphene layers formed by decomposition of the SiC surface remains a challenge. Figure 3(a) shows graphene sheet resistivity as a function of growth temperature for ten growth runs. It is obvious that the number of graphene layers can be controlled by decomposition temperature, time, and other processing conditions. 1500–1550 °C is the growth temperature window for monolayer graphene films on Si face of SiC in the CVD system used in these experiments. Figure 3(b) illustrates drain conductance versus  $V_{\rm gs}$  characteristics as a function of  $V_{\rm ds}$  on a similar graphene FET with the possibility of only one monolayer. The drain current at low drain voltage  $V_{\rm ds}$  = 0.2 V is around 2×10<sup>-6</sup> A, which corresponds to a sheet conductivity of  $2e^2/h$ , the same order as  $4e^2/h$  for a single graphene layer. A clear *n*-type to *p*-type transition, a critical feature for the graphene band structure, is also observed after gate bias sweeps beyond -20 V. The SiO<sub>2</sub> is 120 nm thick, with the gate leakage current less than  $10^{-7}$  A under gate bias from -22 to 20 V. From the simple calculation described above, the hole mobility and electron mobility are 4400 and 2000 cm<sup>2</sup>/V s, respectively. The origin of the observed flat features at the n-type to p-type transition is unclear. It could be introduced by substrate leakage current related to the relative low substrate resistivity (on the order of  $10^5 \Omega$  cm) of the semi-insulating SiC substrate. This does not exclude the possibility of opening a bandgap in the top monolayer of graphene, coupled with a buffer graphene layer.<sup>20</sup> In particular, the narrowing plateau feature with increasing drain voltage fits the bandgap picture well. It could also be related to the coexistence of thermally activated electrons and holes near the Dirac point at room temperature.<sup>23</sup> It could also be related with creating a large fluctuating region, where average carrier density is smaller than disorder or domain boundary induced fluctuations.<sup>24</sup> More experimental and theoretical studies are needed to clarify these points. The drain conductance is not independent of drain voltage, since device operation could become complicated if part of the channel is negatively gate-biased and part is positively gatebiased, as referenced to the neutrality point or Dirac point.

In summary, few-layer graphene FET fabricated on decomposed semi-insulating SiC substrates with  $SiO_2$  as gate dielectric is fabricated. A clear n-type to p-type transition at the Dirac point is observed. A maximum electron mobility of  $5400 \text{ cm}^2/\text{V} \text{ s}$  and hole mobility of  $4400 \text{ cm}^2/\text{V} \text{ s}$  is achieved. Graphene is a promising electronic material for future nanoelectronics, due to its high carrier mobility

and high Fermi velocity compared to conventional semiconductors

The authors would like to thank J. Appenzeller, M. S. Lundstrom, and L. Rokhinson for the valuable discussions.

<sup>1</sup>H. Shang, H. Okorn-Schimdt, J. Ott, P. Kozlowski, S. Steen, E. C. Jones, H. S. P. Wong, and W. Hanesch, IEEE Electron Device Lett. **24**, 242 (2003).

<sup>2</sup>P. D. Ye, G. D. Wilk, J. Kwo, B. Yang, H.-J. L. Gossmann, M. Frei, S. N. G. Chu, J. P. Mannaerts, M. Sergent, M. Hong, K. Ng, and J. Bude, IEEE Electron Device Lett. **24**, 209 (2003).

<sup>3</sup>S. J. Tans, R. M. Verschueren, and C. Dekker, Nature (London) **393**, 49 (1998).

<sup>4</sup>A. Javey, G. Jing, W. Qian, M. Lundstrom, and H. Dai, Nature (London) **424**, 654 (2003).

<sup>5</sup>S. J. Wind, J. Appenzeller, R. Martel, V. Derycke, and P. Avouris, Appl. Phys. Lett. **80**, 3817 (2002).

<sup>6</sup>A. K. Geim and K. S. Novoselov, Nat. Mater. **6**, 183 (2007).

<sup>7</sup>K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, Science **306**, 666 (2004).

<sup>8</sup>Y. Zhang, Y. W. Tan, H. L. Stormer, and P. Kim, Nature (London) 438, 201 (2005).

<sup>9</sup>C. Berger, Z. Song, X. Li, X. Wu, N. Brown, C. Naud, D. Mayou, T. Li, J. Hass, A. N. Marchenkov, E. H. Conrad, P. N. First, and W. A. de Heer, Science 312, 1191 (2006).

<sup>10</sup>M. C. Lemme, T. J. Echtermeyer, M. Baus, and H. Kurz, IEEE Electron Device Lett. 28, 282 (2007).

<sup>11</sup>G. Gu, S. Niu, R. M. Feenstra, R. P. Devaty, W. J. Choyke, W. K. Chan, and M. G. Kane, Appl. Phys. Lett. **90**, 253507 (2007).

<sup>12</sup>V. W. Brar, Y. Zhang, Y. Yayon, T. Ohta, J. L. McChesney, A. Bostwick, E. Totenberg, K. Horn, and M. F. Crommie, Appl. Phys. Lett. **91**, 122102 (2007).

<sup>13</sup>Y. Xuan, Y. Wu, T. Shen, M. Qi, M. A. Capano, J. A. Cooper, and P. D. Ye, Appl. Phys. Lett. **92**, 013101 (2008).

<sup>14</sup>J. R. Willaims, L. DiGarlo, and C. M. Marcus, Science 317, 638 (2007).

<sup>15</sup>D. B. Farmer and R. G. Gordon, Nano Lett. 6, 699 (2006).

<sup>16</sup>M. Y. Han, B. Ozyilmaz, Y. Zhang, and P. Kim, Phys. Rev. Lett. 98, 206805 (2007).

<sup>17</sup>P. Avouris, Z. Chen, and V. Peterbeinos, Nat. Nanotechnol. **2**, 605 (2007). <sup>18</sup>T. Ohta, A. Bostwick, T. Seyller, K. Horn, and E. Rotenberg, Science **313**,

<sup>18</sup>T. Ohta, A. Bostwick, T. Seyller, K. Horn, and E. Rotenberg, Science 313, 951 (2006).

<sup>19</sup>J. B. Oostinga, H. B. Heersche, X. Liu, A. F. Morpurgo, and L. M. K. Vandersypen, arXiv:cond-mat/0707.2487.

<sup>20</sup>S. Y. Zhou, G.-H. Gweon, A. V. Fedorov, P. N. First, W. A. de Heer, D.-H. Lee, F. Guinea, A. H. Castro Neto, and A. Lanzara, arXiv:cond-mat/0709.1706.

<sup>21</sup>B. Huard, J. A. Sulpizio, N. Stander, K. Todd, B. Yang, and D. Goldhaber-Gordon, Phys. Rev. Lett. 98, 236803 (2007).

<sup>22</sup>B. Ozyilmaz, P. Jarillo-Herrero, D. Efetov, D. A. Abanin, L. S. Levitov, and P. Kim, Phys. Rev. Lett. 99, 166804 (2007).

<sup>23</sup>T. Fang, A. Konar, H. L. Xing, and D. Jena, Appl. Phys. Lett. **91**, 092109 (2007).

<sup>24</sup>M. M. Fogler, L. I. Glazman, D. S. Novikov, and B. I. Shklovskii, arXiv:0710.2150.

Downloaded 24 Nov 2008 to 128.46.220.88. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp