### **INFORMATION TO USERS**

The most advanced technology has been used to photograph and reproduce this manuscript from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book. These are also available as one exposure on a standard 35mm slide or as a 17" x 23" black and white photographic print for an additional charge.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

# U·M·I

University Microfilms International A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

Order Number 9011126

#### **Topologies:** Distributed objects in multicomputers

Bo, Win, Ph.D.

.

The Ohio State University, 1989

Copyright ©1989 by Bo, Win. All rights reserved.

### **TOPOLOGIES: DISTRIBUTED OBJECTS IN**

### **MULTICOMPUTERS**

#### DISSERTATION

Presented in Partial Fulfillment of the Requirements for

the Degree Doctor of Philosophy in the Graduate

School of the Ohio State University

By

Win Bo, B.E., M.S.

#### \* \* \* \* \*

The Ohio State University

1989

**Dissertation Committee:**

Dr. Karsten Schwan

Dr. Bruce Weide

Dr. Ponnuswamy Sadayappan

Dr. Richard Parent

Approved by

Bruce mineide

Adviser

Department of

**Computer and Information Science**

© Copyright by Win Bo 1989

•

To My Parents, U Ba Swe and Daw Ma Ma, My Wife, Nge, and My Son, Kyaw

.

.

### ACKNOWLEDGEMENTS

• :

First, I would like to thank Dr. Karsten Schwan, whose encouragement, guidance, understanding, and substantial aid in thesis writing, made this work possible. His advice and assistance have been immensely valuable throughout the entire period of study and research. I would also like to thank Dr. Bruce Weide whose comments on the thesis have been very beneficial and greatly appreciated.

Next, I would like to thank my parents, U Ba Swe and Daw Ma Ma, who cultivated in me the value of education and continually encouraged and supported my pursuit of it. I thank my wife, Nge, for sharing the frustrations, tolerating several lonely nights, and for continually encouraging me throughout the difficult times.

I would also like to thank other members of the research group who have helped with many suggestions and have answered many of my questions. Some of the work described in this thesis involved contributions by Nena Bauman, John Gawkowski, Ben Blake, Rajiv Ramnath, Steve Martin, Fikret Ercal, Cevdet Aykanat, and Siva Monhanachandran. Also, Paul Pierce at Intel Scientific Computers had offered several helpful tips for implementation.

This research would have been impossible without the sponsorship and support

of Universal Energy Systems, the Thomas Alva Edison Program of the State of Ohio, the Intel Corporation, and the Department of Computer and Information Science at the Ohio State University.

### Vita

| August 9, 1953Born - Mandalay, Burma                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------|

| 1977 BE, The Department of Electrical Engineering,<br>Rangoon Institute of Technology, Rangoon, Burma                      |

| 1981 MS, The Department of Computer and Information<br>Science, The Ohio State University, Columbus, Ohio                  |

| 1985-Present PhD Student, The Department of Computer and Information<br>Science, The Ohio State University, Columbus, Ohio |

#### PUBLICATIONS

- 1. "OS Primitives for Implementing Distributed Objects: An Experiment in Parallel Branch-and-Bound Algorithm", Proceedings of the 4th. Intl. Conf. on Hypercube Concurrent Computers and Applications, March, 1989 (With Karsten Schwan, Ben Blake, and John Gawkowski).

- 2. "Topologies Computational Messaging for Structured Multicomputers", Proceedings of the 3rd. Intl. Conf. on Hypercubes Concurrent Computers and Applications, Jan., 1988 (With Karsten Schwan).

- 3. "Mapping Parallel Applications to Hypercubes", Proceedings of the 2nd. Intl. Conf. on Hypercube Concurrent Computers and Applications, Sept, 1986 (With Karsten Schwan, P. Sadayappan, F. Ercal, and N. Bauman).

#### FIELDS OF STUDY

Major Field: Computer and Information Science Studies in Operating Systems: Dr. Karsten Schwan Studies in Computer Architecure: Dr. P. Sadayappan Studies in VLSI and VLSI Algorithms: Dr. T. H. Lai

# **Table of Contents**

| DE                   | DIC   | <b>ATION</b>                                              | ii   |

|----------------------|-------|-----------------------------------------------------------|------|

| ACKNOWLEDGEMENTS iii |       |                                                           |      |

| VITA                 |       |                                                           |      |

| LIS                  | ST OI | F TABLES                                                  | ix   |

|                      |       | F FIGURES                                                 | xi   |

|                      |       |                                                           |      |

| C                    | CHAP  | TER                                                       | PAGE |

| I                    | Intr  | roduction                                                 | 1    |

|                      | 1.1   | Parallel Programs on Structured Multicomputers            | 1    |

|                      | 1.2   | Topologies—Distributed Objects in Multicomputers          | 3    |

|                      | 1.3   | Motivation                                                | 5    |

|                      | 1.4   | Desirable Properties of a Topology's Communication Struc  | -    |

|                      |       | ture                                                      | 9    |

|                      | 1.5   | Usefulness of Topologies                                  | 11   |

|                      | 1.6   | The Thesis                                                | 12   |

|                      | 1.7   | Contributions                                             | 13   |

|                      | 1.8   | Scope, Goals, and Dissertation Overview                   | 13   |

| II                   | Sur   | vey of Related Work                                       | 15   |

|                      | 2.1   | IPC Structures                                            | 15   |

|                      | 2.2   | IPC Support On Structured Multicomputers                  | 21   |

|                      | 2.3   | Activeness in Message-based IPCs                          | 23   |

|                      | 2.4   | Novel IPC Semantics                                       | 26   |

|                      | 2.5   | <b>Programming Environments and Program Visualization</b> | 27   |

|                      | 2.6   | Conclusions                                               | 31   |

|                      |       |                                                           |      |

| III                  | Dec   | omposition Methods: Global Data and Operations            | 32   |

|                      | 3.1   | Domain Decomposition and Global Data                      | 32   |

|                      | 3.2   | Domain Decomposition and Global Operations                | 33   |

|                      | 3.3   | Divide and Conquer and the Task/Queue Model               | 34   |

|                      | 3.4   | Functional Decomposition and Pipelining                   | 35   |

|               | 3.5                                                        | Multiple Phases                                         | 36  |

|---------------|------------------------------------------------------------|---------------------------------------------------------|-----|

|               | 3.6                                                        | Global Data and Operations in Operating Systems         | 36  |

|               | 3.7                                                        | Conclusions                                             | 39  |

| IV            | IV Experimental Testbed and Sample Parallel Applications 4 |                                                         |     |

|               | 4.1                                                        | Testbed Environment                                     | 40  |

|               |                                                            | 4.1.1 Hardware                                          | 40  |

|               |                                                            | 4.1.2 Software                                          | 43  |

|               | 4.2                                                        | A Finite Element Modeling Program                       | 44  |

|               | 4.3                                                        | A Traveling Salesperson Program                         | 48  |

|               | 4.4                                                        | Conclusions                                             | 53  |

| $\mathbf{v}$  | Tor                                                        | oologies                                                | 54  |

|               | 5.1                                                        | Topologies—Basic Definition                             | 54  |

|               |                                                            | 5.1.1 Services (Object Operations)                      | 62  |

|               |                                                            | 5.1.2 Topologies-Extended Definition                    | 63  |

|               | 5.2                                                        | Topologies—Instantiation and Binding                    | 64  |

|               | 5.3                                                        | Programming with Distributed Objects                    | 67  |

|               |                                                            | 5.3.1 Using Topologies                                  | 67  |

|               |                                                            | 5.3.2 Writing Services                                  | 70  |

|               | 5.4                                                        | Using Topologies to Program Global Data and Operations  | 71  |

|               |                                                            | 5.4.1 The FEM Application                               | 71  |

|               |                                                            | 5.4.2 The TSP Application                               | 77  |

|               | 5.5                                                        | Conclusions                                             | 84  |

| VI            | $\mathbf{Im}$                                              | plementation and Evaluation of Topologies               | 86  |

|               | 6.1                                                        | Implementation of Topologies                            | 86  |

|               | 6.2                                                        | Performance and Implementation of Topology System Calls | 91  |

|               | 6.3                                                        | Performance of Topologies Spanning Multiple Processes   | 94  |

|               |                                                            | 6.3.1 A Small Synchronous Topology                      | 95  |

|               |                                                            | 6.3.2 Asynchronous Topologies                           | 97  |

|               |                                                            | 6.3.3 Larger Synchronous Topologies                     | 100 |

|               | 6.4                                                        | Performance and Usefulness of Topologies with Applica-  |     |

|               |                                                            | tion Programs                                           | 104 |

|               |                                                            | 6.4.1 The FEM Application.                              | 104 |

|               |                                                            | 6.4.2 The TSP Application.                              | 106 |

|               | 6.5                                                        | Conclusions                                             | 110 |

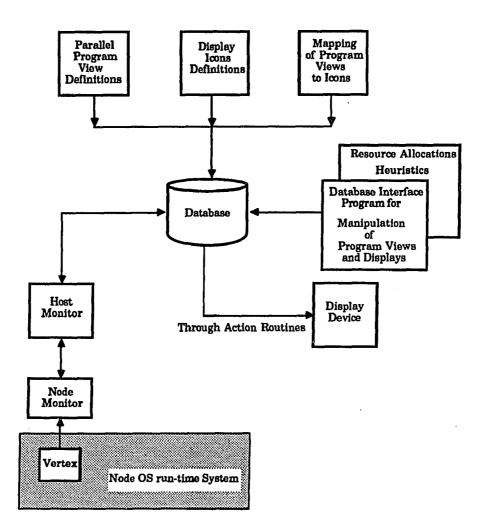

| $\mathbf{VI}$ | [ PF                                                       | <b>RISM—A Programming Environment for Topologies</b>    | 111 |

|               | 7.1                                                        | A Structured Multicomputer Programming Environment      | 111 |

|               |                                                            | 7.1.1 System Requirements                               | 111 |

|       |       | 7.1.2  | Basic Features of PRISM                                 | 113          |

|-------|-------|--------|---------------------------------------------------------|--------------|

|       | 7.2   | Progra | amming Topologies                                       | 117          |

|       |       | 7.2.1  | Topology Compiler                                       | 117          |

|       |       | 7.2.2  | Mapping of a Topology                                   | 119          |

|       |       | 7.2.3  | Loader                                                  | 120          |

|       |       | 7.2.4  | A Vertex-monitoring Utility                             | 121          |

|       |       | 7.2.5  | Support System Calls for Services                       | 122          |

|       | 7.3   | Manip  | oulation of Programmed Topologies                       | 123          |

|       |       | 7.3.1  | The Database Model and Interface                        | 125          |

|       |       | 7.3.2  | Entities, Relationships, and Sets                       | 126          |

|       |       | 7.3.3  | Action Routines                                         | 127          |

|       |       | 7.3.4  | Database Operations                                     | 128          |

|       | 7.4   | Topol  | logies and Their Graphical Views in E-R Model           | 134          |

|       |       | 7.4.1  | <b>Representing Vertices and Edges</b>                  | 135          |

|       |       | 7.4.2  | <b>Representing Processors and Communication Links</b>  | 3 136        |

|       |       | 7.4.3  | <b>Representing Mapping of a Topology to Processors</b> | 137          |

|       |       | 7.4.4  | Representing Graphical Icons                            | 137          |

|       |       | 7.4.5  | Mapping E-, R-, and S-Entities to Graphical Entities    | 3 141        |

|       |       | 7.4.6  | Estimating Database Size                                | 144          |

|       | 7.5   | Imple  | mentation and Evaluation of PRISM                       | 147          |

|       |       | 7.5.1  | Implementation of the PRISM Database                    | 147          |

|       |       | 7.5.2  | Implementation of the DML Programs                      | 149          |

|       | 7.6   | Conclu | usions                                                  | 161          |

| * * * | TT ~  |        |                                                         |              |

| VI    |       |        | ons and Future Research                                 | 162          |

|       | 8.1   |        | w of the Goals                                          | 162          |

|       | 8.2   |        | ary of Lessons Learned                                  | 163          |

|       | 8.3   | Future | e Research                                              | 166          |

| ٨T    | איזסכ | DICES  | 2 D/                                                    | <b>AGE</b>   |

| A     |       |        | alls for Services                                       | 169          |

| л     | •     |        | ed Descriptions                                         | 171          |

|       | A.1   | Detail |                                                         | <b>T 1 T</b> |

| В     |       |        | of Topology Description Language                        | 180          |

| BI    | BLIO  | GRAP   | HY                                                      | 183          |

-

# List of Tables

| 6.1  | Latency of TopSend System Call                                        |

|------|-----------------------------------------------------------------------|

| 6.2  | Latency of TopRecv System Call                                        |

| 6.3  | A Linear Topology vs. iPSC Messages (nonlocal communications) . 96    |

| 6.4  | A Linear Topology vs. iPSC Messages (local communications) 96         |

| 6.5  | A Ring Topology vs. User-level Ring                                   |

| 6.6  | Latencies of User-memory Update                                       |

| 6.7  | A Tree Topology vs. User-level Tree                                   |

| 6.8  | Best and Worst Performances of the Global-sum Topology $\ldots$ . 103 |

| 6.9  | Solution Times for the FEM Application                                |

| 6.10 | Maximum Retransmission Counts of the FEM Application 106              |

| 6.11 | Performance of A Shared-memory Ring Topology                          |

| 6.12 | Completion Times of the TSP Application                               |

| 7.1  | Estimated Database Storage Requirements                               |

# List of Figures

.

•

•

| 1.1 | A Distributed Queue Object                        | 5          |

|-----|---------------------------------------------------|------------|

| 4.1 | The Hypercube Interconnection                     | <b>1</b> 1 |

| 4.2 | Testbed—Cube Manager and the Hypercube            | 13         |

| 4.3 | Node Architecture                                 | 14         |

| 4.4 | Strip Mapping and the Linear Chain of Processors  | 16         |

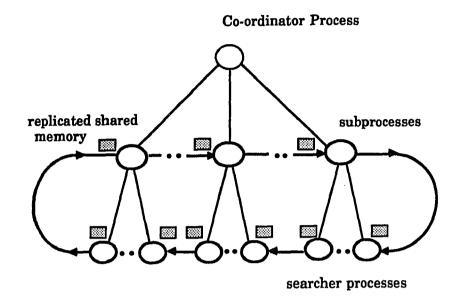

| 4.5 | Three-level Process Structure for Solving the TSP | 50         |

| 5.1 | Topology—A Distributed Object                     | i5         |

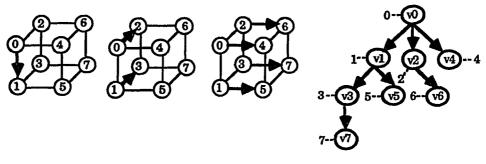

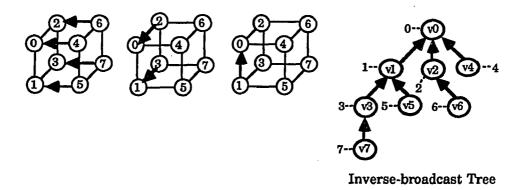

| 5.2 | Broadcast and Inverse-broadcast Trees             | 71         |

| 5.3 | Shared-memory Ring Topology                       | 18         |

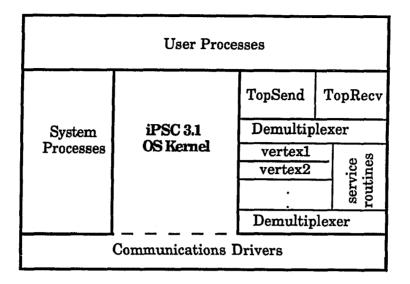

| 6.1 | Extended Node OS Kernel                           | 38         |

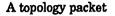

| 6.2 | Demultiplexing a Topology Packet                  | 39         |

| 7.1 | The PRISM Programming Environment                 | 4          |

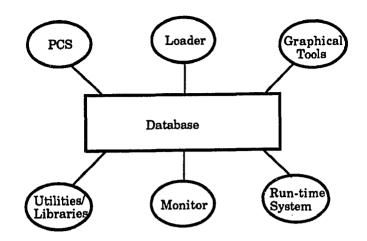

| 7.2 | Logical and Mapped Ring                           | 20         |

| 7.3 | Topology Manipulation Tools                       | 24         |

| 7.4  | High-level and Low-level Tools Integrated Through the Database 125 |

|------|--------------------------------------------------------------------|

| 7.5  | Different Representations of a Vertex and an Edge                  |

| 7.6  | D5 Hypercube                                                       |

| 7.7  | A Spanning Tree Topology                                           |

| 7.8  | A Ring Topology                                                    |

| 7.9  | Subtree of Vertex Id 1                                             |

| 7.10 | Leave Vertices at 2nd Level of the Tree                            |

| 7.11 | Vertices Mapped to a Hypercube                                     |

| 7.12 | Logical Tree Structure of Processors                               |

| 7.13 | Logical Ring Structure of Processors                               |

.

### CHAPTER I

### Introduction

### **1.1 Parallel Programs on Structured Multicomputers**

Structured multicomputers such as hypercubes and toroidal or pyramidal multicomputers are gaining wide acceptance, in part due to a natural match of their physical interconnection structures to the logical communication structures of many scientific applications [25, 80, 10, 60]. However, current multicomputers are hard to program for three reasons:

- 1. Any parallel program with a large number of tasks and communication channels is difficult to design, implement, and debug [35].

- 2. Multicomputers such as hypercubes are harder to program than sharedmemory multiprocessors because programmers have to construct complex communication structures such as trees or rings spanning many application processes and hypercube nodes. Such structures may be inherent parts of an application's computation, or they may be auxiliary structures superimposed

[38] by the programmer or used by the operating system [33] for purposes of maintaining multiple program views for program control, monitoring, debugging, or other purposes [74, 48, 75, 81]. In current multicomputer operating systems, such structures must be built from OS primitives and physical communication links that connect only two nodes at a time.

3. One issue in the programming of multicomputers is that (as with all other parallel applications) good speedup of execution by use of parallelism cannot be attained unless efficient use is made of the multicomputer's distributed processors and memories. This requires decomposition of the application program into multiple, independently executable processes such that global data and control, and therefore interprocess communication, are minimized [75, 35, 25].

This dissertation introduces an operating system and programming construct termed *topology*—that allows programmers to build distributed objects that may internally consist of complex computational communication structures. It provides a versatile mechanism for interprocess communication and structuring of tasks. As an interprocess communication mechanism (IPC) it allows communications among multiple tasks transparent to the user program. As a structuring mechanism it provides an object-oriented view of shared resources in the multicomputer. It may implement distributed objects performing a wide variety of functions, including the exchange of data or control information relevant to the tasks' computations and/or communications required for task synchronization, message forwarding and filtering under program control, and others.

### **1.2** Topologies—Distributed Objects in Multicomputers

As a widely accepted paradigm, the *object* model has been used for designing operating systems, languages, and architectures. It is attractive for its ability to provide abstractions and a uniform and simple model of programming. A distributed object, similar to the conventional object, provides abstractions for parallel and distributed programs and consists of a distributed data representation and a set of operations that can be performed on an instance of the object. For instance, a distributed queue object may be abstracted as a single queue consisting of queue elements distributed across several processors and insert and delete operations performed in a parallel and cooperative manner on an instance of the queue. The operations can be implemented to enforce different queuing disciplines, such as a priority queue or a first-in-first-out queue.

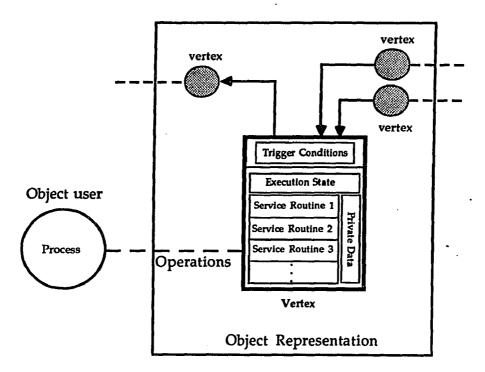

Topologies are distributed objects implementing abstractions on a structured multicomputer such as a hypercube. A topology consists of a distributed data type and a set of operations concurrently executable on the multicomputer's processors. However, unlike object implementations on network architectures [46, 2, 67] or other multiprocessors [22, 7, 73, 28], it enforces the distribution of data representing an object and of the object's operations to match the architecture and the parallel applications using the object. Distribution is expressed in terms of explicitly defined interconnections of a set of nodes implementing the object's data and operations, hence the term "topology".

Each topology implements a distributed object as an arbitrary communication graph linking multiple nodes, which in turn may be attached to specific processors of the parallel program. The operations of a topology are performed cooperatively by the nodes linked by the graph. Specific attributes of a topology are

- *multiple connectivity*—multiple nodes may be linked by a communication structure defined by the graph,

- activeness—a topology employs an active message-passing mechanism that performs distributed computations, and

- separation of concerns—topologies can be constructed independently of the applications using them.

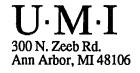

As a simple example, a distributed queue object among three producers and one consumer, each on a different processor, can be implemented as a tree topology with the root node (consumer) and three children (producers) (Figure 1.1). In the figure the gray rectangular area denotes the queue object, consisting of directed edges representing the communication links, and the black dots representing the tree's nodes, where distributed data (queue elements) are stored and distributed

Figure 1.1: A Distributed Queue Object

operations (such as insert and remove) are executed. Parallel insertions by producers are not ordered, and therefore each node attached to a producer either buffers the data locally or forwards it to the consumer. Removal by the consumer retrieves data buffered locally or on one of the producers' processors. The routines to perform insert operations are distributed and replicated on the producers' processors so they can be executed in parallel. Thus, the tree topology provides the abstraction of a *queue*, but its structure and internal interprocess communication are invisible to the user of the queue.

#### **1.3** Motivation

As stated in the previous section, topologies differ from other implementations of distributed objects in that they are distributed implementations of objects; data and operations in each topology have a well-defined communication structure which is crucial to its performance. Most parallel systems do not provide extensive support for such explicitly structured abstractions. A set of processes in a parallel application either communicates in an unstructured manner, or the communication structure is hidden in the processes' implementations. Some exceptions are the Hierarchical Process Composition (HPC) system [45] where an object-oriented model is used to specify the connections between processes and Thoth [14] where a process may have several sub-processes within its address space. However, in HPC, communication structures are composed of low-level connections that are incapable of performing computations. In Thoth, high level descriptions of the communication structures are not represented as long-term connections among processes.

Difficulty in structuring mainly stems from the currently available IPC mechanisms in multicomputers. Existing mechanisms are based on a message passing between two processes. In general, there are two basic communication primitives: *send* and *receive*. The *send* primitive specifies the destination process identifier and a message. The *receive* primitive specifies the sender process identifier and the buffer to receive the message. One process executes a send call while the other executes a matching receive call. The process identifiers of both sender and receiver must be globally known to use these primitives.

The premise of the topology concept is that the communication structures

within a distributed object on a multicomputer should not be hidden from their implementor. Instead, such structures should be explicitly programmable as separable units in implementing the objects.

Although topologies define communication structures among several tasks, they differ from other IPC's in several ways. First, conventional message-based IPC's provide general-purpose channels with which a variety of functions may be implemented. In contrast, topologies are abstractions implementing well-defined operations. For instance, a tree structure of processes can form a logical multicast bus, allowing values from one process (the root) to send values to the remaining processes. A topology describes such a structure as a *multicast bus object* offering the operations *multicast-send* and *multicast-receive*. The implementation of such a structure using IPC constructs would require that addressing information be maintained throughout the processes using the structure. Such low-level information is not visible to the users of a topology. Instead, a topology has a global name and the semantics of its operations determine which of the processes invoking it are affected by the operations' executions.

A second difference between topologies and conventional IPC constructs concerns the implementation of a topology's operations. With conventional IPC constructs, the precise semantics of *send* and *receive* are determined at operating system design time. This may not provide a convenient or efficient basis for the implementation of the specific semantics required by an application. For example, it may be impossible to route messages using an application-specific routing algorithm or to terminate the message forwarding based on the state of a particular process participating in the IPC. In contrast, for a topology, the ability to perform computations in conjunction with the messages transferred on its communication links facilitates implementation of a wide range of link semantics.

Since topologies may be used to implement arbitrary, distributed abstract data types, their efficient implementation requires support by low levels of the operating system. Efficiency is gained by avoiding unnecessary layers of protocol [85]. In addition, low-level support must be provided such that message-sending and receiving semantics remain variable as with packet filters in Mach [1]. An example of such variability is the implementation of a user-defined routing algorithm as part of a topology.

Two additional benefits arise from the decision to support topologies at the operating system level. First, once a topology has been constructed, it can be shared by multiple applications and it can be reused. The client thus treats it like any other operating system resource. Second, language-independent interfaces to topologies encourage their use in a wide variety of parallel applications.

As with the programming of communication protocols, programming topologies can be complex. For instance, it is difficult to debug a large structure mapped onto a hypercube of dimension 4 or more partly because it is hard to visualize the structure. Complexity in debugging may be compounded by the fact that computations are performed on messages in transit which makes it difficult to keep track of partial or incomplete results. Thus, an effective use of topologies in the development of parallel applications requires support tools for topology specification, loading, and debugging. In addition, manipulation of topologies' structures and selection of sub-structures based on certain attributes should be facilitated. Such manipulation should be provided in conjunction with tools for the visualization of multiple views of topologies. The development and evaluation of tools for topology visualization and manipulation for debugging is the second thrust of this thesis.

To conclude, we note that the communication structure of a topology depends on its intended use by a parallel application. Thus, it may not be identical to the structure of the underlying multicomputer. The efficient mapping of the topology to the multicomputer [64] is application dependent and is left to the applications programmer.

### 1.4 Desirable Properties of a Topology's Communication Structure

To provide abstractions through the distributed object model, a topology's communication structure must be powerful enough to implement a wide range of functionalities required in the distributed objects. An ideal communication structure should have the following properties:

- Flexibility—Efficiency and ease of abstraction require that the composite structure of communication links should be changeable. It should support simple one-to-one connections to a regular structure such as a mesh, a tree, or arbitrary graphs. The structure should be scalable with the number of processes linked by it and should not depend on the underlying hardware. Furthermore, it should be able to be created and deleted dynamically, it should be possible to add and delete communication links dynamically, and links should be migratable from one processor to another.

- 2. Variable semantics of link protocols—Ease of representation of arbitrary, distributed operations requires that the semantics of each communication link should be variable along the following dimensions:

- (a) protocol attributes such as time-out periods, flow control, or acknowledgments;

- (b) send/receive semantics such as blocking/nonblocking, buffering/nonbuffering, or return/no return information;

- (c) multiplexing of logical onto physical communication channels;

- (d) typed/untyped logical channels; and

- (e) implicit logical channels that accept and forward (to the intended recipient) a message even when there is no matching *receive* operation.

- 3. Ability to map communication structures to physical machines—Independence of physical communication structures requires that topologies with arbitrary structures be mappable to the physical hardware.

- 4. Ease of programming/debugging—The programming of communication structures and of the computations associated with the structures should be straightforward. In addition, it requires the availability of debugging and powerful program visualization tools since communication structures may span a large number of processes and processors. For debugging, the state of communication structures and the messages in these structures must be monitorable and controllable. This implies that communications structures should be compositional such that complex structures may be formed as compositions of multiple, simple structures.

#### **1.5 Usefulness of Topologies**

Topologies are useful and important elements of any parallel application on a multicomputer. For instance, a linear topology may act as a simple communication link object connecting two processes. In this case, data is not manipulated but simply transferred. Alternatively, a broadcasting object may be implemented as a binary-tree topology, and this tree may be used to broadcast values sent by the root process to all connected processes. In this case, the computations performed by each link consist of buffering and forwarding the values at intermediate nodes. The simple examples above demonstrate the usefulness of topologies. More importantly, however, topologies are a necessary element of most parallel applications because they can efficiently represent the global data and operations required by the application. It is well known[76, 35] that the appropriate implementation of global data and operations in parallel programs is important for several reasons:

- Global data or operations are unavoidable. Any decomposition method for a serial program will require the resulting parallel program's use of some global operations or data as shown in Chapter 3.

- 2. Global data and operations significantly affect performance. Application programs may spend significant amounts of time in nonlocal program portions[35, 76]. More generally, in the absence of other serial phases of a parallel program, sequential implementations of global data and operations limit the parallel program's maximal possible speedup to 1/a, where a is the fraction of the program's total execution time consumed by global data access or global operation execution (a version of Amdahl's law).

#### 1.6 The Thesis

The thesis of this dissertation is that topologies are useful and desirable constructs for programming parallel programs on multicomputers. Furthermore, they are efficient and appropriate for programming global data and operations.

### 1.7 Contributions

The major contributions of this thesis are

- the development of topologies, which are novel high-level constructs for the specification and implementation of distributed objects in a parallel program, and

- the demonstration of the ease of programming of topologies by the provision of a set of tools for their programming and debugging, and examples of their use.

### 1.8 Scope, Goals, and Dissertation Overview

This dissertation focuses on two issues—the runtime support for topologies and the ease of programming of topologies. Although some of the design decisions resulted from the specific characteristics of nex, the Intel iPSC/1 hypercube's node operating system, the basic concept of topologies is readily applicable to other parallel systems.

To prove the thesis, this dissertation addresses three major topics:

1. Desirability of topologies. Chapter 3 and 4 show that topologies are desirable primitives for the interconnection of parallel tasks. Chapter 3 describes various methods of decomposition of parallel applications; each of which results in global data and operations that are efficiently programmed

with topologies. Chapter 4 describes two typical parallel applications and identifies their global data and operations, and Chapter 5 shows how topologies are conveniently used for programming them.

- 2. Appropriateness of the topologies construct with respect to implementation. Chapter 5 describes the topology construct and its components, and Chapter 6 describes the implementation and performance evaluation of the construct. These two chapters show that the construct can be built and used and that it is efficient. Thus, it is a realistic primitive.

- 3. Ease of programming of topologies. Chapter 6 describes the tools and facilities for specifying, compiling, and loading topologies, and it shows that topologies are easily programmable demonstrating tools for the visualization of topologies for debugging and monitoring.

### **CHAPTER II**

### Survey of Related Work

A topology is characterized by (i) multiple process interconnection, (ii) its active message-passing mechanism, and (iii) its capability to be constructed and programmed separately from application programs. In this chapter, other research related to these aspects of topologies is described. Accordingly, the chapter is organized as three sections: (i) process connection and IPC structures, (ii) IPC support on multicomputers, and (iii) programming environment and program visualization support for software components.

#### 2.1 IPC Structures

Few systems offer IPC constructs that can establish entire IPC structures connecting many processes. However, simpler IPC constructs are an integral part of many operating systems. Those systems that offer some support for the establishment of IPC structures are reviewed here. Demos' Switchboard Process. In the Demos Operating System [5] process connections are established by means of a *switchboard* process. Initially, each process only possesses a link to the switchboard process. A link is a simplex communication path that is addressable by a link identifier and can be created and destroyed dynamically. When a process wishes to communicate with another named process, it sends a message to the switchboard process. The switchboard process matches pairs of processes based on the name specified and passes the link from one process to another. This allows a process to form a connection with another consenting process. While complex structures may be built in this fashion, they must be constructed explicitly from many process-to-process connections as is the case with IPC constructs in other research and commercial operating systems such as StarOS [33], Medusa [59], Argus [46], Mach [87], and Unix [63].

Unlike Demos' IPCs which perform several process-to-process connections through a switchboard process to create an IPC structure, the communication structure of a topology is set up as a whole, independent of the processes using the topology.

SMP's IPC Structures. SMP [44] is a message-based programming environment that supports the construction of process families—a set of processes that communicate via asynchronous messages according to a given interconnection structure and naming scheme. It is very similar to topologies in that arbitrary structuring is allowed. The interconnections within the family are defined in a special data structure called *topology*, which is provided during process creation. This data structure is used by the SMP implementation to allocate buffers and to enforce the interconnection restrictions. Communications employ the family name and a list of family members to specify message recipients. Similarly, the recipients use the family name and list of family members to identify the messages to be received.

Enforcing a process structure based on a given interconnection pattern is similar for both SMP and topologies. But naming differs in that SMP requires both the name of the family of processes and the list of family members while topologies only require the structural name. Also SMP channels are passive while topologies have links that can perform computations.

HPC's IPC Structures. HPC—Hierarchical Process Composition [45], is a design that supports hierarchical communication structures. Each process is defined as an object consisting of an internal state, an executable code, and a set of communication interfaces. A composite object is constructed by a combination of already created objects, communication channels among those objects, an encapsulation *shell*, and a set of interfaces to the external world. Object connections are unidirectional channels, and they are established by

connect calls on the objects' local interfaces. The location and identity of the partners of such connections are transparent. Connect calls are executed and channels are created by third parties called *controllers*. The controller associated with each shell modifies and maintains the arbitrary connections among the processes or objects within the shell and enforces protection within the shell. Among shells, communication structures are hierarchical since shells are composed hierarchically.

HPC's IPC structures differ from topologies in that they are hierarchical, resulting in tree structures, whereas topologies can have arbitrary graph structures. One interesting aspect of HPC is the semantics of its communication interface. A communication interface can be a simple, a bundle (where a number of channels may be combined), a multicast or a multiplex interface. These semantics allow one-to-one, many-to-one, one-to-many, and many-to-many connections among objects. These semantics are fixed and cannot be modified whereas the semantics of the interface for topologies to an application process may be varied arbitrarily.

Charlotte's Links and Connector. Charlotte [3] is a distributed operating system with a communication package called *nugget* which provides process control and IPC. Its IPC provides full duplex links addressable by a link identifier and employs nonblocking send and receive calls. It can also cancel a send or a receive and destroy a link or transfer a link from one process to another. A process connection is established by two utility processes— Switchboard and Connector. The Switchboard helps client processes find server processes. Given a description of the processes and the links connecting them, the Connector searches for the process in the Switchboard, creates a new process from a given program file if it is not found, and sets up the links. An interesting aspect of Charlotte's IPC is the ability to cancel a message after it is sent and to perform link migration. However, Charlotte does not provide any facilities for connecting a set of processes or for addressing such a set as a single unit as in topologies.

Although Charlotte provides several interesting aspects, such as its ability to cancel a message after it is sent and link migration, it does not provide any facilities for connecting a set of processes or for addressing such a set as a single unit as topologies can. In addition, as in Demos and unlike topologies, Charlotte has a switchboard process to help establish the communication links.

Thoth's Multi-process Structuring. In Cheriton's Thoth system [14] a concurrent program is described at 3 levels: procedure call, data abstraction, and process. Thoth processes communicate via messages, and they may be grouped into teams, each consisting of a proprietor process which controls access to a resource and a set of helper processes (subprocesses) executing within the same address space as the proprietor, much like threads in Mach [1]. Connections between processes are implicit and short term, lasting from the time the sender sends a message to the time the receiver replies to it. During this connection, the receiver may transfer data to or from the sender or send a reply to the sender without blocking. Dynamic process creation and destruction allow the process structure to change dynamically.

In the Thoth System, the connections last until the receiver sends a reply message to the sender. Thus, the connections are short term and they are not reusable by another set of processes. In contrast, connections in the topologies are long term.

Other Systems. The summary of related research presented above is not complete regarding designs of systems offering IPC constructs. They are merely a representative sample of modern IPC systems. Implicit communication structures exist in IPCs which use a process identifier for addressing. One such facility is broadcasting and multicasting in Intel's iPSC/1 nex OS. It provides limited broadcasting and multicasting on the hypercube using process identifiers. The restriction is that the receiving processes must have the same process identifier and must be on a sub-cube including the sending node. Several other systems exist which support the connection of multiple processes. A multi-RPC facility [66] allows an RPC call to be multicasted to several servers with at-least-once semantics. In Cooper's Replicated Distributed Programs [16], Troupes form a group of replicated programs addressable by a single name. Also in Cheriton's V System, V process groups allow multicasting to a set of processes in a group using a group identifier. Caltech's MOOSE operating system has included two levels of process grouping in its design: teams—a collection of processes, and leagues—a collection of teams. These systems either offer a simple communication structure or have no explicitly defined structures at all.

### 2.2 IPC Support On Structured Multicomputers

Several of the currently available operating systems on structured multicomputers and on the hypercube in particular provide IPC as send and receive calls. These are low-level calls using as the process name a <processor identifier, process identifier> pair. The process name is global, and routing is simplified by the symmetry of the hardware topology. IPC's of some of the current operating systems are summarized below:

**CrOS.** The Crystalline Operating System (CrOS) [25] is an operating system for Caltech's Mark II and Intel iPSC hypercubes and is most suitable for algorithms that exhibit regular communication structures. Basic calls in CrOS II are *rdelt*, which receives a communication packet from a (physical) channel; *wtelt*, which sends a packet through (physical) channel; *rdres*, which receives a unique packet from the host; and *sendres*, which sends a unique packet to the host. In CrOS III, basic calls are *cread* and *cwrite*, which are similar to *rdelt* and *wtelt* respectively. They are all synchronous calls, and the operating system provides no routing of the packets. Special calls such as *pass*, *shift*, and *pipe* in CrOS II and *cshift*, *vshift*, *broadcast*, *combine*, and *concat* in CrOS III are provided to assist routing which must be performed by the node program. These calls are also synchronous and must be executed by all the node programs at roughly the same time. This forces the complete parallel program to be written in a synchronous style, whereas all communications are done in a lock-step fashion. It is a very low-level operating system with little concern for programmability.

MOOSE. MOOSE [65] is an operating system implemented on Caltech Mark II hypercubes for automatic load balancing. It provides multi-tasking, dynamic creation of processes, and priority-based scheduling. The IPC mechanism is *pipes* in the flavor of UNIX although the actual implementation is more like mailboxes with fixed record-length entries. A pipe is created by the system call *pipopen* with a depository on the named processor. System calls *pread* and *pwrite* can be used for exchange of data using pipes. Shared memory may be used if the processes are on the same processor. MOOSE also provides globally accessible semaphores for locking and synchronization.

**Reactive Kernel.** Reactive kernel [79] is an operating system for the Ametek Series 2010 toroidal multicomputer which, together with the Cosmic Programming Environment, addresses portability of the operating system. It consists of a set of daemon processes, utility programs, and libraries. The IPC is based on a message-passing model using process identifiers. The kernel is reactive or message driven since it schedules a process when a message it is waiting for has arrived, and it does not force a context switch until some system exception occurs or until it is blocked for another message. Another interesting aspect of its IPC is that messages are sent and received using buffers from a message heap. These buffers are explicitly allocated and deallocated for sending. A receive call returns a pointer to the buffer, avoiding buffer copy completely. Although sending and receiving messages occur between two processes only, it does allow multicasting by providing a list of destination processes. The reactive kernel has a notion of process groups, but it was only intended for cube sharing in terms of space rather than manipulating a set of processes as a unit.

#### 2.3 Activeness in Message-based IPCs

Operations in the distributed objects implemented by topologies can be executed in parallel, in a cooperative manner. Such cooperation is implemented with active message-passing. Active message-passing has been used in several related research efforts.

- RPC and Remote Invocation. Nelson's remote procedure call (RPC) [9] is an IPC mechanism for which the manner of association of application-dependent computations with IPC actions is particularly obvious. In addition, some changes in RPC semantics are easily made, as shown by Spector's work on remote memory operations [85], by Schwan's work on remote object invocation with varying invocation semantics [73], and by similar recent research at the University of Washington in the Presto Programming Environment [7]. Most of this research is similar in spirit to topologies in that it avoids the strict layering of communication protocols, thereby facilitating the efficient association of application-dependent computations with communications. In fact, a simple topology with a link from the caller to the remote node and a return link to the caller constitutes an implementation of a remote procedure call.

- Active Channels. Linvy and Manber's work on active channel [47] in Active TOken ring Network (ATON) is also related to active links in topologies. Here the token ring protocol is extended so that shift arithmetic operations may be performed directly on the node interfaces. Operations consist of 3 groups: arithmetic, selection, and counting. Each operation is executed as

a sequence of 1 bit operations by the ATON interface hardware consisting of a modem, an input state machine, an output state machine, and a 1-bit ALU. This makes active channels highly efficient for implementing a number of algorithms for determining global information such as minimum load on the ring network.

- Fetch-and- $\Phi$ . Another primitive similar in spirit to topologies is the Ultracomputer's fetch-and- $\Phi$  construct [76]. Although fetch-and- $\Phi$  operations are designed for accessing shared locations on shared-memory machines, they can be viewed as specialized topologies for process synchronization, where topologies are implemented as computational structures embedded in the machine's combining network. The queueing of memory requests and performing operations, as defined by  $\Phi$  functions implemented in the combining switches, are in essence identical to similar operations performed in topologies. In fact,  $\Phi$  exactly defines the computations of analogous topologies' links.

- Packet Filters. Packet filters [49] in the Mach operating system are another means of associating application-dependent operations with the IPC. A filter is a kernel- resident packet demultiplexer that can distinguish between packets according to arbitrary and dynamically variable user-specified criteria. A simple language is defined for specifying such filter predicates. The

filter predicates can be loaded in the kernel and interpreted, or they can be compiled together with the kernel. A received packet is matched with all local filters' predicates in the order of filter priority until it is either accepted by some filters or is rejected. An accepted packet is delivered to the user process while a rejected packet is dropped from the network.

#### 2.4 Novel IPC Semantics

Recent work [12, 11, 72] is beginning to look at process communication activities as the sharing of information among processes by use of message sending. If interpreted as *shared memory* in the sense of multiprocessor hardware, such global sharing in a multicomputer using messages can be expensive due to the communication cost imposed on each process. Such costs arise from the *sharedmemory* requirements of reliable communication, consistent sequencing, and efficient updating. They grow linearly with the number of processors involved [12] and worse than linearly if network failures are considered. Cheriton's ideas regarding problem-oriented shared memory are similar to our intended and actual uses of topologies [71] in that we contend that costs should be reduced by use of application-dependent forms of consistency and reliability. Thus, some of the generic characteristics identified by Cheriton are trivially and efficiently implemented as computational messages in topologies—e.g., detection of stale data on use, sufficient accuracy of stale data, optional data, discardable updates, and democratic memory.

In contrast to our notion of application-dependent sharing, Linda [11] supports a programming model based on a globally shared associative memory mechanism called *tuple space* that consists of data elements called *tuples*. Processes communicate by adding (writing), reading, and retrieving tuples from tuple space. However, it offers only one type of semantics for read or write—all shared information is strictly consistent and fully reliable. Application-dependent forms of sharing cannot be done in Linda. For instance, shared variables in Linda are distributed across the processors using a hashing function, and the user cannot define the distribution of the variables directly. Also, Linda's implementation has a high demand for multicasting on the system, and this may cause substantial communication overhead in many systems where the multicast operation is not efficiently supported.

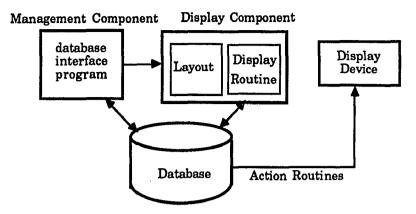

# 2.5 Programming Environments and Program Visualization

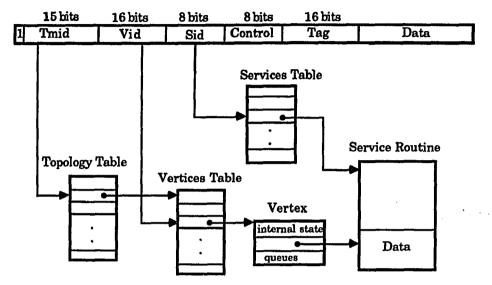

Our programming system for implementing topologies called PRISM consists of a number of tools including a topology compiler, a loader, and a graphical display system integrated through a database. Using a data-manipulation language, topologies can be controlled and manipulated. Some current work related to PRISM concerns systems which provide an integrated environment for display of data structures and/or code of parallel programs. Four examples are discussed here.

Poker. Poker [83] is a parallel programming system in which a parallel program is described as a graph defining the communication structure of the program. The user defines the communication graph by drawing its connections on a two-dimensional stylized lattice using an interactive display system. Graphical symbols depict processes and ports respectively. Ports are linked to sequential program text that is entered textually. Poker does not allow the user to customize displays. Poker's internal database is mainly used to store program segments and other information; it is not intended for tool integration. Hence, user-written mapping schemes are not easily incorporated into a Poker application.

In contrast to Poker, the PRISM system described in Chapter 7 of this thesis is not intended as a graphical programming system. Its displays are not hardwired; they are defined by the user and can be easily changed or manipulated. The database in PRISM stores interesting attributes of a parallel program and is used for manipulating the program. In addition, it provides a basis for uniformly integrating several programming tools.

GARDEN System. The GARDEN system [62] is an experimental system for large-scale graphical programming; it allows pictures to be described and executed using an object-oriented programming environment. A set of types defining the program's objects and their semantics are defined for the visual language. An evaluation function associated with each type defines its semantics. Then for each type, the display prototypes are created and the graphic editor is augmented to support these new types. Thus, in GARDEN, several visual languages can be easily prototyped to describe programs conveniently. The GARDEN system also has a package called GELO, which performs automatic layout of graphical objects.

PRISM differs from GARDEN in several ways. First, it offers no facilities for defining any visual languages, nor does it encourage programming using different visual languages for different applications. Instead it uses the same language to manipulate displays as well as the program structures. Second, PRISM differentiates manipulation of program components from manipulation of their displays while GARDEN considers graphical objects as the same as their corresponding program components. Third, GARDEN is not intended for integration of nongraphical tools whereas PRISM is intended to integrate several tools in addition to the visualization tool, such as program monitoring and resource allocation. Unlike GARDEN, the current implementation of PRISM does not have an automatic layout package similar to GELO. However, it could be implemented as a separate tool and integrated into PRISM. **PV Environment**. Program Visualization environment [40, 26] developed at the

Computer Corporation of America is an interesting environment that provides the user with representations of the program structure and monitoring information, and allows animation of program execution. A program's code and data structure are displayed both graphically and textually, and dynamic changes in data structures or in the control sequence of program execution can be displayed graphically. Users can define their own graphical pictures, which are linked to code and data, permitting the display of different levels of abstraction.

As with the PV environment, PRISM also allows user-defined graphical icons, which may represent different levels of abstractions of the program. However, PRISM is a parallel-programming environment while the PV environment is not, and PRISM does not display code.

Incense. Incense [54], as part of Xerox's MESA environment, provides graphical displays of data structures defined in the strongly typed Mesa language and also depicts the execution sequence graphically. To display a variable, a collection of graphic procedures called the *Artist* is called with parameters that specify the variable's location on the screen. Artist retrieves data from run-time tables or calls other artists associated with each component of the display.

PRISM is similar to Incense in that its display concerns data structures rather than code and in that it is capable of monitoring the execution of the topologies. In both systems, users can define their own displays and can use multiple displays for a single data structure. Incense automatically updates all displays of the same data structure if they are currently displayed, while in PRISM a user-written data-manipulation program must update the displays.

## 2.6 Conclusions

As with distributed objects, topologies address issues of parallel programming However, the concept of topologies focuses on establishing distributed objects' IPC structures. Remote execution on more than one processor has been addressed by Troupes as well as by topologies. Program visualization is also an area addressed by systems such as PV and also by topologies. However, fundamental differences in architecture (i.e., structured multicomputers versus unstructured or simple ethernet-based multicomputers) have implications on the design of topologies that make this work different from others. For instance, it would be inappropriate to have a switchboard (as in Demos or Charlotte) to establish connections on a machine like a hypercube. In the next chapter, the testbed for implementing topologies is described to establish the experimental environment together with the sample applications with which they are evaluated.

# CHAPTER III

# Decomposition Methods: Global Data and Operations

This chapter summarizes several well-known decomposition methods for parallelizing serial programs and indicates the unavoidable global data and operations resulting from such decompositions. It also discusses the importance and the need for a facility for programming global data and operations efficiently in order to obtain good performance.

## 3.1 Domain Decomposition and Global Data

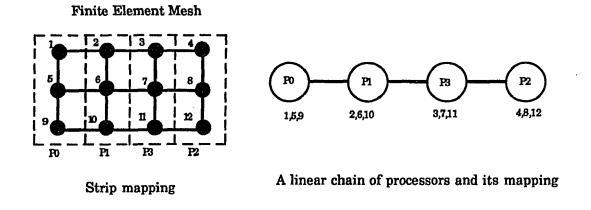

This is one of the most commonly used methods for programming structured multicomputers such as hypercubes. Domains are typically defined as data structures that model physical systems [58, 25, 36, 27], such as a matrix representing a finite element mesh [10], and they are decomposed and mapped onto the parallel machine so that replicated code operates in parallel on different partitions of the structure [34, 35] (also termed SPMD—single program, multiple data). The need for global data arises when a domain's structure is not easily decomposed to match the underlying multicomputer. However, even when the application can be decomposed to match the target hardware perfectly, global data may exist (i) as data shared between processes iterating over adjoining partitions in PDE solution methods [36, 35], (ii) as aggregations of distributed local data and the subsequent broadcast of the aggregates, as in the computation of global objective functions [23, 72] and as in the computation and broadcast of a global error norm from partial local norms when performing convergence testing in the solution part of FEM applications [10], (iii) as global minima or maxima in other *Compute-Aggregate-Broadcast* algorithms [32], or (iv) as cumulative output from partial local outputs, such as alternate scanlines generated by replicated tasks and combined to a complete image in computer graphics applications [24, 60].

# 3.2 Domain Decomposition and Global Operations

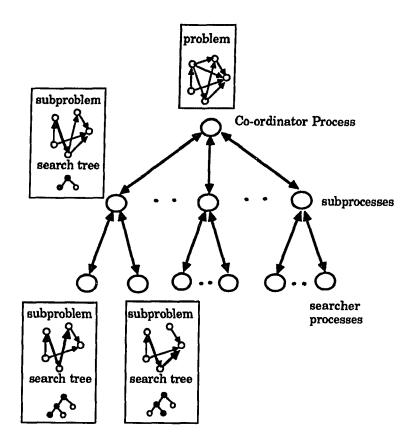

Some domains are constructed during program execution, such as the search tree constructed during the execution of a parallel branch-and-bound algorithm [72] on a hypercube machine. This dynamic tree must be mapped and remapped to the application's processes performing the search, thereby balancing workloads among processes [51, 23]. Remapping involves the dynamic selection of a process able to offload work by a process seeking additional load. This entails the sending of a request seeking work to loaded processes, which may accept or reject it based on local, application-dependent information. Work may be migrated as data describing it [72] or as a process able to perform it [88]. In either case, the selection and migration of work constitute examples of global operations implemented as multiple distributed actions that cooperatively implement such worksharing. Additional global operations in parallel programs generated by domain decomposition concern synchronization between processes that are working independently on data of different *age*. Some parallel algorithms require strict lock-step synchronization of neighboring [6] or all [43, 42] nodes (i.e., all data must be of the same *age*), as with barrier synchronization [32, 84]. Parallel algorithms developed using relaxation techniques can tolerate the existence of distributed values of differing ages [35] but still require occasional synchronization. The distributed actions implementing global synchronization is performed, and for process control, they will interact with the multiple-node operating system kernels.

#### 3.3 Divide and Conquer and the Task/Queue Model

The task/queue model [17] is a generalization of the notion of work sharing. Here each process defines computational tasks dynamically, typically using divide and conquer techniques [35], and offers them for execution to other processes by task insertion into single or multiple, global, or regional [30] queues (this paradigm has also been called *generate and solve* [23, 32]). Sample tasks are subtrees of the search tree in branch and bound algorithms [51], sublists of a list to be sorted [21], futures in Butterfly Scheme, or tasks in the Butterfly's Uniform System [17]. Such global or regional queues constitute abstractions implementing global operations. Their implementations should be distributed ones. (See Section 5.4.2 for a design of a distributed global pool.) Dynamic task generation also occurs with the use of fork and join instructions in automatic methods for program parallelization, such as the DoLoop parallelization methods and constructs used by Kuck [41, 32] and at IBM [84]. Here a single thread of execution spawns (forks) multiple threads, which may later synchronize (or join) at barriers embedded in the code. Spawned threads must be submitted for execution by entry in a global queue, which again (like barriers) constitutes an abstraction used for global operations.

# 3.4 Functional Decomposition and Pipelining

Parallelism generated in this fashion does not pose new problems for the programming of multicomputers. However, the nonhomogeneous parallelism generated in this fashion leads to complications with the previous decomposition methods' uses. Additional instances of global operations may arise in the form of multiple, global task queues [30], and nonuniform communication structures may need to be used, such as multicasting instead of broadcasting [16]. An interesting class of applications typically decomposed functionally are robot control programs [57, 73, 69]. Such applications may require that global deadlines are guaranteed during execution [52]. Global deadline scheduling can be implemented efficiently using distributed objects, which may be explored in future research. In addition, robot control programs may require communication constructs in addition to those provided by the node operating system [69, 73].

## 3.5 Multiple Phases

Most realistic, large parallel applications consist of multiple phases each containing substantial parallelism. For example, the first phase of the FEM application described in Section 4.2 and [4, 10] concerns the parallel generation of distributed data: its second phase concerns the solution of a system of equations based on that data. Global operations are required due to the fact that the second phase cannot start before the first phase has completed. In other applications global data may occur due to data redistribution between phases, which often constitutes a limiting factor in the performance of a parallel program [78].

## **3.6 Global Data and Operations in Operating Systems**

Many global computations in parallel applications on structured multicomputers implement functionalities typically provided by the operating systems of sharedmemory multiprocessors, such as I/O, exception handling, multicast communications, etc. [33, 45]. For example, the output of a multicomputer application may be performed by a distributed object that implements a spanning tree of processes, where each tree node explicitly collects its neighbors' outputs, possibly performing some post-processing, and then forwards the resulting concatenated output data, etc. Other communication structures may be designed to carry certain control messages, such as instructions to processes to resume or terminate execution.

In general, any large parallel program will exhibit many such distributed abstractions among its independently executable processes, where the importance of some of those abstractions is shown by their explicit support in multiprocessor operating systems. For example, an abstraction expressing the *dependencies* [33] between a program's multiple processes in the StarOS operating system for the Cm\* multiprocessor allowed certain processes to terminate or control others, as with parent and child processes in Unix. Similarly, a *bailout* abstraction allowed one process within a parallel application to handle the exceptional conditions of the application's remaining processes (i.e., to *bail out* other processes [33]).

In contrast to the OS support for multiprocessors described in the previous paragraph, the abstractions implementing OS functions in multicomputers must be *programmable* by application programmers to attain suitable performance. For example, a specific parallel application may require partially ordered output data, which may not be provided by the *standard* output utility. Instead the standard utility may be optimized to produce output at the fastest rate possible using a distributed object with nodes that simply concatenate and forward the outputs from neighboring nodes within a spanning tree. Similarly, for specific applications, it may be desirable to associate some output post-processing the output abstraction's concatenation actions, such as filtering, correlation of output data, etc. For example, one implementation of a computer graphics application for the hypercube designed by our research group required pixel data output by one process to be correlated with data on the same pixels known to other processes.

Programmability will also be required for other inherently global operating system facilities, such as program input, program monitoring [55, 82], and debugging, support for process scheduling and/or migration [70, 72], and the implementation of process groups [13, 45]. Monitoring is of particular interest because the obvious approach of sending all monitored data collected at a certain node to a central monitor is infeasible [82]. Monitoring is best performed by distributing both the collection and analysis functions associated with a particular monitoring query across the multicomputer [55, 56]. Thus, a distributed monitoring object consists of cooperating nodes that filter and partially analyze collected data and then forward the reduced amounts of data to other nodes, thereby reducing total communication as well as parallelizing the potentially time-consuming analysis actions. Similarly, the global operations desired for debugging a parallel program may be implemented using a distributed object with nodes that are able to affect their local application processes' execution states.

Higher-level operating system facilities currently being developed for multicomputers also exhibit global data or operations. For example, the names of objects or procedures being invoked are global in RPC and in distributed object implementations [8, 2, 19, 77]. Similarly, tuple space is global in Linda [11], which causes substantial overheads for Linda's hypercube implementation [78].

# 3.7 Conclusions

Several commonly used decomposition methods for parallelizing serial programs exhibit global data and operations. The most significant point of this chapter is that regardless of the decomposition method used, global data and operations will arise, either between different computation phases or as a part of the parallel computation, and that without having a facility to program them efficiently, performance may be drastically affected.

# **CHAPTER IV**

# Experimental Testbed and Sample Parallel Applications

This chapter describes the testbed for implementing topologies and the sample parallel applications used to evaluate topologies and identifies the global data and operations in these applications.

#### 4.1 Testbed Environment

#### 4.1.1 Hardware

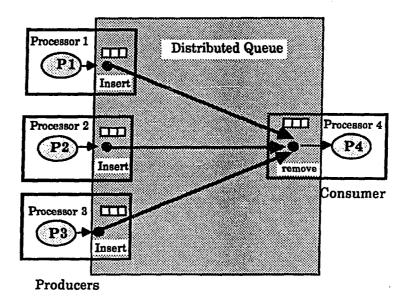

The underlying nonshared-memory machine which serves as a testbed for implementing topologies and sample applications is a 32 node Intel iPSC/1 hypercube. The node processors are connected as a hypercube interconnection, as shown in Figure 4.1. In a hypercube interconnection an n dimensional cube has  $2^n$  total of processors, with each processor having n directly connected neighboring processors. The average distance between two arbitrary node processors is n/2 and the maximum distance is n. A hypercube is a versatile structure onto which trees, rings, meshes, or other regular structures can be mapped easily [64, 25].

Figure 4.1: The Hypercube Interconnection

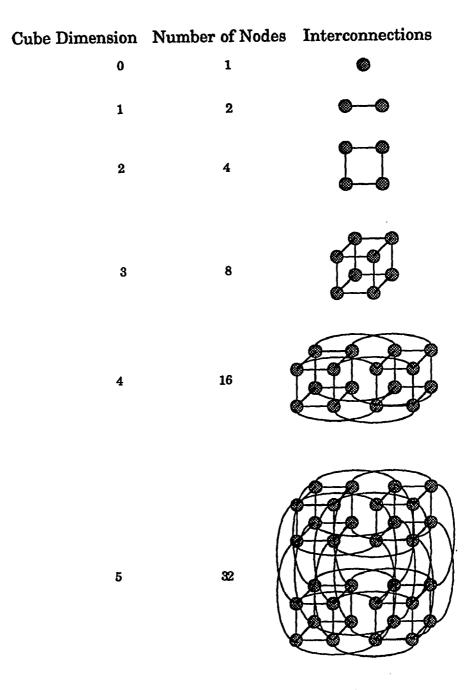

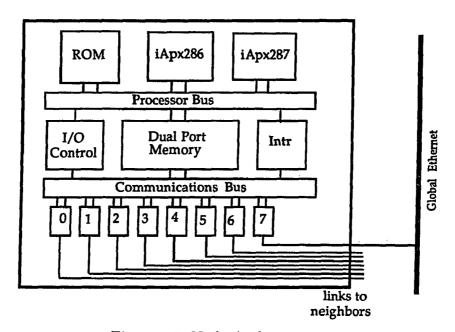

Each node consists of a 12 MHz Intel iAPX 286 processor, 512 kilobytes of memory, an iAPX 287 floating point co-processor, and 8 ethernet communications channels built from local area network (LAN) controllers (each controller is the iAPX 82586 chip), of which 6 channels are in use. Five channels are connected to the neighboring processors to form a hypercube, and the last channel is a global channel which links all the processors to the host, also called the *cube manager*. The cube manager is an Intel System 310/AP running the Xenix 3.4 operating system on an iAPX 286/10 processor. A framebuffer attached to the cube manager provides 640 by 480 pixels display and a total of 1024 colors with 256 colors displayable at a time. Figure 4.2 shows the hardware testbed. Note that a global ethernet connects all the node processors and the cube manager. The cube manager is also connected through the departmental ethernet to a number of Sun workstations. A Sun 3/50 is used as a remote host to the hypercube in place of the Intel System 310/AP for the PRISM environment for programming topologies.

The internal architecture of a node processor is shown in Figure 4.3. The memory is organized as a dual-port memory with two independent buses—one connected to the processor and the other to the communication controllers. Communication between each controller and the processor is provided by data structures called system control blocks in the memory. The hardware controllers understand the system control blocks and are capable of retrieving the list of messages and buffers linked to each of the system control blocks. A message to be sent is linked

Figure 4.2: Testbed-Cube Manager and the Hypercube

to the system control block through a command block and a buffer header. A set of buffers for loading incoming messages is linked through buffer headers [31].

# 4.1.2 Software

Software provided by Intel for the iPSC/1 testbed consists of a node operating system called *nex*, which supports multi-tasking; a dynamic loader for loading processes; and a logger for debugging user applications. The interprocess communication primitives provided by nex can send or receive messages of sizes up to 16 Kbytes using send, recv, sendw or recvw calls. A *send* call initiates the sending of a message, and a *sendw* call causes the calling process to be blocked until the message transmission is done. A *recv* call initiates the receipt of a message but does not block the calling process, whereas a *recvw* call does. Each process on the

Figure 4.3: Node Architecture

hypercube is uniquely addressed by the node processor number on which it resides and by the process identifier, which is unique on each node.

# 4.2 A Finite Element Modeling Program