## Toward a Hardware Accelerated Future

#### Citation

Lyons, Michael John. 2013. Toward a Hardware Accelerated Future. Doctoral dissertation, Harvard University.

#### Permanent link

http://nrs.harvard.edu/urn-3:HUL.InstRepos:11182688

### Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Other Posted Material, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#LAA

## **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

**Accessibility**

# Toward a Hardware Accelerated Future

A dissertation presented

by

MICHAEL JOHN LYONS

to

THE SCHOOL OF ENGINEERING AND APPLIED SCIENCES

in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the subject of

COMPUTER SCIENCE

Harvard University

Cambridge, Massachusetts

June, 2013

## Toward a Hardware Accelerated Future

#### Abstract

Hardware accelerators provide a rare opportunity to achieve orders-of-magnitude performance and power improvements with customized circuit designs.

Many forms of hardware acceleration exist—attributes and trade-offs of each approach is discussed. Single-algorithm accelerators, which maximize efficiency gains through maximum specialization, are one such approach. By combining many of these into a many-accelerator system, high specialization is possible with fewer specialization limits.

The development of one such single-algorithm hardware accelerator for managing compressed Bloom filters in wireless sensor networks is presented. Results from the development of the accelerator highlight scalability deficiencies in the way accelerators are currently integrated into processors, and that the majority of accelerator area is consumed by generic SRAM memory rather than algorithm-specific logic.

These results motivate development of the accelerator store, a system architecture designed for the needs of many-accelerator systems. In particular, the accelerator store improves interaccelerator communication and includes support for sharing accelerator SRAM memories. Using a security application as an example, the accelerator store architecture is able to reduce total processor area by 30% with less than 1% performance overhead.

Using the accelerator store as a base, the ShrinkFit framework allows accelerators to grow and shrink, to achieve accelerated performance within small FPGA budgets and efficiently expand for more performance when larger FPGA budgets are available. The ability to resize accelerators is particularly useful for hybrid systems combining GP-CPUs and FPGA resources, in which applications may deploy accelerators to a shared FPGA fabric. ShrinkFit performance overheads for small and large FPGA resources are found to be low using a robotic bee brain workload and FPGA prototype.

Finally, future directions are briefly discussed along with details about the production of the robotic bee helicopter brain prototype.

# Contents

| Ti | tle              |                |                                         | i    |

|----|------------------|----------------|-----------------------------------------|------|

| Co | opyri            | $\mathbf{ght}$ |                                         | ii   |

| Al | bstra            | ıct            |                                         | iii  |

| Ta | able o           | of cont        | ents                                    | iv   |

| Li | $\mathbf{st}$ of | figure         | s                                       | ix   |

| Li | $\mathbf{st}$ of | tables         |                                         | xii  |

| Pr | evio             | us wor         | ·k                                      | xiii |

| A  | cknov            | wledgn         | nents                                   | xiv  |

| 1  | The              | poter          | ntial for accelerated computing         | 1    |

|    | 1.1              | Trend          | s in computing                          | . 2  |

|    |                  | 1.1.1          | The end of clock scaling                | . 2  |

|    |                  | 1.1.2          | The limits of multicore                 | . 3  |

|    |                  | 1.1.3          | Hardware acceleration                   | . 4  |

|    | 1.2              | Accele         | erated architecture taxonomy            | . 5  |

|    |                  | 1.2.1          | DSP                                     | . 6  |

|    |                  | 1.2.2          | Graphics Processing Unit (GPU)          | . 8  |

|    |                  | 1.2.3          | Specialized homogeneous multicore (SHM) | . 10 |

|    |                  | 1.2.4          | Customized ISA (CISA)                   | . 12 |

|          |     | 1.2.5   | Single-ISA heterogeneous multicore (SIHM) | 14 |

|----------|-----|---------|-------------------------------------------|----|

|          |     | 1.2.6   | Mobile SoC                                | 16 |

|          |     | 1.2.7   | Reconfigurable computing                  | 19 |

|          | 1.3 | Challe  | enges                                     | 21 |

|          |     | 1.3.1   | Rapid accelerator development             | 22 |

|          |     | 1.3.2   | Identifying algorithms to accelerate      | 23 |

|          |     | 1.3.3   | Minimizing accelerator area overheads     | 23 |

|          |     | 1.3.4   | Scaling accelerator systems               | 24 |

| <b>2</b> | Acc | elerato | or composition                            | 26 |

|          | 2.1 | Accele  | erator design requirements                | 26 |

|          | 2.2 | Power   | and performance optimization strategies   | 28 |

|          | 2.3 | Bloom   | n Filter Algorithms                       | 29 |

|          |     | 2.3.1   | Bloom filters                             | 29 |

|          |     | 2.3.2   | Multiply and Shift Hashing                | 31 |

|          |     | 2.3.3   | Golomb-Rice Coding                        | 31 |

|          | 2.4 | Accele  | erator Architecture                       | 32 |

|          |     | 2.4.1   | Bloom Filter Memory                       | 33 |

|          |     | 2.4.2   | Memory Data Controller                    | 33 |

|          |     | 2.4.3   | Memory Address Controller                 | 34 |

|          |     | 2.4.4   | Decompressor                              | 34 |

|          |     | 2.4.5   | Compressor                                | 35 |

|          | 2.5 | Accele  | erator Evaluation                         | 35 |

|          |     | 2.5.1   | Item Insertion and Querying               | 37 |

|          |     | 2.5.2   | Compressing Bloom Filters                 | 39 |

|          |     | 2.5.3   | Merging Compressed Bloom Filters          | 40 |

|          | 2.6 | Applio  | cation Evaluations                        | 41 |

|          |     | 2.6.1   | Mote Status                               | 42 |

|          |     | 2.6.2   | Object Tracking                           | 44 |

|          |     | 263     | Duplicata Packet Removal                  | 45 |

|   | 2.7 | Takear   | ways                                       | 45    |

|---|-----|----------|--------------------------------------------|-------|

| 3 | Acc | or store | 46                                         |       |

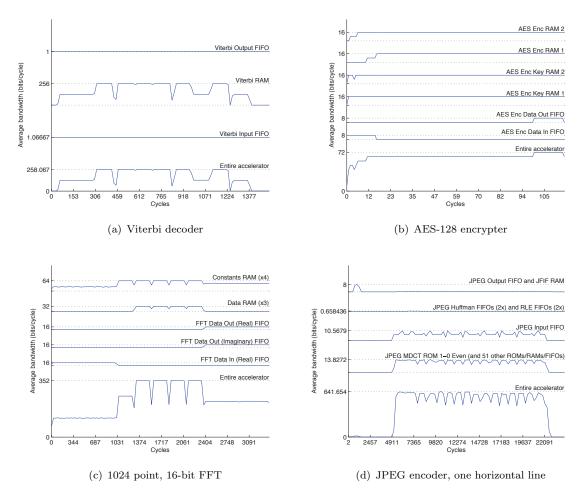

|   | 3.1 | Accele   | erator Characterization                    | 48    |

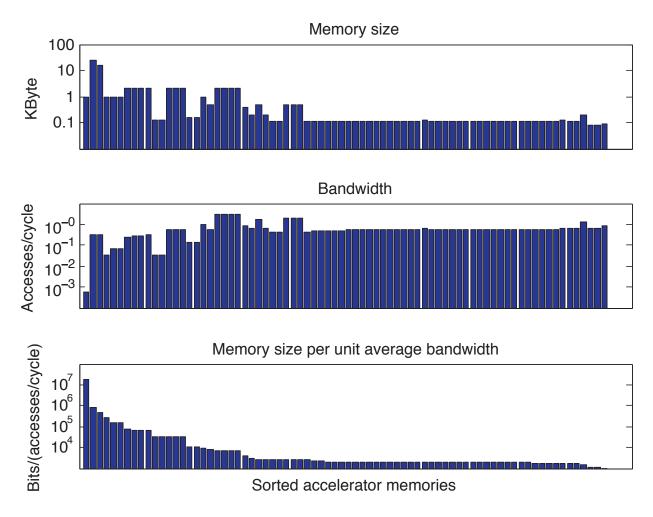

|   |     | 3.1.1    | Accelerator composition characterization   | 49    |

|   |     | 3.1.2    | Memory access pattern characterization     | 50    |

|   |     | 3.1.3    | Shared memory selection methodology        | 53    |

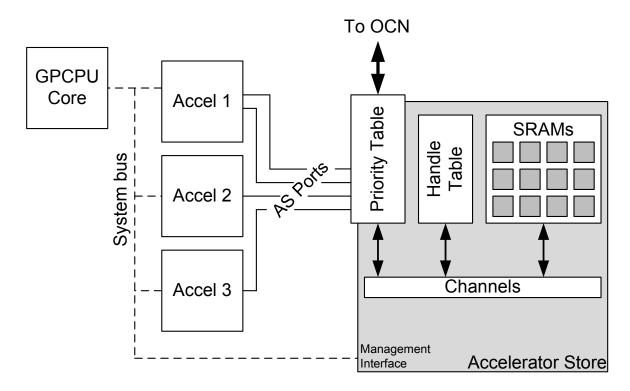

|   | 3.2 | Accele   | erator store design                        | 55    |

|   |     | 3.2.1    | Accelerator store features                 | 56    |

|   |     | 3.2.2    | Architecture of the accelerator store      | 58    |

|   |     | 3.2.3    | Distributed accelerator store architecture | 60    |

|   |     | 3.2.4    | Accelerator/accelerator store interface    | 61    |

|   |     | 3.2.5    | Accelerator store software interface       | 62    |

|   | 3.3 | Accele   | erator Store Evaluation                    | 64    |

|   |     | 3.3.1    | Accelerator-based system model             | 64    |

|   |     | 3.3.2    | Embedded application                       | 65    |

|   |     | 3.3.3    | Server application                         | 74    |

|   | 3.4 | Relate   | ed work                                    | 78    |

| 4 | Shr | inkFit   |                                            | 80    |

| _ | 4.1 |          | $\operatorname{ation}$                     |       |

|   | 4.2 |          | ptual approach                             |       |

|   | 1.2 | 4.2.1    | Decomposition                              |       |

|   |     | 4.2.2    | Building ShrinkFit accelerators with VMs   | 85    |

|   |     | 4.2.3    | Module contexts                            | 86    |

|   |     | 4.2.4    | Accelerator resource sharing               | 86    |

|   |     | 4.2.5    | Dynamic accelerator resizing               | 87    |

|   | 4.3 |          | ework implementation                       | 87    |

|   | 4.0 | 4.3.1    | Accelerator store                          | 88    |

|   |     |          |                                            |       |

|   |     | 4.3.2    | ShrinkFit wrapper                          | 89    |

|   |     | /1 3 3   | SHEHR BU WENDOE                            | - U I |

|   |                                                              | 4.3.4                                                                      | ShrinkFit framework area costs        | 93                         |

|---|--------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------|----------------------------|

|   | 4.4                                                          | Softwa                                                                     | are Development                       | 94                         |

|   |                                                              | 4.4.1                                                                      | Decomposing accelerators              | 95                         |

|   |                                                              | 4.4.2                                                                      | Configure ShrinkFit hard logic blocks | 95                         |

|   |                                                              | 4.4.3                                                                      | Shrinklib SDK                         | 95                         |

|   | 4.5                                                          | Shrink                                                                     | Fit module evaluation                 | 96                         |

|   |                                                              | 4.5.1                                                                      | ShrinkFit PM implementations          | 97                         |

|   |                                                              | 4.5.2                                                                      | Evaluation methodology                | 99                         |

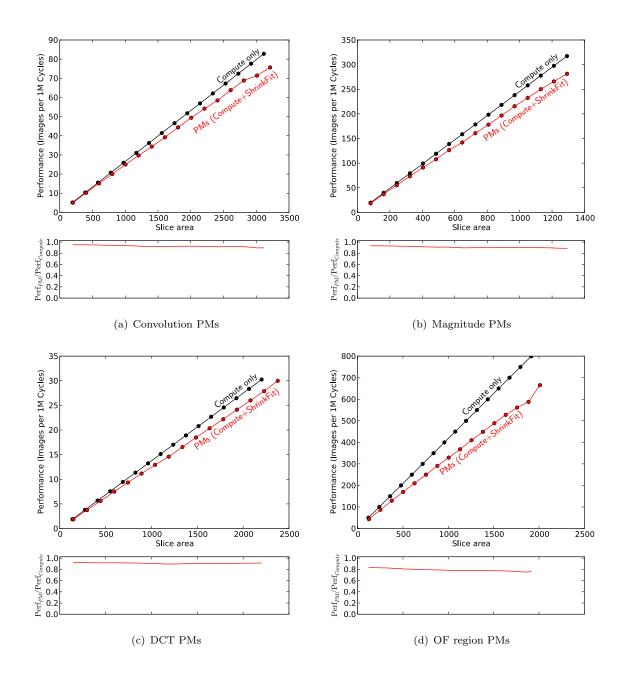

|   |                                                              | 4.5.3                                                                      | PM performance scalability            | 01                         |

|   | 4.6                                                          | RoboE                                                                      | Bee application evaluation            | 02                         |

|   |                                                              | 4.6.1                                                                      | Application evaluation overview       | 02                         |

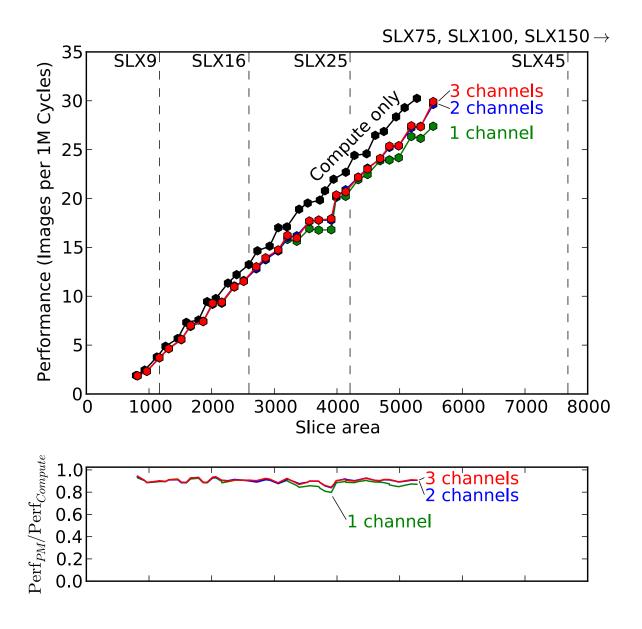

|   |                                                              | 4.6.2                                                                      | Bandwidth impact                      | 04                         |

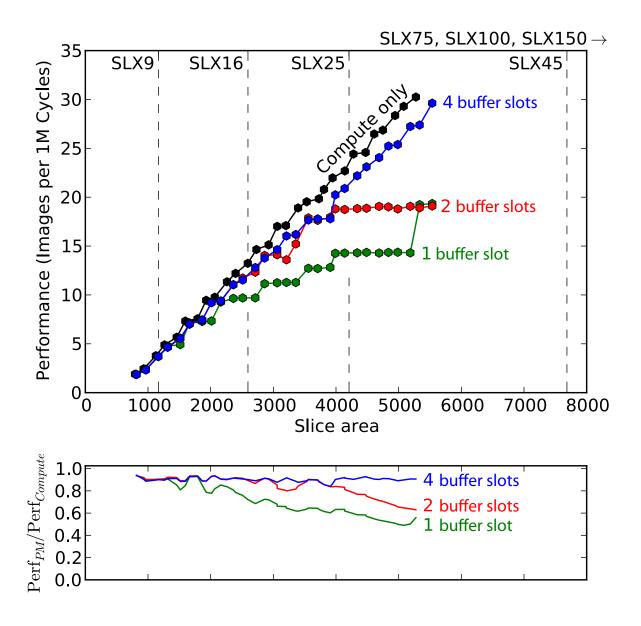

|   |                                                              | 4.6.3                                                                      | Buffering impact                      | 05                         |

|   |                                                              | 4.6.4                                                                      | Hard logic block area overheads       | 07                         |

|   | 4.7                                                          | Relate                                                                     | d work                                | 08                         |

|   |                                                              |                                                                            |                                       |                            |

| 5 | Fut                                                          |                                                                            | rections 1                            | )9                         |

| 5 | <b>Fut</b> : 5.1                                             | ure dir                                                                    |                                       | 0 <b>9</b><br>09           |

| 5 |                                                              | ure dir                                                                    | rator store scalability               | 09                         |

| 5 |                                                              | ure dir<br>Accele                                                          | rator store scalability               | 09<br>10                   |

| 5 |                                                              | ure dir<br>Accele<br>5.1.1<br>5.1.2                                        | rator store scalability               | 09<br>10<br>10             |

| 5 | 5.1                                                          | ure dir<br>Accele<br>5.1.1<br>5.1.2<br>Unifie                              | rator store scalability               | 09<br>10<br>10<br>11       |

| 5 | <ul><li>5.1</li><li>5.2</li></ul>                            | ure dir<br>Accele<br>5.1.1<br>5.1.2<br>Unified<br>Dynan                    | rator store scalability               | 09<br>10<br>10<br>11       |

|   | 5.1<br>5.2<br>5.3<br>5.4                                     | Accele 5.1.1 5.1.2 Unified Dynar Shrink                                    | rator store scalability               | 09<br>10<br>10<br>11       |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>Heli                             | Accele 5.1.1 5.1.2 Unified Dynar Shrink icopter                            | rator store scalability               | 09 10 10 11 11 12          |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>Heli                             | Accele 5.1.1 5.1.2 Unified Dynam Shrink icopten Brain                      | rator store scalability               | 09 10 11 11 12 13          |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>Heli                             | Accele 5.1.1 5.1.2 Unified Dynar Shrink icopter Brain Helico               | rator store scalability               | 09 10 10 11 11 12 13       |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>Heli                             | Accele 5.1.1 5.1.2 Unified Dynar Shrink icopter Brain Helico               | rator store scalability               | 09 10 10 11 11 12 13       |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>Heli<br>A.1<br>A.2<br>A.3        | Acceler 5.1.1 5.1.2 Unified Dynam Shrink icopter Brain Helico Object       | rator store scalability               | 09 10 11 11 12 13 15 16    |

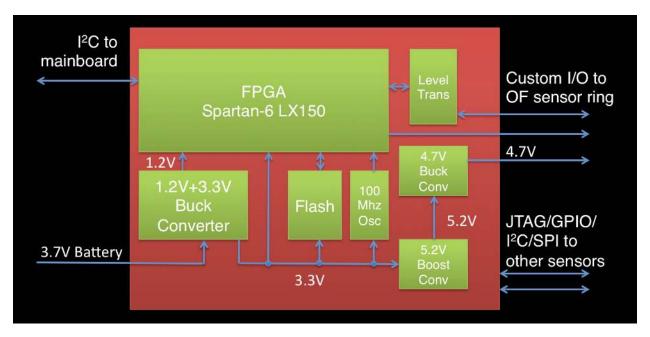

|   | 5.1<br>5.2<br>5.3<br>5.4<br>Heli<br>A.1<br>A.2<br>A.3<br>A.4 | Accele 5.1.1 5.1.2 Unified Dynam Shrink icopten Brain Helico Object System | rator store scalability               | 09 10 11 11 12 13 15 16 17 |

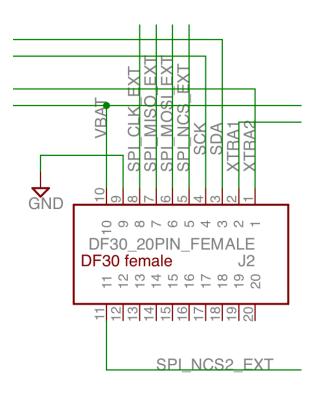

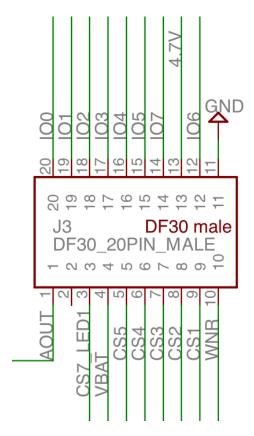

|         | A.5.2            | Connection to optical flow sensor ring | 120 |  |  |  |

|---------|------------------|----------------------------------------|-----|--|--|--|

|         | A.5.3            | JTAG                                   | 122 |  |  |  |

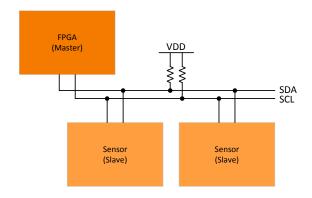

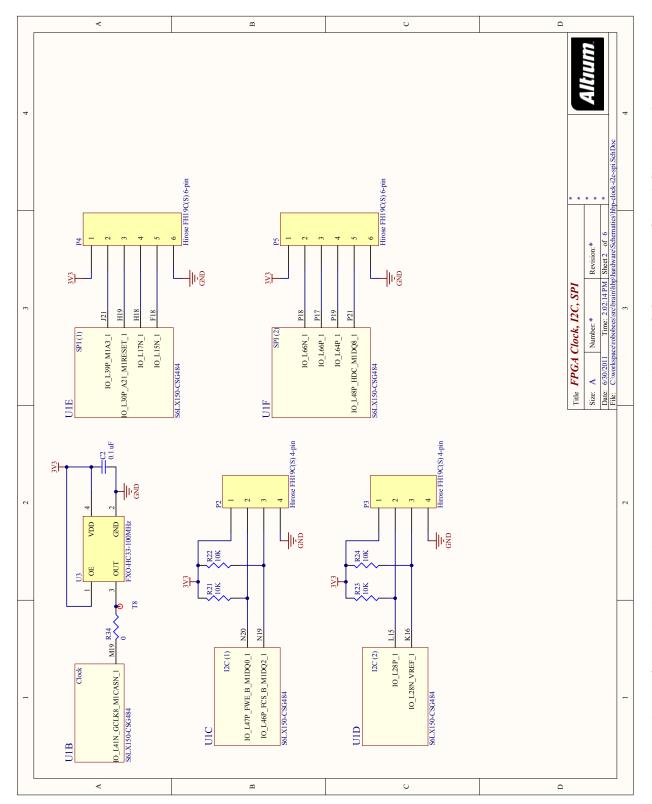

|         | A.5.4            | I2C                                    | 122 |  |  |  |

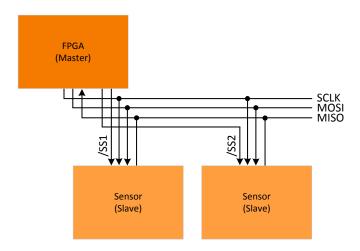

|         | A.5.5            | SPI                                    | 122 |  |  |  |

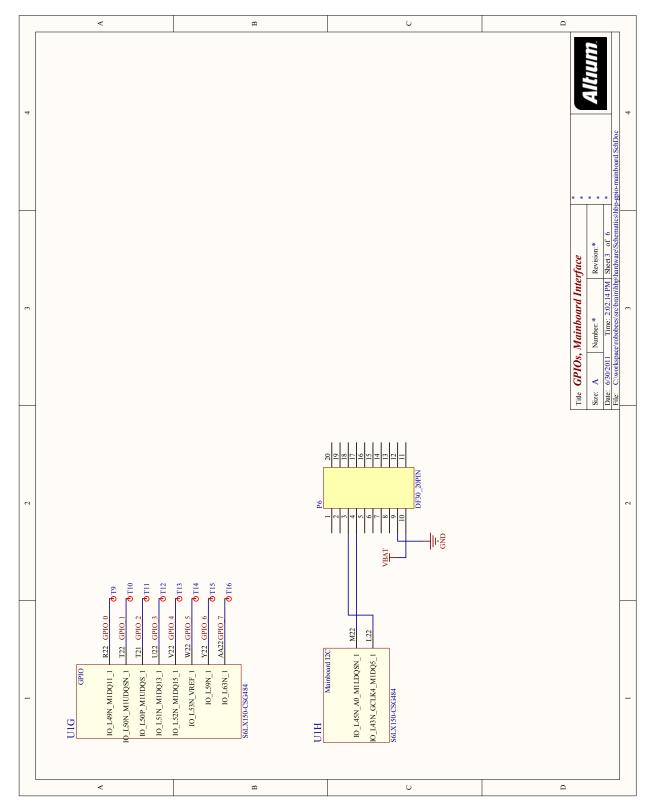

|         | A.5.6            | GPIO                                   | 123 |  |  |  |

| A.6     | Comp             | onents                                 | 123 |  |  |  |

|         | A.6.1            | FPGA                                   | 124 |  |  |  |

|         | A.6.2            | Flash memory                           | 125 |  |  |  |

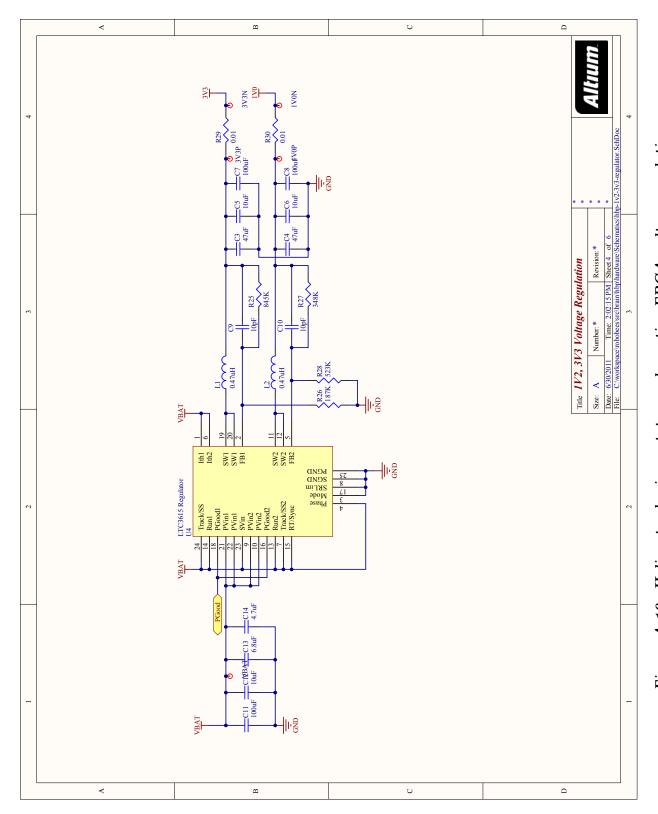

|         | A.6.3            | 1.0V+3.3V Buck Converter               | 126 |  |  |  |

|         | A.6.4            | 4.7V Boost+Buck Converter              | 127 |  |  |  |

|         | A.6.5            | ADC                                    | 127 |  |  |  |

|         | A.6.6            | 100 MHz Oscillator                     | 127 |  |  |  |

|         | A.6.7            | External IO pins                       | 127 |  |  |  |

|         | A.6.8            | PCB                                    | 128 |  |  |  |

| A.7     | Helico           | pter brain prototype implementation    | 129 |  |  |  |

| Bibliog | Bibliography 141 |                                        |     |  |  |  |

# List of Figures

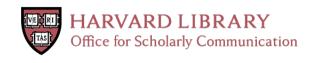

| 2.1  | Bloom filter hardware accelerator hardware flow                                        | 32 |

|------|----------------------------------------------------------------------------------------|----|

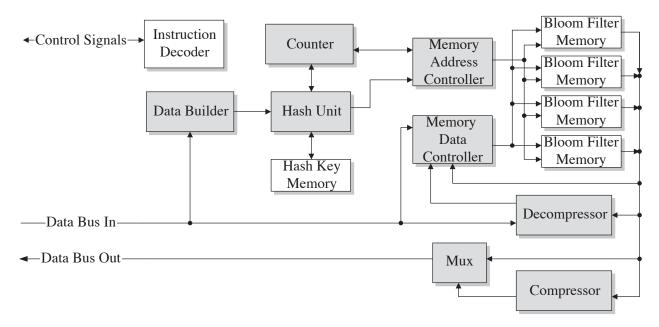

| 2.2  | Decompressor information flow                                                          | 34 |

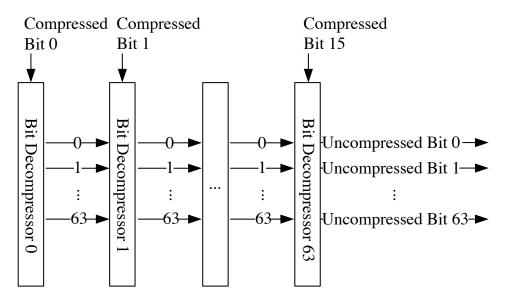

| 2.3  | Placed-and-routed Bloom filter accelerator design                                      | 36 |

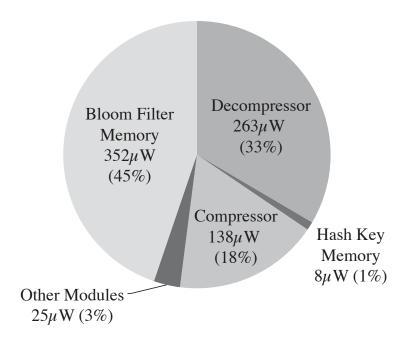

| 2.4  | Average power usage of Bloom filter hardware accelerator modules                       | 37 |

| 2.5  | Item insertion times of application-specific hardware design logic and general purpose |    |

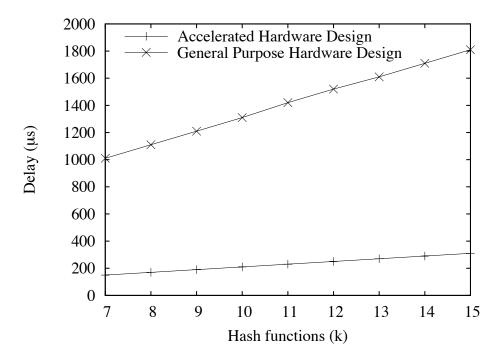

|      | design logic                                                                           | 38 |

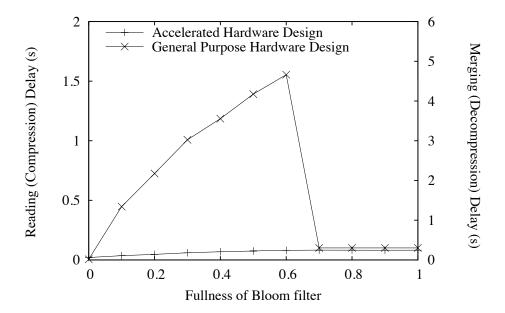

| 2.6  | Bloom filter reading and merging delay at a 1% false positive rate                     | 40 |

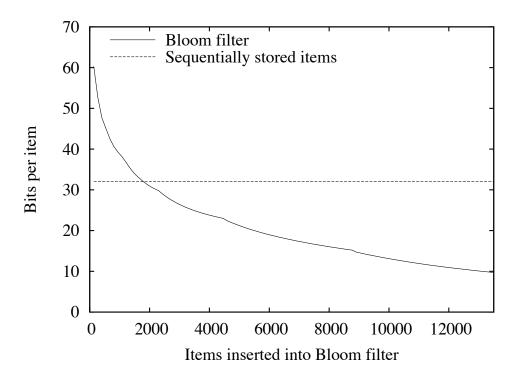

| 2.7  | Storage cost per item for a 16KB Bloom filter and 1% false positive rate               | 43 |

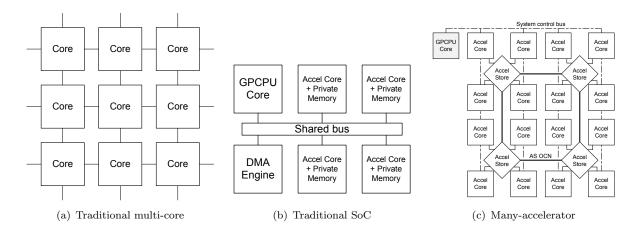

| 3.1  | Comparison of architecture styles                                                      | 47 |

| 3.2  | Total memory bandwidth utilization of several accelerators                             |    |

| 3.3  | Accelerator SRAM memories sorted by memory size per bandwidth                          |    |

| 3.4  | Accelerator store system architecture                                                  | 56 |

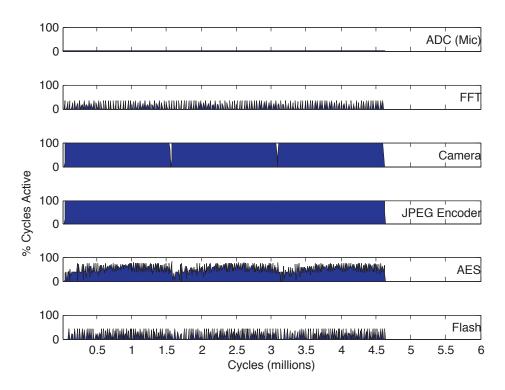

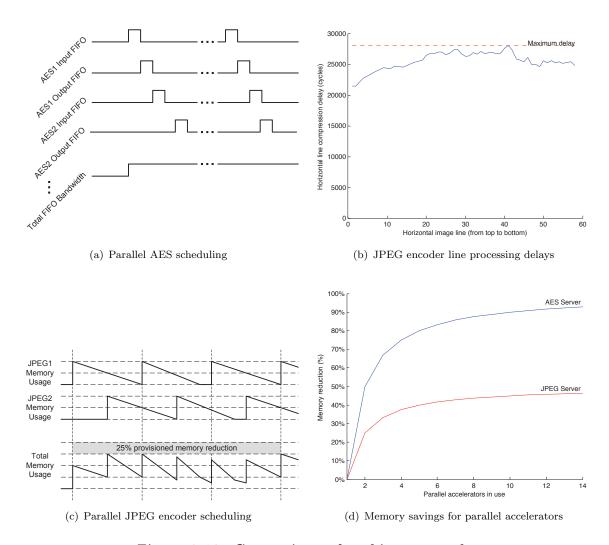

| 3.5  | Embedded application accelerator activity                                              | 66 |

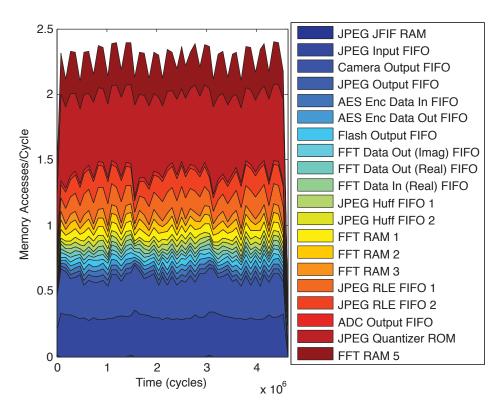

| 3.6  | Embedded application "top 20 to share" memory bandwidth                                | 67 |

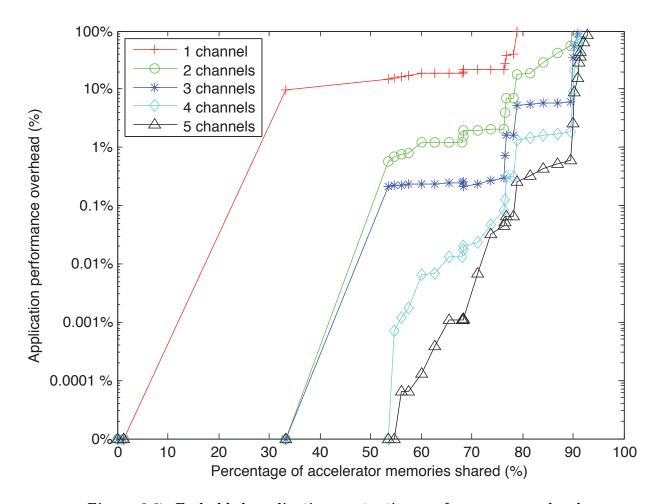

| 3.7  | Embedded application contention performance overhead                                   | 68 |

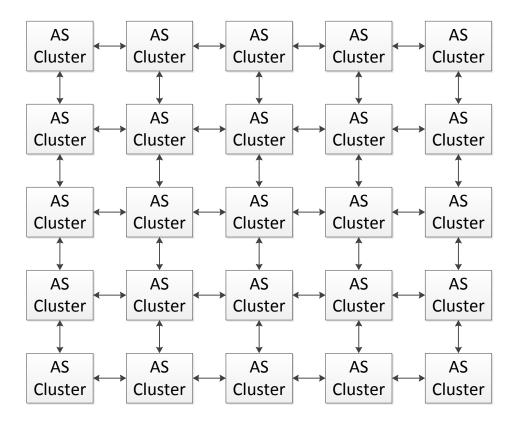

| 3.8  | Distributed AS architecture                                                            | 69 |

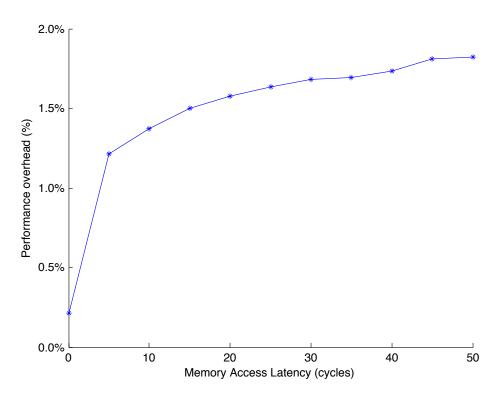

| 3.9  | Embedded application access latency and contention performance overhead                | 70 |

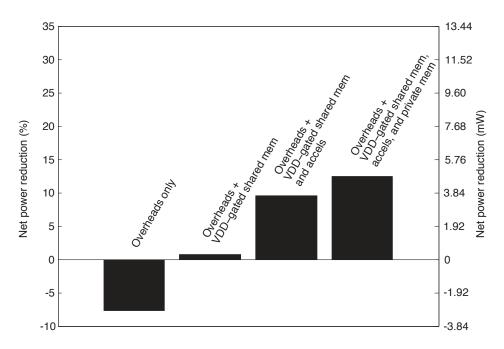

| 3.10 | Embedded app power breakdown                                                           | 72 |

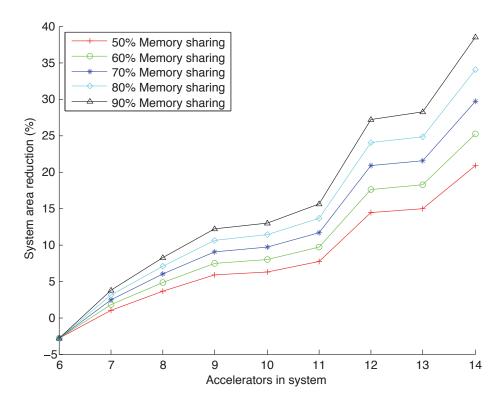

| 3.11 | Embedded app area reduction                                                            | 73 |

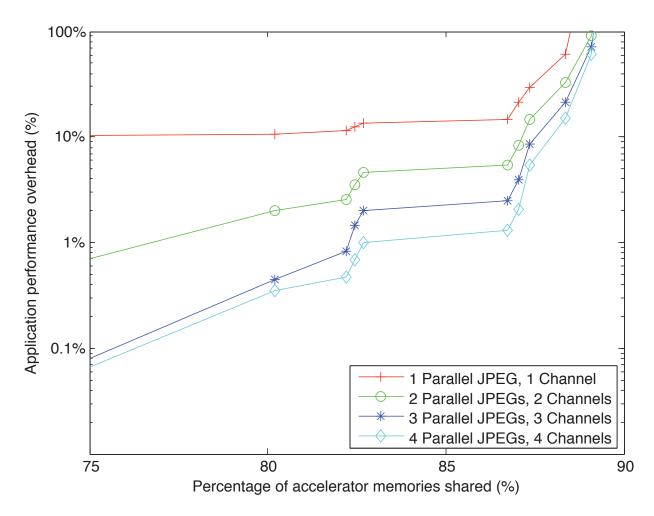

| 3.12 | JPEG server application performance overhead                                           | 75 |

| 3.13 | Comparison of architecture styles                                                      | 76 |

| 4.1  | RoboBee Brain FPGA prototype                                                             |

|------|------------------------------------------------------------------------------------------|

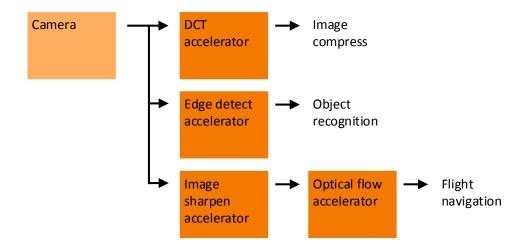

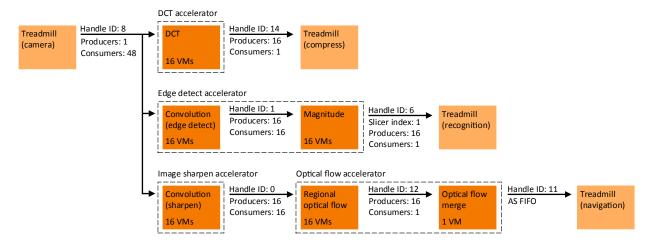

| 4.2  | RoboBee application accelerators                                                         |

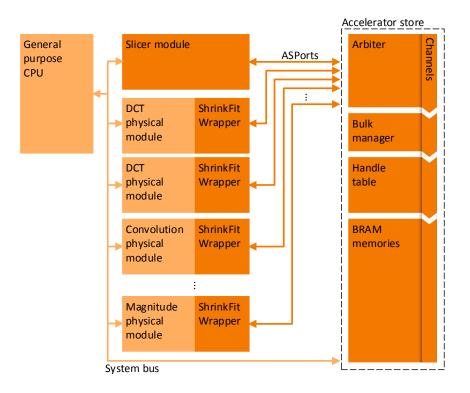

| 4.3  | ShrinkFit framework architecture                                                         |

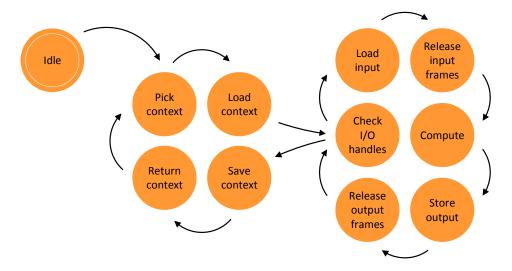

| 4.4  | ShrinkFit wrapper state machine                                                          |

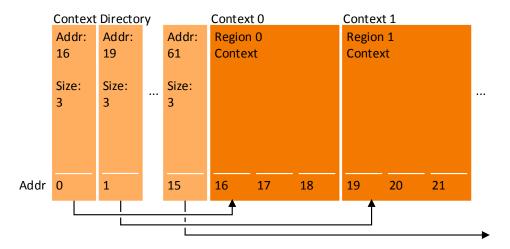

| 4.5  | ShrinkFit wrapper context handle structure                                               |

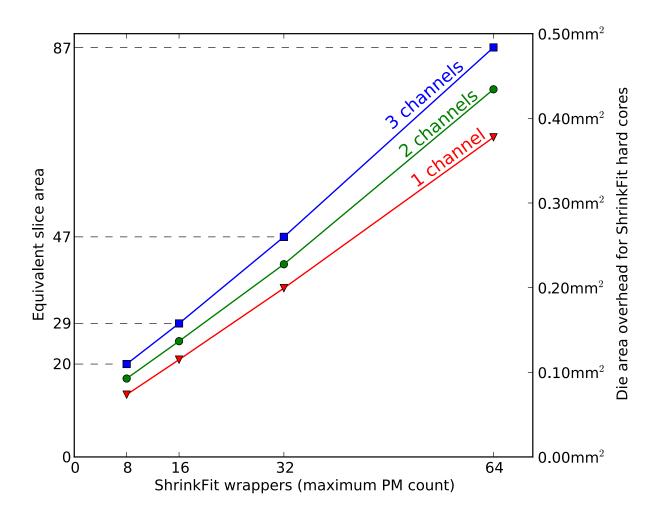

| 4.6  | ShrinkFit hard logic block die area overheads                                            |

| 4.7  | RoboBee application decomposed into VMs                                                  |

| 4.8  | Single PM design resource-to-performance trade-off                                       |

| 4.9  | RoboBee application resource-to-performance trade-off bandwidth impact 103               |

| 4.10 | RoboBee application resource-to-performance trade-off buffering impact 106               |

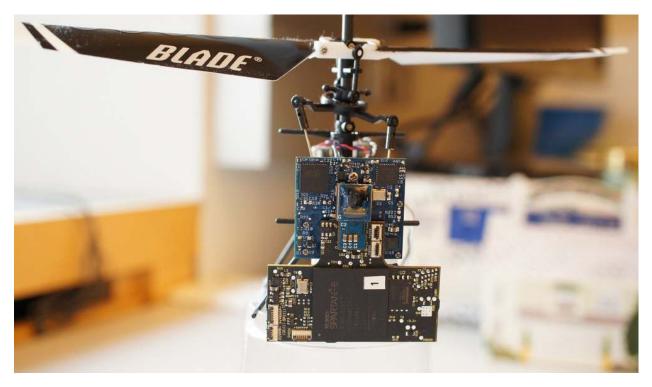

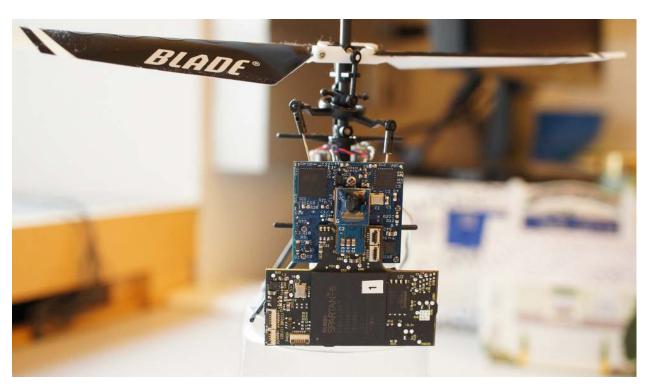

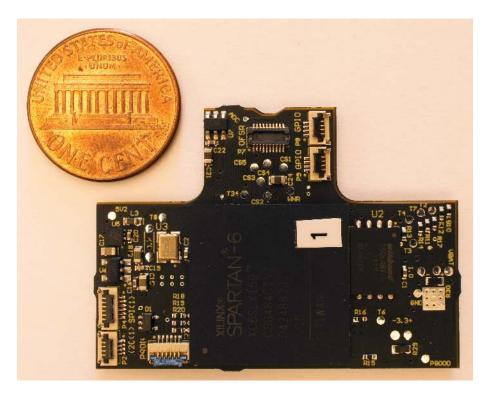

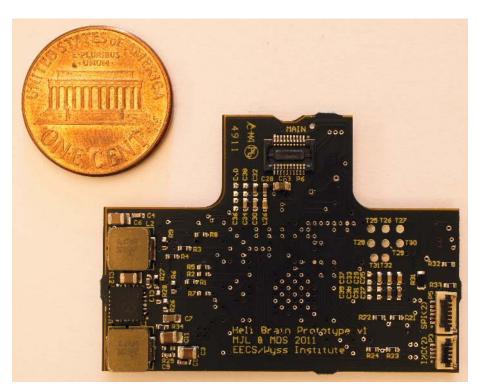

| A.1  | Helicopter brain prototype attached to helicopter and optical flow camera 113            |

| A.2  | Helicopter brain prototype front                                                         |

| A.3  | Helicopter brain prototype back                                                          |

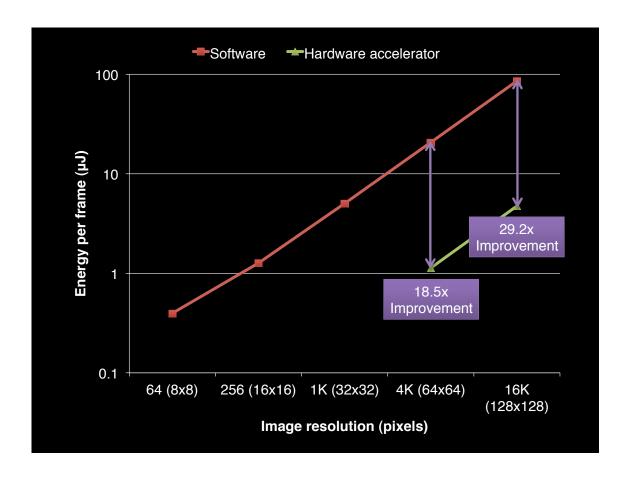

| A.4  | Optical flow software and hardware accelerator energy consumption                        |

| A.5  | MCX2 Toy Helicopter                                                                      |

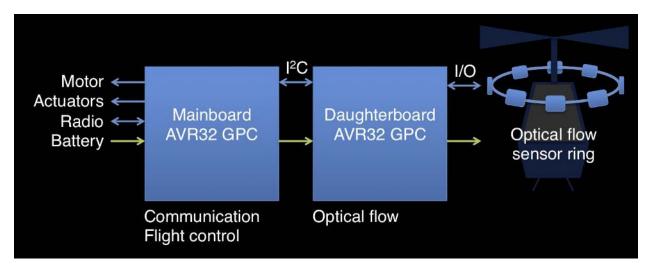

| A.6  | Original CentEye system architecture                                                     |

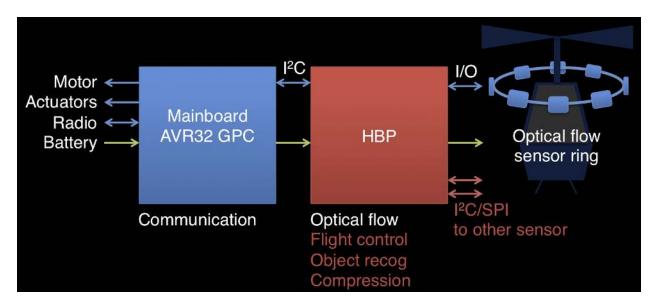

| A.7  | HBP system architecture                                                                  |

| A.8  | Interface to mainboard                                                                   |

| A.9  | Interface to optical flow sensor ring                                                    |

| A.10 | I2C Interface                                                                            |

| A.11 | SPI Interface                                                                            |

| A.12 | HBP Architecture                                                                         |

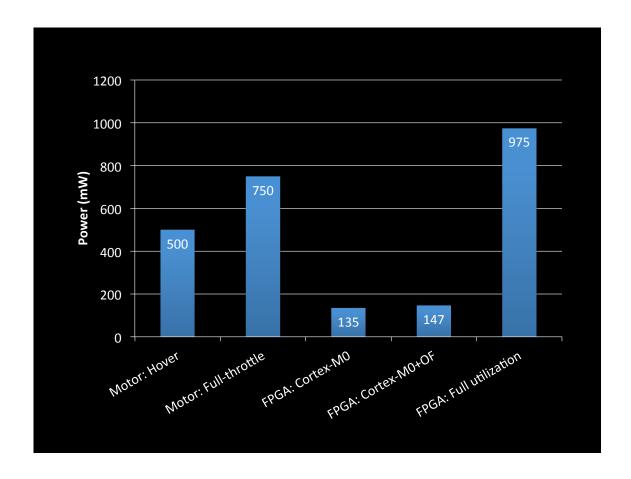

| A.13 | XC6-SLX150 FPGA power consumption                                                        |

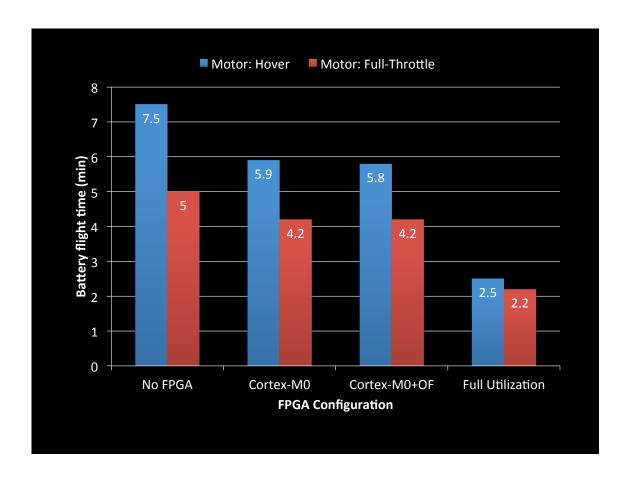

| A.14 | Helicopter battery life with XC6-SLX150                                                  |

| A.15 | Helicopter brain prototype bill of materials (BOM)                                       |

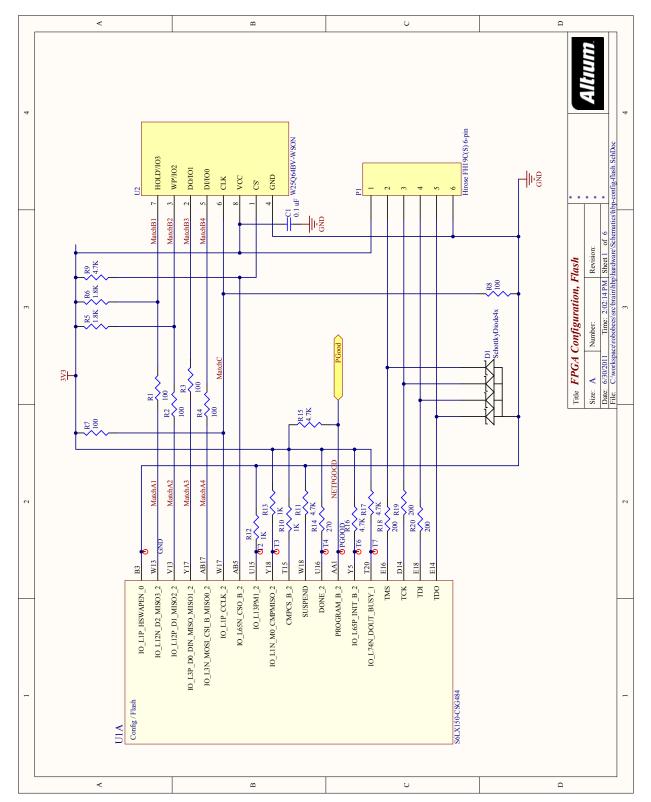

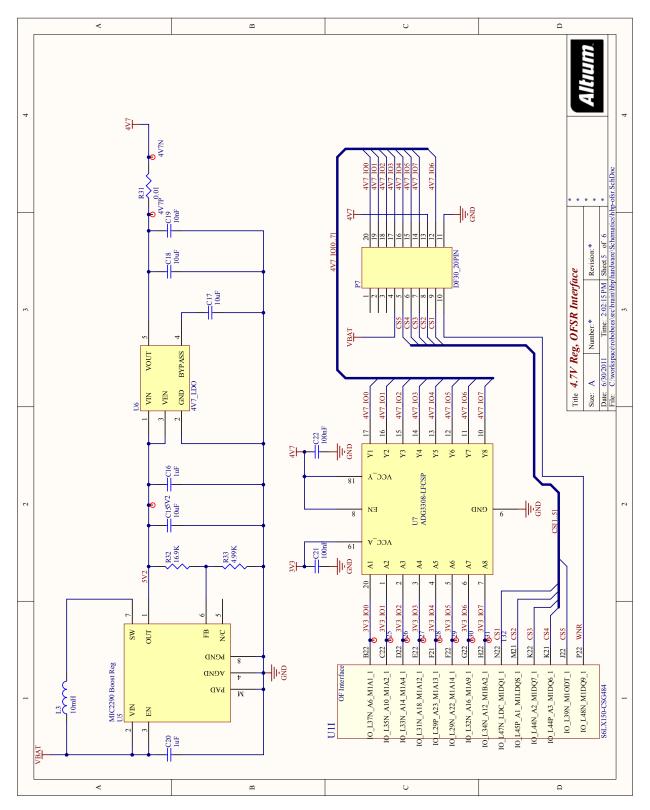

| A.16 | Helicopter brain prototype schematic: FPGA configuration and flash $130$                 |

| A.17 | Helicopter brain prototype schematic: FPGA clock, I2C and SPI interfaces $\dots 131$     |

| A.18 | Helicopter brain prototype schematic: GPIOs and helicopter main<br>board interface $132$ |

| A.19 | Helicopter brain prototype schematic: FPGA voltage regulation                            |

| A.20 Helicopter brain prototype schematic: optical flow camera interface |

|--------------------------------------------------------------------------|

| A.21 Helicopter brain prototype schematic: FPGA power connections        |

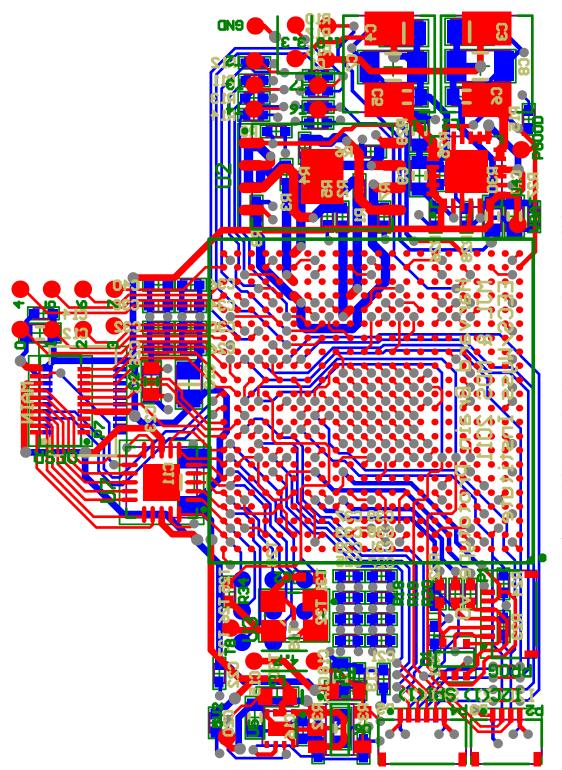

| A.22 Helicopter brain prototype layout: all layers                       |

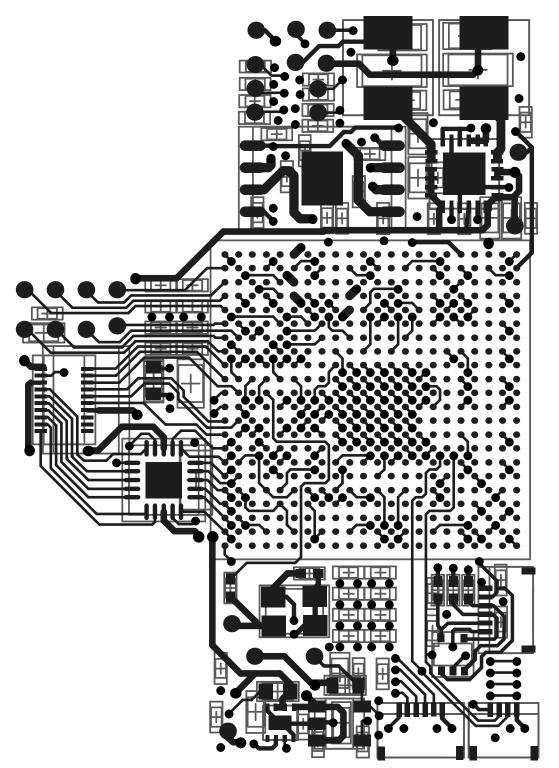

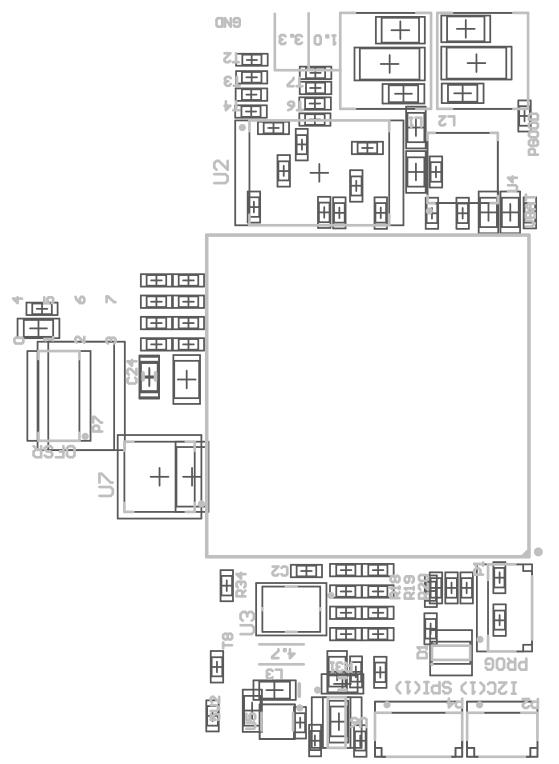

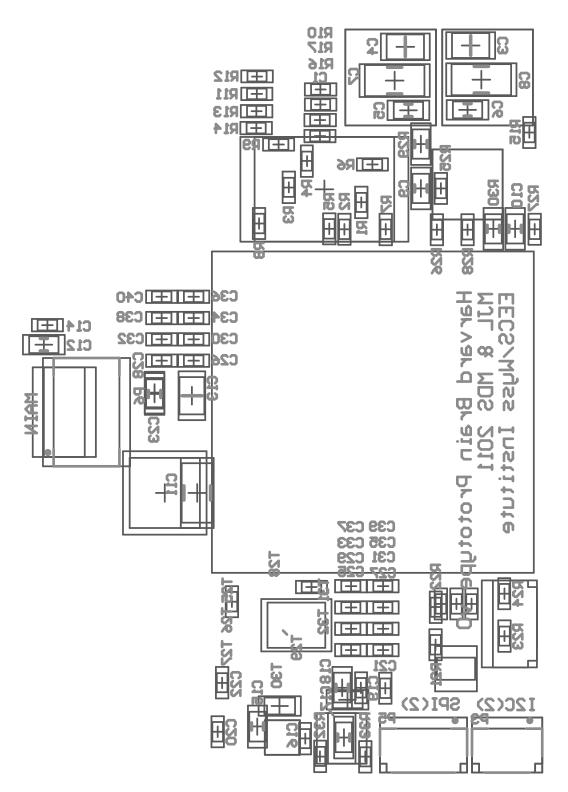

| A.23 Helicopter brain prototype layout: front (top) layer                |

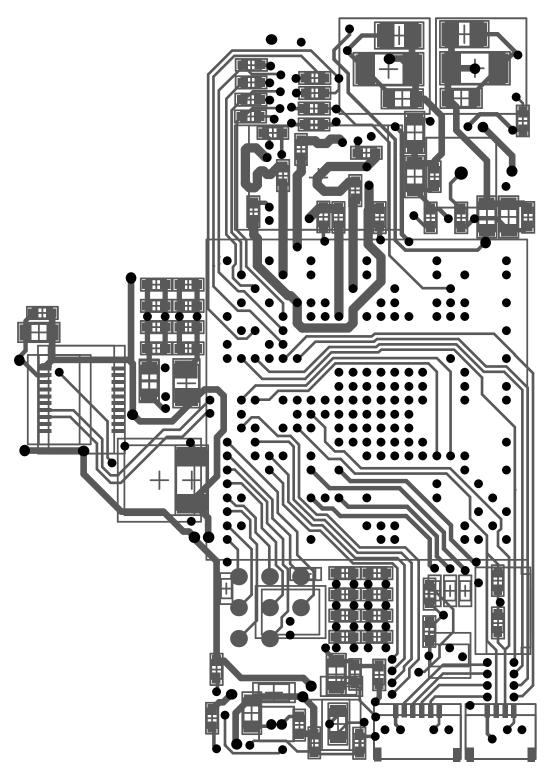

| A.24 Helicopter brain prototype layout: back (bottom) layer              |

| A.25 Helicopter brain prototype components: front                        |

| A.26 Helicopter brain prototype components: back                         |

# List of Tables

| 1.1 | Summary of analyzed accelerated architectures     |

|-----|---------------------------------------------------|

| 2.1 | Bloom filter configurations                       |

| 3.1 | Accelerators studied                              |

| 3.2 | Example handle table layout                       |

| 4.1 | PM FPGA resource overheads                        |

| 4.2 | PM compute logic block processing delays          |

| A.1 | XC6-SLX150 resource utilization for RoboBee brain |

## Previous work

Portions of this dissertation appeared in the following:

- S. Chang, A. Kirsch, and M. Lyons. Energy and storage reduction in data intensive wireless sensor network applications. Technical Report TR-15-07, Harvard University, 2007.

- M. J. Lyons and D. Brooks. The design of a bloom filter hardware accelerator for ultra low power systems. ISLPED, Aug. 2009.

- M. J. Lyons, M. Hempstead, G.-Y. Wei, and D. Brooks. The accelerator store framework for high-performance, low-power accelerator-based systems. IEEE CAL, 9(2): 5356, 2010.

- M. J. Lyons, D. Brooks, and G.-Y. Wei. The accelerator store: A shared memory framework for accelerator-based systems. ACM TACO, 8(4):122, 2012.

- M. Lyons, G. Wei, and D. Brooks. Shrink-fit: A framework for flexible accelerator sizing. IEEE CAL, PP(99), 2012.

- M. Lyons, G. Wei, and D. Brooks. The ShrinkFit Acceleration Framework: Simplifying Multi-Accelerator System Development. Under review.

## Acknowledgements

The past seven years have hardly been spent alone. I'm thankful for the many people who have been with me on this journey.

I would like to thank my family, who have shared my ups and downs many times over. To my parents, thank you for your unwavering trust, advice, and love. To my brother and sister, thank you for being there for me, with plenty of cake. And to the rest of my family, thanks for your support and understanding throughout the many Thanksgivings where I "just had to code up one more thing." I couldn't have gotten this far without your love and patience.

I must thank my friends in Boston, who have kept me grounded each day. Nathan and Hallie, your friendship means more than words or ice cream can express. Sasha and Mike, thank you for the tapir-positive company, over waffles and espressos, for the past ten years. Jud and Kevin, thank you for hearing me out, hanging out, and goading me on day after day.

I certainly couldn't do this without the support of the lab. David and Gu, thank you so much for your years of guidance and advice. Mark, Ben, and Ankur, thank you for leading the way and helping me find my feet when I was new to graduate school. Glenn, thanks for your patient help at all hours! And thank you to my labmates, for their countless hours of discussion, opinion, and tolerance. And good luck to those of you who are still working toward their degree and those who are just starting. If you ever need anything, don't hesitate to ask.

I'd also like to thank my friends at Dropbox, who helped me power through to the end. In particular, I'd like to thank Tido, Alex, Sujay, and Arash, who gave me the energy for my last push.

And finally, I'd like to mention two people who I met while in the midst of my PhD. Nora and Ben, you fill me with hope, and I look forward to all that you will accomplish in the future.

This work is dedicated to Ben and Nora

## Chapter 1

# The potential for accelerated computing

For many years, the computing industry mined clock scaling for consistent performance improvements. Eventually, rising power demands put an end to clock scaling, forcing the industry to switch to multicore architectures. This pivot has not been a silver bullet: multicore performance improvements have failed to keep pace with previous clock scaling gains. The computing industry needs a third approach, not just to regain, but to exceed the performance improvements once taken for granted. A growing body of research suggests that approach is hardware acceleration.

Hardware accelerators (circuits customized for a specific workload or class of workloads) offer many advantages over multicore approaches. First, acceleration can boost performance up to 100x-1000x [30, 33], far beyond multicore's ideal linear increases. Second, acceleration is not dependent on parallelized code and offers significant single-threaded speedups. Third, acceleration performance is not threatened by hard power budgets and the "dark silicon" problem, which will force greater portions of processors to be unused.

By specializing for a specific workload, accelerators can realize orders-of-magnitude performance improvements. This specialization is a double edged sword, however, and results in logic that can only perform its specialized task. The trade-off between performance and workload flexibility, as well as scalability, design complexity, and production cost, distinguish the many types of accelerated computer architectures. No single accelerated architecture is best for all needs—several

approaches exist each with unique trade-offs. This chapter surveys many of these accelerated architecture families, and examines the benefits and trade-offs of each.

This chapter continues with Section 1.1, which discusses the computer industry's previous sources of performance improvements, and describes why acceleration is poised to be a significant part in the future. Section 1.2 analyzes many popular approaches to acceleration in research and in production. Section 1.3 discusses current and upcoming research challenges, critical to realizing the accelerated computing vision.

## 1.1 Trends in computing

Decades of computing have produced countless innovations. The computing industry once depended on process scaling to simultaneously improve performance through faster clock speeds and keep power consumption manageable. When threshold voltage scaling slowed and increased clock speeds incurred prohibitive amounts of power, the computing industry looked to multicore approaches for an alternative source of performance increases. Although the performance of individual cores do not improve much, the increasing core counts on chip offer additional performance improvements. However, multicore performance improvements have not kept pace with performance improvements once offered by clock scaling. A third approach, hardware acceleration, is necessary.

This section explains how the computing industry got here, why current multicore approaches do not keep pace with necessary performance improvements, and how acceleration can meet or exceed performance improvements once taken for granted.

#### 1.1.1 The end of clock scaling

Moore's Law, which states the size of a transistor shrinks in half every eighteen months, has been the cornerstone of processor improvements for most of the industry's existence. Performance improved when process technologies shrunk, since each transistor became faster and more transistors could fit on the same piece of silicon. Threshold voltages also shrank with successive process technologies, keeping power budgets from exploding despite faster clock speeds and doubling transistor counts.

Unfortunately, performance improvements ran dry near the turn of the century. Although process technologies continued to shrink, threshold voltage scaling slowed. Clock speeds could

continue scaling upward, but the power cost would exceed 100W, beyond which operation and cooling costs become too great [11].

#### 1.1.2 The limits of multicore

Although process technology scaling ceased to provide significant threshold voltage reductions, process scaling continued to offer more transistors for the same piece of silicon. To make the most of the increasing transistor counts, multicore architectures utilizing multiple copies of the same cores gained favor. Ideally, processor performance increases linearly with each additional core. However, several impediments dampen the performance increases once common with clock scaling:

Parallelism. Most software cannot take advantage of multicore architectures automatically, but instead must be parallelized to use multiple cores at once. In many workloads, the additional work required to parallelize software is difficult, or parallelization will not improve performance due to multithreading overheads. Even for most parallelized software, there is a limit to parallelism, after which performance suffers from diminished returns. For many workloads, there is a point past which more cores will not substantially increase performance.

Energy. Despite curbing clock frequency increases, multicore architectures are beginning to hit energy limits again. Due to the slowing of threshold voltage reductions and exponential increase in transistors, some multicore processors will not be able to utilize all of their logic simultaneously. Up to 91% of some processors may need to be turned off by the 11nm node, resulting in large amounts of unused logic called "dark silicon" [56].

Slow clocks. Before multicore approaches, successive processor designs utilized both increased transistor budgets and faster clock speeds. The additional transistors were used for more complicated logic, such as deeper pipelines, more complex branch predictors, and so on. Although multicore architectures make use of increasing transistor counts, multicore's performance gains from increased transistors (1.35x) cannot keep up with voltage scaling era performance improvements from faster clock speeds and more transistors (1.58x) [35].

#### 1.1.3 Hardware acceleration

Hardware acceleration (logic optimized for specific workloads) offers an alternative source of performance improvements. Rather than depending on faster transistors or more transistors, hardware acceleration uses transistors more efficiently for certain tasks. As a result, hardware acceleration does not suffer from the multicore problems mentioned above. Accelerators can provide up to and beyond 100x performance improvements [29, 33] without relying on faster clock rates or parallelized software. In addition, performance improvements can be exchanged in part or in full for reduced energy through voltage and clock scaling.

Hardware acceleration typically relies on three types of optimizations to improve performance, energy, and power:

**Private memories.** Accelerators often contain private memories, which are only used by that accelerator. This allows the accelerator to access memory without contention and to use wider memories for additional memory bandwidth.

Custom operations. Support for custom operations allows accelerators to do complex calculations quickly, rather than relying on a general purpose (GP) processor to execute tens or hundreds of instructions.

**Fine-grained parallelism.** Accelerator hardware can be explicitly designed to do multiple calculations and access multiple private memories without the rigidity of SIMD or overheads of multithreading.

Dark silicon remains when using accelerators, but is not problematic for many accelerated systems. Each accelerator may only be used for a certain task and turned off at other times. For example, many smartphones currently use hardware acceleration to decode audio files, but only turn the accelerator on when playing music. Under this accelerated approach, only a small portion of accelerators will be on at a time, so large portions of the chip silicon are already dark and will not require shutting down active regions of the processor.

The biggest downside to hardware acceleration is the trade-off between customization and workload flexibility. Greater acceleration is usually possible with more specialization, but this trade-off means that the accelerator will be usable for fewer types of workloads or classes of workloads.

Unlike general purpose CPUs (GP-CPUs) which support any workload, hardware acceleration only targets a smaller subset. Therefore, acceleration is well suited for common workloads that will realize large performance, energy, or power benefits, but not occasional tasks.

Accelerators offer the potential to regain or even exceed past performance improvements, but there is little agreement on how to build accelerated systems. Several accelerated architectures are used commercially, and research efforts produce new approaches regularly. This paper surveys proven and proposed architectures, and identifies several promising directions for accelerated architecture research.

## 1.2 Accelerated architecture taxonomy

Accelerated architectures come in many forms. This section discusses several approaches for integrating acceleration into computing architectures. This discussion includes an overview of each accelerated approach and discusses six evaluation attributes:

**Execution improvement** considers performance, power, and energy improvements. The three improvements are closely related because performance speedups can be traded off for power and energy reductions by reducing clock frequency and supply voltage.

Customization describes the design variation within the architecture. This attribute spans from completely homogeneous designs supporting many workloads and consisting of several copies of the same core, to completely heterogeneous architectures containing many unique cores, each designed for a narrow set of workloads. Customization also reflects the portion of the processor expected to be active at any given time. Distributing work across multiple cores is much easier in homogeneous designs since each core can process each workload with equal skill. Heterogeneous systems tend to utilize less of the processor at any given time because only certain cores are capable of performing a particular workload. Due to growing power density and the dark silicon problem, reduced utilization may not be problematic.

Scalability reflects the architecture's ability to increase compute logic. The architecture's interconnect, which connects different components within the system, is particularly crucial for architecture scalability.

Table 1.1: Summary of analyzed accelerated architectures

Execution improvement is expressed in magnitudes. Reconfigurable computing design complexity is both low (FPGA fabric design) and high (logic implemented in FPGA).

|                                   | $Execution\\improvement$ | Customization | Scalability | $Design\\ complexity$ | $\begin{array}{c} Production \\ cost \end{array}$ | $Target\\ audience$ |

|-----------------------------------|--------------------------|---------------|-------------|-----------------------|---------------------------------------------------|---------------------|

| Digital signal processor          | 10x                      | Low           | Medium      | Low                   | Low                                               | Medium              |

| Graphics processing unit          | 100x                     | Low           | High        | Medium                | High                                              | Medium              |

| Specialized homogeneous multicore | 100x                     | Medium        | High        | Medium                | Medium                                            | Medium              |

| $Customized\ ISA$                 | 10x                      | Medium        | High        | Low                   | Low                                               | Low                 |

| $Single	ext{-}ISA$                | 1x                       | Low           | Medium      | Low                   | Low                                               | High                |

| $System	ext{-}on	ext{-}Chip$      | 1000x                    | High          | Low         | High                  | Medium                                            | High                |

| Reconfigurable computing          | 10x                      | High          | High        | Low/high              | High                                              | Low                 |

**Design complexity** describes the additional design complexities created by the accelerated architecture. This includes accelerator and system hardware design complexities as well as operating system and application software design complexities.

**Production cost** considers the additional monetary cost to fabricate a processor designed with the accelerated architecture. This cost is highly correlated with silicon area.

Target audience indicates the audience size for a processor designed with the architecture. An architecture that is more flexible to varying workloads can target a wider audience than an architecture targeting a specific workload.

Table 1.1 summarizes these six attributes for each of the accelerator architectures discussed in the remainder of this section.

#### 1.2.1 DSP

Digital signal processors (DSPs) are microprocessors modified to efficiently analyze signals. These modifications provide:

Parallelism through widened VLIW or SIMD instructions.

**Tight looping** to keep the pipeline full for repetitive tasks.

Customized ALU support for common DSP operations including fast multiplication.

Multiple memory accesses in the same cycle to enable common multiply operations at every cycle [24].

When writing DSP software, designers first use the C programming language to quickly develop code and remain close to the processor's execution semantics (pointers, heaps, stacks). Python, Java, and other higher level languages might result in faster software development, but would create too much abstraction between the programmer and the DSP hardware. In contrast, assembly language gives the programmer full access to the DSP's hardware, but slows software development to a crawl.

DSP code optimizations are often too complex for C compilers. These optimizations require absolute control over code design, and are performed in assembly language. DSP designers will first profile their program to identify commonly run code, known as "hotspots." These hotspots are run the most often, and through optimization offer the biggest performance improvements.

DSP programmers implement these optimizations by replacing hotspot C code with handtuned assembly code. To write optimized assembly code, DSP programmers must have a deep knowledge of the DSP processor's capabilities and timing. This knowledge usually only applies to specific DSP processors, and limits software platform independence.

DSP processors are available from several vendors, including Analog Devices, Texas Instruments (TI), and STMicro. DSP cores are also integrated into some mobile processors, such as TI's OMAP family [7].

#### Execution improvement

DSP processors are known to improve performance on the order of 10x when compared to GP-CPUs [69]. Although DSPs do not typically implement any unique power saving features, DSP performance improvements can be traded off for reduced power and energy consumption via frequency and voltage scaling.

#### Customization

Although DSPs feature a fully functional ISA, they are optimized for algorithms making frequent use of multiplication in tight loops. This makes DSPs an excellent choice for specific workloads, such as audio and video media processing. DSPs are highly homogeneous, and share much with GP-

CPU design. As a result, most if not all of the DSP's transistors are utilized when the processor is active. The biggest distinguishing factor of DSPs is multiply optimization in ALUs and parallelized (VLIW, SIMD) instructions.

#### Scalability

Although a single DSP could scale the number of ALUs upward, the complexity of such an approach would quickly eliminate performance gains. Instead, DSP cores could be replicated, much like general-purpose homogeneous multicore processors. This approach would closely resemble graphics processing unit (GPU) architectures.

#### Design complexity

DSP architecture complexity is comparable to general purpose microcontrollers and microprocessors. The major differences include wider instructions, a greater emphasis on looping, multiple memory ports, and additional ALUs optimized for multiplication.

Software development is more complicated, since it requires a detailed knowledge of the DSP timing behavior and optimization in assembly language. Due to the need for applications to run "close to hardware," DSP operating systems typically resemble real time operating system (RTOS) kernels [6] and are simple compared to common GP-CPU operating systems.

#### Production cost

DSPs are roughly the same size as corresponding GP-CPUs. The customizations do not add much to the area cost.

#### Target market

DSPs are typically limited to signal processing applications. Popular signal processing applications include audio, video, wireless, and speech analysis.

#### 1.2.2 Graphics Processing Unit (GPU)

Graphics processing units typically contain more than 100 simple, identical cores. These cores tend to be good at processing data in easily divided, parallelizable datasets. Each core has limited

memory bandwidth, and applications must take care to limit the bandwidth requirements of each core. Cores are designed to efficiently perform single precision floating point calculations, which are common in graphics processing. Software is most efficient when identical copies of the same code are run on each core, processing different data sets, via SIMD. GPU core architecture is as simple as possible, and struggles with control flow-heavy workloads.

GPUs use multiple memory levels, similar to memory caching levels on GP-CPUs. At the highest level, GPUs typically provide a shared cache, which is visible to all cores in the GPU. This shared structure can quickly become a bottleneck if overused, so efficient GPU applications tend to rely on local caches (visible to one core) for most memory needs. GPU programming requires explicit control over data transfers to distribute work to these local caches, and to recover the results of computation afterward.

GPUs are most commonly used for rendering graphics for video games, and are predominately manufactured by ATI and Nvidia. Software toolkits such as OpenCL and CUDA have been instrumental for accelerating scientific domain workloads.

#### **Execution improvement**

Performance improvements of 50x are typical when porting GP-CPU workloads to GPUs, and acceleration of 400x has been reported [68]. Of course, these improvements apply only to workloads well suited to SIMD parallelization and with low per-core memory bandwidth needs.

GPUs are typically performance focused, and currently are less concerned with energy or power savings. Power management approaches, such as multiple voltage domains or sub-second dynamic voltage and frequency scaling (DVFS) are limited to research, but not yet available.

#### Customization

GPUs are homogeneous, consisting of hundreds of copies of the same simple core. For this reason, all of the cores are utilized used when the GPU is active.

#### Scalability

GPUs have already demonstrated the ability to scale into the hundreds of cores. The least scalable aspect of this architecture is the global shared memory interconnect. As the number of cores

continues scaling upward, the per-core bandwidth to the global memory will proportionally decrease, and become a tighter bottleneck. In addition, data must be copied between private GPU core memories and the computer's DRAMs over the PCI bus. PCI and DRAM bandwidth limitations may also limit GPU performance in the future.

#### Design complexity

Although each GPU contains hundreds of cores, each core is an identical copy, simplifying hardware architecture design. Software design becomes more complicated however, since workloads must be parallelized, memory bandwidth requirements minimized, and data transfers carefully scheduled for hundreds of cores. Some of these complexities are lessened by toolkits, such as OpenCL and CUDA.

#### Production cost

GPU silicon area can be large, and some designs consume 3 billion transistors [26]. Roughly half of GPU area is used for cores, and the remaining half is used for graphics-specific logic.

#### Target market

GPUs are limited to easily parallelized workloads with low memory transfer needs. The largest markets with these workload characteristics include video game graphics and domain science.

#### 1.2.3 Specialized homogeneous multicore (SHM)

Specialized homogeneous multicore architectures have much in common with computers utilizing a GP-CPU and GPU. In both approaches, one general purpose CPU controls a large number of identical, simple cores. The SHM architecture replaces graphics rendering acceleration with acceleration for other workloads:

**Anton** uses acceleration for molecular dynamics to accelerate drug discovery simulations by 100x [67].

**Rigel** use a hierarchically connected set of 1000 simple, GPU-like cores to accelerate multiple algorithms with a 100x order of magnitude performance improvement [42].

Cell uses eight "SPE" floating-point, SIMD cores to accelerate media, gaming, and scientific work-loads by roughly 200x [60].

#### **Execution improvement**

Typical  $\frac{performance}{power}$  improvements using the SHM architecture are in the range of 100-200x, as the examples above illustrate. Many architectures, specifically Rigel and SODA, trade off performance improvements to lower power consumption.

#### Customization

Like GPUs, SHMs depend on limited memory transfer bandwidth and SIMD-friendly workloads. Some SHM processors are limited to certain domains (Anton, SODA), and others widen workload support by supporting more generic workloads (Rigel, Cell). Market demand for these processors range from the very limited molecular dynamics audience targeted by Anton, to the wide consumer market for the Cell processor. Although SHM processors contain two types of cores (the GP-CPU controller and the highly replicated compute cores), almost all work is done by the replicated cores, which are identical. In this sense, SHM processors are highly homogeneous, so work can be freely distributed between compute cores and sustain high silicon utilization across the SHM processor when active.

#### Scalability

SHM design scalability varies anywhere from four to over 1000 cores. Designs with few cores use simple, flat interconnects. The shared bus and ring topologies utilized by SODA and Cell, respectively, do not scale effectively in the hundred core regime. However, hierarchical interconnects of clusters, like those used by Anton and Rigel, offer scalability into hundreds and thousands of cores.

#### Design complexity

SHM architecture design complexity is on the same order of a GPU design. The bulk of the work remains in the design of the compute cores, which can be quite complicated when using larger cores such as Cell and SODA. SHMs utilizing greater numbers of simpler cores also require the additional system design complexity of a scalable interconnect. The controller GP-CPU is unlikely to add much hardware complexity, since most designs use off the shelf implementations including ARM or PowerPC designs.

Software design complexity is also similar to GPUs. The programmer must support two types of processors and must also partition workloads and processing techniques to execute well on multiple, memory bandwidth limited cores. There may be additional complexities implementing compiler tools for the computation cores, as they are custom designed.

#### Production cost

SHM production cost can be quite varied, depending on the size and number of computation cores. The cell processor contains roughly 300M transistors, though many-core designs such as Anton and Rigel may reflect similar area attributes due to the large number of cores on chip.

#### Target market

The size of the target market for SHM processors varies highly from design to design. On one end of the spectrum, Anton is highly customized and useful only to the small molecular dynamics audience. On the other end of the spectrum, the Cell processor is widely used for the Playstation 3 and scientific compute clusters.

#### 1.2.4 Customized ISA (CISA)

The customized ISA approach integrates specialization into the GP-CPU, rather than creating distinct accelerator cores. This approach results in new instructions that are limited to finer grained acceleration at the instruction level. Of course, the quantity of additional instructions is limited by the instruction bit width, especially for 32-bit ISAs. Due to the fine-grained nature of the custom ISA approach, adding software support for customized instructions is mostly automatic, courtesy

of the compiler.

Tensilica's Xtensa processor kit is widely used for the development of customized 32-bit RISC processors and corresponding software toolchains [27]. Xtensa-based processors have been used in well-known projects, including Hameed, et al. [30] and Anton. The Conservation Cores architecture takes customization one step further by automatically analyzing source code, identifying kernels ripe for acceleration, and synthesizing customizations for the core [72].

#### **Execution improvement**

Tensilica reports performance improvements of 4-72x. As with other architectures, performance enhancements can be substituted for reduced energy and power consumption.

#### Customization

The customized ISA architecture approach is moderately flexible. Unlike the coarse-grain of accelerator blocks found in SoCs, CISA's acceleration is smaller, on the instruction level. As a result, any algorithm that can benefit from the single instruction's acceleration can benefit from CISA performance improvement. However, custom instructions may still only apply to a small percentage of common computing tasks and are hardly "general purpose."

Because acceleration is built into a GP-CPU, much of the customized core consists of general purpose logic. From this perspective, the percentage of the processor spent on customization is quite low, and often only consists of a few thousand additional gates. Also note that using a CISA core to implement SHM cores, as Anton does, will result in a mostly homogeneous collection of the same replicated CISA core.

#### Scalability

Scalability of customized ISA architectures can be considered both in terms of custom instructions per core, and multicore scalability. Scaling custom instructions within the core is currently limited by the instruction set size, although this problem will lessen with a transition to 64-bit ISAs. Although a CISA core could contain hundreds of customizations, only one customized instruction can be executed at a time. For this reason, there is little reason to scale the number of customizations in a single core.

An alternative technique is to use multiple CISA core designs. Current approaches have synthesized a homogeneous collection of the same CISA core on a single processor. This approach has proven to scale into the thousands of cores using hierarchical interconnects. A heterogeneous collection of CISA cores could also be used to increase the number of parallel accelerated instructions. However, the duplication of non-accelerated logic inherent when replicating GP-CPU cores may be a downside to homogeneous or heterogeneous multicore CISA scaling. The general purpose portion of the CISA core constitutes the majority of logic, and replicating CISA cores to increase customization comes at a significant overhead.

#### Design complexity

Developing a CISA core is relatively simple, because only customizations for an already existing GP-CPU core need implementing. Software development also tends to be low complexity, because the GP-CPU's compiler only needs to be modified for the new customizations. Application support for customizations can be automatic via recompilation, assuming the modified compiler recognizes opportunities to use the new instructions. Because CISA is integrated into the GP-CPU core, no explicit memory transfers are necessary unless building a multicore CISA processor.

#### **Production cost**

Core customizations typically require only thousands of extra gates, and do not require a significant increase in area or production costs.

#### Target market

CISA cores are typically customized for a specific workload, so each CISA core's audience is significantly limited.

#### 1.2.5 Single-ISA heterogeneous multicore (SIHM)

Single-ISA heterogeneous multicore processors combine multiple cores that implement the same or similar ISAs. This approach allows for multiple implementations of a core that favor different strengths and weaknesses. Kumar, et al. uses cores from successive Alpha families to build a SIHM containing simple and lightweight cores to the latest, most complex cores [44]. By switching to

advanced cores only when the workload provides a benefit, the SIHM approach reduces unnecessary active logic.

#### Execution improvement

The SIHM approach does not attempt to increase performance, but to maximize power efficiency. The set of cores contained in a SIHM processor are usually obtained off the shelf, rather than designed specifically for the SIHM processor. Since one core is used at a time, there is no opportunity to improve performance using existing designs. Rather, SIHM allows simpler cores, without branch prediction for example, to be used when workloads would not see performance gains for more complex cores. This approach can reduce power and energy consumption by roughly 40%.

#### Customization

SIHM's reliance on a single-ISA limits the customization possible. Any customizations unique to a single core must not modify the ISA, which limits the amount of customization. Although an ISA customization could be included in all cores, this would result in a large design effort and since the customization would be common on all cores, would no longer offer any trade-off by switching cores.

Relying on off-the-shelf GP-CPUs further halts customization. By their general-purpose nature, all of the cores are designed not to optimize any particular workload.

#### **Scalability**

SIHM processors could scale to many cores, though it is unlikely that many cores supporting the same ISA exist. Also note that the single active core prevents multicore parallelism, reducing the incentives to add many cores. If this barrier is removed, SIHM processors could utilize homogeneous multicore interconnect networks to scale cores upward.

#### Design complexity

By using existing GP-CPU designs, SIHM does not require much hardware design effort. If custom cores were designed for the SIHM processor however, designing multiple unique cores for a single ISA would become a highly complex challenge.

SIHM processors use a common ISA, so no porting work is needed to target the multiple cores.

The only additional software design challenges are to include OS support for picking and switching to the best core for a given workload.

#### **Production cost**

If cores from successive processor families are used, the additional area overhead of SIHM is low. Over time, technology scaling has given processor designers more transistors for the same silicon area. As a result, older core designs use much fewer transistors than modern designs. When fabricated at the same process technology, the area of older core designs is insignificant compared to modern designs. Additionally, sharing the L2 cache SRAM between all cores reduces the area overhead of adding additional cores.

#### Target market

Due to the support for a single general purpose ISA, SIHM's can target large computing markets. If the SIHM uses an already popular ISA, the SIHM can be used as a drop-in replacement to reduce power and energy consumption in existing systems without porting. This approach could quickly provide energy savings for mobile processors which have typically relied on several generations of ARM cores, and whose workloads do not require state of the art performance at all times.

#### 1.2.6 Mobile SoC

Mobile phones typically rely on System-on-Chip (SoC) processors to efficiently handle workloads while maximizing battery life. These mobile SoCs contain a GP-CPU core (often designed by ARM) and a handful of ASIC-like accelerator cores. The accelerators are large and coarse grained, meaning that they implement large algorithm classes like 3D rendering, audio decoding, or radio basebands. The accelerators typically communicate with the GP-CPU and system memory DRAMs via a shared bus. SoCs with many accelerators and peripherals may bridge this bus to a secondary bus connecting UARTs and other low-bandwidth peripherals.

SoCs rely on DMA controllers (DMACs) to copy data between the system memory DRAM and accelerator SRAM I/O scratchpads, and many DMACs add dedicated channels to accelerators

to reduce shared bus contention. DMA is crucial for SoC performance by offloading time consuming memory transfers away from the GP-CPU.

Mobile SoCs are popular in many mobile phones and portable media players. TI's OMAP, Qualcomm's Snapdragon, and Samsung's line of SoCs are frequently used for these devices today.

Research designs have suggested relying on accelerators for frequently executed workloads and using a GP-CPU to perform less common operations when necessary. Under such an approach, the GP-CPU and unused accelerators can be turned off to save power, thus ensuring only specialized circuits are active in the common case. This approach is only feasible for domain-specific processors where "common workloads" can be identified before fabricating the processor. For example, a ULP processor utilized accelerators for wireless sensor networks to significantly reduce energy and power consumption [33] by utilizing performance improvements of up to 1000x, and scaling down voltage and frequency.

#### **Execution improvement**

As noted above, the dedicated accelerators used in mobile SoCs are known to improve performance up to 1000x. Of course, this performance improvement applies to the limited number of operations supported by the ASIC-like accelerators. These performance improvements can, and frequently are, traded off for reduced power consumption. In addition, accelerators frequently use dedicated voltage domains that can be independently turned off (VDD-gated) when not in use.

#### Customization

In contrast to the previously discussed accelerated architectures, mobile SoC accelerators are highly specialized for a specific algorithm. Furthermore, SoCs contain several unique accelerators, resulting in a much more heterogeneous architecture. The SoCs are unlikely to simultaneously compute all of the accelerated algorithms at the same time, so silicon area utilization at any given time will be much lower than homogeneous systems.

Mobile SoCs provide excellent power and performance improvements for the small subset of workloads targeted by its accelerators. These accelerators are typically too workload-specific to accelerate anything beyond this work set, and are inflexible to other domains.

#### Scalability

Mobile SoCs rely on a shared bus and a DMAC to transmit data, which are centralized and will not scale to large numbers of accelerators. The shared bus will quickly become a bottleneck, because every transfer from system DRAM memory to the accelerators or GP-CPU must go over the shared bus. If the number of accelerators grow, the traffic over the shared bus will grow with it and eventually saturate. The DMAC's central control and buffering of accelerator traffic will also become a choke point. DMACs often provide dedicated channels to high bandwidth accelerators, so that each accelerator can transfer data to system DRAMs without delay from shared bus contention. However, this centralized structure is clearly not scalable in its current implementation.

#### Design complexity

Unlike homogeneous multicore architectures, each accelerator core is unique. As a result, the accelerators cannot be replicated from a single design but must be implemented individually. Due to the typically small number of accelerator cores, the interconnect design complexity is low, making system integration of accelerators comparatively simpler.

Software must also be updated to efficiently make use of the accelerators. The operating system and shared libraries must be designed to manage memory transfers between accelerators, system DRAM memory, and the GP-CPU. Accelerators typically process workloads in batches to amortize data transfer costs. As a result, application software may need to adapt to a batched processing model, rather than individually working with small pieces of data.

#### **Production cost**

Mobile SoCs contain several accelerators in addition to the GP-CPU. As a result, the area consumed by the SoC increases with each accelerator. However, the most intensive work is performed efficiently by accelerators, reducing the need for a complex GP-CPU. As a result, a simpler GP-CPU can be used, reducing area increases brought on by the addition of accelerators.

#### Target market

The addition of coarse-grained accelerators limits mobile SoCs to the tasks which depend on popular, preset algorithms. These algorithms typically include support for audio, video, 3D rendering, radio baseband, and signal processing. As a result, these SoCs are well suited for mobile phones and media players, but few systems beyond portable media consoles.

#### 1.2.7 Reconfigurable computing

Reconfigurable computing aims to map acceleration to all possible workloads. Rather than fabricating accelerators for specific workloads, reconfigurable processors contain field programmable gate array (FPGA) logic, which consists of many small look-up tables (LUTs) and D flip-flop (DFF) register memories. By configuring these components at runtime, FPGAs appear to implement different logic. The reconfigurable approach ensures that if it is possible to make an accelerator for an algorithm, an FPGA can implement it, no matter how obscure.

The downside to FPGA technologies is overheads: a 21x increase in area, 12x increase in power, and 3-4x decrease in performance [45]. Unlike ASIC approaches, which synthesize transistors and wires directly on silicon, FPGAs must map netlists into LUTs and DFFs. Although this intermediate mapping enables FPGAs to be flexible through reconfiguration, the mapping is also inefficient. This is not to say that FPGAs will always consume more area or use more power than a synthesized GP-CPU, because FPGAs may implement accelerators that improve performance and power by several magnitudes, more than compensating for FPGA overheads. However, custom ASICs implementing the same accelerator using the same process technology will always have smaller area and power costs, and better performance.

The FPGA business has long since matured, and many FPGA processors are commercially available from Xilinx, Altera, and several other companies. Most FPGA processors now contain a combination FPGA logic and ASIC-style non-reconfigurable cores, such as multipliers, small SRAMs, and GP-CPUs. This approach aims to mitigate the area, performance, and power overheads for these commonly used components, while simultaneously providing FPGA circuitry for rarer logic.

#### **Execution improvement**

FPGAs can provide the same ASIC-style accelerator performance improvements. Due to the performance and power overheads of the inefficient LUT and DFF substrate, the performance and/or power improvements is substantially degraded. Therefore, FPGAs are ideal for less common logic which would be economically unfeasible to fabricate as an ASIC, but a poor implementation style for commonly used logic such as GP-CPUs and commonly used accelerators.

#### Customization

FPGAs are uniquely homogeneous and highly customizable. From a fabrication perspective, FPGAs mostly consist of a highly homogeneous LUT and DFF fabric. From a circuit designer's perspective, FPGAs have the potential for unprecedented customization, since FPGAs can implement any arcane netlist. Further, the same FPGA can then be reconfigured for a different netlist later, as workloads change. As a result, FPGAs are uniquely flexible and highly customized. Also, the FPGA may be fully utilized unlike other highly customized architectures, because the entire FPGA fabric can be reconfigured to efficiently target changing workloads.

#### Scalability

Due to the regular nature of the FPGA fabric, FPGAs are highly scalable. However, building onchip networks using the LUT and DFF building blocks is inefficient. This may motivate optimized, non-reconfigurable network implementations to improve large-FPGA efficiency.

#### Design complexity

Due to the separation of FPGA fabric design and the reconfigurable circuits implemented a layer above, FPGA design complexity is both simple and complex.

The FPGA fabric's design complexity is relatively low, consisting mainly of simple LUTs and DFFs. Although fabrics often contain non-reconfigurable multipliers, SRAMs, and simple GP-CPUs, designs for these components are relatively simple, and replicated throughout the FPGA fabric.

Circuit designs implemented on the FPGA fabric are decidedly more complex. Because

FPGAs make implementing custom hardware for arcane algorithms economically feasible, designing and integrating these custom accelerators introduces the complexities of mobile SoC processors to smaller design efforts. Adding "on-the-fly" reconfigurability (reconfiguring without processor downtime) adds a new level of complexity. Now, the processor must decide when and with which fabric regions to reconfigure. This is a unique and complex challenge for reconfigurable computing, since statically fabricated technologies cannot reconfigure.

#### **Production cost**

The production cost of FPGAs is comparatively cheap for low-volume designs, but high for high-volume designs. For low-volume designs, the monetary costs for one-time costs such as fabrication mask creation, time and cost overruns from design mistakes, and the long time to market makes ASIC fabrication prohibitive. FPGAs, although imposing a 21x area overhead, do not suffer from these overheads and make low-volume designs economically feasible.

However, the one-time overheads associated with ASIC fabrication are insignificant for high-volume designs, whereas the significant area overheads required by FPGA implementations are incurred for every chip. For this reason, the production cost of FPGAs is too large for high-volume projects.

#### Target market

Due to high flexibility, FPGAs can target virtually any low-volume market, since one FPGA processor design can be reconfigured for virtually any application domain. Due to production costs, FPGAs cannot compete on price for high-volume markets, which can afford to give up some processing flexibility given a large enough market for specific accelerated application domains.

## 1.3 Challenges

There are many accelerated architectures, each with a distinct approach to improve performance, energy, power, or all three. Each design has trade-offs in terms of the magnitude of execution improvements, future scalability, support for workload-specific customization, design complexity, product cost, and market potential. There is no "correct" accelerated architecture, rather, archi-

tectures better suited for certain expectations. However, it may be possible to combine approaches to maximize benefits.

Reconfigurable logic provides a unique combination of flexibility and specialization that can accelerate a wide swath of workloads without high-volume demand. However, FPGAs are unable to deliver the ultimate performance, power, and energy improvements found in the ASIC-style accelerators of mobile SoCs. A "many-accelerator" architecture, where each of the many ASIC-style accelerators targets a common workload, combines ASIC execution improvement and FPGA wide workload coverage.

In the many-accelerator vision, many accelerators for common algorithms are available onchip. Applications will therefore benefit from ASIC-level acceleration for most of their workloads, without incurring FPGA overheads. Of course, not all algorithms will be common or mature enough to warrant fabricated accelerators. In these cases, a portion of the many-accelerator processor may contain FPGA fabric. And for algorithms that do not benefit from hardware acceleration, such as state machines and system supervision, the many-accelerator system will include a GP-CPU. However, the majority of workloads will be processed by non-reconfigurable accelerators to maximize performance, power, and energy characteristics, and will only use FPGA or GP-CPU logic for the rare instances that the non-reconfigurable accelerators do not apply. As a result, the many-accelerator approach will support ASIC execution improvement and FPGA flexibility to changing workloads.

There are many opportunities for new innovations and accelerated architectures, all of which are critical to realizing the many-accelerator vision. In this section, areas of accelerated architecture design ripe for innovation are discussed.

#### 1.3.1 Rapid accelerator development

Above all else, the many-accelerator architecture requires a large number of accelerators. Unlike software libraries that utilize high-level languages (HLLs) such as C or Java, hardware accelerators are typically developed in Verilog or VHDL RTL languages. As a result, accelerators are difficult to develop. Algorithms with free software implementations commonly command tens of thousands of dollars at a minimum as RTL designs. From a design perspective, implementing a many-accelerator architecture would be prohibitively costly in terms of money or time via today's approach.

However, support for HLLs is emerging in the accelerator world. Some approaches produce RTL designs from existing languages, such as C/C++ [15]. Other HLL approaches use new languages created to represent the unique design constructs of hardware design, such as Bluespec [9]. With either approach, the time to design accelerators is greatly reduced. Although the HLL compiler may not produce the most efficient hardware designs, HLLs can enable larger design projects and wider design space explorations that would not be tractable using RTL's limited expressiveness. Extensions on the HLL approach have automated compilation tools to automatically identify and synthesize accelerators and co-design software machine code and accelerator hardware [72, 39].

HLL hardware compilers may one day make developing hardware accelerators as easy as designing software. Further, designing hardware and software may cease to be different processes.

#### 1.3.2 Identifying algorithms to accelerate

Before implementing an accelerated system, it is first necessary to identify which algorithms to accelerate. First, identifying "common algorithms" is a subjective task and will require a significant amount of workload profiling. Initially, profiling calls to system functions and shared libraries can reveal which explicitly defined algorithms are the most popular and worth accelerating. As a long term approach, similarity analysis of source code repositories would reveal other algorithms that are frequently used in software, enabling additional common accelerators.

#### 1.3.3 Minimizing accelerator area overheads

The additional area incurred by adding many accelerators must be kept to a minimum. To keep accelerator area low, the granularity of accelerators must change. Coarse-grained ASIC-style accelerators found in mobile SoCs that target entire workloads, such as video and audio decoding, work well when used independently. However, these accelerators introduce redundant logic when used in the same system, since many workloads use the same common algorithms. For example, both H.264 video and MP3 audio decoders utilize Huffman decoders and IDCTs. If these coarse-grained accelerators were included in the same processor, at least two copies of the Huffman decoder and IDCTs would be fabricated. Instead, medium-grained accelerators could reduce redundant logic, while preserving the ASIC-style performance improvements not found in fine-grained instruction level accelerators. In the medium-grain domain, accelerators would accelerate individual stages of

workload processing, such as the Huffman decoder or IDCT. These medium-grained accelerators could then be chained together to implement the same algorithms as coarse-grained accelerators, such as video or audio decoding. As a result, each medium-grained accelerator could be used for multiple algorithms, thus making each medium-grained accelerator more workload-flexible compared to coarse-grained accelerators. Also, duplicate logic area can be eliminated without incurring the performance or energy costs of shoehorning acceleration into a restrictive ISA.

#### 1.3.4 Scaling accelerator systems

To realize the many-accelerator vision, processors will include many more accelerators than current mobile SoCs. This increased accelerator count is particularly inevitable if coarse-grained accelerators are divided into several medium-grain accelerators. However, current mobile SoC interconnects that utilize shared memory for inter-core communication, centralized arbiters such as DMA controllers, and poorly scaling interconnects such as shared buses cannot support an order of magnitude increase in accelerators.