## UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Towards Automated System Synthesis Using SCIDUCTION

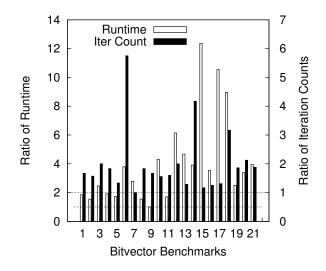

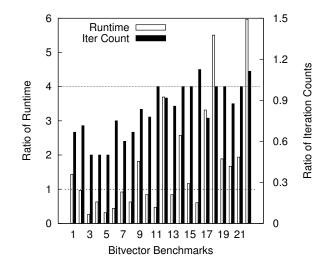

### Permalink

https://escholarship.org/uc/item/7c48g766

## Author

Jha, Susmit Kumar

# Publication Date 2011

Peer reviewed|Thesis/dissertation

Towards Automated System Synthesis Using SCIDUCTION

by

Susmit Kumar Jha

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Sanjit A. Seshia, Chair Professor Claire Tomlin Professor Dorit S. Hochbaum

Fall 2011

Towards Automated System Synthesis Using SCIDUCTION

Copyright 2011 by Susmit Kumar Jha

#### Abstract

#### Towards Automated System Synthesis Using SCIDUCTION

by

#### Susmit Kumar Jha

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

#### University of California, Berkeley

#### Professor Sanjit A. Seshia, Chair

Automated synthesis of systems that are correct by construction has been a long-standing goal of computer science. Synthesis is a creative task and requires human intuition and skill. Its complete automation is currently beyond the capacity of programs that do automated reasoning. However, there is a pressing need for tools and techniques that can automate non-intuitive and error-prone synthesis tasks. This thesis proposes a novel synthesis approach to solve such tasks in the synthesis of programs as well as the synthesis of switching logic for cyberphysical systems.

The common underlying theme of the proposed synthesis techniques is a novel combination of deductive reasoning, inductive reasoning and structure hypotheses on the system under synthesis. We call this combined reasoning technique SCIDUCTION that stands for '<u>Structurally Constrained</u> <u>Induction and Deduction</u>'. SCIDUCTION constrains *inductive* and *deductive* reasoning using *structure hypotheses*, and actively combines *inductive* and *deductive* reasoning: for instance, deductive techniques generate examples for learning, and inductive techniques generate generalizations as candidate designs to be proved or disproved by deduction.

We use the proposed synthesis approach for automated synthesis of loop-free programs from black-box oracle specifications using functions from a library of component functions, synthesizing optimal cost fixed-point code with specified accuracy from floating-point code, and synthesizing switching logic of hybrid systems for safety and performance properties. We illustrate that our approach can be used to automate system synthesis, and thus, can prove to be an effective aid to designers and developers. *To Sumit, Mum and Papa, The Source of Never-ending Eternal Hope and Assurance*

# Contents

| A | eknow | vledgements                                             | V            |  |  |  |  |  |  |

|---|-------|---------------------------------------------------------|--------------|--|--|--|--|--|--|

| 1 | Intr  | roduction                                               | 1            |  |  |  |  |  |  |

|   | 1.1   | Thesis Statement                                        | 2            |  |  |  |  |  |  |

|   | 1.2   | Challenges in Automated Synthesis                       | 3            |  |  |  |  |  |  |

|   |       | 1.2.1 Motivating Examples                               | 3            |  |  |  |  |  |  |

|   |       | 1.2.2 Common Features and Challenges                    | 12           |  |  |  |  |  |  |

|   | 1.3   | Thesis Contribution                                     | 14           |  |  |  |  |  |  |

|   |       | 1.3.1 Elements of SCIDUCTION                            | 15           |  |  |  |  |  |  |

|   |       | 1.3.2 Soundness Guarantee of SCIDUCTION based Synthesis | 16           |  |  |  |  |  |  |

|   |       | 1.3.3 Applications of SCIDUCTION                        | 16           |  |  |  |  |  |  |

|   | 1.4   | Thesis Overview                                         | 17           |  |  |  |  |  |  |

|   |       |                                                         |              |  |  |  |  |  |  |

| Ι | Syı   | nthesis of Programs                                     | 19           |  |  |  |  |  |  |

| 2 | Bac   | kground                                                 |              |  |  |  |  |  |  |

| - | 2.1   | Formalism and Notations                                 | <b>20</b> 20 |  |  |  |  |  |  |

|   |       | 2.1.1 Bitvector Programs                                | 22           |  |  |  |  |  |  |

|   |       | 2.1.2 Floating-point and Fixed-point Programs           | 27           |  |  |  |  |  |  |

|   | 2.2   |                                                         |              |  |  |  |  |  |  |

|   |       | 2.2.1 Deductive Program Synthesis                       | 30           |  |  |  |  |  |  |

|   |       | 2.2.2 Inductive Program Synthesis                       | 30           |  |  |  |  |  |  |

|   |       | 2.2.3 Synthesis from Functional Specification           | 31           |  |  |  |  |  |  |

|   |       | 2.2.4 Automated Synthesis for Program Completion        | 31           |  |  |  |  |  |  |

|   |       | 2.2.5 Program Optimization                              | 31           |  |  |  |  |  |  |

|   |       | 2.2.6 Fixed-point Program Synthesis                     | 32           |  |  |  |  |  |  |

|   |       | 2.2.7 Dimensions                                        | 33           |  |  |  |  |  |  |

| 2 | 0     |                                                         | 35           |  |  |  |  |  |  |

| 3 |       | cle Based Synthesis of Loop-free Program                |              |  |  |  |  |  |  |

|   | 3.1   | Introduction                                            | 35           |  |  |  |  |  |  |

|   |       | 3.1.1 Contributions                                     | 36           |  |  |  |  |  |  |

|   |       | 3.1.2 Problem Definition                                | 37           |  |  |  |  |  |  |

|   |       | 3.1.3 Running Example                                   | 38           |  |  |  |  |  |  |

|   | 3.2  | Scidu    | CTIVE Approach                                    |

|---|------|----------|---------------------------------------------------|

|   |      | 3.2.1    | Encoding Programs                                 |

|   |      | 3.2.2    | Oracle-Guided Synthesis                           |

|   |      | 3.2.3    | Illustration on Running Example                   |

|   |      | 3.2.4    | Optimization                                      |

|   | 3.3  |          | sion                                              |

|   |      | 3.3.1    | Choosing Base Components                          |

|   |      | 3.3.2    | Connections to Learning                           |

|   | 3.4  |          | and Experiments                                   |

|   |      | 3.4.1    | Correctness Guarantee                             |

|   |      | 3.4.2    | Experiments                                       |

|   | 3.5  |          | sion                                              |

|   |      |          |                                                   |

| 4 | Synt | hesis of | Optimal Fixed-Point Code 60                       |

|   | 4.1  | Problem  | m Definition                                      |

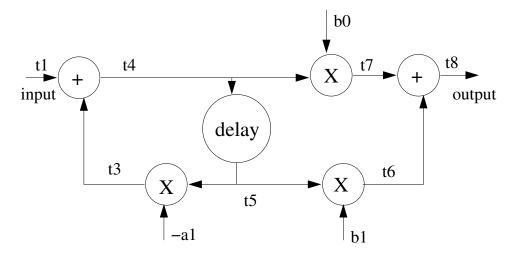

|   |      | 4.1.1    | Floating-point Implementation                     |

|   |      | 4.1.2    | Input Domain                                      |

|   |      | 4.1.3    | Correctness Condition for Accuracy                |

|   |      | 4.1.4    | Implementation Cost Model                         |

|   |      | 4.1.5    | Problem Definition                                |

|   | 4.2  | Scidu    | CTIVE Approach                                    |

|   |      | 4.2.1    | Synthesizing Optimal Types for a Finite Input Set |

|   |      | 4.2.2    | Verifying a Candidate Fixed-Point Program         |

|   |      | 4.2.3    | Illustration on Running Example                   |

|   |      | 4.2.4    | Theoretical Results                               |

|   | 4.3  | Experi   | ments                                             |

|   |      | 4.3.1    | Infinite Impulse Response (IIR) Filter            |

|   |      | 4.3.2    | Finite Impulse Response (FIR) Filter              |

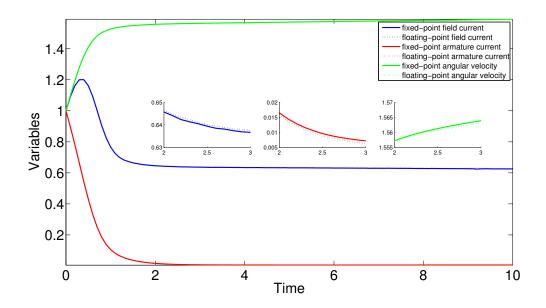

|   |      | 4.3.3    | Field Controlled DC Motor                         |

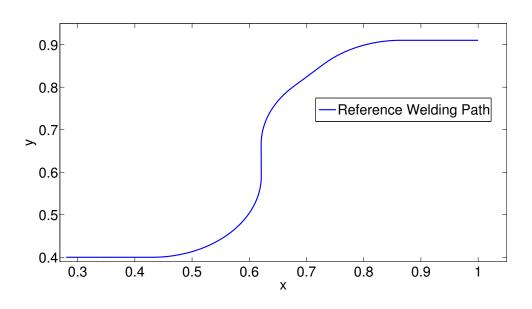

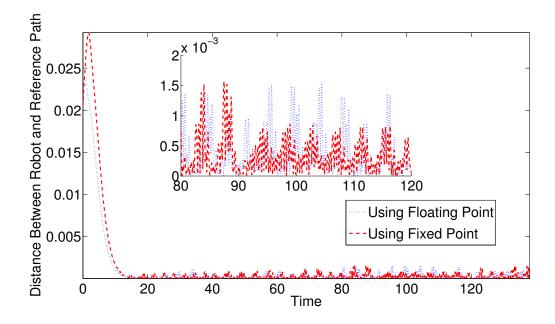

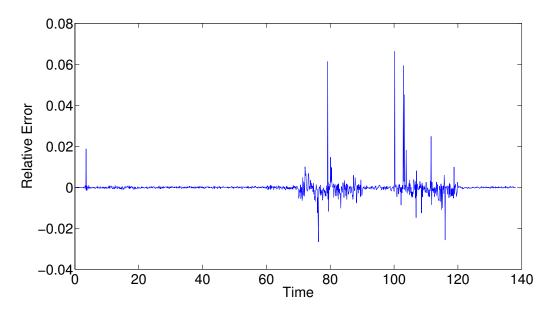

|   |      | 4.3.4    | Two-Wheeled Welding Mobile Robot                  |

|   | 4.4  | Conclu   | 8                                                 |

|   |      |          |                                                   |

# II Synthesis of Switching Logic

| 5 | Background         |                                                         |                                         |  |  |  |  |  |  |  |  |

|---|--------------------|---------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|--|--|

|   | lism and Notations |                                                         |                                         |  |  |  |  |  |  |  |  |

|   |                    | 5.1.1                                                   | Hybrid Automata                         |  |  |  |  |  |  |  |  |

|   |                    | 5.1.2                                                   | Boolean Properties                      |  |  |  |  |  |  |  |  |

|   |                    | 5.1.3                                                   | Quantitative Properties                 |  |  |  |  |  |  |  |  |

|   | 5.2 Related Work   |                                                         |                                         |  |  |  |  |  |  |  |  |

|   |                    | 5.2.1                                                   | Synthesis for Boolean Safety Properties |  |  |  |  |  |  |  |  |

|   |                    | 5.2.2 Synthesis for Quantitative Performance Properties |                                         |  |  |  |  |  |  |  |  |

|   |                    | 5.2.3                                                   | Dimensions                              |  |  |  |  |  |  |  |  |

85

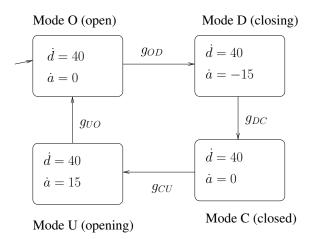

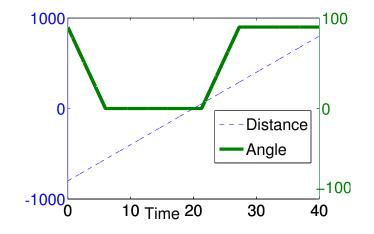

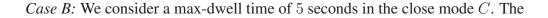

99 Synthesis of Switching Logic for Safety Specifications 6 99 6.1 6.1.1 100 6.1.2 Problem Definition 100 6.1.3 103 6.2 107 Switching Logic Synthesis for Safety 6.2.1 108 6.2.2 110 6.2.3 113 6.3 117 6.3.1 Thermostat Controller 117 6.3.2 Traffic Collision and Avoidance System 118 6.3.3 121 6.3.4 122 6.3.5 124 6.4 125 6.5 Conclusion 126 Synthesis of Switching Logic for Performance Specifications 127 7 127 7.1 7.1.1128 7.1.2 129 7.1.3 131 Running Example 7.2 132 7.2.1 133 7.2.2 135 7.2.3 140 7.3 144 7.3.1 Thermostat Controller 144 7.3.2 Oil Pump Controller 144 7.3.3 145 7.3.4Air Handling Unit in Buildings 147 7.4 Conclusion 155 8 Conclusion 156 8.1 156 Summary 8.2 157 8.2.1 Program Synthesis 157 8.2.2 Synthesis of Switching Logic 158 **Bibliography** 159

#### Acknowledgments

First, and foremost, I would like to thank my parents and my elder brother, Sumit Jha, for their love and understanding. I am ever indebted to my family and friends who I have always taken for granted and whose undying faith and well wishes have never abandoned my side. Your unconditional affection shall always be my inspiration; and *sneh*, my guiding star.

I am also grateful to my advisor, Professor Sanjit A. Seshia, for making my tenure as a graduate student productive as well as filled with fun. His kind guidance and continued encouragement has made this thesis possible. I am thankful to members of my dissertation committee: Professor Claire Tomlin and Professor Dorit Hochbaum for their insightful comments and suggestions. I am thankful to all my instructors at UC Berkeley and Indian Institute of Technology (IIT) Kharagpur. In particular, I am grateful to Professor Alberto Sangiovanni-Vincentelli and the graduate student instructor, Dr. Alessandro Pinto, who introduced me to the area of embedded systems. I am also grateful to Professor Somesh Jha, Professor Michael Jordan, Professor George Necula, Professor Dawn Song, Professor Phil Spector and Professor David Wagner for stirring my interest in programming languages, formal methods, computer security and machine learning.

I am also thankful to my internship mentors at Tata Institute of Fundamental Research (TIFR), Bombay, Ecole Polytechnique Federale de Lausanne (EPFL) and SRI International: Professor R.K. Shyamasundar, Professor Thomas Henzinger, Dr. Nir Piterman, Dr. Jasmin Fisher and Dr. Ashish Tiwari. In particular, I thank Professor Shyamasundar for making me fall in love with computer science. I am also grateful to Dr. Tiwari who is a continued source of inspiration for research as well as trekking. I am thankful to Dr. John Rushby, Dr. Shankar Natarajan and other researchers at SRI International for two wonderful and productive summers at Menlo Park. I am also grateful to my collaborators: Prateek Bhanshali, Dr. Bryan Brady, Luigi Di Guglielmo, Dr. Sumit Gulwani, Dan Holcomb, Professor Trent Jaeger, Wenchao Li, Rhishi Limaye, Dr. David Molnar, Divya Muthukumaran, Dr. David King, John Kotker, Dorsa Sadigh, and Cynthia Sturton. I am thankful to Professor S. Ramesh and Dr. Swarup Mohalik at General Motors Research, Dr. Sriram Rajamani at Microsoft Research India, Dr. Mike Kishinevsky at Intel, and Dr. Aarti Gupta at NEC Research for their continued encouragement.

Last but not the least, I am thankful to the squirrels of Berkeley for inspiring me with their contagious enthusiasm, unbridled curiosity and complete absence of fear.

# Chapter 1

# Introduction

Automated synthesis of systems that are correct by construction has being a long standing goal of computer science and engineering. But, even today, the design and analysis of systems across different domains of hardware and software development remains a predominantly human endeavor. Developers and designers still play a central role in both hardware design and software development from the inception of the design and its specification to the final testing, deployment, and system maintenance [93]. The creation of tools that can aid the designers and developers of engineered systems remains an important goal in different areas of computer science including programming languages [19], software engineering [80], formal verification [16] and electronic design automation [80].

The complete automation of the synthesis process would be an unrealistic expectation. Software development and hardware design are inherently creative tasks which require a lot of human ingenuity and insight. Building systems often involves discovering new algorithms, designing new architectures, and orchestrating details required for building larger systems as a composition of its smaller components. The complete automation of these creative tasks seems improbable in the near future, but there is definitely a pressing need for complementing human intelligence with automated synthesis techniques in domains where manual design is tedious and error-prone.

In the recent past, a lot of progress has been made in automating the verification and testing of engineered systems, and, to a lesser extent, towards automating the synthesis of such systems. Automated verification techniques enable developers and designers to quickly verify their hypothesized designs, and to discover and fix errors, if any. This undoubtedly lightens their burden by freeing them from identifying corner case scenarios, and checking their design with respect to the expected behavior manually. Automated synthesis techniques have also being proposed in niche application areas to automate mechanical aspects of the design process. But, the absence of complete specifications at the start of the design process and the computational hardness of synthesis problems, even when specifications are available, are two main reasons that have prevented a wider adoption of automated synthesis techniques.

Thus, the design and development of engineered systems still remains a *trial and error* process, especially in domains where human intuition and insight are limited due to the inherent

complexity of the design problem, and the characteristic combinatorial nature of design space. We make an effort to develop an automated approach to guide the tedious *trial and error* approach to synthesis. We focus on automated synthesis for problems that are particularly challenging to human designers. Our goal is not to replace human designers and developers; rather, we seek to investigate the development of tools and techniques that can serve as an effective computational aid in their work.

Our work on automated synthesis is motivated, in part, by the recent success in automated verification of systems [108], which is chiefly driven by the advancements in deductive reasoning techniques such as constraint solving [13, 37] and automated theorem proving [72, 111]. Deduction techniques are useful in discovering corner-cases and overlooked scenarios on which a candidate design can fail with respect to a specification provided by the user. Hence, they have proved to be valuable work-horses for automated debugging to software developers as well as hardware designers. However, purely deductive methods cannot handle many complex synthesis tasks, including those considered in this thesis. Therefore, this thesis makes an effort to propose a unified theme for automated synthesis by proposing a new approach that combines deductive reasoning with inductive inference (algorithmic learning). A central idea is to use deduction to discover example behaviors of the desired system, and then use induction to synthesize the system as generalization of the discovered behaviors. Hypotheses on the structure of the system can be provided by users to aid the induction engine in the generalization step, and to constrain the search space of deduction engines.

## **1.1** Thesis Statement

The thesis we explore in this dissertation is the following:

The systematic combination of induction, deduction, and structure hypotheses is effective in automating tricky and tedious synthesis tasks in system design.

We call this combined reasoning technique SCIDUCTION, standing for '<u>S</u>tructurally <u>C</u>onstrained <u>Induction</u> and <u>Deduction</u>' [112]. SCIDUCTION constraint *inductive* and *deductive* reasoning using *structure hypotheses*, and actively combines *inductive* and *deductive* reasoning: for instance, deductive techniques generate examples for learning, and inductive techniques generate generalizations as candidate designs to be proved or disproved by deduction.

In the rest of the chapter, we first motivate the automated synthesis problem by identifying particular applications where human insight and intuition would greatly benefit from automated reasoning support. Then, we identify the common underlying challenge in developing an automated synthesis technique for such applications. We propose SCIDUCTION as an effective solution to the challenge, and discuss how it builds on existing techniques. Then, we summarize the contributions of the thesis, and conclude this chapter by presenting the organization of the thesis.

## **1.2** Challenges in Automated Synthesis

In this section, we briefly present some design and programming problems that illustrate both the need for automation, and the limitations of human ingenuity. These problems are from diverse domains including software engineering, computer security, hardware design and cyber-physical systems. The common thread connecting all these problems is their non-intuitive nature. They clearly provide an opportunity to build techniques that can aid human designers and developers in practice. Our synthesis approach based on SCIDUCTION is motivated by these applications. While we detail our approach and show how they can be used to solve these problems later in this thesis, in this section we introduce these problems and mention how human experts solve these problems.

#### **1.2.1** Motivating Examples

We enumerate the motivating applications along with a simple example to illustrate the need for automated synthesis.

#### **Bitvector Programs**

Bitvector programs manipulate bitvectors (strings of bits) using arithmetic operators such as addition and subtraction, and bitwise operators such as bitwise and, bitwise or, and right shift. These programs are usually small loop-free code, but often involve very intricate and unintuitive tricks. In fact, the upcoming 4th volume of the classic series "Art of Computer Programming" by Knuth has a special chapter on bitwise tricks and techniques [70]. The use of both arithmetic and logical operations makes these programs difficult for programmers, and they often rely on a compendium of these algorithms published by expert programmers such as Hacker's Delight [132]. But, if a particular scenario requires a new solution which has not being previously published, programmers are forced to design these bitvector programs on their own. Such a design process is both time-consuming and error-prone. Further, these bitvector programs are used in embedded systems such as network routers and other systems where performance is important. Thus, it is desirable to use as few operations as possible to accomplish a particular task.

The following is a simple example of a bitvector program from the Hacker's Delight [132].

Given a bit-vector integer x, of finite but arbitrary length, construct a new bit-vector y that corresponds to x with the rightmost string of contiguous 1s turned off, i.e., reset to 0s.

Let us consider writing some sample input-output pairs, or examples, for the problem. For any input x, it is easy to provide the corresponding output y. Some example (x, y) pairs are (01101100, 01100000), (10100111, 10100000), (00000000, 00000000) and so on.

Procedure 1 Code for turning off rightmost contiguous 1s

```

Input: Bitvector x

Output: Bitvector y

currentIndex = length(x) - 1

while x[currentIndex] ≠ 1 do

y[currentIndex] = x[currentIndex]

currentIndex = currentIndex - 1

end while

while x[currentIndex] ≠ 0 do

y[currentIndex] = 1 - (x[currentIndex]))

currentIndex = currentIndex - 1

end while

return y

```

Procedure 2 Turning off rightmost contiguous 1s Input: Bitvector x Output: Bitvector y  $t_1 = x - 1$   $t_2 = t_1 \mid x$   $t_3 = t_2 + 1$   $y = t_3 \& x$ return y

A straightforward, but inefficient, implementation is a loop that iterates through the bits of x and zeroes out the rightmost contiguous string of 1s. We first present this simple implementation with a *while* loop in Procedure 1. The loopy implementation has O(n) comparisons and O(n) arithmetic operations for bitvectors of size n. Such bitvector manipulation programs are often used in embedded devices where they operate on large bitstrings such as network packets. Further, branching in the program in the form of the *while* loops makes this code less efficient than straight line code. It is well known that straight line code often shows better cache performance. Can we synthesize a shorter and more efficient implementation? It is difficult to answer this, but it is easy to speculate that the elementary operators: bit-wise logical operations (OR |, AND &, XOR  $\oplus$ , NEGATION  $\neg$ ), and basic arithmetic operations (ADD +, SUBTRACT -, MULTIPLY \*, DIVIDE /). The program presented in Procedure 2 can solve this problem with a straight line program using only 4 operations. Further, the solution is independent of the wordlength of the input bitvector.

A programmer will require considerable familiarity with bit-level manipulations to come up with such an implementation. In order to better appreciate the ingenuity required to come up with the program, we briefly discuss the intuition behind different operations in this program. In the first step, subtracting 1 from the bitvector turns all the trailing 0s to 1s. For instance, on input 0111001100, subtracting 1 returns 0111001011. In the next step, we do a bitwise OR with the initial input to get a bitvector which is the same except for the trailing 0 bits turned on. In our example, we obtain 0111001111. Adding 1 turns off all the rightmost-ones as well as switches back trailing 0s. The only difference from the final required result is a 1 after the rightmost string of contiguous 1s in the given input. In the case of our example, we obtain 0111010000. In the fourth and last-step, we do a bitwise AND with the initial input to obtain the final desired output bitvector which has the rightmost contiguous 1s turned off. For our example, we get 0111000000.

This example illustrates the level of experience and insight into bitwise operations required to write such bitvector programs. The insight required to write such bitvector programs becomes more and more involved with the length of the code which can be as long as 15 operations. It is difficult to expect common programmers to be able to come up with such non-intuitive programs on their own in a timely manner and without errors. Automatic synthesis of such bitvector programs is one of the applications of our synthesis approach, and is discussed in detail in Chapter 3.

#### **Program Understanding and Deobfuscation**

The next application that we consider is that of program understanding and deobfuscation. A very important component of software engineering is understanding programs. This is of even greater importance to security experts working on tasks, such as auditing third-party code, or understanding decompiled malware code.

The dependence on human experts for understanding code in order to release patches for vulnerable systems delays the response to new malware, and is often responsible for heavy economic losses. Use of obfuscation techniques by malware writers [135] to make programs really difficult to understand by humans coupled with inefficiencies of decompilers used to obtain source code from malware binaries, makes program understanding a very challenging task. An effective aid for program understanding would be the ability to select a particularly puzzling snippet of code and have an automated synthesis engine *resynthesize* its simpler but functionally equivalent version.

We illustrate this problem with a small example snippet of obfuscated code in Procedure 3 from the decompiled code of the Conficker worm. This piece of code has an infinite loop with non-intuitive branching in the control flow of the code. But, functionally, it is equivalent to the code in Procedure 4 which multiplies a number with 45. This simpler version of the program is synthesized using our synthesis technique presented in Chapter 3. It uses operators: shift-left(<<) and add(+), present in the obfuscated code as the component functions. It does not use multiply(\*) since it is not present in the obfuscated code.

Automatically inferring functionally equivalent but simpler version of obfuscated code is a difficult and time-consuming task, and it would be useful to build an automated technique to assist software engineers in this task. We discuss this application in Chapter 3 of the thesis, and show how our synthesis approach can aid programmers in deobfuscation.

```

Procedure 3 Obfuscated Code

Input: Bitvector x

Output: Bitvector y

a = 1, b = 0, z = 1, c = 0

while 1 do

if a == 0 then

if b == 0 then

y = z + y, a = \neg a, b = \neg b, c = \neg c

if \neg c then

break

end if

else

z = z + y, a = \neg a, b = \neg b, c = \neg c

if \neg c then

break

end if

end if

else

if b == 0 then

z = y << 2, a = \neg a

else

z = y << 3, a = \neg a, b = \neg b

end if

end if

end while

return y

```

Procedure 4 Multiply by 45 Input: Bitvector x Output: Bitvector y z = y << 2 y = z + y z = y << 3 y = z + yreturn y

#### **Fixed-point Implementation of Floating-point Code**

Programs written in the domains of digital signal processing and embedded systems have two important characteristics. First, they commonly contain procedures that compute functions of their inputs, where these functions are mathematically specified as operating on the reals; examples include filters used in signal conditioning and the computation of control inputs. Second, they must run in resource-constrained environments and/or at high performance, requiring their optimization for low resource cost (e.g., low power, low area) as well as for performance.

Specifically, at the high-level design stage (which could involve manually writing a "reference" program or using model-based design environments such as Simulink/Stateflow and LabVIEW), the reals are approximated with floating-point arithmetic. Designers create signal processing or control algorithms as programs based on floating-point arithmetic. However, when these algorithms must be implemented in software, they must be optimized for power and performance. It is common for embedded platforms to have processors without floating-point units due to their added cost and performance penalty. Such platforms increasingly include hardware such as field-programmable gate arrays (FPGAs), on which fixed-point arithmetic can be efficiently implemented. The signal processing/control engineer must thus redesign her floating-point program to instead use *fixed-point arithmetic*. Each floating-point variable and operation in the original program is simply replaced by a corresponding fixed-point variable and operation, so the basic structure of the program does not change. The tricky part of the redesign process is to find the *optimal fixed-point types*, viz., the optimal bit-widths of fixed-point variables, so that the implementation on the platform is optimal — lowest cost and highest performance — *and* the resulting fixed-point program is sufficiently accurate.

We present an example in Procedure 5 that illustrates this problem and the difficulty that programmers face in doing the floating-point to fixed-point translation manually. The floating-point code in this example takes radius of a circle as the input, and computes the area of the circle.

| Procedure 5 Floating-point code to compute area of circle |  |  |  |

|-----------------------------------------------------------|--|--|--|

| Input: radius                                             |  |  |  |

| Output: area                                              |  |  |  |

| double mypi, radius, t, area                              |  |  |  |

| mypi = 3.14159265358979323846                             |  |  |  |

| t = radius 	imes radius                                   |  |  |  |

| area = mypi 	imes t                                       |  |  |  |

| return area                                               |  |  |  |

In addition to the inputs of the floating-point code, the fixed-point version of the code takes the fixed-point type of the variables as an input. The fixed-point type is a 3-tuple  $\langle s_j, iwl_j, fwl_j \rangle$  for *j*-th variable where  $s_j$  denotes the signed-ness of the variable,  $iwl_j$  denotes the integer wordlength and  $fwl_j$  denotes the fraction wordlength. For example  $\langle 1, 3, 4 \rangle$  denotes a fixed-point variable that is signed and has a total wordlength of 7 bits, where the first 3-bits denote the integers and the next 4 bits denote the fractional part. So, a constant 0010010 of the fixed-point type  $\langle 1, 3, 4 \rangle$  denotes  $\frac{16+2}{24} = 1.125$  in decimal.

Different choice of the fixed-point types leads to different costs of the implementation as well as different accuracy of the fixed-point program with respect to the floating-point program. Typically, designers have a minimum threshold for accuracy. For example, they might require that the output produced by the fixed-point code might not differ by more than 1% from that produced

Procedure 6 Fixed-point code to compute area of circle

Input: radius,  $\langle s_j, iwl_j, fwl_j \rangle$  for j = 1, 2, 3, 4Output: area  $fx \langle s_1, iwl_1, fwl_1 \rangle$  mypi  $fx \langle s_2, iwl_2, fwl_2 \rangle$  radius  $fx \langle s_3, iwl_3, fwl_3 \rangle$  t  $fx \langle s_4, iwl_4, fwl_4 \rangle$  area mypi = 3.14159265358979323846 t = radius × radius area = mypi × t return area

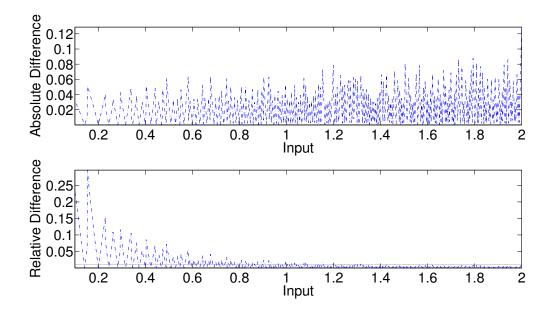

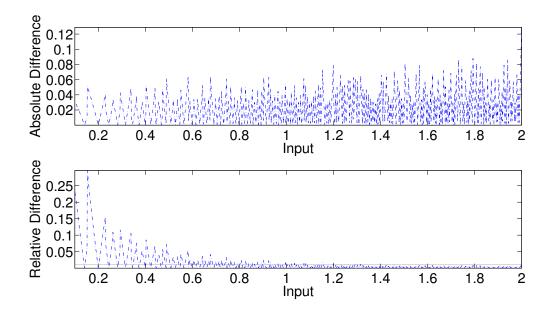

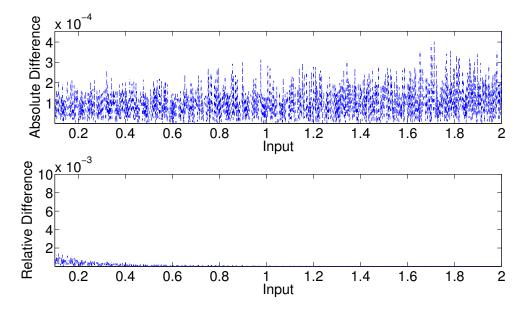

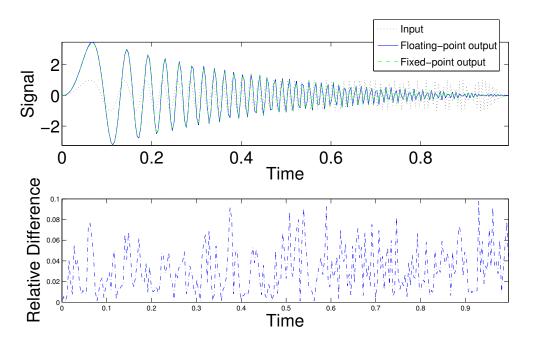

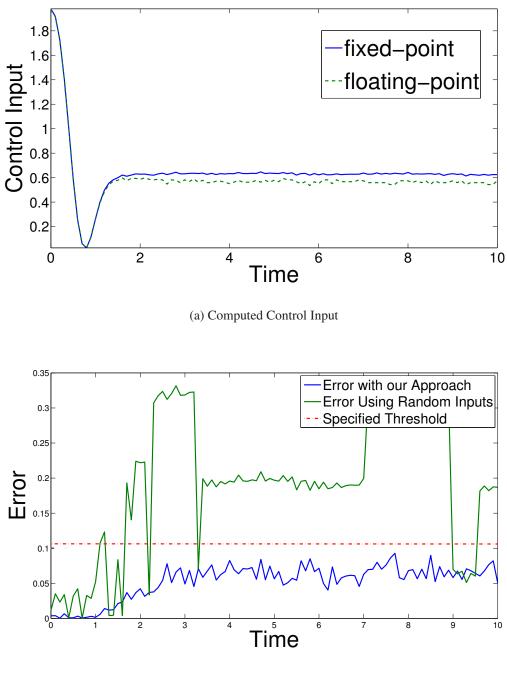

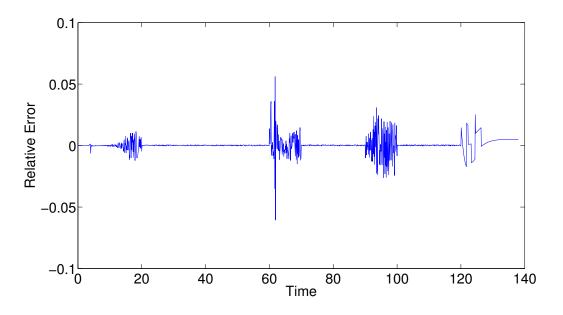

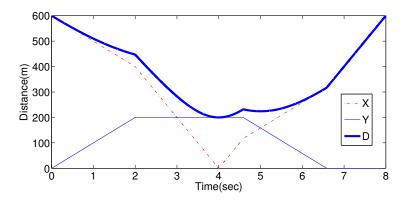

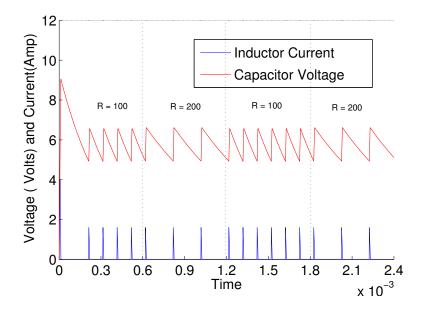

Figure 1.1: Example of Fixed-point Code with Wordlength 8

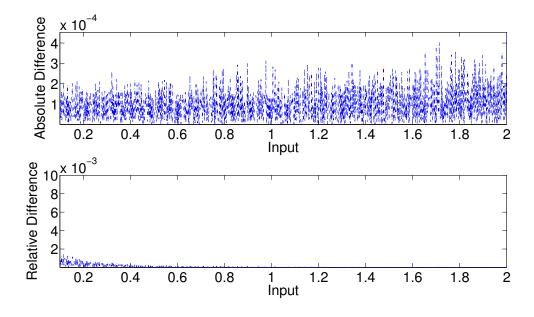

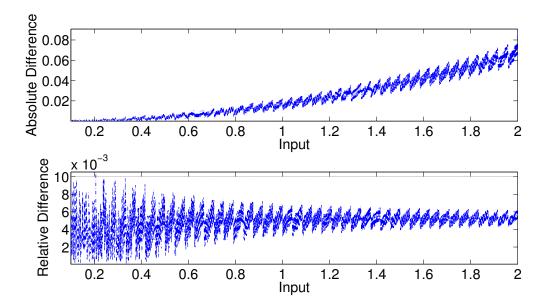

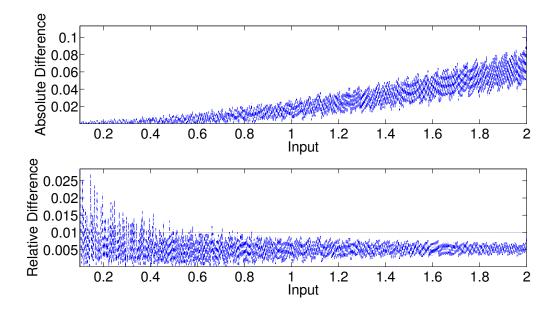

by the floating-point code. While increasing the wordlength of the fixed-point variables will lead to higher accuracy, it will also lead to higher implementation cost depending on the cost model. Using a standard cost model that models area cost of hardware implementation [38], we observe the accuracy and the cost of the example at two extremes in Figure 1.1 and Figure 1.2. The figures plot the relative and absolute difference between the floating-point and fixed-point program with given wordlengths for different values of radius from 0.1 to 2, which is domain of the input. The relative difference is the ratio between the absolute difference and the output of the floating-point program. The horizontal line indicates the maximum relative error threshold suggested by the user.

The wordlengths for all the four variables is 8 in the first case and 16 in the second case. We assign sufficient integer wordlength to avoid overflow, and leave the remaining bits for fractions. The fixed-point types in the first case are  $\langle 0, 2, 6 \rangle$ ,  $\langle 0, 1, 7 \rangle$ ,  $\langle 0, 2, 6 \rangle$ ,  $\langle 0, 4, 4 \rangle$ . The cost for this

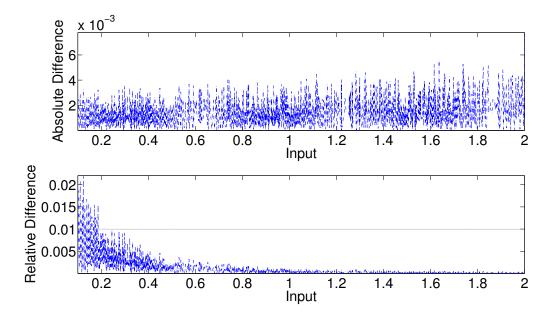

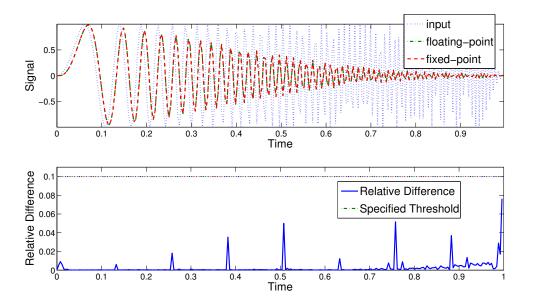

Figure 1.2: Example of Fixed-point Code with Wordlength 16

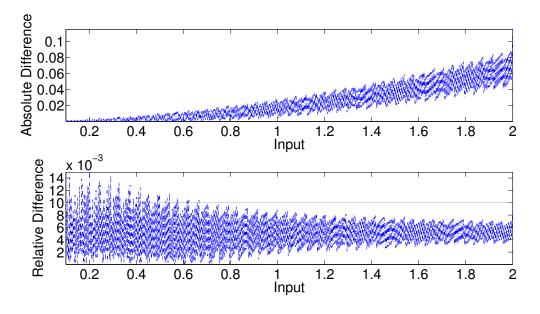

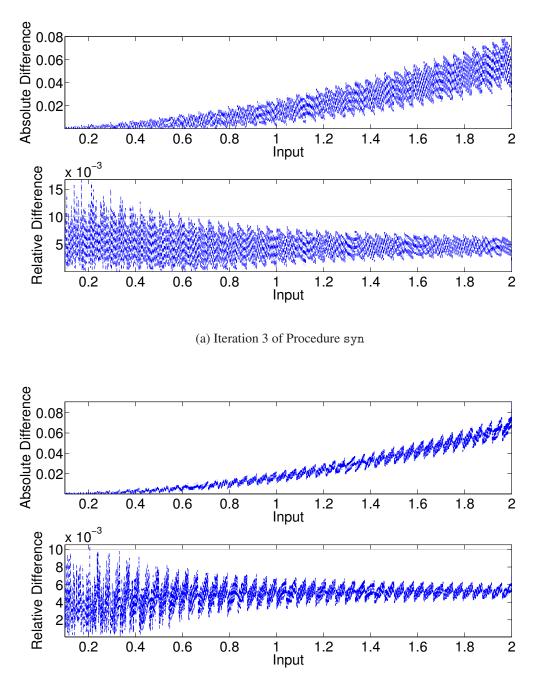

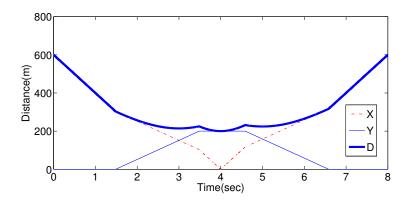

Figure 1.3: Example of Fixed-point Code Synthesized Using SCIDUCTION based Approach

implementation is 81.80 units. In the second case, the fixed-point types are  $\langle 0, 2, 14 \rangle$ ,  $\langle 0, 1, 15 \rangle$ ,  $\langle 0, 2, 14 \rangle$ ,  $\langle 0, 4, 12 \rangle$  and the cost of implementation increases to 316.20. The first case clearly violates the expected accuracy for a number of inputs, while the second one satisfies the accuracy requirement but has a very high cost. The optimal cost fixed-point code with acceptable accuracy lies in between these two extremes and a manual designer has to do a trial and error based search to discover this optimal design.

In Chapter 4, we describe how our synthesis approach can be used to automatically discover the optimal design with respect to a given cost model and expected accuracy constraint. For the example presented above, the optimal wordlengths for the four variables are 5, 10, 13, 14, that is, the optimal fixed-point types for mypi is  $\langle 0, 2, 3 \rangle$ , radius is  $\langle 0, 1, 9 \rangle$ , t is  $\langle 0, 2, 11 \rangle$  and area is  $\langle 0, 4, 10 \rangle$ . The cost for this implementation is 104.65. This was discovered using our synthesis techniques based on SCIDUCTION. The error plot for this implementation is shown in Figure 1.3.

#### Switching Logic Synthesis for Safety Properties

Cyber-physical systems, in which software interfaces with the physical world through sensors and actuators, are increasingly becoming ubiquitous. These systems are modeled as hybrid systems, that consist of multiple modes of operation of the physical plant. Controllers, often designed as software, control the switching between different modes of operation. Each mode of operation is a continuous dynamical system, and is relatively well-studied in literature on control theory [119, 110, 67]. But, the discrete part that accomplishes switching between the mode has often to be designed manually with very little computational support. These systems are used in transportation, health-care, and other societal-scale applications where safe operation of systems is very critical. Safety specifications of the system are often available as invariants on the continuous variables that model the system state of the physical world. Synthesis of switching logic such that the system stays safe is a challenging task, and often designers need to resort to simulations with different switching conditions before identifying a safe switching logic.

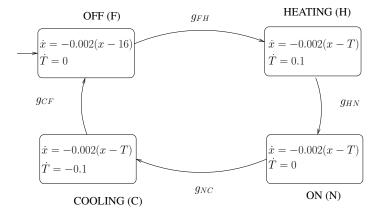

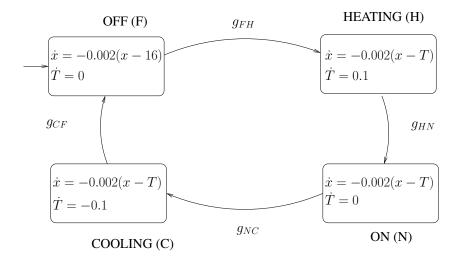

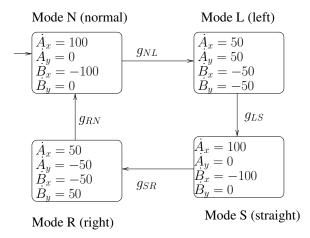

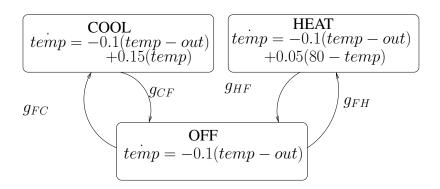

Figure 1.4: 4-mode Thermostat Controller

We illustrate it with a simple example of a 4-mode thermostat controller. It is presented in Figure 1.4. The room temperature is represented by x and the temperature of the heater is represented by T. The initial condition I is given by T = 20 degrees Celsius and x = 19 degrees Celsius. The safety property  $\phi_S$  to be enforced is that the room temperature lies between 18 and 20 degrees Celsius, that is,  $\phi_S$  is  $18 \le x \le 20$ . (We omit the units in the sequel, for brevity.)

In the OFF mode, the temperature falls at a rate proportional to the difference between the

room temperature x and the temperature outside the room, which is assumed to be constant at 16. In the HEATING mode, the heater heats up from 20 to 22. The heater cools down from 22 to 20 in the COOLING mode. In the ON mode, the heater is at a constant temperature of 22. In the HEATING, ON and COOLING mode, the temperature of the room changes in proportion to the difference between the room temperature and the heater temperature. We need to synthesize the four guards:  $g_{FH}$ ,  $g_{HN}$ ,  $g_{NC}$  and  $g_{CF}$  such that the system must respect the safety property on the room temperature x.

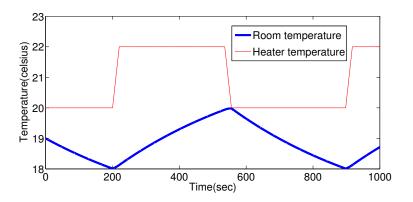

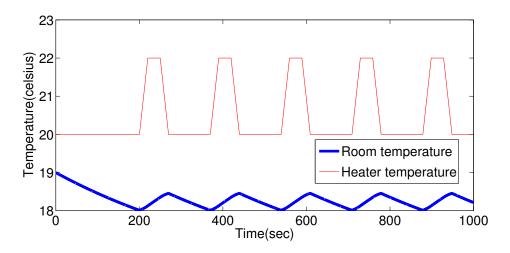

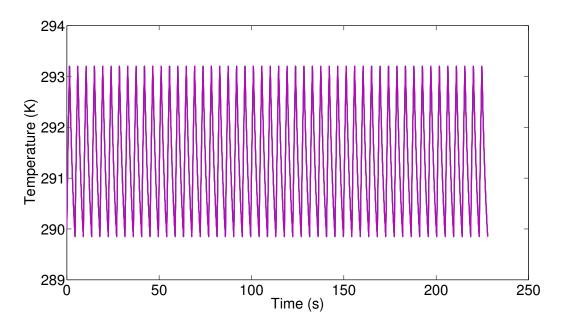

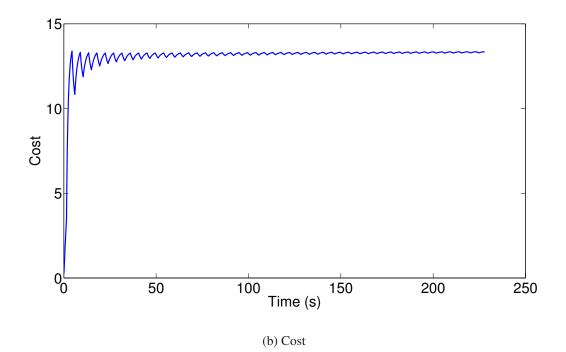

Figure 1.5: Behavior of Thermostat Controller Synthesized for Safety Specifications

We discuss how our SCIDUCTION based synthesis approach can be used to solve this problem in Chapter 6. The final guards synthesized by our technique are as follows.

| $g_{FH}$ | : | $18.00 \le x \le 18.01$ |

|----------|---|-------------------------|

| $g_{HN}$ | : | $18.00 \le x \le 18.26$ |

| $g_{NC}$ | : | $19.94 \le x \le 19.95$ |

| $g_{CF}$ | : | $19.65 \le x \le 20.00$ |

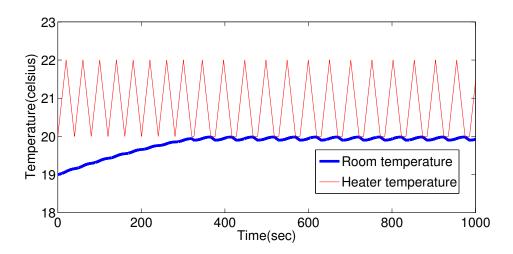

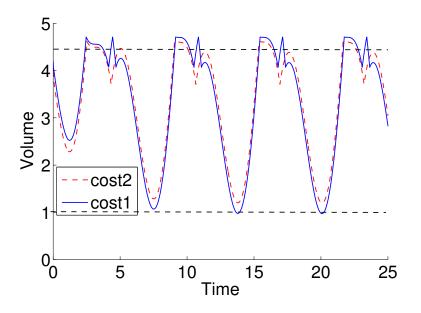

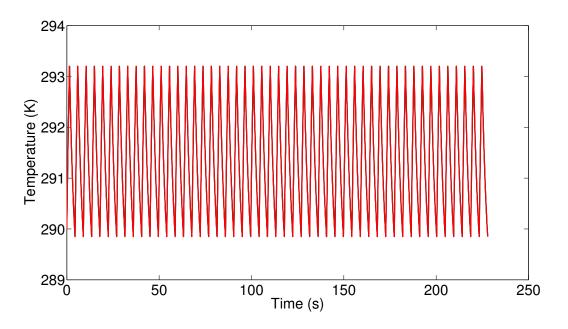

The behavior of the synthesized thermostat for the first 1000 seconds from the initial state is shown in Figure 1.5. Our technique can aid designers by synthesizing switching logic for a given safety specification.

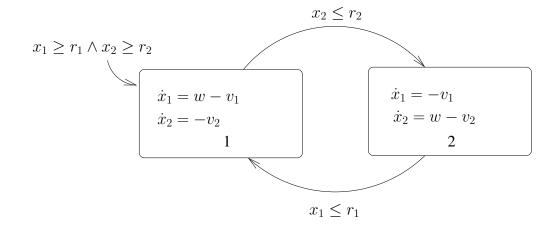

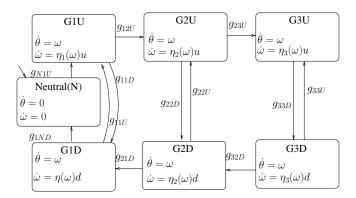

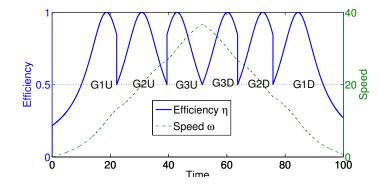

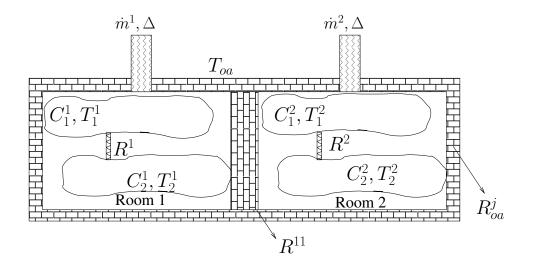

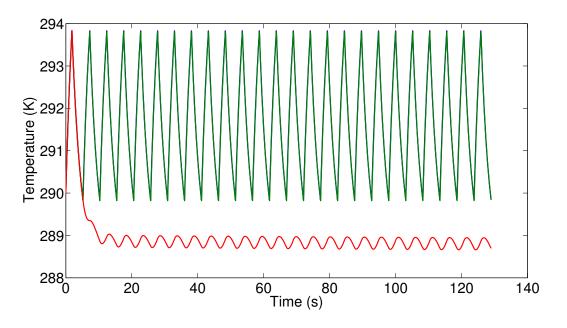

#### Switching Logic Synthesis for Optimal Performance

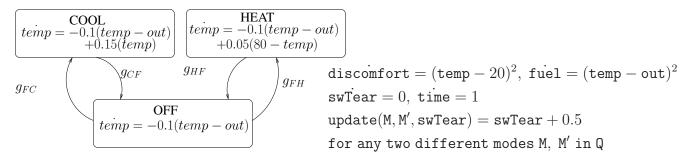

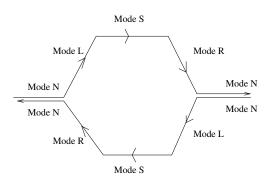

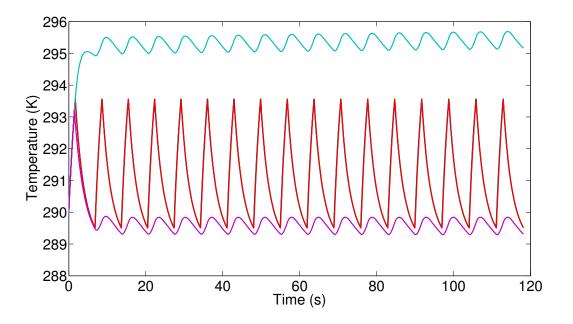

Besides the safety properties, designers often want to synthesize switching logic for controlling the switching through different modes of operations of cyber-physical systems such that the resulting system has optimal behavior with respect to a given cost metric. The cost metric may be provided as a function over the values of the continuous variables used to model the continuous plant that the controller interacts with. Further, the optimality may be desired over the *long-term* behavior of the system as opposed to a finite horizon behavior of the system upto a fixed time. We briefly explain this using a thermostat controller example similar to the one considered in Section 1.2.1. This three mode dynamical system is presented in Figure 1.6. The temperature is recorded in Celsius, and time is measured in minutes.

Figure 1.6: 3-Mode Thermostat Controller

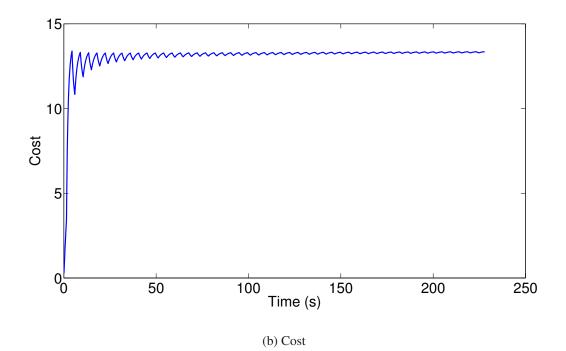

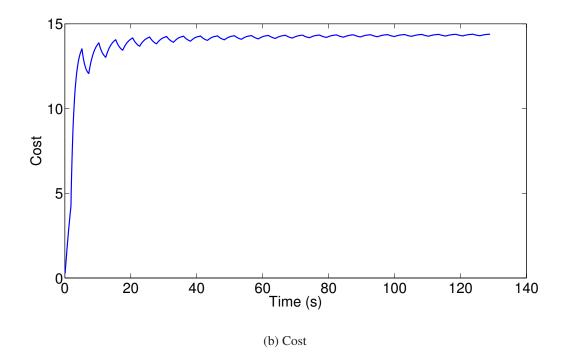

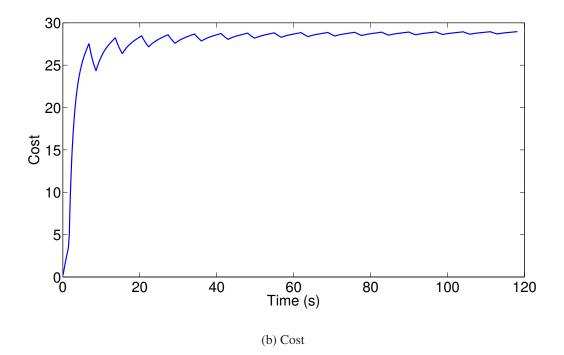

The performance requirement is to keep the temperature as close as possible to the target temperature 20, and to consume as little fuel as possible in the long run. We also want to minimize the wear and tear of the heater caused by switching. The performance metric provided by the user is given by the tuple  $\langle PR, f_{PR}, update \rangle$ , where penalty variables  $P = \{ discomfort, fuel, swTear \}$  denote the discomfort, fuel and wear-tear due to switching and reward variables  $R = \{ time \}$  denote the time spent. The evolution  $(f_{PR})$  and update functions (update) for the penalty and reward variables is shown in Figure 1.6. We need to synthesize the guards such that the following cost metric is minimized.

$$\lim_{t \to \infty} \frac{10 \times \texttt{discomfort}(t) + \texttt{fuel}(t) + \texttt{swTear}(t)}{\texttt{time}(t)}$$

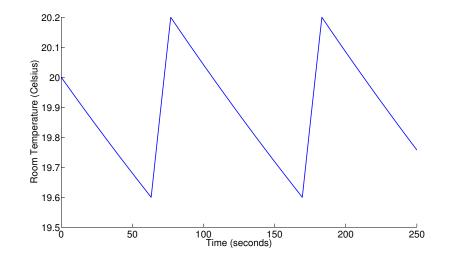

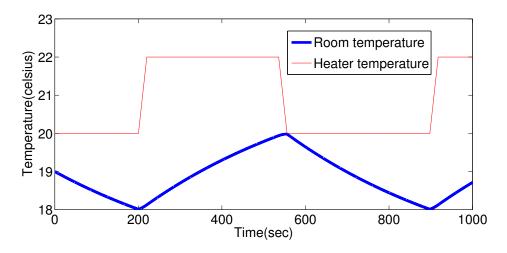

Since the reward variable is the time spent, minimizing this metric means minimizing the *average* discomfort, fuel cost and wear-tear of the heater. We give a higher weight (10) to discomfort than fuel cost and wear-tear. The behavior of room-temperature in the synthesized optimal system from the initial room temperature of 20 is shown in Figure 1.7.

Human designers would require running a huge number of simulations followed by manual reasoning from candidate switching conditions and their observed performance to synthesize a switching logic which is optimal with respect to the given performance requirement. In Chapter 7, we discuss how our automated synthesis approach based on SCIDUCTION can be used to automatically infer a switching logic that is optimal with respect to the provided performance metric.

#### **1.2.2** Common Features and Challenges

The examples presented in the previous section illustrate that a number of design problems across different domains can benefit from automation. The common features and challenges for all these examples are as follows:

Figure 1.7: Behavior of Thermostat Controller Synthesized for Performance Specifications

- 1. *Non-intuitive Design*: Design problems such as those presented in this section are not wellstructured for human reasoning. Manual insight and intuition is of very limited use for these design problems. Designers and developers have to resort to trial and error. This process is both time-consuming as well as error-prone. This makes automated synthesis techniques pertinent for such applications.

- 2. Intricate but Small Designs: The synthesis problems are intricate but are relatively small. While complete automated synthesis of operating systems and compilers appear to be infeasible, problems such as those presented in this section illustrate that automation is possible for a number of synthesis problems, that are relatively small but difficult to solve manually. Further, the fact that these small synthesis problems are often components of large complex engineered system underscores the importance of correctly and optimally solving these small but challenging synthesis problems.

- Difficult to Verify: Verification of a candidate system against the user-provided specification is either computationally expensive, making it practically infeasible such as equivalence checking of obfuscated code with simplified version, or even theoretically undecidable such as verification of multi-modal dynamical systems.

- 4. *Easy Query on Particular System Behavior*: It is easy to query about some specific behavior of the target system. For example, it is easy to obtain output of the target bit-vector code for a given input bitvector and it is easy to check whether a particular system trajectory of a multi-mode dynamical system with a given switching logic satisfies the safety property or not.

## **1.3 Thesis Contribution**

The central contribution of this thesis is a new synthesis paradigm combing induction, deduction, and structure hypotheses, along with four demonstrations. We call this paradigm SCIDUC-TION [112] based synthesis. SCIDUCTION can be used for synthesis as well as verification [112]. It builds on successful deductive techniques, such as satisfiability solving [13, 37], verification techniques [31] and numerical optimization [74], with inductive techniques such as algorithmic concept learning [6, 94]. Different instantiations of this paradigm by combining different inductive and deductive reasoning techniques were used to solve synthesis problems in different application domains. One of our main focus was on selecting applications where automated synthesis would be of most help to designers and developers.

SCIDUCTION can be seen as a *lens* through which we view the key ideas amongst the synthesis techniques presented in this thesis. SCIDUCTION uses structure hypothesis to integrate induction and deduction. *Induction* is the process of inferring a general principle from observed instances. Machine learning algorithms are typically inductive and learn a concept of classifier through generalization of examples [94, 7]. *Deduction*, on the other hand, involves the use of general rules and axioms to infer conclusions about particular problem instances [108, 16, 39]. Traditional formal verification and synthesis techniques, such as model checking or theorem proving, are deductive. It is natural since synthesis and verification are inherently deductive processes. On the other hand, inductive reasoning only ensures that the truth of its premises make it probable that its conclusion is also true. The key is the use of structure hypothesis to combine inductive and deductive reasoning to obtain the kind of guarantees obtained in deductive synthesis and verification techniques. These structure hypotheses are mathematical assumptions used to define the class of artifacts to be synthesized.

Before describing the approach, it would be useful to reflect on the combined use of induction and deduction. Looking back at manual design and development, it is easy to notice that we often employ a combination of inductive and deductive reasoning while performing synthesis. For example, while trying to synthesize a proof for a theorem, we start by working out some examples and then try to find a pattern in the properties satisfied by those examples. This step of generalizing to patterns is an inductive process. Very often, human intuition and experience implicitly provides some guiding hypotheses for discovering these patterns. These patterns yield lemma or background facts that then guide a deductive process of proving the statement of the theorem from known facts and previously established theorems. Similarly, while synthesizing a new design or developing a new program manually, one often starts by enumerating sample behaviors that the design must satisfy and hypothesizing components that might be useful in the design process. The next step is to systematically combine these components using some design rules to obtain a candidate design or program. Thus, manual synthesis process usually iterates between inductive and deductive reasoning. We attempt to formalize this combination of induction and deduction using the notion of SCIDUCTION.

#### **1.3.1 Elements of SCIDUCTION**

Formally, a synthesis problem is a pair  $\langle C_S, C_\phi \rangle$  where

- $C_S$  is the class of systems from which we need to synthesize the system, and

- the synthesized system must satisfy a given specification from the class of specifications  $C_{\phi}$ .

An instance of SCIDUCTION can be described using a triple  $\langle \mathcal{H}, \mathcal{I}, \mathcal{D} \rangle$  where the three elements are as follows:

- 1. Structure Hypothesis  $\mathcal{H}$ : This encodes our hypothesis about the form of the design to be synthesized. Formally,  $\mathcal{H}$  encodes a hypothesis that the system to be synthesized falls in a subclass  $\mathcal{C}_{\mathcal{H}}$  of  $\mathcal{C}_{S}$ , that is,  $\mathcal{C}_{\mathcal{H}} \subseteq \mathcal{C}_{S}$ . For example, consider the class of systems  $\mathcal{C}_{S}$  to be the set of all finite automata over some set of variables and satisfying a specification  $\phi$ . A structure hypothesis  $\mathcal{H}$  could restrict the finite automata to be the synchronous composition of automata from a finite library  $\mathcal{L}$ . Each possible system in  $\mathcal{C}_{\mathcal{H}}$  is some composition of automata from  $\mathcal{L}$ .

- 2. Inductive Inference Engine  $\mathcal{I}$ : This is an algorithm for learning from examples an artifact h defined by  $\mathcal{H}$ . The exact learning algorithm depends on the synthesis problem. It can be any online learning algorithm that can infer concepts from examples generated by one or more *oracles*. The oracles could be implemented using deductive procedures or a light-weight procedure such as execution of concrete model or evaluation of a black-box specification.

- 3. Deductive Engine  $\mathcal{D}$ : This is a lightweight decision procedure that applies deductive reasoning to answer queries generated in the synthesis process. The exact deduction engine depends on the synthesis problem. Deductive engine  $\mathcal{D}$  is used to answer queries generated by inductive inference engine. Each query is typically formulated as a decision problem or an optimization problem to be solved by  $\mathcal{D}$ .

The combination of inductive and deductive reasoning and their connections have being long studied in artificial intelligence [109]. Inductive inference has also being previously formulated as deduction problem where inductive bias is provided as an additional input to the deductive engine. Inductive logic programming [99], an approach to machine learning, blends induction and deduction by performing inference in first-order theories using examples and background knowledge. Combination of inductive and deductive reasoning have also been explored for synthesizing plans in artificial intelligence; for example, the SSGP approach [35] generates plans by sampling examples, generalizing from those examples, and then proving the correctness of the generalization. The important distinction between the past work and our approach is the use of combined inductive and deductive approach for automated synthesis, and we accomplish this using structure hypothesis that the user can provide to the synthesis engine.

#### **1.3.2** Soundness Guarantee of SCIDUCTION based Synthesis

A synthesis technique is sound if, given an arbitary synthesis instance  $\langle C_S, \phi \rangle$ , if it outputs S, then  $S \models \phi$ . The SCIDUCTION based synthesis approach must be proved *sound* if the structure hypothesis  $\mathcal{H}$  is true. Let  $\phi \in C_{\phi}$  be the specification and  $C_S$  be the class of systems from which we need to synthesize the system that satisfies  $\phi$  using a SCIDUCTION based synthesis technique denoted by  $\mathtt{synth}_{\langle \mathcal{H}, \mathcal{I}, \mathcal{D} \rangle}$ . The structure hypothesis  $\mathcal{H}$  assumes that if a system is synthesizable in the class  $C_S$  for the given specification  $\phi$ , the synthesized system falls in a subclass  $C_H \subseteq C_S$ . Formally, "the structure hypothesis is valid" (s.h.i.v) is defined as

$$(s.h.i.v) \triangleq (\exists c \ c \in \mathcal{C}_S \ . \ c \models \phi) \Rightarrow (\exists c \ c \in \mathcal{C}_H \ . \ c \models \phi)$$

The soundness guarantee is as follows:

$$(s.h.i.v) \Rightarrow \operatorname{synth}_{\langle \mathcal{H},\mathcal{I},\mathcal{D} \rangle}(\phi,\mathcal{C}_S) \models \phi$$

#### **1.3.3** Applications of SCIDUCTION

SCIDUCTION provides a common framework to our synthesis techniques and makes it easy to identify and apply our techniques to new problems domains. The novel synthesis techniques presented in this thesis are as follows:

- Synthesis of Loop-free Programs from Oracle Specification: Given a specification as an input/output Oracle which produces desired output for a given input, we present a synthesis technique to automatically synthesize programs using components functions from a given library of primitive functions. We use this to automatically synthesize a number of bit-vector programs. We also use it to automatically deobfuscate snippets of code by using the obfuscated code as input/output oracle, and resynthesizing functionally equivalent but easy-to-understand code. The novelty of our approach lies in using black-box specification available only as an input/output oracle. Our approach does not rely on the availability of a complete functional specification, and is more widely applicable. This enables us to handle applications such as bit-vector programs and deobfuscation. We note that reasoning with a complete specification is often difficult, as in the case of obfuscated programs. In many other cases, a complete specification is not readily available, as in the case of bit-vector programs.

- Synthesis of Fixed-point Code from Floating-Point Code: Given a floating-point code for a numerical computation routine, an accuracy specification, and the cost model of the hard-ware on which fixed-point code will be implemented, we present a synthesis technique to automatically discover the correct length of fixed-point variables in the corresponding fixed-point code. The synthesized fixed-point code meets the accuracy specification, and is of optimal cost with respect to the given cost model. The novelty of our approach lies identifying a small number of sufficient example executions of the floating-point code and

using them to discover minimal cost fixed-point code with an accuracy above the specificed threshold.

- Synthesis of Switching Logic for Safety: Given a multi-mode dynamical system describing the continuous plant representing the physical world, and a safety specification on the variables modeling the behavior of the continuous plant, we propose an automated technique to synthesize the discrete controller that controls the switching between different modes of the system. Our synthesized controller ensures that the hybrid system, consisting of the discrete controllers and the continuous plant, remains safe. The novelty of our work lies in combining numerical simulation, fixed-point algorithm, and algorithmic learning for synthesis that enables us to consider systems with arbitrary continuous behavior as long as they can be simulated.

- *Synthesis of Switching Logic for Performance*: Given a mult-mode dynamical system describing the continuous plant and a cost function on the variables modeling a given performance objective, we propose an automated technique to synthesize the discrete controller for controlling the switching between different modes of the system such that the long-term cost is minimized. The novelty of our work lies in long-term performance objectives, and in combining numerical optimization and algorithmic learning to synthesize switching conditions between different modes of the multi-mode dynamical system.

## **1.4 Thesis Overview**

The thesis is divided into two parts: the first part discusses techniques for automated synthesis of programs and the second part discusses techniques for automated synthesis of switching logic for cyber-physical systems. In Chapter 2, we discuss some preliminary material and notation along with previous work on automated program synthesis. We present the technique for synthesizing loop-free programs in Chapter 3. This is based on joint work with Sumit Gulwani, Sanjit A. Seshia and Ashish Tiwari [58]. We illustrate how our technique can be used to synthesize bitvector programs as well as perform program deobfuscation. We also contrast our work with related work and highlight the novel contributions. In Chapter 4, we present the technique for synthesizing fixed-point code from floating-point code, and demonstrate it over a set of case-studies. This is based on joint work with Sanjit A. Seshia [60]. In Chapter 5, we discuss some preliminary material and notations on automated synthesis of switching logic. We also discuss related work on automated control synthesis for multi-mode dynamical systems (hybrid systems). We present an automated synthesis technique to synthesize switching logic for hybrid systems with respect to safety specifications in Chapter 6. We also present experimental results to demonstrate its effectiveness. This is based on collaborations with Sumit Gulwani, Sanjit A. Seshia and Ashish Tiwari [59]. In Chapter 7, we present an automated approach to synthesize switching logic for hybrid systems with quantitative performance objectives. This is based on joint work with Sanjit A. Seshia and Ashish Tiwari [61]. We highlight the novelty of our work, and present case studies to demonstrate how it can be used in practice. We summarize the contributions made by the thesis in Chapter 8, and conclude the thesis by identifying future research directions.

This research was supported by NSF grants CNS-0644436 and CNS-0627734, the FCRP/-MARCO Multi-Scale Systems Center (MuSyC), Microsoft Research, Intel, and the Berkeley Fellowship for Graduate Studies from UC Berkeley.

# Part I

# **Synthesis of Programs**

# Chapter 2

## Background

In this chapter, we present relevant background on programs that will be helpful in explaining our technique for automated synthesis of loop-free programs from component functions in Chapter 3 as well as fixed-point numerical computation code from its floating-point version in Chapter 4.

## 2.1 Formalism and Notations

In this section, we formally present the syntax and semantics of programs. We begin by introducing a simple programming language *IMP* which manipulates integers using some basic arithmetic operations. The syntactic set associated with *IMP* are as follows.

- numbers N, consisting of positive and negative integers with zero,

- truth values  $\mathbf{T} = \{ false, true \},\$

- variables Var,

- arithmetic expressions Aexp,

- boolean expressions Bexp,

- commands Com.

We assume that the syntactic structure of numbers and locations is given. For instance, numbers N might be the set of signed decimal numerals for positive and negative whole numbers, and the variables Var might consist of non-empty strings of letters or letters followed by digits. The syntactic structure of the arithmetic expressions, boolean expressions and commands is given using Backus-Naur form (BNF). The convention in using metavariables over the syntactic categories is as follows:

- *n*, *m* range over numbers **N**,

- X, Y range over variables Var,

- *a* range over arithmetic expressions Aexp,

- *b* range over boolean expressions **Bexp**,

- *c* range over commands Com.

These variables can be sub-scripted or primed to make reading the rules of syntactic structure more convenient.

The arithmetic expressions Aexp are formed by the following expression rules.

$$a ::= n \mid X \mid a_o \circ a_1$$

$$\circ ::= + \mid - \mid \times \mid$$

The symbol "::=" can be read as "can be" and the symbol "|" as "or". Thus, an arithmetic expression in *IMP* can be a number n or a variable X or  $a_0 + a_1$  or  $a_0 - a_1$  or  $a_0 \times a_1$ , built from arithmetic expressions  $a_0$  and  $a_1$ .

Similarly, the boolean expressions Bexp are formed by the following expression rules.

$$b ::= true | false | a_o = a_1 | a_0 \le a_1 | \neg b | b_0 \land b_1 | b_0 \lor b_1$$

The commands Com are formed by the following expression rules.

$b ::= \mathbf{skip} \mid X := a \mid \mathbf{if} \ b \ \mathbf{then} \ c_0 \ \mathbf{else} \ c_1 \mid \mathbf{while} \ b \ c$

We now describe the semantics of the language *IMP*. Underlying a programming language is an idea of state determined by the contents of the variables Var. With respect to a state, an arithmetic expression in *IMP* evaluates to an integer and a boolean expression evaluates to a truth value. Commands change the state using the evaluated values of the arithmetic and boolean expressions in the commands. Thus, formally defining semantics of a language involves definition of *state* and then, the *evaluation* of the arithmetic and boolean expressions, and finally the *execution* of the commands.

A state is a function  $\sigma : \mathbf{Var} \to \mathbf{N}$  from variables to numbers. The set of states is denoted by  $\Sigma$ . Thus,  $\sigma(X)$  is the value of the variable X in state  $\sigma$ . The evaluation of an expression a in a state  $\sigma$  is denoted by  $\langle a, \sigma \rangle$ . The inductive syntax-directed evaluation rules specify how an arithmetic expression is evaluated in a state is presented in Table 2.1.

The rules can be read as consisting of a premise above a solid line and the conclusion below the line. When there is no premise, the solid line is omitted and only the conclusion is given. For example, the rule for sum can be read as: if  $\langle a_0, \sigma \rangle$  evaluates to  $n_0$  and  $\langle a_1, \sigma \rangle$  evaluates to  $n_1$ , then  $\langle a_0 + a_1, \sigma \rangle$  evaluates to n where n is the sum of  $n_0$  and  $n_1$ .

| Evaluation of numbers:      | $\langle n, \sigma \rangle \to n$                                                |

|-----------------------------|----------------------------------------------------------------------------------|

| Evaluation of variables:    | $\langle X, \sigma \rangle \to X$                                                |

| Evaluation of sums:         | $\langle a_0, \sigma \rangle \to n_0 \qquad \langle a_1, \sigma \rangle \to n_1$ |

| Evaluation of sums.         | $\langle a_0 + a_1, \sigma \rangle \to n$                                        |

|                             | where $n$ is the sum of $n_0$ and $n_1$                                          |

| Evaluation of subtractions: | $\langle a_0, \sigma \rangle \to n_0 \qquad \langle a_1, \sigma \rangle \to n_1$ |

| Evaluation of subtractions. | $\overline{\langle a_0 + a_1, \sigma \rangle \to n}$                             |

|                             | where $n$ is the result of subtraction $n_1$ from $n_0$                          |

| Evaluation of products:     | $\langle a_0, \sigma \rangle \to n_0 \qquad \langle a_1, \sigma \rangle \to n_1$ |

| Evaluation of products.     | $\overline{\langle a_0 \times a_1, \sigma \rangle \to n}$                        |

|                             | where $n$ is the product of $n_0$ and $n_1$                                      |

| Evaluation of division:     | $\langle a_0, \sigma \rangle \to n_0 \qquad \langle a_1, \sigma \rangle \to n_1$ |

|                             | $\langle a_0/a_1, \sigma \rangle \to n$                                          |

|                             | where $n$ is the quotient on dividing $n_0$ by $n_1$                             |

Table 2.1: Inductive Evaluation Rules for Aexp

Similarly, the evaluation of boolean expressions is specified using the set of tables in Table 2.2.

The rules for execution of commands is given in Table 2.3. Similar to evaluation of arithmetic and boolean expressions,  $\langle c, \sigma \rangle \rightarrow \sigma'$  denotes that executing command c from state  $\sigma$  yields a new program state  $\sigma'$ . For any number  $m \in \mathbb{N}$  and  $X \in \operatorname{Var}$ , we write  $\sigma[m/X]$  for the state obtained from  $\sigma$  by replacing the contents in the variable X by m, that is,

$$\sigma[m/X](Y) = \begin{cases} m & \text{if } Y = X\\ \sigma(Y) & \text{if } Y \neq X \end{cases}$$

This completes the formal description of the simple *IMP* language. When the while command is not used in a program, it is said to be a *loop-free* program. This simple *IMP* language needs to be augmented in order to describe bit-vector programs, floating-point programs and fixed-point programs. In the rest of this section, we discuss these augmentations.

#### 2.1.1 Bitvector Programs

In digital computers, data in a variable are often stored in computer memory as a bitvector, that is, a sequence of bits of some finite length. Sometimes, programs directly manipulate bitvectors instead of treating them abstractly as integers. Motivation for this was presented earlier in Section 1.2.1. Such programs that manipulate bitvectors are called bitvector programs. In order to support bitvector programs, we need to extend *IMP* language with bitvector datatypes in addition to integers and also have bitvector operations in addition to integer arithmetic operations. The program state  $\sigma$  is now a mapping from variables to numbers as well as bitvector variables

| true:                             | $\langle true, \sigma \rangle \rightarrow true$                                                           |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------|

| false:                            | $\langle false, \sigma \rangle \to false$                                                                 |

|                                   |                                                                                                           |

| Evaluation of equality:           | $\langle a_0, \sigma \rangle \to n \qquad \langle a_1, \sigma \rangle \to m$                              |

| Evaluation of equality.           | $\langle a_0 = a_1, \sigma \rangle \to true$                                                              |

|                                   | if $n$ and $m$ are equal                                                                                  |

|                                   | $\langle a_0, \sigma \rangle \to n \qquad \langle a_1, \sigma \rangle \to m$                              |

|                                   | $\langle a_0 = a_1, \sigma \rangle \to false$                                                             |

|                                   | if $n$ and $m$ are unequal                                                                                |

| Evaluation of inequality $\leq$ : | $\underline{\langle a_0, \sigma \rangle \to n} \qquad \langle a_1, \sigma \rangle \to m$                  |

| Evaluation of inequality $\leq$ . | $\langle a_0 \le a_1, \sigma \rangle \to true$                                                            |

|                                   | if $n$ is less than or equal to $m$                                                                       |

|                                   | $\langle a_0, \sigma \rangle \to n \qquad \langle a_1, \sigma \rangle \to m$                              |

|                                   | $\overline{\langle a_0 \le a_1, \sigma \rangle \to false}$                                                |

|                                   | if $n$ is not less than or equal to $m$                                                                   |

| Evaluation of negation:           | $\langle b, \sigma \rangle \to true  \langle b, \sigma \rangle \to false$                                 |

|                                   | $\overline{\langle \neg b, \sigma \rangle \to false}  \overline{\langle \neg b, \sigma \rangle \to true}$ |

| Evaluation of conjunction:        | $\langle b_0, \sigma \rangle \to t_0 \qquad \langle b_1, \sigma \rangle \to t_1$                          |

| Evaluation of conjunction.        | $\langle b_0 \wedge b_1, \sigma \rangle \to t$                                                            |

|                                   | where t is true if $t_0$ is true and $t_1$ is true,                                                       |

|                                   | and is <i>false</i> otherwise.                                                                            |

| Evaluation of disjunction:        | $\underline{\langle b_0, \sigma \rangle \to t_0 \qquad \langle \neg b_1, \sigma \rangle \to t_1}$         |

|                                   | $\langle b_0 \vee b_1, \sigma \rangle \to t$                                                              |

|                                   | where t is true if $t_0$ is true or $t_1$ is true,                                                        |

|                                   | and is $false$ otherwise                                                                                  |

| Atomic Commands | $\langle \operatorname{slrip} \sigma \rangle \rightarrow \sigma$                                                                                       |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Atomic Commands | $\langle \mathbf{skip}, \sigma  angle 	o \sigma$                                                                                                       |

|                 | $\langle a, \sigma \rangle \to m$                                                                                                                      |

|                 | $\overline{\langle X := a, \sigma \rangle \to \sigma[m/X]}$                                                                                            |

| Sequencing      | $\langle c_0, \sigma \rangle \to \sigma'' \qquad \langle c_1, \sigma'' \rangle \to \sigma'$                                                            |

| Sequencing      | $\langle c_0; c_1, \sigma \rangle \to \sigma'$                                                                                                         |

| Conditionals    | $\langle b, \sigma \rangle \to true \qquad \langle c_0, \sigma \rangle \to \sigma'$                                                                    |

| Conditionals    | $\langle \mathbf{if} \ b \ \mathbf{then} \ c_0 \ \mathbf{else} \ c_1 \ , \sigma \rangle 	o \sigma'$                                                    |

|                 | $\langle b, \sigma \rangle \to false \qquad \langle c_1, \sigma \rangle \to \sigma'$                                                                   |

|                 | $\langle \mathbf{if} \ b \ \mathbf{then} \ c_0 \ \mathbf{else} \ c_1 \ , \sigma \rangle \to \sigma'$                                                   |

| While-loop      | $\langle b, \sigma \rangle \to false$                                                                                                                  |

| white-toop      | $\langle \mathbf{while} \ b \ c, \sigma \rangle \to \sigma$                                                                                            |

|                 | $ \underline{\langle b, \sigma \rangle \to true}  \langle c, \sigma \rangle \to \sigma''  \langle \textbf{while } b \ c \rangle, \sigma'' \to \sigma $ |

|                 | $\langle \mathbf{while} \ b \ c, \sigma \rangle \to \sigma$                                                                                            |

Table 2.3: Inductive Execution Rules for commands Com

to bitvectors. We add bitvector constants bv, bitvector variables  $\mathbf{BV}$  and bitvector expressions  $\mathbf{BVexp}$  to the syntax of *IMP*. bv ranges over the bitvector constants, BV ranges over the bitvector variables and p ranges over bitvector expressions. We also their use subscripted and primed versions for clarity of the rules. The bitvector expressions  $\mathbf{BVexp}$  are formed by the following expression rules. We overload the arithmetic operations since their meaning can be inferred from the used context.

$$p ::= bv | BV | p_o \circ p_1 | \star p_0 | \text{ concat } p_0 p_1 | \text{ extract } n \ m \ p_0$$

$$\circ ::= \&\& | || | \oplus | + | - | * | / | >> | <<

$$\star ::= - | \neg$$$$

The boolean expressions for IMP are expanded to include the comparison between bitvectors.

$$b ::= true \mid false \mid a_o = a_1 \mid a_0 \le a_1 \mid \neg b \mid b_0 \land b_1 \mid b_0 \lor b_1 \mid p_0 = p_1 \mid p_0 \le p_1$$

We now give the semantics of bitvector operations. A bitvector of length m is a function whose domain is the initial segment of the naturals  $[0 \dots m)$  and the co-domain is  $\{0, 1\}$ . The *i*-the bit of a bitvector bv is denoted by bv[i] and the length of the bitvector is denoted by L(bv). In order to define the semantics, we need the following additional helper functions.

• bv2nat: This takes a bitvector bv of length m and returns an integer in the range  $[0 \dots 2^m)$  and is defined as follows:

$$\mathbf{bv2nat}(bv) = bv(m-1) \times 2^{m-1} + bv(m-2) \times 2^{m-2} + \dots bv(0) \times 2^{0}$$

• nat2bv[m]: This takes a non-negative integer n and returns the unique bitvector  $bv : [0 \dots m) \rightarrow \{0, 1\}$  of length m such that

$$bv(m-1) \times 2^{m-1} + \dots + bv(0) \times 2^0 = n \mod 2^m$$

The semantic evaluation rules for bitvector expressions  $\mathbf{BVexp}$  in a program state  $\sigma$  is given by inductive rules in Table 2.4.

| Evaluation of bitvector constants: | $\langle bv, \sigma \rangle \to bv$                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Evaluation of bitvector variables: | $\frac{\langle bv, \sigma \rangle \to bv}{\langle BV, \sigma \rangle \to BV}$                                                                           |

| Evaluation of concet:              | $\langle p_0, \sigma \rangle \to bv_0 \qquad \langle p_1, \sigma \rangle \to bv_1$                                                                      |

| Evaluation of concat:              | $\overline{\langle \mathbf{concat} \ p_0 \ p_1, \sigma \rangle \to bv}$                                                                                 |

|                                    | where $bv[i]$ is $bv_0[i]$ for $0 \le i < L(bv_0)$ and                                                                                                  |

|                                    | $bv_1[i - L(bv_0)]$ for $L(bv_0) \le i < L(bv_0) + L(bv_1)$                                                                                             |

| Evaluation of extract:             | $\underline{\langle p_0, \sigma \rangle \to bv_0}$                                                                                                      |

| Evaluation of extract.             | $\langle \mathbf{extract} \ n_0 \ n_1 \ p_0, \sigma \rangle \to bv$                                                                                     |

|                                    | where $bv[i]$ is $bv_0[i + n_0]$ for $0 \le i < n_1 - n_0$                                                                                              |

| Evaluation of bynot:               | $\langle p_0, \sigma \rangle \to b v_0$                                                                                                                 |

| Evaluation of bynot.               | $\langle \neg p_0, \sigma \rangle \to bv$                                                                                                               |

|                                    | where $bv[i]$ is $\neg bv_0[i]$ for $0 \le i < L(bv_0)$<br>$\langle p_0, \sigma \rangle \rightarrow bv_0  \langle p_1, \sigma \rangle \rightarrow bv_1$ |

| Evaluation of byand:               |                                                                                                                                                         |

| Evaluation of ovalid.              | $\langle (p_0 \&\& p_1), \sigma \rangle \to bv$                                                                                                         |

|                                    | where $bv[i]$ is 0 if $bv_0[i]$ is 0 else $bv_1[i]$                                                                                                     |

| Evaluation of byor:                | $\langle p_0, \sigma \rangle \to bv_0 \qquad \langle p_1, \sigma \rangle \to bv_1$                                                                      |

| Evaluation of ovor.                | $\langle (p_0 - p_1), \sigma \rangle \to bv$                                                                                                            |

|                                    | where $bv[i]$ is 1 if $bv_0[i]$ is 1 else $bv_1[i]$ $\langle p_0, \sigma \rangle \rightarrow bv_0  \langle p_1, \sigma \rangle \rightarrow bv_1$        |

| Evaluation of byxor:               |                                                                                                                                                         |

|                                    | $\langle p_0 \oplus p_1, \sigma \rangle \to bv$                                                                                                         |

|                                    | where $bv[i]$ is 1 if $bv_0[i] \neq bv_1[i]$ , 0 otherwise                                                                                              |

| Evaluation of byneg:               | $\langle p_0, \sigma \rangle \to b v_0$                                                                                                                 |

|                                    | $\langle -p_0, \sigma \rangle \to bv$                                                                                                                   |

|                                    | where $bv$ is $\mathbf{nat2bv}[L(bv_0)](2^m - \mathbf{bv2nat}(bv_0))$                                                                                   |

| Evaluation of byadd:               | $\underline{\langle p_0, \sigma \rangle \to bv_0 \qquad \langle p_1, \sigma \rangle \to bv_1}$                                                          |

| Living for brand.                  | $\langle p_0 + p_1, \sigma \rangle \to bv$                                                                                                              |

|                                    | where $bv_0$ and $bv_1$ are of length m and                                                                                                             |

|                                    | $bv = \mathbf{nat2bv}[m](\mathbf{bv2nat}(bv_0) + \mathbf{bv2nat}(bv_1))$                                                                                |

| Evaluation of bysub:               | $\frac{\langle p_0, \sigma \rangle \to bv_0 \qquad \langle p_1, \sigma \rangle \to bv_1}{\langle q_1, \sigma \rangle \to bv_1}$                         |