Open access • Proceedings Article • DOI:10.1109/VLSI-TSA.2018.8403867

### Towards high density STT-MRAM at sub-20nm nodes — Source link <a>□</a>

V. D. Nguyen, N. Perrissin, Steven Lequeux, Jyotirmoy Chatterjee ...+7 more authors

Institutions: University of Grenoble

Published on: 16 Apr 2018 - Symposium on VLSI Technology

Topics: Magnetoresistive random-access memory

#### Related papers:

- Spin transfer torque magnetic random-access memory: Towards sub-10 nm devices

- Spin torque switching of 20 nm magnetic tunnel junctions with perpendicular anisotropy

- Highly thermally stable sub-20nm magnetic random-access memory based on perpendicular shape anisotropy

- · Future prospects of MRAM technologies

- · Control of Sub-Nanosecond Precessional Magnetic Switching in STT-MRAM Cells for SRAM Applications

## Towards high density STT-MRAM at sub-20nm nodes

V. Nguyen, N. Perrissin, S. Lequeux, J. Chatterjee, L. Tille, S. Auffret, R. Sousa, E. Gautier, L. Vila, L. Prejbeanu, et al.

### ▶ To cite this version:

V. Nguyen, N. Perrissin, S. Lequeux, J. Chatterjee, L. Tille, et al.. Towards high density STT-MRAM at sub-20nm nodes. 2018 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), Apr 2018, Hsinchu, Taiwan. 10.1109/VLSI-TSA.2018.8403867. hal-01934201

# HAL Id: hal-01934201 https://hal.archives-ouvertes.fr/hal-01934201

Submitted on 6 Dec 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Towards high density STT-MRAM at sub-20nm nodes

# V. D. Nguyen, N. Perrissin, S. Lequeux, J. Chatterjee, L. Tille, S. Auffret, R. Sousa, E. Gautier, L. Vila, I.L. Prejbeanu and B. Dieny

1) Univ.Grenoble Alpes, CEA, CNRS, INAC-SPINTEC, Grenoble, France, steven.lequeux@cea.fr

STT-MRAM are attracting an increasing interest from microelectronics industry. They are about to enter in volume production with the first goal of replacing embedded Flash memory. To go towards high density STT-MRAM at sub-20nm nodes, two major issues have to be solved. One is the nanopatterning of the magnetic tunnel junctions at 1x feature size (F) and narrow pitch (pitch<2F). The other is to increase the thermal stability of the storage magnetization at sub-20nm nodes. Here are proposed innovative approaches to solve these two difficulties.

# I. NOVEL APPROACH FOR THE NANOPATTERNING OF MAGNETIC TUNNEL JUNCTIONS AT NARROW PITCH

Spin-Transfer-Torque Magnetic Random Access Memory (STT-MRAM) based on out-of-plane magnetized MTJ (pMTJ) is one of the most promising emerging non-volatile memory technologies. Indeed, it combines a unique set of assets: quasi infinite write endurance, high speed, low power consumption and scalability. Embedded STT-MRAM are about to replace e-FLASH memory. For this type of applications not requiring very high memory density, the preferred etching technique is still ion beam etching (IBE). However this technique is not appropriate for high density memory due to shadowing effects. This effect worsens as the memory pitch shrinks below typically 5F resulting in a poor control of the critical dimension at very dense pitch [1]. Reactive ion etching (RIE) was also tried for MTJs patterning with various gas but was found to be very complex due to the heterogeneous nature of the MTJ stacks and to cause corrosion and delamination of the magnetic materials [2]. Therefore, to be able to use STT-MRAM as a dense working memory, a new method for nanopatterning MTJ elements at small feature size (F<20nm) and narrow pitch (pitch~2F) is still required. In our novel approach, the MTJ stack is directly deposited on pre-patterned conducting pillars consisting of a non-magnetic material for which the patterning process is already well mastered (e.g Ta pillars prepared by RIE or Cu or W vias prepared by damascene process). Thus, the MTJ stack is naturally patterned while being deposited, not requiring any post-deposition etching. Some magnetic material is also deposited in the spaces between pillars. It can be left there without causing any problem. Fig. 1(a) illustrates the principle of this nanopatterning process. The prepatterned non-magnetic metallic pillars are etched with undercut by a combination of anisotropic and isotropic RIE. The undercuts prevent shortcuts between the MTJ material deposited in the trenches and the feet of the pillars.

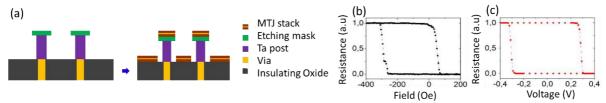

Fig. 1 (a) Illustration of the principle of the nanopatterning of magnetic tunnel junctions at sub-20nm feature size (F) and narrow pitch by depositing the MTJ stack on prepatterned pillars. (b), (c) Room temperature magnetoresistance loop of perpendicular MTJ stack deposited on pre-patterned Ta/Pt pillars versus perpendicular magnetic field (b) and voltage (c).

In this study, the prepatterned pillars consisted of Ta posts capped with a Pt etching mask. Conventional out-of-plane magnetized magnetic tunnel junction stacks were then deposited on these prepatterned arrays of pillars. Subsequently, top contacts were made on top of these junctions to measure their magnetoresistance properties and STT-switching characteristics. Fig.1 (b) and (c) illustrate typical R(H) loops and STT-switching experiments performed on such nanopatterned MTJs [3]. STT switching is observed at write voltage of the order of 0.3V for 100ns write pulse which is comparable to typical values observed in MTJs patterned by RIE.

### II. PERPENDICULAR SHAPE ANISOTROPY STT-MRAM (PSA-STT-MRAM)

In STT-MRAM, a key parameter is the thermal stability factor  $\Delta_T$  which determines the bit error rate in standby (i.e. the memory retention) and during read. In macrospin approximation,  $\Delta_T$  is given by:

$$\Delta_T = \frac{E_B}{k_B T} = \frac{A}{k_B T} \left[ \frac{1}{2} \mu_0 M_S^2 t \left( N_{xx} - N_{zz} \right) + K_S \right]$$

(1)

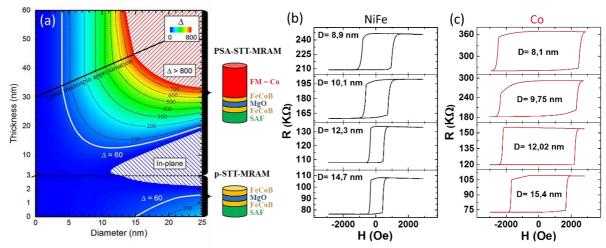

where  $E_B$  is the energy required to switch the memory between its two stable states at temperature T,  $k_B$  and  $\mu_0$  are respectively the Boltzmann constant and the vacuum magnetic permeability.  $M_S$  is the saturation magnetization,  $N_{xx}$  and  $N_{zz}$  are respectively the in-plane and out-of-plane demagnetizing factors where z refers to the out-of-plane direction,  $A=\pi(D/2)^2$  is the storage layer area with D its diameter, t its thickness,  $K_S$  is the interfacial anisotropy at the MgO/FeCoB interface. For standard FeCoB/MgO/FeCoB p-MTJs,  $N_{xx}$  -  $N_{zz}$  = -1 as the thickness (1.4 nm) is much lower than the diameter (> 20 nm) leading to a negative (i.e. in-plane) demagnetizing anisotropy. On the contrary, the strong positive interfacial anisotropy ( $K_S^{FeCoB}\sim1.4$  mJ/m2 for Fe rich alloys) pulls the magnetization out-of-plane. To fulfill industrial needs,  $\Delta_T$  should be typically in the range 60 to 100 at 300K [4] depending on the memory capacity and allowed bit error rate. Because  $\Delta_T$  scales quadratically with D for sub-20nm diameter (macrospin model)[5],  $\Delta_{300}$  inevitably drops below 60, thus limiting the downsize scalability of p-STT-MRAM. To increase  $\Delta_T$  at sub-20nm feature size, it is proposed to dramatically increase the thickness of the storage layer to values comparable to its diameter so that its shape anisotropy becomes positive (i.e. out-of plane) as the interfacial anisotropy. Fig.2 (a) shows the evolution of  $\Delta_T$  (color scale) versus storage layer diameter and thickness. This diagram shows that  $\Delta_T$  above 60 can be maintained for MTJs down to 4nm diameter provided their storage layer thickness is increased up to ~30nm.

Fig. 2 (a) Stability diagram of a cylindrical storage layer made of FeCoB(1.4 nm)/Co(t-1.4 nm) versus its total thickness (t) and diameter (D), at room temperature (300 K).  $M_S^{FeCoB} = 1.0 \cdot 10^6$  A/m and  $K_S^{FeCoB} = 1.4 \cdot mJ/m^2$ ,  $M_S^{Co} = 1.446 \cdot 10^6$  A/m and  $K_u^{Co} = 0 \cdot J/m^3$ . The iso- $\Delta$  line,  $\Delta_{300} = 60$ , is highlighted in bold white, other iso- $\Delta$  lines are shown in dashed black lines. (b), (c) Evolution of the resistance R as a function of a perpendicular field for MTJ of various diameters D in the cases of a 60 nm thick storage layer of NiFe (b) and Co (c).

This concept of Perpendicular Shape Anisotropy STT-MRAM (PSA-STT-MRAM) was demonstrated by patterning narrow MTJ pillars with thick storage layer. NiFe and Co-based storage layers were investigated. The magnetic and transport properties of these MTJs were measured electrically as illustrated in Fig.2 (b) and (c) with field applied out-of-plane. Clearly, strong perpendicular magnetic anisotropy was observed at diameter down to 8nm.  $\Delta_T$  could be as high as 200 in some of these 8nm diameter junctions demonstrating that very high thermal stability can be achieved in these PSA-STT-MRAM. Of course, the cell aspect ratio (t/D) must be adjusted to keep  $\Delta_T$  in the range 60-100 allowing to get switching by STT.

#### ACKNOWLEDGMENT

This work was funded by the ERC Advanced Grant MAGICAL N°669204. The devices were fabricated in the Plateforme de Technologie Amont (PTA) in Grenoble. We gratefully acknowledge support from the technical team. A.Chavent is greatly acknowledged for help with electrical testing instrumentation.

### **REFERENCES**

- 1) Y. Kim et al, VLSI Symposium 2011, pp. 210-211.

- 2) M.Gaidis, "Magnetic back-end technology", IEEE Press Wiley (2017); ISBN 111900974X, 9781119009740.

- 3) V.D.Nguyen et al, Proc. IEDM 2017.

- 4) D.Apalkov, B.Dieny, J.Slaughter, Proc.IEEE 104, 1796 (2016).

- 5) H.Sato et al, Jpn. J. Appl. Phys. 56, 0802A6 (2017).