## Towards Optimal Circuit Layout Using Advanced Search Techniques

by

### Shawki Areibi

A thesis presented to the University of Guelph in fulfilment of the thesis requirement for the degree of Doctor of Philosophy

in

**Electrical Engineering**

Guelph, Ontario, Canada, 2006

$\bigodot$ Shawki Areibi 2006

I hereby declare that I am the sole author of this thesis.

I authorize the University of Guelph to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the University of Guelph to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research. The University of Guelph requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

## Abstract

A VLSI chip can today contain millions of transistors and is expected to contain more than 100 million transistors in the next decade. This tremendous growth is made possible by the development of sophisticated design tools and software. To deal with the complexity of millions of components and to achieve a turn around time in terms of a couple of months, VLSI design tools must not only be computationally fast but also generate layouts close to optimal. The work in this thesis involves exploring algorithmic solutions to the problem of circuit layout in VLSI design. The exploration is an attempt to evaluate, design, improve and integrate the best combinatorial algorithms to solve the circuit layout problem. Advanced search heuristic techniques in the form of Tabu Search, GRASP and Genetic Algorithms are used extensively to solve most of the problems in circuit layout.

We show in this thesis that new hybrid partitioning techniques based on the above mentioned heuristics outperform traditional heuristic methods. In fact, these novel approaches consistently find better solutions than other methods in a fraction of the time. A new placement algorithm that is suitable for standard cell layout is also presented. The initial placement is obtained using the partitioning algorithm. An efficient clustering based algorithm is developed to further reduce the complexity of circuit partitioning and placement and improve the performance of the design process in terms of quality and computation time. Finally, parallel implementations of the developed heuristics on a network of workstations are presented and significant speedups are reported. The ability of the hybrid heuristics to find near optimal solutions is assessed by comparing their performance with a general purpose mixed integer programming package. Experimental results indicate that our heuristics based on clustering and hybridization schemes give very good results and are suitable for VLSI circuits.

## Acknowledgements

My sincere thanks go to my supervisor Professor Vannelli for his support and advice throughout this research. Without his help, this work would never have been possible.

I would like to thank Professor Michel Minoux from the University of Paris for being my external examiner. I am deeply indebted to Professor M. Kamel, C. Gebotys, G. Kesidis from the University of Waterloo, for their advice and helpful discussions.

I would also like to thank Phil Regier the system administrator of the VLSI group, for his patience and help.

Many of my friends helped in one way or another to accomplish this research, thanks to all especially Scott Hadley at Shell Research and Otman Basir and Yousef Berbash at the System Design Department for their helpful discussions and advice. my wife, mother, brother and children whose love and encouragement helped accomplish this thesis.

То

# Contents

| 1 | Intr | duction                                                                                                    | 1  |

|---|------|------------------------------------------------------------------------------------------------------------|----|

|   | 1.1  | The VLSI Design Process                                                                                    | 1  |

|   |      | 1.1.1 Design Representations                                                                               | 2  |

|   |      | 1.1.2 Steps Within A Design Phase                                                                          | 2  |

|   |      | 1.1.3 Electronic Design Phases                                                                             | 4  |

|   |      | 1.1.4 Complexity of Circuit Layout                                                                         | 5  |

|   | 1.2  | Motivation                                                                                                 | 6  |

|   | 1.3  | Dissertation Framework                                                                                     | 8  |

|   |      | 1.3.1 Efficiency                                                                                           | 8  |

|   |      | $1.3.2$ Robustness $\ldots \ldots 1$ | 0  |

|   |      | 1.3.3 Complexity Reduction                                                                                 | 0  |

|   |      | 1.3.4 Speed                                                                                                | 1  |

|   | 1.4  | Research Contributions                                                                                     | 1  |

|   | 1.5  | Thesis Outline                                                                                             | 4  |

| 2 | Bac  | ground 1                                                                                                   | 6  |

| - |      | -                                                                                                          | -  |

|   | 2.1  | Physical Design and Circuit Layout                                                                         | .6 |

|   |      | 2.1.1 Circuit Partitioning                                                                                 | 7  |

|   |     | 2.1.2  | Circuit Placement                           | 25 |

|---|-----|--------|---------------------------------------------|----|

|   |     | 2.1.3  | Routing                                     | 27 |

|   |     | 2.1.4  | Layout Strategies and Styles                | 30 |

|   | 2.2 | Optim  | ization Algorithms                          | 33 |

|   |     | 2.2.1  | Exact Solution Techniques                   | 34 |

|   |     | 2.2.2  | Approximate Solution Techniques             | 34 |

|   |     | 2.2.3  | Randomization Algorithms                    | 37 |

|   | 2.3 | Summ   | ary                                         | 38 |

| 3 | Adv | vanced | Search Techniques                           | 40 |

|   | 3.1 | Bench  | marks                                       | 41 |

|   | 3.2 | A Sim  | ple Dynamic Hill Climbing Heuristic         | 43 |

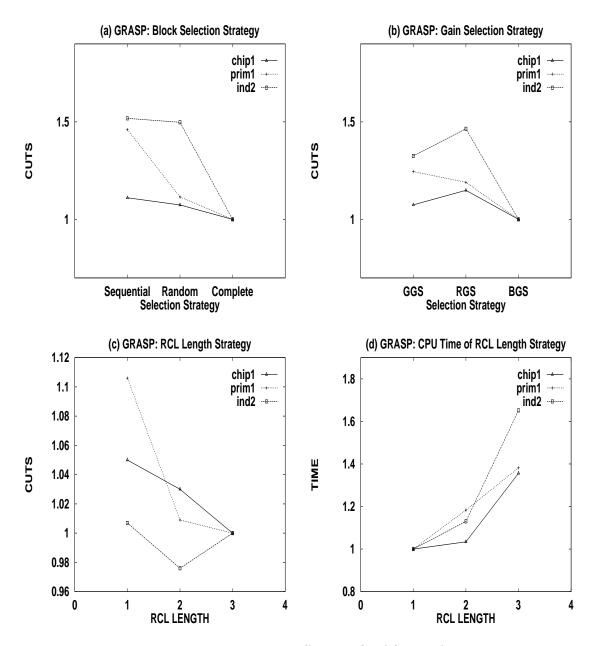

|   | 3.3 | Greed  | y Randomized Adaptive Search                | 47 |

|   |     | 3.3.1  | Implementation                              | 48 |

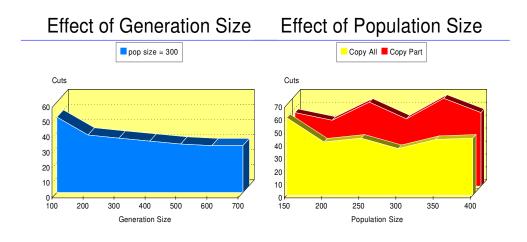

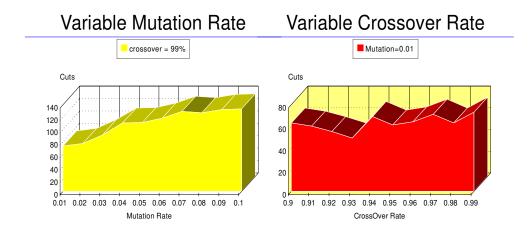

|   | 3.4 | Genet  | ic Algorithms                               | 54 |

|   |     | 3.4.1  | An Overview of Genetic Search               | 54 |

|   |     | 3.4.2  | GA Implementation                           | 60 |

|   | 3.5 | Simula | ated Annealing                              | 65 |

|   |     | 3.5.1  | Annealing Schedule                          | 67 |

|   | 3.6 | Tabu   | Search                                      | 70 |

|   |     | 3.6.1  | Tabu Search Main Foundation                 | 71 |

|   |     | 3.6.2  | Tabu Search Implementation for Partitioning | 76 |

|   |     | 3.6.3  | Adaptive Tabu Search Heuristic              | 79 |

|   |     | 3.6.4  | Performance of Advanced Search Techniques   | 84 |

|   | 3.7 | Summ   | ary                                         | 85 |

| 4 | Hyl                  | brid Se | earch Techniques                          | 87  |

|---|----------------------|---------|-------------------------------------------|-----|

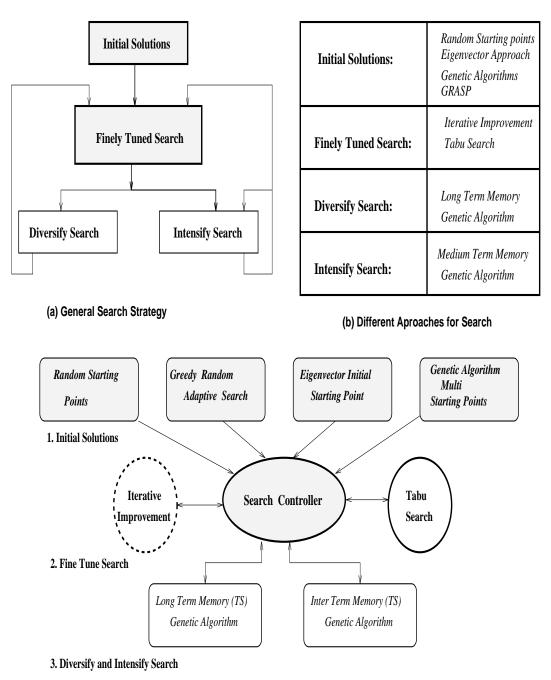

|   | 4.1                  | Hybri   | dization                                  | 87  |

|   |                      | 4.1.1   | Hybridization Strategy                    | 89  |

|   | 4.2                  | Effect  | ive Hybrid Schemes                        | 90  |

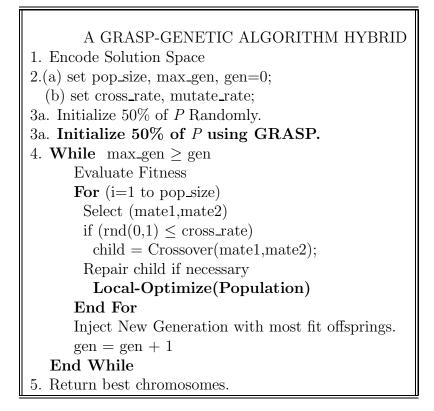

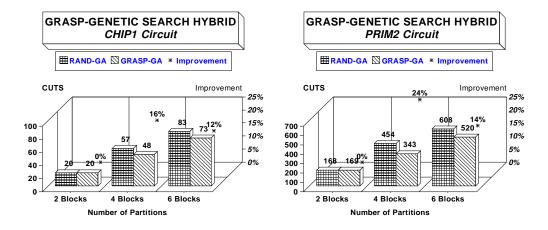

|   |                      | 4.2.1   | A Combined GRASP-Genetic Search Heuristic | 90  |

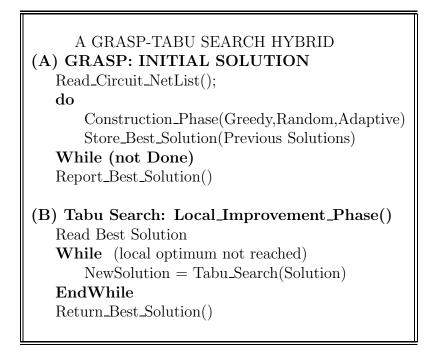

|   |                      | 4.2.2   | A Combined GRASP-Tabu Search Technique    | 95  |

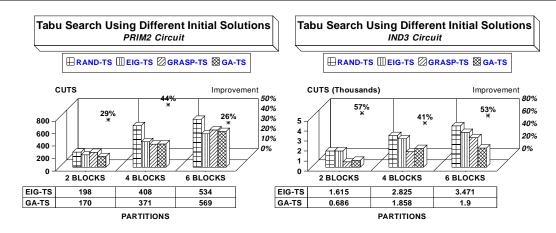

|   |                      | 4.2.3   | Computational Results                     | 95  |

|   | 4.3                  | A Me    | mory Based Annealing Heuristic            | 97  |

|   |                      | 4.3.1   | Simulated Annealing with Memory           | 98  |

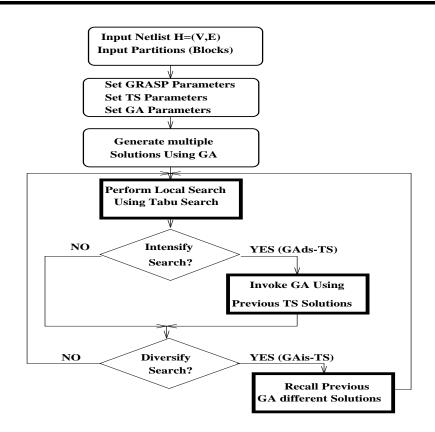

|   | 4.4                  | A Tab   | ou-Genetic Algorithm Approach             | 101 |

|   |                      | 4.4.1   | Search Controller                         | 102 |

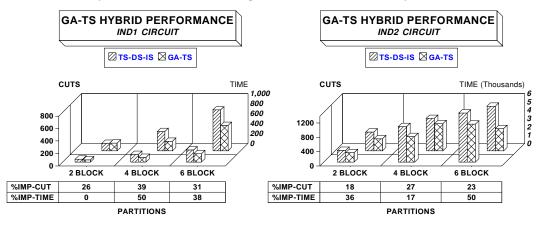

|   |                      | 4.4.2   | Computational Results                     | 106 |

|   | 4.5                  | Summ    | nary                                      | 108 |

| 5 | $\operatorname{Cir}$ | cuit C  | lustering                                 | 110 |

|   | 5.1                  | Motiv   | ration                                    | 112 |

|   |                      | 5.1.1   | Previous Algorithms                       | 114 |

|   | 5.2                  | A GR    | ASP Clustering Heuristic                  | 114 |

|   | 5.3                  | A Sta   | tistical Clustering Heuristic             | 119 |

|   |                      | 5.3.1   | Concepts and Terminology                  | 119 |

|   |                      | 5.3.2   | Statistical Information and Attributes    | 124 |

|   |                      | 5.3.3   | Cluster Size Thresholds                   | 124 |

|   |                      | 5.3.4   | Searching and Forming Clusters            | 125 |

|   |                      | 5.3.5   | Postprocessing                            | 126 |

|   | 5.4                  | Partit  | cioning Clustering Heuristics             | 127 |

|   |      | 5.4.1   | Clustered Single Processing Techniques      | 127 |

|---|------|---------|---------------------------------------------|-----|

|   |      | 5.4.2   | A Clustered Hybrid Technique                | 131 |

|   | 5.5  | Soluti  | on Optimality                               | 132 |

|   |      | 5.5.1   | Improving CPLEX MIP Performance             | 133 |

|   | 5.6  | Summ    | nary                                        | 139 |

| 6 | Dis  | tribute | ed Search Techniques                        | 141 |

|   | 6.1  | Motiv   | ation                                       | 142 |

|   |      | 6.1.1   | Multiprocessing Issues                      | 142 |

|   |      | 6.1.2   | Algorithm Development Strategy              | 143 |

|   | 6.2  | A Net   | work Multiprocessor Environment             | 145 |

|   |      | 6.2.1   | Main NMP Routines                           | 146 |

|   | 6.3  | Parall  | el Partitioning                             | 148 |

|   |      | 6.3.1   | A Simple Distributed Partitioning Heuristic | 148 |

|   |      | 6.3.2   | A Distributed Genetic Search Heuristic      | 150 |

|   |      | 6.3.3   | A Distributed Genetic-Tabu Search Heuristic | 153 |

|   | 6.4  | Summ    | nary                                        | 156 |

| 7 | Cire | cuit Pl | lacement                                    | 157 |

|   | 7.1  | Gener   | al Placement                                | 158 |

|   |      | 7.1.1   | Classification                              | 158 |

|   |      | 7.1.2   | Placement Cost Functions                    | 163 |

|   | 7.2  | Const   | ructive Phase                               | 167 |

|   |      | 7.2.1   | A Quadratic Cost Function                   | 167 |

|   |      | 7.2.2   | Generating a Legal Placement                | 169 |

|   | 7.3  | A Par   | titioning Placement Heuristic               | 170 |

|              | 7.4 | Iterative Improvement Phase               | 171 |

|--------------|-----|-------------------------------------------|-----|

|              |     | 7.4.1 A Tabu Method for Placement         | 173 |

|              |     | 7.4.2 The Objective Function              | 175 |

|              | 7.5 | Experimental Results                      | 179 |

|              | 7.6 | Summary                                   | 180 |

| 8            | Con | nplexity Analysis                         | 181 |

|              | 8.1 | Notations and Definitions                 | 182 |

|              |     | 8.1.1 Notation Used For Main Network      | 182 |

|              |     | 8.1.2 Notation Used For Clustered Network | 183 |

|              |     | 8.1.3 Definitions                         | 184 |

|              | 8.2 | Complexity Analysis of Tabu Search        | 188 |

|              | 8.3 | Complexity of Clustering Heuristics       | 194 |

|              |     | 8.3.1 GRASP Based Clustering              | 194 |

|              |     | 8.3.2 Statistical Based Clustering        | 197 |

|              | 8.4 | Summary                                   | 201 |

| 9            | Con | clusions and Future Directions            | 202 |

|              | 9.1 | Accomplishments                           | 203 |

|              | 9.2 | Summary                                   | 208 |

|              |     | 9.2.1 Clustered GA-TS Approach            | 209 |

|              | 9.3 | Future Work                               | 212 |

|              | 9.4 | Epilogue                                  | 214 |

| $\mathbf{A}$ | Dat | a Structures, and Algorithms              | 215 |

|              | A.1 | Complexity of Partitioning Heuristics     | 215 |

|   | A.2        | Definitions & Data Structures         | 215                                           |

|---|------------|---------------------------------------|-----------------------------------------------|

| в | NM         | P Routines                            | 218                                           |

|   | B.1        | Connection Based Routines             | 218                                           |

|   | B.2        | Identification Routines               | 218                                           |

|   | B.3        | Timing Routines                       | 219                                           |

|   | B.4        | Dynamic Reconfiguration of the System | 219                                           |

| С | Con        | nplete Tabulated Results              | 220                                           |

|   |            | 1                                     | 220                                           |

|   | C.1        | Results of Advanced Search Techniques | _                                             |

|   |            | -                                     | 221                                           |

|   |            | Results of Advanced Search Techniques | 221<br>231                                    |

|   | C.2<br>C.3 | Results of Advanced Search Techniques | <ul><li>221</li><li>231</li><li>236</li></ul> |

# List of Tables

| 1.1 | Example runtime of VLSI CAD tools on a SUN/4 workstation $\ . \ .$ . | 6   |

|-----|----------------------------------------------------------------------|-----|

| 3.1 | Benchmarks used as test cases                                        | 42  |

| 3.2 | Statistical information of benchmarks                                | 42  |

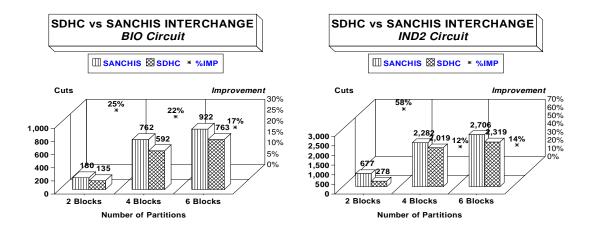

| 3.3 | A comparison between GRASP and Sanchis interchange heuristic .       | 53  |

| 3.4 | A comparison between constructive techniques                         | 65  |

| 3.5 | A comparison between different Tabu Search settings                  | 80  |

| 3.6 | The performance of Adaptive Tabu Search                              | 83  |

| 3.7 | 2-Way partitioning of advanced search heuristics                     | 85  |

| 4.1 | Comparison between different search methods                          | 90  |

| 4.2 | Results of GRASP-GA hybrid implementation                            | 94  |

| 4.3 | Effective hybrid search techniques                                   | 97  |

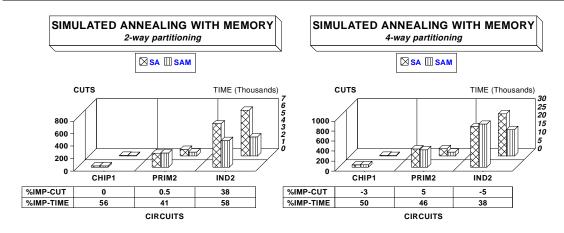

| 4.4 | The performance of Simulated Annealing with memory                   | 100 |

| 4.5 | 2-Way partitioning results of hybrid heuristics                      | 107 |

| 4.6 | 4-Way partitioning results of hybrid heuristics                      | 107 |

| 4.7 | 6-Way partitioning results of hybrid heuristics                      | 108 |

| 5.1 | <u> </u>                                                             | 113 |

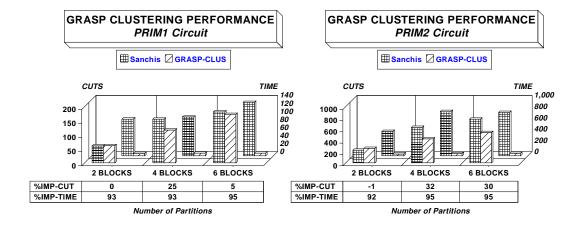

| 5.2 | Results using Sanchis interchange with GRASP clustering              | 118 |

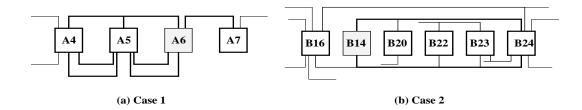

| 5.3  | Case1: preference values depending on $\Psi$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 123 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.4  | Case2: preference values depending on $\Psi$ $\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfi$ | 123 |

| 5.5  | A comparison between attraction functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 124 |

| 5.6  | Performance based on size threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 125 |

| 5.7  | Effect of seed on statistical clustering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 126 |

| 5.8  | The Sanchis interchange heuristic and statistical clustering $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 130 |

| 5.9  | Genetic Search based on statistical clustering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 130 |

| 5.10 | Tabu Search and statistical clustering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 130 |

| 5.11 | Performance of GA-TS hybrid with clustering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 132 |

| 5.12 | Optimal solutions for 2-way partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 134 |

| 5.13 | Optimal solutions for 4-way partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 134 |

| 5.14 | Heur-Stat heuristic used with CPLEX MIP solver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 138 |

| 6.1  | Sanchis interchange heuristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 151 |

| 6.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 154 |

| 6.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 156 |

| 0.0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100 |

| 7.1  | Placement results based on HPWL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 179 |

| 9.1  | 2-Way Partitioning: CPU TIME COMPARISON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 207 |

| 9.2  | 4-Way Partitioning: CPU TIME COMPARISON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 208 |

| 9.3  | 6-Way Partitioning: CPU TIME COMPARISON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 208 |

| A 1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 915 |

| A.1  | Computational complexity of circuit partitioning heuristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 215 |

| C.1  | 2 Way Partitioning SDHC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 221 |

| C.2  | 4 Way Partitioning SDHC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 221 |

| C.3  | 6 Way Partitioning SDHC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 222 |

| C.4 GRASP 2-Way partitioning                                                   |

|--------------------------------------------------------------------------------|

| C.5 GRASP 4-Way partitioning 223                                               |

| C.6 GRASP 6-Way partitioning 224                                               |

| C.7 Comparison of GA Techniques for 2 Way Partitioning 225                     |

| C.8 Comparison of GA Techniques for 4 Way Partitioning 225                     |

| C.9 Comparison of GA Techniques for 6 Way Partitioning 226                     |

| C.10 Constructive Methods for 2-Way Partitioning                               |

| C.11 Constructive Methods for 4-Way Partitioning                               |

| C.12 Constructive Methods for 6-Way Partitioning                               |

| C.13 2 Way Partitioning Results Using Adaptive Tabu Search $\ldots$ 229        |

| C.14 4 Way Partitioning Results Using Adaptive Tabu Search 229                 |

| C.15 6 Way Partitioning Results Using Adaptive Tabu Search $\ .\ .\ .\ .\ 230$ |

| C.16 Results of GRASP-GA hybrid implementation                                 |

| C.17 Effective hybrid search techniques                                        |

| C.18 2 Way Partitioning for SAM Hybrid Heuristic                               |

| C.19 4 Way Partitioning for SAM Hybrid Heuristic                               |

| C.20 6 Way Partitioning for SAM Hybrid Heuristic                               |

| C.21 2 way iterative improvement clustering results                            |

| C.22 4 way iterative improvement clustering results                            |

| C.23 6 way iterative improvement clustering results                            |

| C.24 2 way genetic clustering results                                          |

| C.25 4 way genetic clustering results                                          |

| C.26 6 way genetic clustering resulsts                                         |

| C.27 2 way Tabu Search clustering results                                      |

| C.28 4 way Tabu Search clustering results                                      |

| C.29 6 way Tabu Search clustering results | 241 |

|-------------------------------------------|-----|

| C.30 2-way Distributed Local Search       | 242 |

| C.31 4-way Distributed Local Search       | 242 |

| C.32 6-way Distributed Local Search       | 243 |

| C.33 2-way Distributed Genetic Search     | 244 |

| C.34 4-say Distributed Genetic Search     | 244 |

| C.35 6-way Distributed Genetic Search     | 245 |

# List of Figures

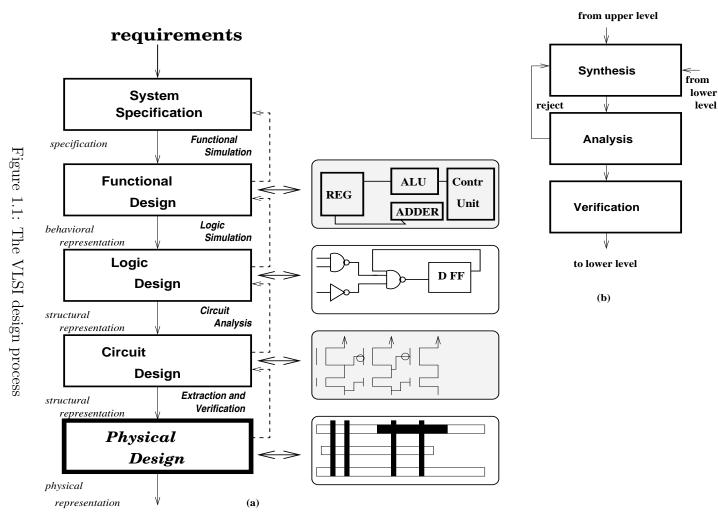

| 1.1  | The VLSI design process                                            | 3  |

|------|--------------------------------------------------------------------|----|

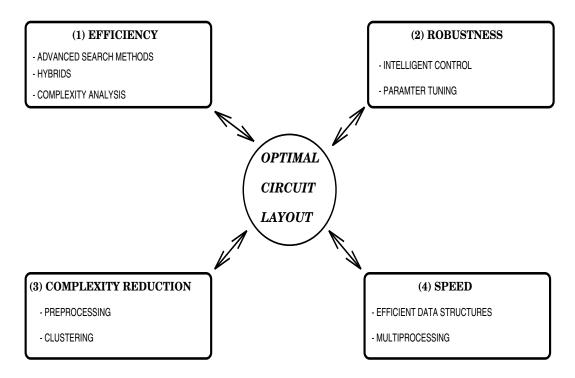

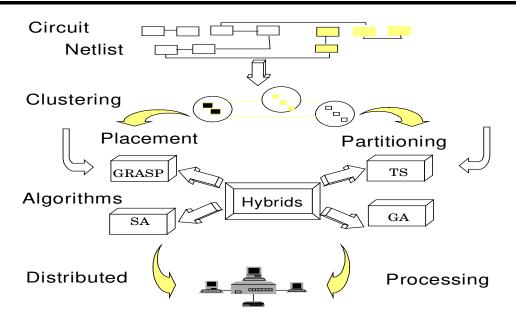

| 1.2  | Dissertation goals and strategy                                    | 9  |

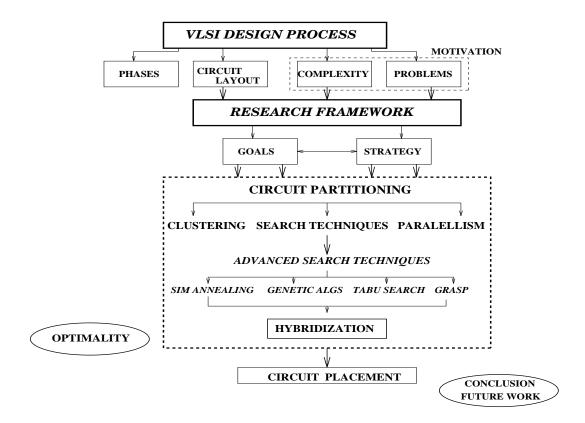

| 1.3  | Dissertation outline                                               | 15 |

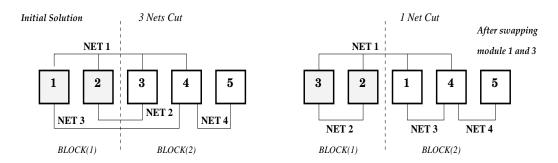

| 2.1  | Illustration of circuit partitioning                               | 18 |

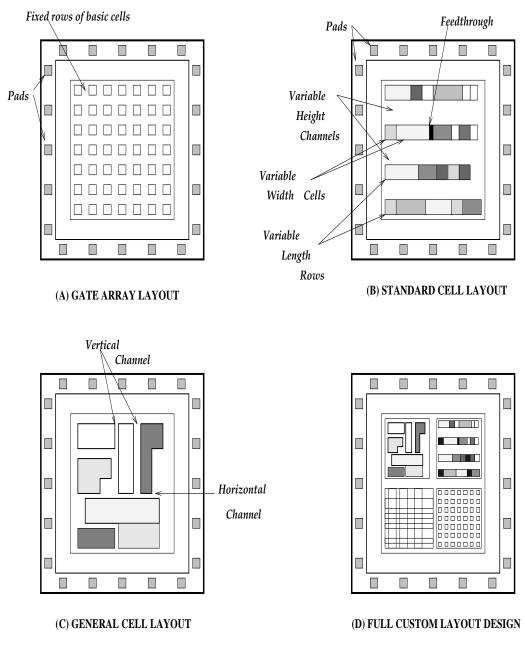

| 2.2  | Layout styles                                                      | 32 |

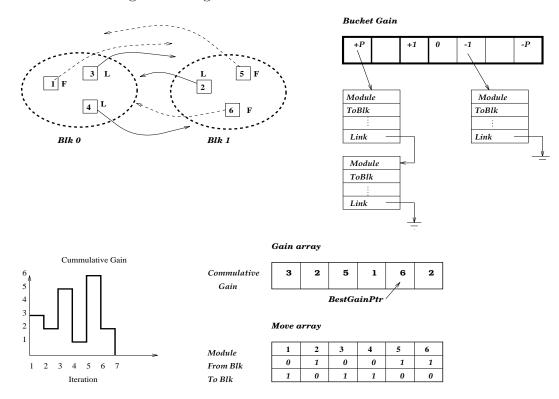

| 2.3  | Iterative improvement example based on node interchange $\ldots$ . | 35 |

| 2.4  | The Kernighan-Lin Algorithm                                        | 36 |

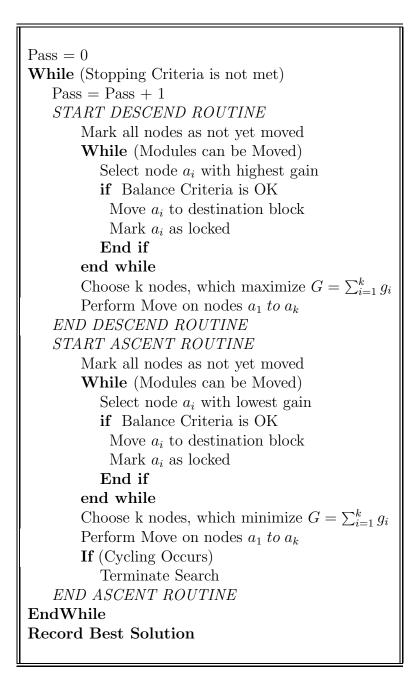

| 3.1  | A dynamic hill climbing heuristic (SDHC)                           | 45 |

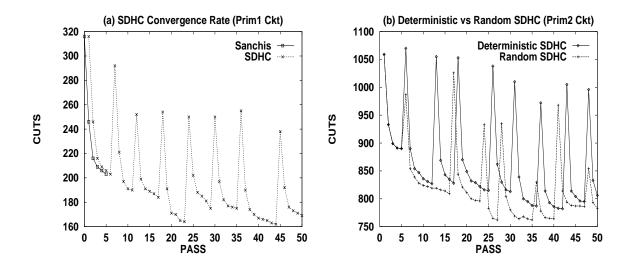

| 3.2  | The convergence of SDHC                                            | 46 |

| 3.3  | The performance of SDHC                                            | 46 |

| 3.4  | GRASP (Greedy Adaptive Search)                                     | 49 |

| 3.5  | Parameters affecting GRASP performance                             | 52 |

| 3.6  | Representation schemes and genetic operators                       | 57 |

| 3.7  | A generic Genetic Algorithm                                        | 61 |

| 3.8  | Parameters affecting GA performance                                | 63 |

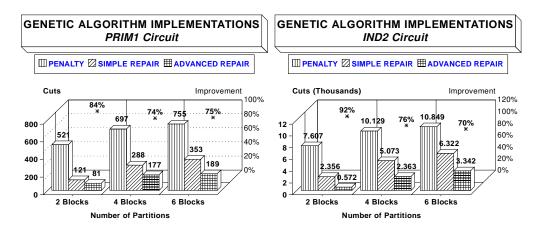

| 3.9  | The GA performance                                                 | 64 |

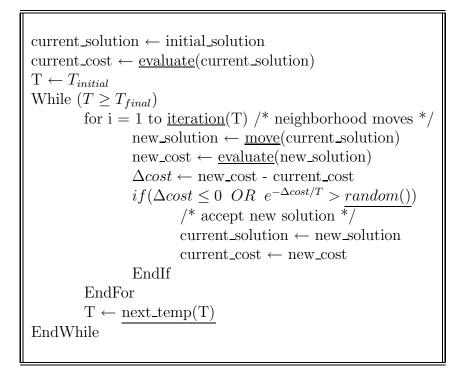

| 3.10 | A Simulated Annealing Algorithm                                    | 66 |

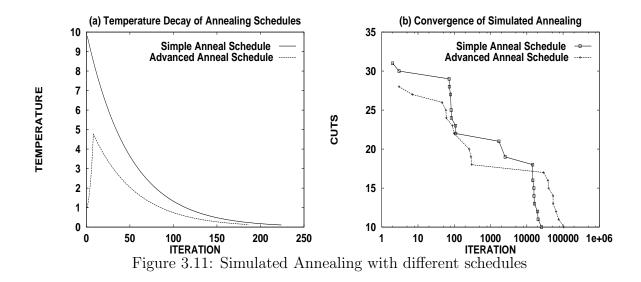

| 3.11 | Simulated Annealing with different schedules         |

|------|------------------------------------------------------|

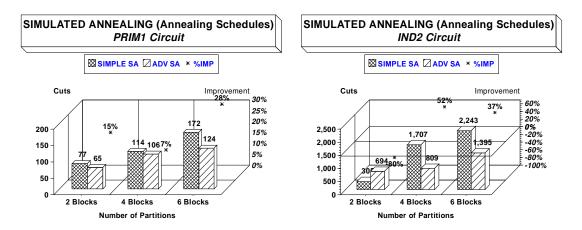

| 3.12 | A comparison between annealing schedules             |

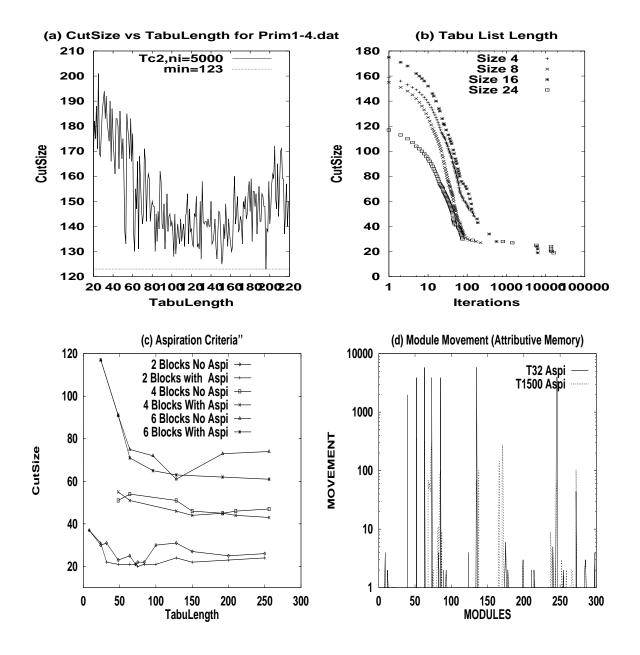

| 3.13 | Parameters affecting Tabu Search                     |

| 3.14 | A Simple Tabu Search implementation                  |

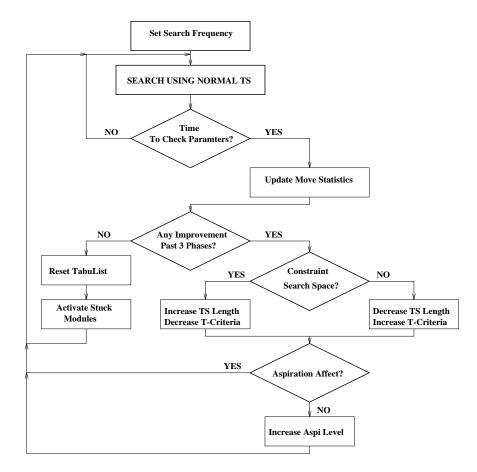

| 3.15 | Adaptive Tabu Search                                 |

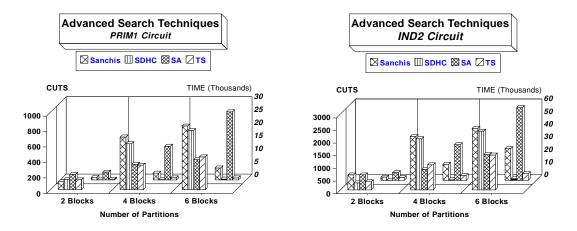

| 3.16 | Performance of advanced search heuristics            |

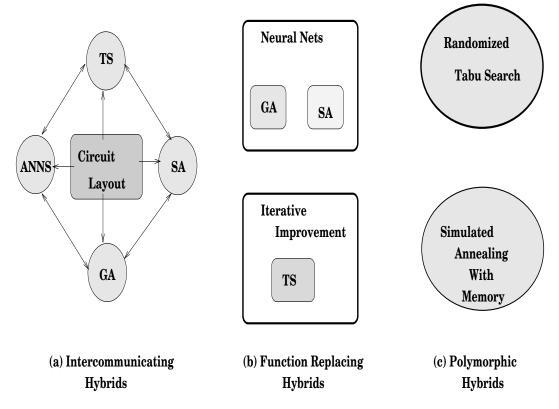

| 4.1  | Hybrid classes applied to combinatorial optimization |

| 4.2  | A GRASP-GA hybrid                                    |

| 4.3  | The performance of the GRASP-GA hybrid               |

| 4.4  | A GRASP-TS hybrid heuristic                          |

| 4.5  | Initial solutions and local search                   |

| 4.6  | Simulated Annealing with memory (SAM)                |

| 4.7  | The performance of SAM                               |

| 4.8  | Interaction between different search strategies      |

| 4.9  | A Tabu Search-Genetic Algorithm hybrid               |

| 4.10 | The performance of GA-TS hybrid                      |

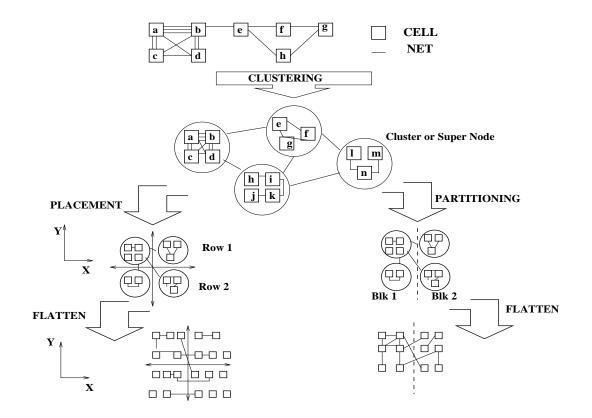

| 5.1  | Overview of clustering                               |

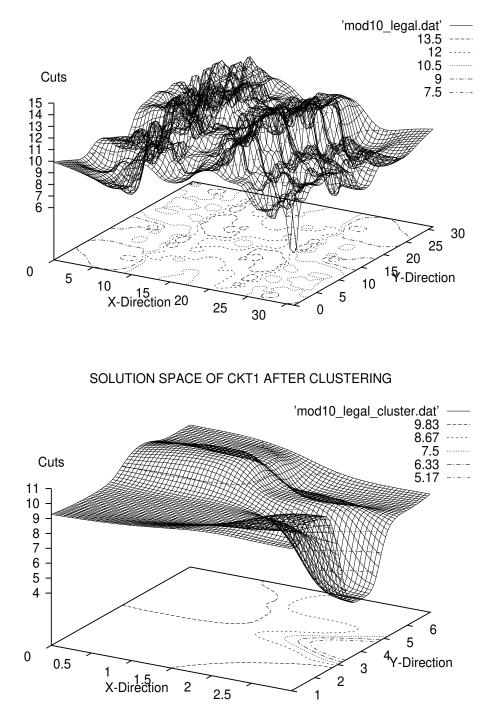

| 5.2  | 3D view of a clustered network 115                   |

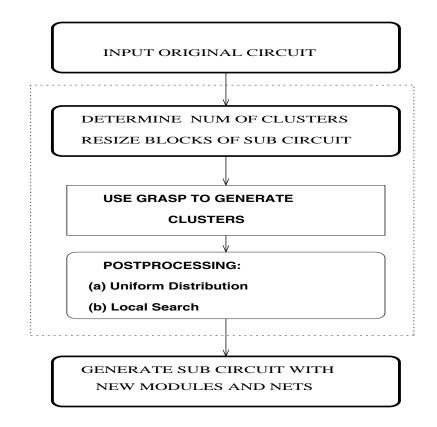

| 5.3  | A GRASP based clustering heuristic                   |

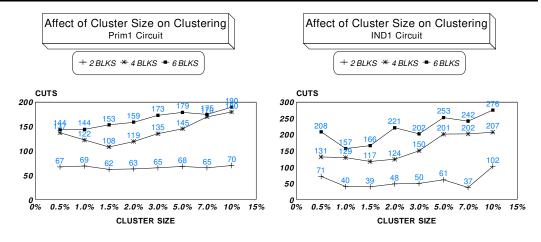

| 5.4  | Performance of clustering based on cluster size      |

| 5.5  | Performance of the GRASP clustering technique        |

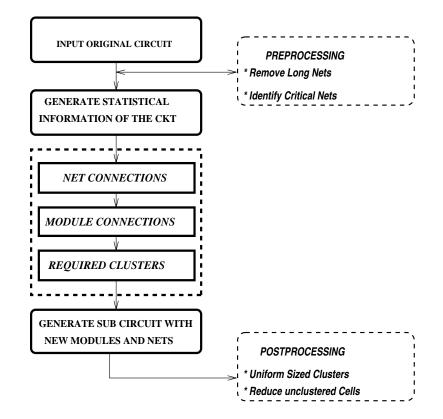

| 5.6  | A clustering heuristic based on attributes           |

| 5.7  | Attractive force between modules                     |

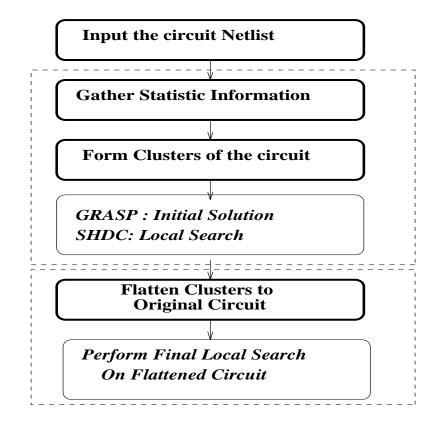

| 5.8  | A combined clustering-partitioning heuristic         |

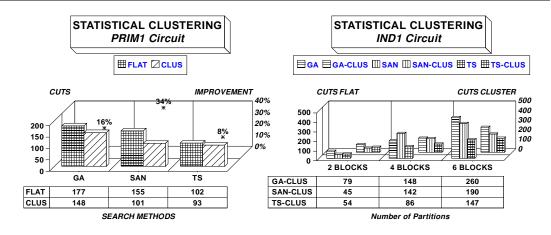

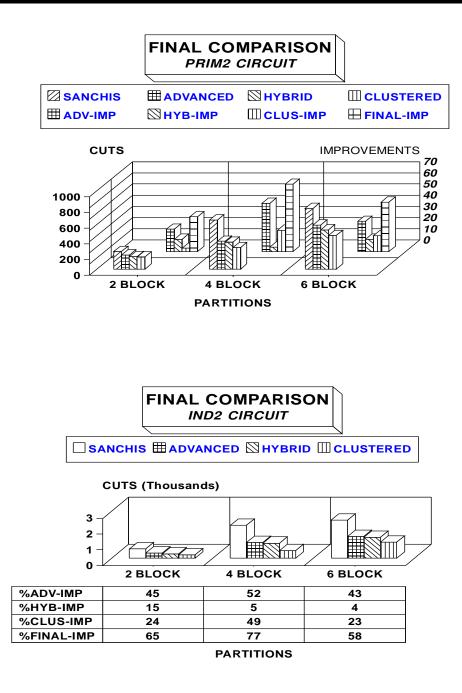

| 5.9  | Performance of the statistical clustering technique                    | 131 |

|------|------------------------------------------------------------------------|-----|

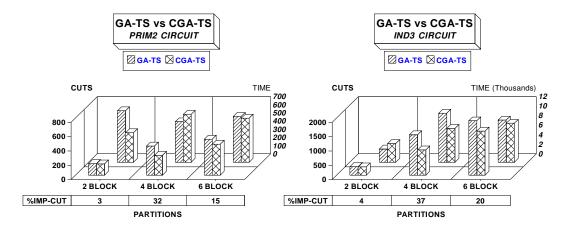

| 5.10 | Performance of the clustered GA-TS heuristic                           | 133 |

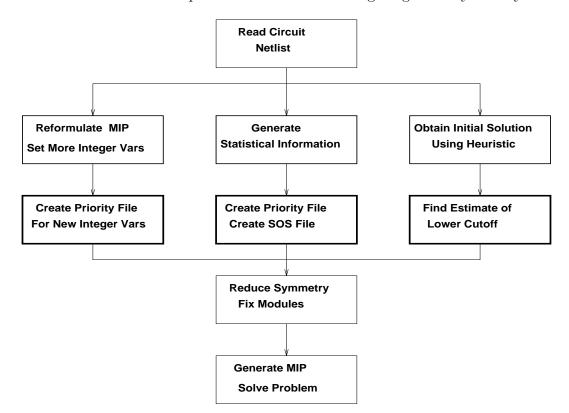

| 5.11 | Stat-Heur heuristic and CPLEX MIP                                      | 136 |

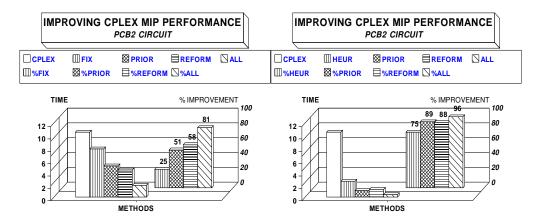

| 5.12 | Effect of Stat-Heur in improving the CPLEX MIP performance             | 139 |

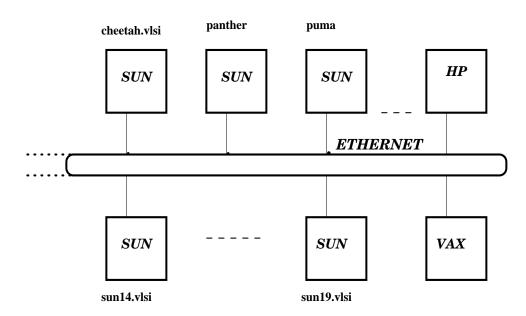

| 6.1  | Computing facilities                                                   | 146 |

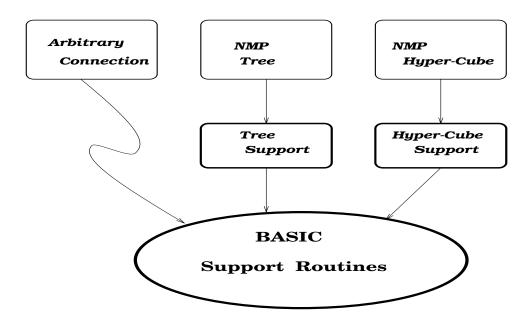

| 6.2  | NMP interconnection structure                                          | 147 |

| 6.3  | A distributed partitioning heuristic                                   | 149 |

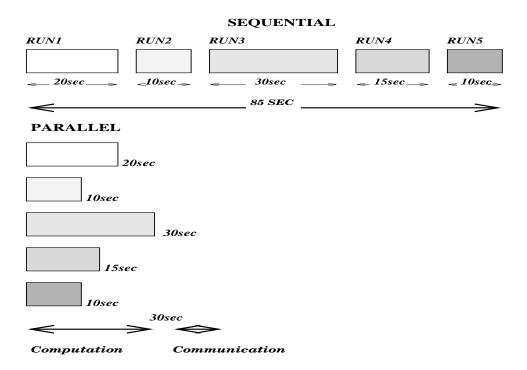

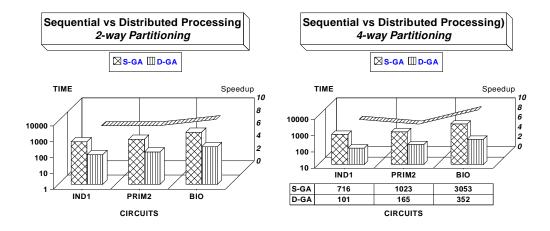

| 6.4  | Sequential vs parallel computation                                     | 151 |

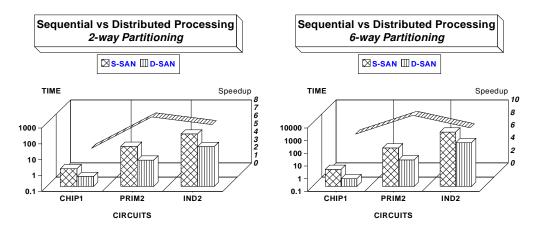

| 6.5  | The performance of Sanchis distributed heuristic                       | 152 |

| 6.6  | A distributed Genetic Algorithm                                        | 153 |

| 6.7  | The performance of a distributed GA heuristic                          | 154 |

| 6.8  | A distributed GA-TS heuristic                                          | 155 |

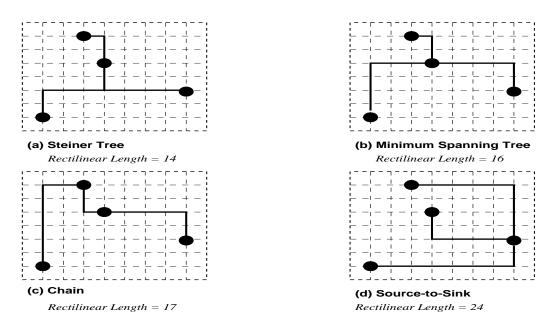

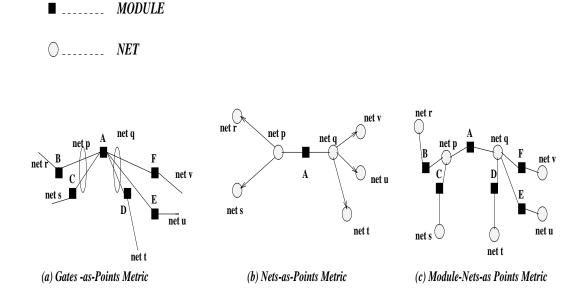

| 7.1  | Interconnection topologies                                             | 165 |

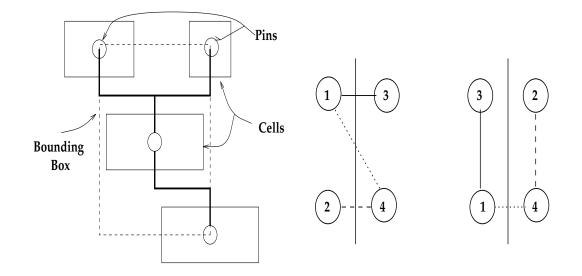

| 7.2  | Approximate wire estimation and congestion                             | 166 |

| 7.3  | Wire estimation for global placement                                   | 168 |

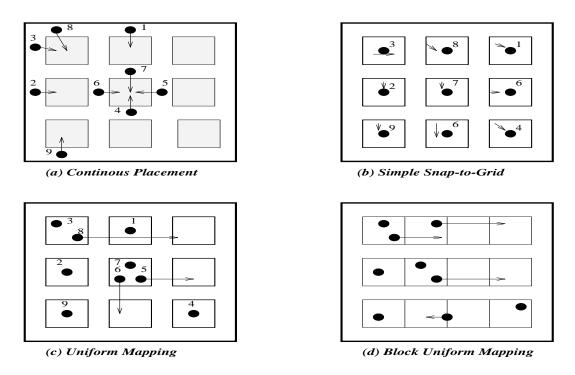

| 7.4  | The mapping to legal placement                                         | 170 |

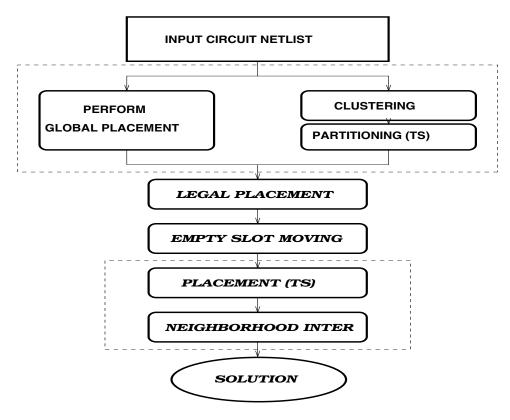

| 7.5  | The GPPSC heuristic                                                    | 172 |

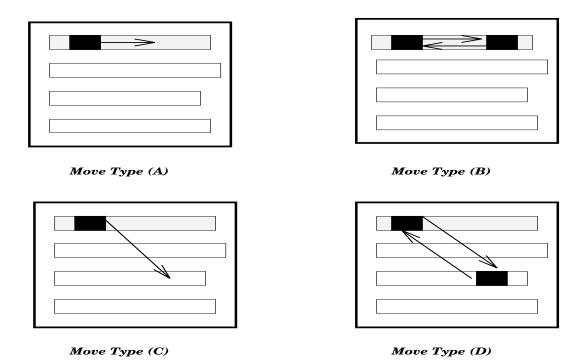

| 7.6  | Type of possible moves                                                 | 174 |

| 7.7  | A Tabu Search technique for circuit placement                          | 178 |

| 9.1  | Towards optimal solution of circuit layout                             | 204 |

| 9.2  | Effect of strategy on an intermediate and large size circuits $\ldots$ | 206 |

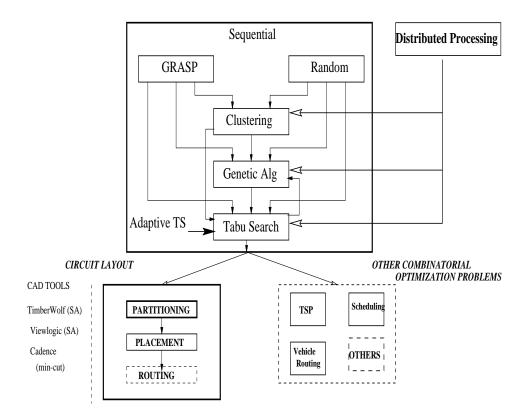

| 9.3  | CGA-TS: The Best Overall Search Heuristic                              | 210 |

## Chapter 1

## Introduction