# TOWARDS PRECISE NETWORK MEASUREMENTS

A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Ki Suh Lee January 2017 © 2017 Ki Suh Lee ALL RIGHTS RESERVED

# TOWARDS PRECISE NETWORK MEASUREMENTS

Ki Suh Lee, Ph.D.

Cornell University 2017

This dissertation investigates the question: How do we precisely access and control time in a network of computer systems? Time is fundamental for network measurements. It is fundamental in measuring one-way delay and round trip times, which are important for network research, monitoring, and applications. Further, measuring such metrics requires precise timestamps, control of time gaps between messages and synchronized clocks. However, as the speed of computer networks increase and processing delays of network devices decrease, it is challenging to perform network measurements precisely.

The key approach that this dissertation explores to controlling time and achieving precise network measurements is to use the physical layer of the network stack. It allows the exploitation of two observations: First, when two physical layers are connected via a cable, each physical layer always generates either data or special characters to maintain the link connectivity. Second, such continuous generation allows two physical layers to be synchronized for clock and bit recovery. As a result, the precision of timestamping can be improved by counting the number of special characters between messages in the physical layer. Further, the precision of pacing can be improved by controlling the number of special characters between messages in the physical layer. Moreover, the precision of synchronized clocks can be improved by running a protocol inside the physical layer by extending bit-level synchronization.

Subsequently, we make three contributions embodied in the design, imple-

mentation and evaluation of our approaches. First, we present how to improve the precision of timestamping and pacing via access to the physical layer at subnanosecond scale. SoNIC implements the physical layer in software and allows users to control and access every bit in the physical layer. Second, we demonstrate that precise timestamping and pacing can improve the performance of network applications with two examples: Covert timing channels and available bandwidth estimation. A covert timing channel, Chupja, is high-bandwidth and robust and can deliver hidden messages while avoiding detection. An available bandwidth estimation algorithm, MinProbe, can accurately estimate the available bandwidth in a high-speed network. Finally, we present how to improve the precision of synchronized clocks via access to the physical layer. DTP, Datacenter Time Protocol, extends the physical layer's link-level synchronization and implements a peer-to-peer clock synchronization protocol with bounded nanosecond precision. Together, these systems and approaches represent important steps towards precise network measurements.

#### **BIOGRAPHICAL SKETCH**

Ki Suh Lee earned his Bachelor of Science degree in Computer Science and Engineering from Seoul National University in Korea in 2007, and his Master of Science degree in Computer Science from Columbia University in 2009. Then, he joined the doctoral degree program in Computer Science in Cornell University, where he worked with Hakim Weatherspoon to build many systems using field-programmable gate array boards. His research interests broadly cover networking, operating systems, and computer architectures. To Kayoung, Ethan, and my parents.

#### ACKNOWLEDGEMENTS

I would like to thank the faculty members at Cornell. I would like to thank my advisor, Hakim Weatherspoon, who showed and taught me how to become a researcher in computer systems. He always guided me to build a system and at the same time not to forget the fundamental research questions that I was trying to answer by building the system. I would not forget the time we spent together to write papers till late nights. Kevin Tang showed me how to do research based on math and theory in computer networks. Further I am sincerely grateful to Fred Schneider and Nate Foster who gracefully accepted to be a member of my special committee and provided me invaluable advice to finish my dissertation.

I would also like to thank my research collaborators. What could I have done without Han Wang. From the earlier years of my study Han was always by my side and helped me in every aspect of my research. I thank Tudor who guided me to become a Linux kernel programmer in my earlier years. I thank Chiun Lin, Erluo Li and Vishal Shrivastav for their collaborations on many projects. I also thank many undergraduate students who helped my research: Ethan Kao, Jason Zhang, and Favian Contreras. I would also like to thank my colleagues in the Computer Science department at Cornell and members of Systems Lab and Networking Lab: Ji-Yong Shin, Zhiyuan Teo, Zhiming Shen, Qin Jia, Praveen Kumar, Robert Escriva, Hussam Abu-Libdeh, Dan Williams, Qi Huang, Joonsuk (Jon) Park, and Moontae Lee. I also thank Ed Kiefer and Eric Cronise from CIT who helped me set up network testbeds.

Outside the Systems Lab and Networking Lab, I had a pleasure to serve God in a praise team where I played acoustic / bass guitar, mixed the sounds, and served as a Bible study leader. I thank all members of the team and am especially grateful to Jayhun Lee and Hyunjung Kim for so many reasons. I would not forget enjoyable moments we had together as a team.

I cannot thank enough for my family for their support. I thank my lovely wife Kayoung who was at my side always and happily endured long seven years of life in Ithaca. Her endless love and support made me who I am now. Further I had a great joy of having a son, Ethan, during my study. He made me happy and laugh. I thank my parents for their endless support and prayer.

Thank God for everything.

|   | Dedie<br>Ackn<br>Table<br>List c | aphical Sketchiiicationivowledgementsvof Contentsviiof Tablesxof Figuresx              |

|---|----------------------------------|----------------------------------------------------------------------------------------|

| 1 |                                  | duction 1                                                                              |

|   |                                  | Background31.1.1Terminology31.1.2Example: Estimating Available Bandwidth4              |

|   |                                  | Challenges for Precisely Accessing Time                                                |

|   |                                  | 1.2.1   Lack of Precise Pacing   7                                                     |

|   |                                  | 1.2.2 Lack of Precise Timestamping                                                     |

|   |                                  | 1.2.3 Lack of Precise Clock Synchronization                                            |

|   |                                  | Contributions                                                                          |

|   | 1.4                              | Organization                                                                           |

| 2 | Scop                             | e and Methodology 15                                                                   |

|   | 2.1                              | Scope                                                                                  |

|   |                                  | 2.1.1         IEEE 802.3 standard                                                      |

|   |                                  | 2.1.2 Precise Timestamping and Pacing Need Access to PHY 20                            |

|   |                                  | 2.1.3 Precise Clock Synchronization Needs Access to PHY 23                             |

|   |                                  | Methodology: Experimental Environments                                                 |

|   |                                  | 2.2.1       Hardware                                                                   |

|   |                                  | 2.2.2         Network Topologies         32           Summary         37               |

|   | 2.0                              |                                                                                        |

| 3 |                                  | rds Precise Timestamping and Pacing: SoNIC 38                                          |

|   |                                  | Design $\dots$ |

|   |                                  | 3.1.1 Access to the PHY in software                                                    |

|   |                                  | 3.1.2Realtime Capability413.1.3Scalability and Efficiency43                            |

|   |                                  | 3.1.3Scalability and Efficiency433.1.4Precision44                                      |

|   |                                  | 3.1.5 User Interface                                                                   |

|   |                                  | 3.1.6 Discussion                                                                       |

|   |                                  | Implementation                                                                         |

|   |                                  | 3.2.1 Software Optimizations                                                           |

|   |                                  | 3.2.2 Hardware Optimizations                                                           |

|   |                                  | Evaluation                                                                             |

|   |                                  | 3.3.1 Packet Generator (Packet Pacing)                                                 |

|   |                                  | 3.3.2Packet Capturer (Packet Timestamping)60                                           |

# TABLE OF CONTENTS

|   |      | 3.3.3 Profiler                                | 52         |

|---|------|-----------------------------------------------|------------|

|   | 3.4  | Application 1: Covert Timing Channel          | 53         |

|   |      |                                               | 6          |

|   |      |                                               | '1         |

|   |      | 3.4.3 Summary                                 | <b>3</b> 9 |

|   | 3.5  | Application 2: Estimating Available Bandwidth | <b>9</b>   |

|   |      |                                               | 1          |

|   |      | 3.5.2 Evaluation                              | 2          |

|   |      | 3.5.3 Summary                                 | 95         |

|   | 3.6  | Summary                                       | 6          |

| 4 | Tow  | ards Precise Clock Synchronization: DTP 9     | 97         |

|   | 4.1  | Design                                        | 9          |

|   |      | 4.1.1 Assumptions                             | 9          |

|   |      | 4.1.2 Protocol                                |            |

|   |      | 4.1.3 Analysis                                | 15         |

|   | 4.2  | Implementation                                |            |

|   |      | 4.2.1 DTP-enabled PHY                         | 8          |

|   |      | 4.2.2 DTP-enabled network device              | 0          |

|   |      | 4.2.3 Protocol messages                       |            |

|   |      | 4.2.4 DTP Software Clock                      | 2          |

|   | 4.3  | Evaluation                                    |            |

|   |      | 4.3.1 Methodology                             | 5          |

|   |      | 4.3.2 Results                                 | 6          |

|   | 4.4  | Discussion                                    |            |

|   |      | 4.4.1 External Synchronization                |            |

|   |      | 4.4.2 Incremental Deployment                  |            |

|   |      | 4.4.3 Following The Fastest Clock             |            |

|   |      | 4.4.4 What about 1G, 40G or 100G?             |            |

|   | 4.5  | Summary                                       | .4         |

| 5 | Rela | ted Work 12                                   |            |

|   | 5.1  | Programmable Network Hardware                 |            |

|   | 5.2  | Hardware Timestamping                         |            |

|   | 5.3  | Software Defined Radio                        |            |

|   | 5.4  | Software Router                               |            |

|   | 5.5  | Clock Synchronization                         | .8         |

| 6 | Futu | re Work 13                                    | -          |

|   | 6.1  | Synchronous DTP                               |            |

|   | 6.2  | Packet Scheduler                              |            |

|   | 6.3  | SoNIC, DTP, and P4                            | 8          |

| 7 | Con  | clusion 14                                    | 0          |

| Α  | PHY Tutorial                                     | 142 |

|----|--------------------------------------------------|-----|

|    | A.1 Physical layer: Encoder and Scrambler        | 142 |

|    | A.1.1 Introduction                               | 142 |

|    | A.1.2 Encoding                                   | 143 |

|    | A.1.3 Scrambler                                  | 145 |

|    | A.1.4 Task                                       | 147 |

|    | A.2 Physical Layer: Decoder and Descrambler      | 148 |

|    | A.2.1 Introduction                               | 148 |

|    | A.2.2 Task                                       | 149 |

|    | A.3 Pseudo C code for 64/66b Encoder and Decoder | 151 |

| В  | Fast CRC algorithm                               | 157 |

|    | B.1 Psuedo assembly code for Fast CRC algorirthm | 158 |

| C  | Optimizing Scrambler                             | 162 |

| D  | Glossary of Terms                                | 165 |

| Bi | bliography                                       | 171 |

# LIST OF TABLES

| 2.1 | List of servers used for development and experiments                                            | 30  |

|-----|-------------------------------------------------------------------------------------------------|-----|

| 2.2 | List of FPGA boards and NICs used for development and exper-                                    |     |

|     | iments                                                                                          | 31  |

| 2.3 | List of evaluated network switches. "SF" is store-and-forward                                   |     |

|     | and "CT" is cut-through.                                                                        | 31  |

| 3.1 | DMA throughput. The numbers are average over eight runs.                                        |     |

|     | The delta in measurements was within 1% or less                                                 | 55  |

| 3.2 | IPD and IPG of homogeneous packet streams                                                       | 71  |

| 3.3 | Evaluated $\epsilon$ values in the number of /I/s and their correspond-                         |     |

|     | ing time values in nanosecond.                                                                  | 71  |

| 3.4 | $\epsilon$ and associated BER with (1518B, 1Gbps) $\ldots$ $\ldots$                             | 80  |

| 3.5 | Characteristics of CAIDA traces, and measured $I_{90}$ and BER                                  | 82  |

| 3.6 | $I_{90}$ values in nanosecond with cross traffic.                                               | 83  |

| 3.7 | Relation between $\epsilon$ , $I_{90}$ , and max $(I_{90}^+, I_{90}^-)$ over different networks |     |

|     | with (1518B, 1Gbps). Values are in nanosecond.                                                  | 84  |

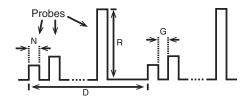

| 3.8 | Parameter setting for existing algorithms. G is the gap between                                 |     |

|     | packet trains. R is the rate of probe. N is the number of probe                                 |     |

|     | packets in each sub-train. D is the gap between each sub-train.                                 | 92  |

| 4.1 | Specifications of the PHY at different speeds                                                   | 123 |

|     |                                                                                                 |     |

| 5.1 | Comparison between NTP, PTP, GPS, and DTP                                                       | 128 |

# LIST OF FIGURES

| 1.1<br>1.2 | Collected interpacket delays between two servers                                                                             | 6<br>11  |

|------------|------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1<br>2.2 | IEEE 802.3 10 Gigabit Ethernet Network stack                                                                                 | 17<br>19 |

| 2.2        | Common approach to measure offset and RTT.                                                                                   | 19<br>24 |

| 2.3<br>2.4 | Clock domains of two peers. The same color represents the same                                                               | 24       |

| 2.5        | clock domain                                                                                                                 | 27<br>30 |

| 2.5        |                                                                                                                              | 33       |

| 2.0<br>2.7 | Simple evaluation setup                                                                                                      | 55       |

| 2.1        | dotted lines are 1G connections.                                                                                             | 34       |

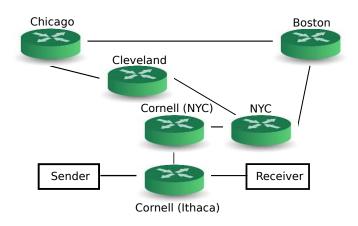

| 2.8        | Our path on the National Lambda Rail                                                                                         | 35       |

| 2.0<br>2.9 | Evaluation Setup for DTP                                                                                                     | 36       |

| 2.)        |                                                                                                                              | 50       |

| 3.1        | Example usages of SoNIC                                                                                                      | 43       |

| 3.2        | Example C code of SoNIC Packet Generator and Capturer                                                                        | 45       |

| 3.3        | SoNIC architecture                                                                                                           | 47       |

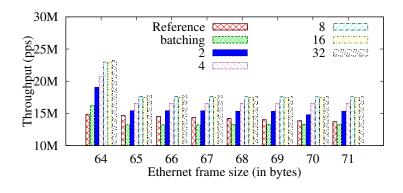

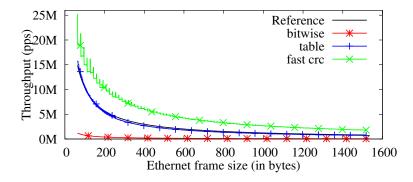

| 3.4        | Throughput of packing                                                                                                        | 51       |

| 3.5        | Throughput of different CRC algorithms                                                                                       | 51       |

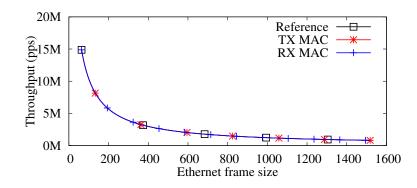

| 3.6        | Throughput of packet generator and capturer                                                                                  | 57       |

| 3.7        | Comparison of packet generation at 9 Gbps                                                                                    | 58       |

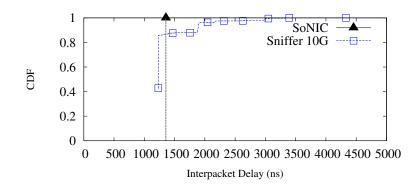

| 3.8        | Comparison of timestamping                                                                                                   | 60       |

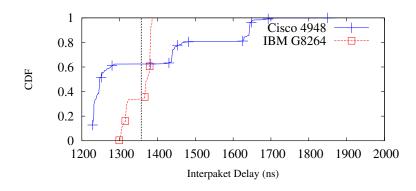

| 3.9        | IPDs of Cisco 4948 and IBM G8264. 1518B packets at 9 Gbps                                                                    | 61       |

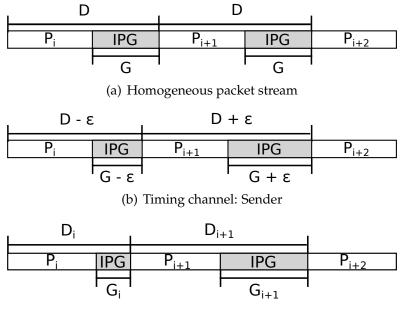

| 3.10       | Chupja encoding and decoding.                                                                                                | 68       |

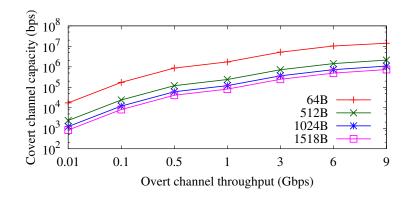

| 3.11       | Maximum capacity of PHY timing channel                                                                                       | 69       |

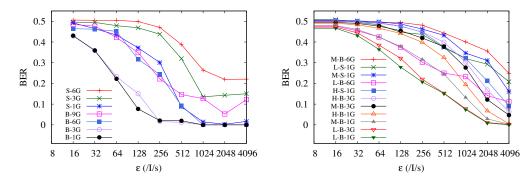

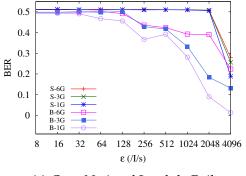

| 3.12       | BER of Chupja over a small network and NLR. X-Y-Z means that workload of cross traffic is X (H-heavy, M-medium, or L-light), |          |

|            | and the size of packet and data rate of overt channel is Y (B-                                                               |          |

|            | big=1518B or S-small=64B) and Z (1, 3, or 6G)                                                                                | 73       |

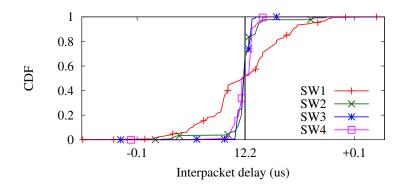

| 3.13       | Comparison of IPDs after switches process a homogeneous                                                                      |          |

|            | packet stream (1518B, 1Gbps)                                                                                                 | 76       |

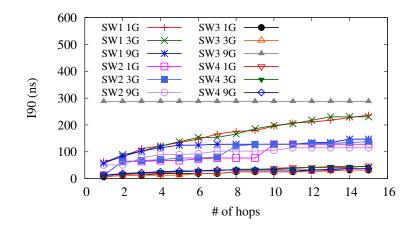

| 3.14       | $I_{90}$ comparison between various switches                                                                                 | 77       |

| 3.15       | Comparison of homogeneous streams and covert channel                                                                         |          |

|            | streams of (1518B, 1Gbps)                                                                                                    | 78       |

| 3.16       | BER over multiple hops of SW1 with various $\epsilon$ values with (1518B, 1Gbps)                                             | 81       |

| 3.17       | Packet size distributions of CAIDA traces                                                                                    | 81       |

| 3.18       | Comparison of various timestamping methods. Each line is a                                                                   |          |

|            | covert channel stream of (1518B, 1Gbps) with a different $\epsilon$ value.                                                   | 85       |

| 3.19       | Kernel timestamping with (1518B, 1Gbps).                                                                                     | 87       |

| 3.20       | Hardware timestamping with (64B, 1Gbps)                                                                                      | 88       |

| 3.21 | Generalized probe train model                                    | 91  |

|------|------------------------------------------------------------------|-----|

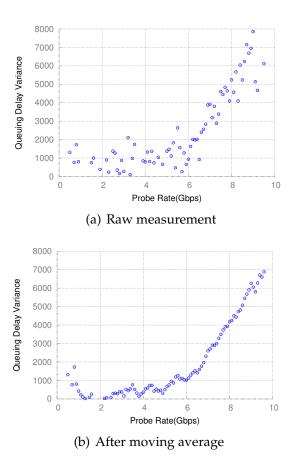

| 3.22 | Bandwidth estimation of CAIDA trace, the figure on the top is    |     |

|      | the raw data trace, the figure on the bottom is the moving aver- |     |

|      | age data                                                         | 93  |

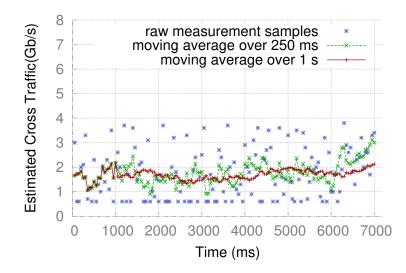

| 3.23 | Measurement result in NLR                                        | 94  |

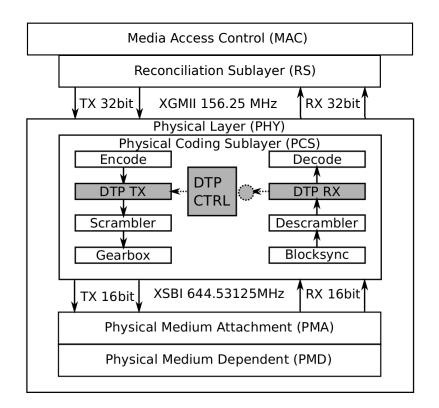

| 4.1  | Low layers of a 10 GbE network stack. Grayed rectangles are      |     |

|      | DTP sublayers, and the circle represents a synchronization FIFO. | 109 |

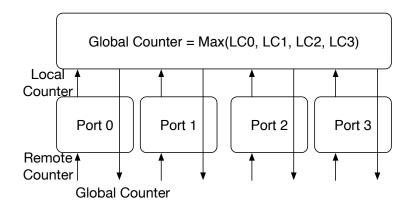

| 4.2  | DTP enabled four-port device.                                    | 110 |

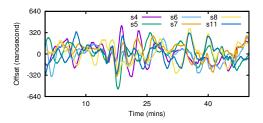

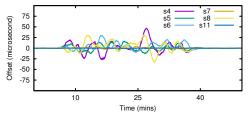

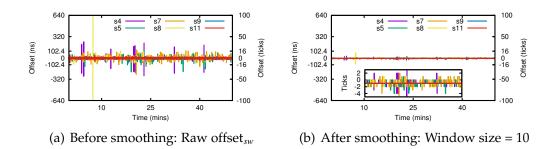

| 4.3  | Precision of DTP and PTP. A <i>tick</i> is 6.4 nanoseconds       | 117 |

| 4.4  | Precision of DTP daemon.                                         | 118 |

| A.1  | 10G Network Stack                                                | 143 |

| A.2  | 66b block format                                                 |     |

| A.3  | Example                                                          | 145 |

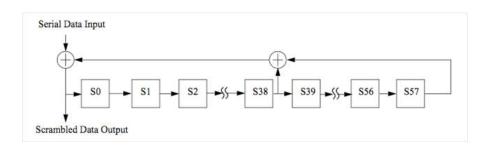

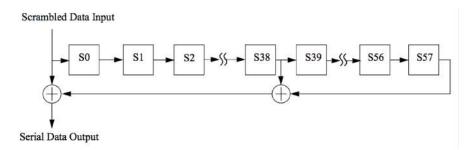

| A.4  | Scrambler                                                        |     |

| A.5  | Descrambler                                                      | 149 |

# CHAPTER 1

#### INTRODUCTION

Time is "a finite extent or stretch of continued existence, as the interval separating two successive events or actions, or the period during which an action, condition, or state continues" [35]. In other words, we use the term, *time*, to specify the moment or duration of a particular event. We also use time to serialize the ordering of events. Time is inseparable from our daily lives and has been an interesting research topic in many different areas including physics and philosophy. For example, in physics, Einstein defined *time* as what a *clock* at a particular location *reads* to explore the concept of relativity [56]. When one wants to compare the time of two events from two different locations, the clocks from two locations must be *synchronized* to provide a common time. There are many commonly used *standard times* including Coordinated Universal Time (UTC).

In computer systems, *system time* is used to specify a moment of creation, update, or removal of an object, to measure the duration of an event, and to order a series of events. System time is measured by a *system clock*, which normally keeps track of the number of seconds since the Epoch (00:00:00 UTC, January 1, 1970) [33]. The synchronization between a system clock and the reference time (UTC) can be achieved via a time protocol such as Network Time Protocol (NTP) [98] or Precise Time Protocol (PTP) [18]. The time difference between a system clock and a reference time can vary from tens of nanoseconds to any number of seconds.

Time is also essential for many network applications and network management. For example, many network applications use *timestamps* of messages, i.e. marking the time at which the message is sent or received. A timestamp can be generated by *reading* the system clock or the hardware clock of the network interface card (NIC) that sends or receives the particular message. Then, a process can measure a round trip time (RTT) to another process in a network by comparing two timestamps: One is generated before sending a request message and the other is generated upon receiving a response message. Similarly, a process can measure a one-way delay (OWD) to another process by sending a probe message with its current time. Then, the receiving process can compute the OWD by subtracting the received time from its own time. Note that measuring OWD requires the clocks of two processes to be synchronized.

In this dissertation, we focus on three fundamental research problems that are important for network measurements with respect to time: Timestamping messages, controlling timing of messages (*pacing*), and clock synchronization. Precisely timestamping and pacing messages and synchronizing clocks in a network is challenging, especially as the speed of the network continues to increase while at the same time processing delay of network devices continues to decrease over time. For instance, a packet can arrive every 64 nanoseconds in 10 Gigabit Ethernet (GbE), and even more frequently in faster networks such as in 40 or 100 GbE. On the other hand, it takes nearly a microsecond for a network switch to process a message. As a result, it is necessary to have a capability of timestamping and pacing messages at nanosecond scale and to synchronize clocks at similar granularity. Therefore, we seek to investigate the following research question in this dissertation: *How do we precisely access and control time in a network of computer systems*?

In the course of exploring the above research question, we devised an augmented physical layer of the network protocol stack that provides timing information for network measurements. The augmented physical layer allows users to control and access every single bit over the medium for precise timestamping and pacing. Further, the augmented physical layers in a network provide tightly synchronized clocks with bounded precision. In this dissertation, we investigate how the physical layer can provide precise time and how it improves the performance of network applications.

### 1.1 Background

# 1.1.1 Terminology

A *clock c* of a process  $p^1$  is a function that returns a local clock counter given a real time *t*, i.e.  $c_p(t) = \text{local clock counter}$ . Note that a clock is a discrete function that returns an integer, which we call clock *counter* throughout the dissertation. A clock changes its counter at every clock *cycle* (or *tick*). If clocks  $c_i$  for all *i* are synchronized, they will satisfy

$$\forall i, j, t \ |c_i(t) - c_j(t)| \le \epsilon \tag{1.1}$$

where  $\epsilon$  is the level of *precision* to which clocks are synchronized [116].

Each clock is usually driven by a quartz oscillator, which oscillates at a given frequency. *Oscillators* with the same nominal frequency may run at different rates due to frequency variations caused by external factors such as temperature. As a result, clocks that have been previously synchronized will have clock counters that differ more and more as time progresses. The difference

<sup>&</sup>lt;sup>1</sup>We will use the term *process* to denote not only a program that is being executed on a processor but also a program running inside a network interface card.

between two clock counters is called the *offset* or *skew*, which tends to increase over time, if not resynchronized. Therefore, clock synchronization protocols periodically adjust offsets between clocks (offset synchronization) and/or frequencies of clocks (frequency synchronization) so that they remain close to each other [116].

If a process attempts to synchronize its clock to true time by accessing an external clock source such as an atomic clock or a satellite, it is called *exter-nal synchronization*. If a process attempts to synchronize with another (peer) process with or without regard to true time, it is called *internal synchronization*. Thus, externally synchronized clocks are also internally synchronized, but not vice versa [50]. In many cases, monotonically increasing and internally synchronized clocks are sufficient. For example, measuring one-way delay and processing time or ordering global events do not need true time.

## **1.1.2** Example: Estimating Available Bandwidth

In order to illustrate the challenges of precisely accessing and controlling time, we will use an example of estimating available bandwidth, the maximum data rate that a process can send to another process without going over the network capacity between the two. Many algorithms for estimating available bandwidth use OWD [68, 111, 120].

Suppose a process p wants to estimate available bandwidth between itself and a process q. The process p uses a train of probe messages  $(m_1, \dots, m_n)$  to estimate available bandwidth. The process p controls the time gap between messages to be a pre-computed interval: Let  $d_i^p$  be the time gap between  $m_i$  and  $m_{i+1}$ . Each message  $m_i$  carries the timestamp  $t_i^p$  which is the time when the message was sent by p. The process q then timestamps incoming messages  $(t_i^q)$  and computes OWD of each message  $(=t_i^q - t_i^p)$ . Available bandwidth estimation algorithms then examine and detect any changes in measured OWDs, which are good indicators of buffering, queuing or congestion in the network. Then the algorithms infer the available bandwidth.

There are a few potential places which can contribute to inaccuracy in the estimated available bandwidth. Accuracy means the closeness of an estimated bandwidth to an actual bandwidth available. First, the timestamp  $t_i^p$  of the probe messages could be imprecise mainly due to the time gap between the moment p timestamps a message<sup>2</sup> and the moment the message is transmitted over the wire. The timestamp of a message is *precise* when the timestamp is close to the actual time when the message was sent or received by hardware. Similarly the timestamp  $t_i^q$  could also be imprecise. Second, the time gap  $d_i^p$  might not be the actual time gap between  $m_i$  and  $m_{i+1}$ . The sender normally controls the time gap by sleeping for  $d_i^p$  seconds after sending  $m_i$ . However, sleeping, waking up and sending a message can introduce random delays, and thus can make the actual gap  $d_i^{\prime p}$  to be larger than  $d_i^{p}$ . Pacing, or controlling time gap, is *precise* when an intended time gap between two packets  $d_i^p$  is close to the actual gap  $d_i'^p$  between them after they are transmitted by hardware. Lastly, there is an uncertainty in the degree of synchronization of the clocks of *p* and *q*, which could vary from nanoseconds to any number of seconds. We explore each contributor in the following section.

Note that OWD is often estimated to be RTT / 2 as synchronizing clocks is

<sup>&</sup>lt;sup>2</sup>We will assume that reading a clock and embedding time to a message can happen almost at the same time or with very small time gap for simplicity.

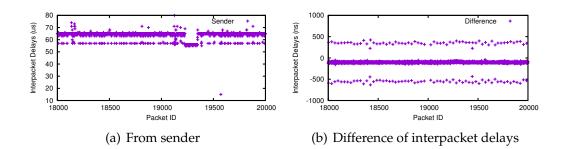

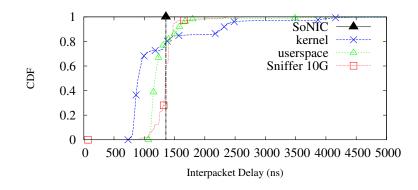

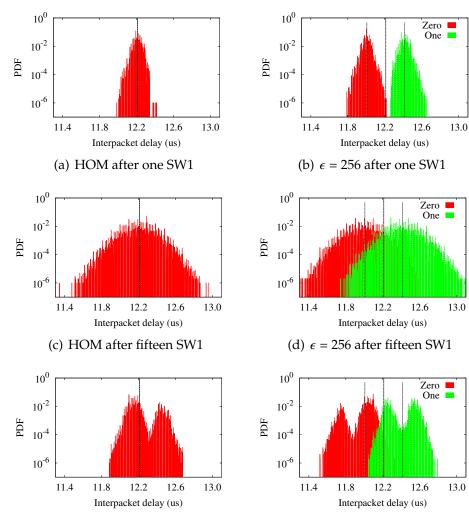

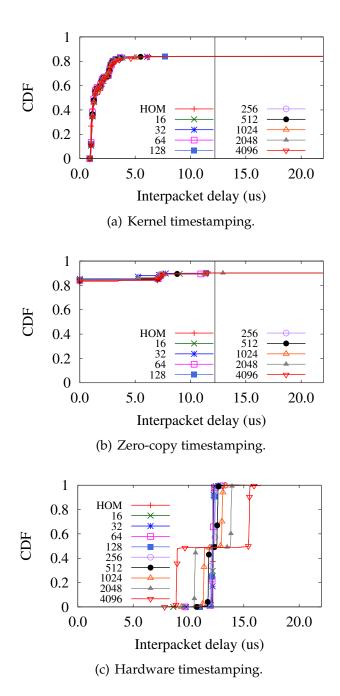

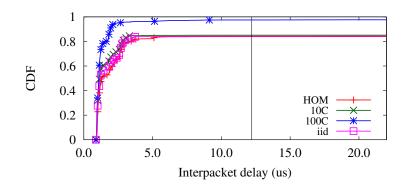

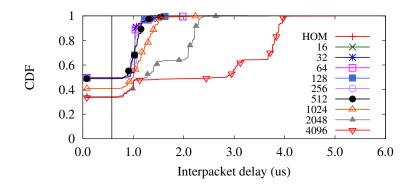

Figure 1.1: Collected interpacket delays between two servers.

a difficult problem. However, such estimation is prone to errors mainly due to path asymmetry: The path that a request message takes might be different from the path that a response message takes and the time that a request message takes might also be different from the time that a response message takes.

Also note that time gaps between messages could be very small when the rate of probe messages is high. For example, time gaps of probe messages at 9 Gigabits per second (Gbps) are smaller than 1.5 microsecond in 10 Gigabit networks. As a result, accurate available bandwidth estimation requires at least microsecond level of precision of pacing and timestamping messages and synchronized clocks in a 10 Gigabit network. Without fine-grained control of time gaps and precise timestamping, the accuracy of available bandwidth estimation algorithms could dramatically decrease [125].

## 1.2 Challenges for Precisely Accessing Time

# **1.2.1** Lack of Precise Pacing

Pacing messages is to insert arbitrary delays between messages, i.e. pacing controls time gap between packets. Pacing is often used to improve the performance of network protocols [126, 135]. There are mainly three places where time gaps can be controlled: Userspace, Kernel-space, and hardware (NIC). Userspace applications can control the time gap between two packets by waiting or sleeping for a certain amount of time after sending the first packet. However, controlling the time gap with fine granularity at microseconds or nanoseconds scale is challenging because the scheduler of the system can introduce random delays into the time gap when the process waits or sleeps. In kernel space, controlling time gaps at microsecond granularity is possible with a high-resolution timer [121]. Pacing in kernel space is often limited to support transport protocols [121, 110], and other network applications not implemented in the kernel cannot normally use the high-resolution timer to control time gaps. Commodity network interface cards normally do not provide an interface for controlling time gaps, and hardware that supports pacing only supports Transmission Control Protocol [129].

In order to demonstrate how hard it is to precisely pace messages, we conducted a simple experiment. We used two servers each with a NIC with hardware timestamping (Discussed below in Section 1.2.2) capability on both transmit and receive paths. The NICs were identical and directly connected via a three-meter cable. The sender periodically sent a message and waited for one microsecond before sending the next. The sender recorded timestamps of outgoing messages reported by the hardware. Then, we computed time gaps between two successive messages and plotted them in Figure 1.1(a). Figure 1.1(a) shows that the actual time gap between messages is around 65 microseconds which is much larger than the intended time gap, one microsecond. This simple experiment demonstrates the challenge of precisely controlling time gaps. As a result, we investigate the following research question in this thesis: *What is required to precisely pace messages*?

In this dissertation, we explore an alternative way of packet pacing. Instead of waiting / sleeping, or relying on a high-resolution timer, we attempt to directly control the number of bits between messages in the physical layer. We mainly exploit the fact that Ethernet uses one bit per *symbol* over the medium for data communication. For example, it takes about 100 picoseconds to deliver one symbol over the wire in 10 Gigabit Ethernet (GbE). As a result, controlling bits in the physical layer allows precise pacing on the transmit path, which is not readily available in commodity NICs. We present SoNIC in Chapter 3 which achieves the precise pacing by implementing the physical layer of a network stack in software.

#### **1.2.2** Lack of Precise Timestamping

Messages can also be timestamped at three places: Kernel-space, userspace, and hardware. On the receive (RX) path, kernel records arrival times of packets upon receiving them from hardware. Since so many factors are involved during the delivery of a packet to kernel space, such as DMA transaction, interrupt routines, and scheduler, kernel timestamping can be imprecise in a high-speed network. As a result, userspace timestamping will also be imprecise because of delays added due to interaction between kernel and userspace.

Modern commodity NICs provide *hardware timestamping*. A NIC uses an additional quartz oscillator inside the hardware to timestamp incoming and outgoing packets at a very early (late) stage for the receive (transmit) path to achieve better precision normally between the Media Access Control (MAC) layer and the physical layer. The oscillator can be synchronized to an external clock or be free-running. As a result, the precision of timestamping can be significantly improved.

Unfortunately, hardware timestamping is still not precise. With the same experiment setup discussed in Section 1.2.1, we also captured timestamps of messages from the receiver and computed interpacket delays. Then, we compared computed delays from the sender and the receiver. Figure 1.1(b) illustrates the difference between corresponding interpacket delays in nanoseconds. As there is nothing in the middle between two identical NICs except a cable, we would expect that corresponding interpacket delays from the sender and the receiver would match or close to each other assuming that timestamps are precise. However, Figure 1.1(b) shows that the interpacket delays from the sender and the receiver could differ by four or five hundred nanoseconds for the most of time and at worst case could differ by ten microseconds (which is not shown in the graph).

Therefore, we investigate the following research question: *What is required to improve the precision of timestamping?*

In this dissertation, we explore an alternative way of hardware timestamp-

ing. Instead of timestamping messages between the Media Access Control (MAC) layer and the physical layer (PHY), we attempt to timestamp messages inside the PHY. In particular, rather than using an extra clock to timestamp messages outside the physical layer, we use the clock that generates bits over the wire for timestamping. By doing so, we can use the number of bits between any two messages inside the physical layer as a base for precise timestamping. As noted in Section 1.2.1, it takes about 100 picoseconds to deliver one symbol over the wire in 10 GbE. As a result, the precision of timestamping can significantly improve. We discuss in Chapter 3 how SoNIC which implements the physical layer in software can also improve the precision of timestamping.

## **1.2.3** Lack of Precise Clock Synchronization

Synchronizing clocks is a challenging problem. It is challenging due to the problem of measuring round trip times (RTT) accurately. RTT is used by many clock synchronization protocols to compute clock *offset* (*skew*), the time difference between two system clocks. RTTs are prone to variation due to characteristics of packet switching networks: Network jitter, packet buffering and scheduling, asymmetric paths, and network stack overhead. As a result, any protocol that relies on RTTs must carefully handle measurement errors.

There are many time synchronization protocols that provide different levels of precision including NTP [98] and PTP [18]. NTP normally provides millisecond to microsecond precision in a Local Area Network (LAN), and PTP provides microsecond to tens of nanosecond precision in a LAN when properly configured. PTP employs many techniques to remove uncertainties in mea-

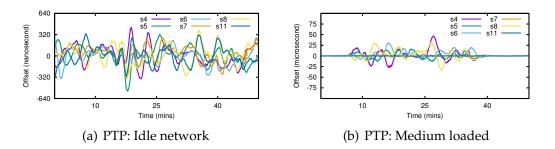

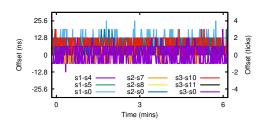

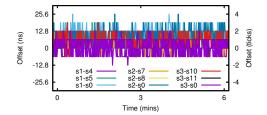

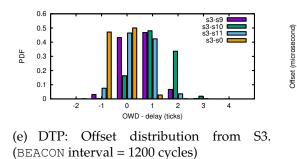

Figure 1.2: PTP precision

sured RTTs. For example, hardware timestamping is commonly used and PTPenabled switches are deployed to minimize network jitter.

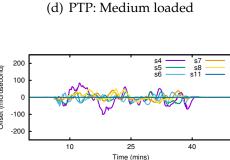

Nonetheless, it is not possible to completely remove the network jitter and non-deterministic delays. Figure 1.2 illustrates the problem. Figure 1.2(a) shows the performance of PTP when the network is idle, and Figure 1.2(b) shows the performance of PTP when the network is loaded with network traffic. The detailed test environment is described in Section 2.2. The takeaway is that the performance of PTP can be as good as hundreds of nanoseconds, and can degrade to tens of microseconds depending on network conditions. Therefore, we investigate the following research question: *How can we minimize non-deterministic delays from the network to improve the precision of time synchronization protocols?*

In this dissertation, we developed a new time synchronization protocol called DTP, Datacenter Time Protocol (DTP), that can provide tens of nanosecond precision in a datacenter environment. The protocol runs inside the physical layer in order to eliminate many non-deterministic delay errors from the network. In particular, by running the protocol in the physical layer in a peerto-peer fashion, it can minimize the network jitter and easily scale up to a larger network. Chapter 4 discusses the design and evaluation of the system.

### **1.3 Contributions**

Traditionally, the physical layer of a network stack in a wired network has been considered as a black box and excluded from network research opportunities. However, we demonstrate that an augmented physical layer with timing information can improve many fundamental capabilities that are important for network measurements including packet pacing, packet capturing, and clock synchronization.

Our research is based on a fact that the physical layer of a network device is already synchronized with the physical layer of its directly connected device. Further, they send a continuous stream of symbols to each other in order to maintain the link between them. Our systems extend and utilize such symbollevel synchronization to achieve fine-grained timestamping, pacing and highly precise clock synchronization. In particular, we present the following three contributions in this dissertation.

**Precise timestamping and pacing** Accessing individual symbols on the wire requires complete access to the very bottom of the network protocol stack, the physical layer where symbols are transmitted over or received from the wire. Unfortunately, accessing the inside of the physical layer is not easy: The physical layer is often implemented as a physical chip with a limited or no interface. As a result, complete access to the physical layer requires a different approach: We demonstrate a new approach via SoNIC, a Software-defined Network Interface Card, where the entire physical layer is accessible from software in a way that a user application can control and capture the timing of physical layer bits and achieve bit level precision.

**Covert timing channel and Estimating available bandwidth** In order to demonstrate how precise timestamping and pacing offered by SoNIC can improve network applications, we implemented a covert timing channel, *Chupja*, and an available bandwidth estimation algorithm, *MinProbe*. Chupja is created by modulating timings of messages precisely and can deliver hundreds of thousands of bits covertly without being detected. MinProbe generates a train of probe messages with pre-defined intervals, measures received intervals, and can accurately estimate the available bandwidth.

**Precise clock synchronization** Achieving high precision in a clock synchronization protocol is not easy due to uncertainties from the network stack and network itself. We present a clock synchronization protocol that runs in the physical layer. DTP, Datacenter Time Protocol, is a decentralized protocol that eliminates many non-deterministic elements from the network. As a result, it provides tens of nanosecond bounded precision in a datacenter network. We demonstrate that DTP advances the state-of-the-art protocol.

## 1.4 Organization

The rest of this dissertation is organized as follows. Chapter 2 describes the scope of the problem and methodology including the details of how the physical layer works. We present SoNIC which provides precise timestamping and pacing in Chapter 3. Chapter 3 also covers two network applications that benefit from precise timestamping and pacing: Chupja in Section 3.4 and MinProbe in Section 3.5. Then, we describe DTP that provides precise clock synchronization in Chapter 4. We survey related work in Chapter 5, which is followed by

future work in Chapter 6 and conclusion in Chapter 7.

#### CHAPTER 2

#### SCOPE AND METHODOLOGY

In this chapter, we discuss the scope of the problem and the methodology we used for investigation. Our research focuses on how to improve the precision of timestamping, pacing and clock synchronization for network measurements. We use the physical layer to advance the state-of-the-art systems. As a result, we describe how the physical layer of 10 GbE performs first and then describe the scope and methodology.

#### 2.1 Scope

The physical layer of the network stack can provide timing information necessary for precise timestamping, pacing and clock synchronization. In particular, when two physical layers are connected via a cable (we call them *peers*), each physical layer always generates a continuous bitstream that consists of either special characters or Ethernet frames to maintain the link connectivity. Further, each physical layer recovers the clock from the received bitstream generated by the peer's physical layer. In other words, two physical layers are already synchronized for reliable and robust communication. As a result, if we can control and access every single bit in the physical layer, we can achieve precise timestamping and pacing. Similarly, if we can extend the synchronization between two physical layers, we can achieve precise clock synchronization. Therefore, understanding how the physical layer operates is important for addressing research questions we investigate in this dissertation. In this section, we first discuss how the physical layer operates in Section 2.1.1. We mainly focus on 10 Gigabit Ethernet (GbE) which our systems are based on. Other standards such as 40 and 100 GbE share many details and same techniques we use in 10 GbE can also be applied to them. In Section 2.1.2, we discuss how accessing the physical layer allows precise timestamping and pacing, and what are the challenges to do so in software in realtime. In Section 2.1.3, we describe why it is hard to precisely synchronize clocks and why implementing a protocol in the physical layer can improve the precision.

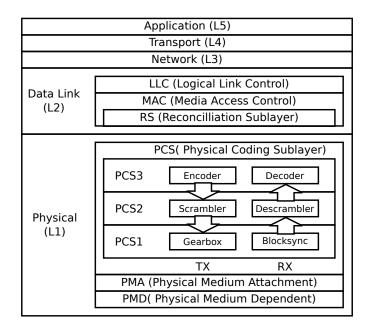

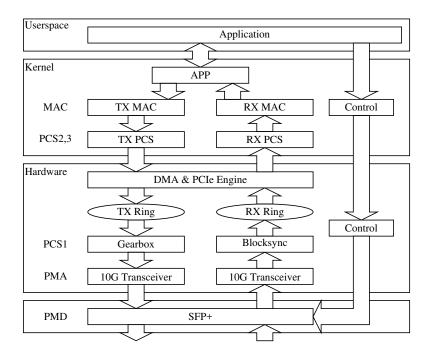

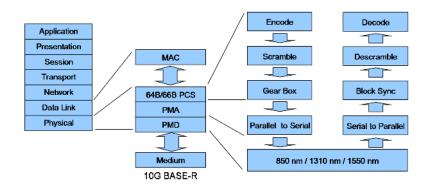

#### 2.1.1 IEEE 802.3 standard

According to the IEEE 802.3 standard [19], the physical layer (PHY) of 10 GbE consists of three sublayers: the Physical Coding Sublayer (PCS), the Physical Medium Attachment (PMA) sublayer, and the Physical Medium Dependent (PMD) sublayer (See Figure 2.1). The PMD sublayer is responsible for transmitting the outgoing symbolstream over the physical medium and receiving the incoming symbolstream from the medium. The PMA sublayer is responsible for clock recovery and (de-)serializing the bitstream. The PCS performs the blocksync and gearbox (we call this PCS1), scramble/descramble (PCS2), and encode/decode (PCS3) operations on every Ethernet frame. The IEEE 802.3 Clause 49 explains the PCS sublayer in further detail, but we will summarize below.

When Ethernet frames are passed from the data link layer to the PHY, they are reformatted before being sent across the physical medium. On the transmit (TX) path, the PCS performs 64b/66b encoding and encodes every 64-bit

Figure 2.1: IEEE 802.3 10 Gigabit Ethernet Network stack.

of an Ethernet frame into a 66-bit *block* (PCS3), which consists of a two-bit *syn-chronization header* (syncheader) and a 64-bit *payload*. As a result, a 10 GbE link actually operates at 10.3125 Gbaud ( $10G \times \frac{66}{64}$ ). Syncheaders are used for block synchronization by the remote RX path.

There are two types of *blocks*: Data blocks and control blocks. Both are 66 bits in length. The data block (/D/) is shown in the first row of Figure 2.2 and represents data characters from Ethernet frames. All other blocks in Figure 2.2 are control blocks, which contain a combination of data and control characters. Each rectangle labeled by  $D_i$  represents a 8-bit data character, and  $C_i$  represents a 7-bit control character. An idle character (/I/) is a control character that is used to fill the gap between two Ethernet frames. Given an Ethernet frame, the PCS first encodes a *Start* control block ( $S_0$  and  $S_4$  in Figure 2.2), followed by multiple data blocks. At the end of the frame, the PCS encodes a *Terminate* control block ( $T_0$  to  $T_7$ ) to indicate the end of the Ethernet frame. Note that one

of Start control blocks ( $S_4$ ) and most of Terminate control blocks ( $T_0$  to  $T_7$ ) have one to seven control characters. These control characters are normally filled with idle characters (zeros).

There is a 66-bit Control block (/E/), which encodes eight 7-bit idle characters (/I/). As the standard requires at least twelve /I/s in an interpacket gap, it is *guaranteed* to have at least one /E/ block preceding any Ethernet frame.<sup>1</sup> Moreover, when there is no Ethernet frame, there are always /E/ blocks: 10 GbE is always sending at 10 Gbps and sends /E/ blocks continuously if there are no Ethernet frames to send.

The PCS scrambles each encoded 66-bit block (PCS2) to maintain Direct Current (DC) balance<sup>2</sup> and adapts the 66-bit width of the block to the 16-bit width of the PMA interface (PCS1; the gearbox converts the bit width from 66- to 16bit width.) before passing it down the network stack. The entire 66-bit block is transmitted as a continuous stream of *symbols* which a 10 GbE network transmits over a physical medium (PMA & PMD). On the receive (RX) path, the PCS performs block synchronization based on two-bit syncheaders (PCS1) and descrambles each 66-bit block (PCS2) before decoding it (PCS3).

Above the PHY is the Media Access Control (MAC) sublayer and Reconciliation Sublayer (RS). The 10 GbE MAC operates in full duplex mode; it does not handle collisions. Consequently, it only performs data encapsulation/decapsulation and media access management. Data encapsulation includes framing as well as error detection. A Cyclic Redundancy Check (CRC) is used to detect bit corruption. Media access management inserts at least 96 bits (twelve /I/

<sup>&</sup>lt;sup>1</sup>Full-duplex Ethernet standards such as 1, 10, 40, 100 GbE send at least twelve / I/s (at least one /E/) between every Ethernet frame.

<sup>&</sup>lt;sup>2</sup>DC balance ensures a mix of 1's and 0's is sent.

|    |      | sync |           | Block Payload |    |    |    |    |     |    |      |    |       |    |    |    |    |    |

|----|------|------|-----------|---------------|----|----|----|----|-----|----|------|----|-------|----|----|----|----|----|

|    |      | 01   | 2         | Bit Position  |    |    |    |    |     |    |      |    |       |    |    |    |    |    |

| 1  | /D/  | 01   | D0        | D1            | D2 | D3 | ;  | D4 |     | D5 |      | D6 |       | D7 |    |    |    |    |

|    |      |      | BlockType | lockType      |    |    |    |    |     |    |      |    |       |    |    |    |    |    |

| 2  | /E/  | 10   | 0x1e      | C0            | C1 | C2 | 0  | 23 | C4  | 4  | C5   |    | C6    | C7 |    |    |    |    |

| 3  | /S0/ | 10   | 0x78      | D1            | D2 | D3 | D4 |    | 4   |    | D5   |    | D5 D6 |    | D6 | D7 |    |    |

| 4  | /S4/ | 10   | 0x33      | C0            | C1 | C2 | C3 |    |     |    | D5 D |    | D6    | D7 |    |    |    |    |

| 5  | /T0/ | 10   | 0x87      |               | C1 | C2 | 0  | 23 | C4  | 4  | C5   |    | C6    | C7 |    |    |    |    |

| 6  | /T1/ | 10   | 0x99      | D0            |    | C2 | (  | 23 | C4  | 4  | C5   |    | C6    | C7 |    |    |    |    |

| 7  | /T2/ | 10   | 0xaa      | D0            | D1 |    | 0  | 23 | C4  | 4  | C5   |    | C6    | C7 |    |    |    |    |

| 8  | /T3/ | 10   | 0xb4      | D0            | D1 | D2 | 2  |    | C4  | 4  | C5   |    | C6    | C7 |    |    |    |    |

| 9  | /T4/ | 10   | 0xcc      | D0            | D1 | D2 | D2 |    | : C |    | 3    |    | C5    |    | C6 | C7 |    |    |

| 10 | /T5/ | 10   | 0xd2      | D0            | D1 | D2 | D2 |    | 3   |    | D4   |    | C6    | C7 |    |    |    |    |

| 11 | /T6/ | 10   | 0xe1      | D0            | D1 | D2 | D2 |    | D2  |    | D    |    | 3     |    | D4 |    | D5 | C7 |

| 12 | /T7/ | 10   | 0xff      | D0            | D1 | D2 |    | D  | 3   | I  | D4   |    | D5    | D6 |    |    |    |    |

Figure 2.2: IEEE 802.3 64b/66b block format

characters) between two Ethernet frames. The RS is responsible for additionally inserting or removing idle characters (/I/s) between Ethernet frames to maintain the link speed. The channel between the RS and the PHY is called the 10 gigabit media independent interface (XGMII) and is four bytes wide. Data is transferred at every rising and falling edge. As a result, the channel operates at 156.25 MHz (= 10Gb/32bit/2).

On the transmit path, upon receiving a layer 3 packet, the MAC prepends a preamble, start frame delimiter (SFD), and an Ethernet header to the beginning of the frame. It also pads the Ethernet payload to satisfy a minimum framesize requirement (64 bytes), computes a CRC value, and places the value in the Frame Check Sequence (FCS) field. On the receive path, the MAC checks the CRC value and passes the Ethernet header and payload to higher layers while discarding the preamble and SFD.

#### 2.1.2 Precise Timestamping and Pacing Need Access to PHY

Accessing the PHY provides the ability to study networks and the network stack at a heretofore inaccessible level: It can help improve the precision of network measurements by orders of magnitude [58]. A 10 GbE network uses one bit per symbol. Since a 10 GbE link operates at 10.3125 Gbaud, each and every symbol length is 97 pico-seconds wide (=  $1/(10.3125 * 10^9)$ ). Knowing the number of bits can then translate into having a precise measure of time at the sub-nanosecond granularity. In particular, depending on the combination of data and control characters in the PCS block (Figure 2.2), the number of bits between data frames is not necessarily a multiple of eight. Therefore, on the RX path, we can tell the exact distance between Ethernet frames in bits by counting *every bit*. On the TX path, we can control time gaps by controlling the number of bits (idle characters) between frames.

Unfortunately, current commodity network interface cards do not provide any Application Program Interfaces (API) for accessing and controlling every bit in the PHY. One way of doing it is to use physics equipment such as an oscillator for capturing signals and a laser modulator for transmitting signals as shown in BiFocals [58]. However, BiFocals is not a realtime tool: It can only transmit pregenerated symbols and must perform extensive offline computation to recover symbols from captured signals by the oscillator. As a result, we take a different approach to access and control bits in the PHY: Implement the PHY in software.

The fundamental challenge to perform the PHY functionality in software is maintaining synchronization with hardware while efficiently using system resources. Some important areas of consideration when addressing this challenge include *hardware support, realtime capability, scalability and efficiency, and a usable*  interface.

#### Hardware support

The hardware must be able to transfer raw symbols from the wire to software at high speeds. This requirement can be broken down into four parts: a) Converting optical signals to digital signals (PMD), b) Clock recovery for bit detection (PMA), and c) Transferring large amounts of bits to software through a high-bandwidth interface. Additionally, d) the hardware should leave recovered bits (both control and data characters in the PHY) intact until they are transferred and consumed by the software. Commercial optical transceivers are available for a). However, hardware that simultaneously satisfies b), c) and d) is not common since it is difficult to handle 10.3125 Giga symbols in transit every second.

NetFPGA 10G [91] does not provide software access to the PHY. In particular, NetFPGA pushes not only layers 1-2 (the physical and data link layer) into hardware, but potentially layer 3 as well. Furthermore, it is not possible to easily undo this design since it uses an on-board chip to implement the PHY which prevents direct access to the PCS sublayer. As a result, we need a new hardware platform to support software access to the PHY.

#### **Realtime Capability**

Both hardware and software must be able to process 10.3125 Gigabits per second (Gbps) continuously. The IEEE 802.3 standard [19] requires the 10 GbE PHY to generate a continuous bitstream. However, synchronization between hardware and software and between multiple pipelined cores is non-trivial. The overheads of interrupt handlers and OS schedulers can cause a discontinuous bitstream which can subsequently incur packet loss and broken links. Moreover, it is difficult to parallelize the PCS sublayer onto multiple cores. This is because the (de-)scrambler relies on state to recover bits. In particular, the (de-)scrambling of one bit relies upon the 59 bits preceding it. This fine-grained dependency makes it hard to parallelize the PCS sublayer. The key takeaway here is that everything must be efficiently pipelined and well-optimized in order to implement the PHY in software while minimizing synchronization overheads.

#### **Scalability and Efficiency**

The software must scale to process multiple 10 GbE bitstreams while efficiently utilizing resources. Intense computation is required to implement the PHY and MAC layers in software. (De-)Scrambling every bit and computing the CRC value of an Ethernet frame is especially intensive. A functional solution would require multiple duplex channels that independently perform the CRC, encode/decode, and scramble/descramble computations at 10.3125 Gbps. The building blocks for the PCS and MAC layers will therefore consume many CPU cores. In order to achieve a scalable system that can handle multiple 10 GbE bitstreams, resources such as the PCIe, memory bus, Quick Path Interconnect (QPI), cache, CPU cores, and memory must be efficiently utilized.

#### **User Interface**

Users must be able to easily access and control the PHY. Many resources from software to hardware must be tightly coupled to allow realtime access to the PHY. Thus, an interface that allows fine-grained control over them is necessary. The interface must also implement an I/O channel through which users can retrieve data such as the count of bits for precise timing information.

### 2.1.3 Precise Clock Synchronization Needs Access to PHY

The common mechanism of synchronizing two clocks is similar across different algorithms and protocols: A process *reads* a different process's current clock counter and computes an offset, adjusting its own clock frequency or clock counter by the offset.

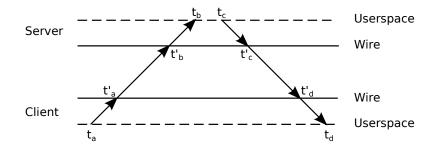

In more detail, a process p sends a time request message with its current *local* clock counter ( $t_a$  in Figure 2.3) to a process q (q reads p's clock). Then, process q responds with a time response message with its local clock counter and p's original clock counter (p reads q's clock). Next, process p computes the offset between its local clock counter and the *remote clock* counter (q) and round trip time (RTT) of the messages upon receiving the response at time  $t_d$ . Finally, p adjusts its clock counter or the rate of its clock to remain close to q's clock.

In order to improve precision, q can respond with two clock counters to remove the internal delay of processing the time request message: One upon receiving the time request ( $t_b$ ) and the other before sending the time response ( $t_c$ ). See Figure 2.3. For example, in NTP, the process p computes RTT  $\delta$  and offset  $\theta$ ,

Figure 2.3: Common approach to measure offset and RTT.

as follows [98]:

$$\delta = (t_d - t_a) - (t_c - t_b)$$

$$\theta = \frac{(t_b + t_c)}{2} - \frac{(t_a + t_d)}{2}$$

Then, *p* applies these values to adjust its local clock.

#### **Problems of Clock synchronization**

Precision of a clock synchronization protocol is a function of clock skew, errors in reading remote clocks, and the interval between resynchronizations [50, 63, 75]. We discuss these factors in turn below and how they contribute to (reduced) precision in clock synchronization protocols.

**Problems with Oscillator skew** Many factors such as temperature and quality of an oscillator can affect oscillator skew. Unfortunately, we often do not have control over these factors to the degree necessary to prevent reduced precision. As a result, even though oscillators may have been designed with the same nominal frequency, they may actually run at slightly different rates causing clock counters to diverge over time, requiring synchronization.

Problems with Reading Remote Clocks There are many opportunities where

reading clocks can be inaccurate and lead to reduced precision. In particular, reading remote clocks can be broken down into multiple steps (enumerated below) where each step can introduce random delay errors that can affect the precision of clock synchronization.

- 1. Preparing a time request (reply) message

- 2. Transmitting a time request (reply) message

- 3. Packet traversing through a network

- 4. Receiving a time request (reply) message

- 5. Processing a time request (reply) message

Specifically, there are three points where precision is adversely affected: (a) Precision of timestamping affects steps 1 and 5, (b) the software network stack can introduce errors in steps 2 and 4, and (c) network jitter can contribute errors in step 3. We discuss each one further.

First, precise timestamping is not trivial. Before transmitting a message, a process timestamps the message to embed its own local counter value. Similarly, after receiving a message, a process timestamps it for further processing (i.e. computing RTT). Timestamping is often imprecise in commodity systems [81], which is a problem. It can add random delay errors which can prevent the nanosecond-level timestamping required for 10 Gigabit Ethernet (10 GbE) where minimum sized packets (64-byte) arriving at line speed can arrive every 68 nanoseconds. Improved timestamping with nanosecond resolution via new NICs are becoming more accessible [24]. However, random jitter can still be introduced due to the issues discussed below.

Second, transmitting and receiving messages involve a software network stack (e.g., between  $t_a$  and  $t'_a$  in Figure 2.3). Most clock synchronization protocols (e.g., NTP and PTP) run in a time daemon, which periodically sends and receives UDP packets between a remote process (or a time server). Unfortunately, the overhead of system calls, buffering in kernel and network interfaces, and direct memory access transactions can all contribute to errors in delay [53, 58, 81]. To minimize the impact of measurement errors, a daemon can run in kernel space or kernel bypassing can be employed. Nonetheless, non-deterministic delay errors cannot be completely removed when a protocol involves a network stack.

Third, packet propagation time can vary since it is prone to network jitter (e.g., between  $t'_a$  and  $t'_b$  or between  $t'_c$  and  $t'_d$  in Figure 2.3). Two processes are typically multiple hops away from each other and the delay between them can vary over time depending on network conditions and external traffic. Further, time requests and responses can be routed through asymmetric paths, or they may suffer different network conditions even when they are routed through symmetric paths. As a result, measured delay, which is often computed by dividing RTT by two, can be inaccurate.

### **Problems with Resynchronization Frequency**

The more frequent resynchronizations, the more precise clocks can be synchronized to each other. However, frequent resynchronizations require increased message communication, which adds overhead to the network, especially in a datacenter network where hundreds of thousands of servers exist. The interval between resynchronizations can be configured. It is typically configured to resynchronize over a period of once per second [18], which will keep

Figure 2.4: Clock domains of two peers. The same color represents the same clock domain.

network overhead low, but on the flip side, will also adversely affect precision of clock synchronization.

#### Why clock synchronization in the PHY?

Our goal is to achieve synchronizing clocks with nanosecond-level precision and with scalability in a datacenter network, and without *any* network overhead. We achieve this goal by running a decentralized protocol in the PHY.

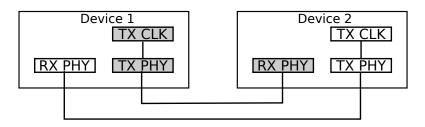

We exploit the fact that two *peers*<sup>3</sup> are already synchronized in the PHY in order to transmit and receive bitstreams reliably and robustly. In particular, the receive path (RX) of a peer physical layer recovers the clock from the physical medium signal generated by the transmit path (TX) of the sending peer's PHY. As a result, although there are two physical clocks in two network devices, they are virtually in the same circuit (Figure 2.4).

Further, a commodity switch often uses one clock oscillator to feed the sole switching chip in a switch [7], i.e. all TX paths of a switch use the same clock source. Given a switch and N network devices connected to it, there are N + 1 physical oscillators to synchronize, and all of them are virtually in the same

<sup>&</sup>lt;sup>3</sup>two peers are two physically connected ports via a cable.

circuit.

As delay errors from network jitter and a software network stack can be minimized by running the protocol in the lowest level of a system [116], the PHY is the best place to reduce those sources of errors. In particular, we give three reasons why clock synchronization in the PHY addresses the problems discussed previously.

First, the PHY allows precise timestamping at sub-nanosecond scale, which can provide enough fidelity for nanosecond-level precision. Timestamping [58, 81] in the PHY achieves high precision by counting the number of bits between and within packets. Timestamping in the PHY relies on the clock oscillator that generates bits in the PHY, and, as a result, it is possible to read and embed clock counters with a deterministic number of clock cycles in the PHY.

Second, a software network stack is not involved in the protocol. As the PHY is the lowest layer of a network protocol stack, there is always a deterministic delay between timestamping a packet and transmitting it. In addition, it is always possible to avoid buffering in a network device because protocol messages can always be transmitted when there is no other packet to send.

Lastly, there is little to no variation in delay between two peers in the PHY. The only element in the middle of two physically communicating devices is the wire that connects them. As a result, when there is no packet in transit, the delay in the PHY measured between two physically connected devices will be the time to transmit bits over the wire, a few clock cycles required to process bits in the PHY (which can be deterministic), and a clock domain crossing (CDC) which can add additional random delay. A CDC is necessary for passing data between two clock domains, namely between the transmit and receive paths. Synchronization First-In-First-Out (FIFO) queues are commonly used for a CDC. In a synchronization FIFO, a signal from one clock domain goes through multiple flip-flops in order to avoid meta-stability from the other clock domain. As a result, one random delay could be added until the signal is stable to read.

Operating a clock synchronization protocol in the PHY layer not only provides the benefits of zero to little delay errors, but also zero overhead to a network: There is no need for injection of packets to implement a clock synchronization protocol. As mentioned in Section 2.1.1 a network interface continuously generates either Ethernet frames or special characters (idle characters) to maintain a link connection to its peer. If we use these idle characters to deliver protocol messages (and revert them back to idle characters), no additional packets will be required. Further, we can send protocol messages between every Ethernet frame without degrading the bandwidth of Ethernet and for different Ethernet speeds.

## 2.2 Methodology: Experimental Environments

We used various types of hardware and network topologies throughout this dissertation to evaluate our approach. We illustrate them in the following subsections.

(a) HiTech Global FPGA board

(b) Terasaic DE5-Net board

Figure 2.5: FPGA development boards used for our research.

| Name      | CPU                       | # of cores | L3 Cache | Memory | NIC                    |

|-----------|---------------------------|------------|----------|--------|------------------------|

| SoNIC     | Two Xeon X5670, 2.93GHz   | 6          | 12 MB    | 12 GB  | HiTech with SoNIC      |

| ALT10G    | Two Xeon X5670, 2.93GHz   | 6          | 12 MB    | 12 GB  | HiTech with 10 GbE     |

| Client    | Two Xeon X5670, 2.93GHz   | 6          | 12 MB    | 12 GB  | Myricom dual 10G port  |

| Adversary | Two Xeon X5670, 2.93GHz   | 6          | 12 MB    | 12 GB  | Myricom dual 10G port  |

| Fractus   | Two Xeon E5-2690, 2.90GHz | 8          | 20 MB    | 96 GB  | Terasic DE5 with DTP   |

|           |                           |            |          |        | Mellanox dual 10G port |

Table 2.1: List of servers used for development and experiments

# 2.2.1 Hardware

For developing and evaluating SoNIC, Chupja and MinProbe, Dell Precision T7500 workstations and Dell T710 servers were used. Each machine was a dual socket, 2.93 GHz six core Xeon X5670 (Westmere [21]) with 12 MB of shared Level 3 (L3) cache and 12 GB of RAM, 6 GB connected to each of the two CPU sockets. We differentiated hardware configurations of the T7500 workstations for various purposes; a machine with an HiTech Global FPGA board [15] (Figure 2.5(a)) with SoNIC firmware (we call this SoNIC server), a machine with an FPGA board with an Altera 10G Ethernet design [1] (we call this ALT10G), and a machine with a Myricom 10G-PCIE2-8B2-2S dual 10G port NIC (we call this Client). Similarly, we also differentiated hardware configurations of the T710 servers for various purposes: We used one 10 GbE Dual-port NIC for receiving

| Name                     | # of 10 GbE ports | Note                         |  |  |

|--------------------------|-------------------|------------------------------|--|--|

| HiTech                   | 2                 | Stratix IV FPGA              |  |  |

| DE5-NET                  | 4                 | Stratix V FPGA               |  |  |

| Myricom 10G-PCIE2-8B2-2S | 2                 | HW timestamping              |  |  |

| Mellanox ConnectX-3      | 2                 | HW timestamping, PTP-enabled |  |  |

Table 2.2: List of FPGA boards and NICs used for development and experiments

|              | Туре | 40G | 10G | 1G | Full bandwidth | Forwarding | Note        |  |

|--------------|------|-----|-----|----|----------------|------------|-------------|--|

| SW1          | Core | 0   | 8   | 0  | 160 Gbps       | SF         |             |  |

| SW2          | ToR  | 4   | 48  | 0  | 1280 Gbps      | СТ         |             |  |

| SW3          | ToR  | 0   | 2   | 48 | 136 Gbps       | SF         |             |  |

| SW4          | ToR  | 0   | 2   | 24 | 105.6 Gbps     | SF         |             |  |

| Cisco 6900   | Core | 0   | 8   | 0  | 160 Gbps       | SF         |             |  |

| Cisco 4948   | ToR  | 0   | 2   | 48 | 136 Gbps       | SF         |             |  |

| IBM G8264    | ToR  | 4   | 48  | 0  | 1280 Gbps      | СТ         | PTP-enabled |  |

| Dell Force10 | ToR  | 4   | 48  | 0  | 1280 Gbps      | СТ         |             |  |

Table 2.3: List of evaluated network switches. "SF" is store-and-forward and "CT" is cut-through.

packets for evaluating Chupja (we call this the adversary) and used an HiTech Global FPGA board with SoNIC firmware for evaluating MinProbe (we also call this SoNIC server).

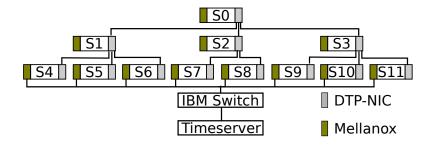

For evaluating DTP, a cluster of twelve Dell R720 servers were used (we call them Fractus nodes). Each server was a dual socket, 2.90 GHz eight core Xeon E5-2690 with 20 MB of shared L3 cache and 96 GB of RAM, 48 GB connected to each of the two CPU sockets. The machines had seven PCIe Gen 3.0 slots, where DTP hardware was plugged in: We used DE5-Net boards from Terasaic [9] (Figure 2.5(b). A DE5-Net board is an FPGA development board with an Altera Stratix V FPGA [5] and four Small Form-factor Pluggable (SFP+) modules. Each server also had a Mellanox ConnectX-3 MCX312A 10G NIC, which supports hardware timestamping for incoming and outgoing packets. Table 2.3 summarizes the commercial switches that we used for evaluating our systems. SW1 was a core / aggregate router with multiple 10 GbE ports, and we installed two modules with four 10 GbE ports. SW2 was a high-bandwidth 10 GbE top-of-rack (ToR) switch which was able to support forty eight 10 GbE ports at line speed. Moreover, it was a cut-through switch whose latency of forwarding a packet was only a few microseconds. SW3 and SW4 were 1 GbE ToR switches with two 10 GbE uplinks. Other than SW2, all switches were store-and-forward switches. Further, we used Cisco 6500, 4948, IBM G8264, Dell Force10 switches for the evaluation of SoNIC, DTP, and MinProbe. IBM G8264 switch is a PTP-enabled cut-through switch.

### 2.2.2 Network Topologies

### Simple Setup

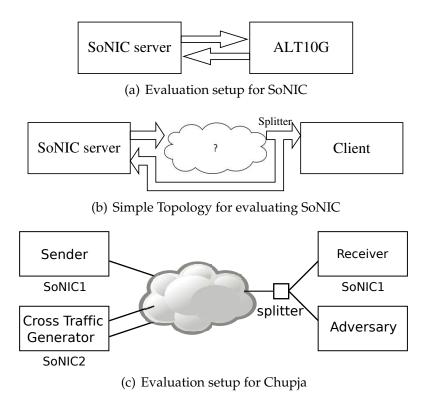

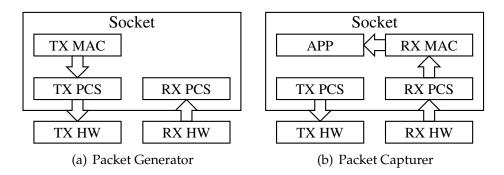

In order to evaluate pacing and timestamping capabilities of SoNIC, we used two FPGA boards. In particular, we connected the SoNIC board and the ALT10G board directly via optic fibers (Figure 2.6(a)). For evaluating SoNIC's pacing capability, we used SoNIC to generate packets to ALT10G. ALT10G provided detailed statistics such as the number of valid/invalid Ethernet frames, and frames with CRC errors. We compared these numbers from ALT10G with statistics from SoNIC to verify the correctness of SoNIC. Similarly, for evaluating SoNIC's timestamping capability, we used ALT10G for packet generation. ALT10G allowed us to generate random packets of any length and with the minimum interpacket gap. We verified if SoNIC was able to correctly receive and timestamp all packets from ALT10G.

Figure 2.6: Simple evaluation setup

Further, we created a simple topology to evaluate SoNIC: We used port 0 of SoNIC server to generate packets to the Client server via an arbitrary network, and split the signal with a fiber optic splitter so that the same stream can be directed to both the Client and port 1 of the SoNIC server capturing packets (Figure 2.6(b)). We used various network topologies composed of Cisco 4948 [8] and IBM BNT G8264 [17] switches for the network between the SoNIC server and the Client.

For experiments of covert channels called Chupja in Chapter 3.4, we deployed two SoNIC servers each equipped with two 10 GbE ports to connect fiber optic cables. We used one SoNIC server (SoNIC1) to generate packets of the sender destined to a server (the adversary) via a network. We placed a fiber optic splitter at the adversary which mirrored packets to SoNIC1 for capture

Figure 2.7: A small network. Thick solid lines are 10G connections while dotted lines are 1G connections.

(i.e. SoNIC1 was both the sender and receiver). SoNIC2 was used to generate cross traffic flows when necessary (Figure 2.6(c)). We placed none or multiple commercial switches between the sender and the adversary (the cloud within Figure 2.6(c)). A similar topology was used to evaluate available bandwidth estimation called MinProbe in Chapter 3.5. We placed two network switches between the sender and the receiver.

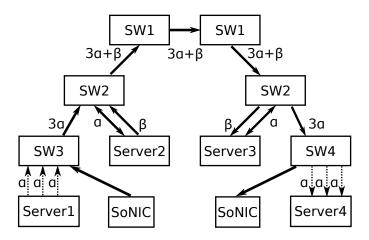

### Small Network in a Lab

We created our own network for evaluating Chupja by connecting six switches, and four servers (See Figure 2.7). The topology resembled a typical network where core routers (SW1) were in the middle and 1 GbE ToR switches (SW3 and SW4) were leaf nodes. Then, SoNIC1 (the sender) generated packets to SW3 via one 10 GbE uplink, which forwarded packets to the receiver which was connected to SW4 via one 10 GbE uplink. Therefore, it was a seven-hop network with 0.154 ms round trip time delay on average. Then, we used four servers (Server1 to 4) to generate cross traffic. Each server had four 1 GbE and two 10 GbE ports. Server1 (Server4) was connected to SW3 (SW4) via three 1

Figure 2.8: Our path on the National Lambda Rail

GbE links, and Server2 (Server3) was connected to SW3 via two 10 GbE links. These servers generated traffic across the network with Linux pktgen [106]. The bandwidth of cross traffic over each link between switches is illustrated in Figure 2.7: 1 GbE links were utilized with flows at  $\alpha$  Gbps and 10 GbE links at  $\beta$ Gbps.

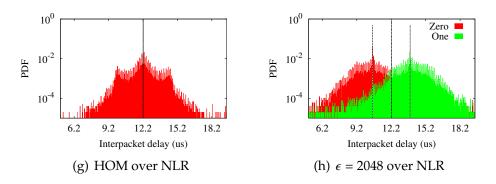

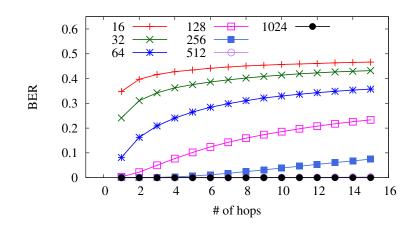

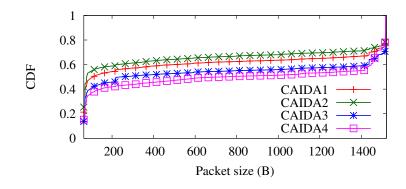

### National Lambda Rail