The Pennsylvania State University

The Graduate School

Department of Computer Science and Engineering

# TOWARDS SELF-OPTIMIZING MEMORY MANAGEMENT

A Thesis in

Computer Science and Engineering

by

Gokul B. Kandiraju

© 2004 Gokul B. Kandiraju

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

May 2004

We approve the thesis of Gokul B. Kandiraju.

Date of Signature

Anand Sivasubramaniam Associate Professor of Computer Science and Engineering Thesis Adviser Chair of Committee

Mary Jane Irwin Distinguished Professor of Computer Science and Engineering

Natarajan Gautam Associate Professor of Industrial Engineering

Mahmut Kandemir Assistant Professor of Computer Science and Engineering

Ekanadham Kattamuri Research Staff Member of IBM T. J. Watson Research Center Special Member

Raj Acharya Professor of Computer Science and Engineering Head of the Department of Computer Science and Engineering

## Abstract

Systems today are application driven. Increasing application sizes re-iterate the importance of memory management and increasing application complexity stresses the need for selfmanagement. At the same time, different memory requirements of different applications require that optimizations for memory management be done from a complete system perspective. In the view of this, the goal of this thesis is to take a step towards self-optimizing memory management at all the different levels of the memory hierarchy.

This thesis makes three main contributions to the memory management system. First, it undertakes a thorough characterization study for the TLBs and proposes a novel prefetching mechanism that is simple, powerful and adapts to the applications. Second, it presents a dynamic memory allocator that tunes itself to the applications. Finally, towards the goal of developing a self-optimizing VMM, it finds the important VMM parameters that govern the system performance, relates the influence of these parameters to the application/OS characteristics, and provides a solid motivation to set these parameters dynamically.

# **Table of Contents**

| List of Tabl | vi                                               | ii |

|--------------|--------------------------------------------------|----|

| List of Figu | res                                              | x  |

| Acknowled    | ments                                            | ii |

| Chapter 1.   | Introduction                                     | 1  |

| 1.1          | Hardware Enhancements for the TLB                | 4  |

| 1.2          | Software Memory Management                       | 6  |

| 1.3          | Adaptivity in the Operating System               | 8  |

| 1.4          | Application-controlled Memory Management         | 9  |

| 1.5          | Roadmap 1                                        | 0  |

| Chapter 2.   | Hardware Enhancements for the TLB                | 1  |

| 2.1          | Related Work                                     | 5  |

| 2.2          | Experimental Setup                               | 7  |

| 2.3          | Characterization Results                         | 9  |

|              | 2.3.1 What is the impact of TLB structure?       | 9  |

|              | 2.3.2 Will a multi-level TLB help?               | 1  |

|              | 2.3.3 Can we improve TLB coverage? (Superpaging) | 4  |

|              | 2.3.4 Where are the Misses Occurring?            | 6  |

|              |                                                  | 8  |

|     | 2.3.6   | Where are the misses occurring? - Static                         | 29 |  |  |  |

|-----|---------|------------------------------------------------------------------|----|--|--|--|

|     | 2.3.7   | How do procedure calls influence TLB behavior?                   | 29 |  |  |  |

|     | 2.3.8   | How would software TLB management help?                          | 34 |  |  |  |

|     | 2.3.9   | How far apart are the misses spatially?                          | 36 |  |  |  |

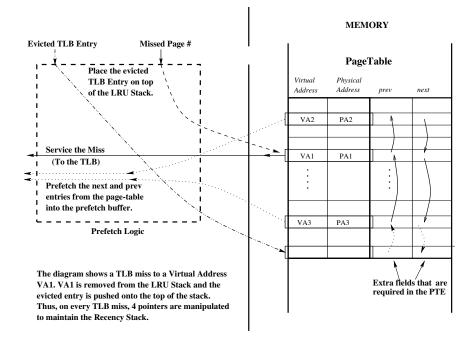

| 2.4 | Prefetc | ching TLB Entries                                                | 37 |  |  |  |

| 2.5 | Prefetc | ching Mechanisms                                                 | 43 |  |  |  |

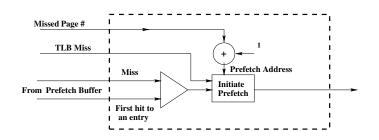

|     | 2.5.1   | Sequential Prefetching (SP)                                      | 45 |  |  |  |

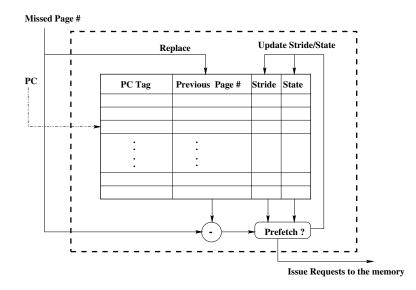

|     | 2.5.2   | Arbitrary Stride Prefetching (ASP)                               | 46 |  |  |  |

|     | 2.5.3   | Markov Prefetching (MP)                                          | 47 |  |  |  |

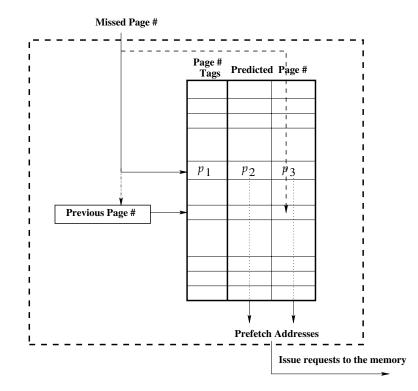

|     | 2.5.4   | Recency Based Prefetching (RP)                                   | 49 |  |  |  |

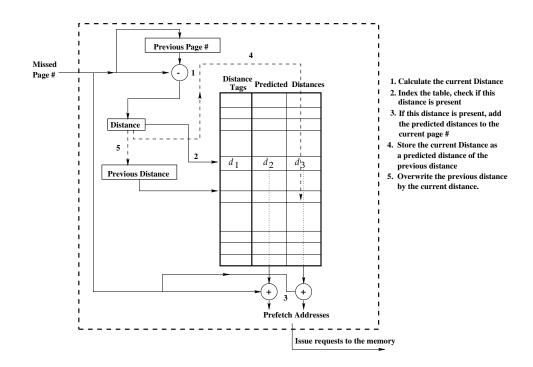

|     | 2.5.5   | Distance Prefetching (DP)                                        |    |  |  |  |

|     | 2.5.6   | Review of Hardware Requirements                                  | 54 |  |  |  |

| 2.6 | Qualita | ative Comparison of Schemes                                      | 55 |  |  |  |

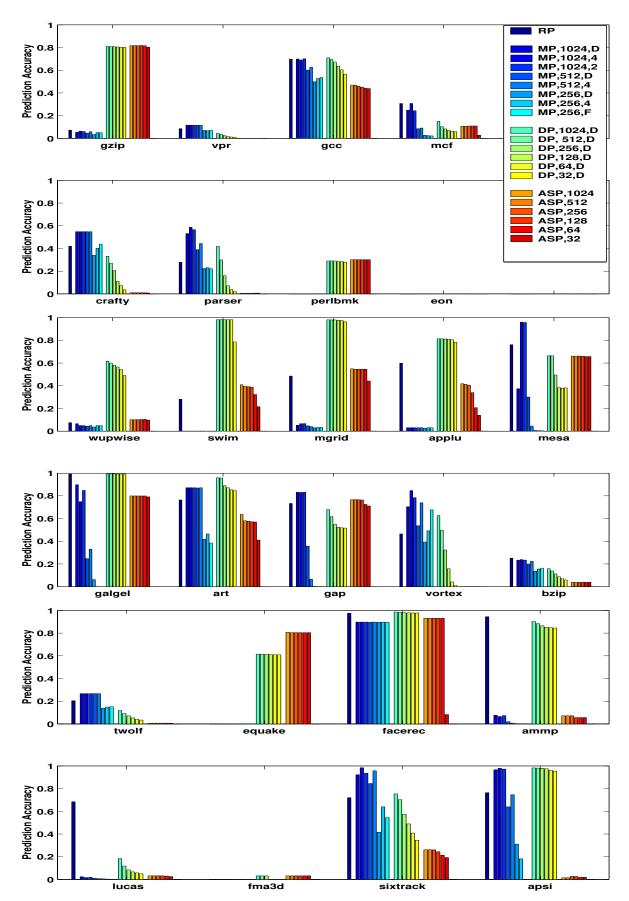

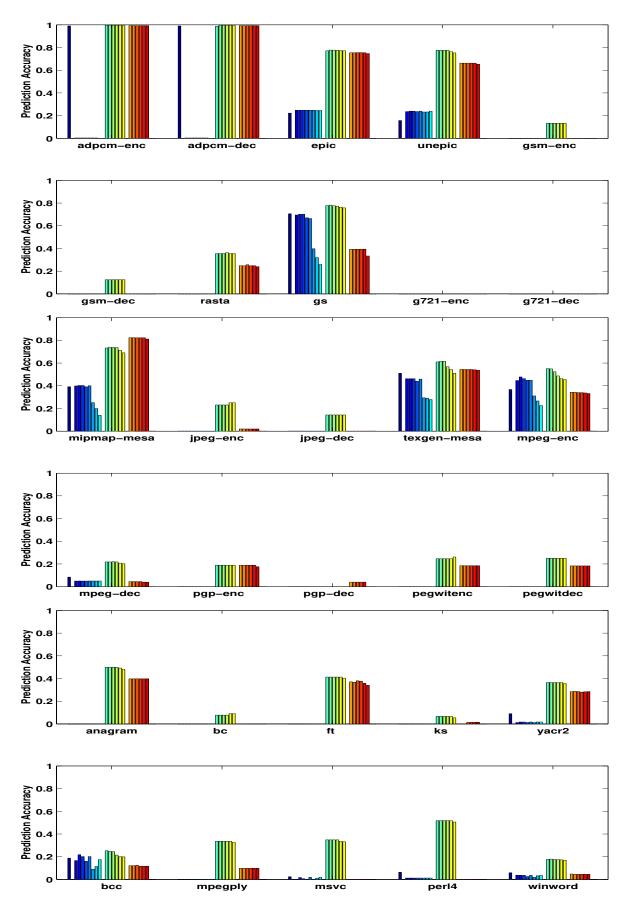

| 2.7 | Perform | mance Evaluation                                                 | 61 |  |  |  |

|     | 2.7.1   | Experimental Setup                                               | 61 |  |  |  |

|     | 2.7.2   | Comparing the Schemes                                            | 62 |  |  |  |

|     | 2.7.3   | Fine-tuning Distance Prefetching                                 | 72 |  |  |  |

|     |         | 2.7.3.1 Number of Rows and Associativity of the Prediction Table | 73 |  |  |  |

|     |         | 2.7.3.2 Number of prediction entries                             | 74 |  |  |  |

|     |         | 2.7.3.3 Prefetch Buffer Size                                     | 74 |  |  |  |

|     |         | 2.7.3.4 Influence of TLB Size                                    | 75 |  |  |  |

| 2.8 | Conclu  | Iding Remarks                                                    | 76 |  |  |  |

| Chapter 3. | Memo     | nory Management in the runtime environment                    |     |  |  |  |  |

|------------|----------|---------------------------------------------------------------|-----|--|--|--|--|

| 3.1        | Proble   | ns with Custom Allocators                                     |     |  |  |  |  |

| 3.2        | Basic    | perations of a Memory Allocator                               |     |  |  |  |  |

| 3.3        | Issues   | in designing a memory allocator                               | 80  |  |  |  |  |

|            | 3.3.1    | Issues considered in designing a traditional memory allocator | 80  |  |  |  |  |

|            | 3.3.2    | Next-generation memory allocator                              | 81  |  |  |  |  |

| 3.4        | Is there | re any scope for adaptivity?                                  | 82  |  |  |  |  |

|            | 3.4.1    | Application Characterization w.r.t. Adaptivity                | 83  |  |  |  |  |

|            |          | 3.4.1.1 How many 'Distinct Sizes' do these applications have  |     |  |  |  |  |

|            |          | and what is their frequency ?                                 | 83  |  |  |  |  |

|            |          | 3.4.1.2 What are these sizes ?                                | 84  |  |  |  |  |

|            |          | 3.4.1.3 What are the lifetimes for these sizes ?              | 85  |  |  |  |  |

|            |          | 3.4.1.4 Is there a Working-set ?                              | 86  |  |  |  |  |

| 3.5        | Systen   | n Design                                                      | 88  |  |  |  |  |

|            | 3.5.1    | Background : The Slab Allocator                               | 88  |  |  |  |  |

|            | 3.5.2    | Design                                                        | 89  |  |  |  |  |

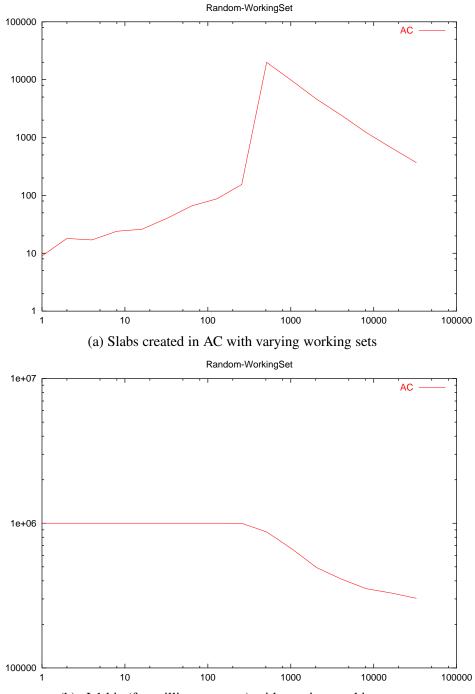

|            |          | 3.5.2.1 The Adaptive Cache - for frequently incoming sizes    | 90  |  |  |  |  |

| 3.6        | Perfor   | mance Evaluation                                              | 94  |  |  |  |  |

|            | 3.6.1    | Experimental Setup                                            | 94  |  |  |  |  |

|            | 3.6.2    | Quantitative comparison of the components                     | 95  |  |  |  |  |

|            |          | 3.6.2.1 Adaptive Cache                                        | 95  |  |  |  |  |

|            |          | 3.6.2.2 AOL/RB                                                | 99  |  |  |  |  |

|            | 3.6.3    | Performance Evaluation using applications                     | 101 |  |  |  |  |

vi

|            | 3.6.3.1 The Adaptive Cache                               | 101 |

|------------|----------------------------------------------------------|-----|

|            | 3.6.4 Slab Cache                                         | 105 |

|            | 3.6.4.1 The Slab Cache - servicing smaller sizes quickly | 105 |

|            | 3.6.5 Summary                                            | 107 |

| 3.7        | Conclusion                                               | 109 |

| Chapter 4. | Memory Management in the Operating System                | 110 |

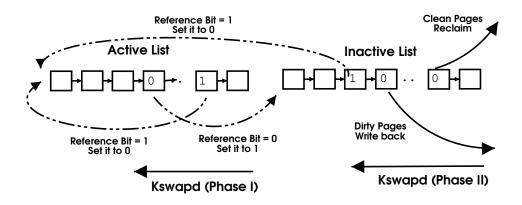

| 4.1        | Overview of the Linux VMM                                | 114 |

| 4.2        | Description and Qualitative Analysis of Parameters       | 117 |

| 4.3        | Quantitative Analysis of Parameters                      | 124 |

|            | 4.3.1 Experimental Setup                                 | 124 |

|            | 4.3.2 Quantitative analysis                              | 125 |

| 4.4        | Conclusion and Future Work                               | 142 |

| Chapter 5. | Conclusions                                              | 145 |

| 5.1        | Future Research                                          | 146 |

| References |                                                          | 149 |

# List of Tables

| 2.1 | TLBs in Commercial Microprocessors                                                     | 12 |

|-----|----------------------------------------------------------------------------------------|----|

| 2.2 | i-TLB Missrates for all the applications using a 64-entry, 4-way set-associative       |    |

|     | i-TLB for 7 billion instructions                                                       | 17 |

| 2.3 | Hit and Miss Rates for the 2-level TLB configuration. Table shows the hits and         |    |

|     | miss rates for each of the 2-levels as a percentage of the number of references to     |    |

|     | that level, as well as the overall miss rate which is the percentage of references     |    |

|     | that do not find a translation in either of the levels. Also shown are the miss        |    |

|     | rates for a single monolithic TLB of the same size                                     | 22 |

| 2.4 | Comparing miss rates for OPT' and LRU replacement policies                             | 34 |

| 2.5 | Comparing the Hardware Issues of the Schemes at a glance. $s$ is assumed to be         |    |

|     | 2 for MP and DP. PC Tag, Page # Tag, and Distance Tag for ASP, MP and DP               |    |

|     | respectively are needed for tag comparison when indexing/looking up the table.         | 54 |

| 2.6 | Example Reference Strings and No. of Correct Predictions for Each Mechanism.           | 56 |

| 2.7 | Table showing the average and weighted average of prediction accuracy for              |    |

|     | the prefetching schemes which was calculated using the miss $\mbox{rates}(m_i)$ and    |    |

|     | prediction accuracies( $p_i$ ) over all the 56 applications. $s = 2$ and $r = 256$ for |    |

|     | DP, MP and ASP.                                                                        | 68 |

| 2.8 | Comparing DP with RP: Normalized execution cycles(w.r.t. no prefetching) for           |    |

|     | RP and DP for 1 billion instructions after the first 2 billion instructions. $s = 2$   |    |

|     | and $r = 256$ for DP                                                                   | 72 |

| 3.1 | Applications that were used for malloc study.                                   | 82  |

|-----|---------------------------------------------------------------------------------|-----|

| 3.2 | Table showing percentage of requests covered by the most frequent sizes         | 83  |

| 3.3 | Table showing percentage of requests within a specific size                     | 85  |

| 3.4 | Table showing average lifetime for the requests (in requests)                   | 86  |

| 3.5 | Table showing average lifetime for the requests (in seconds)                    | 87  |

| 3.6 | Adaptive Cache Statistics                                                       | 101 |

| 3.7 | AOL and RB operations and timings, AC timings - comparison                      | 104 |

| 3.8 | Effect of the Adaptive Cache                                                    | 106 |

| 4.1 | Table showing a classification of VMM parameters based on their functionality   | 122 |

| 4.2 | Applications used                                                               | 124 |

| 4.3 | Table showing LRU stack depth frequency for some applications. This is a pure   |     |

|     | application characteristic that was derived from application memory references. | 129 |

| 4.4 | Table showing page-fault distances and their frequency for apsi and mummer      | 138 |

| 4.5 | Summary of influence of parameters                                              | 139 |

ix

# List of Figures

| 1.1  | Figure shows optimization methods for memory management                          | 3  |

|------|----------------------------------------------------------------------------------|----|

| 2.1  | Figure showing TLB miss rates of all the SPEC2000 applications with different    |    |

|      | TLB sizes (64, 128, 256) and three different associativities (2-way, 4-way and   |    |

|      | FA)                                                                              | 20 |

| 2.2  | Figure showing what size TLB would suffice when we combine contiguous            |    |

|      | virtual page translations with superpage entries. A 128 entry fully associative  |    |

|      | TLB is used                                                                      | 25 |

| 2.3  | PC Values Incurring TLB Misses                                                   | 30 |

| 2.4  | Figure showing Use and Replace matrices for different procedures. Applica-       |    |

|      | tions like galgel will not benefit from procedure based TLB allocation. $\ldots$ | 31 |

| 2.5  | Figure showing Use and Replace matrices for different procedures. mcf is a       |    |

|      | potential candidate because of interaction between $p_2$ , $p_3$ and $p_4$       | 32 |

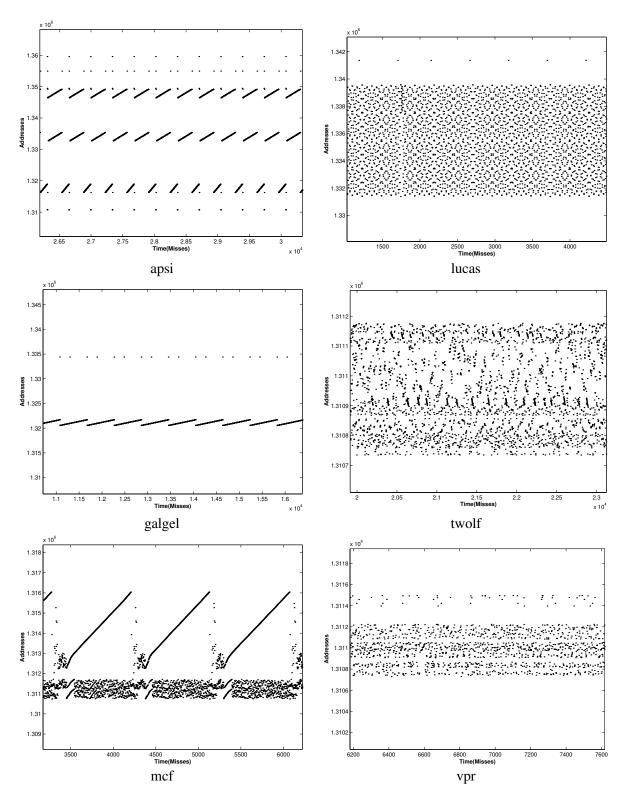

| 2.6  | Figure showing the data addresses that miss during the course of program exe-    |    |

|      | cution shown in the x-axis in terms of misses (Time)                             | 38 |

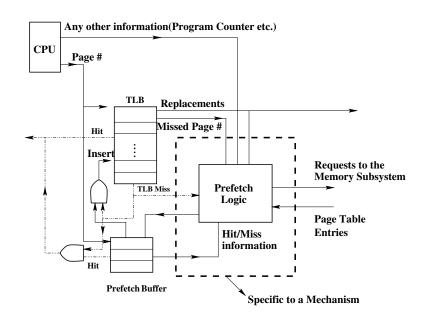

| 2.7  | Schematic of Hardware for Prefetching in all the Considered Mechanisms           | 44 |

| 2.8  | Schematic of Hardware for SP                                                     | 45 |

| 2.9  | Schematic of Hardware for ASP                                                    | 47 |

| 2.10 | Schematic of Hardware for MP with $s = 2$                                        | 48 |

| 2.11 | Schematic of Hardware for RP                                                     | 50 |

| 2.12 | Schematic of Hardware for DP with $s = 2$ .                                      | 52 |

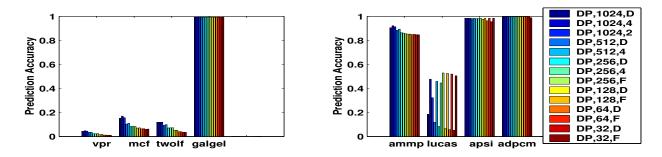

| 2.13 | Prediction Accuracy of different Prefetching mechanisms for all the SPEC CPU200                                                         | )0  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | Applications                                                                                                                            | 63  |

| 2.14 | Prediction Accuracy of different Prefetching mechanisms for Mediabench, Etch                                                            |     |

|      | and Pointer Intensive benchmark Suites. Legends are same as in Figure 2.13.                                                             | 64  |

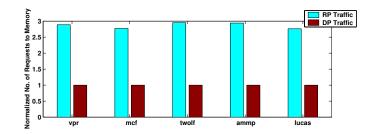

| 2.15 | Normalized Memory Traffic (in terms of requests) generated by RP and DP                                                                 |     |

|      | with respect to DP. In each application, the left bar is the traffic for RP, and the                                                    |     |

|      | right bar is for DP. The bar for DP is with direct-mapped table of $r = 256$ and                                                        |     |

|      | $s = 2. \ldots $ | 71  |

| 2.16 | Influence of Prediction Table Parameters on DP accuracy                                                                                 | 73  |

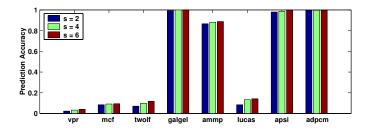

| 2.17 | Impact of number of slots(s) on DP accuracy( $r = 256, b = 16$ )                                                                        | 74  |

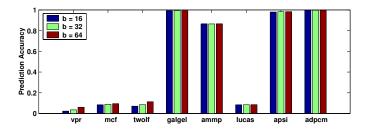

| 2.18 | Impact of Prefetch Buffer Size (b) on DP accuracy( $r = 256, s = 2$ )                                                                   | 75  |

| 2.19 | Influence of different TLB sizes on DP Accuracy( $r = 256, b = 16, s = 2$ )                                                             | 76  |

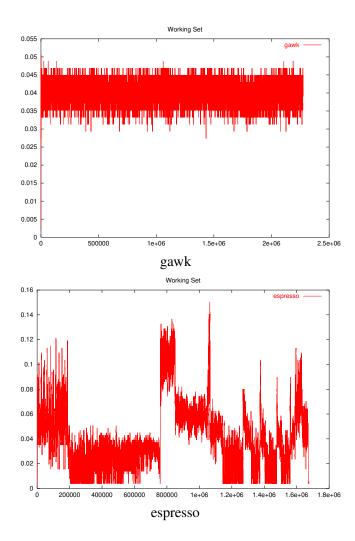

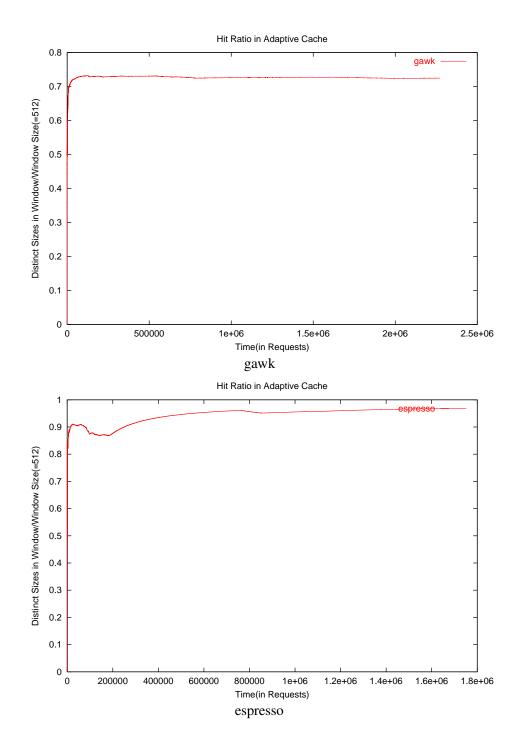

| 3.1  | Number of distinct sizes in a window of 512 for espresso and gawk                                                                       | 87  |

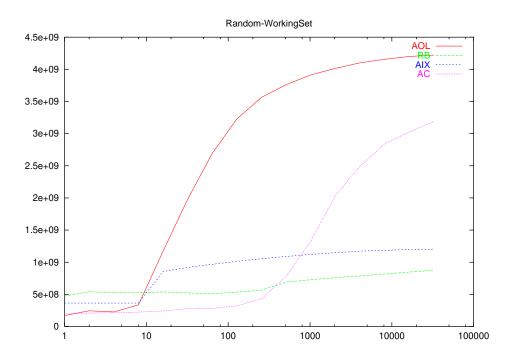

| 3.2  | Performance of various components for the varying working- sets                                                                         | 96  |

| 3.3  |                                                                                                                                         | 97  |

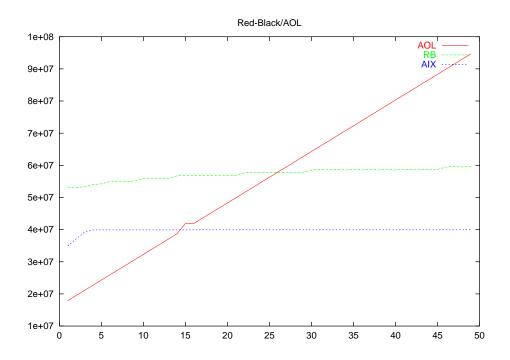

| 3.4  | Graph showing the response time of RB and AOL - AOL is a better than AIX                                                                |     |

|      | for $n \leq 15$ and RB for $n \leq 25$                                                                                                  | 100 |

| 3.5  | Hit Rate in the Adaptive Cache                                                                                                          | 102 |

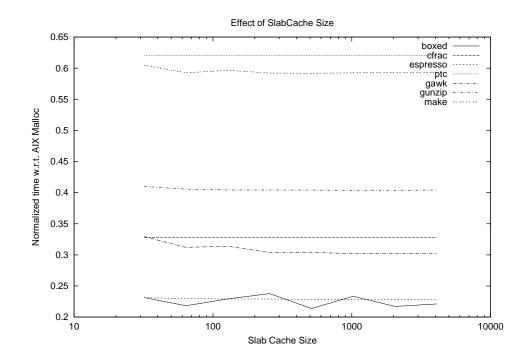

| 3.6  | Effect of Slab Cache size on the performance                                                                                            | 108 |

| 4.1  | Linux Page Management Policy                                                                                                            | 114 |

| 4.2  | Summary of various parameters in the Linux VMM                                                                                          | 123 |

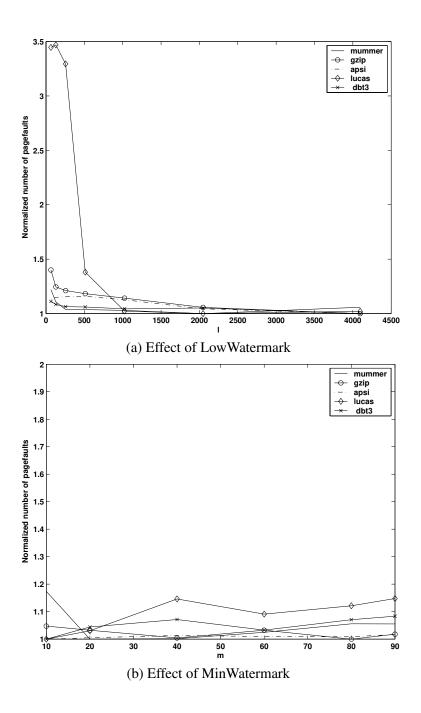

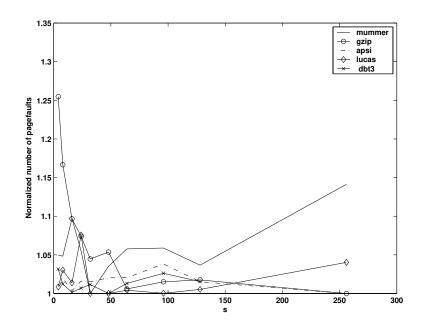

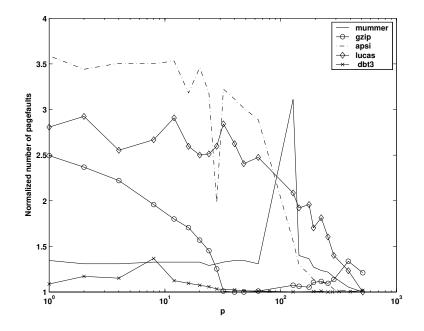

| 4.3  | Figure showing the effect of LowWatermark and MinWatermark                                                                              | 126 |

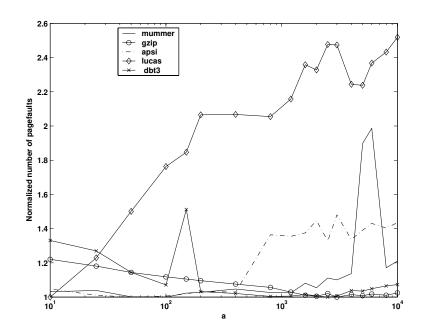

| 4.4 | Figure showing the effect of ActiveInactiveRatio on applications | 131 |

|-----|------------------------------------------------------------------|-----|

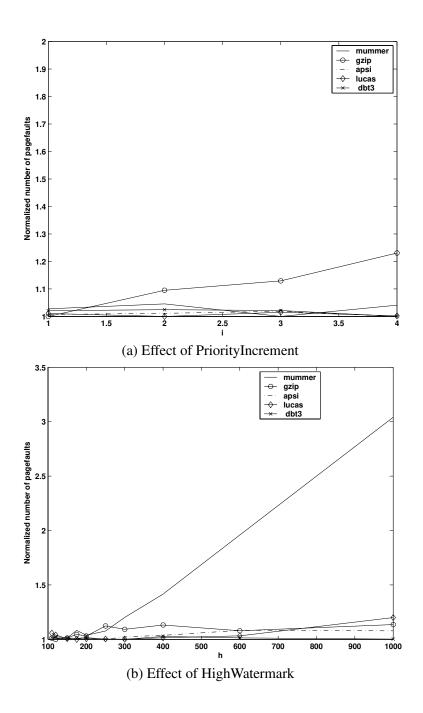

| 4.5 | Figure showing the effect of PriorityIncrement and HighWatermark | 133 |

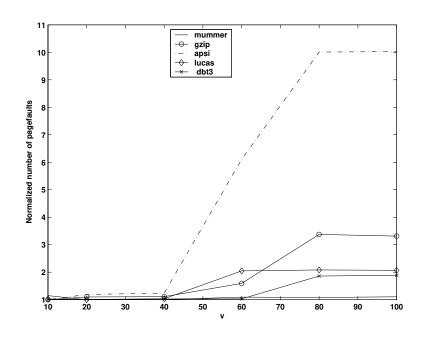

| 4.6 | Figure showing the effect of VMSwappiness                        | 135 |

| 4.7 | Figure showing the effect of Swap Cluster                        | 144 |

| 4.8 | Figure showing the effect of Page Cluster                        | 144 |

## Acknowledgments

It has been a pleasure and an honor doing my PhD at Penn State. Looking back, I am glad I did my PhD here and my heart is filled with gratitude for all those who made it happen. I always believed that there is Divine Grace behind everything we do. My gratefulness for this Grace, which I know in the form of *Guru* (or Baba) cannot be expressed in words.

I am deeply thankful to my advisor Dr. Anand Sivasubramaniam for everything he has given me in the last five years. I owe all my success to him. He is a great researcher, a perfect mentor and above all, a great friend. His encouragement, persistence, aggression and enthusiasm have been the driving force for me to learn, develop skills and accomplish. Of course, there have been moments of complain and mis-understanding from my side, but in retrospect, I only feel more grateful for his understanding, maturity and foresight. His technical expertise in analyzing intricacies and his sharp intellect where he saw through things which I could not, have taught me a lot. His criticism was perfect. It made me progress. He also played a major role in placing me at IBM T. J. Watson Research Center. More than anything else, I feel fortunate because I got to work with someone who really cares about me. I hope to collaborate with him in future and seek his advice when necessary.

The three summers that I spent in the IBM T. J. Watson Research Center have been a learning experience for me. I would like to thank my mentor, Dr. Ekanadham Kattamuri, for it. In many ways, he has changed my perspective on research from a grass-root level. Our collaboration has gone well beyond three summers and I hope to continue this with him.

Next, my gratitude goes to my referees: Dr. Mary Jane Irwin, Dr. Natarajan Gautam, and Dr. Raj Acharya, who took time from their busy schedules, writing strong recommendation letters for me. Their strong support has made my job search much easier.

I would also like to thank the members in my Ph.D committee: Dr. Mary Jane Irwin, Dr. Mahmut Kandemir, Dr. Natarajan Gautam and Dr. Ekanadham Kattamuri. They gave me a lot of valuable comments on my thesis work, which helped me refine my dissertation.

In the last five years, I realised that during the process of a PhD, one not only learns from one's advisors but also from one's peers. I have been extremely lucky to have a group of excellent lab-mates and house-mates who have made my stay at Penn State very colorful. Murali Vilayannur and Deepak Ramrakhyani have been amazing friends and the first persons for me to approach for anything. Shailabh Nagar, Ning An and Yanyong Zhang have helped me throughout my PhD, as seniors, to make many important decisions. Chun Liu, Sudhanva Gurumurthi, Partho Nath, and Jianyong Zhang have been really great and sweet friends, who were always ready to help. Naveen Cherukuri, Saurabh Agarwal, Ananth Indrakanti, Ashish Kulkarni and Rajdeep Pradhan have been roomies who taught me a lot.

After five years, I realise that PhD is not an achievement of a single person. There are many people that contribute to one's success - every PhD is an organizational effort. All the administrative people at Penn State, especially those from the Department of Computer Science and Engineering have played a significant role in my PhD. I am especially grateful to Vicki Keller who has been so helpful from the first day at Penn State and to Eric Prescott who has spent significant time helping me to get the right set of resources.

A very important phase of my PhD began after I did the *Art of Living* Course. There was a distinct difference in the quality of my days after Art of Living. I am very grateful to Kaushik Narayanan and Birjoo Vaishnav for making me aware of this course. Birjoo Vaishnav has been an inspiration for me as a person filled with love and one who spends his time for others. In retrospect, the highlight of my PhD is getting involved in Art of Living.

Last but not the least, I am extremely grateful to my parents and my brother. They have been with me all the five years (although I have not visited them), and encouraged me in every decision I made, even though it may be painful to them. Their unwavering encouragement and enthusiasm pulled me through hard times.

This acknowledgment list is by no means complete. There are many people not mentioned above who have contributed to my success. Whether I went through joyful moments or depressing moments, it all happened for good. I believe that I have become aware of, and hence became immune to, many ups and downs that are possible in life. I am leaving Penn State filled with confidence, enthusiasm and love to take on the rest of my life as a challenge. Now I know why this is called Doctor of Philosophy and not Doctor of Computer Science.

# Introduction

Systems today are becoming application driven. Application performance is critical in various fields like biology, genetics, military, space exploration etc. For instance, the protein folding problem that could provide a cure to Alzheimer's disease requires massive computational power and IBM is building the Bluegene system [21] in an attempt to solve this problem. Several large-scale projects in industry and academia have applications as their primary motivation today. With regard to applications themselves, two fundamental trends can be observed in their evolution: (i) Application sizes are increasing and (ii) Application complexity is increasing.

Today's applications are much larger than those from a decade ago. Common desktop applications like KDE [10], Netscape [16] or Mozilla [13] need about 20-32 megabytes(MB) of memory. High-end server applications like WebSphere [9] need a minimum of 256MB to run and a few gigabytes of memory is recommended. It is not only a question of fitting applications in the processor caches but also that of fitting them in the main memory. As the distance between the processor and memory increases, with disk access times showing few signs of improvement, optimizations to reduce the data access time by having the right data at the right time in the right level of this hierarchy become all the more important. At the same time, diversity of application working-sets can mandate different optimizations. For example, desktop applications generally fit in memory. For such applications, optimizations done in the processor memory management structures, the caches and the TLBs, can have greater impact on their performance compared to those done in the operating system. Thus, techniques to increase the performance of these onchip structures will help. On the other hand, if we consider high-end applications like DBT3 [17] or Websphere [9], the bottleneck for these applications is the disk access. Though optimizations done in the processor-memory path might help, optimizations done to manage data effectively in the main memory, thereby preventing disk accesses, will have much greater benefits. Thus, for such applications, memory management techniques employed in the operating system become more important. Therefore, due to diverse requirements of today's applications, it is necessary to provide optimizations at all levels in this hierarchy. In other words, memory management optimizations need to be done from a complete system perspective.

At the same time, phenomenal growth of computing power has also resulted in making applications more complex. Complexity has not only increased for a single application in terms of the number of lines of code, bugs, error conditions etc. [2], but also in the diversity of applications that are being developed. In fact, it is not just application complexity that has increased, but systems in general have become more complex. Today, a lot of time and effort is spent in managing systems. For instance, large companies spend about 40% of their investment in just managing systems [62, 58]. As the proliferation of the Internet continues and device complexities increase, managing systems will become an indomitable task. The goal of *Autonomic Computing* [62] is to reduce the increasing complexity of managing larger computing systems by making them self-managing. If we take a typical computer system, there are a number of variables on which performance of applications depend. For instance, the parameters within an operating system have significant effect on the application runtime. Humans cannot be expected to sit and tune such parameters for every application - this is not economical both in terms of time and cost. Thus, in the light of emerging technologies, memory management needs to be self-managing. While there are several aspects of Autonomic Computing, this thesis specifically focuses on making memory management *self-optimizing*, i.e. the ability of a system to adapt itself to the workload behavior in order to provide the best performance at anytime.

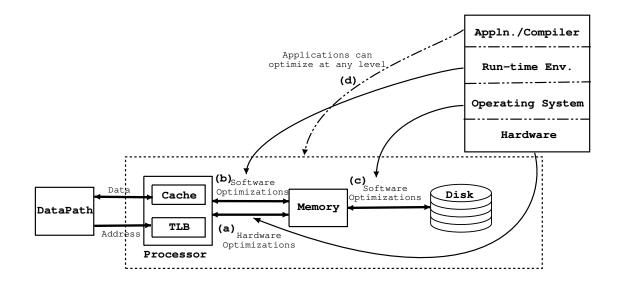

Fig. 1.1. Figure shows optimization methods for memory management.

Increasing application sizes reiterate the importance of efficient and effective memory management. Differing memory requirements of different applications imply the need for memory management optimizations to be done at all the levels. Increasing application complexity stresses the need for self-optimization. The goal of this thesis is to take a step towards making memory management self-optimizing - this being done from a complete system perspective at all the levels in the memory hierarchy without requiring applications to be modified. While one could think of writing an application by keeping the complete memory hierarchy in perspective, we do not want to burden application programmers to do this. Also, as applications become more complex, this task will become non-trivial. This thesis takes a step towards proposing adaptive mechanisms for optimizing the Memory Management System(MMS) at different levels - hardware, operating system and runtime libraries, to improve application performance.

#### **1.1 Hardware Enhancements for the TLB**

On the hardware front (shown as (a) in Figure 1.1), the caches and the TLBs are responsible for providing efficient data access and protection to the processor core. The performance of these two structures has direct implication on the application. Numerous efforts have been undertaken to improve the performance of these structures, especially for caches. Methods to improve performance of data caches include design of exclusive caches [70], adaptive caches [90], stream buffers [69], column associative caches [22] etc. Methods have also been proposed on the software side to improve the performance of caches [52, 72, 98, 40, 35]. Techniques have been proposed to improve the performance of instruction caches as well [95]. Some of these proposals have even been implemented in commercial microprocessors. Caches have also been investigated quite extensively with regard to prefetching [42, 75, 48, 108]. In all, a plethora of literature exists for caches in the past while TLBs have received much less attention. Most of the optimizations for TLBs in the past have been mainly been limited to structural optimizations like Multi-level TLBs[84] and Superpaging[104]. There has not even been a characterization study that has been undertaken for the TLBs (where as such studies have been done extensively for caches [28, 36, 60], for different kinds of workloads). Since the access time of TLB is extremely important, there has been reluctance to propose novel enhancements in case it affects the design of the critical path. Further, since this is an on-chip structure, use of elaborate hardware

to monitor and optimize the datapath reference patterns would be limited by space and power constraints.

Several previous studies [63, 94, 97, 23] have noted the importance of the TLB. Some studies report that TLB overhead could constitute as much as 40% of the execution time in extreme cases with an average overhead of 8-9% [63]. TLB overhead could be upto 80% of a kernel's computation time [94] and studies with commercial and scientific applications [97] have shown that the TLB miss rate can account for over 10% of their execution time even with an optimistic 30-50 cycle miss overhead. It has also been observed in the past [23] that TLB handler is the most frequently executed kernel service.

Keeping the current trends in mind, it is important to provide optimizations for the TLBs due to several reasons: First, the growing gap between the processor and the memory can only increase the TLB overhead in case the translation is not cached. Second, as application working-sets get larger it is difficult for the TLB to cover the working-set effectively, even with large TLBs. For instance, many of the SPEC CPU 2000 benchmarks have working sets larger than the TLB coverage provided by any of the processors today. In fact, it might even become difficult to find the translations in the cache. Third, as pipelines get deeper, overhead of software handled TLBs will increase due to the increased cost of flushing the pipelines. Therefore, the issue of improving TLB performance will continue to remain an important problem to be looked at even in future.

Before proposing enhancements, it is important to understand how applications behave and then justify the extra hardware based on the cost-benefit trade-offs. Such an approach has been used in the design and analysis of other system components (eg. [28] for caches, [100] for I/O, [111] for processors etc.), and to our knowledge there is no other prior study that has done the same for the TLBs. In our quest for a self-optimizing MMS, we begin with such a study (Chapter 2), studying numerous applications to find out what is it that applications need from the TLB, and whether we can provide it in a fashion that is not specifically tailored for an application while still dynamically adapting itself to the application characteristics. Our thorough characterization study yields several good insights into the application characteristics based on which we develop a novel TLB prefetching technique Our technique is simple, yet powerful, and it adapts to applications as they execute.

#### **1.2** Software Memory Management

Optimizations to the memory structures can also be done in software Software optimizations ((b) in Figure 1.1) for caches, which can also have an effect on the TLBs have used compiler transformations and data reorganization to enhance locality [40, 98, 72, 52]. Increasing complexity of applications (and hence that of application code) can make compiler optimizations more difficult in future. Compiler optimizations may not be possible when we do not have access to the source code. Also, most of these optimizations target static data and arrays but not dynamic memory, which is managed by the runtime environment. Many applications today spend significant amount of time in managing dynamic memory. For example common utility applications like GNU Make [6] and GNU Awk [4] spend about 5% of their runtime in dynamic memory allocation. Cfrac, a prime number factoring application, spends about 15% of its execution time in memory allocation. SPEC benchmarks twolf, vpr and SPEC JBB [18] spend about 1-3% of application runtime in memory allocation. Efficient dynamic memory allocation is a necessity for all these applications. Although operating systems ship libraries that do have allocators, applications do not trust or use them. The reason being that these allocators are much more generic than what is required by the applications and hence are not optimized for a given application. At the same time, these allocators need to be generic enough to work with any given application. In order to prevent the application slowdown using generic memory allocators, many applications today come with their own *custom allocators* e.g. The Apache Webserver [1], MySQL Database [15], Natural Language Processing Benchmark parser [18], GNU C Compiler [5] etc. As the application complexity and working set sizes increase, application writers cannot be expected to supply an efficient allocator with every application. This is not good software engineering practice, may not be feasible at times and can also result in duplication of work. Also, use of custom allocators often precludes the use of memory leak detection tools [30] and makes debugging more difficult. There are also several other disadvantages with traditional custom allocators and these have been discussed in [30] in detail. The solution rather lies in building an adaptive memory allocator that tunes itself to application behavior. As a next step in a self-optimizing MMS, this thesis proposes an allocator that *observes* incoming allocation/deallocation events and their properties and optimizes itself to the application. Before designing such an adaptive memory allocator, we first look at application allocation/deallocation characteristics. These characteristics show promise for an adaptive allocator. We then build an adaptive memory allocator and compare it with traditional allocators which are similar to custom allocators. Our results indicate that adaptivity can help reduce application runtime in many cases but can also hurt in a few. We conclude that adaptivity does not come for free. The overhead involved in monitoring application characteristics might overshadow the performance gain using adaptivity. We finally recommend an infrastructure that is a combination of our adaptive allocator and a traditional custom allocator that can reap the benefits of both.

#### **1.3** Adaptivity in the Operating System

Applications whose working-sets fit into the memory would benefit from the optimizations discussed above that are in the processor-memory path. Many high-end server applications today do not fit in memory. For such applications, disk accesses become the bottleneck and it is important to minimize the need to go to the disk. The operating system's Virtual Memory Manager (VMM) is responsible for moving the data in and out of the disk(represented by (c) in Figure 1.1) and keeping the important data in the memory. VMM is composed of two main components: the policy and the parameters of the policy. The policy determines how the pages are managed by the operating system and is typically fixed. The parameters used by the policy, on the other hand, have influence on its performance and can be varied dynamically as the system is running. Operating system developers spend a lot of time tuning these parameters. During development, these parameters are set 'intuitively' based on the developer's experience. After the systems get deployed, if the users start observing poor application performance, these parameters are again tuned after massive experimentation. It is neither possible to think of every application when fixing these parameters, nor are the same values good for all classes of applications. Developers spend days to set these parameters after hundreds of experiments. Finally, 'hooks' are provided to change these parameters while the system is running if the user wishes to. Most of the users do not have any idea about the internals of the system and do not know how to set such parameters. This motivates the need for a self-tuning system that can tune the parameters by itself when different applications are running, to deliver the best performance at any time. Such a system would adapt to different applications automatically and no external tuning would be required.

Observing application characteristics within an operating system and tuning parameters dynamically using these characteristics is a very challenging problem. Towards this goal, investigating the influence of important VMM parameters on the application execution, coming up with methods to capture application characteristics in the operating system (where not all information is available), and correlating these characteristics to the influence of parameters is a good starting point. In this thesis, we undertake a thorough characterization study and compare pure application characteristics with those that can be inferred in the OS. We show that a few parameters have significant impact on the performance of the applications and finally show how these characteristics impact performance. The insights gained in this study provide a solid background to investigate different methods for designing a self-tuning VMM.

#### 1.4 Application-controlled Memory Management

Finally, we would like to point out that memory management can also be done by applications themselves ((d) in Figure 1.1). Application developers can pass hints or use operating system/architectural features explicitly to manage the memory more efficiently. This would definitely place a large burden on the programmers. Instead, in the light of emerging system and application complexities, this thesis takes a different approach by proposing to self-optimize Memory Management at different levels - hardware, operating system and runtime environment - to save application programmers from this burden of application-level memory management.

# 1.5 Roadmap

The rest of the thesis is organized as follows: Chapter 2 goes over the issues on TLB characterization and optimization. Chapter 3 discusses the design and evaluation of the adaptive runtime memory allocator and Chapter 4 discusses the memory management issues in an operating system. Finally, Chapter 5 presents concluding remarks.

#### Chapter 2

### Hardware Enhancements for the TLB

Virtual to physical address translation is one of the most critical operations in computer systems since this is invoked on every instruction fetch and data reference. To speed up address translation, computer systems that use page based virtual memory provide a cache of recent translations called the Translation Lookaside Buffer (TLB). The TLB is usually a small structure indexed by the virtual page number that can be quickly looked up by the memory management unit (MMU) to get the corresponding physical frame number. The importance of the TLB has always been recognized, and emerging technological and application trends only reaffirm its dominance in determining system performance. Increases in instruction level parallelism, higher clock frequencies, and the growing demands for larger working sets by applications continue to make TLB design and implementation critical in current and future microprocessors.

Several studies have quantified the importance of TLB performance on system execution [66]. Anderson et al. [23] show that TLB miss handling has an important consequence on performance, and this is the most frequently executed kernel service. TLB miss handling has been shown to constitute as much as 40% of execution time [63]. and upto 90% of a kernel's computation [94]. Studies with specific applications [97] have also shown that the TLB miss rate can account for over 10% of their execution time even with an optimistic 30-50 cycle miss overhead.

| B                |                 |                     |                   |

|------------------|-----------------|---------------------|-------------------|

| Processor        | i-TLB           | d-TLB               | TLB Miss Handler  |

| MIPS R10000      | 8-entry FA      | 64-paired-entry FA  | Software          |

| Alpha 21164      | 48-entry FA     | 64-entry FA         | Software          |

| PowerPC 604      | 128-entry 2-way | 128-entry 2-way     | Hardware          |

| HP               | 4-entry Micro-T | LB for Instructions | Software          |

| PA-RISC 2.0      | 96-entry F      | A Main-TLB          |                   |

| Sun UltraSparc-I | 64-entry FA     | 64-entry FA         | Software          |

| Intel Pentium II | 32-entry 4-way  | 64-entry 4-way      | Hardware          |

| Intel Itanium    | 64-entry FA     | 32-entry level1 FA  | Hardware/Software |

|                  |                 | 96-entry level2 FA  |                   |

| AMD Athlon       | 24-Entry        | 32-Entry            | Hardware          |

|                  | level1 FA       | level1 FA           |                   |

| (Thunderbird)    | 256-Entry       | 256-Entry           |                   |

|                  | level2 FA       | level2 FA           |                   |

| AMD Athlon       | 24-Entry        | 40-Entry            | Hardware          |

|                  | level1 FA       | level1 FA           |                   |

| (Palomino)       | 256-Entry       | 256-Entry           |                   |

|                  | level2 FA       | level2 FA           |                   |

|                  | (Exclusive)     | (Exclusive)         |                   |

Table 2.1. TLBs in Commercial Microprocessors

With its importance widely recognized, the TLB has been the target for several optimizations to reduce access latency, miss rates and miss handling overheads. With regard to TLB structures themselves, there have been investigations on suitable organizations in terms of size, associativities and multi-level organizations [104, 84, 41, 25]. Superpaging is a concept that has been proposed to boost TLB coverage. The basic idea is to use a single entry to map several pages, thereby increasing the number of translations within the TLB. Hardware and software techniques for supporting this mechanism have come under a lot of scrutiny [104, 105, 103, 56, 88, 93]. Most prior work in TLB optimizations has targeted lowering miss rates or miss handling costs. It is only recently [97, 89, 26] that the issue of prefetching TLB entries to hide all or some of the miss costs has started drawing interest. Many research findings on TLBs have also made their way into commercial offerings. Today's microprocessors exhibit a wide range of TLB organizations and miss handling capabilities as is shown in Table 2.1. A very nice survey of several of these TLB structures can be found in [65]. In all, a good deal of research has been undertaken on TLB design and evaluation. However, to our knowledge, there has not been any study looking at characterizing the TLB support that is required from an application's perspective. At the same time, different studies have used different workloads to evaluate their designs/improvements, and the lack of a common ground makes a uniform comparison difficult. Further, one may ignore one or more issues when optimizing any particular detail, and such omissions can play an important role in the effectiveness of the optimizations. For instance, in the recent study on prefetching benefits [97], it is not clear if there is a reasonable window of chance for performing the prefetching. It is thus essential to uniformly examine a wide range of application characteristics at the same time (from an application's perspective) to gain better insights on:

- How can TLB structures/organization be optimized to reduce misses?

- How much scope is there to benefit from superpaging?

- Can we use the program's static code structure and/or dynamic instruction stream to trigger optimizations?

- Would the flexibility provided by software TLB management<sup>1</sup> offset the higher overheads of miss handling compared to a hardwired approach?

- How well suited are applications to prefetching TLB entries? Which prefetching techniques should be employed, and under what circumstances?

- Do we have a large enough window to benefit from prefetching? If not, what other techniques should we employ for latency tolerance/reduction?

Characterizing the behavior of an application is crucial in any systems design endeavor as many application-driven studies have shown [67, 47, 46]. Application characteristics can specify what is really important from an application's perspective, identify bottlenecks in the execution for a closer look, help evaluate current/proposed designs with real workloads, and even suggest architectural/OS enhancements for better performance (in fact, an examination of some of our characterization results have really led to the development of a new TLB prefetching mechanism called Distance Prefetching [73]) While there have been characterization efforts in the context of other processor features, caches [46], I/O and interconnects, this issue has not been looked at previously for TLBs.

<sup>&</sup>lt;sup>1</sup>We would like to differentiate between the terms software TLB management and software TLB handling in this thesis. We use the latter to denote that the miss handling is done by the software i.e. the operating system, and the former term is used to denote more sophisticated software that can control placement, pinning and replacement of TLB entries. While many current systems provide software miss handlers (see Table 2.1), software TLB management has not been investigated extensively.

Towards addressing this deficiency, this thesis first sets out to examine the different characteristics of applications from the SPEC2000 suite that affect TLB performance to answer many of the questions raised above. The SPEC2000 [45, 61] suite contains 26 candidate C, C++ and Fortran applications for CPU evaluations, that encompass a wide spectrum of application domains containing interesting and important problems for several users. We have used all the applications from this suite in this study to quantify their TLB behavior for different configurations, but focus specifically on those incurring the highest miss rates for the characterization effort. We limit ourselves to d-TLB (only data references) in this study since data references are usually much less well-behaved than instructions in terms of misses (i-TLB miss rates in our experiments are very low) Several other studies have also focussed primarily on data misses [97].

#### 2.1 Related Work

TLB design, implementation and management has always been and continues to be the target for different optimizations because of its presence in the critical path of program execution. As was mentioned earlier, many studies [43, 65, 23, 63, 94] have pointed out the importance of the TLB and the necessity of speeding up the miss handling process.

Several studies [104, 65, 84] have looked at hardware TLB structures/organization and their impact on system performance in terms of capacity and/or associativity. While some of these have focussed on single (monolithic) TLBs, there have been studies which have investigated the benefits of multi-level TLBs [41, 25]. There are also implementations of multi-level TLBs in commercial processors such as MIPS R4000, Hal's SPARC64, IBM AS/400 PowerPC, AMD K-7 and Intel Itanium. With instruction level parallelism (ILP) being exploited by most current processors, there is a need a provide multi-ported TLBs to allow several concurrent instruction streams to access the TLB. Austin and Sohi [25] show how multiple ports can impact access latencies, and argue for interleaved and multi-level designs. They show that combining requests at the TLB access port (called piggybacking), to reduce the number of ports, can provide significant benefits.

TLB miss handling costs need to be kept extremely low for good performance. Commercial processors use either a hardware mechanism or a software mechanism to fill the TLB on a miss. Unlike hardware managed TLB misses which have a relatively small refill penalty, handlers for software managed TLBs need to be carefully crafted to both reduce misses as well as reduce the miss handling costs. Nagle et al. [84] study the influence of the operating system on the software managed MIPS R2000 TLB, and investigate the impact of size, associativity and partitioning of TLB entries (between OS and application). They point out that the operating system has a considerable influence on the number and nature of misses. Bala et al. [26] focus in specifically on interprocess communication activities, and illustrate software techniques for lowering miss penalties on software managed TLBs.

Superpaging is another well investigated technique to boost the coverage of the TLB and better utilize its capacity [104, 105, 103, 55]. Studies have looked at hardware and operating system support for providing superpage translations in the TLB. Recent work in this area [55] is investigating memory controller support for re-mapping pages so that there is more scope for creating superpage entries (without incurring the overheads of copying).

| Application | i-TLB Missrate       | Application | i-TLB Missrate       | Application | i-TLB Missrate        | Application | i-TLB Missrate        |

|-------------|----------------------|-------------|----------------------|-------------|-----------------------|-------------|-----------------------|

| galgel      | $1.4 \times 10^{-8}$ | mcf         | $4.4 \times 10^{-9}$ | ammp        | $7.3 \times 10^{-9}$  | apsi        | $2.46 \times 10^{-7}$ |

| vpr         | $7.2 \times 10^{-9}$ | lucas       | $1.1 \times 10^{-8}$ | twolf       | $1.28 \times 10^{-8}$ | facerec     | $8.8 \times 10^{-8}$  |

| art         | $3 \times 10^{-9}$   | bzip2       | $4.4 \times 10^{-9}$ | parser      | $8.28 \times 10^{-8}$ | vortex      | $2.74 \times 10^{-4}$ |

| crafty      | $1.8 \times 10^{-8}$ | swim        | $1.3 \times 10^{-8}$ | applu       | $5.75 \times 10^{-8}$ | gcc         | $1.08 \times 10^{-4}$ |

| mesa        | $3.6 \times 10^{-8}$ | mgrid       | $1.5 \times 10^{-8}$ | equake      | $5.55 \times 10^{-9}$ | perlbmk     | $3.35 \times 10^{-5}$ |

| wupwise     | $1.2 \times 10^{-8}$ | sixtrack    | $8.8 \times 10^{-8}$ | gap         | $2.34 \times 10^{-8}$ | fma3d       | $3.42 \times 10^{-5}$ |

|             |                      | gzip        | $5 \times 10^{-9}$   | eon         | $6.8 \times 10^{-8}$  |             |                       |

Table 2.2. i-TLB Missrates for all the applications using a 64-entry, 4-way set-associative i-TLB for 7 billion instructions

#### 2.2 Experimental Setup

We have studied the TLB behavior for all 26 applications from the SPEC2000 suite. The benchmarks were compiled on an Alpha 21264 machine using Compaq's cc V5.9-008, cxx V6.2-024, f77 V5.3-915 and f90 V5.3-915 compilers using -O4(-O5 for Fortran) optimization flags which enable loop unrolling, software pipelining using dependency analysis, vectorization of some loops, inline expansion of small functions etc. All the simulations are conducted using the SimpleScalar-3.0 toolset [34] that simulates the Alpha architecture. Since we are mainly interested in the TLB behavior, we have modified sim-cache component of this toolset, by adding a TLB simulator that traps all memory references. sim-cache does a functional (not a cycle-by-cycle) simulation of instructions, and we only examine the memory references for the d-TLB investigation. While there could be some possible effects due to instructions retiring in a different order than that with a cycle accurate simulator, we do not feel that this will substantially change the results given in this thesis since we usually find that TLB misses are reasonably spaced to affect the relative ordering of the misses. We also found that differences in what gets replaced is also not significantly affected by the coarser simulation granularity.

As was mentioned earlier, we are only examining the data references (d-TLB). Table 2.2 shows the i-TLB miss rates which are very low for these applications. Some studies have pointed out the influence of the OS on TLB behavior [84]. However, similar to what many other studies [97, 41] have done, in this thesis we examine only application TLB references(we do not simulate the OS) since our focus is more on investigating application level characteristics. Issues about the interference between application and OS TLB entries, or reserving some entries for the OS are not considered here (we understand that these issues can and have been shown to have a considerable influence on TLB performance). The effect of coexisting applications and context switching is not considered, i.e. TLB fills after a context switch. One could perhaps think of the TLB being saved and restored at context switches to capture purely application effects. Simulations have been conducted with different TLB configurations - sizes (64, 128, 256, and 512 entries), and associativities (full, 4-way and 2-way) and we assume a page size of 4KB. We do not consider the effect of page faults on TLB behavior (the entry needs to be invalidated on a page replacement), since we believe that page faults are much less frequent than TLB misses to have a meaningful influence. Further, all these applications take less than 256MB of space, which can be accommodated in most current systems.

Simulation of these benchmarks is very time-consuming as has been pointed out by others as well [87, 37]. In fact, the recent study on quantifying cache performance for these benchmarks mentions that it *takes 30 CPU years*, and their study used several workstations over several days to conduct this evaluation. In this study, we do not attempt to execute these applications to completion. Rather, we have examined the TLB behavior over *five billion instructions after*  *skipping the first two billion instructions* of the execution for each application. We believe that this ignores the initialization/start-up properties of the application, and captures the representative facets of the main execution. The simulated instructions constitute around 1%(parser)-12%(mcf) of the application run time [37].

For gzip/bzip2, perlbmk and vortex the input files that we used are input.source, diffmail.pl and lendian3.raw respectively.

The term, *miss rate*, which is often used in the following discussion is defined as the number of TLB misses expressed as a percentage of the total number of memory references.

#### 2.3 Characterization Results

#### 2.3.1 What is the impact of TLB structure?

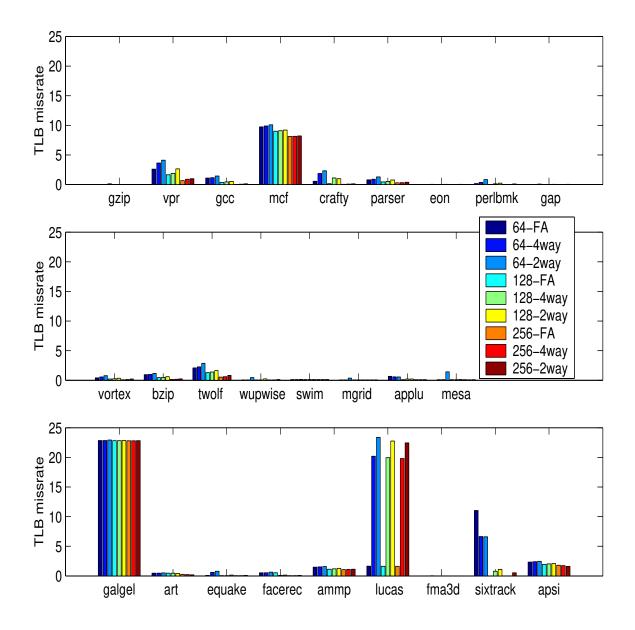

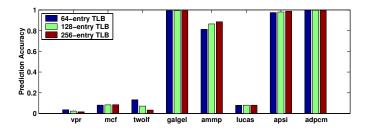

As a starting step, we first examine the overall TLB performance for the different applications for 9 different TLB configurations (combinations of three sizes - 64, 128, and 256, and three associativities - fully associative (FA), 4-way and 2-way). The resulting miss rates are shown in Figure 2.1, and we observe the following:

• A diverse spectrum of TLB characteristics is exhibited by these applications. We have applications such as gzip, eon, perlbmk, gap, vortex, wupwise, swim, mgrid, applu, mesa, art, equake, facerec and fma3d which incur few TLB misses. On the other hand, applications such as vpr, mcf, twolf, galgel, ammp, lucas, sixtrack and apsi have a significant number (greater than 1%) of TLB misses (at least in some of the configurations). TLB miss penalties can be quite significant. For instance, the IBM PowerPC 603 that handles misses in software, incurs a latency of 32

Fig. 2.1. Figure showing TLB miss rates of all the SPEC2000 applications with different TLB sizes (64, 128, 256) and three different associativities (2-way, 4-way and FA).

cycles just to invoke and return from the handler, leave alone the cost of loading the TLBs [53]. Even if we optimistically assume a TLB miss penalty of 30 cycles, a 1% TLB miss rate can result in significant overheads - around 10% of the overall execution time for a CPI of 1.0. Other studies have pointed out that TLB miss handling overheads can be even higher [55, 97, 56]. Applications such as bzip, gcc, crafty and parser fall between these extremes. We focus on the six applications which incur higher TLB miss rates.

- Even though making the TLB larger helps, the benefit is not very significant in most of these applications except vpr, twolf and mcf.

- Applications such vpr, mcf, twolf, lucas and apsi are more influenced by the associativity than the others.

These results reiterate the importance of the TLB in the execution of these applications. Nearly a fourth of the SPEC2000 suite have reasonably high TLB miss rates to be affected by its miss penalty. While capacity and associativity do help in cases, they are not the universal solutions to address the TLB bottleneck.

#### 2.3.2 Will a multi-level TLB help?

Processors, such as the Itanium IA-64 (32-entry L1, 96-entry L2), AMD Athlon (32-entry L1, 256-entry L2) etc. provide Multi-level TLB structures, instead of a single monolithic TLB, i.e. lookup in a smaller first level TLB, and only on a miss there do we go to the second level TLB. With a smaller first level TLB, overall TLB lookup time can become much lower as long as we have good hit rates in the first level. Performance of 2-level TLBs has been conducted by others [41], but its benefit for SPEC2000 workloads has not been investigated to our knowledge.

An in-depth investigation of the impact of multi-level TLBs requires varying numerous parameters for each of the levels. Rather than undertake such a full factorial experiment, we limit our study to a 2-level TLB with a 32 entry fully associative 1st level and a 96 entry fully associative 2nd level that is similar to the Itanium's(IA-64) structure. We also assume that the 2-level TLB obeys the containment property(whatever is in the first level is duplicated in the second level). Table 2.3 shows the hit and miss rates with this 2-level structure for the applications.

| Application | 1 <sup>st</sup> Leve | l-1 TLB |       |        | Overall Miss Rate | Monolithic TLB |        |

|-------------|----------------------|---------|-------|--------|-------------------|----------------|--------|

|             | Hits                 | Misses  | Hits  | Misses |                   | Hits           | Misses |

| ammp        | 98.07%               | 1.93%   | 38%   | 62%    | 1.2%              | 98.87%         | 1.13%  |

| mcf         | 89.5%                | 10.5%   | 11.2% | 88.8%  | 9.24%             | 91.01%         | 8.99%  |

| twolf       | 96.57%               | 3.43%   | 53.2% | 46.8%  | 1.60%             | 98.71%         | 1.29%  |

| vpr         | 94.5%                | 4.5%    | 56.6% | 43.4%  | 1.95%             | 98.36%         | 1.64%  |

| lucas       | 98.33%               | 1.67%   | 2%    | 98%    | 1.64%             | 98.37%         | 1.63%  |

| apsi        | 97.39%               | 2.61%   | 12.6% | 87.4%  | 2.28%             | 98.04%         | 1.96%  |

| galgel      | 77.1%                | 22.9%   | 0.05% | 99.95% | 22.8%             | 77.2%          | 22.8%  |

Table 2.3. Hit and Miss Rates for the 2-level TLB configuration. Table shows the hits and miss rates for each of the 2-levels as a percentage of the number of references to that level, as well as the overall miss rate which is the percentage of references that do not find a translation in either of the levels. Also shown are the miss rates for a single monolithic TLB of the same size.

To study the impact of a hierarchical TLB, we compare these results with that of a single monolithic TLB of the same size (32 + 96 = 128 entries) in Table 2.3. It is to be expected that the 2-level TLB is making less effective use of the overall space because of the containment property and as a result we do find slightly higher miss rates for the seven applications (especially twolf, vpr, apsi and mcf). On the other hand, the benefit of a multi-level TLB would be felt due to

the much lower access time of the 1st level TLB and the avoidance of accessing the second level - which is inturn determined by the miss rates for the 1st level TLB.

Assume that the access time for a single monolithic TLB (i.e. 128 entry in this situation) is a. Let the access time for the 1st and 2nd level TLBs in the hierarchical alternative be  $a_1$  and  $a_2$  respectively. Let us denote the miss fraction of the monolithic TLB, the 1st level and 2nd level of the hierarchical TLB to be  $m, m_1$ , and  $m_2$  respectively. Also, let the cost of fetching a translation that is not in the TLB be denoted by C. Then, the cost of translating an address in the monolithic structure ( $C_m$ ) is calculated by

$$C_m = a + m \times C \tag{2.1}$$

The cost of translating an address in the 2-level TLB  $({\cal C}_s)$  is given by

$$C_s = a_1 + m_1 \times (a_2 + m_2 \times C) \tag{2.2}$$

The 2-level TLB is a better alternative when

$$a_1 + m_1 \times (a_2 + m_2 \times C) < a + m \times C$$

(2.3)

i.e.,

$$m_1 < \frac{a - a_1 + m \times C}{a_2 + m_2 \times C} \tag{2.4}$$

Actual access times for associative memories of different sizes are hardware sensitive and fairly accurate models have been developed. We use the model described in [82]. According to this model, access times for 32, 96 and 128-entry TLBs would approximately be 2.7ns, 2.9ns and 3.0ns respectively. Plugging in these values and assuming an optimistic 30 cycle miss penalty(C = 30), we find that the miss rate ( $m_1$ ) in the first level TLB has to be less than 2.97%, 10.15%, 4.05%, 4.97%, 2.44%, 3.04% and 21.71% for ammp, mcf, twolf, vpr, lucas, apsi and galgel respectively. If we compare these numbers with the actual miss rates in the 1st level TLB in Table 2.3(column 3), multi-level structure is definitely a better choice for ammp, twolf, vpr and apsi. For mcf and galgel, the choice is questionable since the difference in miss rate is not significant (and we have used a very optimistic 30 cycle miss penalty). It is only for lucas that level-2 TLB does not do as well.

#### 2.3.3 Can we improve TLB coverage? (Superpaging)

The previous set of results showed how much we can gain by improving the structure (i.e. capacity and associativity) of the TLB, and these gains are obtained with an increase in hardware complexity. The recent trend [104] to improve performance without significantly increasing hardware costs is through the concept of superpaging. TLBs that support superpaging use a single entry for translating a set of consecutive virtual pages - the number of pages for a single entry is typically a power of two - as long as these pages are located physically contiguous as well. As a result, pages that are accessed at around the same time and which are adjacent to each other virtually can share the same TLB entry, thus freeing up slots for other translations (to improve TLB coverage).

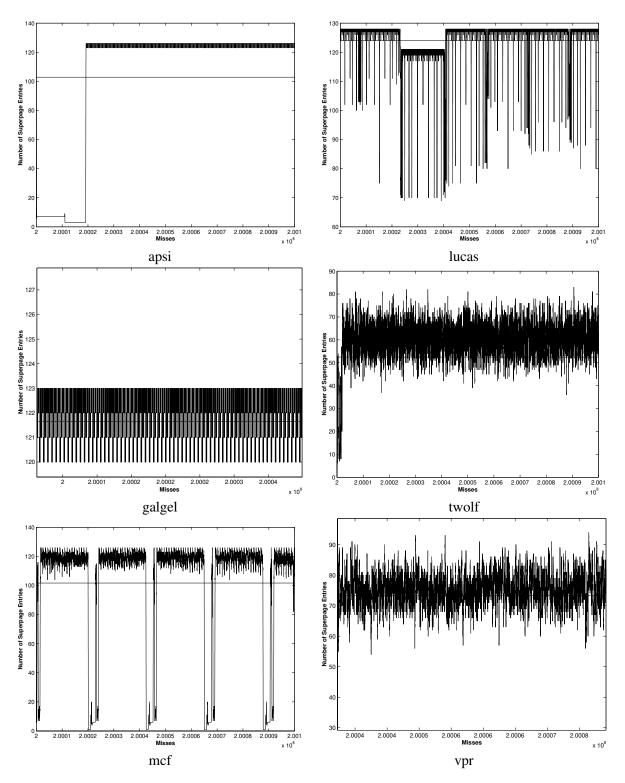

To study the potential benefits of superpaging for these applications, we next examine the contents of the TLB during the course of execution. In particular, we are interested in finding out how small a TLB would suffice to hold all the translations if it supported superpaging. At every

Fig. 2.2. Figure showing what size TLB would suffice when we combine contiguous virtual page translations with superpage entries. A 128 entry fully associative TLB is used.

miss (since TLB changes only on a miss), we examine all the TLB entries and find out how many of them can be combined into a single one (they are virtually contiguous pages). The number of resulting entries is plotted in Figure 2.2 during the course of execution (in terms of the misses in the *x*-axis). It should be noted that we are not restricting ourselves to a power of two and are assuming that the operating system will automatically allocate these virtually contiguous pages in contiguous physical locations, since our goal here is to examine the potential of superpaging from an application perspective. For better clarity, only a small window of the execution is plotted (similar execution is seen over a much larger window).

We find quite different behaviors across the applications. Applications like lucas, mcf, galgel and apsi may not benefit much from superpaging. These applications require at-least around 100 TLB entries on the average without too much scope for combining these entries. Provisioning superpage support may not show much improvement in the performance while adding hardware complexity. On the other hand, applications like ammp, twolf and vpr show the potential to benefit from superpaging mechanisms. Of these, the working set in ammp at any time can be covered by just a handful of superpage entries (since it just sequentially scans a lot of data).

#### 2.3.4 Where are the Misses Occurring?

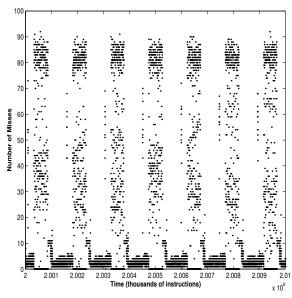

We move on to examining how the TLB misses are distributed over the execution of the program. This can help us identify hot spots in the execution that are worth a closer look for optimizations. Dynamically chosen/triggered optimizations based on different phases of the execution may perhaps be beneficial, if we do find well-defined phases.

(a) TLB misses as the application is executing(for mcf). x axis denotes the number of instructions executed in thousands, and y axis denotes the number of misses for every thousand instructions.

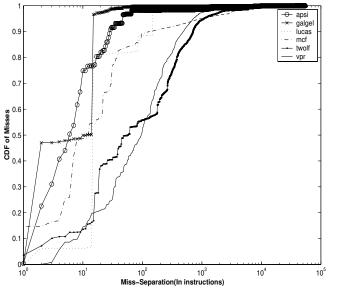

(b) Cumulative Density Function (CDF) of miss separation/interval. x-axis shows the number of instructions between successive misses in increasing order, and y-axis denotes the fraction of misses that have miss separations of at most this many instructions.

Since we are working with the sim-cache version of SimpleScalar, we do not have the time stamps for the memory references and the TLB misses. Instead, we plot the TLB misses as a function of the number of executed instructions (in thousands). Note that the scale of the graph can make it look as though there are multiple y values for a given x, while this is actually not the case.

From the dynamic optimization viewpoint, mcf a candidate that shows phases of varying TLB activity as shown in the Figure 2.3.4(a). The variance over time for the others is not as significant, and dynamic triggers in those cases may not be very helpful.

## 2.3.5 How far apart are the misses temporally?

The temporal separation of misses is an important characteristic for examining possible optimizations. If most misses are fairly close to each other temporally, then mechanisms that prefetch a TLB entry based on the previous miss may not enjoy a large enough window of overlap to completely hide miss latencies. In such situations, we should explore techniques for bulk loading/prefetching TLB entries. A significantly larger window suggests that more sophisticated prefetching techniques (which may take more time) can be viable. To our knowledge, no previous work has looked at the temporal separation of TLB misses previously. Figure 2.3.4(b) shows the cumulative density distribution of temporal miss separations (i.e. the y-axis shows the fraction of misses that are separated by at most a given value on the x-axis), where the separations are expressed in terms of instructions. A steep curve indicates that more misses have very short temporal separations.

For nearly all applications, a large portion of misses are separated by at most 30-50 instructions. For instance, ammp, galgel and apsi have over 90% of misses separated by

less than 50 instructions. mcf also has small temporal separation with around 70% of misses falling within 50 instructions. Only lucas, twolf and vpr have less steep curves. In some applications (lucas and galgel), a few miss-distances dominate the execution, suggesting that the TLB misses are occurring very periodically/regularly.

These results provide insight on the constraint window that prefetch mechanisms need to operate under. As CPIs get smaller (with higher ILPs) and processor speeds increase (making memory from where the TLB entries are fetched an even bigger problem), this window can shrink even further.

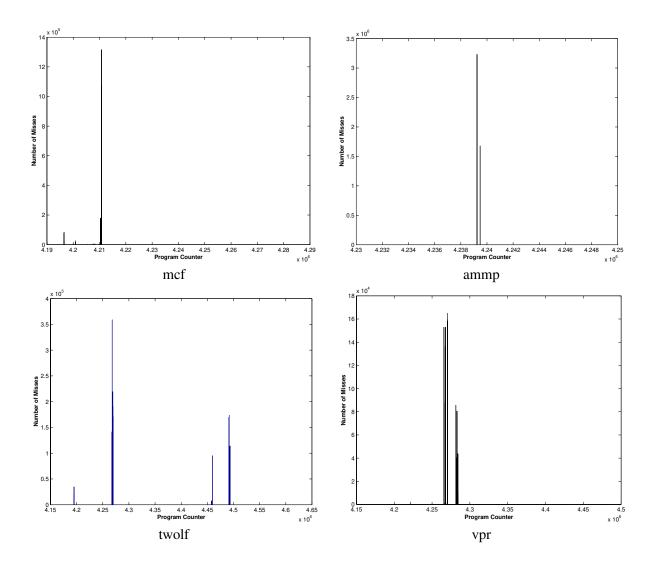

#### 2.3.6 Where are the misses occurring? - Static

If there are not very well demarcated phases of execution to trigger actions dynamically based on the phase, then it may perhaps be more rewarding to examine the (static) structure of the application programs to find out where compiler or user-directed optimizations need to concentrate on. To identify the points in the program contributing to the TLB misses, we plot the number of data TLB misses incurred by each program counter (PC) value in Figure 2.3. Overall, we find that there are only a handful of instructions that contribute to the bulk of TLB misses. These memory reference instructions are typically called repetitively (in a loop), and in the following discussion we briefly go through each application describing the points in the program corresponding to these instructions.

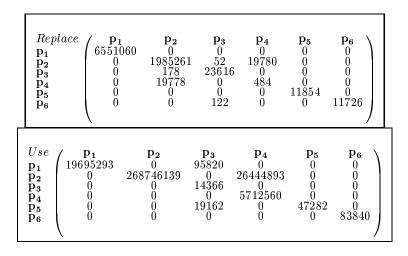

### 2.3.7 How do procedure calls influence TLB behavior?

Another possible piece of information that may be useful is how the dynamic procedure activations are affecting TLB performance. Just as context switches are wiping out locality

Fig. 2.3. PC Values Incurring TLB Misses

аттр

|                                                                                                                                                           | $\begin{array}{c} Replace \\ P_1 \\ P_2 \\ P_3 \\ P_4 \\ P_5 \\ P_6 \end{array}$                       | $\left(\begin{array}{c} \mathbf{p_1} \\ 4214667 \\ 37629 \\ 0 \\ 123 \\ 0 \end{array}\right)$      | $\begin{array}{cccc} 37632 \\ 0 \\ 0 \\ 23 \\ 0 \\ 0 \end{array}$                       | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                             | $\begin{smallmatrix}&0\\&0\\&0\\18922\end{smallmatrix}$                | $ \begin{array}{c} \mathbf{p_6} \\ 0 \\ 0 \\ 0 \\ 94 \\ 0 \\ 679 \end{array} \right) $           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Use<br><b>p</b> <sub>1</sub><br><b>p</b> <sub>2</sub><br><b>p</b> <sub>3</sub><br><b>p</b> <sub>4</sub><br><b>p</b> <sub>5</sub><br><b>p</b> <sub>6</sub> | $\left(\begin{array}{c} \mathbf{p_1} \\ 17515172 \\ 25086 \\ 0 \\ 0 \\ 212 \\ 0 \\ \end{array}\right)$ | $\begin{array}{c} {\bf p_2} \\ 15353856 \\ 1680896 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{array}$ | $\begin{array}{c} {\bf p_3} \\ 659276 \\ 0 \\ 15744440 \\ 3 \\ 0 \\ 0 \\ 0 \end{array}$ | $\begin{array}{c} {\bf p_4}\\ 218923\\ {}_{0}\\ 0\\ 10446698\\ 0\\ 0\end{array}$ | $\begin{array}{c} {\bf P5}\\ 0\\ 0\\ 0\\ 13581567\\ 12788 \end{array}$ | $\left(\begin{array}{c} \mathbf{p_6}\\ 364857\\ 0\\ 0\\ 37629\\ 0\\ 13983648 \end{array}\right)$ |

galgel

| $\begin{array}{c} Rep \\ p_1 \\ p_2 \\ p_3 \\ p_4 \\ p_5 \\ p_6 \end{array}$ | place            |                                              | $\mathbf{p_1} \\ 16029 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ $ | $\begin{array}{c} \mathbf{p}_{2} \\ 2 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{array}$ |                                                     | - 0<br>0<br>0<br>0<br>0<br>0                               | 4 P<br>0<br>0<br>0<br>0<br>0<br>0<br>0                     |                                                                                 |  |

|------------------------------------------------------------------------------|------------------|----------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------|--|

| U<br>P<br>P<br>P<br>P<br>P                                                   | 2<br>3<br>4<br>5 | <b>(                                    </b> | 1<br>1880<br>)<br>)<br>)<br>)                                            | <b>p</b> <sub>2</sub><br>0<br>0<br>0<br>0<br>0<br>0                                   | <b>P</b> <sub>3</sub><br>0<br>0<br>0<br>0<br>0<br>0 | ${f p_4} \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ $ | ${f p_5} \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ $ | $\begin{pmatrix} \mathbf{p_6} \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{pmatrix}$ |  |

Fig. 2.4. Figure showing Use and Replace matrices for different procedures. Applications like galgel will not benefit from procedure based TLB allocation.

lucas

| $\begin{array}{c} Re\\ \mathbf{p_1}\\ \mathbf{p_2}\\ \mathbf{p_3}\\ \mathbf{p_4}\\ \mathbf{p_5}\\ \mathbf{p_6} \end{array}$                               | 1                                                                                              | $\begin{array}{cccc} \mathbf{p_1} & \mathbf{p_2} \\ 4568 & 0 \\ 28 & 13547. \\ 0 & 115 \\ 0 & 2 \\ 0 & 3 \\ 0 & 0 \end{array}$ |                                                                                             | $\begin{array}{c} {\bf p_4} \\ 3 \\ 0 \\ 2 \\ 0 \\ 0 \\ 0 \\ 0 \end{array}$ |                                                                      | $     \begin{array}{c}             96 \\             3 \\             0 \\           $ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Use<br><b>p</b> <sub>1</sub><br><b>p</b> <sub>2</sub><br><b>p</b> <sub>3</sub><br><b>p</b> <sub>4</sub><br><b>p</b> <sub>5</sub><br><b>p</b> <sub>6</sub> | $\left(\begin{array}{c} {\bf p_1}\\ 88043027\\ 8\\ 1\\ 0\\ 0\\ 0\\ 0\\ 0\\ \end{array}\right)$ | $\begin{array}{c} \mathbf{p_2} \\ 6205515 \\ 116268798 \\ 1377055 \\ 1 \\ 0 \\ 0 \end{array}$                                  | $\begin{array}{c} \mathbf{p_3} \\ 12583409 \\ 0 \\ 8380144 \\ 0 \\ 0 \\ 0 \\ 0 \end{array}$ | ${f p_4}{74}\ 0\ 0\ 533\ 16\ 68$                                            | $\begin{array}{c} {\bf p_5}\\ 228\\ 0\\ 2\\ 1\\ 47\\ 75 \end{array}$ | $\begin{pmatrix} \mathbf{p_6} \\ 32 \\ 0 \\ 0 \\ 0 \\ 0 \\ 8 \end{pmatrix}$            |

| mof |  |

|-----|--|

| тсf |  |