### Transport Properties of a MoS<sub>2</sub>/WSe<sub>2</sub> Heterojunction Transistor and Its Potential for Application

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

| Citation     | Nourbakhsh, Amirhasan et al. "Transport Properties of a MoS2/<br>WSe2Heterojunction Transistor and Its Potential for Application."<br>Nano Letters 16, 2 (February 2016): 1359–1366. doi:10.1021/<br>acs.nanolett.5b04791. |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| As Published | http://dx.doi.org/10.1021/acs.nanolett.5b04791                                                                                                                                                                             |  |  |

| Publisher    | American Chemical Society (ACS)                                                                                                                                                                                            |  |  |

| Version      | Author's final manuscript                                                                                                                                                                                                  |  |  |

| Citable link | itable link http://hdl.handle.net/1721.1/11113                                                                                                                                                                             |  |  |

| Terms of Use | Article is made available in accordance with the publisher's policy and may be subject to US copyright law. Please refer to the publisher's site for terms of use.                                                         |  |  |

DSpace@MIT

See discussions, stats, and author profiles for this publication at: https://www.researchgate.net/publication/291328930

## Transport Properties of a MoS2/WSe2 Heterojunction Transistor and Its Potential for Application

#### Article in Nano Letters · January 2016

DOI: 10.1021/acs.nanolett.5b04791

Project

| CITATIONS<br>33       |                                                                                                               | reads<br>98 |                                                                                                       |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------|--|

| 4 authors, including: |                                                                                                               |             |                                                                                                       |  |

| 0                     | Amirhasan Nourbakhsh<br>Massachusetts Institute of Technology<br>33 PUBLICATIONS 359 CITATIONS<br>SEE PROFILE | 0           | Ahmad Zubair<br>Massachusetts Institute of Technology<br>23 PUBLICATIONS 147 CITATIONS<br>SEE PROFILE |  |

#### Some of the authors of this publication are also working on these related projects:

Scaling and transport properties of two-dimensional materials transistor View project

All content following this page was uploaded by Ahmad Zubair on 30 March 2017.

#

## Transport Properties of a MoS<sub>2</sub>/WSe<sub>2</sub> Heterojunction Transistor and Its Potential for Application

Amirhasan Nourbakhsh,\*<sup>,†</sup> Ahmad Zubair,<sup>†</sup> Mildred S. Dresselhaus,<sup>†,‡</sup> and Tomás Palacios<sup>†</sup>

<sup>†</sup>Department of Electrical Engineering and Computer Sciences and <sup>‡</sup>Department of Physics, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139, United States

Supporting Information

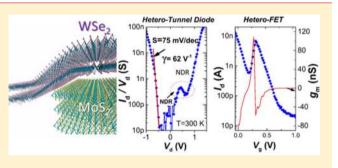

**ABSTRACT:** This paper studies band-to-band tunneling in the transverse and lateral directions of van der Waals  $MoS_2/WSe_2$  heterojunctions. We observe room-temperature negative differential resistance (NDR) in a heterojunction diode comprised of few-layer  $WSe_2$  stacked on multilayer  $MoS_2$ . The presence of NDR is attributed to the lateral band-to-band tunneling at the edge of the  $MoS_2/WSe_2$  heterojunction. The backward tunneling diode shows an average conductance slope of 75 mV/dec with a high curvature coefficient of 62 V<sup>-1</sup>. Associated with the tunnel-diode characteristics, a positive-to-negative transconductance in the  $MoS_2/WSe_2$  heterojunction transistors

is observed. The transition is induced by strong interlayer coupling between the films, which results in charge density and energyband modulation. The sign change in transconductance is particularly useful for multivalued logic (MVL) circuits, and we therefore propose and demonstrate for the first time an MVL-inverter that shows three levels of logic using one pair of p-type transistors.

**KEYWORDS:** Transition metal dichalcogenide, heterojunction transistor, band-to-band tunneling, negative differential resistance, multivalued logic

wo-dimensional (2D) crystals based on atomically thinfilms of layered semiconductors, such as the family of transition metal dichalcogenides (TMDCs), offer an attractive platform for various optoelectronic applications<sup>1-14</sup> that stems from their unique electrical, mechanical, and optical properties. The 2D crystals derived from layered crystals, such as graphene, molybdenum disulfide  $(MoS_2)$ , and hexagonal boron nitride (h-BN), have no dangling bonds on their surfaces. This is in distinct contrast to their counterpart quasi low-dimensional semiconductors, which are produced by thinning down conventional 3D crystals. The trapping sites induced by the dangling bonds in 3D crystal-derived quasi low-dimensional semiconductors are considered to be a major problem as they become trap and recombination sites. The 2D electronics can take advantage of the absence of dangling bonds to provide high quality electronic devices on an atomic scale.

The unique optoelectronic and crystal properties of atomically thin 2D crystals make them particularly attractive for heterojunction devices, which can potentially overcome some of the problems that conventional heterostructure devices face and thin 2D crystals also demonstrate novel photovoltaics and optoelectronic applications. Lee et al.<sup>8</sup> reported an atomically thin p–n vertical junction consisting of van der Waals-bonded monolayers of MoS<sub>2</sub> and WSe<sub>2</sub>. The junction shows strong rectifying electrical characteristics and photovoltaic response. Additionally, Fang et al.<sup>15</sup> demonstrated evidence of strong electronic coupling between the 2D MoS<sub>2</sub> and WSe<sub>2</sub> layers, which leads to a new photoluminescence (PL) mode in this artificial van der Waals heterostructure.

A very promising field of applications for van der Waals heterostructures of 2D crystals is as interband tunneling transistors for low power applications. Such van der Waals heterostructures can in principle benefit from atomically sharp interfaces. This is crucial for tunneling devices that suffer from impurities and interfacial defects. Moreover, the wide range of available 2D crystals allow different band-edge alignments with distinct band energy structures, ranging from the gapless graphene with a symmetric electron and hole band structure to the wide band gap semiconductors and insulators.

Several in-plane tunneling transistors based on 2D and 1D semiconductors, such as carbon nanotubes,<sup>16</sup> bilayer graphene,<sup>17</sup> graphene nanoribbons,<sup>18</sup> and so forth, have been studied. However, interlayer tunneling devices, which require tunneling in the vertical direction of 2D crystals, are still in their early stages and need further in-depth studies to obtain band structure parameters and tunneling probability along their out-of-plane direction to assess their suitability for high performance tunneling transistors. Nevertheless, some vertical field-effect transistors (FETs) comprising stacks of 2D crystals have already been reported. Britnell et al.<sup>19</sup> and Kang et al.<sup>20</sup>

Received: November 24, 2015 Revised: January 11, 2016

ACS Publications © XXXX American Chemical Society

demonstrated graphene/h-BN/graphene vertical tunneling transistors with h-BN as the tunneling barrier. This device shows quantum electron tunneling through the barrier modulated by electrostatic gating of the graphene layers.

Recently, Yan et al.<sup>21</sup> demonstrated an Esaki diode based on a heterojunction composed of a van der Waals stack of SnSe<sub>2</sub> and black phosphorus crystals separated by a native thin tunneling barrier. Their diode showed strong negative differential resistance (NDR), which confirms band-to-band tunneling in this van der Waals heterojunction. However, black phosphorus is unstable when exposed to ambient conditions and rapidly degrades.<sup>22</sup> As mentioned above, 2D crystals that have stable chemical structures, such as MoS<sub>2</sub> and WSe<sub>2</sub>, are very promising for creating ultraclean, defect-free heterointerfaces. In a pioneering work, Roy et al.<sup>23</sup> reported evidence of band-to-band tunneling in a MoS<sub>2</sub>/WSe<sub>2</sub> diode. Esaki diode characteristics were observed with NDR at temperatures below 125 K. The authors speculate that bandto-band tunneling occurs in the vertical direction.

The present work aims to provide further understanding of the transport properties in MoS<sub>2</sub>/WSe<sub>2</sub> heterojunction FETs (hetero-FET). Despite the earlier work on the optoelectronic properties of MoS<sub>2</sub>/WSe<sub>2</sub> devices, the transfer characteristic features of such devices are yet to be fully discussed in the literature. The first part of this work studies a novel feature in the transfer characteristics  $(I_d - V_g)$  and transconductance  $(g_m)$ of a generic MoS<sub>2</sub>/WSe<sub>2</sub> hetero-FET. We present an optimized device geometry to enhance the transfer characteristic parameters to be suitable for high performance electronics. We then discuss the possibility of band-to-band tunneling in this heterojunction. We answer the question whether the vertical (or out-of-plane) direction is the dominant path for band-to-band tunneling in the MoS<sub>2</sub>/WSe<sub>2</sub> heterojunction by simulating and comparing the band diagrams of the heterojunction in both the in-plane and out-of-plane directions. We also design a  $MoS_2/WSe_2$  tunnel diode based on the information obtained from the simulation and we investigate its tunnel diode characteristics. Finally, a novel application of the optimized MoS<sub>2</sub>/WSe<sub>2</sub> hetero-FET as a building block for multivalued logic is provided.

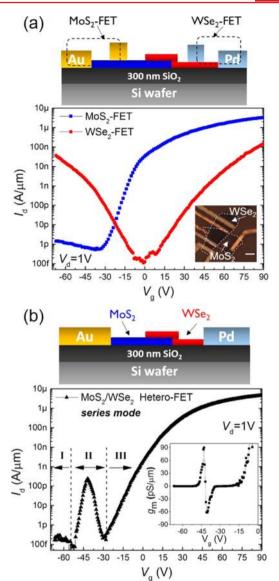

Figure 1a shows the transfer characteristics  $(I_d-V_g)$  of generic few-layer (2–4 layers, confirmed by atomic force microscopy (AFM)) MoS<sub>2</sub>- and WSe<sub>2</sub>-FETs, where  $V_g$  is the voltage applied to the substrate. The MoS<sub>2</sub> FET, consistent with previous literature, is shown to be an n-type semiconductor, while WSe<sub>2</sub> demonstrates both n- and p-type characteristics giving rise to ambipolar transfer characteristics with a relatively wide OFF-state region. The symmetry of the electron and hole conductions of the WSe<sub>2</sub> FETs can be strongly affected by the Schottky barrier at the WSe<sub>2</sub>-metal junction. High-performance ambipolar WSe<sub>2</sub>-FETs have already been reported using dissimilar low and high work function metal contacts to obtain low-resistance, ohmic contacts to electrons and holes, respectively.<sup>7,24</sup>

Figure 1b plots the transfer characteristics of a  $MOS_2/WSe_2$  hetero-FET arranged in the in-series mode. In this configuration, the  $MOS_2$  and  $WSe_2$  films form an overlapped region so that the source and drain electrodes (S/D) are in contact with the films, while leaving the overlapped region away from direct contact with the electrodes. In this configuration, electrons injected from the source to the  $MOS_2$  film have to proceed through the WSe<sub>2</sub> film in the overlapped region and continue to the drain electrode. Therefore, the  $MOS_2$  and WSe<sub>2</sub> films can

**Figure 1.** (a) Transfer characteristics  $(I_d-V_g)$  of a back-gated few-layer MoS<sub>2</sub>- and WSe<sub>2</sub>-FET. The inset shows an optical image of a typically stacked MoS<sub>2</sub>/WSe<sub>2</sub> FET. The scale bar is 5  $\mu$ m. (b)  $I_d-V_g$  of the MoS<sub>2</sub>/WSe<sub>2</sub> heterojunction FET in the series measurement mode. The inset shows the transconductance centered around the peak in region II. The schematics show the corresponding device measurement setups.

independently modulate the overall transport characteristics of the FET. As shown in Figure 1b,  $I_d - V_g$  of a back-gated in-series  $MoS_2/WSe_2$  FET shows three distinct regions. In region I ( $V_g$ < -53 V),  $I_{d}$  is very low within the noise of the measurement setup. This region is modeled by an  $i-p^+$  junction because the  $MoS_2$  is depleted, while the  $WSe_2$  shows hole accumulation. Therefore, the electron path from source to drain is blocked by highly resistive depleted MoS<sub>2</sub>, which results in low current. However, in region II (-53 V  $< V_g < -30$  V), the current increases and shows a peak with substantial current centered at -42 V with a peak-to-valley ratio in excess of 1000. This region corresponds to the condition where the MoS<sub>2</sub>- and WSe<sub>2</sub>-FET are both in their subthreshold regimes, where decreasing  $V_{\rm G}$ from -30 to -53 V leads to an exponential increase of hole conduction on the WSe<sub>2</sub> side and an exponential decrease of the electron concentration on the MoS<sub>2</sub> side toward its

Letter

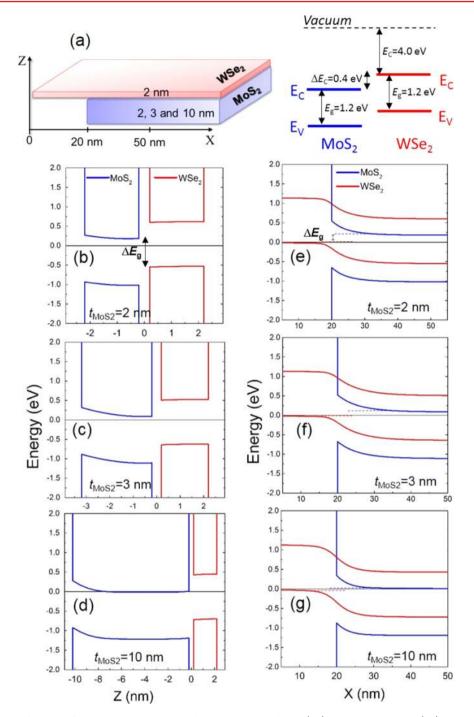

Figure 2. (a) Schematic of a  $MoS_2/WSe_2$  heterostructure and the conduction band  $(E_C)$  and valence band  $(E_V)$  positions that are used for calculation of the band diagrams. (b–d) Calculated band diagrams of  $MoS_2/WSe_2$  heterojunctions in the out-of-plane direction at the middle of the overlapped region (X = 50 nm). The WSe\_2 is 2 nm thick while the thickness of  $MoS_2$  varies as (b) 2, (c) 3 and (d) 10 nm. (e–g) In-plane band diagram of the same heterojunctions along the X-axis of the schematic in (a) at edges of the  $MoS_2$  and  $WSe_2$  films. In all the structures, the  $WSe_2$  charge is  $5 \times 10^{18}/cm^3$  and the  $MoS_2$  charge density is  $1 \times 10^{19}/cm^3$ , which are in the typical range that can be achieved by both chemical and electrostatic doping and the gap between the  $MoS_2$  and  $WSe_2$  films is 4 Å, assuming that there is a van der Waals gap between the two films. See Figure S7 of the Supporting Information for the band diagrams of 2 nm  $WSe_2/10$  nm  $MoS_2$  with different charge densities.

depletion regime. Hence, this condition can be assigned to a  $p^--n^-$  junction. The resulting current peak shows a rapid change in the gated transconductance  $(g_m = dI_d/dV_g)$  from positive to negative, as shown in the inset of Figure 1b. This feature, which occurs when one of the semiconductor layers (MoS<sub>2</sub> here) is near its depletion condition, is distinct from the negative transconductance owing to the resonance tunneling phenomena, which occurs at matched carrier densities in two-

dimensional electron gas systems (2DEGs).<sup>25–28</sup> We will then further discuss this sign-changing  $g_m$  characteristic and its possible application.

At larger  $V_{g}$ , region III, the current increases monotonically with increasing  $V_{g}$ . The current in this region is dominated by electron conduction in both the MoS<sub>2</sub> and WSe<sub>2</sub> regions, as both are in their electron accumulation regimes. Therefore, for this region, the system can be modeled by an n-n heterostructure. Figures S3 and S6 in the Supporting Information show the photoresponse of the in-series  $MoS_2/WSe_2$  FET and transfer characteristics of a  $MoS_2/WSe_2$ -FET in the parallel mode, respectively.

Similar to 2DEG bilayer heterostructures,<sup>17,29</sup> the most interesting transport regime in the MoS<sub>2</sub>/WSe<sub>2</sub> FET shown in this work is when the MoS<sub>2</sub> and WSe<sub>2</sub> layers are oppositely charged and form a p-n heterojunction. Heterostructure semiconductors are widely used for the fabrication of tunneling FETs (TFETs), which are among the most promising devices for achieving very low power operation, owing to the possibility of achieving a steep inverse subthreshold slope below the thermionic limit of 60 mV/decade. In principle, heterojunction TFETs, using two different semiconductors forming a vertical or horizontal junction, are interesting compared with homojunction TFETs, as they enable bandgap engineering to form a heterojunction with a narrower effective bandgap, which improves the tunneling probability and, thus, the drive-current that significantly depends on the bandgap. A variety of semiconductor heterostructures, especially those based on III-V compounds, have already been fabricated to make heterojunctions with the desired bandgap features. Examples include GaAsSb/InGaAs,<sup>30,31</sup> InP/InGaAs,<sup>32</sup> and GaSb/InAS.<sup>33</sup> Analogous to these conventional bilayer heterojunctions, bilayer heterojunctions of van der Waals stacked 2D materials, such as the ones studied in this work, are considered very promising for tunneling devices. As was mentioned earlier, the charge transferred between the layers can strongly modulate the energy bands of WSe<sub>2</sub> and MoS<sub>2</sub> forming a region with an abrupt, atomically precise interface that is of high importance, as nonidealities, such as defects and nonabrupt band-edges, owing to, for example, the random doping distribution case, are critical in TFET technology.

To determine the possible band-to-band tunneling paths in a MoS<sub>2</sub>/WSe<sub>2</sub> heterojunction, we calculated the band diagram of some representative MoS<sub>2</sub>/WSe<sub>2</sub> heterojunctions with different charge densities and film thicknesses. The details of the calculations can be found in the Supporting Information. Figure 2b-g shows band diagrams of the heterojunction between a 2 nm thick p-doped WSe<sub>2</sub> (equivalent to a three-layer WSe<sub>2</sub>) with charge density of  $5 \times 10^{18}$ /cm<sup>3</sup> and an n-doped MoS<sub>2</sub> with bulk charge density of  $1 \times 10^{19}$ /cm<sup>3</sup> for three different thicknesses, (i)  $t_{MoS2} = 2 \text{ nm}$ ,  $t_{WSe2} = 2 \text{ nm}$ , (ii)  $t_{MoS2} = 3 \text{ nm}$ ,  $t_{\text{WSe2}} = 2 \text{ nm}$ , and (iii)  $t_{\text{MoS2}} = 10 \text{ nm}$ ,  $t_{\text{WSe2}} = 2 \text{ nm}$  (Figure 2a shows a schematic of the MoS<sub>2</sub>/WSe<sub>2</sub> layers and the conduction band and valence band alignments used for calculation of the band diagrams). The band diagram in the transverse direction (i.e., Z) (Figure 2b-d) of the heterojunction interface shows a minimum effective band gap of  $\Delta E_{o}$ = 0.85 eV between the conduction band of WSe<sub>2</sub>,  $E_{C,WSe2}$  and the valence band of MoS<sub>2</sub>,  $E_{V,MoS2}$ , which corresponds to  $t_{MoS2} = 10$ nm,  $t_{WSe2} = 2$  nm. This is a relatively large band gap for a tunneling device compared with other proposed heterostructures that have been developed for high-performance TFETs, because the tunneling probability decreases as the effective band gap increases. In addition, the weak van der Waals interaction between the layers, owing to the random orientation of their lattices, leads to an effective vacuum potential barrier. This further suppresses the tunneling probability and therefore the tunneling current. Therefore, vertical tunneling in  $MoS_2/$ WSe<sub>2</sub> seems very unlikely. However, the band diagram along the horizontal direction (i.e., X), plotted in Figure 2e-g shows promising features. In fact, owing to the thin nature of the films,

the interaction between layers at the junction leads to substantial band bending between the overlapped and nonoverlapped regions. As expected, the band bending is stronger in the thinner film and the effective band gap  $\Delta E_{\rm g}$  strongly decreases with increasing the asymmetry of the thicknesses of the layers. In the case of 2 nm WSe<sub>2</sub>/10 nm MoS<sub>2</sub>, a small inplane  $\Delta E_{\rm g} < 50$  meV is achieved, compared with 0.85 eV in the transverse band diagram at the overlapped region. The band diagram of the 2 nm WSe<sub>2</sub>/10 nm MoS<sub>2</sub> heterojunction predicts the occurrence of NDR owing to band-to-band tunneling between the conduction band ( $E_{\rm C}$ ) of MoS<sub>2</sub> in the overlapped region and the valence band ( $E_{\rm V}$ ) of WSe<sub>2</sub> of the nonoverlapped region.

Before discussing the experimental results of the predicted tunneling performance, we would like to highlight once again that in modeling 2D materials-based heterojunctions in addition to the band alignment in the transverse direction the band structure modulation along the interface needs to be taken into account to obtain a comprehensive evaluation of the transport in any ultrathin low or moderately doped heterostructure device. This also enables the selection of suitable materials for NDR enhancement. Additionally, despite the promising features of van der Waals TMDC heterostructures the out-of-plane carriers possess heavier masses in the layered materials than the masses parallel to the layers (e.g.,  $MoS_{2}$ , in-plane mass = 0.45 m<sub>e</sub>, out-of-plane mass =1.73 m<sub>e</sub><sup>-3</sup> Additionally, the out-of-plane resistance can be orders of magnitude larger than the in-plane resistance, which is a consequence of their anisotropic nature owing to the weak van de Waals interlayer interaction compared with the strong covalent in-plane interaction between atoms. However, a comprehensive, quantitative study is required to obtain an indepth understanding of tunneling transport in both the in-plane and out-of-plane directions in 2D heterojunctions. Nevertheless, knowing that in general the tunneling transmission

probability<sup>17,35</sup> is

$$T(F) = \exp\left(\frac{-\pi (m_{\text{tunnel}}^{*})^{1/2} \Delta E_g^{-3/2}}{2\sqrt{2} \hbar q F}\right)$$

(where  $m_{\text{tunnel}}^{*}$

is the carrier effective mass in the tunneling direction,  $\Delta E_{\sigma}$  is the effective bandgap, and F is the electric field across the semiconductor body), we can anticipate that the heavier carriers in the out-of-plane direction as well as the larger band gap can dramatically decrease the tunneling probability in this direction compared with the in-plane direction. Hence, given the smaller in-plane carrier masses and band gap, the in-plane heterojunction of TMDC atomic layers, as discussed above, promises to be a practical structure for actual tunneling devices. However, one should consider that in such van der Waals heterojunctions, carriers in both horizontal and vertical directions still have to tunnel through an extra effective van der Waals barrier. However, this barrier, which can be considered as a square barrier, is thinner (<1 nm) than the tunneling distance. Therefore, the tunneling barrier height defined by the effective bandgap, remains the main crucial tunneling parameter.

Next, to evaluate the possibility of band-to-band tunneling in an in-plane MoS<sub>2</sub>/WSe<sub>2</sub> heterojunction, as suggested by the afore-discussed band diagram, we study a transistor whose channel comprises of a thickness-asymmetric ~2 nm WSe<sub>2</sub>/~10 nm MoS<sub>2</sub> stack (thicknesses confirmed by AFM measurements). For a comparison of  $I_d$ – $V_d$  of MoS<sub>2</sub>/WSe<sub>2</sub> stacks with different thicknesses, see the Supporting Information. To enhance the performance of the transistors and

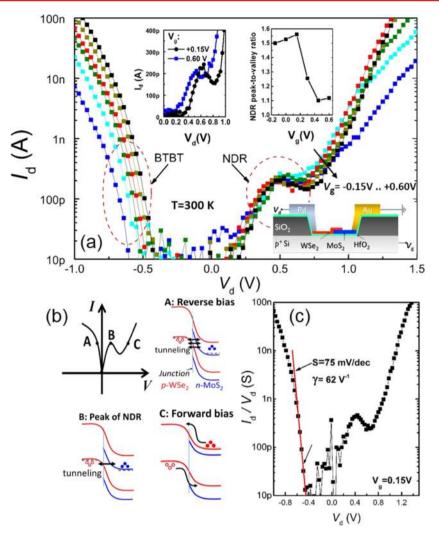

**Figure 3.** (a) Room temperature  $I_d - V_d$  of a 10 nm MoS<sub>2</sub>/2 nm WSe<sub>2</sub> transistor at different  $V_g$  values. The insets show  $I_d - V_d$  at the NDR region with a linear scale for  $V_g = +0.15$  V (black) and +0.60 V (blue) on the left and NDR peak-to-valley ratio versus  $V_g$  on the right. The schematic shows the corresponding device measurement setups. (b) Schematic band diagrams of a MoS<sub>2</sub>/WSe<sub>2</sub> junction at points A, B, and C, illustrating the three different bias regimes. (c) Conductance ( $G = I_d/V_d$ ) versus  $V_d$  at  $V_g = 0.15$  V.

improve the gate efficiency, we need to increase the gate dielectric capacitance and yet keep the gate leakage current as low as possible. Herein, we fabricate the transistor channel on a thin high-k dielectric, for example, HfO<sub>2</sub>, while the metal pads and wires are isolated using a thick SiO<sub>2</sub> layer to optimize the trade-off between the gate efficiency and gate-source/drain leakage current. The details of the device fabrication process can be found in the Supporting Information.

Figure 3a shows the room temperature  $I_d - V_d$  in reverse and forward bias regions at different  $V_g$  values. In the forward bias region, a clear NDR with a maximum peak to valley of 1.6 is observed at  $V_g = 0.15$  V. The insets show the NDR region in the linear scale for  $V_g = 0.15$  and 0.60 V and the NDR peak to valley ratio versus  $V_{g'}$  which decreases monotonically by increasing  $V_g$  to 0.60 V. In fact, applying a more positive  $V_g$ widens the gap, owing to the different gate efficiencies associates with MoS<sub>2</sub> and WSe<sub>2</sub>, which move the bands at different rates. This makes the NDR process more difficult and explains the decrease of the peak-to-valley values toward zero. Schematic band diagrams of the in-plane MoS<sub>2</sub>/WSe<sub>2</sub> junction at different bias regimes are shown in Figure 3b. Figure 3c shows the conductance  $(G = \frac{I}{V})$  for  $V_g = 0.15$  V. Our gated tunneling diode in the reverse bias regime shows an average conductance slope of S = 75 mV/dec over 2 orders of magnitude, and a maximum curvature coefficient  $(\gamma = \frac{d^2I}{dV^2} / \frac{dI}{dV})$  of 62.2  $V^{-1}$  above the noise level, at  $V_d = -0.45$  V.

The curvature coefficient is an important figure of merit parameter for designing high-performance tunneling diodes that are promising devices for several applications, such as highfrequency detectors.<sup>36</sup> Because the operation of these diodes is based on band-to-band tunneling, their I-V curvature characteristics are not limited by their thermionic emission of carriers. Our tunnel diode reached the typical goal of  $\gamma > 40 V^{-1}$ for backward diode operation.<sup>36</sup> The best  $\gamma$  reported so far, based on Si and III-V semiconductor-based backward diodes, are in the range of 47 to 70 V<sup>-1</sup> in the low  $V_d$  regime,<sup>37–39</sup> which places our MoS<sub>2</sub>/WSe<sub>2</sub> tunnel diode among the highest performance tunnel diodes reported to date. However, to obtain a transistor with a subthreshold slope SS < 60 mV/dec,  $\gamma$ should be larger than 80 V<sup>-1.36</sup> Given the fact that unlike the conventional semiconductor devices, where the charge concentration of the semiconductor is well-controlled by

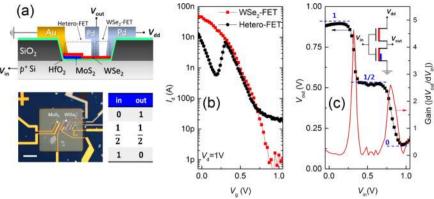

Figure 4. (a) Schematic of the ternary inverter, an optical image of the device, and an input–output table of the inverter. (b) Comparison of  $I_d - V_o$ curves of the hetero-FET and WSe<sub>2</sub>-FET shown in (a). (c)  $V_{out}$  versus  $V_{in}$  plot of the ternary inverter showing three distinct levels of logic. The inset shows a circuit schematic of the inverter.

doping techniques, in this MoS<sub>2</sub>/WSe<sub>2</sub> device, its unintentional, natural doping is not prepared through any specific doping approach. Developing efficient doping approaches to precisely control the charge density in 2D crystals and yet preserve their excellent properties will certainly aid in the preparation of the sharp band-edge feature in the 2D heterojunctions that is needed to observe the sharp threshold characteristics beyond the SS = 60 mV/dec limit.

Negative transconductance has been demonstrated in gated resonant tunneling devices<sup>25</sup> as well as modulation doped FETs.<sup>27</sup> Among different applications of negative transconductance, multivalued logic (MVL)<sup>26</sup> has attracted much attention. Owing to a higher number of logic states, MVL has the potential for higher data storage in less area as compared with binary logic.

In the past decades, MVL, such as ternary (three-level logic), has been considered as an alternative to binary logic and, so far, significant development has been achieved in the theory and design of ternary-based arithmetic operations.<sup>40</sup> Different MVL architectures, such as current-mode<sup>41</sup> and voltage-mode<sup>42</sup> multivalued CMOS, as well as multivalued charge-coupled devices<sup>43</sup> have already been demonstrated.

Herein, we demonstrate the application of MoS<sub>2</sub>/WSe<sub>2</sub> heterojunction FETs with the sign-changing transconductance feature for a ternary inverter using only one type of FET (p-FET). The inverter, as schematically depicted in Figure 4a, comprises two FETs built on a WSe2 film partially stacked on a MoS<sub>2</sub> film. The WSe<sub>2</sub> end is contacted by Pd and the overlapping region is contacted with Au. This configuration can be considered as a WSe<sub>2</sub>-FET in series with a parallel-mode MoS<sub>2</sub>/WSe<sub>2</sub> FET. For this device, an asymmetrical stack of a few-layer WSe2 and a multilayer MoS2 were used. The work function difference of MoS<sub>2</sub> and WSe<sub>2</sub><sup>44</sup> leads to charge accumulation of electrons in MoS<sub>2</sub> and of holes in WSe<sub>2</sub>. Given the thin body of the WSe2, this charge transfer creates two distinct regions in WSe<sub>2</sub>: a part that overlaps with the MoS<sub>2</sub> and a nonoverlapped region that can be considered as  $p^+-p^$ regions. This multicharge density profile induces multithreshold voltages (multi- $V_{\rm th}$ ) in the transfer characteristics of a FET comprising the  $p^+-p^-$  regions. Figure 4b compares the  $I_d-V_g$ curves of the WSe2-FET built on the overlapped region with the curve of the combined WSe<sub>2</sub> and overlapping WSe<sub>2</sub>/MoS<sub>2</sub>  $(p^+-p^- \text{ channel})$ , which is analogous with the FETs in Figure 1, and that we named a parallel-series mode FET. In region I of the  $I_d - V_g$  curves, which corresponds to the threshold regime, a

strong decrease of the current, which gives rise to the negative transconductance feature, is observed. As a result, the current of the parallel-series FET in this region is lower than its WSe<sub>2</sub> counterpart FET, which shows regular  $I_d - V_g$  behavior. In region II, corresponding to the subthreshold region of both FETs, both devices behave similarly with parallel  $I_d - V_g$  curves. However, in region III or the OFF-state region, the WSe2-FET has substantially lower current than the parallel-series FET owing to the fact that the OFF current of the parallel-series FET is larger. In the inverter configuration (inset of Figure 4c), the back gate is used for the input voltage  $(V_{in})$ , the middle electrode for output voltage  $(V_{out})$ , and the sides electrodes for the source and supply voltage. The three regions described in Figure 4b, form three distinct levels in the input-output characteristics ( $V_{out}$  versus  $V_{in}$ ) of the inverter, shown in Figure 4c, corresponding to three logic states. In this plot,  $V_{in}$  varies in the range of 0-1 V where  $V_{out}$  shows a high value of ~0.9 V for  $0 < V_{\rm in} < 0.3$  V, corresponding to state 1, a medium value of  $V_{\rm out} \sim$  0.5 V for 0.4 <  $V_{\rm in}$  < 0.8 V, corresponding to state 1/2, and a low level of  $V_{out} \sim 0.15$  V for  $V_{in} > 0.85$  V. The ternary device shown in this work is the first demonstration of how a multi-V<sub>th</sub> design, enabled by ultrathin nature of 2D semiconductors and their heterojunction engineering, can be suited and ubiquitous for the design of efficient multivalued logic circuits.

In conclusion, to obtain a better understanding of band-toband tunneling in MoS<sub>2</sub>/WSe<sub>2</sub> hetero-FETs, the energy band diagram of the MoS<sub>2</sub>/WSe<sub>2</sub> heterostructure was calculated and compared in the out-of-plane and in-plane directions to evaluate the possibility of band-to-band tunneling in different regions and directions. The results confirm that the effective heterojunction bandgap at the edge of the overlapped region of n-MoS<sub>2</sub> and p-WSe<sub>2</sub> in the horizontal direction is significantly smaller than their bandgap in the overlapped region in the outof-plane direction. These results indicate that the band-to-band tunneling dominantly occurs at the edge rather than the, commonly believed, overlapped region of the MoS<sub>2</sub>/WSe<sub>2</sub> heterojunction. Next, a tunnel-diode was designed and fabricated based on this heterostructure. We observe for the first time room-temperature NDR in a MoS<sub>2</sub>/WSe<sub>2</sub> tunneling diode with an average conductance slope of 75 mV/dec and a large curvature coefficient of 62 V<sup>-1</sup> at room temperature that highlights the remarkable potential of 2D crystals-based heterostructures for high performance tunneling transistors. Also, we have demonstrated MoS<sub>2</sub>/WSe<sub>2</sub> van der Waals heterojunction transistors with negative differential transconductance. After gate dielectric optimization, as an application, the optimized transistor was then used to build a ternary logic inverter with three stable logic states operating with a supply voltage of  $V_{\rm dd} = 1$  V, which is the first demonstration of such electronic devices with 2D materials.

#### ASSOCIATED CONTENT

#### **Supporting Information**

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acs.nano-lett.5b04791.

Additional data concerning the  $MoS_2/WSe_2$  heterostructure fabrication by dry transfer technique, optical characterization of the heterostructure, device fabrication, and band diagram calculations. (PDF)

#### AUTHOR INFORMATION

#### Corresponding Author

\*E-mail: anour@mit.edu.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The author would like to thank Winston Chern, Redwan Sajjad, and James Teherani for helpful discussions on this work. The authors also acknowledge the financial support from the Office of Naval Research (ONR) PECASE and The Air Force Office of Scientific Research (AFOSR) FATE-MURI programs.

#### REFERENCES

(1) Baugher, B. W. H.; Churchill, H. O. H.; Yang, Y. F.; Jarillo-Herrero, P. Nat. Nanotechnol. 2014, 9 (4), 262–267.

(2) Wu, S. F.; Buckley, S.; Schaibley, J. R.; Feng, L. F.; Yan, J. Q.; Mandrus, D. G.; Hatami, F.; Yao, W.; Vuckovic, J.; Majumdar, A.; Xu, X. D. *Nature* **2015**, *520* (7545), 69–U142.

(3) Lopez-Sanchez, O.; Lembke, D.; Kayci, M.; Radenovic, A.; Kis, A. *Nat. Nanotechnol.* **2013**, 8 (7), 497–501.

(4) Qian, X. F.; Liu, J. W.; Fu, L.; Li, J. Science **2014**, 346 (6215), 1344–1347.

(5) Wang, H.; Yu, L. L.; Lee, Y. H.; Shi, Y. M.; Hsu, A.; Chin, M. L.; Li, L. J.; Dubey, M.; Kong, J.; Palacios, T. *Nano Lett.* **2012**, *12* (9), 4674–4680.

(6) Tosun, M.; Chuang, S.; Fang, H.; Sachid, A. B.; Hettick, M.; Lin, Y. J.; Zeng, Y. P.; Javey, A. ACS Nano **2014**, 8 (5), 4948–4953.

(7) Yu, L. L.; Zubair, A.; Santos, E. J. G.; Zhang, X.; Lin, Y. X.; Zhang, Y. H.; Palacios, T. *Nano Lett.* **2015**, *15* (8), 4928–4934.

(8) Lee, C. H.; Lee, G. H.; van der Zande, A. M.; Chen, W. C.; Li, Y. L.; Han, M. Y.; Cui, X.; Arefe, G.; Nuckolls, C.; Heinz, T. F.; Guo, J.;

Hone, J.; Kim, P. Nat. Nanotechnol. 2014, 9 (9), 676-681.

(9) Loan, P. T. K.; Zhang, W. J.; Lin, C. T.; Wei, K. H.; Li, L. J.; Chen, C. H. *Adv. Mater.* **2014**, *26* (28), 4838.

(10) Ross, J. S.; Klement, P.; Jones, A. M.; Ghimire, N. J.; Yan, J. Q.; Mandrus, D. G.; Taniguchi, T.; Watanabe, K.; Kitamura, K.; Yao, W.;

Cobden, D. H.; Xu, X. D. Nat. Nanotechnol. 2014, 9 (4), 268–272. (11) Pospischil, A.; Furchi, M. M.; Mueller, T. Nat. Nanotechnol.

**2014**, 9 (4), 257–261.

(12) Zhang, Y. J.; Oka, T.; Suzuki, R.; Ye, J. T.; Iwasa, Y. Science **2014**, 344 (6185), 725–728.

(13) Roy, K.; Padmanabhan, M.; Goswami, S.; Sai, T. P.; Ramalingam, G.; Raghavan, S.; Ghosh, A. *Nat. Nanotechnol.* **2013**, 8 (11), 826–830.

(14) Nourbakhsh, A.; Zubair, A.; H, S.; Ling, X.; Dresselhaus, M. S.; Kong, J.; De Gendt, S.; Palacios, T. VLSI Technology (VLSI Technology), 2015 Symposium on **2015**, T28–T29. (15) Fang, H.; Battaglia, C.; Carraro, C.; Nemsak, S.; Ozdol, B.; Kang, J. S.; Bechtel, H. A.; Desai, S. B.; Kronast, F.; Unal, A. A.; Conti, G.; Conlon, C.; Palsson, G. K.; Martin, M. C.; Minor, A. M.; Fadley, C. S.; Yablonovitch, E.; Maboudian, R.; Javey, A. *Proc. Natl. Acad. Sci. U. S. A.* **2014**, *111* (17), 6198–6202.

(16) Appenzeller, J.; Lin, Y. M.; Knoch, J.; Avouris, P. Phys. Rev. Lett. **2004**, 93 (19), 196805.

(17) Agarwal, S.; Teherani, J. T.; Hoyt, J. L.; Antoniadis, D. A.; Yablonovitch, E. *IEEE Trans. Electron Devices* **2014**, *61* (5), 1599– 1606.

(18) Zhang, Q.; Fang, T.; Xing, H. L.; Seabaugh, A.; Jena, D. *IEEE Electron Device Lett.* **2008**, 29 (12), 1344–1346.

(19) Britnell, L.; Gorbachev, R. V.; Jalil, R.; Belle, B. D.; Schedin, F.; Mishchenko, A.; Georgiou, T.; Katsnelson, M. I.; Eaves, L.; Morozov, S. V.; Peres, N. M. R.; Leist, J.; Geim, A. K.; Novoselov, K. S.; Ponomarenko, L. A. *Science* **2012**, 335 (6071), 947–950.

(20) Kang, S.; Fallahazad, B.; Lee, K.; Movva, H.; Kim, K.; Corbet, C. M.; Taniguchi, T.; Watanabe, K.; Colombo, L.; Register, L. F.; Tutuc, E.; Banerjee, S. K. *IEEE Electron Device Lett.* **2015**, *36* (4), 405–407.

(21) Yan, R.; Fathipour, S.; Han, Y.; Song, B.; Xiao, S.; Li, M.; Ma, N.; Protasenko, V.; Muller, D. A.; Jena, D.; Xing, H. G. Nano Lett.

2015, 15 (9), 5791-8. (22) Wood, J. D.; Wells, S. A.; Jariwala, D.; Chen, K. S.; Cho, E.;

Sangwan, V. K.; Liu, X.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Nano Lett. **2014**, *14* (12), 6964–70.

(23) Roy, T.; Tosun, M.; Cao, X.; Fang, H.; Lien, D. H.; Zhao, P. D.; Chen, Y. Z.; Chueh, Y. L.; Guo, J.; Javey, A. ACS Nano **2015**, *9* (2), 2071–2079.

(24) Das, S.; Appenzeller, J. Appl. Phys. Lett. 2013, 103 (10), 103501.

(25) Beltram, F.; Capasso, F.; Luryi, S.; Chu, S. N. G.; Cho, A. Y.;

Sivco, D. L. Inst. Phys. Conf. Ser. 1989, No. 96, 599-604.

(26) Capasso, F.; Sen, S.; Cho, A. Y. Appl. Phys. Lett. 1987, 51 (7), 526-528.

(27) Ismail, K.; Chu, W.; Yen, A.; Antoniadis, D. A.; Smith, H. I. Appl. Phys. Lett. **1989**, 54 (5), 460-462.

(28) Luryi, S.; Capasso, F. Appl. Phys. Lett. 1985, 47 (12), 1347–1349.

(29) Lattanzio, L. D. M, L.; Ionescu, A. M. Solid-State Device Research Conference (ESSDERC), 2011 Proceedings of the European 2011.

(30) Bijesh, R.; Liu, H.; Madan, H.; Mohata, D.; Li, W.; Nguyen, N. V.; Gundlach, D.; Richter, C. A.; Maier, J.; Wang, K.; Clarke, T.; Fastenau, J. M.; Loubychev, D.; Liu, W. K.; Narayanan, V.; Datta, S. 2013 Ieee International Electron Devices Meeting (IEDM), Washington, DC, December 9–11, 2013.

(31) Mohata, D. K.; Bijesh, R.; Mujumdar, S.; Eaton, C.; Engel-Herbert, R.; Mayer, T.; Narayanan, V.; Fastenau, J. M.; Loubychev, D.; Liu, A. K.; Datta, S. 2011 Ieee International Electron Devices Meeting (IEDM), Washington, DC, December 5–7, 2011.

(32) Zhou, G. L.; Lu, Y. Q.; Li, R.; Zhang, Q.; Hwang, W. S.; Liu, Q. M.; Vasen, T.; Chen, C.; Zhu, H. J.; Kuo, J. M.; Koswatta, S.; Kosel, T.; Wistey, M.; Fay, P.; Seabaugh, A.; Xing, H. L. *IEEE Electron Device Lett.* **2011**, 32 (11), 1516–1518.

(33) Borg, B. M.; Dick, K. A.; Ganjipour, B.; Pistol, M. E.; Wernersson, L. E.; Thelander, C. *Nano Lett.* **2010**, *10* (10), 4080– 4085.

(34) Peelaers, H.; Van de Walle, C. G. Phys. Rev. B: Condens. Matter Mater. Phys. 2012, 86 (24), 241401.

(35) Kane, E. O. J. Phys. Chem. Solids 1960, 12 (2), 181-188.

(36) Agarwal, S.; Yablonovitch, E. *IEEE Trans. Electron Devices* **2014**, *61* (5), 1488–1493.

(37) Zhang, Z.; Rajavel, R.; Deelman, P.; Fay, P. *Ieee Microw Wirel Co* **2011**, 21 (5), 267–269.

(38) Karlovsky, J.; Marek, A. Czech. J. Phys. 1961, 11 (1), 76.

(39) Karlovsky, J. Solid-State Electron. 1967, 10 (11), 1109.

(40) Smith, K. C. IEEE Trans. Comput. 1981, 30 (9), 619–634.

(41) Druzeta, A.; Sedra, A. S. In *Multithreshold circuits in the design of multistate storage elements*, Proceedings of the 3rd International Symposium Multiple Valued Logic; pp 49–58, 1973.

(42) Mouftah, H. T.; Jordan, I. B. Electron. Lett. 1974, 10 (21), 441-442.

6265-6272.

<sup>(42).

(43)</sup> Kerkhoff, H. G.; Dijkstra, H. In *The application of CCD's in multiple-valued logic*, Proceedings of the 5th International Conference Charge-Coupled Devices; Edinburgh, Sept 1979; pp 304–309.

(44) McDonnell, S.; Azcatl, A.; Addou, R.; Gong, C.; Battaglia, C.; Chuang, S.; Cho, K.; Javey, A.; Wallace, R. M. ACS Nano 2014, 8 (6), 2017.