This is an electronic reprint of the original article.

This reprint may differ from the original in pagination and typographic detail.

Spoof, Kalle; Unnikrishnan, Vishnu; Zahra, Mahwish; Stadius, Kari; Kosunen, Marko; Ryynänen, Jussi

True-Time-Delay Beamforming Receiver With RF Re-Sampling

Published in:

IEEE Transactions on Circuits and Systems - I: Regular Papers

DOI:

10.1109/TCSI.2020.3005475

Published: 01/12/2020

Document Version

Peer reviewed version

Please cite the original version: Spoof, K., Unnikrishnan, V., Zahra, M., Stadius, K., Kosunen, M., & Ryynänen, J. (2020). True-Time-Delay Beamforming Receiver With RF Re-Sampling. *IEEE Transactions on Circuits and Systems - I: Regular Papers*, 67(12), 4457-4469. https://doi.org/10.1109/TCSI.2020.3005475

This material is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of the repository collections is not permitted, except that material may be duplicated by you for your research use or educational purposes in electronic or print form. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone who is not an authorised user.

# True-Time-Delay Beamforming Receiver With RF Re-Sampling

Kalle Spoof, Vishnu Unnikrishnan, *Member, IEEE*, Mahwish Zahra, Kari Stadius, *Member, IEEE*, Marko Kosunen, *Member, IEEE*, and Jussi Ryynänen, *Senior Member, IEEE*

Abstract-Analog domain true-time-delays (TTD) are desired in hybrid beamforming receivers with large relative bandwidths to mitigate the problem of beam squint. We propose a true-timedelay beamforming receiver architecture which enables squintfree wideband spatial filtering prior to the A/D conversion. The receiver implements true-time-delay with delayed re-sampling of the discrete-time output of a passive mixer. The receiver has the capability to extend the range of the beamforming delays from one to several carrier periods of the RF signal with pulse-skipped local oscillator (LO) signals, thereby enabling TTD beamforming with large antenna arrays. Further, a polyphase structure with parallel mixers is proposed to prevent spectral aliasing resulting from the lowered sample rate of the pulse-skipped LO signals. In addition, the maximum beamforming delay scales with the LO frequency, supporting large arrays also at low frequencies where the antenna separation set by the wavelength is large. We verify the proposed concepts with transistor-level simulation of the receiver implemented with a 28-nm CMOS process. The design achieves a squint-free beamforming for a 400 MHz RF bandwidth, and a maximum beamforming delay of three carrier time periods. The power consumption for a 3 GHz carrier frequency is 4 mW per antenna.

*Index Terms*—Analog beamforming, hybrid beamforming, true-time-delay, spatial filtering, RF sampling, re-sampling, beam squint, phased array, radio receiver, CMOS.

#### I. INTRODUCTION

Electronic beamforming with antenna arrays required for radars and upcoming communication systems with spatial filtering, like the 5G systems [1], can be implemented either in the analog [2]–[4] or the digital [5]–[8] domain. In analog beamforming receivers the signals from different antennas are combined to form one beam before the analog-to-digital converter (ADC). This beamforming creates spatial filtering prior to the ADC, which improves the receiver chain's dynamic range performance in the presence of in-band blockers [7]. Analog beamforming limits the number of supported simultaneous beams, since implementing parallel analog reception paths for each beam becomes prohibitive due to increased hardware complexity leading to large area and power consumption [9]. In digital beamforming, signals from different antennas are digitized separately and the beams are formed in

K. Spoof is with Saab Finland and Department of Electronics and Nanoengineering, School of Electrical Engineering, Aalto University, 02150 Espoo, Finland. (e-mail: kalle.spoof@aalto.fi)

V. Unnikrishnan, M. Zahra, K Stadius, M Kosunen, and J. Ryynänen are with the Department of Electronics and Nanoengineering, School of Electrical Engineering, Aalto University, 02150 Espoo, Finland

This project has received funding from the European Union's Horizon 2020 research and innovation programme under the Marie Sklodowska-Curie grant agreement No 704947

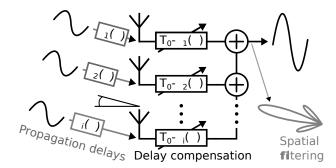

Fig. 1. Illustration of a true-time-delay beamforming. The propagation delays are compensated with tunable delays on each antenna path. Delay compensation, instead of phase compensation, prior to signal summation creates frequency-independent spatial filtering.

the digital domain. As digital signal processing supports efficient hardware paralellization, multiple simultaneous beams in different directions are feasible [8]. On the other hand, digital beamforming does not provide spatial filtering at the ADC inputs, which limits dynamic range in the case of inband blockers [10]–[12]. Hybrid beamforming can alleviate the blocker problem by means of analog spatial filtering while retaining the computational flexibility of digital signal processing [1], [9], [13].

The instantaneous signal bandwidth of a hybrid beamformer can be limited by the analog beamforming front-end. Analog beamforming is most often implemented with phase shifts, which approximate the time-of-flight delays caused by the antenna array geometry. Phase shift beamforming for large relative bandwidths leads to a spatial error called beam squint [14]-[21]. Squint leads to different parts of the signal band to be steered to different directions, resulting in signal loss towards the intended direction. Beam-squinting can be avoided by using true-time-delays (TTD) instead of the phase shifts [15], [22]. Several TTD elements for wideband analog beamforming have been published. Elements based on delay lines, [16], [17], require inductors and hence large area. Active all-pass filter based TTD solutions [18]–[20] have high power consumption and limited operating frequencies. Hence, discrete-time solutions have recently gained interest [23].

In this work, we propose a TTD beamforming receiver front-end with RF re-sampling to solve beam squint in hybrid beamforming systems with large bandwidths. The proposed solution realizes beamforming delays by re-sampling the discrete-time output signal from the passive mixer of a direct conversion receiver during its hold period. Inclusion of

1

a re-sampling stage extends the local oscillator (LO) phase shifting, like the one implemented in [3], to a true-time-delay beamformer. The beamforming delays are controlled by tuning the relative delay between the LO and the re-sampler clock. Such a realization of the analog delays with clock timing benefits from the increasing temporal resolution and power efficiency offered by CMOS technology scaling. Further, the re-sampling delays are implemented without inductors, which enables area-efficient CMOS integration.

The range of beamforming delay that can be achieved with the LO tuning and RF re-sampling is set by a single period of the LO signal, which is the carrier signal period,  $T_c$ , in a direct conversion receiver. The proposed receiver significantly extends the range of beamforming delays to several times  $T_c$ by utilizing pulsed LO signals. This enables larger antenna arrays, where the maximum beamforming delay exceeds  $T_c$ . We also present a polyphase implementation with parallel mixers that prevents aliasing caused due to the lowered LO sample rate due to pulse skipping. The delay range obtained with the proposed pulse-skipped LO technique scales with the carrier frequency, enabling the receiver to support large arrays also at lower frequencies where a large  $\lambda_c/2$  antenna spacing demands long beamforming delays. Furthermore, the proposed architecture has most of the power consumed in stages common to all the antenna paths, thus providing an efficient scaling of power consumption with the number of antennas, where the power does not increase linearly with the number of antennas. The concept of true-time-delay beamforming with RF re-sampling and pulse-skipped LO signals is demonstrated with transistor-level simulations of the receiver implemented in a 28-nm CMOS process.

The paper is organized as follows. Section II presents the background for analog beamforming, discusses beam squint, and reviews the state-of-the-art TTD solutions. Section III presents the beamforming with RF re-sampling. Section IV describes integration of RF re-sampling with passive mixer down-conversion. Section V presents the extension of the beamforming delay range with the pulse-skipped LO signals. Section VI derives spectral aliasing which would result from the LO pulse skipping, and describes a polyphase structure with parallel mixers to prevent the aliasing. Verification of the proposed true-time-delay beamforming receiver with transistor level simulations is presented in Section VII.

# II. OVERVIEW OF ANALOG-DOMAIN BEAMFORMING

To justify the implementation and provide theoretical basis for our work we present the established [15], [21] differences between beamforming based on phase shifts and true-time-delays in terms of the beam squint directivity error.

# A. Beamforming with Phase Shifts

Fig. 1, shows a signal arriving to a beamforming antenna array from an incident angle  $\theta$ . The distance between antennas in the array causes  $\theta$ -dependent propagation delays for the signal. The delays at the antenna inputs can be referenced to the first antenna and expressed as

$$\tau_i = \frac{(i-1)d}{c}\sin(\theta),\tag{1}$$

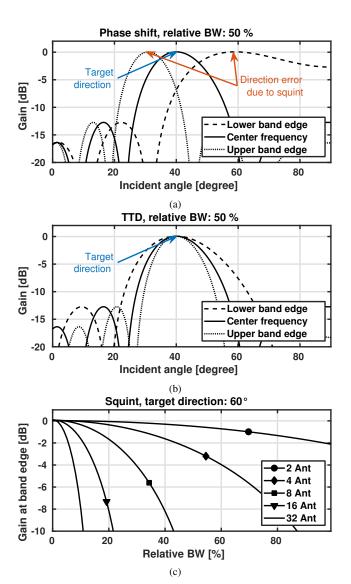

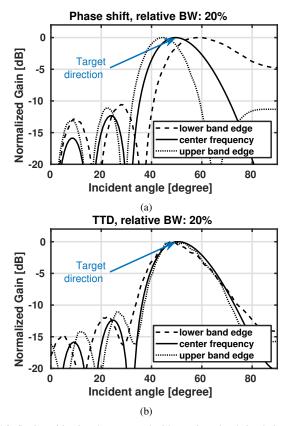

Fig. 2. Illustration of beam squint with simulation of a behavioral model: (a) phase shift beamforming, leading to significant beam squint for 50% signal bandwidth, (b) true-time-delay beamforming mitigating the beam squint, and (c) variation of gain in the target direction, at the band edge, as a function of relative bandwidth and number of antennas.

where i is the index of the antenna, d is the antenna spacing as shown in Fig. 1, and c the speed of light [21]. In phase shift beamforming the delays are mapped to frequency f-dependent phase shifts  $\phi_i$

$$\phi_i = 2\pi f \tau_i \tag{2}$$

for each antenna. Phase shift beamforming is realized by cancelling  $\phi_i$  at the center frequency  $f_c$  and summing the signals. The cancellation is achieved with individual phase shifts at each antenna's signal path. Since the signal path phase shifts match  $\phi_i$  only at  $f_c$ , beamforming is implemented imperfectly for frequencies other than  $f_c$ .

# B. Beam Squint

Beam squinting is a spatial error caused by the imperfect phase cancellations in phase shift beamforming [15], [21]. Squint results in a frequency dependency for the beamforming angle, which is visualised with simulations in Fig. 2a. The simulation shows beam patterns at different frequencies for an 8-antenna array with antenna spacing of  $\lambda_c/2$ , where  $\lambda_c$  is the wavelength at  $f_c$ . The main lobes of the beam patterns at 25% frequency offsets from  $f_c$  have visibly diverged from the target angle of 40 degrees. The squint error in the beam direction causes a loss of 7 dB for the target direction in this case. In addition to the steering angle and the relative bandwidth (BW), the squint loss depends on the array size. Fig. 2c plots the loss towards the target direction at the edge of the bandwidth for a target direction of 60 degrees as a function of the array size and relative RF bandwidth. The increasing loss for larger arrays and relative bandwidths is demonstrated, highlighting the drawback of phase shift beamforming for large bandwidths and arrays.

#### C. True-Time-Delay Beamforming

The problem of the frequency-dependent beam direction can be avoided with true-time-delay beamforming, which replaces the phase shifts with delays [15]. Delay cancellation for direction  $\theta$  is achieved with signal path delays  $\Delta \tau$  for each antenna, as shown in Fig. 1.

$$\Delta \tau_i = T_0 - \tau_i,\tag{3}$$

where  $T_0$  is a common delay, which is added for all antennas to avoid having to implement negative delays. Fig. 2b shows TTD beamforming implemented for the same antenna array which was used in the phase shift beamforming simulations in Fig. 2a. Since delays are frequency independent, squinting does not occur, and, the beam direction remains constant at 40 degrees regardless of frequency. As squinting is avoided, TTD beamforming can be implemented for any relative bandwidth.

#### D. Prior Art of Integrated Analog Domain TTD Elements

Analog-domain delay-based beamforming can be implemented with true-time-delay elements in the analog signal path. The published TTD elements for beamforming mainly fit two categories, passive and active. The passive solutions are based on LC delay lines [16], [17] or transmission lines [24]. The passive TTD elements support wide frequency ranges up to tens of GHz. However, the delay lines require inductors and hence very large area, in the order of over 1 mm<sup>2</sup> per delay element. Because of the large area required, they are not feasible for cost effective integrated beamforming receivers.

The second category are active solutions, which are based on all-pass filters, [18] [20]. These filters create true-time-delays with a phase shift that changes linearly with frequency. The active solutions can be made with orders of magnitude less area consumption compared to the passive TTD elements. However, their operating frequencies are limited below 2.5 GHz. Moreover their power consumption is large, in the range of 100 mW per element. Since both active and passive solutions have significant drawbacks, there is a need for research into new types of TTD solutions.

Recently TTD beamforming based on discrete-time signal processing has been shown in [23] to improve the area and power consumption compared to the previous solutions. The

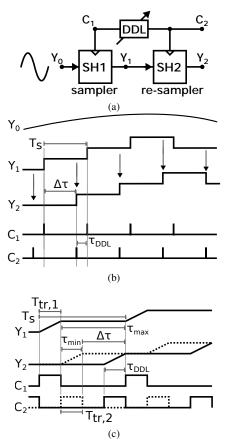

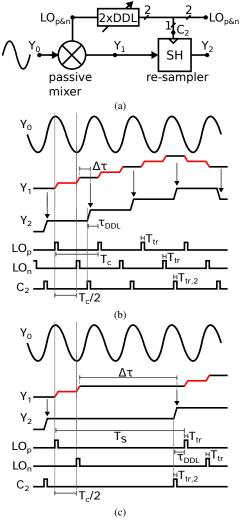

Fig. 3. The concept of true-time-delay realized with re-sampling: (a) the block diagram, (b) respective signal waveforms, and (c) the limitations on  $\Delta \tau$  introduced by the sampler track times. Tuning the sampling instants with the DDL changes delay between  $Y_1$  and  $Y_2$ .

improvement is due to the implementation of true-time-delays with clock tuning and switching, which are efficient in modern CMOS processes. This paper presents a receiver front-end, which takes similar advantage of discrete-time TTDs as the baseband solution in [23].

# III. RE-SAMPLING TRUE-TIME-DELAYS FOR BEAMFORMING

Power and area efficient implementation of a frequency-independent true-time-delay can be achieved with discrete-time signal processing, as summarized in Section II-D. We propose a true-time-delay beamforming receiver, in which the analog-domain time-delay is realized by re-sampling a discrete-time signal. We start the explanation of our receiver in this section by presenting how sampling and re-sampling can be used to create a TTD for analog domain beamforming, which is controlled through a digital delay line. This concept is then expanded by merging it with passive mixer down-conversion in Section IV.

# A. Implementation of Delay with Re-sampling

A practical circuit realization of a discrete-time signal is usually obtained by sampling the signal voltage at discrete time-instances onto a capacitor. The resulting sampled-andheld signal can be modeled with a first-order-hold applied to a discrete time sequence. A discrete-time signal with first-order hold can be delayed by a fraction of its sample period by simply re-sampling the signal with a delayed clock signal. A circuit realization of such a re-sampling delay system is shown in Fig. 3a. The continuous-time input signal at node  $Y_0$  is sampled to generate a first-order-hold discrete-time signal at node  $Y_1$ , which is re-sampled to generate a delayed version of the signal at  $Y_2$ .

The amount by which the analog signal  $Y_1$  is delayed matches the delay between the sampling clock signal  $C_1$  and the re-sampling clock signal  $C_2$ . The clock delay is generated with a configurable digital delay line (DDL), which creates a delay  $\tau_{\rm DDL}$  between  $C_1$  and  $C_2$ . The resulting delay for the analog signal is

$$\Delta \tau = T_s - \tau_{\text{DDL}},\tag{4}$$

where  $T_s$  is the sampling period of the samplers. The connection of  $\tau_{\rm DDL}$  and  $\Delta \tau$  is shown in Fig. 3b, together with waveforms of the signals at  $C_1$ ,  $C_2$ ,  $Y_0$ ,  $Y_1$ , and  $Y_2$ . The re-sampling delay  $\Delta \tau$  in (4) has the same form as the beamforming delay of (3).

#### B. Maximum Delay with Track-and-Hold Samplers

With the ideal sample-and-hold functions in Fig. 3b, the maximum beamforming delay  $\tau_{max}$  is limited to the sample period  $T_s$ . Circuit implementations of the sampling and resampling functions can be achieved with track-and-hold circuits, which track their input signals, while the clock signals  $C_1$  and  $C_2$  are high. The sampler is required to be in hold mode during re-sampling, which results in the track times limiting the beamforming delay tuning range.

The effects of the track times on the re-sampling delay range shown in Fig. 3c, where  $T_{\rm tr,1}$  and  $T_{\rm tr,2}$  are the track times of  $C_1$  and  $C_2$ , respectively. The tuning range of the delay is limited in two ways. Firstly, the minimum signal delay is not zero. The dashed lines in Fig. 3c show the case when the re-sampling starts immediately after the sampler enters hold mode. As the re-sampler output requires  $T_{\rm tr,2}$  to settle, the signal is always delayed by at least  $T_{\rm tr,2}$ . The total delay for the signal can be split into constant and configurable parts

$$\tau_{\text{tot}} = T_{\text{tr}\,2} + \Delta\tau,\tag{5}$$

of which only  $\Delta \tau$  can be used for beamforming. Secondly, the re-sampling has to finish before the sampler is clocked again. This limits the maximum delay to  $\tau_{max} = T_s - T_{\rm tr,1}$ , as shown in Fig. 3c with the solid lines. The maximum  $\Delta \tau$  is achieved by setting  $\tau_{DDL} = T_{\rm tr,2}$ , and  $\tau_{DDL}$  cannot be set smaller than this.

With these two limitations, the tuning range for  $\Delta \tau$  can be expressed by subtracting the constant delay term from the maximum delay

$$\Delta \tau = 0...T_s - T_{\text{tr.1}} - T_{\text{tr.2}}.$$

(6)

This equation highlights that the track times can take away large portion of the delay tuning range if  $T_s$  is short, and, that the delay range can be extended by lowering sample rate since  $T_s = 1/F_s$ .

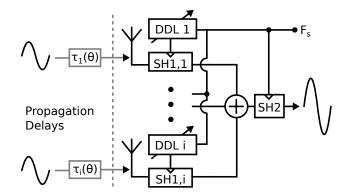

Fig. 4. An example of true-time-delay beamforming using individual resampling delays for each antenna.

#### C. Delay Resolution

The resolution of the tunable delay  $\Delta \tau$ , which dictates the beam direction resolution, is directly set by the used DDL. As an example, [3] presents a beamformer based on LO phase shifting implemented with DDLs. The DDL achieves picosecond delay resolution, which maps to a beam resolution of 2.4 degrees at 5 GHz, with a power consumption of 11 mW. Usage of high-resolution DDLs, e.g. [25], further increase the temporal resolution for  $\Delta \tau$  to the order of tens of femtoseconds. This precision and digital nature of the delay resolution means it is possible to control the beamforming direction accurately and efficiently.

# D. Beamforming with Re-Sampling Delays

The re-sampling delays can be used to build a TTD beamformer for a receiver. Instead of using one sampler and one re-sampler, as shown in Fig. 3a, for each antenna, it is possible to share the re-sampling function between the differently delayed signal paths. The sharing is enabled by placing the signal summation point before the re-sampling, as shown in Fig. 4. In addition to requiring less hardware, this sharing avoids any timing errors between individually implemented re-samplers. Since the summed signal is constant when re-sampling occurs, timing errors in the shared re-sampling clock do not affect beamforming. As long as the sampling and re-sampling clocks don't overlap, an error in the shared re-sampling simply appears as a common delay for all signal paths without affecting relative delays between paths.

The summation point before re-sampling doesn't change the delays created for each path. Delay cancellation for each path is achieved with DDL delays, which match the delays at the antenna inputs  $\tau_{DDL,i} = \tau_i + T_{\rm tr,2}$ . With the delay cancellation and summation, Fig. 4 realizes the TTD beamforming of Fig. 1 with the presented re-sampling delays. The delays are controlled with DDLs, and the delay range is set by the sample rate and sampler track times according to (6).

# IV. BEAMFORMING BY RE-SAMPLING MIXER OUTPUT

The re-sampling delay technique of Section III can be implemented for any sampled-and-held signal, which has the same sample rate as the re-sampler. We integrate the delay

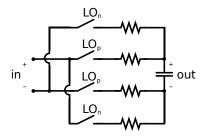

Fig. 5. Passive mixer and the output sampling capacitor.

Fig. 6. Proposed technique to realize true-time-delay with re-sampling the output of a passive mixer: (a) the block diagram, (b) respective signals for a conventional LO signal, and (c) signals for the pulse-skipped LOs, employed to extend the beamforming delay range.

technique with down-conversion in a direct conversion receiver by replacing the first sampling stage SH1, i, shown in Fig. 4, with a passive mixer in sampling configuration.

# A. Passive Mixer in Sampling Configuration

A passive mixer in sampling configuration is presented in Fig. 5. It performs down-conversion by controlling its switches with positive and negative phases of the local oscillator (LO) signal,  $LO_p$  and  $LO_m$ , respectively. The resulting down-

converted baseband signal appears on the output capacitor. The capacitor holds the output constant while  $LO_p$  and  $LO_m$  are OFF, i.e. the mixers output voltage is sampled at the end of the LOs' ON periods.

# B. Re-sampling Delay with Passive Mixer

As the voltage over the mixer's output capacitor is a sampled-and-held signal, it can be delayed by re-sampling as described in Section III. A block diagram of the re-sampling delay applied for a passive mixer output is shown in Fig. 6a. An RF signal at node  $Y_0$  is down-converted using the passive mixer, which produces a sampled-and-held baseband signal on node  $Y_1$ . The baseband signal is re-sampled during its hold time, creating a delayed version at node  $Y_2$ .

The re-sampler is clocked with the positive phase LO signal  $\mathrm{LO}_p$ .  $\mathrm{LO}_p$  and  $\mathrm{LO}_n$  are passed through identical configurable DDLs to delay the re-sampling instant compared to the LOs. The delay between  $LO_n$  and  $C_2$  defines the delay between the signals at  $Y_1$  and  $Y_2$ . The waveforms at nodes  $\mathrm{LO}_p$ ,  $\mathrm{LO}_n$ ,  $C_2$ ,  $Y_0$ ,  $Y_1$  and  $Y_2$ , are shown in Fig. 6b. In the figure,  $T_c$  is the time period of the carrier wave at  $f_c$ . Apart from the added down-conversion between  $Y_0$  and  $Y_1$ , the re-sampling delay setup with passive mixers is identical to the delay concept that was presented in Fig. 3a.

#### C. Delay Tuning Range with Down-conversion

Similarly to the analysis in Section III-B, the delay tuning range  $\Delta \tau$  is limited by the requirement that the re-sampling has to finish during the hold time of the previous stage. The hold time of the mixer is between  $LO_n$  ending and  $LO_p$  starting. The track time of the LOs is notated  $T_{\rm tr}$  for the rest of the paper. Since  $LO_p$  and  $LO_n$  occur  $T_c/2$  apart and are high for  $T_{\rm tr}$ , the hold time is  $T_c/2-T_{\rm tr}$ . The re-sampling time has to fit into this time window, represented by the black part of signal  $Y_1$ . The tuning range for the signal delay is

$$\Delta \tau = 0 \cdots T_c / 2 - T_{\text{tr}} - T_{\text{tr},2} \tag{7}$$

$$\Delta \tau = 0 \cdots T_s - (T_c/2 + T_{tr}) - T_{tr,2}, \tag{8}$$

where  $T_s=T_c$ . With typical 25% duty-cycle LO signals  $T_{\rm tr}=T_c/4$ , and the delay range is limited to

$$\Delta \tau = 0 \cdots T_c / 4 - T_{\text{tr,2}}.\tag{9}$$

The next section presents pulse-skipped LO signals, which can overcome this delay limitation.

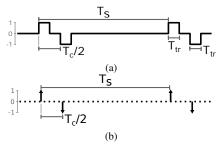

#### V. PULSE-SKIPPED LO

The delay tuning range is limited by the hold time of the mixer, as shown in section IV-C. A pulse-skipped LO signal shown in Fig. 7a allows the hold time and hence the delay tuning range to be extended. The following subsections go through the effects of pulse-skipped LO on mixer conversion gain and the re-sampling delay range.

Fig. 7. Pulse-skipped LO signal: (a) example waveform, and (b) impulse train used in the analysis.

#### A. Conversion Gain

Down-conversion in mixers is based on multiplication. The passive mixer achieves signal multiplication by continuously reversing the polarity of the connection between the input and output with the switches. When  $LO_p$  is high the input is connected to the output directly, i.e. with a gain of one. When  $LO_n$  is high, the connection polarity is reversed and the gain is -1. When  $LO_p$  and  $LO_n$  are low, all of the switches are OFF and the gain between input and output is zero.

Multiplying the RF input signal with the LO results in new frequencies frequencies defined by

$$A_{c}sin(f_{c}t)A_{LO}sin(f_{LO}t)$$

$$= \frac{1}{2}A_{c}A_{LO}[sin((f_{c} - f_{LO})t) + sin(f_{c} + f_{LO})t)],$$

(10)

where  $A_c$  is the amplitude of the RF signal and  $A_{LO}$  is the unitless spectral amplitude of the LO waveform at  $f_{LO}$ . The term  $sin((f_c-f_{LO})t)$  is the down-conversion result, and the down-conversion gain is  $A_{LO}/2$ . Consequently, the conversion gain from around  $f_c$  to baseband is defined by the LO's spectral amplitude at  $f_c$ .

#### B. Pulsed LO spectrum

The spectrum of the pulse-skipped LO can be calculated by modelling it as impulses multiplied by a zero-order-hold. The impulses model the positions of the LO pulses and the hold operation takes into account their track time. An impulse train for creating the pulse-skipped LOs is shown in Fig. 7b. The positive phases of the LO can be represented in frequency domain as  $\sum_n \delta(f-nF_s)$ , where  $F_s=1/T_s$  is the pulse-skipped LO sample rate. The negative LO phases are also repeated with  $F_s$ , but they occur  $T_c/2$  after the positive phases. In frequency domain, this delay is represented by  $e^{-sT_c/2}$ , allowing the negative phases to be added to the impulse train by multiplying it with  $(1-e^{-sT_c/2})$ . The spectrum of the impulses of Fig. 7b is

$$S_{imp}(j\omega) = (1 - e^{-sT_c/2}) \sum_{n} \delta(f - nF_s),$$

$$= 2e^{-j\pi f T_c/2} sin(\frac{\pi f T_c}{2}) \sum_{n} \delta(f - nF_s)$$

$$= 2e^{-j\pi f/(2f_c)} sin(\frac{\pi f}{2f_c}) \sum_{n} \delta(f - nF_s). \quad (11)$$

The track time  $T_{\rm tr}$  of the LO phases is modelled by lengthening these impulses using a hold operation. Each impulse is

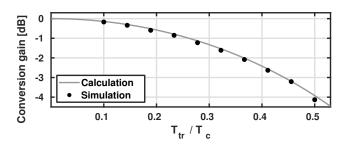

Fig. 8. Variation of conversion gain with pulse-skipped LO (N=3), as a function of LO track time, as calculated by (15) and obtained with simulation of the behavioral model.

multiplied by a zero-order-hold response with a hold time of  $T_{\rm tr}$ . The frequency response of the hold operation is

$$H_{hold}(j\omega) = \frac{e^{-j\pi T_{tr}f}sin(\pi T_{tr}f)}{j\pi T_{tr}f}$$

$$= \frac{e^{-j\pi T_{tr}f}}{j}sinc(\pi T_{tr}f), \tag{12}$$

and the resulting spectrum of the pulse-skipped LO signal is

$$S_{LO}(j\omega) = S_{imp}(j\omega)H_{hold}(j\omega)$$

$$= \frac{e^{-j\pi T_{tr}f}}{j}sinc(\pi T_{tr}f)$$

$$\times 2e^{-j\pi f/(2f_c)}sin(\frac{\pi f}{2f_c})\sum_{r}\delta(f - nF_s). \quad (13)$$

In order to down-convert from  $f_c$  to baseband the LO must have a component at  $f_c$ , which can be ensured by limiting the LO sample rate  $F_s$  to

$$F_s = f_c/N, (14)$$

where the LO pulse-skipping factor N is a positive integer. The conversion gain from the carrier frequency is

$$CG(f_c) = \frac{1}{2} \left| S_{LO}(j2\pi f_c) \right| = sinc(\frac{T_{tr}}{T_c}). \tag{15}$$

The conversion gain analysis is verified by comparing (15) to a simulated conversion gain using a pulse-skipped LO with the selection N=3. The results shown in Fig. 8 demonstrate a good match between the analysis and simulation. Furthermore, since the conversion gain is unaffected by N, down-conversion with pulse-skipped LOs is shown to be viable.

#### C. Mixer Bandwidth with Pulsed LOs

Unlike conversion gain, the mixer's bandwidth is affected by the pulse-skipped LOs. As analysed in [26], the RC bandwidth of a passive mixer scales with used duty-cycle. The duty-cycle of the passive mixer in Fig. 5 is set by the pulse-skipped LO parameters  $T_{\rm tr}$  and  $T_s$

Duty-cycle =

$$\frac{2T_{tr}}{T_s} = 2T_{tr}F_s = \frac{2T_{tr}}{NT_c}$$

. (16)

The scaled -3 dB bandwidth of the mixer is

$$BW = \frac{2T_{tr}}{NT_c} \frac{1}{2\pi RC}.$$

(17)

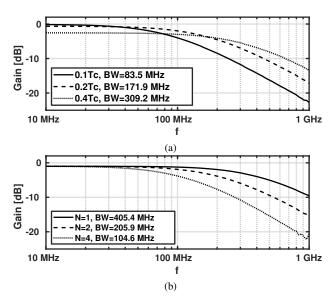

Fig. 9. Scaling of the mixer bandwidth as a function of pulse-skipped LO parameters. Simulated baseband responses and the respective scaling of the bandwidth with different (a) LO track times relative to the carrier time period, and (b) pulse-skipped LO sample rates set by N.

Fig. 9 shows simulated baseband responses for the passive mixer with constant R and C. The x-axis shows the baseband frequency, and the input is at this frequency plus  $f_c$ . Bandwidth scaling with  $T_{\rm tr}$  is demonstrated in Fig. 9a, in which the bandwidth doubles when  $T_{\rm tr}$  is doubled. The DC-gain variance visible in Fig. 9a is due to  $T_{\rm tr}$ 's effect on the mixer conversion gain, which was described (15). Bandwidth scaling with  $F_s$  is shown in Fig. 9b, demonstrating again the bandwidth scaling according to (17). It can be concluded that pulse-skipped LO parameters  $T_{\rm tr}$  and sample rate  $F_s = f_c/N$  linearly scale the mixers bandwidth. This means that, for example if N is doubled, the sampling capacitor size can be halved in order to keep the bandwidth constant.

# D. $\Delta \tau$ Tuning Range with Pulsed LO

Fig. 6c demonstrates the extension in delay tuning range with the pulse-skipped LO compared to continuous LO signals. The pulse-skipped LO signals control the re-sampling delay setup of Fig. 6a.  $LO_p$  and  $LO_n$ , which implement the positive and negative phases of the pulse-skipped LO, occur  $T_c/2$  apart from each other and are repeated every  $T_s = NT_c$ . Multiplying the RF input  $Y_0$  with this LO produces a baseband signal  $Y_1$ , which changes only when either  $LO_p$  or  $LO_n$  is active.  $Y_1$  re-sampled with the clock  $C_2$ , creating a delayed version at  $Y_2$ . The delay for  $Y_2$  is set by the timing between LOs and  $C_2$ , which is configured with  $\tau_{DDL}$ .

With the pulse-skipped LO the possible delay is increased. The hold time is again between  $LO_n$  ending and  $LO_p$  starting, and the delay range is

$$\Delta \tau = 0 \cdots T_s - T_c/2 - T_{tr} - T_{tr,2}. \tag{18}$$

With  $T_s = NT_c$  and  $T_{tr} = T_{tr,2} = T_c/4$

$$\Delta \tau = 0 \cdots N T_c - T_c / 2 - T_{tr} - T_{tr,2}$$

$$= 0 \cdots (N-1) T_c. \tag{19}$$

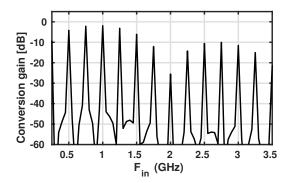

Fig. 10. Conversion gain from different RF frequencies to the baseband with pulse-skipped LO (N=4 and  $f_c=1$  GHz). The pulse-skipped LO has high conversion gain at sub-harmonic frequencies  $nf_c/N$ .

The equation shows the relation between the increased delay range and the LO pulse factor N.

In summary the pulse-skipped LOs increase the delay tuning range as shown in (19), without negatively affecting the conversion gain from  $f_c$ . As such, they enable a passive mixer to be used as the first sampling stage in the re-sampling delay method.

#### VI. PARALLEL POLYPHASE MIXERS

While the pulse-skipped LOs allow TTD beamforming with increased delays, they lower the sample rate  $F_s$  of the mixer. The lowered  $F_s$  causes spectral aliasing through down-conversion of additional unwanted input frequency bands. Unless removed, these down-conversions negatively affect the noise performance of the receiver. The unwanted down-conversions can be prevented with a polyphase structure.

#### A. Unwanted Down-Conversions

In addition to the desired down-conversion from  $f_c$ , the pulse-skipped LO also down-converts from unwanted frequencies. Conversion gain from  $f_c$  was found in (15) with the pulse-skipped LO spectrum at  $f_c$ . Similarly, additional conversion gains are defined by the spectral components of (13) at sub-harmonics  $nf_c/N$ . Fig. 10 shows simulated conversion gains from different  $f_{\rm in}$ , with LO parameters  $f_c=1$  GHz and N=4. There are conversion gains at  $n(1~{\rm GHz})/4$  as predicted by the analysis.

Any signals present at the input at these sub-harmonic frequencies fall on top of the desired signal at baseband. Blocker signals at the input could be attenuated with a RF filter before the mixer. However, such filters are difficult to implement, especially if  $f_c$  should be tunable. Moreover, even if there are no blockers on the sub-harmonics, or the blockers can be filtered out, there is still noise on these frequencies. Increase in noise from sub-harmonic down-conversions is analysed in the next subsection.

# B. Noise Increase

The noise factor of a receiver is defined as  $F = SNR_i/SNR_o$ , where  $SNR_i$  and  $SNR_o$  are the signal-to-noise ratios in the input and output, respectively. We assume

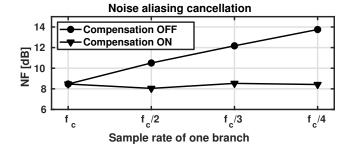

Fig. 11. Simulated NF (a) as a function of LO track time, compared against NF calculated with (20), and (b) as a function of the pulse-skipped LO sample rate. It can be seen that the polyphase noise compensation structure employed (Compensation ON) prevents the increase in noise with the pulse-skipped LOs.

white noise at the mixer input and define the noise power across the input bandwidth to be  $N_i$ . The pulse-skipped LO down-converts from equal noise bands around frequencies  $f=nf_c/N$ , according to the conversion gains defined by the spectral components of the LO at these frequencies in (13). As noise at each input band is equal to the noise at the band around  $f_c$ , we get output noise with (13) to be  $N_o=1/2\big|S_{LO}(j2\pi f)\big|^2\,N_i$ . The signal power at the output is simply  $S_o=CG(f_c)^2S_i$ , where  $S_i$  is the input signal power. With  $S_o$  and  $N_o$  as functions of  $S_i$  and  $N_i$ , respectively, the noise factor is

$$F = SNR_{i}/SNR_{o} = \frac{S_{i}/(2Ni)}{S_{o}/N_{o}} = \frac{S_{i}N_{o}}{S_{o}2N_{i}}$$

$$= [(sin(\frac{\pi f}{2f_{c}})sinc(T_{tr}f)\sum_{n}\delta(f - nF_{s}))^{2}]$$

$$/(2*(CG)^{2}), \tag{20}$$

where the factor 2 in the denominator is used for double side-band noise. The simulations were done for a behavioral spice model of the passive mixer circuit shown in Fig. 5. The mixer switch resistances were considered noiseless. Fig. 11a compares (20) to a simulated noise figure (NF) with different LO track times  $T_{\rm tr}$  with N=1. The plots reveal that to avoid higher NF,  $T_{\rm tr}$  should maximized even though (15) demonstrated higher gain for lower  $T_{\rm tr}$ . The maximum  $T_{\rm tr}$  is limited to  $T_c/4$  to enable quadrature down-conversion.

The effect of the LO sample rate on the NF of the simulated passive mixer is shown in Fig. 11b. The plots labelled 'compensation OFF' compare (20) to simulations, when  $T_{\rm tr}$  is chosen to be  $T_c/4$ . The comparison shows good

Fig. 12. Polyphase filter structure: (a) discrete-time and a continuous-time equivalent, and (b) parallel pulse-skipped LO mixers and respective signals.

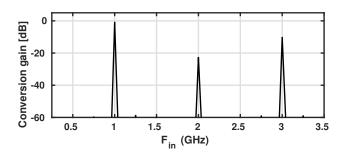

Fig. 13. Conversion gain with pulse-skipped LO (N=4) along with a polyphase filter structure having 4 branches. The polyphase structure prevents sub-harmonic conversion gains of the pulse-skipped LOs.

match between the analysis and simulation, and showcases the undesired NF increase in using the pulse-skipped LO mixers on their own. The NF can be kept constant while allowing low  $F_s$  and hence long delay range by implementing parallel mixers in a polyphase structure.

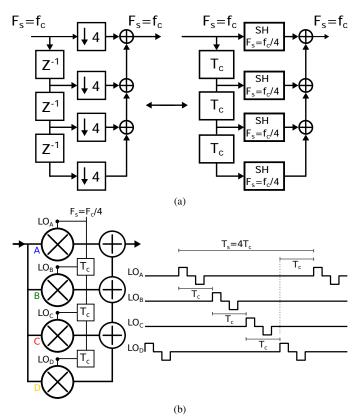

#### C. Polyphase Structure

The additional unwanted down-conversions and noise increase resulted from under-sampling of the RF input at  $f_c$ . The under-sampling is caused by selecting the pulse-skipped LO sample rate as  $F_s = f_c/N$ , which was done to allow longer beamforming delays. Polyphase structures with parallel branches, such as the ones in Fig. 12a, can be used to prevent the under-sampling while simultaneously allowing the long delays. the polyphase structures have a combined sample rate

which equals the sample rate of the branches multiplied by the number of branches. Due to the combined sample rate, a beamforming receiver which samples the input at  $f_c$  can be implemented with N polyphase branches, each sampling at  $f_c/N$ .

Fig. 12b shows a polyphase filter implemented with parallel mixers driven with pulse-skipped LO signals. The delays on the signal paths in Fig. 12a are placed on the LO path, and the resulting LOs for the branches A, B, C and D are shown. LO offset between branches equals one sample period of the combined sample rate, which is  $T_c$ . Simulated conversion gains for the polyphase mixers shown in Fig. 13 demonstrate that the additional sub-harmonic down-conversions introduced by the pulse-skipped LOs are removed. The remaining conversion gains in Fig. 13 are from the  $f_c$  of 1 GHz and it's harmonics. This harmonic behaviour is identical to typical direct conversion receivers with switched square wave down-conversion. Along with the sub-harmonic down-conversions, the noise increase is also prevented. Simulations with 'compensation ON' in Fig. 11b demonstrate how LO sample rate in the branches can be lowered without increasing the NF compared to one mixer with continuous LO  $(N = 1, F_s = f_c)$ . In this simulation, different number of parallel branches are used for different branch sample rates so that N branches are used for  $F_s = f_c/N$ . The simulated NF with the pulse-skipped LO and compensation branches matches one mixer driven with a continuous LO ( $F_s = f_c$ ), and the noise increase from the pulse-skipped LOs is removed.

#### D. Beamforming with Polyphase Mixers

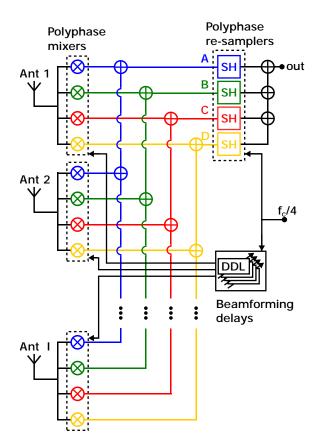

Since the sub-harmonic down-conversions and noise increase are not present, the polyphase structure enables the usage of pulse-skipped LOs for TTD beamforming with extended delays without aliasing. Fig. 14 shows the polyphase beamforming delay compensation branches for a receiver with I antennas. In the presented example each branch has an LO sample rate of  $f_c/4$ , which requires four parallel branches, A to D, and enables a maximum beamforming delay of 3  $T_c$  according to (19). Each branch realizes beamforming for the four antennas, and the outputs of the branches are summed to create an effective sample rate of  $f_c$ . The polyphase structure does not affect the beamforming functionality, as will be shown in the next section.

#### VII. VERIFICATION BY CIRCUIT SIMULATIONS

The re-sampling delay beamforming concept was verified with transistor level circuit simulations in 28-nm CMOS. A receiver front-end which implements the concept was designed for demonstrating the simultaneous operation of long delay range TTD beamforming with the pulse-skipped LO signals, and, the noise cancelling polyphase branches.

# A. Receiver Design

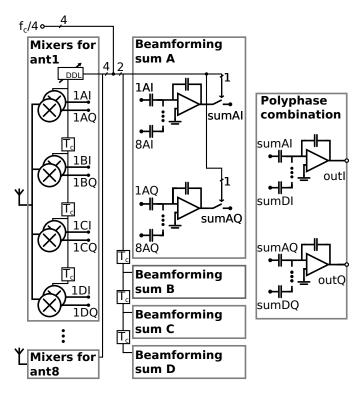

Fig. 15 describes the designed 8-antenna beamforming receiver front-end. A single-ended version of the implemented differential receiver is shown for simplicity. The chosen number of four parallel branches (A to D) enables pulse-skipped

Fig. 14. Receiver block diagram with four parallel re-sampling delay compensation branches. The branches are represented with separate colors for illustration.

LO sample rates of  $F_s = f_c/4$  as explained in Section VI. This  $F_s$  gives a beamforming delay tuning range from 0 to  $3T_c$ , as described by (18).

Each antenna is connected to four parallel passive mixers. Each mixer includes the circuit of Fig. 5 two times for quadrature down-conversion. The mixer switches are implemented with NMOS transistors whose gates are driven with two-inverter chain LO buffers. The switches are sized for 7 Ohm ON resistance as a trade-off between mixer noise and power consumption. The LO buffers are sized to support an RF frequency range of 1–6 GHz. The beamforming delay  $\tau_{DDL}$  is common for all mixers connected to the same antenna. In addition to  $\tau_{DDL}$ , the mixers of each branch are delayed by  $T_c$  from each other. The LO track-time is set to 25% of  $T_c$  and the LOs of Q mixers are delayed by  $0.25T_c$  compared to I. The output capacitors of the mixers are sized for a bandwidth of 200 MHz according to (17).

There are separate 200 MHz beamforming summation opamps for each of the four branches which sum the mixer outputs from corresponding mixers of all eight antennas. The summation is implemented by connecting the mixer output capacitors between the mixer switches and the virtual ground of the op-amp. This configuration allows both hold operation for the discrete-time baseband signal, and spatial filtering from beamforming already at the input of the first amplifier of the receiver, which helps with out-of-beam blocker tolerance. The feedback of these amplifiers are purely capacitive to prevent

Fig. 15. Receiver front-end implementation with re-sampling delay based beamforming.

the beamformed output from discharging over time. The output only changes when one of the mixers is active, which allows the following re-sampling operation to complete the true-time-delays. The beamforming summation op-amps' 1/f and thermal noise are significantly higher than the mixer switches' noise contribution, and therefore mainly set the NF of the receiver. The gain of the op-amp is set by the ratio of the mixer and feedback capacitors. A 20 dB gain was chosen to suppress the noise contribution from the polyphase combination op-amp.

The beamformed outputs are combined to prevent aliasing as explained in Section VI-C. Outputs from the four beamforming summation op-amps are connected to the polyphase combination op-amps through re-samplers. All the op-amps used in the receiver are identical. The re-samplers are implemented with simple NMOS switches with inverter buffering for the clocks. Again, the polyphase combination setup has discrete-time operation. The re-sampled voltages are stored on capacitors connected to the virtual ground of the polyphase combination op-amp, and the feedback is capacitive to avoid discharging during hold time. The feedback capacitor was sized for unity gain.

A layout was drawn to estimate the area consumption of the receiver. The area required for one antenna input including the shared amplifiers and re-sampling is 0.13 mm<sup>2</sup>. The estimated area consumption is orders of magnitude lower than the published passive solutions which were discussed in II-D, and hence large arrays can be supported. The simulations in the following section do not include layout parasitics.

Fig. 16. Squint mitigation demonstrated with transistor-level simulation of the designed beamforming front-end: (a) beamforming with phase shifts causing beam squint, and (b) beamforming with true-time-delay where beam squint is mitigated.

# B. Simulation Results

TTD beamforming with the receiver is demonstrated with simulations in Fig. 16, for a relative bandwidth of 20%. The center frequency  $f_c$  is selected as 2 GHz and the antenna spacing is  $\lambda_c/2$ . The upper and lower band edges are at 200 MHz offsets from the center frequency. Fig. 16a shows a phase shift beamforming comparison result, which is achieved with the same circuit by bypassing the re-sampling switch, i.e. keeping it in ON state. Bypassing the re-sampling reduces the receiver to an LO tuning phase shift beamformer, and as expected, squinting is visible in this phase shift mode. Fig. 16b depicts squint free beamforming for the TTD beamforming mode where the re-samplers are clocked as intended. The removal of squint verifies that the TTD operation is unaffected by the polyphase structure. The longer-than- $T_c$  delay range of the pulse-skipped LO is also verified, since the delay required for the 8-antenna array and the beamforming angle of 50 degrees is 2.68  $T_c$ , according to (1). The beamforming simulations were done with the four parallel branches enabled, verifying that the beamforming delay range is unaffected by the polyphase structure.

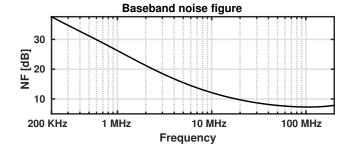

Fig. 17 depicts the simulated polyphase noise cancellation operation. As derived in Section VI-B, lowering the LO sample rate while using only one mixer branch increases the noise figure. The transistor level simulations verify the increase, as shown in the plot with polyphase compensation OFF. Lower sample rates lead to an increasingly higher NF compared to

$\begin{tabular}{l} TABLE\ I\\ SIMULATED\ PERFORMANCE\ OF\ THE\ BEAMFORMING\ FRONT-END\\ \end{tabular}$

| Technology                        | 28nm FD-SOI CMOS                    |

|-----------------------------------|-------------------------------------|

| Supply voltage                    | 1 V                                 |

| Delay method                      | Re-sampling                         |

| Delay range                       | $3*T_c$ (absolute delay             |

|                                   | scales with $f_c$ )                 |

| Baseband BW                       | 200 MHz                             |

| Power per antenna                 | $4 \text{ mW } (f_c = 3\text{GHz})$ |

| Power, common for all antennas    | 35.6 mW (no dependance on $f_c$ )   |

| Power, complete 8-input front-end | 67.6 mW ( $f_c = 3\text{GHz}$ )     |

| Noise Figure                      | 8.5 dB                              |

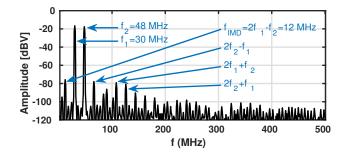

| In-band IIP3                      | -8.4 dBm                            |

| Out-of-band IIP3                  | 0.52 dBm                            |

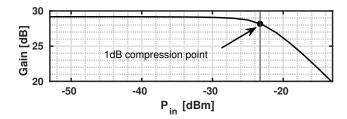

| 1 dB compression point            | -23.3 dBm                           |

the continuous LO case of  $F_s=f_c=2\,$  GHz. In the simulation with compensation ON, additional branches are enabled to keep the effective sample rate as  $f_c$ . With the proposed polyphase compensation, the NF of the receiver is unaffected by the LO sample rate. The baseline NF of 8.5 dB is dominated by the first first baseband amplifiers used for the beamforming summation. The NF as a function of the baseband frequency is shown in Fig. 18. Since the NF in Fig. 17 stays within 0.5 dB of the continuous LO case, the polyphase structure is shown to function as expected. Hence, the structure enables increased beamforming delays without affecting NF.

Performance of the simulated receiver front-end is listed in Table I. The chosen delay tuning range of  $3T_c$  is enough to cover TTD beamforming for an 8-antenna array. Since the delays scale with  $T_c$ , the supported number of antennas is the same regardless of frequency, which defines the absolute antenna spacing of  $\lambda_c/2$ . For example at 1 GHz this delay range is 3 ns. The baseband bandwidth of the receiver is 200 MHz, which with quadrature demodulation gives a 400 MHz RF bandwidth. This bandwidth was chosen to showcase TTD beamforming and is selected with the mixer's sampling capacitor size according to Section V-C. The only bandwidth limitation from the re-sampling delay is at  $f_c/2$  due to Nyquist limit. The input referred 1 dB compression point is -23.3, and the related gain sweep is shown in Fig. 19. With the beam maximum at 30 degrees, we add an in-band blocker to a zero at 16 degrees. This results in improving the blocker compression by 13.3 dB compared to a blocker at the beam direction. This improvement in compression at the beam zero is limited by the linearity of the summing amplifier The in-band IIP3 of -8.4 dBm is calculated from the output spectrum shown in Fig. 20. The two input tones at 30 MHz and 48 MHz above the carrier frequency of 2 GHz are selected such that they are in-band at both RF and baseband. The in-band IIP3 is calculated from the intermodulation tone at 12 MHz. Out-ofband IIP3 is simulated similarly, with tones at 245 MHz and 392MHz offsets and with  $f_c$  of 2 GHz. With these tones, the intermodulation falls to 98 MHz which is inside the baseband bandwidth of the receiver.

The proposed receiver can be scaled efficiently in terms of power consumption. Since the beamforming summation and polyphase combination amplifiers are common for the

Fig. 17. Transistor-level simulation demonstrating the effectiveness of noise-compensating polyphase structure in keeping the NF low when using pulse-skipped LO, regardless of the lowered sample rates due to pulse-skipped LO.

Fig. 18. Noise figure of the transistor-level circuit as a function of the baseband frequency.

different antenna inputs, the power consumption of the frontend does not increase linearly with the number of antennas. At 3.56 mW each, these ten amplifiers consume a large portion of the total simulated 67.6 mW 8-antenna front-end power. Only components on the signal path specific to each antenna input are its mixers and related LO buffering, which were simulated to consume 4 mW per antenna. Due to the lowered sample rate of the LOs, the combined buffering power of the polyphase mixers matches only one passive quadrature mixer driven with continuous LO. Since this power required for additional antennas is small, the proposed front-end is promising for TTD beamforming receivers with large number of antennas.

#### VIII. CONCLUSIONS

This paper presented a true-time-delay beamforming receiver, which can be used for squint-free wideband analog domain part of hybrid beamforming. The beamforming delays are implemented with delayed re-sampling of the discrete-time output of a passive mixer. The re-sampling delay on the analog signal path is controlled with a digital delay line, thus taking advantage of the increasing timing accuracy of CMOS technologies.

The delay tuning range is set by the sample rate of these signals. Introduced pulse-skipped LO signals were shown to increase the delay range to several  $T_c$ . Since  $T_c$  scales with the carrier frequency, the proposed TTD beamforming can support arrays with large number of antennas even at low frequencies where  $\lambda_c/2$  is long. A polyphase structure was demonstrated to prevent noise increase resulting from the lowered sample rate of pulse-skipped LOs.

Fig. 19. Input power sweep for the 1 dB compression point of the transistor level circuit.

Fig. 20. Two-tone linearity test for in-band IIP3. Down-converted output spectrum of the transistor level-circuit. Input tones are at 30 and 48 MHz offsets from the 2 GHz carrier.

A simultaneous operation of the polyphase structure and beamforming with delays over  $T_c$  was verified with transistor level receiver simulations. Squint-free TTD beamforming was demonstrated for a relative RF bandwidth of 20%. The pulse-skipped LOs required for covering the beamforming delay range were shown to not increase the NF of the receiver when the polyphase branches were used. The power consumption per antenna in the receiver is low at only 4 mW, which makes the proposed TTD beamforming feasible for large arrays.

#### REFERENCES

- [1] I. Ahmed, H. Khammari, A. Shahid, A. Musa, K. S. Kim, E. De Poorter, and I. Moerman, "A survey on hybrid beamforming techniques in 5G: Architecture and system model perspectives," *IEEE Commun. Surveys Tuts.*, vol. 20, no. 4, pp. 3060–3097, Fourthquarter 2018.

- [2] L. Wu, H. F. Leung, A. Li, and H. C. Luong, "A 4-element 60-ghz cmos phased-array receiver with beamforming calibration," *IEEE Trans. Circuits Syst. I*, vol. 64, no. 3, pp. 642–652, March 2017.

- [3] Y. Antonov, M. Zahra, K. Stadius, Z. Khonsari, I. Kempi, T. Miilunpalo, J. Inkinen, V. Unnikrishnan, L. Anttila, M. Valkama, M. Kosunen, and J. Ryynänen, "A delay-based LO phase-shifting generator for a 2-5ghz beamsteering receiver in 28nm cmos," in ESSCIRC 2019 - IEEE 45th European Solid State Circuits Conference (ESSCIRC), Sep. 2019, pp. 389–392.

- [4] V. Szortyka, K. Raczkowski, M. Kuijk, and P. Wambacq, "A wideband beamforming lowpass filter for 60 ghz phased-array receivers," *IEEE Trans. Circuits Syst. I*, vol. 62, no. 9, pp. 2324–2333, Sep. 2015.

- [5] S. Jang, J. Jeong, R. Lu, and M. P. Flynn, "A 16-element 4-beam 1 ghz IF 100 MHz bandwidth interleaved bit stream digital beamformer in 40 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1302–1312, May 2018.

- [6] S. Jang, R. Lu, J. Jeong, and M. P. Flynn, "A 1-ghz 16-element four-beam true-time-delay digital beamformer," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1304–1314, May 2019.

- [7] J. Jeong, N. Collins, and M. P. Flynn, "A 260 mhz if sampling bit-stream processing digital beamformer with an integrated array of continuoustime band-pass δσ modulators," *IEEE J. Solid-State Circuits*, vol. 51, no. 5, pp. 1168–1176, May 2016.

- [8] S. H. Talisa, K. W. O'Haver, T. M. Comberiate, M. D. Sharp, and O. F. Somerlock, "Benefits of digital phased array radars," *Proc. IEEE*, vol. 104, no. 3, pp. 530–543, March 2016.

- [9] S. Mondal, R. Singh, A. I. Hussein, and J. Paramesh, "A 25–30 ghz fully-connected hybrid beamforming receiver for MIMO communication," IEEE J. Solid-State Circuits, vol. 53, no. 5, pp. 1275–1287, May 2018.

- [10] S. Golabighezelahmad, E. Klumperink, and B. Nauta, "A 1-4 ghz 4x4 MIMO receiver with 4 reconfigurable orthogonal beams for analog interference rejection," 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), pp. 339–342, June 2019.

- [11] L. Zhang and H. Krishnaswamy, "24.2 a 0.1-to-3.1ghz 4-element MIMO receiver array supporting analog/RF arbitrary spatial filtering," 2017 IEEE International Solid-State Circuits Conference (ISSCC), pp. 410– 411. Feb 2017.

- [12] S. Jain, Y. Wang, and A. Natarajan, "A 10ghz cmos RX frontend with spatial cancellation of co-channel interferers for MIMO/digital beamforming arrays," 2016 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), pp. 99–102, May 2016.

- [13] S. Blandino, G. Mangraviti, C. Desset, A. Bourdoux, P. Wambacq, and S. Pollin, "Multi-user hybrid MIMO at 60 ghz using 16-antenna transmitters," *IEEE Trans. Circuits Syst. I*, vol. 66, no. 2, pp. 848–858, Feb 2019.

- [14] S. K. Garakoui, E. A. M. Klumperink, B. Nauta, and F. E. van Vliet, "Phased-array antenna beam squinting related to frequency dependency of delay circuits," in 2011 8th European Radar Conference, Oct 2011, pp. 416–419.

- [15] R. Rotman, M. Tur, and L. Yaron, "True time delay in phased arrays," Proc. IEEE, vol. 104, no. 3, pp. 504–518, March 2016.

- [16] M. Cho, I. Song, and J. D. Cressler, "A true time delay-based SiGe bidirectional T/R chipset for large-scale wideband timed array antennas," in 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), June 2018, pp. 272–275.

- [17] N. Rajesh and S. Pavan, "Design of lumped-component programmable delay elements for ultra-wideband beamforming," *IEEE J. Solid-State Circuits*, vol. 49, no. 8, pp. 1800–1814, Aug 2014.

- [18] S. K. Garakoui, E. A. M. Klumperink, B. Nauta, and F. E. van Vliet, "Compact cascadable gm-C all-pass true time delay cell with reduced delay variation over frequency," *IEEE J. Solid-State Circuits*, vol. 50, no. 3, pp. 693–703, March 2015.

- [19] S. K. Garakoui, E. A. M. Klumperink, B. Nauta, and F. F. E. V. Vliet, "A 1-to-2.5ghz phased-array IC based on gm-RC all-pass time-delay cells," in 2012 IEEE International Solid-State Circuits Conference, Feb 2012, pp. 80–82.

- [20] I. Mondal and N. Krishnapura, "A 2-ghz bandwidth, 0.25-1.7 ns true-time-delay element using a variable-order all-pass filter architecture in 0.13 μm cmos," *IEEE J. Solid-State Circuits*, vol. 52, no. 8, pp. 2180–2193, Aug 2017.

- [21] R. J. Mailloux, Phase Array Antenna Handbook. Artech House, 2005.

- [22] T. Chu and H. Hashemi, "True-time-delay-based multi-beam arrays," IEEE Trans. Microw. Theory Techn., vol. 61, no. 8, pp. 3072–3082, Aug 2013.

- [23] E. Ghaderi, A. Sivadhasan Ramani, A. A. Rahimi, D. Heo, S. Shekhar, and S. Gupta, "An integrated discrete-time delay-compensating technique for large-array beamformers," *IEEE Trans. Circuits Syst. I*, vol. 66, no. 9, pp. 3296–3306, Sep. 2019.

- [24] F. Hu and K. Mouthaan, "A 1-20 ghz 400 ps true-time delay with small delay error in 0.13 μm cmos for broadband phased array antennas," in 2015 IEEE MTT-S International Microwave Symposium, May 2015, pp. 1–3.

- [25] I. Sourikopoulos, A. Frappé, A. Cathelin, L. Clavier, and A. Kaiser, "A digital delay line with coarse/fine tuning through gate/body biasing in 28nm fdsoi," in ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference, Sep. 2016, pp. 145–148.

- [26] M. C. M. Soer, E. A. M. Klumperink, P. T. de Boer, F. E. van Vliet, and B. Nauta, "Unified frequency-domain analysis of switched-series-RC passive mixers and samplers," *IEEE Trans. Circuits Syst. I*, vol. 57, no. 10, pp. 2618–2631, Oct 2010.

Kalle Spoof was born in Helsinki, Finland, in 1990. He received the M.Sc. degree in electrical engineering from Aalto University, Espoo, in 2017. He is currently pursuing the Ph.D. degree as an industrial doctoral candidate with Saab in cooperation with the Department of Electronics and Nanoengineering in Aalto University. His research interests include wideband true-time-delay beamforming receivers.

Marko Kosunen (S'97–M''07) received his M.Sc, L.Sc and D.Sc (with honors) degrees from Helsinki University of Technology, Espoo, Finland, in 1998, 2001 and 2006, respectively. He is currently a Senior Researcher at Aalto University, Department of Electronics and Nanoengineering. Academic years 2017-2019 he visited Berkeley Wireless Reserarch Center, UC Berkeley, on Marie Sklodowska-Curie grant from European Union. He has authored and co-authored more than 90 journal and conference papers and holds several patents. His current research

interests include programmatic circuit design methodologies, digital intensive and time-based transceiver circuits, and medical sensor electronics.

Vishnu Unnikrishnan (S'12-M'17) received the B.Tech. degree in electronics and communication engineering from Kannur University, India, in 2004, the M.Sc. degree in electrical engineering, and the Ph.D. degree in integrated circuits and systems both from Linköping University, Sweden, in 2012 and 2016 respectively. Since 2017, he is a postdoctoral researcher at the dept. of Electronics and Nanoengineering, Aalto University, Finland. From 2004 to 2009, he was with Bosch Engineering and Business Solutions. His research interests

include energy-efficient integrated circuits and systems, digital-intensive radio/wire transceiver architectures, digital implementation/enhancement of analog/mixed-signal functions in integrated circuits, and time-domain signal processing.

Mahwish Zahra received the B.Eng. degree in electronics from National University of Sciences and Technology, Islamabad, Pakistan and M.Sc.(Tech.) degree in electrical engineering from Tampere University of Technology, Tampere, Finland, in 2011 and 2016 respectively. She is currently pursuing the D.Sc.(Tech.) degree at Aalto University school of Electrical Engineering. Her current research interests are mixed-signal RF circuits and receiver front-end design.

Jussi Ryynänen (S'99—M'04—SM'16) was born in Ilmajoki, Finland, in 1973. He received the M.Sc. and D.Sc. degrees in electrical engineering from the Helsinki University of Technology, Espoo, Finland, in 1998 and 2004, respectively. He is a full professor and the Head of the Department of Electronics and Nanoengineering, Aalto University, Espoo, Finland. He has authored or co-authored more than 140 refereed journal and conference papers in analog and RF circuit design. He holds seven patents on RF circuits. His research interests are integrated

transceiver circuits for wireless applications. Prof. Ryynänen has served as a TPC Member for the European Solid-State Circuits Conference (ESSCIRC) and the IEEE International Solid-State Circuits Conference (ISSCC), and as a Guest Editor for the IEEE Journal of Solid-State Circuits.

Kari Stadius (S'95–M"03) received the M.Sc., Lic. Tech., and Doctor of Science degrees in electrical engineering from the Helsinki University of Technology, Helsinki, Finland, in 1994, 1997, and 2010, respectively. He is currently working as a staff scientist at the Department of Micro- and Nanosciences, Aalto University School of Electrical Engineering. His research interests include RF and microwave circuits for communications with especial emphasis on frequency synthesis, analog and mixed-mode circuit design. He has authored or coauthored over

a hundred refereed journal and conference papers in the areas of analog and RF circuit design.