# Ultrafast Synaptic Events in a Chalcogenide Memristor

SUBJECT AREAS: ELECTRONIC DEVICES INFORMATION STORAGE SPIKE-TIMING-DEPENDENT PLASTICITY

**ELECTRONIC PROPERTIES AND**

Yi Li<sup>1,2\*</sup>, Yingpeng Zhong<sup>1,2\*</sup>, Lei Xu<sup>1,2\*</sup>, Jinjian Zhang<sup>1,2</sup>, Xiaohua Xu<sup>1,2</sup>, Huajun Sun<sup>1,2</sup> & Xiangshui Miao<sup>1,2,3</sup>

Received

10 December 2012

Accepted 20 March 2013

MATERIALS

Published 8 April 2013

Correspondence and requests for materials should be addressed to X.M. (miaoxs@mail. hust.edu.cn)

\*These authors contributed equally to this work. <sup>1</sup>Wuhan National Laboratory for Optoelectronics, Huazhong University of Science and Technology, Wuhan 430074, China, <sup>2</sup>School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China, <sup>3</sup>Wuhan National High Magnetic Field Center, Huazhong University of Science and Technology, Wuhan 430074, China.

Compact and power-efficient plastic electronic synapses are of fundamental importance to overcoming the bottlenecks of developing a neuromorphic chip. Memristor is a strong contender among the various electronic synapses in existence today. However, the speeds of synaptic events are relatively slow in most attempts at emulating synapses due to the material-related mechanism. Here we revealed the intrinsic memristance of stoichiometric crystalline  $Ge_2Sb_2Te_5$  that originates from the charge trapping and releasing by the defects. The device resistance states, representing synaptic weights, were precisely modulated by 30 ns potentiating/depressing electrical pulses. We demonstrated four spike-timing-dependent plasticity (STDP) forms by applying programmed pre- and postsynaptic spiking pulse pairs in different time windows ranging from 50 ms down to 500 ns, the latter of which is  $10^5$  times faster than the speed of STDP in human brain. This study provides new opportunities for building ultrafast neuromorphic computing systems and surpassing Von Neumann architecture.

umankind has never stopped his footsteps to pursue a machine that can function like the human brain, which is the most sophisticated organ in existence. The large number of neurons (10<sup>11</sup>) and synapses (10<sup>15</sup>) in the brain, along with the network complexity of the nervous system may be the biggest obstacles to creating such a machine. Although their design has benefited greatly from the scaling of complementary metaloxide semiconductor (CMOS) technology, neuromorphic circuits and chips are still hindered by challenges related to area and power consumption restrictions. Tens of transistors and capacitors are required to build a neuron, a synapse and a learning module<sup>1</sup>. In particular, when considering the high-level connections of neuronal dynamics, a large area on existing neuromorphic chips is dedicated to synapses, whereas neurons occupy only a small portion of a synaptic matrix. To the end, a lack of compact and power-efficient electronic synapses could be a key factor affecting the development of brian scale neuromorphic systems<sup>2</sup>.

In recent years, researchers have demonstrated the feasibility of various nanoscale electronic devices that emulate representative neuronal and synaptic functions, such as synaptic modifications, excitatory/inhibitory postsynaptic currents and memory consolidation<sup>3–16</sup>. The resistance or conductance of the electronic synapses in these physical implementations represents the synaptic efficacy (synaptic weight), which is the connection strength between neurons<sup>17</sup>. The Hebbian spike-timing-dependent plasticity (STDP) rule has been a commonly demonstrated biological function in various electronic synapses<sup>3-6,13-16</sup>. This function has been experimentally observed in a wide variety of neural circuits in different species, ranging from locusts to humans, and is regarded as the basis for learning and memory<sup>18–20</sup>. Among currently available devices, chalcogenide device is a competitive candidate for combining data storage and processing in a manner similar to neural cognitive processing<sup>21,22</sup>. In addition to being used as a non-volatile memory because of the reversible switching between chalcogenide's amorphous and crystalline states<sup>23–25</sup>, chalcogenide device is also capable of acting as an arithmetic processor<sup>26</sup>, as a result of the natural energy accumulation property. Kuzum et al. recently utilized the partial crystallization property of chalcogenide controlled by different RESET and SET pulses to mimic STDP and achieved picojoulelevel energy consumption<sup>27</sup>. However, the high precision programming of resistance states, which is crucial for emulating the analog nature of synaptic efficacy, can be perturbed by percolation phenomena. Moreover, most electronic synapses neglect the tuning of the STDP time window, and duplicating the biological window with a time scale on the order of tens of milliseconds is obviously insufficient for creating future ultrafast neuromorphic systems.

We uncovered the intrinsic memristance of stoichiometric crystalline  $Ge_2Sb_2Te_5$  (c-GST), a mature chalcogenide material used for non-volatile memory. The memristive characteristics facilitated fine resistance programming through the application of polarity electrical pulses, which were capable of emulating synaptic weight modification. We demonstrated four STDP forms using programmed preand postsynaptic spike pairs and tuned the STDP time window from the order of milliseconds down to nanoseconds, addressing the potential for ultrafast synaptic events to occur outside the brain. Note that our approach focused on the use of the crystalline state of GST, which is very different from the methods used by Kuzum et al. and Suri et al. $^{27,28}$ .

## Results

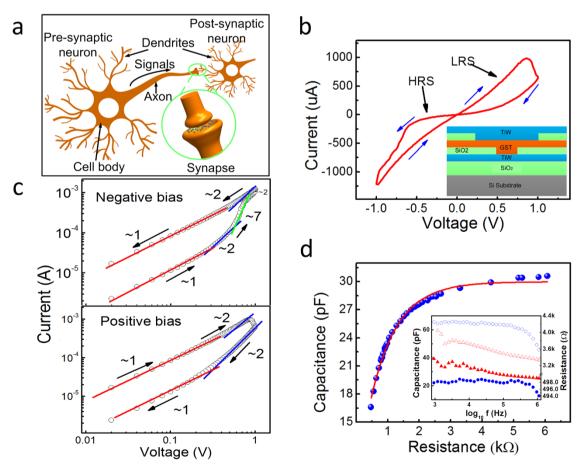

Memristance of crystalline  $Ge_2Sb_2Te_5$ . We fabricated a typical T-structure GST based memristor using micro/nano fabrication processes (See Methods). The two terminal device is used as the electronic synapse. We built up an electrical characterization system to perform electrical measurements (See Methods and Supplementary Fig. S1). The device switched between the amorphous and crystalline states and displayed good endurance without failure (Supplementary Fig. S2). To study the memristance of c-GST, the device was first set to the crystalline state at several kilo-ohms using a DC voltage sweep. Next, the hysteresis and asymmetry memristive characteristics were observed under the clockwise voltage sweep  $0 \rightarrow -1 \text{ V} \rightarrow 0 \rightarrow 1 \text{ V} \rightarrow 0$  (Fig. 1b) with a current compliance of 100 mA. Our results

indicated that the resistance could be modulated within a certain range depending on the voltage polarity. The highest resistance state (HRS) in the c-GST was below 10 k $\Omega$ , while the lowest resistance state (LRS) was approximately 500  $\Omega$ . The resistance states were all measured at a read current of 1  $\mu A$  during the electrical measurements.

To further analyze the memristive mechanism, different conduction models were used to fit the nonlinear I–V curve²9. Thermionic emission (I  $\propto V$ ), Schottky emission (ln  $I \propto \sqrt{V}$ ), Poole-Frenkel emission (ln  $I/V \propto \sqrt{V}$ ), and Fowler-Nordheim quantum tunneling (ln  $I/V^2 \propto V^{-1}$ ) were not good fits for the curve; space charge limited conduction (SCLC) ( $I \propto V^2$ ) was the best model for interpreting the memristance of c-GST and can be described by

$$I = (\varepsilon \mu_0 N_c e^{-E/kT} / N_t d^3) V^2, \tag{1}$$

where  $\varepsilon$  is the dielectric constant,  $\mu_0$  is the carrier mobility,  $N_c$  is the density of states in the valence band, E is the effective trapping potential, k is the Boltzmann's constant, T is the temperature,  $N_t$  is the number of traps, d is the effective film thickness<sup>30–33</sup>. The slopes of the double-logarithmic plots of negative bias and positive bias were analyzed (Fig. 1c). The low voltage region (<–0.25 V) was dominated by linear Ohmic conduction. At subsequent higher voltages, the I–V relationship agreed with the trap-controlled SCLC, as has been observed in other memristive materials<sup>30,32,34</sup>. Such memristive phenomena could account for the defects in the c-GST. Although GST has a stable hexagonal structure, the fast phase transformation

Figure 1 | Intrinsic memristance of a crystalline GST-based synapse. (a) Schematic illustration of a typical biological neuron possessing a cell body (soma), an axon and dendrites. The synapses are the connections between neurons. (b) I-V characteristics measured by DC double sweeping, exhibiting a memristive hysteresis loop. The blue arrows indicate the voltage sweeping directions, and the inset shows the structure of the chalcogenide synapse. (c) Double-logarithmic plot of negative bias (upper) and positive bias (lower) regions exhibiting SCLC behavior. (d) Dependence of capacitance on resistance. The inset shows the frequency dependence of  $R(\omega)$  (circle symbols) and  $C(\omega)$  (triangle symbols) at zero bias for HRS (open symbols) and LRS (solid symbols).

proceeds between the amorphous and metastable distorted rocksalt structure with a face-centered-cubic (fcc) lattice, which has been confirmed by high-resolution transmission electron microscopy and X-ray diffraction<sup>35,36</sup>. In the GST fcc structure, Te atoms occupy the anionic sites, while the cationic sites are occupied randomly by Ge and Sb atoms, with 20% vacancies<sup>35–38</sup>. These vacancies and defects at grain boundaries create deep energy levels in the band gap between the conduction and valence bands, and act as charge trap centers. During the application of external negative voltage bias in this experiment, the injection electrons were captured by the vacancies, filling the deep-level traps. The conduction behavior in the positive bias region indicated the transition from trap-filled to trap-unfilled SCLC associated with charge emission. These processes resulted in the variation of resistance, which occured simultaneously with a change in capacitance.

Figure 1d shows that when the resistance varied from 474  $\Omega$  to 6.07 k $\Omega$ , the capacitance increased from 16.6 to 30.6 pF, suggesting a change in the space-charge distribution. Meanwhile, the inverse relationships between resistance  $R(\omega)$  or capacitance  $C(\omega)$  and the frequency also support the model<sup>31,39</sup>, as shown in the inset of Fig. 1d. The high frequency disturbed the establishment of the space charge distribution, and the trapped and free carriers could not reach a thermal equilibrium, resulting in the increase in current. Therefore, the  $R(\omega)$  and  $C(\omega)$  values at higher  $\omega$  were less than the respective low- $\omega$  values.

Although bipolar resistive switching phenomena have been reported in GST, they are all based on the conductive filament theory<sup>40–42</sup>. The memristive characteristics of c-GST are intrinsic characteristics. Lattice defects, mainly vacancies, and defects at grain boundaries appear as a natural cause of the memristance.

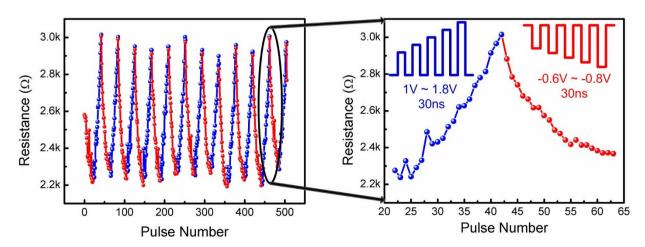

# Modification of synaptic efficacy and implementation of ultrafast STDP. The postsynaptic conductance changes as ion channels open or close when they are induced by potentiating or depressing postsynaptic potentials. To emulate this synaptic weight modification, the conductance of a chalcogenide memristor was used to represent the synaptic weight, and positive and negative pulses were applied to modulate the conductance. The shortest pulses that we used are presented in Fig. 2. First, the device was set to an initial crystalline state of approximately 2.6 k $\Omega$ using a SET pulse (2 V, 100 ns). The negative pulses led to the increase in conductance that represented potentiating spikes, while the positive pulses represented depressing spikes. The pulse widths and rise and fall times were fixed at 30, 10

and 10 ns, respectively. The amplitudes of 20 consecutive poten-

tiating spikes increased from -0.6 to -0.8 V with a 10-mV step,

and the amplitude of 20 consecutive depressing spikes increased from 1 to 1.8 V with a 40-mV step. Note that the 1.8-V, 30-ns pulse was not sufficient to induce the phase change from crystalline to amorphous. The resistance exhibited a gradual repeatable change ranging from 2.2 to 3.0 k $\Omega$ , and the mean resistance change per pulse was approximately 40  $\Omega$ , which indicates a relative accuracy of 1.8%. Theoretically, a more accurate modulation could be possible by using an adaptable variation-tolerant algorithm<sup>43</sup>. Based on the fine synaptic weight modulation that occurred in response to pulses of different polarities, more complex synaptic events could be implemented in the chalcogenide synapse.

Biologically, as Hebb stated, "Neurons that fire together, wire together"44. STDP, as a refinement of Hebb's theory, is considered to be a possible first law of synaptic plasticity. STDP refers to that the precise relative timing of pre- and postsynaptic spikes significantly affects the sign and magnitude of long-term synaptic modification, which have been found to vary in different cases 19,45,46. (i) In temporal windows for excitatory to excitatory connections, long-term potentiation (LTP) occurs if the presynaptic action potential precedes the postsynaptic firing ( $\Delta t > 0$ , where  $\Delta t$  is the relative time interval of the pre- and postsynaptic spikes), whereas presynaptic activity that followes postsynaptic spike ( $\Delta t < 0$ ) causes long-term depression (LTD). (ii) In windows for excitatory to inhibitory connections, LTP and LTD can be induced in the opposite manner. In some other cases, synaptic modification depends only on the relative timing amount of the pre- and postsynaptic spikes, but not on their orders. For example, (iii) a symmetric Hebbian learning rule occurs at the neuromuscular junction, which means that potentiation occurs when  $\Delta t$  is  $\sim 0$  and depression when  $\Delta t$  moves away from 0. Moreover, (iv) in synapses between spiny stellate neurons in neocortexlayer 4, depression occurs at all values of  $\Delta t$ . Biological experimental results indicated that these different STDP forms could be ascribed to the influence of different spikes, reflecting the complexity of the respective underlying cellular mechanisms, and that they have a variety of functional consequences in neural information processing.

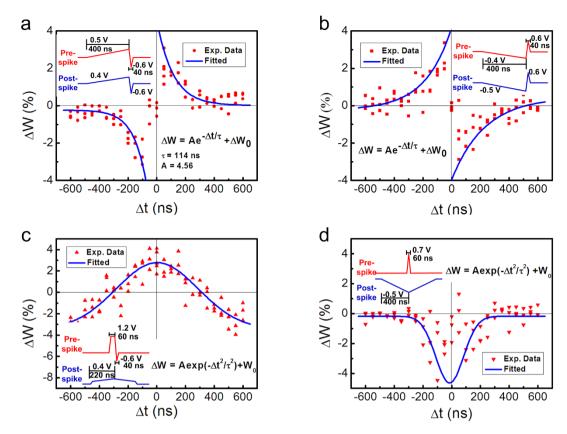

These four different STDP forms with nanosecond-scale time windows were successfully implemented in our chalcogenide synapse (Fig. 3) by following a typical spike paring protocol used in biological synaptic studies and in other electronic synapses. These synaptic events were demonstrated in a critical time window of approximately 500 ns, which is  $10^5$  times faster than the human brain.  $\Delta w$  represents the percent change in synaptic weight i.e., the device conductance, representing the long-term nonvolatile modification of the synaptic efficacy as a function of the time interval  $\Delta t$ . For example, LTP occurs when  $\Delta t > 0$  and LTD occurs when  $\Delta t < 0$

Figure 2 | Pulse-driven memristive behavior. The conductance increases or decreases in response to negative or positive pulses, respectively, representing synaptic weight modulation due to potentiating or depressing pulses. The pulse amplitudes vary with identical 30-ns widths and 1-s pulse intervals.

Figure 3 | Implementation of STDP with nanosecond-scale time windows in the chalcogenide synapse with the (a), antisymmetric Hebbian learning rule, (b), antisymmetric anti-Hebbian learning rule, (c), symmetric Hebbian learning rule and (d), symmetric anti-Hebbian learning rule. The red dots indicate the experimental data and the blue lines are the fitted curves. The insets show the pre- and postsynaptic spike schemes and fitting functions.

in a typical antisymmetric Hebbian learning rule as shown in Fig. 3a, and the left upper inset shows the shapes of the pre- and postsynaptic spikes. The maximum amount of synaptic modification which reached 3.26%, occured when the paired spikes were separated by only a few ns, and the evoked plasticity decreased to nearly zero as  $\Delta t$  increased. A total of 75 spike pairs were applied in our measurements, and the STDP data had statistical scatter, which also exists in biological synapses.

When we applied the pulse stimulus to drive the device resistance variation, a threshold voltage  $V_{\theta}$  exists, approximately 0.6 V. The pulse amplitudes of all pre- and post-spikes in all STDP experiments were less than 0.6 V, which are below the threshold, that means a single pre- or postspike could not modify the weight. When the pre- and post-spike arrived at the device in an opposite direction, the amplitude of the total voltage at the device may exceed the threshold, leading to a resistance variation. The effective flux that can influence the resistance variation should be

$$\varphi(t) = \int V_E dt, \qquad (2)$$

Where

$$V_{E} = \begin{cases} V_{pre} - V_{post} + V_{\theta} & V_{pre} - V_{post} < -V_{\theta} \\ 0 & -V_{\theta} \le V_{pre} - V_{post} \le V_{\theta} \\ V_{pre} - V_{post} - V_{\theta} & V_{pre} - V_{post} > V_{\theta} \end{cases} , \quad (3)$$

As  $\Delta t$  increases, the effective voltage  $V_E$  and effective time both decrease, leading to the decrease in effective flux, so the evoked synaptic weight change also decreases (Note that ns-level weight modulation does not equal to the ns-level STDP time window, see Supplementary Fig. S3 and Fig. S4).

STDP can be simplified in computational neuroscience using mathematical models by fitting it with an exponential function:

$$\Delta w = Ae^{-\Delta t/\tau} + \Delta w_0, \tag{4}$$

where A and  $\tau$  refer to the scaling factor and time constant of the STDP function, respectively, and  $\Delta w$  is a constant representing a non-associative component of the synaptic change<sup>47</sup>. Here A=4.56 and  $\tau=114$  ns for the LTP in antisymmetric Hebbian learning rule, whereas the time constant of the STDP window is of the order of tens of milliseconds for biological synapses. Additionally, the other three STPD forms could be implemented by modulating the shapes of the spike pairs. For example, the antisymmetric anti-Hebbian learning rule could be realized by applying the same spike pairs as those used in the Hebbian learning rule in a reversed temporal sequence (Fig. 3b). Moreover, the learning function for the symmetric Hebbian learning rule and symmetric anti-Hebbian learning rule could be expressed as a Gaussian function (Fig. 3c and Fig. 3d):

$$\Delta w = A \exp\left(-\Delta t^2/\tau^2\right) + \Delta w_0. \tag{5}$$

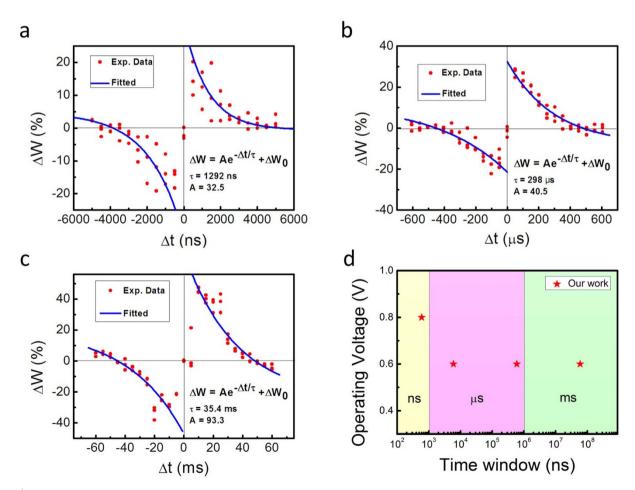

Tuning of the STDP time window. The above process allowed us to successfully implement ultrafast STDP events in a chalcogenide memristor. Furthermore, by employing the same spike coincidence strategy, we could easily tune the time constant of the STDP rules by modulating the pulse width and interval, which is critical to the application of electronic synapses in neuromorphic engineering. On one hand, synapses with various τ in different cortex locations or develop periods are related to different computational tasks and play instructive roles in neural functions<sup>48,49</sup>. For example, recent studies revealed that relative spikes separated by 25 ms or more promote synapse elimination in development as in adult plasticity.

When spikes are separated by 20 ms or less, the activity is perceived as synchronous, and elimination is prevented<sup>50</sup>. On the other hand, if the chalcogenide synapse allows the implementation of STDP on various temporal scales, meaning that the chalcogenide synapse respondes only to the pre- and postspike forms rather than to the spiking rate, circuit design flexibility could be improved while reducing the complexity of peripheral neuron circuits.

We demonstrated STDP forms with different time constants, as shown in Fig. 4 a-c. The time windows in these diagrams are 5 μs, 500 µs and 50 ms, respectively, the latter of which is comparable to biological values. The single spike pulse for the 5 µs STDP was modulated to approximate 5 µs width, whereas the shapes of the spike pairs for 500 µs and 50 ms were modulated to a sequence of step-up pulses with an identical 500-ns width and pulse intervals of 50 µs and 5 ms, respectively (details of the spike pairs, see Supplementary Fig. S5 and Fig. S6). The pulse width of the spikes were enlarged to provide a greater injection of charges. This enhancement of the charge-trapping amount broadened the resistance variation range, which led to an increase in the scaling factor. The increase in the the pulse intervals resulted in an increase in the time constant. After exponential fitting, the  $A/\tau$  for the 5 µs, 500 µs and 50-ms time window are 32.5/1292 ns, 40.5/298 µs and 93.3/35.4 ms, respectively.

Note that, biologically, the neurons always fire persistently and generate pre- and postsynaptic spike trains to affect the synaptic facilitation and depression. In our above STDP experiments, only

one pre- and post-spike pair was applied to evoke the change in synaptic weight, resulting a relative small  $\Delta w$ . When we increased the spike pair number, the evoked weight change also increased. Take the LTD in 500-ns time window for example, the largest synaptic weight change can reach -45% if we input 220 continous pairs of pre- and post-spikes (See Supplementary Fig. S7).

### **Discussion**

Compared with other emerging electronic synapses<sup>5,6,11,13,14,16,27</sup>, the analog chalcogenide synapse displayed the advantages of ultralow operation voltage, ultrafast synaptic events and feasibility of time window tuning (Fig. 4d). While chalcogenide devices have already demonstrated a drastic reduction in power and time requirements for operation<sup>51,52</sup>, the mature CMOS-compatible fabrication processes of chalcogenide materials enable us to intergrate the electronic synaptic matrix with traditional CMOS neuron chips with the goal of performing more complex cognitive functions in one chip, such as visual pattern cognition and associative learning<sup>28</sup>. And based on the network arthictecture (crossbar and 3D stacking), the important superiority of neural system, parrallelism, could be further investigated. In addition, the energy accumulation phenomenon associated with chalcogenide's amorphous state has been proposed to emulate neuronal threshold spiking behavior, which was verified in our memristor device (Supplementary Fig. S8 and Fig. S9). We envisage a complete neuron-synapse system being implemented in a

Figure 4 | Tuning of the STDP time window. (a) A 5  $\mu$ s time window with a time constant of 1.29  $\mu$ s. (b) A 500  $\mu$ s time window with a time constant of 298  $\mu$ s. (c) A 50-ms time window with a time constant of 35.4 ms. The time constant  $\tau$  is tuned by modulating the pulse width and interval. The increasing of scaling factor A results from the enhancement of the resistance change variation due to wider pulses that provide more injection charges. (d) Chalcogenide synapse shows its advantages: operating at ultralow voltage and tuning of the time window down to the nanosecond scale, whereas the time window of biological synapse is about 50 ms.

chalcogenide-based matrix, which could be an attractive option for the design of future neuromorphic system.

This study demonstrated that ultrafast synaptic events can be implemented in chalcogenide synapses. We revealed that the intrinsic memristive characteristics of crystalline GST originated from the charge trapping and releasing by defects in the material. The memristance offered us a foundation for emulating synaptic weight modulation, and we used it to implement four different STDP forms. Furthermore, the feasibility of STDP time window tuning in this material was also demonstrated from 50 ms to 500 ns, the latter of which is 105 times faster than the speed of STDP in human brain. In principle, the scaling up of the number of analog/plastic synapses with low power consumption and ultrafast response times is in urgent demand for further evolution of neuromorphic chips. We believe that the completely passive, non-volatile chalcogenide synapse is a strong contender for replacing the existing transistor- and capacitor-based electronic synapse and provides a promising method of surpassing Von Neumann architecture.

# **Methods**

Chalcogenide device fabrication. The chalcogenide device was fabricated on a Si substrate with a 1  $\mu m$  thick thermally grown SiO $_2$  layer. The confined structure (Fig. 1B inset) was fabricated using magnetron sputtering, photolithography and lift-off processes. The thicknesses of the bottom electrode (TiW), Ge $_2$ Sb $_2$ Te $_5$  (GST) film, SiO $_2$  insulator and top electrode (TiW) were 50, 150, 100 and 150 nm, respectively, and all deposited without the substrate heating. The background and working pressures for GST sputtering were below  $10^{-5}$  Pa and approximately 0.5 Pa. The GST deposition rate was approximate 0.5 nm/s at 30 W DC power. The contact area (1  $\mu m$  diameter) was patterned using photolithography. The GST and SiO $_2$  films were deposited subsequently using lift-off with supersonic vibration in acetone to remove the AZ5214 photoresist.

**Electrical characterization.** The electrical measurements of the chalcogenide device were conducted on a self-built electrical characterization system containing a semiconductor characterization system (Keithley 4200-SCS), an oscilloscope (Agilent Technologies DSO5012A), a Precision LRC Meter (Agilent E4980A) and a self-design PCB testing board, as shown in Fig. S1.

The pulse generator integrated in the system has the specifications of pulse duration, rising time and falling time ranging from 10 ns to 1 s, each portion of segment pulse, including duration, rising time and falling time, ranging from 20 ns to 1 s, and amplitude ranging from -5 to 5 V. AC pulse channel, DC current/voltage force and sense channels converge to a Keithley 4205 Remote Bias-Tee and output to memristor. The wire-bonded memristor chip is embedded in the PCB testing board, while two terminals of the testing boarding connected to two terminals of a selected memristor cell, respectively. In Fig. S1, Switch1 (SW1) to SW5 are selectively closed or opened. When only one channel is needed to send and sense signal, like IV curve sweeping and sending pulses to gradually change the resistance, SW1 is closed, the others are opened. When two channels are needed, like emulating STDP, SW2 is closed, the others are opened. When closing SW3 or SW4, wave forms of the corresponding nodes can be observed by oscilloscope.

To measure the capacity of the memristor device, the wire-bonded memristor chip is connected to the Precision LCR Meter though a Test Fixture (Agilent 6334A) applying 10 MHz, 10 mV small signal.

- 1. Rachmuth, G. & Poon, C. S. Transistor analogs of emergent iono-neuronal dynamics. *HFSP J.* **2**, 156–166 (2008).

- 2. Strukov, D. B. Smart connections. Nature 476, 403-405 (2011).

- 3. Snider, G. S. Spike-timing-dependent learning in memristive nanodevices. *IEEE/ACM Int. Symp. on Nanoscale Architectures*, 85–92 (2008).

- Linares-Barranco, B. & Serrano-Gotarredona, T. Memristance can explain spiketime-dependent-plasticity in neural synapses. Nature Precedings (2009).

- Jo, S. H. et al. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 10, 1297–1301 (2010).

- Seo, K. et al. Analog memory and spike-timing-dependent plasticity characteristics of a nanoscale titanium oxide bilayer resistive switching device. Nanotechnology 22, 254023 (2011).

- Hasegawa, T. et al. Learning abilities achieved by a single solid-state atomic switch. Adv. Mater. 22, 1831–1834 (2010).

- 8. Ohno, T. *et al.* Short-term plasticity and long-term potentiation mimicked in single inorganic synapses. *Nat. Mater.* **10**, 591–595 (2011).

- Nayak, A. et al. Controlling the synaptic plasticity of a Cu<sub>2</sub>S gap-type atomic switch. Adv. Funct. Mater. 20, 3606–3613 (2012).

- 10. Chang, T., Jo, S. H. & Lu, W. Short-term memory to long-term memory transition in a nanoscale memristor. *ACS nano* 5, 7669–7676 (2011).

- Lai, Q. et al. Ionic/electronic hybrid materials integrated in a synaptic transistor with signal processing and learning functions. Adv. Mater. 22, 2448–2453 (2010).

- 12. Alibart, F. et al. An organic nanoparticle transistor behaving as a biological spiking synapse. Adv. Funct. Mater. 20, 330–337 (2010).

- 13. Alibart, F. et al. A memristive nanoparticle/organic hybrid synapstor for neuroinspired computing. Adv. Funct. Mater. 22, 609–616 (2012).

- Krzysteczko, P., Münchenberger, J., Schäfers, M., Reiss, G. & Thomas, A. The memristive magnetic tunnel junction as a nanoscopic synapse-neuron system. *Adv. Mater.* 24, 762–766 (2012).

- Wang, Z. Q. et al. Synaptic learning and memory functions achieved using oxygen ion migration/diffusion in an amorphous InGaZnO memristor. Adv. Funct. Mater. 22, 2759–2765 (2012).

- Choi, S.-J. et al. Synaptic behaviors of a single metal–oxide–metal resistive device. Appl. Phys. A 102, 1019–1025 (2011).

- Bear, M. F. & Malenka, R. C. Synaptic plasticity: LTP and LTD. Curr. Opin. Neurobiol. 4, 389–399 (1994).

- Bi, G. Q. & Poo, M. M. Synaptic modifications in cultured hippocampal neurons: dependence on spike timing, synaptic strength, and postsynaptic cell type. J. Neurosci. 18, 10464–10472 (1998).

- Caporale, N. & Dan, Y. Spike timing-dependent plasticity: a Hebbian learning rule. Annu. Rev. Neurosci. 31, 25–46 (2008).

- Cassenaer, S. & Laurent, G. Hebbian STDP in mushroom bodies facilitates the synchronous flow of olfactory information in locusts. *Nature* 448, 709–713 (2007).

- Salinga, M. & Wuttig, M. Phase-change memories on a diet. Science 332, 543–544 (2011).

- Shi, L. et al. Artificial cognitive memory—changing from density driven to functionality driven. Appl. Phys. A 102, 865–875 (2011).

- Ovshinsky, S. R. Reversible electrical switching phenomena in disordered structures. *Phys. Rev. Lett.* 21, 1450–1453 (1968).

- Wuttig, M. Phase-change materials: Towards a universal memory? Nat. Mater. 4, 265–266 (2005).

- Burr, G. W. et al. Phase change memory technology. J. Vac. Sci. Techno. B 28, 223–262 (2010).

- Wright, C. D., Liu, Y., Kohary, K. I., Aziz, M. M. & Hicken, R. J. Arithmetic and biologically-inspired computing using phase-change materials. *Adv. Mater.* 23, 3408–3413 (2011).

- Kuzum, D., Jeyasingh, R. G. D., Lee, B. & Wong, H.-S. P. Nanoelectronic programmable synapses based on phase change materials for brain-inspired computing. *Nano Lett.* 12, 2179–2186 (2012).

- Suri, M. et al. Physical aspects of low power synapses based on phase change memory devices. J. Appl. Phys. 112, 054904 (2012).

- Yan, Z., Guo, Y., Zhang, G. & Liu, J. M. High-performance programmable memory devices based on Co-doped BaTiO<sub>3</sub>. Adv. Mater. 23, 1351–1355 (2011).

- Tsui, S. et al. Field-induced resistive switching in metal-oxide interfaces. Appl. Phys. Lett. 85, 317–319 (2004).

- Das, N., Tsui, S., Xue, Y., Wang, Y. & Chu, C. Electric-field-induced submicrosecond resistive switching. Phys. Rev. B 78, 235418 (2008).

- Shang, D. S. et al. Effect of carrier trapping on the hysteretic current-voltage characteristics in Ag/La<sub>0.7</sub>Ca<sub>0.3</sub>MnO<sub>3</sub>/Pt heterostructures. Phys. Rev. B 73, 245427 (2006).

- 33. Rose, A. Space-charge-limited currents in solids. Phys. Rev. 97, 1538-1544 (1955).

- Kim, K. M., Choi, B. J., Jeong, D. S., Hwang, C. S. & Han, S. Influence of carrier injection on resistive switching of TiO2 thin films with Pt electrodes. *Appl. Phys. Lett.* 89, 162912 (2006).

- 35. Park, Y. J., Lee, J. Y., Youm, M. S., Kim, Y. T. & Lee, H. S. Crystal structure and atomic arrangement of the metastable  $Ge_2Sb_2Te_5$  thin films deposited on  $SiO_2/Si$  substrates by sputtering method. *J. Appl. Phys.* **97**, 093506 (2005).

- 36. Nonaka, T., Ohbayashi, G., Toriumi, Y., Mori, Y. & Hashimoto, H. Crystal structure of GeTe and Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> meta-stable phase. *Thin Solid Films* **370**, 258–261 (2000).

- Wuttig, M., Lüsebrink, D. & Daniel Wamwangi, W. W. The role of vacancies and local distortions in the design of new phase-change materials. *Nat. Mater.* 6, 122–128 (2006).

- 38. Lee, T. & Elliott, S. Structural role of vacancies in the phase transition of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> memory materials. *Phys. Rev. B* **84**, 094124 (2011).

- 39. Tsui, S., Wang, Y., Xue, Y. & Chu, C. Mechanism and scalability in resistive switching of metal- $Pr_{0.7}Ca_{0.3}MnO_3$  interface. *Appl. Phys. Lett.* **89**, 123502 (2006).

- Pandian, R. et al. Polarity-dependent resistance switching in GeSbTe phasechange thin films: The importance of excess Sb in filament formation. Appl. Phys. Lett. 95, 252109 (2009).

- 41. Woo, J. et al. Effect of interfacial oxide layer on the switching uniformity of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>-based resistive change memory devices. Appl. Phys. Lett. **99**, 162109 (2011).

- Kim, S. et al. Excellent resistive switching in nitrogen-doped Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> devices for field-programmable gate array configurations. Appl. Phys. Lett. 99, 192110 (2011).

- Alibart, F., Gao, L., Hoskins, B. D. & Strukov, D. B. High precision tuning of state for memristive devices by adaptable variation-tolerant algorithm. *Nanotechnology* 23, 075201 (2012).

- 44. Hebb, D. O. The Organization of Behavior: A Neuropsychological Theory (Wiley, 1949).

- Abbott, L. F. & Nelson, S. B. Synaptic plasticity: taming the beast. Nat. Neurosci. 3, 1178–1183 (2000).

- Roberts, P. D. & Bell, C. C. Spike timing dependent synaptic plasticity in biological systems. *Biol. Cybern.* 87, 392–403 (2002).

- 47. Froemke, R. C. & Dan, Y. Spike-timing-dependent synaptic modification induced by natural spike trains. *Nature* **416**, 433–438 (2002).

- 48. Clopath, C. & Gerstner, W. Voltage and spike timing interact in STDP a unified model. Front. Synaptic Neurosci. 2, 25 (2010).

- 49. Berninger, B. & Bi, G. Q. Synaptic modification in neural circuits: a timely action. *BioEssays* 24, 212–222 (2002).

- Favero, M., Busetto, G. & Cangiano, A. Spike timing plays a key role in synapse elimination at the neuromuscular junction. *Proc. Natl. Acad. Sci. USA* 109, E1667–E1675 (2012).

- 51. Xiong, F., Liao, A. D., Estrada, D. & Pop, E. Low-power switching of phase-change materials with carbon nanotube electrodes. *Science* **332**, 568–570 (2011).

- Loke, D. et al. Breaking the speed limits of phase-change memory. Science 336, 1566–1569 (2012).

# **Acknowledgments**

This work was supported by the Program of International S&T Cooperation (2010DFA11050) and the National High-Tech R&D Program (863 Program) of China (2011AA010404). The authors thank the WNLO Optoelectronic Micro/nano Fabrication Team for providing facility support. The authors also thank Prof. Shaoqun Zeng and Dr. Xiangning Li of HUST (China) and Dr. Massimiliano Giulioni of ISDS (Italy) for useful discussions on neurons and synapses, as well as Prof. Qiangfei Xia of UMass (US) and

Dr. Tomas Fernandes of FIAS (Germany) for helpful discussions on memristors. Li thanks Dr. Towchong Chong of SUTD (Singapore) for inspiring discussions on capacitance experiments.

### **Author contributions**

Y. L. and X. M. conceived and designed the experiments, Y. L. and Y. Z. drafted the paper. Y. Z., L. X. and X. X. carried out the electronic measurements, Y. L., J. Z. and L. X. contributed to the device fabrication and material analysis, Y. L. carried out the simulation, Y. L., X. M. and H. S. performed theoretical analysis. X. M. directed the projects and provided overall guidance throughout. All authors discussed the results and commented on the manuscript.

### **Additional information**

Supplementary information accompanies this paper at http://www.nature.com/scientificreports

Competing financial interests: The authors declare no competing financial interests.

License: This work is licensed under a Creative Commons

Attribution-NonCommercial-NoDerivs~3.0~Unported~License.~To~view~a~copy~of~this~license,~visit~http://creativecommons.org/licenses/by-nc-nd/3.0/

How to cite this article: Li, Y. et al. Ultrafast Synaptic Events in a Chalcogenide Memristor. *Sci. Rep.* **3**, 1619; DOI:10.1038/srep01619 (2013).