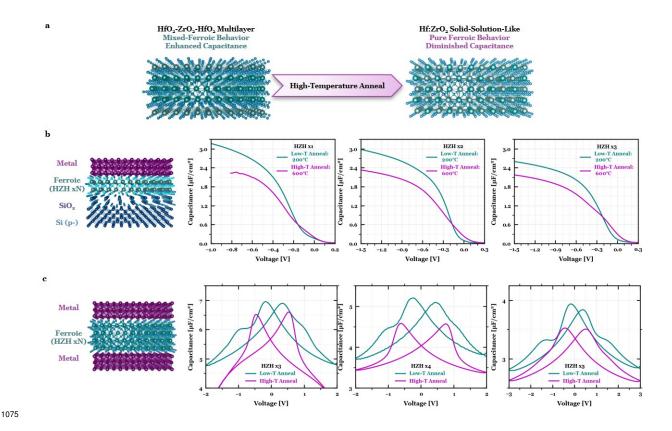

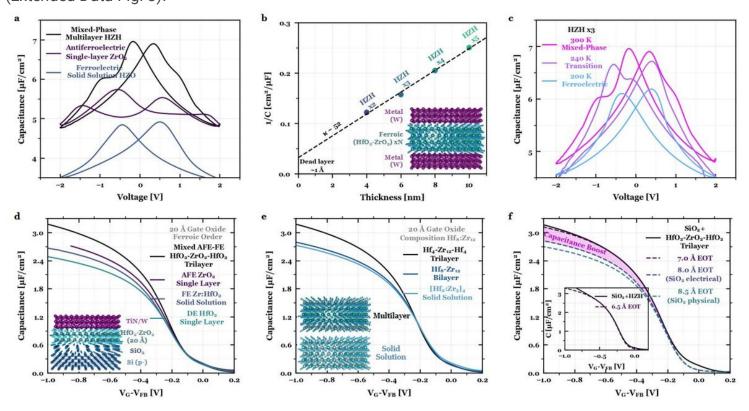

**Extended Data Fig. 5. Solid solutions versus superlattice structure: Role of annealing temperature.** (a) Schematic of HfO<sub>2</sub>-ZrO<sub>2</sub> multilayer and Hf:ZrO<sub>2</sub> solid solution films. Under a high-temperature anneal, the multilayer structure transitions towards a Hf:ZrO<sub>2</sub> solid-solution-like structure demonstrating more FE-like behavior. The solid solution state yields diminished capacitance due to the lack of both the higher-permittivity AFE phase and the mixed-ferroic-induced capacitance enhancement (Fig. 1a). (b) Comparison of MOS capacitor accumulation *C-V* characteristics in HfO<sub>2</sub>-ZrO<sub>2</sub> multilayers, where the superstructure was repeated (left) 1, (center) 2, or (right) 3 times, under both low- and high-temperature anneals. (c) Comparison of mixed-ferroic behavior in low-temperature treated MIM HfO<sub>2</sub>-ZrO<sub>2</sub> multilayers versus FE behavior in in the same multilayers annealed at high temperatures, where the superstructure was repeated (left) 3, (center) 4, or (right) 5 times. In all instances, the high-temperature anneal (> 500°C) results in diminished accumulation capacitance compared to the low-temperature anneals, as the multilayered mixed-ferroic films presumably transition to more FE-like solid-solution alloys.

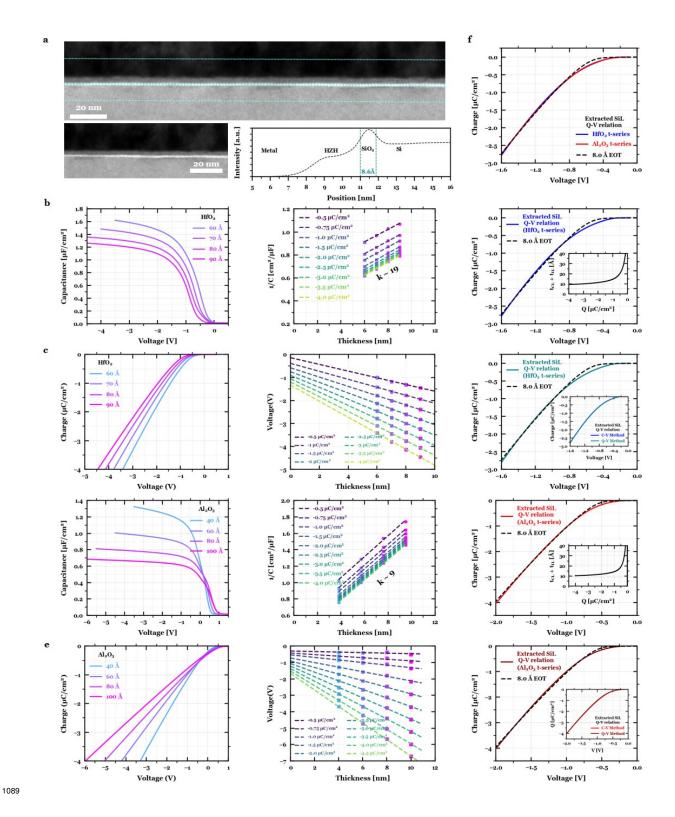

Extended Data Fig. 6. SiO<sub>2</sub> interlayer thickness. (a) Wide field-of-view cross-sectional TEM 1090 images of the HfO2-ZrO2 multilayer structure and its corresponding intensity line scan (bottom 1091 right) averaged across the entire field-of-view (FoV) of the top cross-sectional image ( $\sim 150$  nm), 1092 specified by the teal-colored box. Note the vertical teal-colored lines in the intensity line scan cor-1093 respond to the inner teal-colored box in the wide-FoV image, which delineate the SiO<sub>2</sub> interlayer 1094 boundaries. The bottom cross-sectional TEM image is provided to highlight the thin SiO<sub>2</sub> inter-1095 layer (white region) without obfuscation by the teal-colored box. A physical SiO<sub>2</sub> thickness of 8.6 1096 Å is extracted from analysis of the averaged intensity line scan of the wide FoV TEM (Methods). 1097 (b), (d) C-V measurements of HfO2 (b) and Al2O3 (d) thickness series in MOS capacitor struc-1098 tures (left), extracted inverse capacitance versus thickness at various values of charge (center), and 1099 extracted Q-V relation Si charge layer and SiO<sub>2</sub> interlayer (SiL) (right), which fits to TCAD sim-1100 ulations for 8.0 Å SiO<sub>2</sub>. The SiL Q-V relation was found by integrating the extracted capacitance 1101 equivalent thickness of SiL versus charge (right, inset). This electrical interlayer thickness (8.0 Å) 1102 is slightly less the physical thickness determined by TEM (8.6 Å). As a sanity check, the extracted 1103 permittivity from this methodology for HfO2 and Al2O3 corresponds to 18 and 9, respectively, as 1104 is expected (Methods, Permittivity Extraction). (c), (e) Q-V curves of HfO<sub>2</sub> (c) and Al<sub>2</sub>O<sub>3</sub> (e) 1105 thickness series obtained from integrating MOS C-V measurements (left), extracted voltage vs 1106 thickness at various values of charge (center), and extracted Q-V relation of SiL (right). The SiL 1107 Q-V relation is consistent with the Q-V relation extracted from the C-V data (inset). (f) Consis-1108 tency in the SiL Q-V relation extracted from the C-V data from both the HfO2 and Al2O3 thickness 1109 series, which both fit to an SiO<sub>2</sub> interlayer thickness of 8.0 Å. 1110

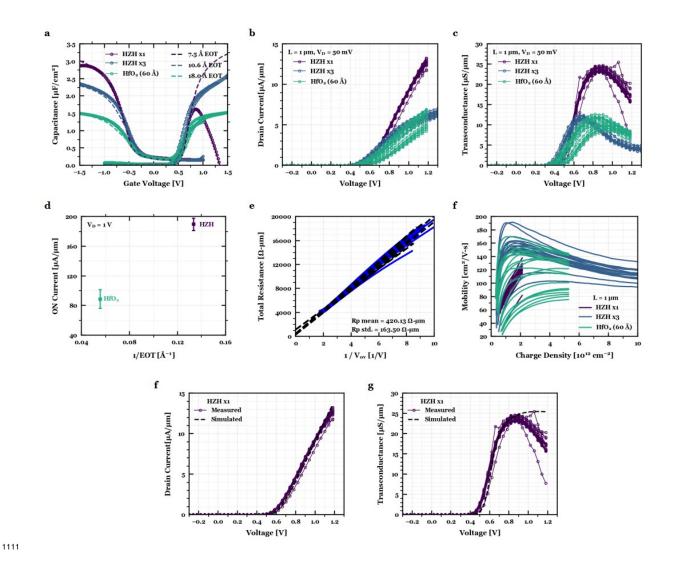

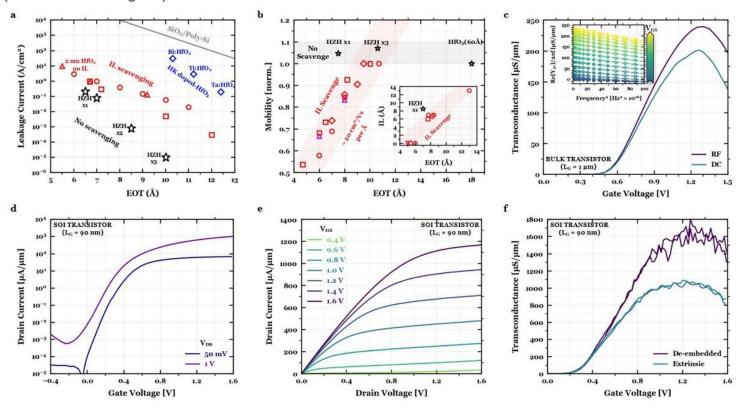

Extended Data Fig. 7. Mobility extraction. (a) Split C-V curves obtained for multilayer HfO<sub>2</sub>-ZrO<sub>2</sub> gate stacks (repeated 1 and 3 times i.e. HZHx1 and HZHx3) and 60 Å HfO<sub>2</sub> dielectric control (Hf-60) from  $L_G = 50 \ \mu m$  bulk transistors at 10 kHz. These C-V curves were fit to EOT simulations of 7.5 Å, 10.6 Å, and 18 Å for HZHx1, HZHx3, and Hf-60, respectively. From the off-state accumulation C-V, a doping level of  $N_a = 2 \times 10^{17} \ cm^{-3}$  was extracted and from the slope of the inversion C-V, the interface trap density was found to be  $D_{it} = 3 \times 10^{12} \ eV^{-1} \ cm^{-2}$ . (b, c)  $I_D$ - $V_G$  (b) and  $g_m$ - $V_G$  (c) transfer characteristics for  $L_G = 1 \mu m$  bulk transistors at  $V_{DS} = 50 \ mV$  for multiple devices per sample. (d) ON current-capacitance (plotted as  $I_{ON}$ -1/EOT) comparison

of the HZH multilayer gate stack versus the HfO<sub>2</sub> dielectric control for  $L_G$  = 0.5  $\mu$ m devices. Here, 1120 the ON-current is defined as  $I_D$  at  $V_D = 1$  V with an overdrive voltage  $V_{ov} = 0.5$  V. The error bars 1121 represent 1 standard deviation of the ON-current measured from 20 different devices. As expected, 1122 the ON current increases as the inverse-EOT (proportional to the gate capacitance) increases. (e) 1123 Series resistance extraction from  $1/V_{ov}$  method for  $V_{ov} = V_{gs} - V_t = 0.3$  V to 0.5 V for  $L_G = 1$ 1124  $\mu m$  devices. The threshold voltage was extracted from the maximum  $g_m$  method. (f) Extracted 1125 mobility as a function of inversion sheet charge density. The effective mobility was taken to be 1126 the average maximum mobility across multiple  $L_G = 1 \mu m$  devices. (g, h) Transfer  $I_D$ - $V_G$  (g) and 1127  $g_m$  (h) data fit to a constant mobility model based on the extracted effectively mobility in (f). A 1128 summary of the EOT-mobility trend from the various samples is provided in Figure 3b. 1129

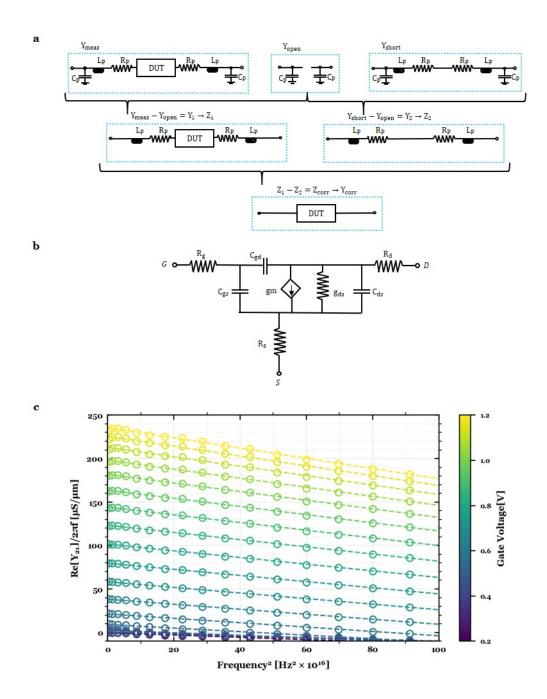

**Extended Data Fig. 8. RF device characterization.** (a) De-embedding procedure for extracting corrected admittance parameters  $(Y_{corr})$  by decoupling parasitic shunt capacitance and series resistance and inductance by measuring scattering parameters for the device under test (DUT) as well as open and short structures. More details can be found in the Methods. (b) Small-signal model for

transistor used to extract transconductance  $(g_m)$  and total gate capacitance  $(C_{gg}=C_{gs}+C_{gd})$ ). (c) De-embedded  $\frac{Re[Y_{21}]}{2\pi f}$  (open circles) as a function of squared frequency at different DC  $V_{GS}$  bias points extrapolated to the zero frequency limit (dotted lines) to extract the RF  $g_m$ . All data shown was extracted from bulk transistors ( $L_G=1~\mu m$ ) integrating the 2 nm HfO<sub>2</sub>-ZrO<sub>2</sub>-HfO<sub>2</sub> ferroic gate stack.

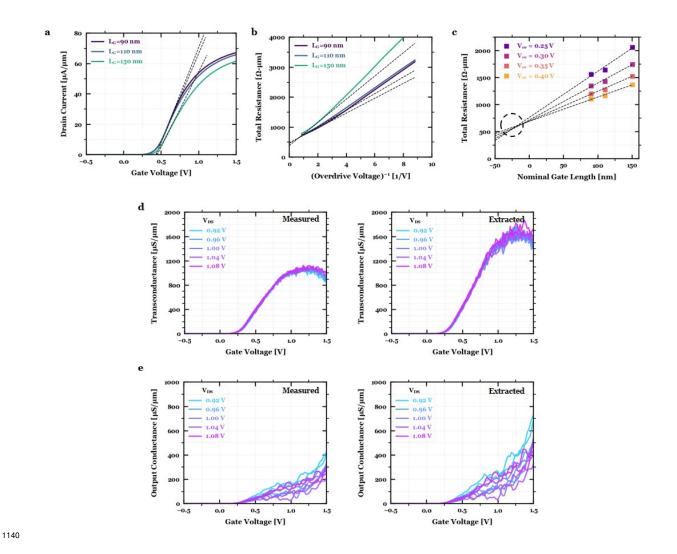

Extended Data Fig. 9. Transconductance extraction. (a) Threshold voltage extraction by linear extrapolation for various channel lengths. All channel lengths give nearly constant  $V_T$  ( $\sim$  0.42 V), satisfying the assumption for the line resistance method. (b) Source/drain series resistance extracted using the  $1/V_{ov}$  method (Methods). By performing a linear interpolation of the total resistance for  $V_{ov} = 0.5$ -0.6 V, the extracted series resistance is  $\sim 500~\Omega$ - $\mu$ m. (c) Source/drain series resistance extracted using the line resistance method (Methods). The trend is considered down to  $L_G = 90$  nm, which intersects at  $\sim 500$ -600  $\Omega$ - $\mu$ m – consistent with the  $1/V_{ov}$  method—with an  $L_G$  offset of  $\sim 50$  nm. (d), (e) Measured (left) and extracted (right) transconductance (d)

and output conductance (e) versus  $V_G$  for  $V_{DS} = 0.9$ -1.1 V, assuming  $R_s = R_d = 250~\Omega$ - $\mu$ m for  $L_G = 90$  nm. The de-embedding of intrinsic  $g_m$  and  $g_{ds}$  from extrinsic  $G_m$  and  $G_{ds}$  is described in the Methods. All data shown was measured on SOI short-channel transistors integrating the 2 nm  $HfO_2$ - $ZrO_2$ - $HfO_2$  ferroic gate stack.

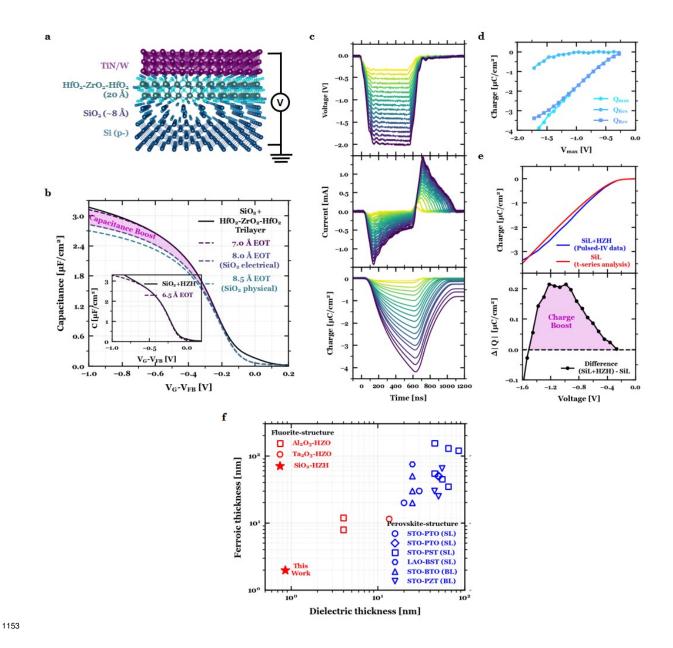

Extended Data Fig. 10. Capacitance and charge enhancement. (a) MOS schematic of the  $20 \text{ Å HfO}_2\text{-ZrO}_2\text{-HfO}_2$  mixed ferroic trilayer sample on lightly-doped Si  $(10^{15} \text{ cm}^{-3})$  considered for the following accumulation C-V and pulsed I-V measurements. (b) Accumulation C-V curves for the 2 nm HfO $_2\text{-ZrO}_2\text{-HfO}_2$  trilayer grown on sub-nm SiO $_2$  fit to effective oxide thickness (EOT) simulations (Methods). Inset: Externally verified MOS accumulation C-V of the same trilayer stack (Methods), demonstrating 6.5 Å EOT. The 2 nm trilayer on top of SiO $_2$  demonstrates

lower EOT than the thickness of SiO<sub>2</sub> interlayer alone, carefully extracted via physical (8.5 Å) 1160 and electrical (8.0 Å) methodologies (Extended Data Fig. 6), providing evidence of capacitance 1161 enhancement. (c) The applied voltage pulse (top), the measured current response (center) and the 1162 integrated charge (bottom) as a function of time for 2 nm HfO<sub>2</sub>-ZrO<sub>2</sub>-HfO<sub>2</sub> trilayer in MOS capac-1163 itors. (d) The maximum charge  $Q_{max}$ , the residual charge  $Q_{res}$ , and their difference,  $Q_{rev}$ , derived 1164 from the charge vs time curve for each of the voltage pulses (Methods). (e) The reversible charge 1165 of the MOS layer (top) compared against the extracted charge of the Si charge layer plus SiO<sub>2</sub> 1166 interlayer (SiL) derived electrically (Extended Data Fig. 5f). The charge boost (bottom) present 1167 in the total MOS structure (SiL plus HZH capacitors) compared to just the SiL is a signature of 1168 negative capacitance, as previously demonstrated in metal-ferroelectric-insulator-metal (MFIM) 1169 structures 47,67. (f) Scatter plot of reported ferroelectric-dielectric systems demonstrating nega-1170 tive capacitance at the capacitor level via capacitance (C-V measurements) or charge (pulsed I-V 1171 measurements) enhancement. The plot considers fluorite-structure bilayers 47,67 (red), perovskite-1172 structure bilayers <sup>22,91</sup> (blue, BL), and perovskite-structure superlattices <sup>38–41</sup> (blue, SL). This work 1173 employing sub-nm SiO<sub>2</sub> interlayer and 2 nm HfO<sub>2</sub>-ZrO<sub>2</sub> multilayer on silicon (black, star) provides 1174 the most scaled demonstration of negative capacitance, as supported by enhanced capacitance from 1175 C-V measurements (b) and amplified charge from pulsed I-V measurements (e) relative to the SiO<sub>2</sub> 1176 dielectric interlayer. 1177

## **Figures**

Figure 1

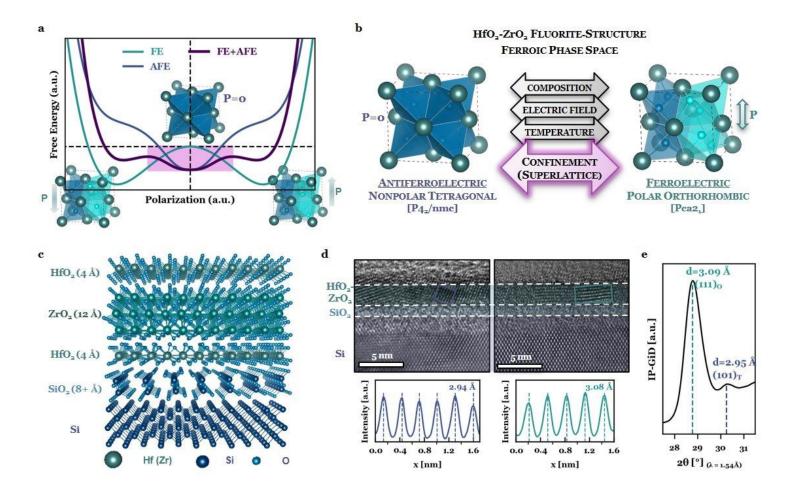

Atomic-scale design of negative capacitance in ultrathin HfO2-ZrO2. (a) Phenomeno logical model of negative capacitance (NC) in a mixed ferroic system. Landau free energy land scapes for a FE, AFE, and mixed FE-AFE system (Methods). Mixed FE-AFE phase competition should suppress polarization48 and enhance electric susceptibility22,40 via proximity to a phase4 boundary, and flattens the energy landscape, desirable traits for NC stabilization. The stable energy minimum of the composite free energy landscape, corresponding to the negative curvature (NC) regime of the ferroelectric energy landscape, is highlighted. (b) Engineering ferroic phase competition in the HfO2-ZrO2 fluorite-structure system. Beyond the conventionally-studied tuning parameters – composition, electric field, temperature23,35 – here we introduce dimensional confine ment via superlattice layering to tailor ferroic phase competition at the atomic-scale. (c) Schematic of the HfO2-ZrO2 fluorite-structure multilayer on Si; the heterostructures maintain distinct layers (i.e. not solid solution alloys) based on EELS, XRR, and depth-resolved XPS (Extended Data Fig. 1). The role of the layering on the underlying ferroic order and capacitance is studied by electrical measurements as a function of HfO2-ZrO2 stacking structure and annealing temperature (Extended Data Fig. 4 and 5, respectively). (d) HR-TEMimage of the atomic-scale HfO2-ZrO2-HfO2 trilayer (top) and extracted d-lattice spacings (bottom) corresponding to the fluorite-structure AFE

tetrago nal (P42/nmc, red) and FE orthorhombic (Pca21, blue) phases, respectively. The layer delineations are approximate, as the Hf02-Zr02 and Si02 interlayer thicknesses are more rigorously deter mined by XRR and TEM analysis (Extended Data Fig. 1 and 6, respectively). Note imaging the crystallinity of the Hf02-Zr02 layers requires mistilt with respect to the Si lattice (Methods). (e) Synchrotron IP-GiD demonstrating the presence of both the AFE T-phase (101)t and FE 0-phase (111)o reflections whose d-lattice spacings are consistent with those extracted from TEM. Detailed indexing to higher-order reflections for structural identification of the ferroic phases is provided by wide-angle synchrotron diffraction (Extended Data Fig. 2a). Further evidence of inversion symmetry breaking is provided by second harmonic generation and synchrotron linear dichroism (Extended Data Fig. 2c,d). Additionally, the evolution between these two ferroic phases are also studied as a function of temperature (Extended Data Fig. 3).

Figure 2

Enhanced capacitance in ultrathin HfO2-ZrO2 mixed-ferroic heterostructures. (a) MIM C-V hysteresis loops for a mixed FE-AFE HfO2-ZrO2 multilayer demonstrating higher ca pacitance compared against its AFE (ZrO2) and FE (Zr:HfO2) counterparts of the same thickness. (b) Inverse capacitance versus thickness of the MIM HfO2-ZrO2 multilayers up to 5 superlattice repeats (10 nm), with an extracted permittivity of 52 (Methods), extremely large for HfO2-based oxides. (c) MIM C-V hysteresis loops for HfO2-ZrO2 multilayers of the same periodicity demon strating an evolution from mixed-ferroic to FE-like hysteresis upon cooling slightly below room temperature. The proximity to the temperature-dependent phase transition (Extended Data Fig. 3) suggests the HfO2-ZrO2 heterostructures lies near its maximum electric susceptibility position, ideal for negative capacitance stabilization40,48. (d) MOS accumulation

C-V of Hf02-Zr02-Hf02 trilayer compared to AFE Zr02, FE Zr:Hf02, and DE Hf02, all of the same thickness (20 Å), indicating mixed-ferroic behavior is optimal for enhancing capacitance rather than purely FE or AFE behavior. (e) Accumulation C-V of the HfO2-ZrO2-HfO2 trilayer compared to bilayer and solid solutions films of the same thickness (ALD cycles) and composition (Hf:Zr cycles). Inset: Schematic of multilayer (Hf and Zr cations vertically separated) versus solid solution (Hf and Zr cations inter-mixed). These results suggest the capacitance enhancement in multilayer films is not simply driven by Hf:Zr composition23,35, but instead the atomic-scale stacking (Extended Data Fig. 4, 5). (f) Accumulation C-V curves for a 2 nm HfO2-ZrO2-HfO2 trilayer grown on sub-nm SiO2 fit to effective oxide thickness (EOT) simulations (Methods). Inset: Externally verified MOS accumulation C V of the same trilayer stack (Methods), demonstrating 6.5 Å EOT. The 2 nm trilayer on top of SiO2 demonstrates lower EOT than the thickness of SiO2 interlayer alone, carefully extracted via physical (8.5 Å) and electrical (8.0 Å) methodologies (Extended Data Fig. 6), providing evidence of capacitance enhancement. Furthermore, these 2 nm ferroic gate stacks demonstrate amplified charge from pulsed I-V measurements relative to the SiO2 interlayer (Extended Data Fig. 10). Notably, this 2 nm HfO2-ZrO2 multilayer on sub-nm SiO2 provides the most scaled demonstration of charge and capacitance enhancement at the capacitor-level (Extended Data Fig. 10).

Figure 3

Device performance benefits utilizing ultrathin mixed-ferroic HfO2-ZrO2 gate stacks. (a) Leakage-effective oxide thickness (JG-EOT) scaling of the multilayer gate stacks (black) bench marked against reported HKMG literature3, including interlayer-scavenged 2 nm HfO2 (red), high-doped HfO2 (blue), and SiO2/poly-Si (gray). The leakage is the lowest reported for a 6.5-7.0 Å EOTMOS capacitor on silicon3, due

to the EOT reduction without requiring interlayer SiO2 thickness reduction. (b) Normalized mobility versus EOT scaling of the multilayer gate stacks (black) benchmarked against reported HKMG literature3, including interlayer-scavenged 2 nm HfO2 (red) and hybrid silicate-scavenged interlayer (magenta). For EOT scaling in conventional HKMG systems, the SiO2 interlayer has to be reduced to lower EOT, which leads to degraded mobility3. In this case, enhanced capacitance in HfO2-ZrO2 multilayers achieves scaled EOT without having to thin the SiO2 interlayer; therefore, mobility is not degraded. Inset: SiO2 interlayer thickness versus EOT scaling comparing the 7.0 Å EOT HfO2-ZrO2-HfO2 trilayer against notable HKMG literature which employ interlayer scavenging to reduce EOT3. This scatter plot highlights the underlying reason for the enhanced leakage-EOT and mobility-EOT behavior in the ultrathin trilayer gate stacks: low EOT without reduced SiO2 interlayer thickness. (c) Transconductance (gm) versus gate voltage (VG) 450 for long-channel bulk transistors (LG = 1 m) obtained from both DC (derivative of ID-VG) and RF (Re[Y21]) measurements (Methods) at VDS = 1 V. Inset: De-embedded Re[Y21] (open circles) as a function of squared frequency at different DC VGS bias points extrapolated to the zero frequency limit (dotted lines) to extract the RF gm (Extended Data Fig. 8). The high frequency measurements help suppress defect contributions which would otherwise dampen the intrinsic gm. (d, e, f) DC I-V transfer characteristics (ID-VG, d), DC output characteristics (ID-VD, e), and DC transconductance (gm-VG, f) for short-channel (LG = 90 nm) SOI transistors. Notably, the maximum on-current and gm at VDS = 1 V exceeds 1 mA/m and 1 mS/m. DC mobility and transconductance values are carefully extracted after deembedding the series resistance from double-swept I-V measurements (Extended Data Fig. 7 and 9, respectively).