# Unified Parallel Lattice Structures for Time-Recursive Discrete Cosine/Sine/Hartley Transforms

K. J. Ray Liu, Member, IEEE, and Ching-Te Chiu, Member, IEEE

Abstract-The problems of unified efficient computations of the discrete cosine transform (DCT), discrete sine transform (DST), discrete Hartley transform (DHT), and their inverse transforms are considered. In particular, a new scheme employing the time-recursive approach to compute these transforms is presented. Using such approach, unified parallel lattice structures that can dually generate the DCT and DST simultaneously as well as the DHT are developed. These structures can obtain the transformed data for sequential input timerecursively with throughput rate one per clock cycle and the total number of multipliers required is a linear function of the transform size N. Furthermore, there is no constraint on N. The resulting architectures are regular, modular, and without global communication so that they are very suitable for VLSI implementation for high-speed applications such as ISDN networks and HDTV systems. It is also shown in this paper that the DCT, DST, DHT and their inverse transforms share an almost identical lattice structure. The lattice structures can also be formulated into prelattice and postlattice realizations. Two methods, the SISO and double-lattice approaches, are developed to reduce the number of multipliers in the parallel lattice structure by 2N and N, respectively. The tradeoff between time and area for the block data processing is also considered. The concept of filter bank interpretation of the time-recursive sinusoidal transforms is also discussed.

#### I. INTRODUCTION

TRANSFORM coding has found many applications in image, speech, and digital signal transmission and processing. Due to the advances in ISDN networks and high definition television (HDTV) technology, high speed transmission of digital video signal has become very desirable. Among the many transforms, the discrete cosine transform (DCT), discrete sine transform (DST), and discrete Hartley transform (DHT) are very effective in transform coding applications to digital signals, such as speech and image signals. The DCT is the most widely used transform in speech and image processing for data compression. This is due to its better energy compaction property and its near optimal performance which is closest to that of the Karhunen-Loeve transform (KLT) among many discrete transforms for highly correlated signals, especially for the first-order Markov process [1]-[3]. It was shown by Jain that the performance of the DST approaches that of the KLT for a first-order Markov sequence with given boundary conditions, especially for signal with low correlation coefficients [4], [5]. In 1983, Bracewell introduced the DHT [6] which uses a transform kernel similar to that of the discrete Fourier transform (DFT), except that it is a real-valued transform. Therefore, it is simpler than the DFT with respect to the computational complexity [7]. Like the DCT and DST, the DHT has found many applications in signal and image processing [6], [8], [24], [28].

Since the DCT was introduced, many algorithms were proposed to improve the computation speed and to reduce the hardware complexity. These algorithms can be classified into the following categories: 1) indirect computation, 2) matrix factorization, 3) recursive computation, and 4) systolic structure implementation. The indirect computation [9], [10]-[13] applies the existing fast algorithms in the DFT or the Walsh-Hadamard transform to the DCT. It is not particularly efficient because the inherent properties of the DCT are not exploited. The matrix factorization [14], [15], [25], [26] decomposes the DCT into multiplications of many sparse matrices, therefore the numbers of multiplications and additions can be substantially reduced. The recursive computations [16], [7] calculate higher order DCT coefficients from lower-order ones, but their signal flow architectures need global communication which is not suitable for VLSI implementation. By using the recursive properties effectively, this kind of DCT algorithms has fewer multipliers and adders, while additional multiplexers are required. As for the systolic structure implementation [17], [18], [27], it uses existing systolic architectures for the DFT or other transforms to implement the DCT in a systolic manner. But some of the methods require that the number of samples of the signal must be decomposed into mutually prime numbers. Like the DCT, many fast algorithms have been proposed to improve the performance of the DST and DHT [8], [19], [20], [4], [5]. Basically, they can be classified in the same ways as those of the DCT and similar advantages and disadvantages can also be found.

In this paper, we propose unified time-recursive lattice structures that can be used for the discrete orthogonal transforms mentioned above, i.e., the DCT, DST, and DHT. We consider the orthogonal transforms from a timerecursive point of view instead of the whole block of data. We do so because in digital signal transmission, data arrive serially. Also, many operations such as filtering and coding are done in a time-recursive way. Based on this

Manuscript received March 26, 1991; revised February 24, 1992. This work was supported in part by NSF Grant ECD-8803012.

The authors are with the Department of Electrical Engineering, Systems Research Center, University of Maryland, College Park, MD 20742.

IEEE Log Number 9206036.

approach, the resulting architectures are almost identical for the DCT, DST, and DHT, and their inverses. Our structures decouple the transformed data components, hence, there is no global communication needed. Besides, the number of multipliers in these structures is a linear function of N, so they require fewer multipliers than most other algorithms when N is large. Therefore, our architectures are very suitable for VLSI implementation. One of the important characteristics of these structures is that the transform size N can be any integer, which is not the case for most of the fast algorithms for discrete transforms which do have certain constraints on N. Another important result is that based on the time-recursive approach, the dual generation properties of the DCT, DST, and DHT, as well as some related inverse transforms, can be obtained.

The rest of the paper is organized as follows. In Section II, the dual generation of lattice structures for the DCT and DST with the time-recursive approach is considered. The inverse discrete cosine transform (IDCT) and the inverse discrete sine transform (IDST) based on the lattice structures are discussed in Section III. In Section IV, the time-recursive lattice structure for the DHT is presented. All the above time-recursive properties are derived by updating the time index by one. With block data processing, the time index is updated by more than one. The detailed effects and results of the block data processing are discussed in Section V. Denormalized methods to reduce the number of multipliers in those lattice structures are considered in Section VI. Then we compare these kinds of lattice structures with other architectures in terms of the number of multipliers and adders in Section VII. The synthesis bank structures based on the time-recursive concept is discussed in Section VIII. Finally, we give the conclusion in Section IX.

### II. DUAL GENERATION OF DCT AND DST

We will show an efficient implementation of the DCT from the time-recursive point of view as an alternative to find fast algorithms through matrix factorizations or convert the DCT to DFT, which can be implemented on various existing architectures. Focusing on the sequence instead of the block of input data, we can obtain not only the time-recursive relation between the DCT of two successive data sequences, but also the fundamental relation between the DCT and DST. In the following, the timerecursive relation for the DCT will be considered first.

### A. Time-Recursive Discrete Cosine Transform

The one-dimensional (1-D) DCT of a sequential input data starting from x(t) and ending with x(t + N - 1) is defined as

$$X_{c}(k, t) = \frac{2C(k)}{N} \sum_{n=t}^{t+N-1} x(n) \cos\left[\frac{\pi [2(n-t)+1]k}{2N}\right],$$

$$k = 0, 1, \cdots, N-1,$$

where

$$C(k) = \begin{cases} \frac{1}{\sqrt{2}} & \text{If } k = 0\\ 1 & \text{otherwise.} \end{cases}$$

(1)

Here the time index t in  $X_c(k, t)$  denotes that the transform starts from x(t). Since the function C(k) has a different value only when k = 0, we can consider those cases that C(k)'s equal one (i.e.,  $k = 1, 2, \dots, N-1$ ) first and reexamine the case for k = 0 later on. In transmission systems data arrive seriesly, therefore we are interested in the 1-D DCT of the next input data vector  $[x(t + 1), x(t + 2), \dots, x(t + N)]$ . From the definition, it is given by

$$X_{c}(k, t + 1) = \frac{2}{N} \sum_{n=t+1}^{t+N} x(n) \cos\left[\frac{\pi [2(n-t-1)+1]k}{2N}\right],$$

$$k = 1, \cdots, N-1.$$

(2)

This can be rewritten as

$$X_{c}(k, t + 1) = \overline{X}_{c}(k, t + 1) \cos\left(\frac{\pi k}{N}\right) + \overline{X}_{s}(k, t + 1) \sin\left(\frac{\pi k}{N}\right)$$

(3)

where

$$\overline{X}_{c}(k, t+1) = \frac{2}{N} \sum_{n=t+1}^{t+N} x(n) \cos\left[\frac{\pi [2(n-t)+1]k}{2N}\right]$$

(4)

and

$$\overline{X}_{s}(k, t+1) = \frac{2}{N} \sum_{n=t+1}^{t+N} x(n) \sin\left[\frac{\pi [2(n-t)+1]k}{2N}\right].$$

(5)

As we can see, a DST-like term  $\overline{X}_s(k, t + 1)$  appears in the equation. This motivates us to investigate the time-recursive DST.

### B. Time-Recursive Discrete Sine Transform

There are several definitions for the DST. Here we prefer the definition made by Wang in [20] since it is of the form completed with the following derivations. The 1-D DST of a data vector  $[x(t), x(t + 1), \dots, x(t + N -$ 1)] is defined as

$$X_{c}(k, t) = \frac{2D(k)}{N} \sum_{n=t}^{t+N-1} x(n) \sin \left[ \frac{\pi [2(n-t) + 1]k}{2N} \right],$$

$$k = 1, \cdots, N$$

where

$$D(k) = \begin{cases} \frac{1}{\sqrt{2}} & \text{If } k = N \\ 1 & \text{otherwise.} \end{cases}$$

(6)

LIU AND CHIU: UNIFIED PARALLEL LATTICE STRUCTURES

Note that the range of k is from 1 to N. Again, we consider those cases that D(k)'s equal one first, i.e.,

$$X_{s}(k, t) = \frac{2}{N} \sum_{n=t}^{t+N-1} x(n) \sin\left[\frac{\pi [2(n-t)+1]k}{2N}\right],$$

$$k = 1, 2, \cdots, N-1.$$

(7)

The DST of the time update sequence  $[x(t + 1), x(t + 2), \dots, x(t + N)]$  is given by

$$X_{s}(k, t+1) = \frac{2}{N} \sum_{n=t+1}^{t+N} x(n)$$

$$\cdot \sin\left[\frac{\pi [2(n-t-1)+1]k}{2N}\right]$$

$$= \overline{X}_{s}(k, t+1)$$

$$\cdot \cos\left(\frac{\pi k}{N}\right) - \overline{X}_{c}(k, t+1) \sin\left(\frac{\pi k}{N}\right).$$

(8)

Here the terms  $\overline{X}_s(k, t+1)$  and  $\overline{X}_c(k, t+1)$  that are used in (3) to generate  $X_c(k, t+1)$  appear in the equation of the new DST transform  $X_s(k, t+1)$  again. This suggests that the DCT and DST can be dually generated from each other.

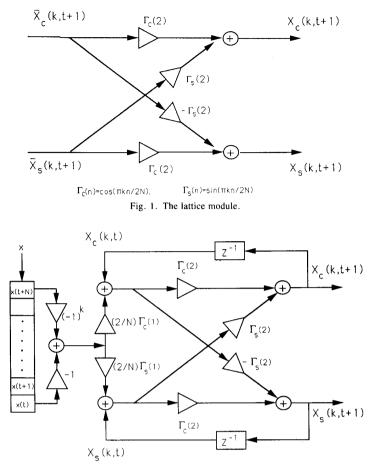

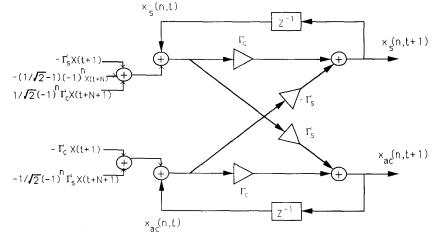

## C. The Lattice Structures

From (3) and (8), it is noted that the new DCT and DST transforms  $X_c(k, t + 1)$  and  $X_s(k, t + 1)$ , can be obtained from  $\overline{X}_c(k, t + 1)$  and  $\overline{X}_s(k, t + 1)$  in the lattice form as shown in Fig. 1. The next step is to update  $\overline{X}_c(k, t + 1)$  and  $\overline{X}_s(k, t + 1)$  from the previous transforms  $X_c(k, t)$  and  $\overline{X}_s(k, t)$ . We notice that  $X_c(k, t)$  and  $\overline{X}_c(k, t + 1)$  have similar terms except the old datum x(t) and the incoming new datum x(t + N). Therefore  $\overline{X}_c(k, t + 1)$  and  $\overline{X}_s(k, t + 1)$  and

$$\overline{X}_{c}(k, t + 1) = X_{c}(k, t) - x(t) \left(\frac{2}{N}\right) \cos\left(\frac{\pi k}{2N}\right) + x(t + N) \left(\frac{2}{N}\right) \cos\left[\frac{\pi (2N + 1)k}{2N}\right] = X_{c}(k, t) + [-x(t) + (-1)^{k}x(t + N)] \cdot \left(\frac{2}{N}\right) \cos\left(\frac{\pi k}{2N}\right)$$

(9)

and

$$\overline{X}_{s}(k, t + 1) = X_{s}(k, t) - x(t) \left(\frac{2}{N}\right) \sin\left(\frac{\pi k}{2N}\right) + x(t + N) \left(\frac{2}{N}\right) \sin\left[\frac{\pi (2N + 1)k}{2N}\right] = X_{s}(k, t) + [-x(t) + (-1)^{k}x(t + N)] \cdot \left(\frac{2}{N}\right) \sin\left(\frac{\pi k}{2N}\right).$$

(10)

1359

From (3), (8)-(10), the new transforms  $X_c(k, t + 1)$  and  $X_s(k, t + 1)$  can be calculated from the previous transforms  $X_c(k, t)$  and  $X_s(k, t)$  by adding the effect of input signal samples x(t) and x(t + N). This demonstrates that the DCT and DST can be dually generated from each other in a recursive way. The time-recursive relations for the new transforms  $X_c(k, t + 1)$  and  $X_s(k, t + 1)$  as well as the previous transforms  $X_c(k, t)$  and  $X_s(k, t)$  are given by

$$X_{c}(k, t+1) = \begin{cases} X_{c}(k, t) + [-x(t) + (-1)^{k}x(t+N)] \\ \cdot \left(\frac{2}{N}\right)\cos\left(\frac{\pi k}{2N}\right) \\ \cos\left(\frac{\pi k}{N}\right) \\ + \left\{ X_{s}(k, t) + [-x(t) + (-1)^{k}x(t+N)] \\ \cdot \left(\frac{2}{N}\right)\sin\left(\frac{\pi k}{2N}\right) \\ \sin\left(\frac{\pi k}{N}\right) \end{cases}$$

(11)

and

$$X_{s}(k, t+1) = \left\{ X_{s}(k, t) + \left[ -x(t) + (-1)^{k}x(t+N) \right] \\ \cdot \left( \frac{2}{N} \right) \sin\left( \frac{\pi k}{2N} \right) \right\} \cos\left( \frac{\pi k}{N} \right) \\ - \left\{ X_{c}(k, t) + \left[ -x(t) + (-1)^{k}x(t+N) \right] \\ \cdot \left( \frac{2}{N} \right) \cos\left( \frac{\pi k}{2N} \right) \right\} \sin\left( \frac{\pi k}{N} \right).$$

(12)

Now, let us consider the cases for k = 0 in the DCT and k = N in the DST respectively. According to (1), the 1-D DCT of the time-update input vector  $[x(t + 1), x(t + 2), \dots, x(t + N)]$  for k = 0 is

$$X_{c}(0, t + 1) = \frac{2}{N\sqrt{2}} \sum_{n=t+1}^{t+N} x(n).$$

(13)

The relation of  $X_c(0, t + 1)$  with the old transformed datum  $X_c(0, t)$  is

$$X_{c}(0, t + 1) = X_{c}(0, t) + \frac{2}{N\sqrt{2}}$$

$$\cdot [-x(t) + x(t + N)].$$

(14)

And, the time-recursive relation between the new transforms  $X_s(N, t + 1)$  and the previous transforms  $X_s(N, t)$  is

$$X_{s}(N, t + 1) = \frac{2}{N\sqrt{2}} \sum_{n=t+1}^{t+N} x(n)(-1)^{n-t-1}$$

$$= -X_{s}(N, t) + \frac{2}{N\sqrt{2}}$$

$$\cdot [x(t) + (-1)^{N-1}x(t+N)]. (15)$$

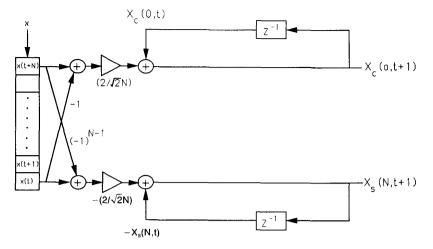

The complete time-recursive lattice modules for  $(k = 1, 2, \dots, N - 1)$  are shown in Fig. 2. It consists of a N

Fig. 2. The lattice structure for the DCT and DST with coefficients C(k)'s and D(k)'s,  $k = 1, 2, \dots, N-1$ .

+ 1 shift register and a normalized digital filter performing the plane rotation. The multiplications in the plane rotation can be reduced to addition and subtraction for k= 0 in the DCT and k = N in the DST, respectively, these two cases can be simplified and combined together as shown in Fig. 3.

The following illustrates how this dually generated DCT and DST lattice structure works to obtain the DCT and DST with length N of a series of input data [x(t), x(t)]+ 1),  $\cdots$ , x(t + N - 1), x(t + N),  $\cdots$ ] for a specific k. The initial values of the transformed signals  $X_c(k, t - k)$ 1) and  $X_s(k, t-1)$  are set to zero; so are the initial values in the shift register in the front of the lattice module. The input sequence  $[x(t), x(t + 1), \cdots]$  shifts sequentially into the shift register as shown in Fig. 2. Then the output signals  $X_c(k, t)$  and  $X_s(k, t), k = 0, 1, \dots, N - 1, N$ , are updated recursively according to (11), (12), (14), and (15). After the input datum x(t + N - 1) shifts into the shift register, the DCT and DST of the input data vector  $[x(t), x(t+1), \cdots, x(t+N-1)]$  are obtained at the output for this index k. It takes N clock cycles to get the  $X_c(k, t)$  and  $X_s(k, t)$  of the input vector [x(t), x(t + 1), $\cdots$ , x(t + N - 1)]. Since there are N different values for k, the total computational time to obtain all the transformed data is  $N^2$  clock cycles, if only one lattice module is used. In this case, the delay time and throughput are the same  $N^2$  clock cycles.

A parallel lattice array consists of N lattice modules can be used for parallel computations and it improves the computational speed drastically as shown in Fig. 4. Here we have seen that the transform domain data X(k, t) have been decomposed into N disjoint components that have the same lattice modules with different multiplier coefficients in them. In this case the total computational delay time decreases to N clock cycle. It is important to notice that when the next input datum x(t + N) arrives, the transformed data of the input data vector  $[x(t + 1), x(t + 2), \dots, x(t + N)]$  can be obtained immediately. Likewise, it takes only one clock cycle to generate the transformed data of subsequent inputs. That is, the latency and throughput of this parallel system are N and 1, respectively.

It is obvious that this lattice structure is quite different from the signal flow graph realization obtained from the fast DCT algorithms [14], [15]. Since there is no global communication and the structure is modular and regular,

Fig. 3. The lattice structure of k = 0 for the DCT and k = N for the DST with coefficient C(0) and D(N).

Fig. 4. The parallel lattice structure for the DCT and DST.

it is suitable for practical VLSI implementation. The most interesting result is that this architecture can be applied to any value of N. From this point of view, it is more attractive than existing algorithms. In fact, most algorithms [21], [18] are limited to the sequence length N which either must be power of 2 or must be decomposable into mutually prime numbers. In addition, this lattice structure reveals some interesting properties of the DCT and DST, i.e., the DCT and DST can be generated simultaneously. The DCT is near optimal to the KLT transform in highly correlated signals, while the DST approaches the KLT in signals with low correlation coefficient. As we are able to obtain the DCT and DST at the same time, this lattice structure is very useful especially when we do not know the statistics of the incoming signal. Furthermore, we can use a single lattice module with only 6 multipliers and 5 adders to recursively compute any *N*-point DCT and DST simultaneously. To obtain the transformed data in parallel, we need *N* lattice modules. As mentioned before, it is suitable for VLSI implementation since all the modules have the same structure except the 0th module which can be simplified as shown in Fig. 3. This parallel lattice structure requires 6N - 4 multipliers and 5N - 1 adders.

III. INVERSE DISCRETE COSINE TRANSFORM (IDCT) AND INVERSE DISCRETE SINE TRANSFORM (IDST)

# A. Time-Recursive IDCT

According to the definition of the DCT in (1), the IDCT for the transform domain sequence  $[X(t), X(t + 1), \cdots,$

$$X(t + N - 1)] \text{ is}$$

$$x_{c}(n, t) = \sum_{k=t}^{t+N-1} C(k-t)X(k) \cos\left[\frac{\pi (2n+1)(k-t)}{2N}\right],$$

$$n = 0, 1, \cdots, N-1.$$

(16)

The coefficients C(k)'s are given in (1). From the timerecursive point of view, the IDCT of the new sequence  $[X(t + 1), X(t + 2), \cdots, X(t + N)]$  can be expressed as

$$x_{c}(n, t+1) = \sum_{k=t+1}^{t+N} C(k-t-1)X(k)$$

$$\cdot \cos\left[\frac{\pi (2n+1)(k-t-1)}{2N}\right]. \quad (17)$$

Similar to the previous sections, we can decompose (17) into

$$x_{c}(n, t + 1) = \bar{x}_{c}(n, t + 1) \cos\left[\frac{\pi(2n + 1)}{2N}\right] + \bar{x}_{as}(n, t + 1) \sin\left[\frac{\pi(2n + 1)}{2N}\right]$$

(18)

where

$$\bar{x}_{c}(n, t+1) = \sum_{k=t+1}^{t+N} C(k-t-1)X(k) \\ \cdot \cos\left[\frac{\pi (2n+1)(k-t)}{2N}\right]$$

(19)

and

$$\bar{x}_{as}(n, t+1) = \sum_{k=t+1}^{t+N} C(k-t-1)X(k)$$

$$\cdot \sin\left[\frac{\pi (2n+1)(k-t)}{2N}\right]. \quad (20)$$

In order to be a dually generated pair of the IDCT given in (16), we define the auxiliary inverse discrete sine transform (AIDST) as

$$x_{as}(n,t) = \sum_{k=t}^{t+N-1} C(k-t)X(k) \sin\left[\frac{\pi (2n+1)(k-t)}{2N}\right],$$

$$n = 0, 1, \cdots, N-1.$$

(21)

Although this definition utilizes the same sine functions as the transform kernel, it is not the inverse transform of the DST. To differentiate it from the IDST, we call this the AIDST. Compared to the IDST defined in (26), we observe that the AIDST has the special coefficients  $C(0) = 1/\sqrt{2}$  associated with the first term, while the IDST with the last term. The AIDST for the data sequence  $[X(t + 1), X(t + 2), \cdots, X(t + N)]$  can be written as

$$x_{as}(n, t+1) = \sum_{k=t+1}^{t+N} C(k-t-1)X(k)$$

$$\cdot \sin\left[\frac{\pi(2n+1)(k-t-1)}{2N}\right]. \quad (22)$$

. . .

By using the trigonometric function expansions,  $x_{as}(n, t + 1)$  becomes

$$x_{as}(n, t + 1) = \bar{x}_{as}(n, t + 1) \cos\left[\frac{\pi (2n + 1)}{2N}\right] - \bar{x}_{c}(n, t + 1) \sin\left[\frac{\pi (2n + 1)}{2N}\right].$$

(23)

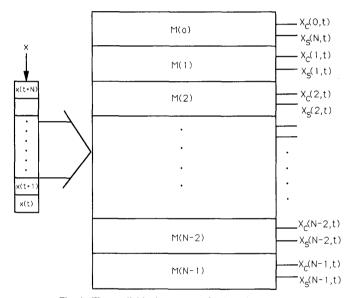

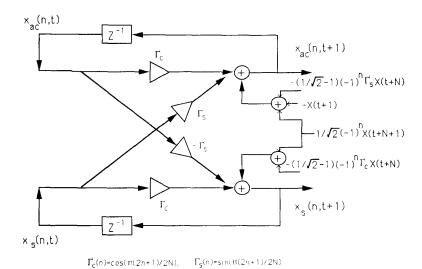

1) Lattice Structure for IDCT: Combining (18) and (23), we observe that the IDCT and AIDST can be generated in exactly the same way as the dual generation of the DCT and DST. Therefore, the lattice structure in Fig. 1 can be applied here except that the coefficients must be modified. Since the coefficients C(k)'s are inside the expression in the inverse transform, the relation between  $x_c(n, t)$  and  $\overline{x}_c(n, t + 1)$  will be different from what we have in the DCT. Equations (16) and (19) as well as (20) and (21) have the same terms for  $k \in \{t + 2, t + 3, \dots, t + N - 1\}$ . After adding the effects of the terms for k = t and k = t + 1, we obtain

$$\bar{x}_{c}(n, t+1) = x_{c}(n, t) - \frac{1}{\sqrt{2}}X(t) + \left(\frac{1}{\sqrt{2}} - 1\right)$$

$$\cdot \cos\left[\frac{\pi(2n+1)}{2N}\right]X(t+1)$$

(24)

and

$$\bar{x}_{as}(n, t+1) = x_{as}(n, t) + (-1)^{n}X(t+N) + \left(\frac{1}{\sqrt{2}} - 1\right) \\ \cdot \sin\left[\frac{\pi(2n+1)}{2N}\right]X(t+1).$$

(25)

The complete lattice module for the IDCT and AIDST is shown in Fig. 5. This IDCT lattice structure has the same lattice module as that of the DCT except for the input stage where one more adder and one more multiplier are required. The procedure to calculate the inverse transformed data is the same. Therefore, this IDCT lattice structure has the same advantages as that of the DCT. To obtain the inverse transform in parallel, we need N such IDCT lattice modules where 7N multipliers and 6N adders are required. Again, we see that the numbers of adders and multipliers are linear functions of N. Here we should notice that to obtain the inverse transform of the original input data sequence, for example,  $[x(0), x(1), x(2), \cdots,$ x(N-1)] and  $[x(N), x(N+1), \cdots, x(2N-1)]$ , it is sufficient only to send the transformed data corresponding to these two blocks, i.e.,  $[X(0), X(1), \cdots, X(N-1)]$ and  $[X(N), X(N + 1), \cdots, X(2N - 1)]$  respectively, although we have all the intermediate transformed data. Then by applying the time-recursive algorithm mentioned above, we obtain the original data after X(N-1) and X(2N-1) arrive, the intermediate data obtained by the inverse transform are redundant.

$$\label{eq:Gamma-constant} \begin{split} \Gamma_{c}(n) = & cos(\pi(2n+1)/2N), \qquad \Gamma_{s}(n) = sin(\pi(2n+1)/2N) \end{split}$$

Fig. 5. The lattice structure for the IDCT and AIDST.

## B. Time-Recursive IDST

From the definition of the DST in (6), the IDST for the transform domain sequence  $[X(t + 1), X(t + 2), \cdots, X(t + N)]$  is given by

$$x_{s}(n,t) = \sum_{k=t+1}^{t+N} D(k-t)X(k) \sin\left[\frac{\pi (2n+1)(k-t)}{2N}\right],$$

$$n = 0, 1, \cdots, N-1.$$

(26)

The coefficients D(k)'s are given in (6). Analogous to Section III-A, we define the auxiliary inverse discrete cosine transform (AIDCT)

$$x_{ac}(n, t) = \sum_{k=t+1}^{t+N} D(k-t)X(k) \\ \cdot \cos\left[\frac{\pi (2n+1)(k-t)}{2N}\right], \\ n = 0, 1, \cdots, N-1$$

(27)

which is the dually generated counterpart of the IDST. The IDST and AIDCT of the new sequence of transformed data  $[x(t + 2), X(t + 3), \dots, X(t + N + 1)]$  are given, respectively, by

$$x_{s}(n, t+1) = \sum_{k=t+2}^{t+N+1} D(k-t-1)X(k)$$

$$\cdot \sin\left[\frac{\pi(2n+1)(k-t-1)}{2N}\right]$$

(28)

and

$$x_{ac}(n, t+1) = \sum_{k=t+2}^{t+N+1} D(k-t-1)X(k)$$

$$\cdot \cos\left[\frac{\pi(2n+1)(k-t-1)}{2N}\right]. \quad (29)$$

Same as before, we can decompose (28) and (29) to

$$x_{s}(n, t + 1) = \bar{x}_{s}(n, t + 1) \cos\left[\frac{\pi (2n + 1)}{2N}\right] - \bar{x}_{c}(n, t + 1) \sin\left[\frac{\pi (2n + 1)}{2N}\right]$$

(30)

and

$$x_{ac}(n, 1) = \bar{x}_{c}(n, t + 1) \cos\left[\frac{\pi(2n + 1)}{2N}\right] + \bar{x}_{s}(n, t + 1) \sin\left[\frac{\pi(2n + 1)}{2N}\right]$$

(31)

where

$$\bar{x}_{ac}(n, t+1) = \sum_{k=t+2}^{t+N+1} D(k-t-1)X(k) \\ \cdot \cos\left[\frac{\pi (2n+1)(k-t)}{2N}\right]$$

(32)

and

$$\bar{x}_{s}(n, t+1) = \sum_{k=t+2}^{t+N+1} D(k-t-1)X(k)$$

$$\cdot \sin\left[\frac{\pi(2n+1)(k-t)}{2N}\right].$$

(33)

1) Lattice Structure for IDST and AIDCT: If we employ the time-recursive derivation in the previous section to exploit the relations between  $x_s(n, t + 1)$  and  $\bar{x}_s(n, t + 1)$  as well as  $x_{ac}(n, t + 1)$  and  $\bar{x}_{ac}(n, t + 1)$ , the results

1363

1364

are

$$\bar{x}_{s}(n, t + 1) = x_{s}(n, t) - \sin\left\{\frac{\pi (2n + 1)}{2N}\right\} X(t + 1)$$

$$- \left(\frac{1}{\sqrt{2}} - 1\right) (-1)^{n} X(t + N)$$

$$+ \frac{1}{\sqrt{2}} (-1)^{n} \cos\left[\frac{\pi (2n + 1)}{2N}\right]$$

$$\cdot X(t + N + 1)$$

(34)

and

$$\bar{x}_{ac}(n, t + 1) = x_{ac}(n, t) - \cos\left[\frac{\pi (2n + 1)}{2N}\right] X(t + 1)$$

$$-\frac{1}{\sqrt{2}} (-1)^n \sin\left[\frac{\pi (2n + 1)}{2N}\right]$$

$$\cdot X(t + N + 1).$$

(35)

Equations (30), (31), (34), and (35) reveal that to dually generate the IDST and AIDCT requires 9 multipliers and 7 adders, more than that required for the IDCT and AIDST. The result is shown in Fig. 6. To reduce the number of multipliers and adders, substitute (34) and (35) into (30) and (31) and rearrange (30) and (31), we have

$$x_{s}(n, t + 1) = \cos\left[\frac{\pi(2n + 1)}{2N}\right] x_{s}(n, t)$$

-  $\sin\left[\frac{\pi(2n + 1)}{2N}\right] x_{ac}(n, t)$

-  $\left(\frac{1}{\sqrt{2}} - 1\right)(-1)^{n}$

$\cdot \cos\left[\frac{\pi(2n + 1)}{2N}\right] X(t + N)$

+  $\left(\frac{1}{\sqrt{2}}\right)(-1)^{n} X(t + N + 1)$  (36)

and

$$\begin{aligned} x_{ac}(n, t+1) &= \cos\left[\frac{\pi (2n+1)}{2N}\right] x_{ac}(n, t) \\ &+ \sin\left[\frac{\pi (2n+1)}{2N}\right] x_s(n, t) - X(t+1) \\ &- \left(\frac{1}{\sqrt{2}} - 1\right) (-1)^n \sin\left[\frac{\pi (2n+1)}{2N}\right] \\ &\cdot X(t+N) + \left(\frac{1}{\sqrt{2}}\right) (-1)^n \\ &\cdot X(t+N+1). \end{aligned}$$

(37)

The lattice module of this rearranged IDST and AIDCT is shown in Fig. 7. This structure differs from all the previous lattice modules in that the input signals are added at the end of the lattice. From now on, we call this lattice

structure a postlattice module and the previous ones prelattice modules. This postlattice module needs 7 multipliers and 7 adders, less than required for the corresponding prelattice module. A parallel post-lattice structure, which generates N transformed data simultaneously, requires 7N multipliers and 7N adders. All the forward and inverse transform pairs mentioned above have prelattice and postlattice structures. Not all postlattice structures are superior to their prelattice counterparts in the hardware complexity. For example, the IDCT and AIDST postlattice form can be expressed as

$$\begin{aligned} x_{as}(n, t+1) &= \cos\left[\frac{\pi(2n+1)}{2N}\right] x_{as}(n, t) \\ &- \sin\left[\frac{\pi(2n+1)}{2N}\right] x_c(n, t) \\ &- \left(\frac{1}{\sqrt{2}}\right) \sin\left[\frac{\pi(2n+1)}{2N}\right] X(t) \\ &+ (-1)^n X(t+N) \cos\left[\frac{\pi(2n+1)}{2N}\right] \end{aligned}$$

(38)

and

$$\begin{aligned} x_{c}(n, t+1) &= \cos\left[\frac{\pi (2n+1)}{2N}\right] x_{c}(n, t) \\ &+ \sin\left[\frac{\pi (2n+1)}{2N}\right] x_{as}(n, t) - \left(\frac{1}{\sqrt{2}}\right) \\ &\cdot \cos\left[\frac{\pi (2n+1)}{2N}\right] X(t) \\ &- X(t+1) + \left(\frac{1}{\sqrt{2}} - 1\right) X(t+1) \\ &+ (-1)^{n} \sin\left[\frac{\pi (2n+1)}{2N}\right] X(t+N). \end{aligned}$$

(39)

This postlattice module has 9 multipliers and 7 adders which are more than its prelattice realization. As to the DCT and DST, the postlattice form can be expressed as

$$X_{c}(k, t + 1) = \cos\left(\frac{\pi k}{N}\right) X_{c}(k, t) + \sin\left(\frac{\pi k}{N}\right) X_{s}(k, t)$$

$$+ \left(\frac{2}{N}\right) \cos\left(\frac{\pi k}{2N}\right)$$

$$\cdot \left[-x(t) + (-1)^{k} x(t + N)\right]$$

(40)

and

$$X_{s}(k, t + 1) = \cos\left(\frac{\pi k}{N}\right) X_{s}(k, t) - \sin\left(\frac{\pi k}{N}\right) X_{s}(k, t)$$

$$- \left(\frac{2}{N}\right) \sin\left(\frac{\pi k}{2N}\right)$$

$$\cdot [-x(t) + (-1)^{k} x(t + N)].$$

(41)

Fig. 6. The prelattice structure for the IDST and AIDCT.

Fig. 7. The postlattice structure for the IDST and AIDCT.

In this case, the prelattice and postlattice modules have the same numbers of multipliers and adders.

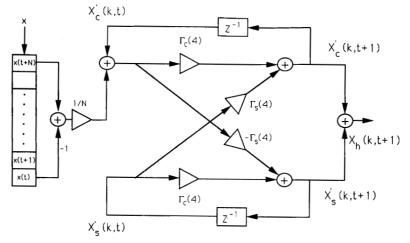

# IV. DISCRETE HARTLEY TRANSFORM (DHT)

According to Bracewell's definition of the DHT in [6], the data sequence x(n) and the DHT transformed data X(k) have the following relation:

$$X_{h}(k, t) = \frac{1}{N} \sum_{n=t}^{t+N-1} x(n) \cos\left(\frac{2\pi k(n-t)}{N}\right)$$

=  $\frac{1}{N} \sum_{n=t}^{t+N-1} x(n) \left[\cos\left(\frac{2\pi k(n-t)}{N}\right) + \sin\left(\frac{2\pi k(n-t)}{N}\right)\right],$

$k = 0, 1, \dots, N-1.$  (42)

The DHT uses real expressions  $\cos (2\pi k(n - t)/N) + \sin (2\pi k(n - t)/N)$  as the transform kernel, while discrete Fourier transform (DFT) uses the complex exponential expression exp  $(i2\pi k(n - t)/N)$  as the transform kernel. Because the kernel of the DHT is a summation of cosine and sine terms, we can separate them into a combination of a DCT-like and a DST-like transforms as follows:

$$X_{h}(k, t) = \dot{X}_{c}(k, t) + \dot{X}_{s}(k, t)$$

(43)

where

$$\dot{X}_{c}(k, t) = \frac{1}{N} \sum_{n=t}^{t+N-1} x(n) \left[ \cos \left( \frac{2\pi k(n-t)}{N} \right) \right]$$

(44)

and

$$\dot{X}_{s}(k, t) = \frac{1}{N} \sum_{n=t}^{t+N-1} x(n) \left[ \sin \left( \frac{2\pi k (n-t)}{N} \right) \right].$$

(45)

Fig. 8. The lattice structure for the DHT for  $k = 1, 2, \cdots, N - 1$ .

Fig. 9. The lattice structure for the DHT for k = 0.

The  $\dot{X}_c(k, t)$  is the so-called DCT-I and the  $\dot{X}_s(k, t)$  is the DST-I that are defined by Yip and Rao in [22]. Since the DHT can be decomposed into the combination of the DCT-I and DST-I, the dual generation of both for the DHT is thus possible. The DCT-I and DST-I of the data sequence  $[x(t + 1), x(t + 2), \cdots, x(t + N)]$  are

$$\dot{X}_{c}(k, t+1) = \frac{1}{N} \sum_{n=t+1}^{t+N} x(n) \cos\left[\frac{2\pi k (n-t-1)}{N}\right]$$

(46)

and

$$\dot{X}_{s}(k, t+1) = \frac{1}{N} \sum_{n=t+1}^{t+N} x(n) \sin\left[\frac{2\pi k(n-t-1)}{N}\right].$$

(47)

The new transforms  $\dot{X}_c(k, t + 1)$  and  $\dot{X}_s(k, t + 1)$  can be further expressed as

$$\dot{X}_{c}(k, t+1) = \overline{\dot{X}}_{c}(k, t+1) \cos\left(\frac{2\pi k}{N}\right) + \overline{\ddot{X}}_{s}(k, t+1) \sin\left(\frac{2\pi k}{N}\right)$$

(48)

and

$$\dot{X}_{s}(k, t+1) = \overline{\dot{X}}_{s}(k, t+1) \cos\left(\frac{2\pi k}{N}\right) - \overline{\dot{X}}_{c}(k, t+1) \sin\left(\frac{2\pi k}{N}\right)$$

(49)

where

$$\overline{\vec{X}}_{c}(k, t+1) = \frac{1}{N} \sum_{n=t+1}^{t+N} x(n) \cos\left(\frac{2\pi k(n-t)}{N}\right)$$

$$= \vec{X}_{c}(k, t) + \frac{1}{N} \left[-x(t) + x(t+N)\right] \quad (50)$$

and

$$\overline{\hat{X}}_{s}(k, t + 1) = \frac{1}{N} \sum_{n=t+1}^{t+N} x(n) \sin\left(\frac{2\pi k(n-t)}{N}\right) = \hat{X}_{s}(k, t).$$

(51)

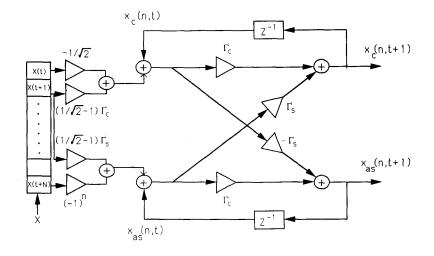

The lattice module for the DHT is shown in Fig. 8. For the case of k = 0, the lattice structure can be simplified as shown in Fig. 9. From Fig. 8, we can see that the numbers of multipliers and adders are less than those of

1366

Fig. 10. The lattice structure for block-size-two operation on the DCT and DST.

the dual generation of the DCT and DST. The total numbers of multipliers and adders in the parallel DHT lattice architecture are 5N - 4 and 5N - 3, respectively.

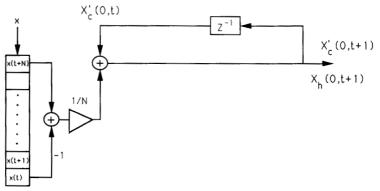

## V. BLOCK PROCESSING

All the time-recursive discrete transforms derived above are based on the block-size-one update which means the time index is updated by one. That is, at each iteration only the effect of one old datum is removed and the information of one new datum is added. We are interested in the relation between the area-time complexity (AT) and block size. This motivates us to discuss the effect on the lattice structure when the block size is increased.

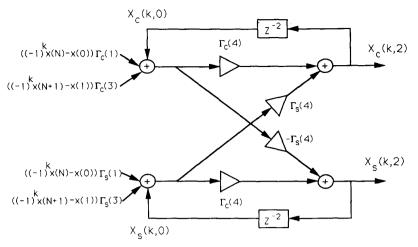

#### A. Block Processing of Time-Recursive DCT and DST

We begin the discussion of block processing with the block-size-two update. Here we assume the time index t in (1) is zero for simplicity, and we will use this in the following discussions. As before, the transformed data  $X_c(k, 2)$  and  $X_s(k, 2)$  are defined as the DCT and DST of the input vector  $[x(2), x(3), \dots, x(N), x(N + 1)]$ . That is,

$$X_{c}(k, 2) = \sum_{n=2}^{N+1} x(n) \cos\left\{\frac{\pi [2(n-2)+1]k}{2N}\right\}$$

(52)

and

$$X_{s}(k, 2) = \sum_{n=2}^{N+1} x(n) \sin\left\{\frac{\pi [2(n-2)+1]k}{2N}\right\}.$$

(53)

To obtain  $X_c(k, 2)$  from  $X_c(k, 0)$  and  $X_s(k, 2)$  from  $X_s(k, 0)$  directly, we can rewrite  $X_c(k, 2)$  and  $X_s(k, 2)$  as

$$X_{c}(k, 2) = \overline{X}_{c}(k, 2) \cos\left(\frac{2\pi k}{N}\right) + \overline{X}_{s}(k, 2) \sin\left(\frac{2\pi k}{N}\right)$$

(54)

$$X_{s}(k, 2) = \overline{X}_{s}(k, 2) \cos\left(\frac{2\pi k}{N}\right) - \overline{X}_{c}(k, 2) \sin\left(\frac{2\pi k}{N}\right)$$

(55)

where

$$\overline{X}_{c}(k, 2) = \sum_{n=2}^{N+1} x(n) \cos\left[\frac{\pi (2n+1)k}{2N}\right]$$

$$= X_{c}(k, 0) + [-x(0) + (-1)^{k}x(N)] \cos\left(\frac{\pi k}{2N}\right)$$

$$+ [-x(1) + (-1)^{k}x(N+1)] \cos\left(\frac{3\pi k}{2N}\right)$$

(56)

and

$$\overline{X}_{s}(k, 2) = \sum_{n=2}^{N+1} x(n) \sin\left[\frac{\pi(2n+1)k}{2N}\right]$$

$$= X_{s}(k, 0) + [-x(0) + (-1)^{k}x(N)] \sin\left(\frac{\pi k}{2N}\right)$$

$$+ [-x(1) + (-1)^{k}x(N+1)] \sin\left(\frac{3\pi k}{2N}\right).$$

(57)

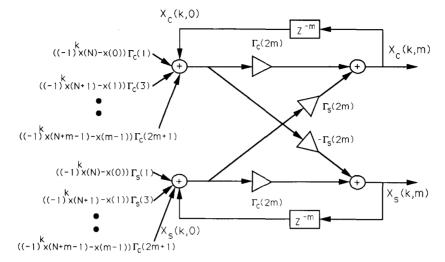

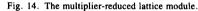

The lattice module for the block-size-two update is shown in Fig. 10. There are two more multipliers in the lattice, i.e., the total number of multipliers is eight. To obtain the transformed data in parallel, we need N such lattice modules. The latency for this kind of parallel structure is N/2and the total number of multipliers is 8N. Since there is no complex communication problem in the lattice structure, the area-time complexity (AT) can be approximated by the product of the number of multipliers and the time latency, plus the area-time complexity of the adders, which is  $o(m \log (m))$  for adding m data. Next, let us consider the more general case for the block-size-m update, where m ranges from one to N. The 1-D DCT and DST of block-size-m update are to obtain the transform of  $[x(m), x(m + 1), \dots, x(N + m - 1)]$  directly from

Fig. 11. The lattice structure for block-size-m operation on the DCT and DST.

(58)

the transform of  $[x(0), x(1), \cdots, x(N-1)]$ . We have  $X_c(k, m) = \sum_{n=m}^{N+m-1} x(n) \cos \left[ \frac{\pi [2(n-m)+1]k}{2N} \right]$

and

$$X_{s}(k, m) = \sum_{n=m}^{N+m-1} x(n) \sin\left[\frac{\pi [2(n-m)+1]k}{2N}\right].$$

(59)

Applying the same procedure in the case of block-sizetwo update, we can write (58) and (59) as

$$X_{c}(k, m) = \overline{X}_{c}(k, m) \cos\left(\frac{m\pi k}{N}\right) + \overline{X}_{s}(k, m) \sin\left(\frac{m\pi k}{N}\right)$$

(60)

and

$$X_s(k, m) = \overline{X}_s(k, m) \cos\left(\frac{m\pi k}{N}\right) - \overline{X}_c(k, m) \sin\left(\frac{m\pi k}{N}\right)$$

(61)

where

$$\bar{X}_{c}(k, m) = \sum_{n=m}^{N+m-1} x(n) \cos \left[ \frac{\pi (2n+1)k}{2N} \right]$$

$$= X_{c}(k, 0) - \sum_{n=0}^{m-1} x(n) \cos \left( \frac{\pi (2n+1)k}{2N} \right)$$

$$+ \sum_{n=N}^{N+m-1} x(n) \cos \left[ \frac{\pi (2n+1)k}{2N} \right]$$

$$= X_{c}(k, 0) + \sum_{n=0}^{m-1} [-x(n) + (-1)^{k} x(N+n)]$$

$$\cdot \cos \left[ \frac{\pi (2n+1)k}{2N} \right]$$

(62)

and

$$\overline{X}_{s}(k, m) = \sum_{n=m}^{N+m-1} x(n) \sin\left[\frac{\pi (2n + 1)k}{2N}\right]$$

$$= X_{s}(k, 0) - \sum_{n=0}^{m-1} x(n) \sin\left[\frac{\pi (2n + 1)k}{2N}\right]$$

$$+ \sum_{n=N}^{N+m-1} x(n) \sin\left[\frac{\pi (2n + 1)k}{2N}\right]$$

$$= X_{c}(k, 0) + \sum_{n=0}^{m-1} [-x(n) + (-1)^{k}x(N + n)]$$

$$\cdot \sin\left[\frac{\pi (2n + 1)k}{2N}\right].$$

(63)

Combining those input terms with same cosine and sine multiplier coefficients together, we can obtain the lattice module for block size m as shown in Fig. 11. To obtain the transform data X(k) in parallel, N lattice modules of Fig. 11 are required. The total number of multipliers of the parallel structure is (4 + 2m)N, the total number of adders is (3m + 2)N, and the throughput is 1. The areatime complexity due to multipliers and adders are (4 +2m)N and  $(3m + 2)N \log ((3m + 2)N)$ , respectively. Denote ATm as the area-time complexity of the block-sizem update, then  $ATm = (4 + 2m)N + (3m + 2)N \log ((3m + 2)N)$ (+2)N). For example,  $AT1 = 6N + [5N \log (5N)]$  and  $AT2 = 8N + [8N \log (8N)]$ . In the limiting case of blocksize N update, i.e., we move a whole block of the input data sequence,  $ATN \simeq (4 + 2N)N + 3N^2 \log (3N^2)$ . In general, the area-time product gets smaller as block size m decreases. We found that when m = 1, the minimum AT complexity is achieved.

# VI. MULTIPLIER REDUCTION OF THE LATTICE STRUCTURE

In the VLSI implementation, the number of multipliers is an important factor to the cost and complexity of the

Fig. 13. The model of multiplier reduction.

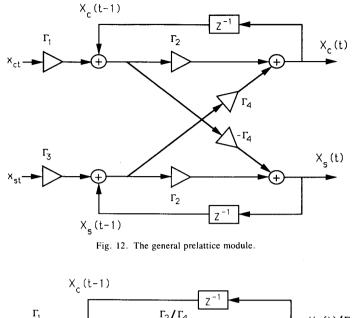

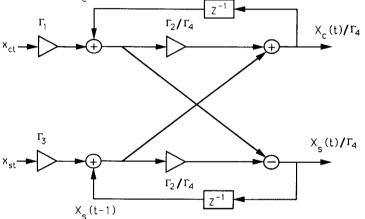

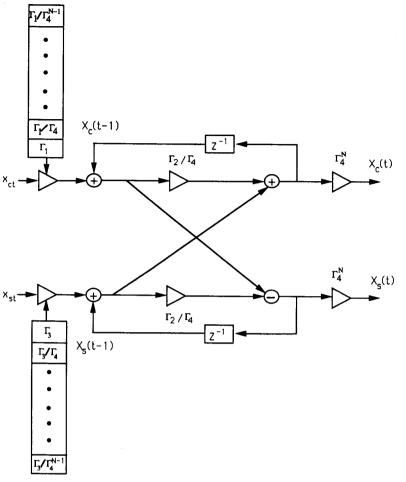

system. In this section, we develop two methods to reduce the number of multipliers in our parallel lattice structures. The first scheme makes use of a series input series output (SISO) approach and 2N multipliers can be saved; the tradeoff is that the latency and throughput is increased. The second approach, which reconstructs the structure into a double-lattice realization, saves N multipliers and the latency remains intact.

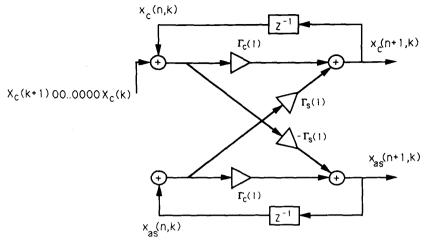

#### A. SISO Approach

Let us consider this problem through a general lattice structure as shown in Fig. 12. Denote the output and input data at time t as  $(X_c(t), X_s(t))$  and  $(x_{ct}, x_{st})$ , respectively, where the input and output have the following relations:

$$\begin{aligned} X_c(t) &= [X_c(t-1) + \Gamma_1 x_{ct}] \Gamma_2 + [X_s(t-1) + \Gamma_3 x_{st}] \Gamma_4 \\ X_s(t) &= [X_s(t-1) + \Gamma_3 x_{st}] \Gamma_2 - [X_c(t-1) + \Gamma_1 x_{ct}] \Gamma_4. \end{aligned}$$

(64)

By dividing both equations by  $\Gamma_4$ , we have

$$X_{c}(t)/\Gamma_{4} = [X_{c}(t-1) + \Gamma_{1}x_{ct}]\Gamma_{2}/\Gamma_{4} + [X_{s}(t-1) + \Gamma_{3}x_{st}] X_{s}(t)/\Gamma_{4} = [X_{s}(t-1) + \Gamma_{3}x_{st}]\Gamma_{2}/\Gamma_{4} - [X_{c}(t-1) + \Gamma_{1}x_{ct}].$$

(65)

The lattice structure manifesting the above relations is shown in Fig. 13. It is noted that only four multipliers exist in this structure and the outputs obtained differ from the original one by a factor  $\Gamma_4$ . To examine the effect of this multiplier reduction on the recursive operation from  $X_c(1)$  to  $X_c(N)$ , we start with the derivation from t = 1. That is

$$X_{c}(1)/\Gamma_{4} = [X_{c}(0) + \Gamma_{1}x_{c1}]\Gamma_{2}/\Gamma_{4} + [X_{s}(0) + \Gamma_{3}x_{s1}]$$

$$X_{s}(1)/\Gamma_{4} = [X_{s}(0) + \Gamma_{3}x_{s1}]\Gamma_{2}/\Gamma_{4} - [X_{c}(0) + \Gamma_{1}x_{c1}].$$

(66)

For

$$t = 2$$

$$\begin{aligned} X_c(2)/\Gamma_4 &= [X_c(1) + \Gamma_1 x_{c2}] \Gamma_2/\Gamma_4 + [X_s(1) + \Gamma_3 x_{s2}] \\ X_s(2)/\Gamma_4 &= [X_s(1) + \Gamma_3 x_{s2}] \Gamma_2/\Gamma_4 - [X_c(1) + \Gamma_1 x_{c2}]. \end{aligned}$$

(67)

Because the outputs at time t = 1 are  $X_c(1)/\Gamma_4$  and  $X_s(1)/\Gamma_4$ ,  $X_c(1)$  and  $X_s(1)$  at (67) should be replaced by  $X_c(1)/\Gamma_4$  and  $X_s(1)/\Gamma_4$ . To keep the above equations valid, we can multiply both equations by  $1/\Gamma_4$  as shown

$$X_{c}(2)/\Gamma_{4}^{2} = [X_{c}(1)/\Gamma_{4} + (\Gamma_{1}/\Gamma_{4})x_{c2}]\Gamma_{2}/\Gamma_{4} + [X_{s}(1)/\Gamma_{4} + (\Gamma_{3}/\Gamma_{4})x_{s2}] X_{s}(2)/\Gamma_{4}^{2} = [X_{s}(1)/\Gamma_{4} + (\Gamma_{3}/\Gamma_{4})x_{s2}]\Gamma_{2}/\Gamma_{4} - [X_{s}(1)/\Gamma_{4} + (\Gamma_{1}/\Gamma_{4})x_{c2}].$$

(68)

The coefficients of the input multipliers are  $\Gamma_1/\Gamma_4$  and  $\Gamma_3/\Gamma_4$ , instead of  $\Gamma_1$  and  $\Gamma_3$  at times t = 1, and the outputs are  $X_c(2)/\Gamma_4^2$  and  $X_s(2)/\Gamma_4^2$ . For t = N, the recursive

equations become

$$X_{c}(N)/\Gamma_{4}^{N} = [X_{c}(N-1)/\Gamma_{4}^{N-1} + (\Gamma_{1}/\Gamma_{4}^{N-1})x_{cN}]\Gamma_{2}/\Gamma_{4} + [X_{s}(N-1)/\Gamma_{4}^{N-1} + (\Gamma_{3}/\Gamma_{4}^{N-1})x_{sN}]$$

$$X_{s}(N)/\Gamma_{4}^{N} = [X_{s}(N-1)/\Gamma_{4}^{N-1} + (\Gamma_{3}/\Gamma_{4}^{N-1})x_{sN}]\Gamma_{2}/\Gamma_{4} - [X_{c}(N-1)/\Gamma_{4}^{N-1} + (\Gamma_{1}/\Gamma_{4}^{N-1})x_{cN}].$$

(69)

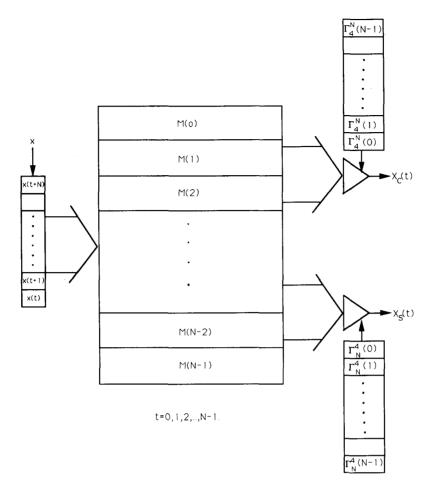

From the above derivations, we observe that the two multipliers can be removed by using variable multipliers in the input stage where the coefficients  $(\Gamma_1, \Gamma_1/\Gamma_4, \cdots, \Gamma_1/\Gamma_4^{N-1})$  and  $(\Gamma_3, \Gamma_3/\Gamma_4, \cdots, \Gamma_3/\Gamma_4^{N-1})$  are stored in shift registers. The structure is shown in Fig. 14. The output can be obtained by multiplying the factor  $\Gamma_4^N$ . This kind of rearrangement does not save multipliers. However, for N such lattice structures, the number of multi-

Fig. 15. The complete parallel multiplier-reduced lattice structure.

pliers can be reduced by using variable multipliers at the output stage and the coefficients for each stage  $\Gamma_4^N(i)$ ,  $i = 0, 1, 2, \dots, N-1$ , are stored in the shift registers. Fig. 15 shows the final structure where the total number of multipliers is 4N + 2. This means that the number of multipliers for N parallel such lattice structures is reduced from 6N to 4N + 2. The tradeoff is that 4N + 2 shift registers are required and the latency becomes 2N instead of N. Also, this resulting structure is a SISO system, while the original parallel structure is a SIPO system.

For example, the variable-multiplier method derived above can be applied to the lattice structure of the DCT and DST. There are no multipliers needed for t = 0, therefore the module remains the same. For  $t = 1, 2, \cdots$ , N - 1, the multiplier-reduced lattice structure is shown in Fig. 15, where the coefficients are  $\Gamma_1 = \cos(k\pi/2N)$ ,  $\Gamma_2 = \cos(k\pi/N)$ ,  $\Gamma_3 = \sin(k\pi/2N)$ , and  $\Gamma_4$  $= \sin(k\pi/N)$ . The total number of multipliers is 4N - 2and the latency for this SISO structure is 2N.

It is readily seen that the SISO approach for multiplier reduction is in fact a denormalization of the orthogonal rotation in the lattice. It is well known that the orthogonal rotation is numerical stable so that the roundoff errors will not be accumulated. However, the denormalized lattice does not have such a nice numerical property in finiteprecision implementation, i.e., the roundoff errors may continue to accumulate and lower the signal-to-noise ratio. This effect can be minimized by giving enough register length such as double precision in the implementation. Also, we note that since  $\Gamma_4 < 1$ ,  $\Gamma_4^N$  could be very small. Not enough precision may result in bad numerical accuracy when  $\Gamma_4^N$  is multiplied at the output stage. Thus, the registers that store  $\Gamma_4^N$  do need enough precision to avoid the accuracy problem. The problems addressed here are consequences of the tradeoff between complexity and performance.

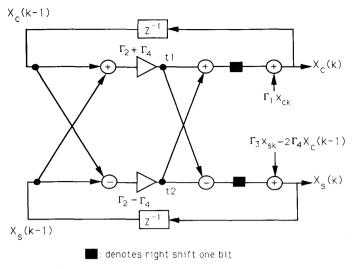

#### B. Double-Lattice Approach

Generally, a postlattice structure has the following forms:

$$X_{c}(k) = \Gamma_{2}X_{c}(k-1) + \Gamma_{4}X_{s}(k-1) + \Gamma_{1}x_{ck}$$

$$X_{s}(k) = \Gamma_{2}X_{s}(k-1) - \Gamma_{4}X_{c}(k-1) + \Gamma_{3}x_{sk}.$$

(70)

1371

Fig. 16. The double-lattice form of the postlattice realization.

Based on the relationships shown below

$$\begin{split} \Gamma_2 X_c(k - 1) &+ \Gamma_4 X_s(k - 1) \\ &= \frac{1}{2} \left\{ (\Gamma_2 + \Gamma_4) \left[ X_c(k - 1) + X_s(k - 1) \right] \right. \\ &+ \left. (\Gamma_2 - \Gamma_4) \left[ X_c(k - 1) - X_s(k - 1) \right] \right\} \ (71) \end{split}$$

and

$$\Gamma_{2}X_{s}(k-1) - \Gamma_{4}X_{c}(k-1)$$

$$= \Gamma_{2}X_{s}(k-1) + \Gamma_{4}X_{c}(k-1) - 2\Gamma_{4}X_{c}(k-1)$$

$$= \frac{1}{2} \{ (\Gamma_{2} + \Gamma_{4}) [X_{c}(k-1) + X_{s}(k-1)] - (\Gamma_{2} - \Gamma_{4}) [X_{c}(k-1) - X_{s}(k-1)] \}$$

$$- 2\Gamma_{4}X_{c}(k-1)$$

(72)

$X_c(k)$  and  $X_s(k)$  can be rearranged in the following manner:

$$\begin{aligned} X_{c}(k) &= \frac{1}{2} \left\{ (\Gamma_{2} + \Gamma_{4}) [X_{c}(k-1) + X_{s}(k-1)] \right. \\ &+ (\Gamma_{2} - \Gamma_{4}) [X_{c}(k-1) - X_{s}(k-1)] \right\} + \Gamma_{1} x_{ck} \\ &= \frac{1}{2} \left\{ t1 + t2 \right\} + \Gamma_{1} x_{ck} \\ X_{s}(k) &= \frac{1}{2} \left\{ (\Gamma_{2} + \Gamma_{4}) [X_{c}(k-1) + X_{s}(k-1)] \right. \\ &- (\Gamma_{2} - \Gamma_{4}) [X_{c}(k-1) - X_{s}(k-1)] \right\} \\ &- 2\Gamma_{4} X_{c}(k-1) + \Gamma_{3} x_{ck} \\ &= \frac{1}{2} \left\{ t1 - t2 \right\} - 2\Gamma_{4} X_{c}(k-1) + \Gamma_{3} x_{ck} \end{aligned}$$

(73)

where

$$t1 = (\Gamma_2 + \Gamma_4) [X_c(k-1) + X_s(k-1)]$$

(74)

and

$$t2 = (\Gamma_2 - \Gamma_4) [X_c(k-1) - X_s(k-1)]. \quad (75)$$

The operational flow chart of (73) is illustrated in Fig. 16. Instead of calculating the outputs from (70) directly (that requires 6 multipliers and 4 adders), the first lattice adds and subtracts  $X_c(k-1)$  and  $X_s(k-1)$ , then multiplies the results by  $\Gamma_2 + \Gamma_4$  and  $\Gamma_2 - \Gamma_4$ , respectively. The results are called t1 and t2 as defined in (74) and (75). The second lattice adds and subtracts t1 and t2 again, then divides the results by 2, which can be achieved by right shifting. Finally, we complete the computations by adding the inputs  $\Gamma_1 x_{ck}$  and  $\Gamma_3 x_{ck} - 2\Gamma_4 X_c (k-1)$ . This reconstruction can save one multiplier. A parallel postlattice structure with N lattice modules requires 6Nmultipliers and 4N adders. As for this reconstructed parallel structure, only 5N multipliers and 7N adders are needed. This approach can be applied to all the parallel postlattice structures of different orthogonal transforms. In general, this parallel double-lattice structure can save N multipliers, but requires 3N more adders. The latency is N clock cycles and the system remains SIPO.

#### VII. COMPARISONS OF ARCHITECTURES

From the previous discussions, we see that the proposed unified parallel lattice structures have many attractive features. There are no constraints on the transform size N. It dually generates the two discrete transforms DCT and DST simultaneously. Since it produces the transformed data of subsequent input vector every clock cycle, it is especially efficient for systems with series input data such as communication systems. Further, the structure is regular, modular, and without global communication. As a consequence, it is suitable for VLSI implementation.

Here, we would like to compare our lattice structures of the DCT and DST with those proposed in [14], [15], [7]. The architecture in [14] uses the matrix factorization method which is a representative of fast algorithms. In [15], an improved fast structure with fewer multipliers is

|                                | COM       | IPARISON OF DIFFERE | NT DCT ALGORITHMS         |                          |              |

|--------------------------------|-----------|---------------------|---------------------------|--------------------------|--------------|

|                                | Liu-Chiu1 | Liu-Chiu2           | Chen [14]<br>et. al.      | Lee [15]                 | Hou [7]      |

| No. of Multipliers             | 6N - 4    | 4 <i>N</i>          | $\frac{N\ln(N)}{-3N/2+4}$ | $(N/2) \ln (N)$          | N - 1        |

| Latency                        | Ν         | 2 <i>N</i>          | N/2                       | $[\ln(N)(\ln(N) - 1)]/2$ | 3N/2 (order) |

| Limitation on Transform Size N | no        | no                  | power of 2                | power of 2               | power of 2   |

| Communication                  | local     | local               | global                    | global                   | global       |

| I/O operation                  | SIPO      | SISO                | PIPO                      | PIPO                     | ŠIPO         |

TABLE I

Comparison of Different DCT Algorithms

| TABLE II<br>Comparison of the Number of Multipliers |                |                |            | TABLE III           Comparison of the Number of Adders |          |          |                |                |            |            |           |

|-----------------------------------------------------|----------------|----------------|------------|--------------------------------------------------------|----------|----------|----------------|----------------|------------|------------|-----------|

| No                                                  | Liu-Chiu1      | Liu-Chiu2      | Chen       | Lee                                                    | Hou      | No       | Liu-Chiu1      | Liu-Chiu2      | Chen       | Lee        | Hou       |

| 8<br>16                                             | 44/2<br>92/2   | $\frac{32}{2}$ | 16<br>44   | 12<br>32                                               | 7        | 8<br>16  | 39/2<br>79/2   | 39/2<br>79/2   | 26<br>74   | 29<br>81   | 18        |

| 32<br>64                                            | 188/2<br>380/2 | 128/2<br>256/2 | 116<br>292 | 80<br>192                                              | 31<br>63 | 32<br>64 | 159/2<br>319/2 | 159/2<br>319/2 | 194<br>482 | 209<br>513 | 88<br>183 |

proposed. Hou's architecture in [7] uses recursive computations to generate the higher order DCT from the lower order one. The characteristics of these structures are discussed in the introduction. A comparison regarding their inherent properties is listed in Table I. To be clear, the quantitative comparisons in terms of the parameters, which are the numbers of multipliers, adders, and the latency, are given in Tables II-IV.

The lattice architecture with six multipliers in the module as shown in Fig. 2 is called Liu-Chiu1 structure, the one in Fig. 15 is called Liu-Chiu2, and the parallel structure with the double-lattice modules as shown in Fig. 16 is called Liu-Chiu3. The structure in Liu-Chiu1 has 6N - 4 multipliers, 5N - 1 adders, and the latency is N. There are 4N multipliers, 5N - 1 adders, and the latency is 2N in the structure of Liu-Chiu2. The number of multipliers is reduced by the order 2N in the expense of doubling the latency and the data flow becoming SISO. The Liu-Chiu3 architecture has 5N multipliers and 7N adders and the latency is N clock cycles. From these tables, it is noted that the number of multipliers in our architectures is higher than that of others when N is small. This is due to the dual generation of two transforms structure which is compatible with Lee's. Since the numbers of multipliers and adders of our structures are on the order N, our algorithms have fewer multipliers and adders than those proposed in [14], [15]. Although Hou's algorithm has the fewest multipliers, his architecture needs global communications and the design complexity is much higher than ours. In addition, the operations of other structures cannot start until all of the data in the block arrive.

A comparison for our DHT structure based on the lattice module in Fig. 8 and different DHT algorithms [23], [18] is listed in Table V. The architecture in [23], a representative fast algorithm, is developed base on the existing FFT method. Chaitali-JaJa's algorithm in [18] decomposes the transform size N into mutually prime numbers and implements them in a systolic manner. Their structure needs extra registers and the latency is higher

TABLE IV

| COMPARISON OF THE LATENCY |           |           |      |     |     |  |

|---------------------------|-----------|-----------|------|-----|-----|--|

| No                        | Liu-Chiul | Liu-Chiu2 | Chen | Lee | Hou |  |

| 8                         | 8         | 16        | 4    | 6   | 13  |  |

| 16                        | 16        | 32        | 6    | 10  | 21  |  |

| 32                        | 32        | 64        | 8    | 15  | 44  |  |

| 64                        | 64        | 128       | 10   | 21  | 73  |  |

than others. It is easy to see that our structure is better than others in terms of hardware complexity and speed.

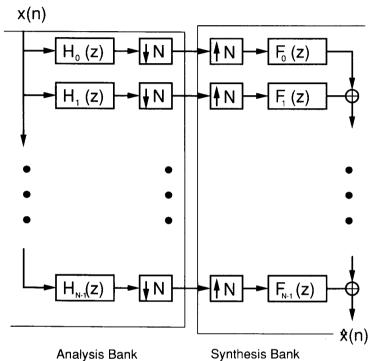

#### VIII. FILTER BANK INTERPRETATION OF THE TIME-RECURSIVE SINUSOIDAL TRANSFORMS

Multirate digital filters and filter banks find applications in communications, speech processing, and image compression. There are two basic types of filter banks. An analysis bank is a set of analysis filters  $H_k(z)$  and Nfold decimators which split a signal into N subbands. A synthesis filter bank (the right part of Fig. 17) consists of N synthesis filters  $F_k(z)$  and N-fold interpolators, which combine N signals into a reconstructed signal  $\hat{x}(n)$ . As described in Section II, the time-recursive approach decomposed the transformed domain data into N different components. If we are interested in the block-size-N transform and perform the N-fold decimation in the outputs of every lattice modules, the analysis bank is simply the seriesinput-parallel-output filter bank described in Fig. 17. Under this condition, the analysis bank is equivalent to perform a transformation and the synthesis bank to perform an inverse transformation on successive blocks of N data samples. In this section, we describe how to employ the time-recursive concept to generate the synthesis banks based on the DCT, DST, and DHT.

#### A. Synthesis Bank Structure Based on DCT

To perform the inverse transform in the synthesis bank, we feed the DCT transformed domain components  $X_c(k)$

| COMPARISON OF DIFFERENT DHT ALGORITHMS |          |                       |                                              |  |  |  |

|----------------------------------------|----------|-----------------------|----------------------------------------------|--|--|--|

|                                        | Liu-Chiu | Sorenson [23]         | Chitali-JaJa [18]                            |  |  |  |

| No. of Multipliers                     | 4N       | $N \ln (N) - 3N + 4$  | N1 + N2                                      |  |  |  |

| No. of Adders                          | 5N - 2   | $3N \ln (N) - 3N + 4$ | $4N + \sqrt{N1}$                             |  |  |  |

| Latency                                | Ν        | $N \ln (N)$           | N1 + N2                                      |  |  |  |

| Limitation on Transform Size           | no       | power of 2            | N = N1 * N2, N1 and N2<br>are mutually prime |  |  |  |

| Communication                          | local    | global                | local                                        |  |  |  |

| I/O operation                          | SIPO     | PIPO                  | SISO                                         |  |  |  |

TABLE V Comparison of Different DHT Algorithms

into the synthesis modules and combine all the outputs of every synthesis modules to produce the original input sequence  $x_c(n)$ . That is, the synthesis bank performs the following inverse DCT operations:

$$x_{c}(n) = \sum_{k=0}^{N-1} C(k) X_{c}(k) \cos\left[\frac{\pi k (2n+1)}{2N}\right].$$

(76)

Since in the synthesis bank different transform components are sent to independent synthesis modules, we therefore focus on a specific transform component. Denote  $\bar{x}_c(n, k)$  as the output signal generated by a specific synthesis module

$$\bar{x}_c(n, k) = C(k)X_c(k) \cos\left[\frac{\pi k(2n+1)}{2N}\right].$$

(77)

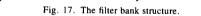

The time-recursive concept can be applied here to update  $\bar{x}_c(n, k)$  recursively. Use the result in Section III-A that IDCT and AIDST can be generated from each other recursively and denote  $\bar{x}_{as}(n, k)$  as the auxiliary inverse sine

transform generated by a specific synthesis filter. We can obtain the following recursive-generated relations for  $\bar{x}_c(n, k)$  and  $\bar{x}_{as}(n, k)$  as

$$\bar{x}_{c}(n+1, k) = C(k)X_{c}(k)\cos\left[\frac{\pi k [2(n+1)+1]}{2N}\right]$$

$$= \bar{x}_{c}(n, k)\cos\left(\frac{\pi k}{2N}\right) - \bar{x}_{as}(n, k)\sin\left(\frac{\pi k}{2N}\right)$$

(78)

and

$$\bar{x}_{as}(n + 1, k) = C(k)X_{c}(k) \sin\left[\frac{\pi k [2(n + 1) + 1]}{2N}\right]$$

$$\cdot \bar{x}_{as}(n, k) \cos\left(\frac{\pi k}{2N}\right) + \bar{x}_{c}(n, k)$$

$$\cdot \sin\left(\frac{\pi k}{2N}\right).$$

(79)

Fig. 18. The synthesis bank structure of the DCT.

Equations (78) and (79) suggest that the  $\bar{x}_c(n + 1, k)$  and  $\bar{x}_{as}(n, + 1, k)$  can be dually generated from the previous values  $\bar{x}_c(n, k)$  and  $\bar{x}_{as}(n, k)$  in a lattice form as shown in Fig. 18. Because the initial values for  $x_c(0, k)$  and  $x_{as}(0, k)$  are

$$\bar{x}_c(0, k) = X_c(k) \cos\left[\frac{\pi k}{2N}\right]$$

(80)

and

$$\bar{x}_{as}(0, k) = X_{as}(k) \sin\left[\frac{\pi k}{2N}\right]$$

(81)

this means that the  $x_c(n + 1, k)$  and  $x_{as}(n + 1, k)$  can be generated by sending a sequence with  $X_c(k)$  as the first element followed by N - 1 zeros into the input of the synthesis module. This is exactly the up sampling procedure required in the synthesis bank structure. The  $\bar{x}_{as}(n, k)$  output is reset every N clock cycles. The synthesis module diagram for the DCT is plotted in Fig. 18. The inverse transform is obtained by summing all the outputs of the synthesis modules.

### B. Synthesis Bank Structure of the DST and DHT

In this section, we apply the same approach mentioned in the previous section to the DST and DHT. The results are summarized as below. By using the dual generation concept, the operation of the synthesis module for the DST is

$$\bar{x}_{s}(n+1, k) = D(k)X_{s}(k) \sin\left[\frac{\pi k [2(n+1)+1]}{2N}\right]$$

$$= \bar{x}_{s}(n, k) \cos\left(\frac{\pi k}{2N}\right) + \bar{x}_{ac}(n, k) \sin\left(\frac{\pi k}{2N}\right)$$

(82)

and

$$\bar{x}_{ac}(n + 1, k) = D(k)X_s(k)\cos\left[\frac{\pi k[2(n + 1) + 1]}{2N}\right]$$

$$= \bar{x}_{ac}(n, k)\cos\left(\frac{\pi k}{2N}\right) - \bar{x}_s(n, k)$$

$$\cdot \sin\left(\frac{\pi k}{2N}\right). \tag{83}$$

Because D(k) and C(k) have the same values for k = 1, 2,  $\cdots$ , N - 1 and D(N) = C(0). Therefore, the structure of the synthesis modules for the DST are the same as that for the DCT except for k = N.

As for the DHT, the IDHT is defined as

$$x_{h}(n) = \sum_{k=0}^{N-1} X_{h}(k) \cos\left(\frac{2\pi kn}{N}\right)$$

$$= \sum_{k=0}^{N-1} X_{h}(k) \left[\cos\left(\frac{2\pi kn}{N}\right) + \sin\left(\frac{2\pi kn}{N}\right)\right]$$

$$n = 0, 1, \dots, N-1.$$

(84)

Again, we separate them into a combination of a DCT-like and a DST-like transforms as follows:

$$x_h(n) = x'_c(n) + x'_s(n).$$

(85)

The operation of the synthesis module for the DHT is generated from  $x'_{c}(n)$  and the  $x'_{s}(n)$  by the following relation

$$x'_{c}(n + 1, k) = x'_{c}(n, k) \cos\left(\frac{2\pi k}{N}\right)$$

$$- x'_{s}(n, k) \sin\left(\frac{2\pi k}{N}\right) \qquad (86)$$

and

$$x'_{s}(n + 1, k) = x'_{s}(n, k) \cos\left(\frac{2\pi k}{N}\right)$$

$$- x'_{c}(n, k) \sin\left(\frac{2\pi k}{N}\right). \quad (87)$$

To obtain the IDHT  $x_h(n)$  we must sum up both of the outputs of the synthesis modules. It is noted that the multiplier coefficients in the synthesis module for the DHT is different from that of the DCT and DST.

#### IX. CONCLUSIONS

In this paper, unified time-recursive algorithms and lattice structures that can be applied to the DCT, DST, DHT, and their inverse transforms, are considered. In fact, there are various forms of sin and cosine transform pairs (the DCTI/DSTI, DCTII/DSTII, DCTIII/DSTIII, DCTIV/ DSTIV, and complex lapped transform (CLT)) as mentioned in [22], [33]. They also have their time-recursive lattice realizations. The procedures to attain the lattice structures of different transforms are similar and the resulting SIPO lattice structures differ only in the multiplying coefficients and the input stage. All the transform pairs have their pre- and postlattice realizations that differ in that the input signals are added in the front and the end of the lattice respectively. The hardware complexity of the pre-lattice realizations and their postlattice counterparts depends on the definitions of the transforms and it cannot be readily determined which one is better. The number of multipliers in all the parallel lattice structures is a linear function of the transform size N and the latency is N clock cycles. Two methods, the SISO and double-lattice approaches, are developed to reduce the number of multipliers for the parallel lattice structures. The SISO approach can reduce 2N multipliers and the latency becomes 2N. The double-lattice approach can reduce N multipliers and the latency remains intact. From the discussion of the block processing, it is noted that the area-time complexity is efficient when the block size *m* is small, especially when m = 1. All the resulting parallel structures are modular. regular, and only locally connected. Further, there is no constraint on the transform size N. It is obvious that the design complexity of these structures is relatively low compared with other algorithms. The characteristics of these algorithms are suitable for processing series input data since the transformed data for sequential input can be obtained every clock cycle. Therefore, it is very attractive to VLSI implementations and high speed applications such as HDTV signal coding and transmission.

Since the orthogonal rotation is the major operation in the lattice, it is noted that such rotation can be easily implemented using coordinate rotation digital computer (CORDIC) [29], [30] which is known as an efficient method for the computation of orthogonal rotations and trigonometric functions.

#### ACKNOWLEDGMENT

The authors would like to thank the reviewers for their careful and detailed comments.

#### REFERENCES

[1] A. Rosenfeld and A. C. Kak, Digital Picture Processing, 2nd ed. New York: Academic, 1982.

- [2] N. Ahmed, T. Natarajan, and K. R. Rao, "Discrete cosine transform," IEEE Trans. Comput., vol. C-23, pp. 90-93, Jan. 1974.

- [3] R. J. Clark, "Relation between the Karhunen-Loeve and cosine transform," Proc. Inst. Elec. Eng., vol. 128, pt. F, no. 6, pp. 359-360. Nov. 1981.

- [4] A. K. Jain, "A fast Karhunen-Loeve transform for a class of stochastic process," IEEE Trans. Commun., vol. COM-24, pp. 1023-1029. 1976.

- R. Yip and K. R. Rao, "On the computation and effectiveness of discrete sine transform," *Comput. Elec. Eng.*, vol. 7, pp. 45–55, [5] 1980

- [6] R. N. Bracewell, "Discrete Hartley transform," J. Opt. Soc. Amer., vol. 73, pp. 1832-1835, Dec. 1983

- [7] H. S. Hou, "A fast recursive algorithm for computing the discrete cosine transform," IEEE Trans. Acoust., Speech, Signal Processing, vol. ASSP-35, pp. 1455-1461, Oct. 1987. R. N. Bracewell, "The fast Hartley transform," *Proc. IEEE*, vol.

- [8] 72, pp. 1010-1018, Aug. 1984.

- [9] B. D. Tseng and W. C. Miller, "On computing the discrete cosine transform," IEEE Trans. Comput., vol. C-27, pp. 966-968, July 1976

- [10] M. Vetterli and H. Nussbaumer, "Simple FFT and DCT algorithm with reduced number of operations," Signal Processing, vol. 6, no. 4, pp. 267-278, Aug. 1984.

- [11] M. Vetterli and A. Ligtenberg, "A discrete Fourier-cosine transform chip," IEEE J. Select. Areas Commun., vol. SAC-4, no. 1, pp. 49-61, Jan. 1986

- [12] H. W. Jones, D. N. Hein, and S. C. Knauer, "The Karhunen-Loeve, discrete cosine and related transform via the Hadmard transform, Proc. Inc. Telemeter Conf., Los Angeles, CA, Nov. 1978, pp. 87-98

- [13] M. J. Narashimha and A. M. Peterson, "On the computation of the discrete cosine transform," *IEEE Trans. Commun.*, vol. COM-26, pp. 934-936, June 1978.

- W. H. Chen, C. H. Smith, and S. C. Fralick, "A fast computational [14] algorithm for the discrete cosine transform," IEEE Trans. Commun., vol. COM-25, pp. 1004-1009, Sept. 1977.

- [15] B. G. Lee, "A new algorithm to compute the discrete cosine trans-form," *IEEE Trans. Acoust., Speech, Signal Processing*, vol. ASSP-32, pp. 1243-1245, Dec. 1984.

- [16] B. G. Kashef and A. Habibi, "Direct computation of higher order DCT coefficients from lower-order DCT coefficients," presented at the SPIE 28th Annu. Int. Tech. Symp., San Diego, CA, Aug. 19-24, 1984

- [17] M. H. Lee, "On computing 2-D systolic algorithm for discrete cosine transform," IEEE Trans. Circuits Syst., vol. 37, no. 10, pp. 1321-1323, Oct. 1990.

- [18] C. Chakrabarti and J. J'aJ'a, "Systolic architectures for the computation of the discrete Hartley and the discrete cosine transforms based on prime factor decomposition," IEEE Trans. Comput., vol. 39, no. 11, pp. 1359-1368, Nov. 1990.

- [19] H. S. Hou, "The fast Hartley transform algorithm," IEEE Trans. Comput., vol. C-36, no. 2, pp. 147-156, Feb. 1987.

- [20] Z. Wang, "Fast algorithms for the discrete W transform and for the discrete Fourier transform," IEEE Trans. Acoust., Speech, Signal Processing, vol. ASSP-32, Aug. 1984.

- [21] R. W. Owens and J. J'aJ'a, "A VLSI chip for the Winograd/prime factor algorithm to compute the discrete Fourier transform," IEEE Trans. Acoust., Speech, Signal Processing, vol. ASSP-34, pp. 979-989, Aug. 1986.

- [22] R. Yip and K. R. Rao, "On the shift property of DCT's and DST's," IEEE Trans. Acoust., Speech, Signal Processing, vol. ASSP-35, no. 3, pp. 404-406, Mar. 1987.

- [23] H. V. Sorenson et al., "On computing the discrete Hartley trans-form," IEEE Trans. Acoust., Speech, Signal Processing, vol. ASSP-33, no. 4, pp. 1231-1238, Oct. 1985.

- [24] S. B. Narayanan and K. M. M. Prabhu, "Fast Hartley transform pruning," IEEE Trans. Signal Processing, vol. 39, no. 1, pp. 230-233. Jan. 1991

- [25] W. Kou and J. W. Mark, "A new look at DCT-type transforms," IEEE Trans. Acoust., Speech, Signal Processing, vol. 37, no. 12, pp. 1899-1908, Dec. 1989.

- [26] N. I. Cho and S. U. Lee, "DCT algorithms for VLSI parallel implementations," IEEE Trans. Acoust., Speech, Signal Processing, vol. 38, no. 1, pp. 1899-1908, Dec. 1989

- [27] L. W. Chang and M. C. Wu, "A unified systolic array for discrete cosine and sine transforms," *IEEE Trans. Signal Processing*, vol. 39, no. 1, pp. 192-194, Jan. 1991.

#### LIU AND CHIU: UNIFIED PARALLEL LATTICE STRUCTURES

- [28] E. A. Jonckheere and C. Ma, "Split-radix fast Hartley transform in one and two dimensions," *IEEE Trans. Signal Processing*, vol. 39, no. 2, pp. 499-503, Feb. 1991.

- [29] N. Takagi, T. Asada, and S. Yajima, "Redundant CORDIC methods with a constant scale factor for sine and cosine computation," IEEE Trans. Comput., vol. 40, no. 9, pp. 989-995, Sept. 1991.

- [30] H. M. Ahmed, J. M. Delosme, and M. Morf, "Highly concurrent computing structures for matrix arithmetic and signal processing," IEEE Comput. Mag., vol. 15, no. 1, pp. 65-82, Jan. 1982. [31] A. V. Oppenheim and R. W. Schafer, Discrete-Time Signal Process-

- ing. Englewood Cliffs, NJ: Prentice-Hall, 1989. [32] S. A. White, "High-speed distributed-arithmetic realization of a second-order normal-form digital filter," *IEEE Trans. Circuits Syst.*, vol. 33, no. 10, pp. 1036-1038, Oct. 1986.

- [33] R. Young and N. Kingsbury, "Motion estimation using lapped transforms," in Proc. IEEE ICASSP, Mar. 1992, pp. III 261–264.

- [34] C. T. Chiu and K. J. R. Liu, "Real-time parallel and fully pipelined two-dimensional DCT lattice structures with application to HDTV systems, "*IEEE Trans. Circuits Syst. Video Technol.*, vol. 2, no. 1, pp. 25-37, Mar. 1992.

[35] C. T. Chiu, R. Kolagotla, K. J. R. Liu, and J. JaJa, "VLSI imple-

- mentation of real-time parallel DCT/DST lattice structure for video communications," in VLSI Signal Processing V, Yao et al., Eds. New York: IEEE Press, 1992, pp. 101-110.

K. J. Ray Liu (S'86-M'90) received the B.S. degree in electrical engineering from National Taiwan University in 1983, the M.S.E. degree in electrical engineering and computer science from the University of Michigan, Ann Arbor, in 1987, and the Ph.D. degree in electrical engineering from the University of California, Los Angeles, in 1990.

During 1983-1985, he served in the Signal Corps, Taiwan, as a Communications Officer. He then became a Teaching and Research Assistant at the University of Michigan and the University of California, Los Angeles. Since August 1990, he has been an Assistant Professor in the Department of Electrical Engineering and Systems Research Center, University of Maryland, College Park. His research interests include parallel processing algorithms and architectures for signal/image processing and communications, adaptive signal processing, spectral estimation, video signal processing, fault-tolerant computing in VLSI systems, design automation for DSP VLSI systems, and fast algorithms. He has published 50 papers in these areas.

Dr. Liu is a member of the VLSI Signal Processing Technical Committee, IEEE Signal Processing Society. He was awarded the President Re-search Partnership from the University of Michigan in 1987, and the University Fellowship and the Hortense Fishbaugh Memorial Scholarship from UCLA in 1987-1988 and 1989, respectively. He was also awarded the Outstanding Graduate Student Award in Science and Engineering from the Taiwanese-American Foundation. He is a member of ACM and SIAM.

Ching-Te Chiu (S'90-M'93) received the B.S. and M.S. degrees in electrical engineering from National Taiwan University, Taiwan, in 1986 and 1988, respectively, and the Ph.D. degree in elec-trical engineering from the University of Maryland, College Park, in 1992. She did research work as a summer research

student at Electronics Research Service Organization (ERSO), National Taiwan Institute of Technology in 1987. From 1989 to 1992, she was a Research Assistant in the Department of Elec-

trical Engineering at the University of Maryland, College Park. Her current research interests include signal processing, VLSI architectures and algorithms, image processing, and HDTV systems.