Open access • Journal Article • DOI:10.1109/JSSC.2011.2116490

### **Unipolar Organic Transistor Circuits Made Robust by Dual-Gate Technology**

— Source link < □</p>

Kris Myny, Monique J. Beenhakkers, N. A. J. M. van Aerle, Gerwin H. Gelinck ...+3 more authors

Institutions: Katholieke Universiteit Leuven

Published on: 17 Mar 2011 - IEEE Journal of Solid-state Circuits (Institute of Electrical and Electronics Engineers)

Topics: NAND gate, Inverter, Logic gate, Noise margin and Ring oscillator

#### Related papers:

- A 13.56-MHz RFID System Based on Organic Transponders

- A Fully Integrated \$\Delta \Sigma\$ ADC in Organic Thin-Film Transistor Technology on Flexible Plastic Foil

- · Dual-gate organic thin-film transistors

- Flexible active-matrix displays and shift registers based on solution-processed organic transistors.

- An 8-Bit, 40-Instructions-Per-Second Organic Microprocessor on Plastic Foil

# Unipolar Organic Transistor Circuits Made Robust by Dual-Gate Technology

Kris Myny, *Student Member, IEEE*, Monique J. Beenhakkers, Nick A. J. M. van Aerle, Gerwin H. Gelinck, Jan Genoe, *Member, IEEE*, Wim Dehaene, *Senior Member, IEEE*, and Paul Heremans

Abstract—Dual-gate organic transistor technology is used to increase the robustness of digital circuits as illustrated by higher inverter gains and noise margins. The additional gate in the technology functions as a  $V_{\rm T}$ -control gate. Both zero- $V_{\rm GS}$ -load and diode-load logic are investigated. The noise margin of zero- $V_{\rm GS}$ -load inverter increases from 1.15 V (single gate) to 2.8 V (dual gate) at 20 V supply voltage. Diode-load logic inverters show an improvement in noise margin from  $\sim\!0$  V to 0.7 V for single gate and dual gate inverters, respectively. These values can be increased significantly by optimizing the inverter topologies. As a result of this optimization, noise margins larger than 6 V for zero- $V_{\rm GS}$ -load logic and 1.4 V for diode-load logic are obtained. Functional 99-stage ring oscillators with 2.27  $\mu{\rm s}$  stage delays and 64 bit organic RFID transponder chips, operating at a data rate of 4.3 kb/s, have been manufactured.

Index Terms—Dual-gate, organic circuits, organic RFID, organic transistor.

#### I. INTRODUCTION

RESEARCH towards organic RFID tags is one of the drivers of organic electronics. In recent years, 64 bit organic RFID tags have been published with capacitive coupling [1] and inductive coupling at 13.56 MHz [2]–[4]. Recently, we reported a 128 bit organic transponder chip with basic anticollision protocol and Manchester encoding [2], [5]. In all these realizations, the most widespread technology is single- $V_{\rm T}$  p-type only. This technology has intrinsic limitations concerning integration of larger circuits, as a result of parameter variability [6]. The move towards an organic complementary technology [7], [8] is the most favorable route to obtain robust

Manuscript received February 25, 2010; revised December 01, 2010; accepted December 31, 2010. Date of publication March 17, 2011; date of current version April 22, 2011. This paper was approved by Associate Editor Ken Shepard.

- K. Myny is with imec, 3001 Leuven, Belgium. He is also with Katholieke Universiteit Leuven, 3001 Leuven, Belgium, and Katholieke Hogeschool Limburg, 3590 Diepenbeek, Belgium (e-mail: kris.myny@imec.be).

- M. J. Beenhakkers is with Polymer Vision, 5656 AE Eindhoven, The Netherlands

- N. A. J. M. van Aerle was with Polymer Vision. He is now with ASML, 5504 DR Veldhoven, The Netherlands.

- G. H. Gelinck is with Holst Centre/TNO, Hightech Campus 31, 5605 KN, Eindhoven, The Netherlands.

- J. Genoe is with imec, 3001 Leuven, Belgium. He is also with Katholieke Hogeschool Limburg, 3590 Diepenbeek, Belgium.

- W. Dehaene is with imec, 3001 Leuven, Belgium. He is also with Katholieke Universiteit Leuven, 3001 Leuven, Belgium.

- P. Heremans is with imec, 3001 Leuven, Belgium. He is also with Katholieke Universiteit Leuven, 3001 Leuven, Belgium.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2011.2116490

organic circuitry [9] and first 4 bit tags in complementary organic technology [7] have been made. This requires, however, matching of the n-type material in device performance. This matching has turned out to be difficult for close integration in complex circuits. Here, we present an alternative to improve the robustness of organic circuits [10]. It is based on p-type organic transistors equipped with a double gate [11]-[13]. The extra gate is used to vary the  $V_{\rm T}$ , which effectively leads to a dual- $V_{\rm T}$  p-type technology. The dual-gate transistor configuration allows to innovate the topology of logic gates. In this paper, we first discuss the logic families possible in unipolar organic electronics. Subsequently, dual-gate topologies are introduced and optimized topologies are selected. We show inverter topologies with substantially increased gain and noise margin [6]. Finally, we demonstrate a 64 bit organic RFID transponder chip based on these dual-gate organic thin-film transistors (OTFTs) for two different inverter topologies.

#### II. LOGIC FAMILIES WITH UNIPOLAR LOGIC

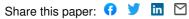

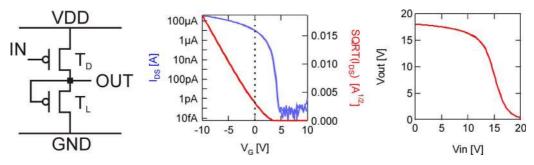

In p-type only organic electronics, inverters and NANDs are designed in zero- $V_{\rm GS}$ -load logic or diode-load logic. Both schemes are depicted in Figs. 1 and 2. Both inverters comprise a drive transistor, which is the pull-up transistor in p-type logic and a load transistor, i.e., the pull-down transistor.

#### A. Zero- $V_{GS}$ -Load Logic

In zero- $V_{\rm GS}$ -load configuration, the gate and source nodes are shorted and effectively the load transistor is a current-source with a constant  $V_{GS}$ -voltage of 0 V. As a consequence, this transistor needs to have a positive threshold voltage (depletion transistor), as shown in Fig. 1. The operation of the inverter can readily be understood as follows. For low  $V_{\rm IN}$ , the drive transistor is strongly on, in other words the channel resistance of this transistor in low, much lower than the channel resistance of the load transistor ( $V_{\rm GS}=0$  V). Therefore, the resistive divider between the load and drive transistors sets  $V_{\rm OUT}$  close to  $V_{\rm DD}$ . In the other case, when  $V_{\rm IN}$  is high, the drive transistor has a gate-source voltage close to 0 V. Therefore, the dimensions (W/L) of the load transistor are chosen significantly (e.g., 5 to 10 times) larger than those of the drive transistor. Now, the resistive divider between the load and drive transistor pulls  $V_{\rm OUT}$ close to 0 V. For these inverters, non-idealities are present, being the swing of  $V_{\text{OUT}}$  that is smaller than 0 to  $V_{\text{DD}}$ , caused by the leakage current of the drive and load transistors which are always "on". Another non-ideality is the asymmetrical trip point that is not at  $V_{\rm DD}/2$  caused by the equal threshold voltages of both drive and load transistors. A typical measured inverter is shown in Fig. 1. The single gate inverter in this work yields a

Fig. 1. (left) Schematics of zero- $V_{\rm GS}$ -load inverter with unipolar p-type logic. (middle)  $I_{\rm DS}$ - $V_{\rm GS}$  transfer characteristic of a depletion-mode, p-channel OTFT with positive threshold voltage. (right) Typical measured transfer characteristics of a zero- $V_{\rm GS}$ -load inverter.

Fig. 2. (left) Schematics of diode-load inverter with unipolar p-type logic. (middle)  $I_{\rm DS}$ - $V_{\rm GS}$  transfer characteristic of an enhancement-mode, p-channel OTFT with negative threshold voltage. (right) Typical measured transfer characteristics of a diode-load inverter.

noise margin of 1.15 V at a supply voltage of 20 V. Its gain is 3.90.

#### B. Diode-Load Logic

Fig. 2 shows the configuration of a diode-load inverter. The gate and drain nodes of the pull-down transistor are connected, resulting in a diode-connected transistor. This configuration is, in contrast to the zero- $V_{GS}$ -load configuration, compatible with enhancement-mode transistors [14] (Fig. 2) and mildly depletion-mode transistors [15]. This type of logic therefore has some more robustness against large threshold-voltage variations of the load transistor and it provides faster circuits [1]. The inverters yield lower gains than the zero- $V_{\rm GS}$ -load inverters, resulting in severely reduced noise margins, as indicated by the characteristics of a diode-load organic inverter of Fig. 2. The swing of  $V_{\rm OUT}$  in this logic is also smaller than 0 to  $V_{\rm DD}$ . In order to be able to integrate more logic gates in a circuit, the use of level-shifters has shown to be successful to improve the noise margin of diode-load inverters [1]. A level-shifter is an additional stage which requires a third voltage rail. This circuit results in a shift of the transfer characteristics of the inverter. This is testified by the demonstration of relatively large circuits with this configuration [16]. A major advantage of diode-load logic is an increased speed compared to zero- $V_{GS}$ -load logic. As a consequence of using a diode-connected transistor as load, this OTFT yields large pull-down currents leading to a decreased stage delay for diode-load gates versus zero- $V_{\rm GS}$ -load gates, in which the pull-down action is speed limiting.

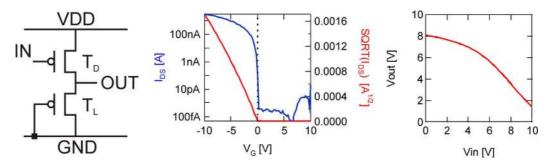

#### III. CIRCUITRY WITH DUAL-GATE OTFTS

So far, we have discussed organic unipolar circuitry with one threshold voltage. The availability of a second threshold voltage would be beneficial for the characteristics of building blocks for digital circuits, similar to the silicon n-MOS logic used in the 1980s. One option to obtain multiple threshold voltages is the addition of a second gate in the technology. The organic dual-gate TFT technology that is used in this work is described elsewhere [17], [18]. The organic insulator layers and the p-type pentacene semiconductor are processed from solution. The transistors have a typical channel length of 5  $\mu$ m and an average saturation mobility of 0.15 cm<sup>2</sup>/Vs. A cross section image of the layers and a typical measured dual-gate OTFT are shown in Fig. 3. The coupling to the channel of the second or back-gate is weaker than for the front-gate, therefore it is used as  $V_{\rm T}$ -control gate. By varying the back-gate bias between +30 V and -30 V, the transistor threshold voltage can be controlled, leading from depletion-mode to more enhancement-mode curves, in agreement with earlier publications [18], [19].

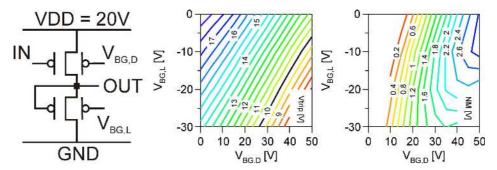

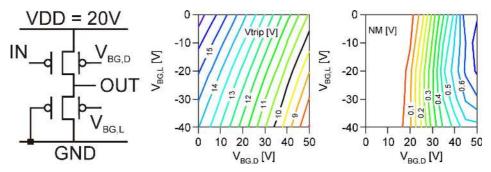

In this section, we investigate both architectures of inverters discussed previously for a technology where both the load and drive transistors have a back gate available. The electric schemes are depicted in Figs. 4 and 5. The  $V_{\rm T}$ -control gate is denoted with the subscript 'BG'. The ratio between the drive and load transistor for the diode-load logic is 10:1, however we have found that the zero- $V_{\rm GS}$ -load logic can be designed with a 1:1 ratio resulting in a significantly smaller chip area. Figs. 4 and 5 depict contour plots of noise margin and trip point when varying the  $V_{\rm T}$ -control gate voltage of the drive and load transistor for both inverter topologies. As can be seen, noise margins can exceed 2.8 V for zero- $V_{\rm GS}$ -load inverters and 0.7 V for diode-load inverters at  $V_{\rm DD}=20$  V. The trip point can be shifted towards  $V_{\rm DD}/2$  (i.e., 10 V) for both designs by appropriate  $V_{\rm T}$  control.

Fig. 3. Cross-section of the dual-gate OTFT technology (left) and a typical measured transfer characteristic of this OTFT when using the back-gate as  $V_{\rm T}$ -control gate (right). The channel width equals 140  $\mu$ m, the channel length 5  $\mu$ m.

Fig. 4. Architecture of a dual-gate zero- $V_{\rm GS}$ -load inverter (left). Contour plots of the trip point (middle) and the noise margin (right) determined from measured transfer curves of inverters when varying the back-gate voltage of the load and drive transistor and applying a supply voltage of 20 V.

Fig. 5. Architecture of a dual-gate diode-load inverter (left). Contour plots of the trip point (middle) and the noise margin (right) determined from measured transfer curves of inverters when varying the back-gate voltage of the load and drive transistor and applying a supply voltage of 20 V.

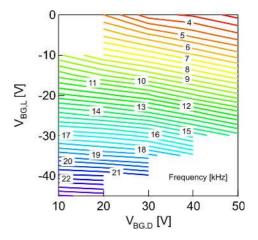

Next, besides the inverter topologies of Figs. 4 and 5, we have fabricated and measured 19-stage ring oscillators, designed using the dual-gate zero- $V_{\rm GS}$ -load inverter architecture with a 1:1 ratio. Fig. 6 shows the obtained frequency when varying back gate of the drive and load transistor. A frequency range between 3 kHz and 24 kHz has been obtained. The influence of the threshold voltage of the drive transistor is much weaker than the influence of the threshold voltage of the load transistor, which delivers the small pull-down current to discharge the input capacitance of the next stage. The variation of the back-gate is a viable route to increase the frequency of the dual-gate zero- $V_{\rm GS}$ -load circuits.

#### IV. ENHANCED DUAL-GATE ARCHITECTURE

One disadvantage of previous dual-gate configurations is that the threshold voltage of the load transistor changes dynamically with the output node, since this node is also the source-contact for the back gate transistor. The threshold voltage moves in opposite direction as required for high gains when the output node

Fig. 6. Contour plot of the frequency determined from measured curves of 19-stage ring oscillators using the dual-gate zero- $V_{\rm GS}$ -load architecture (Fig. 4) when varying the back-gate voltage of the load and drive transistor and applying a supply voltage of 20 V.

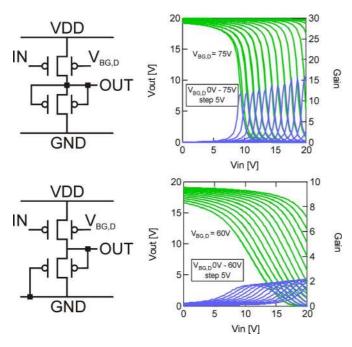

Fig. 7. Architecture of optimized inverter architectures in dual gate technology for (top left) zero- $V_{\rm GS}$ -load inverter and (bottom left) diode-load inverter. Transfer curves of these inverters are plotted for a supply voltage of 20 V, as a function of the voltage on the  $V_{\rm T}$ -control gate of the drive transistor (right).

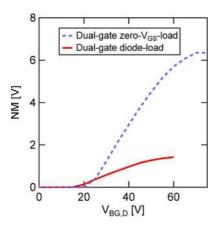

Fig. 8. Extracted noise margin for both zero- $V_{\rm GS}$ -load and diode-load inverter logic as function of the back-gate voltage of the drive transistor.

varies. In other words, the load transistor is made dynamically weaker when it should pull the output node down. Therefore, we have found an optimized architecture. Connecting the back-gate of the load with the output node delivers a topology that leads to increased noise margin and gain (see Fig. 7). The transfer curves of zero- $V_{\rm GS}$ -load and diode-load inverters using this optimized topology are depicted in Fig. 7.

De Vusser *et al.* [6] showed that, for zero- $V_{\rm GS}$ -load logic, a linear increase in noise margin is directly proportional to a  $V_{\rm T}$ -difference between load and drive transistor. In our topology, this  $V_{\rm T}$ -difference is obtained by a back-gate voltage difference between load and drive TFT. Fig. 3 depicts that, in our device configuration, the threshold voltage shifts with about 35% of the applied back-gate voltage. This yields an increase in noise margin of 16% of the applied back-gate voltage, as can be seen in Fig. 8. For the diode-load logic, a

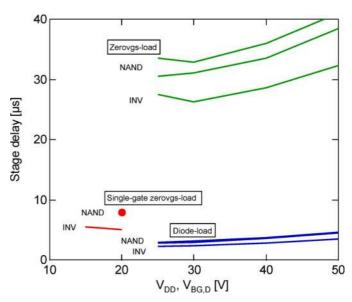

Fig. 9. The stage delay is plotted as a function of the  $V_{\rm T}$ -control voltage of the drive transistor ( $V_{\rm BG,D}$ ) for optimized zero- $V_{\rm GS}$ -load and diode-load inverters for a supply voltage of 20 V. The stage delay of a single-gate zero- $V_{\rm GS}$ -load inverter is shown for reference. This stage delay is plotted as a function of the power supply voltage ( $V_{\rm DD}$ ).

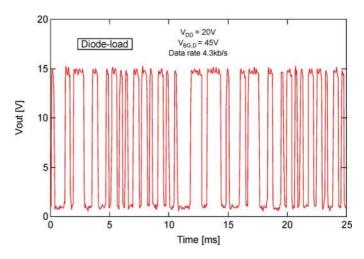

Fig. 10. The output signal of a 64 bit organic RFID transponder chip with optimized diode-load configuration for a supply voltage of 20 V and a back-gate voltage of 45 V. The corresponding data rate is 4.3 kb/s.

much smaller increase in noise margin (4%) is obtained with the change in the back-gate voltage. The  $V_{\rm T}$ -control gate of the drive transistor can be used to move the trip point towards  $V_{\rm DD}/2$  (see Fig. 7). At this point, in zero- $V_{\rm GS}$ -load inverters, the gain exceeds 11 and the noise margin is larger than 6 V at  $V_{\rm DD}=20$  V. Importantly, the typically low gain of diode-load inverters increases to 2.

In order to demonstrate that organic p-type only dual-gate technology can obtain a high integration density, we made 99-stage dual-gate ring oscillators with zero- $V_{\rm GS}$ -load and diode-load architectures. In Fig. 9, we show the extracted stage delays of NAND-gates and inverters, using the topologies of Fig. 7, and compare them to reference single-gate zero- $V_{\rm GS}$ -load gates fabricated on the same foil. The fastest family is the optimized diode-load topology, with a stage delay of 2.27  $\mu$ s. The optimized zero- $V_{\rm GS}$ -load topology is an order

Fig. 11. The output signal of a 64 bit organic RFID transponder chip with optimized zero- $V_{\rm GS}$ -load configuration for a supply voltage of 20 V and a back-gate voltage of 30 V. The corresponding data rate is 522 b/s.

of magnitude slower ( $\tau_{\rm stage} = 26~\mu s$ ), due to limited pull-down current and the high parasitic output-capacitance.

## V. ORGANIC RFID TRANSPONDER CHIP WITH ENHANCED DUAL-GATE ARCHITECTURE

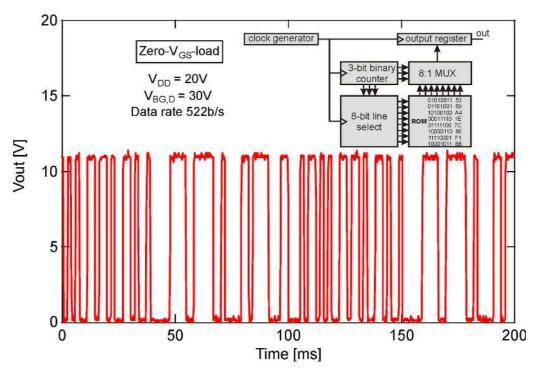

Next, we fabricated 64 bit RFID transponder chips similar to earlier designs [2]. To secure accurate clocking, we increased the size of the ring oscillator that generates the clock from 19 to 33 stages. The inset of Fig. 11 shows the digital schematic of the RFID transponder chip. The ring oscillator generates the clock signal when powered. This clock signal is used to clock the output register, the 3-bit binary counter and the 8-bit line select. The 8-bit line select has an internal 3-bit binary counter and a 3-to-8 decoder. This block selects a row of 8 bits in the code. The 3-bit binary counter drives the 8:1 multiplexer, selecting a column of 8 bits in the code matrix. The data bit at the crossing of the active row and column, is transported via an 8:1 multiplexer to the output register, which sends out this bit on the rising edge of the clock. The 3 bits of the 3-bit binary counter are also used in the 8-bit line select block for selecting a new row after all 8 bits in a row are transmitted. The design is made using only inverters and NAND-gates. For the optimized diode-load logic, the ratio between drive and load transistor is 10:1 leading to a transponder chip area of 74.48 mm<sup>2</sup>. Fig. 10 shows the output signal of the chip designed in optimized diode-load topology for  $V_{\rm DD}=20~{\rm V}$  and  $V_{\rm BG,D}=45~{\rm V}$ . The data rate is 4.3 kb/s, more than twice the fastest single gate transponder chips shown in [2] and [5]. We verified on three different wafers that some chips start operating at  $V_{\mathrm{DD}}$  as low as 10 V and all chips work at 15 V.

The 64 bit transponder chip in optimized zero- $V_{\rm GS}$ -load topology is only 45.38 mm<sup>2</sup> in size, thanks to the 1:1 ratio used

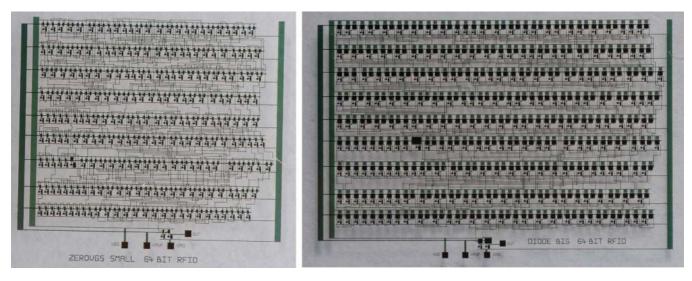

in this logic. In Fig. 11, the output is shown for  $V_{\rm DD}=20~{\rm V}$  and  $V_{\rm BG,D}=30~{\rm V}$ . Also this transponder chip has been measured on three different wafers. All measured transponder chips are operational at  $V_{\rm DD}=10~{\rm V}$ . The data rate at  $V_{\rm DD}=20~{\rm V}$  is 522 b/s. These findings are fully in line with the fact that the zero- $V_{\rm GS}$  topology has higher noise margin but larger stage delay than the diode-load topology. Fig. 12 shows a photograph of both 64 bit transponder chips.

For comparison, a 64 bit transponder chip having single-gate zero- $V_{\rm GS}$ -load logic has also been fabricated. The onset voltage, more precisely the minimal supply voltage at which the transponder is functional, on the three wafers differs between 20 V and 26 V. These onset voltages for power supply are comparable to the second generation transponder chips published by Myny *et al.* [2], [5]. As mentioned earlier, the dual-gate technology allows to lower the supply voltage, even to 10 V, which is the lowest value reported to-date for 64 bit transponder chips.

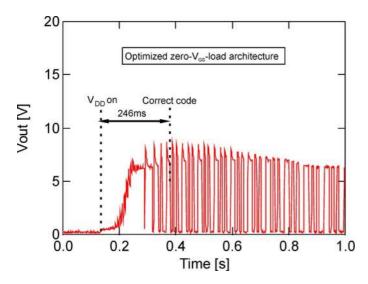

The back-gate voltages of the drive transistors are relatively high, 30 to 45 V. In an organic RFID transponder, such high voltage cannot be generated by a rectifier. However, it can be generated by charge pumps, provided that the required current is limited. To verify whether that last assumption is realistic, we have operated the chips with a 1-nA current compliance for the voltage supply of the back gate of the driver transistor. All chips were fully operational after a delay to charge all back gates. This delay was about 2.09 s for the diode-load configuration and only 246 ms for the zero- $V_{\rm GS}$ -load configuration. The output signal measured in latter circuit is plotted in Fig. 13. The difference in delay time is due to the fact that the drive transistor is  $10 \times 10^{-10}$  larger for the diode-load (ratioed) than the zero- $V_{\rm GS}$ -load configuration. We conclude that charge pumps are a viable route

Fig. 12. Photograph of the 64 bit organic RFID transponder chip designed with optimized zero- $V_{\rm GS}$ -load configuration (left) and optimized diode-load configuration (right).

Fig. 13. The output signal of an 8 bit organic RFID transponder chip with optimized zero- $V_{\rm GS}$ -load configuration for a supply voltage of 20 V and a back-gate voltage being charged towards 50 V at a current compliance of 1 nA.

to charge the back gates of the logic blocks of the proposed dual- $V_{\rm T}$  technology. A better solution to enable lower back-gate voltage levels can be found in technology improvements targeting a higher oxide capacitance of the back-gate dielectric. This can be achieved by means of e.g., a thinner back-gate dielectric. A drawback of this solution is a limited performance in terms of stage delay of logic gates due to an increased output capacitor for the enhanced dual-gate architecture.

#### VI. CONCLUSION

In this work we have demonstrated that a dual-gate OTFT technology is a realistic option to increase the robustness of digital building blocks for larger integration into circuitry. Therefore, dual-gate zero- $V_{\rm GS}$ -load and diode-load logic are investigated. For both topologies, noise margins and trip points could be improved when varying the back-gate voltage for the drive and load transistor. Next, an optimized design for

both topologies is found. The new design is used to integrate 99-stage ring oscillators, to determine stage delays, and in 64 bit organic RFID transponder chips, yielding data rates of 4.3 kb/s. This is, to our knowledge, the first integration of a dual-gate OTFT technology in complex digital circuits.

#### ACKNOWLEDGMENT

This work was performed in a collaboration between IMEC and TNO in the frame of the Holst Centre.

#### REFERENCES

- [1] E. Cantatore, T. C. T. Geuns, G. H. Gelinck, E. van Veenendaal, A. F. A. Gruijthuijsen, L. Schrijnemakers, S. Drews, and D. M. de Leeuw, "A 13.56-MHz RFID system based on organic transponders," *IEEE J. Solid-State Circuits*, vol. 42, no. 1, pp. 84–92, Jan. 2007.

- [2] K. Myny, S. Steudel, P. Vicca, M. J. Beenhakkers, N. A. J. M. van Aerle, G. H. Gelinck, J. Genoe, W. Dehaene, and P. Heremans, "Plastic circuits and tags for 13.56 MHz radio-frequency communication," *Solid State Electron.*, vol. 53, no. 12, pp. 1220–1226, 2009.

- [3] K. Myny, S. Van Winckel, S. Steudel, P. Vicca, S. De Jonge, M. J. Beenhakkers, C. W. Sele, N. A. J. M. van Aerle, G. H. Gelinck, J. Genoe, and P. Heremans, "An inductively-coupled 64b organic RFID tag operating at 13.56 MHz with a data rate of 787 b/s," in *IEEE ISSCC Dig. Tech. Papers*, 2008, pp. 290–291.

- [4] A. Ullmann, M. Böhm, J. Krumm, and W. Fix, "Polymer multi-bit RFID transponder," in *Int. Conf. Organic Electronics (ICOE)* 2007, Eindhoven, The Netherlands, Jun. 4–7, 2007, abstract 53.

- [5] K. Myny, M. J. Beenhakkers, N. A. J. M. van Aerle, G. H. Gelinck, J. Genoe, W. Dehaene, and P. Heremans, "A 128b organic RFID transponder chip, including Manchester encoding and ALOHA anticollision protocol, operating with a data rate of 1529 b/s," in *IEEE ISSCC Dig. Tech. Papers*, 2009, pp. 206–207.

- [6] S. De Vusser, J. Genoe, and P. Heremans, "Influence of transistor parameters on the noise margin of organic digital circuits," *IEEE Trans. Electron Devices*, vol. ED-53, pp. 601–610, 2006.

- [7] R. Blache, J. Krumm, and W. Fix, "Organic CMOS circuits for RFID applications," in *IEEE ISSCC Dig. Tech. Papers*, 2009, pp. 208–209.

- [8] K. Ishida, N. Masunaga, Z. Zhou, T. Yasufuku, T. Sekitani, U. Zschieschang, H. Klauk, M. Takamiya, T. Someya, and T. Sakurai, "A stretchable EMI measurement sheet with 8x8 coil array, 2 V organic CMOS decoder, and -70 dBm EMI detection circuits in 0.18 μm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, 2009, pp. 472–473.

- [9] D. Bode, C. Rolin, S. Schols, M. Debucquoy, S. Steudel, G. H. Gelinck, J. Genoe, and P. Heremans, "Noise-margin analysis for organic thin-film complementary technology," *IEEE Trans. Electron Devices*, vol. 57, pp. 201–208, 2010.

- [10] K. Myny, M. J. Beenhakkers, N. A. J. M. van Aerle, G. H. Gelinck, J. Genoe, W. Dehaene, and P. Heremans, "Robust digital design in organic electronics by dual-gate technology," in *IEEE ISSCC Dig. Tech. Papers*, 2010, pp. 140–141.

- [11] J. B. Koo, C. B. Koo, C. H. Ku, J. W. Lim, and S. H. Kim, "Novel or-ganic inverters with dual-gate pentacene thin-film transistor," *Organic Electronics*, vol. 8, pp. 552–558, 2007.

- [12] M. Spijkman, E. C. P. Smits, P. W. M. Blom, D. M. de Leeuw, Y. B. S. Côme, S. Setayesh, and E. Cantatore, "Increasing the noise margin in organic circuits using dual gate field-effect transistors," *Appl. Phys. Lett.*, vol. 92, no. 143304, 2008.

- [13] M. Takamiya, T. Sekitani, Y. Kato, H. Kawaguchi, T. Someya, and T. Sakurai, "An organic FET SRAM for Braille sheet display with back gate to increase static noise margin," in *IEEE ISSCC Dig. Tech. Papers*, 2006, pp. 276–277.

- [14] H. Klauk, Y.-Y. Lin, D. J. Gundlach, and T. N. Jackson, "Pentacene thin film transistors and inverter circuits," in *Int. Electron Devices Meeting (IEDM) Tech. Dig.*, 1997, pp. 539–542.

- [15] H. Sirringhaus, T. Kawase, R. H. Friend, T. Shimoda, M. Inbasekaran, W. Wu, and E. P. Woo, "High-resolution inkjet printing of all-polymer transistor circuits," *Science*, vol. 290, no. 5499, pp. 2123–2126, 2000.

- [16] G. H. Gelinck, H. E. A. Huitema, E. van Veenendaal, E. Cantatore, L. Schrijnemakers, J. B. P. H. van der Putten, T. C. T. Geuns, M. Beenhakkers, J. B. Giesbers, B. H. Huisman, E. J. Meijer, E. M. Benito, F. J. Touwslager, A. W. Marsman, B. J. E. van Rens, and D. M. de Leeuw, "Flexible active-matrix displays and shift registers based on solution-processed organic transistors," *Nat. Mater.*, vol. 3, pp. 106–110, Feb. 2004

- [17] G. H. Gelinck, H. E. A. Huitema, M. van Mil, E. van Veenendaal, P. J. G. van Lieshout, F. Touwslager, S. F. Party, S. Sohn, T. H. Whitesides, and M. D. McCreary, "A rollable, organic QVGA display with field-shielded pixel architecture," *J. Soc. Information Display (SID)*, vol. 14, pp. 113–118, 2006.

- [18] G. H. Gelinck, E. van Veenendaal, and R. Coehoorn, "Dual-gate or-ganic thin-film transistors," Appl. Phys. Lett., vol. 87, p. 073508, 2005.

- [19] S. Iba, T. Sekitani, Y. Kato, T. Someya, H. Kawaguchi, M. Takamiya, T. Sakurai, and S. Takagi, "Control of threshold voltage of organic field-effect transistors with double-gate structures," *Appl. Phys. Lett.*, vol. 87, p. 023509, 2005.

Vision BV.

Monique J. Beenhakkers was born in The Hague, The Netherlands, in 1964. After her education in electronics engineering, she joined Philips Research in Eindhoven in 1987. Over the years she gained vast experience in thin film processing and technology for many projects related to semiconductors. From the start of Polymer Vision in the Philips Technology Incubator in 2003 she was involved in the development of organic TFT technology on thin plastic foils with the goal to produce rollable displays. Currently, she is part of the technology R&D team of Polymer

**Nick A. J. M. van Aerle** graduated in physical chemistry from the University of Nijmegen, The Netherlands, in 1985 and received the Ph.D. degree in polymer physics in 1989 from the Eindhoven University of Technology, The Netherlands.

From 1989 until 2006 he worked in different product divisions of Philips Electronics in research and development functions varying from Research Scientist to Development Manager. From 2007 until 2009 he managed the Technology R&D team within Polymer Vision Ltd., a Philips spin-out, focusing on

the development of rollable displays for mobile applications based on polymer electronics. In 2010 he joined ASML to support the development of the next generation lithography manufacturing equipment based on extreme ultraviolet light. He has authored and co-authored over 35 papers international journals and conference reports and over 15 patent applications.

Gerwin H. Gelinck After receiving his Ph.D., he joined Philips Research as a Senior Scientist in 1998 where he started working on polymer and organic transistors and their use in integrated circuits, displays, and memories. In 2002 he was co-founder of Polymer Vision. From 2002 to 2006 he was Chief Scientist of Polymer Vision. Since 2007 he has been Program Manager of Organic and Oxide Circuitry at the Holst Centre, a joint research initiative of TNO

Kris Myny (S'08) was born in Hasselt, Belgium, on July 26, 1980. He received the Master degree from the Katholieke Hogeschool Limburg, Diepenbeek, Belgium, in 2002. He joined imec, Leuven, Belgium, in 2004 as a member of the Polymer and Molecular Electronics group. In 2008, he started his Ph.D. on the design of organic circuits.

His main research interests are the design, fabrication and optimization of digital organic circuits for, among others, organic RFID tags, and AMOLED backplanes.

**Jan Genoe** (S'87–M'02) was born in Leuven, Belgium, on May 19, 1965. He received the M.S. degree in electrical engineering and the Ph.D. degree from the Katholieke Universiteit Leuven, in 1988 and 1994, respectively.

Afterward, he joined the Grenoble High Magnetic Field Laboratory as a Human Capital and Mobility Fellow of the European Community. In 1997, he became a Lecturer at the Katholieke Hogeschool Limburg (KHLim) in Diepenbeek, Belgium. Since 2003, he is both Professor at the KHLim and head of the

Polymer and Molecular Electronics (PME) group of imec. His current research interests are organic and oxide transistors and circuits as well as organic photovoltaics. He is the author and coauthor of about 90 papers in refereed journals. Jan Genoe is a member of the IEEE.

Wim Dehaene (S'89–M'97–SM'04) was born in Nijmegen, The Netherlands, in 1967. He received the M.Sc. degree in electrical and mechanical engineering in 1991 from the Katholieke Universiteit Leuven. In November 1996 he received the Ph.D. degree also from the Katholieke Universiteit Leuven. His thesis was entitled "CMOS Integrated Circuits for Analog Signal Processing in Hard Disk Systems."

After receiving the M.Sc. degree, he was a research assistant at the ESAT-MICAS Laboratory of

the Katholieke Universiteit Leuven. His research involved the design of novel CMOS building blocks for hard disk systems. The research was first sponsored by the IWONL (Belgian Institute for Science and Research in Industry and agriculture) and later by the IWT (the Flemish institute for Scientific Research in the Industry). In November 1996, he joined Alcatel Microelectronics, Belgium, where he was a senior project leader for the feasibility, design and development of mixed mode Systems on Chip. The application domains were telephony, xDSL and high speed wireless LAN. In July 2002, he joined the staff of the ESAT-MICAS Laboratory of the Katholieke Universiteit Leuven where he is now a full Professor. His research domain is circuit-level design of digital circuits. The current focus is on ultra-low-power signal processing and memories in advanced CMOS technologies. Part of this research is performed in cooperation with imec, Belgium, where he is also a part-time principal scientist. Dr. Dehaene teaches several classes on electrical engineering and digital circuit and system design.

**Paul Heremans** received the Ph.D. degree in electrical engineering in 1990 from the University of Leuven, Belgium, on hot-carrier degradation of MOS transistors.

He then joined the opto-electronics group of imec, where he worked on optical interchip interconnects, and on high-efficiency III-V thin-film surface-textured light-emitting diodes. His current research interest is oxide and organic electronics, including circuits, backplanes and memories, as well as organic photovoltaics. He is an IMEC Fellow, Director of

IMEC's Large Area Electronics Department and part-time Professor at the Electrical Engineering Department of the University of Leuven.