#### Universal Utility Interface for Plug-in Hybrid Electric Vehicles with Vehicle-to-Grid Functionality

### A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

$\mathbf{B}\mathbf{Y}$

Nathan David Weise

#### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy

Advisor: Ned Mohan

August, 2011

© Nathan David Weise 2011 ALL RIGHTS RESERVED

## Acknowledgements

It is my honor and distinct pleasure to thank the many people who have guided me through my graduate schooling. I would like to express my sincere gratitude to my advisor, Professor Ned Mohan, for giving me the opportunity to work in the area of power electronics, for guiding me through the research topics, and finally, for believing in me. I feel honored to be a student of Professor Mohan's.

I would like thank my committe members, Professor Bruce Wollenberg, Professor William Robbins, and Professor Willard Miller.

I gratefully acknowledge the financial support from Institute of Renewable Energy and Environment, University of Minnesota.

Special thanks to Dr. Hariharan Krishnaswami for all of advice, ideas, and guidance, when I was just getting started. Thanks to Dr. Krushna K. Mohapatra for all the guidance during my initial stages of research. Thanks to Apurva, Kaushik, Gysler, Rashmi, Ranjan for the various discussions, debates, collaboration, ideas, and support.

I would like to thank my parents who have believed in me from the start and provided unfailing love and support.

# Dedication

This thesis is dedicated to my parents, Nancy and Jim, my love Katelin, my stepmother Ruth, my sisters, Caitlyn and Ashley, my Grandparents Grandma Weise, Grandpa Weise, and Grandma Keil, my aunts, uncles, cousins, and the rest of my family and friends. I would have never accomplished what I have without the huge support system of family and friends. I am blessed to have them and for that I am eternally grateful.

#### Abstract

Utility transmission lines are under-utilized during the night. Charging Plug-in Hybrid Electric Vehicles during the night and redistributing the power stored in the batteries utilizes the transmission lines more efficiently and is the motivation for this thesis. In an example scenario, a vehicle is fully charged at home during the night, and is driven to work in the morning. The vehicle is plugged in at work and continues to charge. Under peak power demand the grid can command some power from these vehicles, relieving stress on the utility. This thesis develops an in-vehicle interface to achieve this functionality.

A novel topology is developed for an all-in-one system for electric vehicles. The system is a bi-directional battery charger when plugged into single or three-phase, and doubles as the motor inverter when the vehicle is driven. The novel topology allows to source or sink power from the grid. A control scheme was developed for single-phase and three-phase inputs and simulation results are presented. A prototype of the topology is developed. Results from the prototype are compared against the simulation results and theory. Different modulation strategies are presented and compared.

# Contents

| A        | ckno  | wledgements                         | i    |

|----------|-------|-------------------------------------|------|

| D        | edica | tion                                | ii   |

| A        | bstra | let                                 | iii  |

| Li       | st of | Tables                              | vii  |

| Li       | st of | Figures                             | viii |

| 1        | Intr  | roduction                           | 1    |

|          | 1.1   | State of the Art                    | 1    |

|          | 1.2   | Proposed Converter                  | 5    |

|          | 1.3   | Motivation and Scope                | 6    |

|          | 1.4   | Contributions                       | 6    |

|          | 1.5   | Organization                        | 6    |

|          | 1.6   | Conclusion                          | 7    |

| <b>2</b> | Sing  | gle Phase Power and Voltage Control | 8    |

|          | 2.1   | Analysis                            | 9    |

|          |       | 2.1.1 Power Controller              | 11   |

|          |       | 2.1.2 Power Controller Redesign     | 15   |

|          |       | 2.1.3 Steady State Analysis         | 17   |

|          | 2.2   | Power Plant Error                   | 20   |

|          | 2.3   | Voltage Controller Design           | 21   |

|   |                | 2.3.1  | Voltage Controller Redesigned                    | 23 |

|---|----------------|--------|--------------------------------------------------|----|

|   |                | 2.3.2  | Bidirectional Power Flow                         | 25 |

|   | 2.4            | Concl  | usion                                            | 26 |

| 3 | Pov            | ver an | d Voltage Control with Three Phase Input         | 28 |

|   | 3.1            | Analy  | <i>r</i> sis                                     | 29 |

|   |                | 3.1.1  | Modelling Error                                  | 34 |

|   |                | 3.1.2  | Power Controller Design                          | 34 |

|   |                | 3.1.3  | Balancing Currents and Reducing Harmonics        | 38 |

|   |                | 3.1.4  | Voltage Control                                  | 42 |

|   |                | 3.1.5  | Bidirectional Power Flow                         | 44 |

|   | 3.2            | Concl  | usion                                            | 47 |

| 4 | $\mathbf{Sin}$ | gle-Ph | ase Modulation using Dual Active Bridge Analysis | 49 |

|   | 4.1            | Analy  | <i>v</i> sis                                     | 49 |

|   |                | 4.1.1  | DC - DC Dual Active Bridge Analysis              | 50 |

|   |                | 4.1.2  | AC - DC Dual Active Bridge Analysis              | 53 |

|   | 4.2            | Bidire | ectional Power Flow                              | 64 |

|   | 4.3            | Concl  | usion                                            | 66 |

| 5 | $\mathbf{Thr}$ | ree-Ph | ase Modulation using Dual Active Bridge Analysis | 67 |

|   | 5.1            | Analy  | <sup>7</sup> sis                                 | 69 |

|   |                | 5.1.1  | First Third Cycle Analysis                       | 69 |

|   |                | 5.1.2  | Second Third of Period                           | 72 |

|   |                | 5.1.3  | Third Third of Cycle                             | 73 |

|   | 5.2            | Virtua | al to Real Currents                              | 75 |

|   |                | 5.2.1  | Average Power                                    | 77 |

|   |                | 5.2.2  | Utilization Factor                               | 78 |

|   |                | 5.2.3  | RMS Ripple Current                               | 80 |

|   | 5.3            | Simul  | ation                                            | 81 |

|   | 5.4            | Bidire | ectional Power Flow                              | 83 |

|   | 5.5            | Concl  | usion                                            | 85 |

| 6 | Haı   | dware Results for Single Phase Input         | 87  |

|---|-------|----------------------------------------------|-----|

|   | 6.1   | Power Board                                  | 87  |

|   | 6.2   | Single Phase Experimental Results            | 88  |

|   |       | 6.2.1 Experiment                             | 88  |

| 7 | Haı   | dware Results for Three Phase Input          | 92  |

|   | 7.1   | Three Phase Experimental Results             | 92  |

|   | 7.2   | Experiment                                   | 93  |

|   | 7.3   | Bidirectional Power Flow                     | 97  |

| 8 | Cor   | nclusion                                     | 100 |

|   | 8.1   | Single Phase Control                         | 100 |

|   | 8.2   | Three Phase Control                          | 101 |

|   | 8.3   | Single Phase DAB Modulation Strategy         | 101 |

|   | 8.4   | Three Phase DAB Modulation Strategy          | 101 |

|   | 8.5   | Hardware                                     | 102 |

|   | 8.6   | Future Work                                  | 102 |

| R | efere | nces                                         | 104 |

| A | ppe   | ndix A. Protection Module                    | 111 |

| A | ppe   | ndix B. Single Phase Matrix Converter Module | 114 |

| A | ppe   | ndix C. H-Bridge Module                      | 121 |

| A | ppe   | ndix D. Three Phase Matrix Converter Module  | 127 |

| A | ppe   | ndix E. H-Bridge Module                      | 181 |

# List of Tables

| 2.1 | Control Design Variables            | 13 |

|-----|-------------------------------------|----|

| 2.2 | Controller Gains                    | 13 |

| 2.3 | Controller Gains                    | 16 |

| 2.4 | Voltage Control Design Variables    | 22 |

| 2.5 | Voltage Control Loop Parameters     | 23 |

| 2.6 | Voltage Control Loop Parameters     | 24 |

| 3.1 | Modulation Values                   | 32 |

| 3.2 | Power Control Loop Design Variables | 36 |

| 3.3 | Voltage Control Loop Values         | 43 |

| 3.4 | Voltage Controller Gains            | 43 |

| 4.1 | Simulation Parameters               | 53 |

| 4.2 | Calculated Values                   | 53 |

| 4.3 | Simulation Parameters               | 57 |

| 4.4 | Simulation Results                  | 57 |

| 4.5 | Simulation Results                  | 64 |

| 5.1 | Simulation Values                   | 81 |

| 6.1 | Experimental Values                 | 89 |

| 7.1 | Experimental Values                 | 94 |

# List of Figures

| 1.1  | Grid Tied Inverter                                 | 2  |

|------|----------------------------------------------------|----|

| 1.2  | Grid Tied Inverter back to back Dual Active Bridge | 3  |

| 1.3  | Isolated Current Link AC to DC Converter           | 4  |

| 1.4  | Isolated Resonant Link Converter                   | 4  |

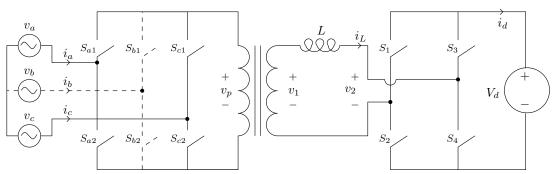

| 1.5  | Proposed Topology                                  | 5  |

| 2.1  | Single Phase Topology                              | 8  |

| 2.2  | Switches                                           | 9  |

| 2.3  | Matrix Converter Output                            | 10 |

| 2.4  | Bridge Outputs                                     | 11 |

| 2.5  | Actual System                                      | 12 |

| 2.6  | Linearized Control Design                          | 13 |

| 2.7  | Power Command                                      | 14 |

| 2.8  | Input Currents                                     | 15 |

| 2.9  | Harmonic Analysis                                  | 15 |

| 2.10 | Power Step Command                                 | 16 |

| 2.11 | Power Step Command                                 | 17 |

| 2.12 | Harmonic Analysis                                  | 17 |

| 2.13 | Simplified Voltage Circuit                         | 18 |

| 2.14 | Steady State Voltage                               | 19 |

| 2.15 | Power Error                                        | 21 |

| 2.16 | Voltage Control Loop                               | 21 |

| 2.17 | Output Voltage                                     | 23 |

| 2.18 | Input Current Spectrum                             | 24 |

| 2.19 | Voltage Control Loop                               | 24 |

|      |                                                    |    |

| 2.20 | Output Voltage                        | 25 |

|------|---------------------------------------|----|

| 2.21 | Input Current Frequency Spectrum      | 26 |

| 2.22 | Bidirectional Simulation Topology     | 26 |

| 2.23 | Bidirectional Power Flow              | 27 |

| 2.24 | Current Harmonics                     | 27 |

| 3.1  | Three Phase Topology                  | 28 |

| 3.2  | Duty Ratios                           | 31 |

| 3.3  | PWM Generation                        | 31 |

| 3.4  | Virtual DC Link                       | 32 |

| 3.5  | Quasi Square Wave                     | 33 |

| 3.6  | Phase Shift Voltage Waveforms         | 34 |

| 3.7  | Modelling Error                       | 35 |

| 3.8  | Three Phase Power Controller          | 35 |

| 3.9  | 3kW Power Command                     | 36 |

| 3.10 | Average Currents                      | 37 |

| 3.11 | Switch Currents                       | 37 |

| 3.12 | Current Harmonics                     | 38 |

| 3.13 | Voltage Six Sectors                   | 39 |

| 3.14 | Input Current Sectors                 | 39 |

| 3.15 | Average Three Phase Currents          | 40 |

| 3.16 | Switch Currents                       | 41 |

| 3.17 | Input Current Harmonics               | 41 |

| 3.18 | Three Phase Voltage Control Loop      | 42 |

| 3.19 | Capacitor Voltage                     | 44 |

| 3.20 | Filtered Currents for 10kW Load       | 44 |

| 3.21 | Current Spectrum for 10kW Load        | 45 |

| 3.22 | Bidirectional System Simulation       | 45 |

| 3.23 | Input Voltage and Filtered Current    | 46 |

| 3.24 | Harmonic Content                      | 46 |

| 3.25 | Power Step Command from -10kW to 10kW | 47 |

| 4.1  | DC-DC Dual Active Bridge              | 49 |

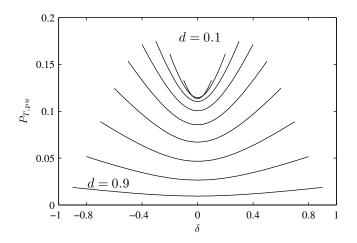

| 4.2  | DC-DC DAB Plots                       | 51 |

| 4.3  | Steady State Simulation Results                  | 4 |

|------|--------------------------------------------------|---|

| 4.4  | Zero Current Switching                           | 5 |

| 4.5  | AC-DC Dual Active Bridge 5                       | 5 |

| 4.6  | Simulation Results                               | 8 |

| 4.7  | Frequency Spectrum                               | 8 |

| 4.8  | Zero Current Switching 5                         | 9 |

| 4.9  | Average DC Current                               | 0 |

| 4.10 | Reactive Power Flow                              | 2 |

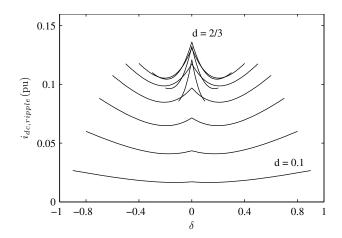

| 4.11 | Utilization Factor                               | 3 |

| 4.12 | Capacitor RMS Ripple Current                     | 4 |

| 4.13 | Simulation Currents                              | 5 |

| 4.14 | Modulation Cycle                                 | 5 |

| 5.1  | AC-DC Dual Active Bridge                         | 7 |

| 5.2  | Modulation Cycle                                 | 8 |

| 5.3  | First Third Cycle                                | 9 |

| 5.4  | Second Third Cycle                               | 2 |

| 5.5  | Third Third Cycle                                | 4 |

| 5.6  | Virtual Currents                                 | 6 |

| 5.7  | Space Vectors                                    | 7 |

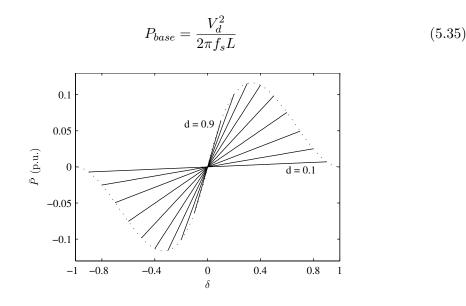

| 5.8  | Average Power Per Unit                           | 8 |

| 5.9  | Reactive Power Per Unit                          | 9 |

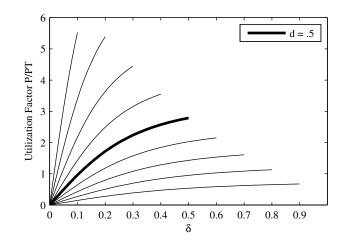

| 5.10 | Transformer Utilization                          | 0 |

| 5.11 | Output RMS Ripple Current    8                   | 1 |

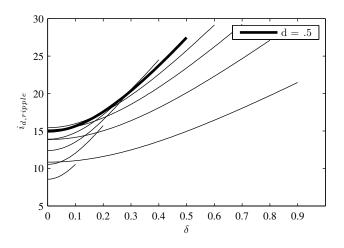

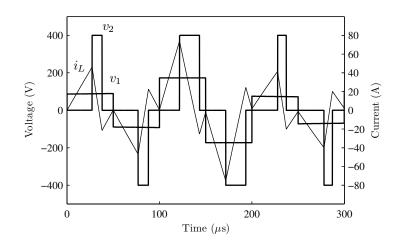

| 5.12 | Simulation Result : Zero Current Switching (ZCS) | 2 |

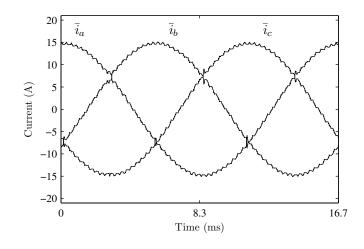

| 5.13 | Average Three Phase Currents    8                | 3 |

| 5.14 | Switch Currents                                  | 3 |

| 5.15 | Frequency Spectrum of $i_a$                      | 4 |

| 5.16 | Frequency Spectrum of $i_a$                      | 4 |

| 5.17 | One Cycle of Modulation Scheme                   | 5 |

| 5.18 | Filtered Phase A Current                         | 5 |

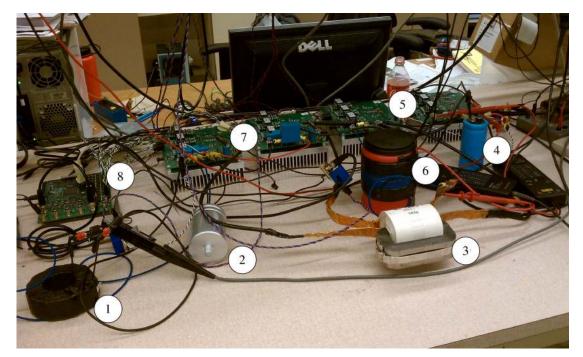

| 6.1  | Single Phase Hardware Topology                   | 7 |

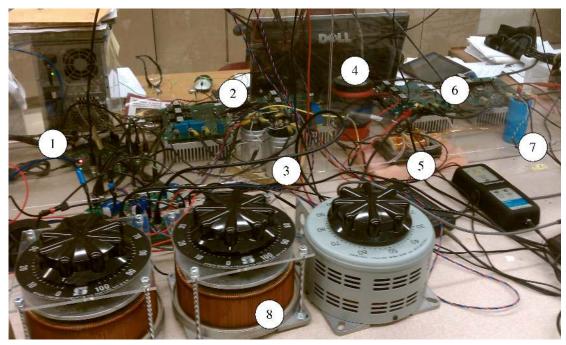

| 6.2  | Single Phase Input Experimental Setup 8          | 8 |

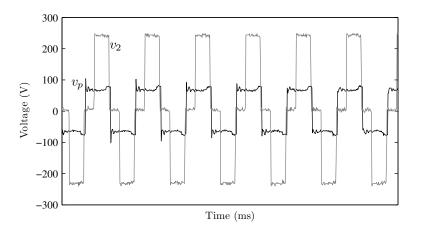

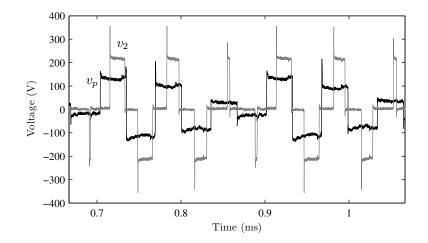

| 6.3  | Primary and H-Bridge Voltage         | 89 |

|------|--------------------------------------|----|

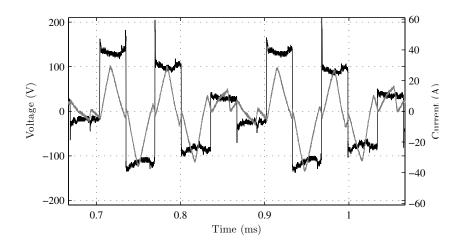

| 6.4  | Primary Voltage and Current          | 90 |

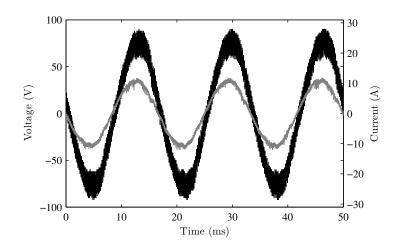

| 6.5  | Input Current                        | 91 |

| 6.6  | Input Current Harmonics              | 91 |

| 7.1  | Hardware Topology                    | 92 |

| 7.2  | Three Phase Input Experimental Setup | 93 |

| 7.3  | Primary and H-Bridge Voltage         | 94 |

| 7.4  | Primary Voltage and Current          | 95 |

| 7.5  | Phase A Input Voltage and Current    | 95 |

| 7.6  | Input Currents                       | 96 |

| 7.7  | Input Current Harmonics              | 96 |

| 7.8  | Zero Current Switching               | 97 |

| 7.9  | Primary and H-Bridge Voltage         | 98 |

| 7.10 | Input Currents                       | 98 |

| 7.11 | Input Current Harmonics              | 99 |

|      |                                      |    |

### Chapter 1

### Introduction

Renewable energy sources like wind, solar, and wave are becoming more predominant because of the rising demand of power, the dependence on foreign oil, and the detrimental effects of converting fossil fuels to power. Due to rising oil and gas prices and the drive to become more green, vehicle companies like Toyota, General Motors, Nissan, are developing more Hybrid Electric Vehicles (HEV), Plug-in Hybrid Electric Vehicles (PHEV), and Electric Vehicles (EV). With the introduction PHEV's and EV's into the market and the increasing popularity, demand, and availability of these vehicles, the grid is becoming more stressed. While more PHEV's and EV's hit the street each year, the availability to implement Vehicle-to-grid (V2G) becomes more feasible and practical.

Parking lots full of PHEV's and EVs can be used for ancillary services [1]. Also, V2G can become distributed generation and supply power to the grid during peak loads [2] [3] [4]. V2G can be used to supply reactive power to the grid [5]. V2G can be used for home back up power. It can also be used to set up a micro grid for military type applications.

#### 1.1 State of the Art

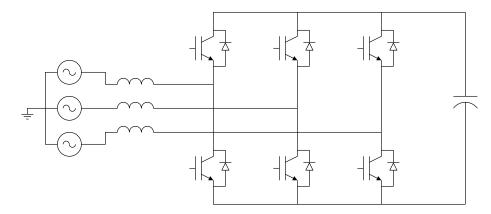

There are many topologies investigated in the literature for Vehicle-to-Grid applications [6, 7, 8, 9, 10, 11]. The topologies are either isolated or not isolated. The most common topology is the grid tied inverter shown in Fig. 1.1 [12] [13] [14]. A three-phase grid-tied inverter is shown, but in household applications it will be a single-phase grid-tied

inverter.

Figure 1.1: Grid Tied Inverter

The grid tied inverter is not an isolated topology but is well researched and documented [13] [14]. The advantage of this topology, besides its widespread use, is that the current can be controlled because of the input inductances in the line. Typically the switching frequency is large, compared to the input voltage frequency, leading to very small switching ripple on the input current. This leads to input currents with very low Total Harmonic Distortion. Another advantage of this topology is it is able to be reused. The PHEV or EV motor's inverter can have contactors that disconnect from the motor and connect with inductors in series with the input line voltages [7]. This alleviates car manufactures from the cost of two separate inverters but makes the system more complex from a systems engineer point of view. Lastly, there is only one switch or diode in the path of the current for each phase, leading to very efficient operation compared to topologies with more stages of conversion.

Another topology researched in EV applications is the multilevel inverter [15]. The advantage of this topology is there are more levels and the current ripple can be reduced, but the disadvantage is more switches and more complex control.

One topology reuses the motor windings as the input inductances for the grid tied inverter. These type of topologies are termed integrated because they reuse parts already there for traction, is the motor windings in this case [16, 17, 18].

The Z-source inverter is a bi-directional topology [19]. The draw back with this topology is the additional passive components, two inductors, two capacitors, and one

IGBT. These additional components add cost and increase reliability concerns.

There are also isolated topologies for PHEV and EV charging. One area of isolated topologies are the inductive charging topologies [20] [21] [22]. These topologies have no electrical connection therefore they have the advantage of isolation for safety. However inductive topologies are less efficient than there conductive counterparts.

Another isolated topology includes reusing the motor as an isolation transformer at 60Hz [23]. This topology has the benefit of reusing 2 sets of 3 phase windings as an isolation transformer. The drawback is the design of motor because it has two separate conflicting goals. On one hand the motor design is optimized for traction applications and on the other hand the motor is designed for 60Hz isolation applications. There also can be high amounts of magnetizing current depending on the design of the motor. Another drawback is the possibility of creating a sinusoidal varying flux in air gap, leading to rotation of the motor shaft which is undesirable when stationary and charging.

The multi port converter is another isolated topology that has the ability to draw power from multiple sources [24, 25, 26, 27, 28, 28, 29]. The multi port converter is better suited for multiple DC sources, for example a fuel cell and a battery pack.

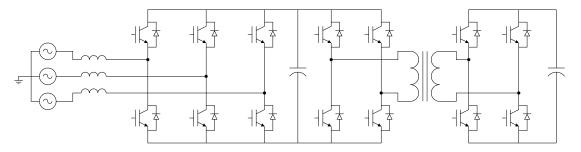

Typically isolated topologies for AC to DC are created by using two converters back to back [30] [31]. An example of this type of topology is shown in Fig. 1.2.

Figure 1.2: Grid Tied Inverter back to back Dual Active Bridge

The first converter is a bidirectional AC to DC grid-tied inverter. The second converter is a DC to DC isolated dual active bridge [32, 33, 34, 35, 36, 37, 38]. The disadvantage of this topology is the DC link in between the two converters. The capacitor raises the cost of the topology and also reliability concerns. The other disadvantage of this converter, compared to the grid tied inverter, is the efficiency. The efficiency is

the product of the efficiency of the inverter and efficiency of the dual active bridge. The advantage here is the DC bus is isolated from the AC source.

The back to back current link isolated topology is shown in Fig. 1.3 [39].

Figure 1.3: Isolated Current Link AC to DC Converter

This topology creates a current link with the inductor. The disadvantage of this topology is the extra inductor needed. Also, the size of the inductor is large adding cost and reducing power density. The efficiency also is lower than the DC link structure because the current flows through additional diodes.

Another topology is the resonant high frequency link converter 1.4 [40].

Figure 1.4: Isolated Resonant Link Converter

An advantage of this topology is that it does not create an intermediate current or voltage link. A disadvantage of this converter is the additional resonant tank elements, capacitor and inductor.

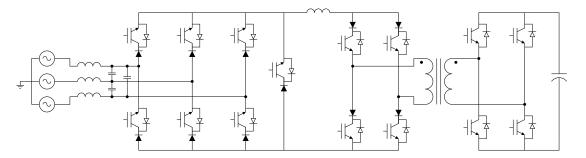

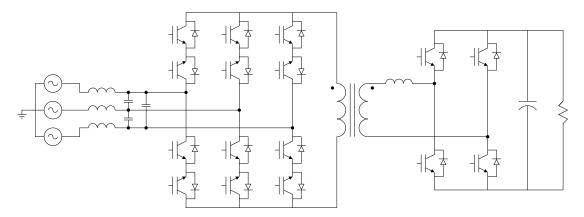

#### 1.2 Proposed Converter

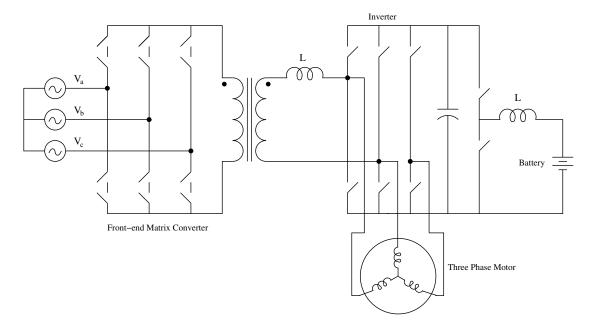

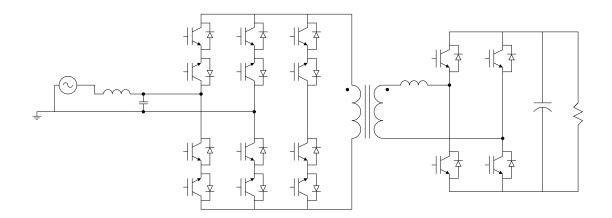

The proposed converter, in which this thesis and research is based, is shown in Fig. 1.5. During traction operation, meaning the vehicle is moving from place to place, the

Figure 1.5: Proposed Topology

transformer is disconnected from the inverter by means of contactors. The DC-DC converter maintains a constant DC bus voltage and the inverter employs some type of modulation to drive the motor. During charging or discharging operation, the vehicle is stationary, the motor is disconnected from the inverter by means of contactors. The motor inverter is reused as a H-Bridge for the bidirectional isolated AC to DC converter. The inductance, L, of the transformer is the lumped leakage inductance referred to the secondary. The input converter is a three-phase to single-phase matrix converter. The switches are four quadrant switches and are realized with a pair of emitter tied IGBT's. The input can accept single-phase for household type applications or it can accept three-phase for high power fast charging installations. This converter is bidirectional in nature and can source or sink power. This thesis will consider this topology only for charging and discharging operations. The bidirectional DC-DC converter between the DC bus and the battery pack will be modelled as a load resistance R when charging and as a

DC source when discharging. This topology has the following advantages over isolated back to back AC to DC converters: no intermediate DC link capacitor or current link inductor, higher reliability, higher power density, and smaller volume.

#### **1.3** Motivation and Scope

Grid-tied inverters are predominant in EV chargers. There is no AC to DC isolated bidirectional charger in literature without an intermediate current or voltage link. The motivation of this thesis is to present a new topology applicable to EV's , Solar installations, home backup, and military mirco-grid applications. Another objective of this thesis is to provide modulation and control strategies for single-phase and threephase input. This thesis analyzes the proposed modulation and control, and provides simulation and hardware results.

#### **1.4** Contributions

The contributions of this thesis are:

- A novel Single-Phase/Three-Phase AC to DC isolated bidirectional converter

- Detailed analysis of the converter for single-phase and three-phase control

- Detailed analysis of DAB modulation strategy for single-phase and three-phase input

- Design procedure for DAB modulation strategy of the converter

- Hardware results confirming the theoretical analysis of DAB modulation strategy for single-phase and three-phase input

#### 1.5 Organization

Chapter 1 introduces the current state of the art research in electric vehicle bidirectional chargers. It also introduces a novel converter which is the subject of this thesis. In Chapter 2 the converter is considered with single-phase input. A model of the average

power flow per cycle, based on the first harmonic, is derived and used as the basis of control. Controllers are designed for the power and voltage loops. Results are given for the input currents, harmonics, and bus voltages. Chapter 3 discusses control of the converter based on three-phase input. The control uses a duty ratio based method to create a quasi square wave. A power and voltage controller are designed. Input currents, current harmonics, and output voltages results are given and discussed. Chapter 4 introduces a new modulation method for single-phase AC to DC dual active bridge. The input current, current harmonics, and bus voltage simulation results are given and match theoretical analysis. Chapter 5 introduces a new modulation strategy for three-phase AC to DC dual active bridge. The input currents, power, utilization factor, rms ripple current are all analysed. Simulation results are given to confirm the analytical results. Lastly in Chapter 6 and 7, the hardware is presented, and results for the DAB modulation method are given in single-phase and three-phase input.

#### 1.6 Conclusion

In Chapter 1 the context and layout of the thesis is established. EV bidirectional chargers are introduced and a novel isolated bidirectional topology is introduced.

### Chapter 2

# Single Phase Power and Voltage Control

Figure 2.1: Single Phase Topology

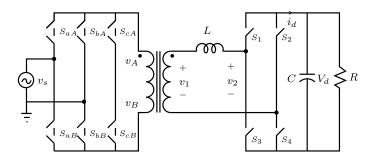

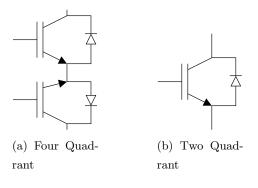

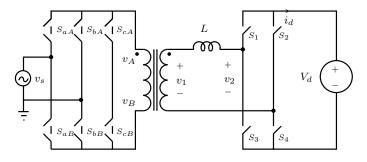

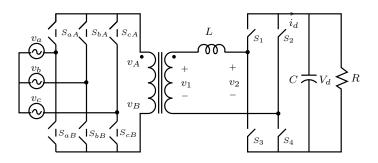

The topology is investigated for single-phase input and is shown in Fig. 2.1. The switches  $S_{aA}$ ,  $S_{bA}$ ,  $S_{cA}$ ,  $S_{aB}$ ,  $S_{bB}$ , and  $S_{cB}$  are four quadrant switches. The four quadrant switches are realized as shown in Fig. 2.2a. The transformer magnetizing inductance is neglected, the turns ratio is assumed to be one, and the total leakage inductance is referred to the secondary and represented by L. The switches  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$  are reused from the motor inverter and are two quadrant switches as shown in Fig. 2.2b. The capacitor, C, is the DC Bus capacitor and the load is modelled as R during charging. When feeding power back to the grid, R will be removed and the DC bus will be fed by a voltage source.

Figure 2.2: Switches

#### 2.1 Analysis

The input matrix converter is comprised of four-quadrant switches  $S_{aA}$ ,  $S_{bA}$ ,  $S_{cA}$ ,  $S_{aB}$ ,  $S_{bB}$ , and  $S_{cB}$ . In the single-phase configuration switches  $S_{cA}$  and  $S_{cB}$  are not connected to a phase therefore will be considered in the off state during the analysis. The input voltage,  $v_s(t)$ , is sinusoidal with frequency  $\omega_i$ , as shown in (2.1). During this analysis I have selected  $\omega_i$  as  $2\pi 60$  or 60Hz and  $\hat{V}_s$  as  $120\sqrt{2}$  because it is the most common in the U.S.

$$v_s(t) = \hat{V}_s \sin(\omega_i t) \tag{2.1}$$

The input matrix converter has two states. The first state is when switches  $S_{aA}$  and  $S_{bB}$  are on and switches SbA and  $S_{aB}$  are off. During this state the voltage  $+v_s(t)$  is applied to  $v_{AB}$ . In the second state, switches  $S_{bA}$  and  $S_{aB}$  are on and switches SaA and  $S_{bB}$  are off. During this state the voltage  $-v_s(t)$  is applied to  $v_{AB}$ . The states are on for 50% of the time at a frequency of  $f_s$ . The voltage applied to  $v_{AB}$  is shown in (2.2).

$$v_{AB}(t) = \hat{V}_s \sin(2\pi f_i t) \operatorname{sgn}(\sin(2\pi f_s t))$$

(2.2)

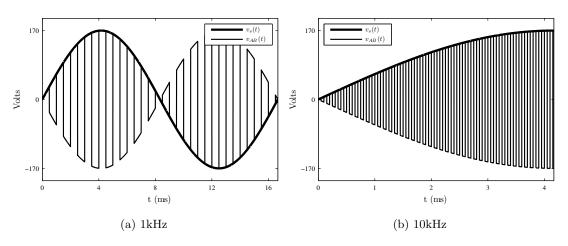

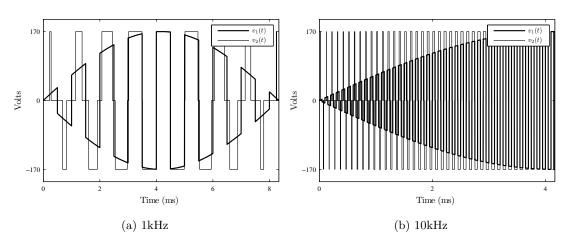

Fig. 2.3a shows the output of the matrix converter, for a lower  $f_s$  of 1kHz, for illustrative purposes and Fig. 2.3a shows the output of the matrix converter for a  $f_s$  of 10kHz.

For this analysis, I have picked the turns ratio of the transformer to be one, n = 1, therefore  $v_1(t)$  is equal to  $v_{AB}(t)$ . The output of the half-bridge  $v_2(t)$ , is a square wave of magnitude  $V_d$ . The output square wave of the half bridge is at frequency  $f_s$ . The output of the half bridge is represented mathematically in (2.3). The duty ratio of the square

Figure 2.3: Matrix Converter Output

wave is adjustable from zero to one by adjusting  $\phi(t)$ . For example if d = 1, then  $\phi = 0$ , therefore both squares are in phase in (2.3) and add to a square wave of magnitude  $V_d$ . On the contrary, if d = 0, then  $\phi = \frac{\pi}{2}$ , therefore both square waves are out of phase by 180 degrees and sum to zero. The duty ratio is given in (2.4). This selection of the duty ratio ensures that for any half period of  $f_s$ , the average voltage applied to  $v_1(t)$  is equal to the average voltage applied to  $v_2(t)$ . For visualization purposes, (2.3) has been plotted in Fig. 2.4a at  $f_s = 1kHz$  and in Fig. 2.4b at  $f_s = 10kHz$ .

$$v_{2}(t) = \frac{V_{d}}{2} [\operatorname{sgn} [\sin(2\pi f_{s}t - \phi(t) - \theta(t))] + \operatorname{sgn} [\sin(2\pi f_{s}t + \phi(t) - \theta(t))]]$$

(2.3)

$$d(t) = 1 - \phi(t)\frac{2}{\pi}$$

(2.4)

The phase shift  $\theta(t)$  is zero in both Fig. 2.4a and Fig. 2.4b. In order to do power flow there must be a finite phase shift. In the next section a power controller will be evaluated, designed, and simulated.

Figure 2.4: Bridge Outputs

#### 2.1.1 Power Controller

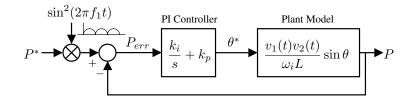

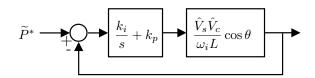

The power controller is designed to control the power in and out of the converter. The plant is assumed to be similar to the power systems analogy as shown in (2.5) [41, 42]. The power in (2.6) is the average power over a cycle of  $f_s$  at time t. Note that in power systems the two waveforms are sine waves but in this scheme they are square waves, therefore in this analysis the model is valid only for the first harmonic power flow. The fundamental of  $v_1$  is  $\frac{4}{\pi}$  times the voltage at that time. The fundamental of  $v_2$ , considering a duty ratio of 1, is  $\frac{4}{\pi}$  times the bus voltage  $V_d$ . The control diagram of the systems is shown in Fig. 2.5. In single-phase the power command is multiplied by a sine squared reference to insure sinusoidal input current with respect to the input voltage. The actual power transferred is measured by multiplying  $i_d$  by  $V_d$ , integrating that product during a cycle of  $f_s$  and dividing by  $T_s$  to get the average power transferred in that cycle.

$$P = \frac{V_1 V_2}{\omega L} \sin \theta \tag{2.5}$$

$$P(t) = \frac{16}{\pi^2} \frac{v_1(t)v_2(t)}{\omega_s L} \sin \theta$$

(2.6)

A simple Proportional Integral controller is selected for control. The equation in (2.6) is given a small perturbation about  $\theta$ . The equation is then solved in (2.7),

(2.8), (2.9), and the result is (2.10). In (2.10),  $v_1(t)$  and  $v_2(t)$  vary with time, but their product vary in a sine squared fashion. The reference is also multiplied by a sine squared reference therefore  $v_1(t)$  is replaced by the constant peak input voltage  $\hat{V}_s$ , and  $v_2(t)$  is replaced by the constant bus voltage  $V_c$ .

$$P + \widetilde{P} = \frac{16}{\pi^2} \frac{v_1(t)v_2(t)}{\omega_s L} \sin(\theta + \Delta\theta)$$

(2.7)

$$P + \widetilde{P} = \frac{16}{\pi^2} \frac{v_1(t)v_2(t)}{\omega_s L} \left[\cos\theta\sin\Delta\theta + \cos\Delta\theta\sin\theta\right]$$

(2.8)

$$P + \widetilde{P} = \frac{16}{\pi^2} \frac{v_1(t)v_2(t)}{\omega_s L} \left[\Delta\theta\cos\theta + \sin\theta\right]$$

(2.9)

$$\frac{\widetilde{P}}{\Delta\theta} = \frac{16}{\pi^2} \frac{v_1(t)v_2(t)}{\omega_s L} \cos\theta \tag{2.10}$$

The PI controller is designed around a linearized plant as shown in Fig. 2.6. The plant is a constant gain around the operating point  $\theta$ . The PI controller is selected because even though the plant we design the control loop around is a constant, the actual plant is not linear, and the PI controller will take care of the errors associated with the model inaccuracies.

The gain of the power stage is defined in (2.11). In order to design the controller gains a bandwidth and phase margin are chosen to suit the application. Next equations (2.12) and (2.13) are solved to determine the controller gains  $k_i$  and  $k_p$ . The values for solving the system of equations, (2.12) and (2.13), are shown in Table 2.1.

$$K_{pow} = \frac{\hat{V}_s \hat{V}_d}{\omega_s L} \cos\theta \tag{2.11}$$

Figure 2.5: Actual System

Figure 2.6: Linearized Control Design

$$|G_{OL}(s)|_{s=j2\pi f_{cp}} = \left|\frac{k_p s + k_i}{s} K_{pow}\right|_{s=j2\pi f_{cp}} = 1$$

(2.12)

$$\angle G_{OL}(s)|_{s=j2\pi f_{cp}} + 180 = \phi_{PM} \tag{2.13}$$

| Parameter   | Value | Unit    |

|-------------|-------|---------|

| $\hat{V}_s$ | 170   | V       |

| $\hat{V}_d$ | 300   | V       |

| $f_s$       | 10    | kHz     |

| L           | 50    | $\mu H$ |

| $\theta$    | 45    | degrees |

| $\phi_{PM}$ | 60    | degrees |

Table 2.1: Control Design Variables

The results for the design of the controller gains are shown in Table 2.2. The complete system in Fig. 2.1 is simulated using the designed PI controller gains. The load R is assumed to be  $45\Omega$  and C is  $1000\mu F$ .

| Parameter | Value  |  |

|-----------|--------|--|

| $k_p$     | 4.3e-5 |  |

| $k_i$     | 0.5    |  |

Table 2.2: Controller Gains

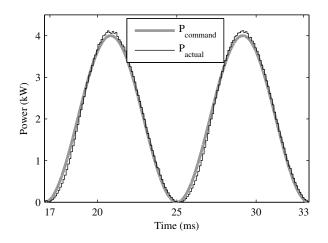

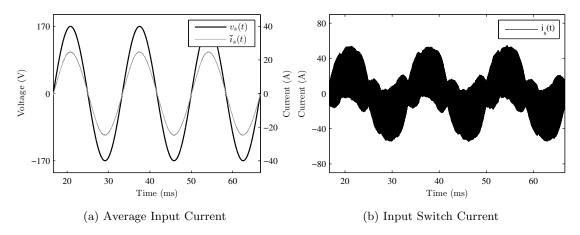

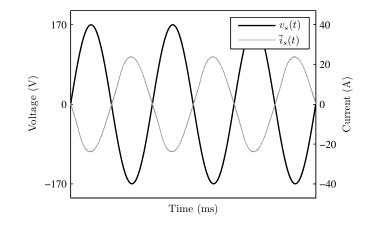

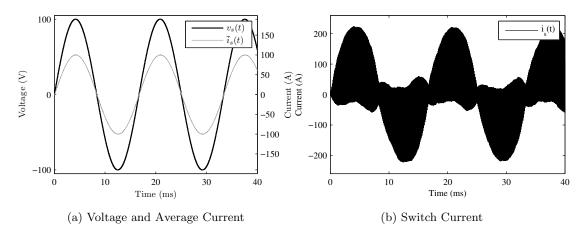

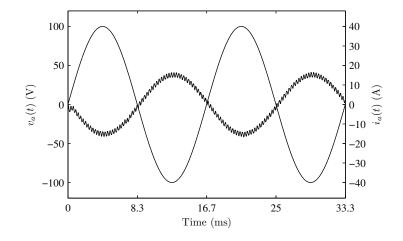

A power command of 4kW is given to the controller in Fig. 2.5. The results of the actual power flow plotted with the commanded power are shown in Fig. 2.7. The results of the power command show the actual power tracking the sine squared reference power command. The results of the average input current and input voltage are shown in Fig.

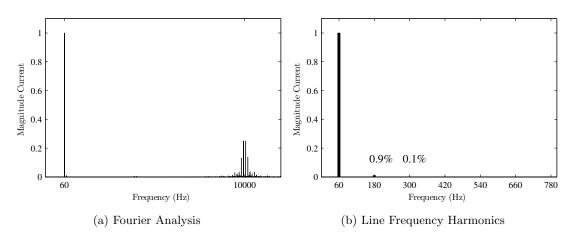

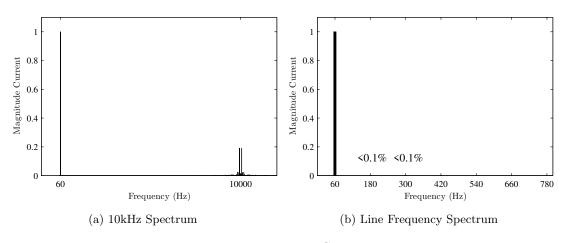

2.8a. The average input current is sinusoidal and in phase with the input voltage thus obtaining unity power factor. A fourier analysis is done on the switched current  $i_s(t)$ , in Fig. 2.8b, to determine the harmonics present in the input current. The results of the fourier analysis are shown in Fig. 2.9a and Fig. 2.9b. The spectrum in Fig. 2.9a shows the fundamental at 60Hz, some low level line frequency harmonics, and the switching harmonics at 10kHz. The switching harmonics can be removed from the input current by properly designing a LC input filter. In Fig. 2.9b the fourier analysis is zoomed in to capture the magnitude levels of the line frequency harmonics. The 3rd harmonic is present at 3% and the 5th harmonic is present at 0.8%.

Figure 2.7: Power Command

The present values of the 3rd and 5th harmonic meet the requirements for maximum current distortion in IEEE spec but further effort can be done to reduce these harmonics. The power controller is given step command from 4kW down to 2kW in order to investigate the dynamics of the power controller design. The step function, power command, and actual power are plotted in Fig. 2.10. The actual power settles within 5ms which is sufficient because in battery charging applications, the command won't change often.

Figure 2.8: Input Currents

Figure 2.9: Harmonic Analysis

#### 2.1.2 Power Controller Redesign

The power controller design provided acceptable current harmonics in the input current but will be redesigned in order to reduce the 3rd harmonic. The third harmonic is present because attenuation at 120Hz is not low enough which is similar to a PFC circuit. This time Eq. (2.12) and (2.14) are used to design the gains of the power controller. Eq. allows us to set the gain of the third harmonic of the closed loop system.

Figure 2.10: Power Step Command

$$|G_{OL}(s)|_{s=j2\pi 180} = \left|\frac{k_p s + k_i}{s} K_{pow}\right|_{s=j2\pi 180} = x$$

(2.14)

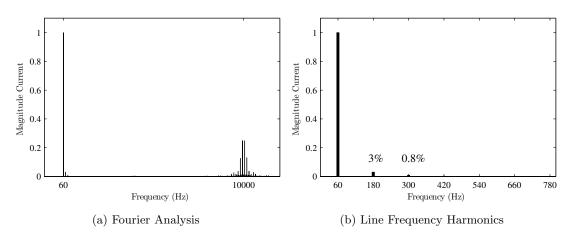

The new gains are shown in Table 2.3. The system is simulated with the controller gains and the response in a step power command from 4kW to 2kW are shown in Fig. 2.11. The bandwidth of the controller lowered due to the lowering of the gain at the third harmonic. Again, the bandwidth is acceptable because during the course of charging a battery the power command does not change often. The fourier spectrum of the input current is shown in Fig. 2.12a and 2.12b.

| Parameter | Value  |

|-----------|--------|

| $k_p$     | 4.3e-5 |

| $k_i$     | 0.1    |

Table 2.3: Controller Gains

Similar to the previous control design, there is current at 60Hz, and the switching frequency of 10kHz. The third and fifth harmonic are now both below 1% of the fundamental. The conclusion of the new power controller design is that the 3rd and 5th harmonics can both be reduced below 1% at the expense of the control loop bandwidth.

Figure 2.11: Power Step Command

Figure 2.12: Harmonic Analysis

#### 2.1.3 Steady State Analysis

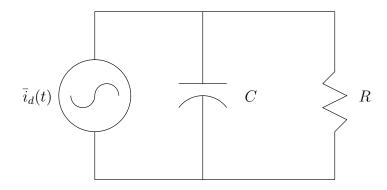

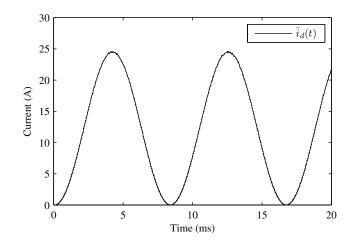

In this section the steady state for  $v_d(t)$  will be analyzed and solved for. The circuit shown in Fig. 2.13 represents the average system. The average current  $\bar{i}_d(t)$  (2.15) flows into the RC circuit. The current  $i_s(t)$  and duty cycle d(t) are defined in (2.16) and (2.17). The current  $i_d(t)$  is derived in (2.18) and is of sine squared form. The steady state voltage is solved in Laplace domain because it is simple. The voltage V(s) is solved for in (2.19) and then reverse transformed back to time domain. The current I(s) is transformed to Laplace domain in (2.20). The impedance of the RC circuit is defined in (2.21).

Figure 2.13: Simplified Voltage Circuit

$$\bar{i}_d(t) = \bar{i}_s(t)d(t) \tag{2.15}$$

$$\bar{i}_s(t) = \hat{I}_s \left| \sin \omega_i t \right| \tag{2.16}$$

$$d(t) = \frac{\hat{V}_s}{V_d} \left| \sin \omega_i t \right| \tag{2.17}$$

$$\bar{i}_d(t) = \hat{I}_s \frac{\hat{V}_s}{V_d} \sin^2 \omega_i t \tag{2.18}$$

$$V(s) = I(s)Z(s) \tag{2.19}$$

$$\mathcal{L}(\sin^2 \omega_i t) = \frac{1}{2}\mathcal{L}(1 - \cos 2\omega_i t) = \frac{1}{2}\left[\frac{1}{s} + \frac{s}{s^2 + (2\omega_i)^2}\right] = I(s)$$

(2.20)

$$Z(s) = \frac{\frac{1}{sC}R}{\frac{1}{sC} + R} = R\frac{1}{1 + \frac{s}{1/RC}}$$

(2.21)

Eq. (2.22) defines the magnitude k of the sine squared average current flowing into the RC circuit. Eq. (2.20) and (2.21) are multiplied together then partial fraction decomposition is used to get the result (2.23). The first fraction in (2.23) is the DC

Figure 2.14: Steady State Voltage

component of the voltage  $v_d(t)$ . The second fraction is a decay component so for steady state it is disregarded. The third term in (2.23) contains the second harmonic component of  $v_d(t)$ . Taking the inverse Laplace transform of the first and third fraction in (2.23) leads to the time domain equation of  $v_d(t)$  (2.24) (2.25). The peak to peak ripple voltage is defined in (2.26).

$$k = \hat{I}_s \frac{\hat{V}_s}{V_d} \tag{2.22}$$

$$V(s) = \frac{kR}{2s} - \frac{2C^3kR^4\omega_i^2}{(1+CRs)\left(1+4C^2R^2\omega_i^2\right)} + \frac{-kRs - 4CkR^2\omega_i^2}{2\left(s^2+4\omega_i^2\right)\left(1+4C^2R^2\omega_i^2\right)}$$

(2.23)

$$z = \sin^{-1} \left[ \frac{1}{\sqrt{1 + (2w_i R C)^2}} \right]$$

(2.24)

$$v_d(t) = \frac{kR}{2} + \frac{kR}{2\sqrt{1 + (2w_i RC)^2}} \sin(z - 2\omega_i t)$$

(2.25)

$$v_{d,pp-ripple} = \frac{RI_s V_s}{2V_c \sqrt{1 + (2w_i RC)^2}}$$

(2.26)

The system is simulated for a 2kW load where R = 45 and  $C = 1000 \mu F$ . The results of the simulation for  $v_d(t)$  are shown in Fig. 2.14. The steady state equation of  $v_d(t)$ (2.25) is plotted in grey in Fig. 2.14 and the actual system is plotted in black. The simulation shows the system powering up and converges to the steady state solution by time 80ms. Fig. 2.14 validates the steady state analysis.

#### 2.2 Power Plant Error

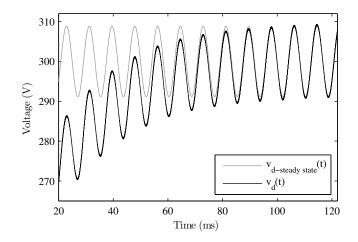

The power controller is designed around a plant that is an model of the actual system and because of this point, there will be a difference between the power that flows in the actual system and the power that flows in the model of the system. The error between the two will be explored in order to determine the amount of error. The three power flows will be investigated as follows: 1st harmonic power flow, square wave power flow, and the actual power flow. The average power flow of the first harmonic of the square waves is calculated in (2.27). The first harmonic of  $v_1$  is a sine wave of magnitude  $\frac{4}{\pi}120\sqrt{2}$ . The first harmonic of  $v_2$  is a sine wave of magnitude  $\frac{4}{\pi}120\sqrt{2}\cos\phi$ . The power is calculated across  $\phi$ , ranging from 10 to 80 degrees in steps of 10 degrees, and across  $\theta$ , ranging from -90 degrees to 90 degrees. Next the average power is calculated for two square waves in (2.28) [43, 44, 45, 46].  $v_1$  is a square wave of magnitude  $120\sqrt{2}\cos\phi$ and  $v_2$  is a square wave governed by (2.3). For each  $\phi$ , in steps of 10 degrees from 10 to 80 degrees, the power is calculated for all  $\theta$  from -90 to 90 degrees. Lastly, the power of the actual systems is calculated by simulation for  $\phi$ , in steps of 10 degrees from 10 to 80 degrees, and all  $\theta$  from -90 degrees to 90 degrees.

$$P_{1st-harmonic} = \frac{V_1 V_2}{\omega_s L} \sin\theta \tag{2.27}$$

$$P_{square} = \frac{V_1 V_2}{\omega_s L} \theta \left( 1 - \frac{|\theta|}{\pi} \right)$$

(2.28)

The difference between the actual power flow and the 1st harmonic and square wave power flows will give insight into the accuracy of the model. The error between the 1st harmonic power flow and the actual power flow is calculated in (2.29) and shown in Fig. 2.15a. The error between the square wave power flow and the acutal power is calculated in (2.30) and shown in Fig. 2.15b.

$$E_{1st-harmonic} = \frac{P_{actual} - P_{1st-harmonic}}{P_{1st-harmonic}}$$

(2.29)

Figure 2.15: Power Error

$$E_{square} = \frac{P_{actual} - P_{square}}{P_{square}}$$

(2.30)

The error between the 1st harmonic power flow and the actual power flow ranges from .18pu to -.2pu for all  $\theta$  and given set points of  $\phi$ . The error between the square wave power flow and the actual power flow ranges from .21pu to -.35pu for all  $\theta$  and given set points of  $\phi$ . The error is not minimal by any means but is small enough that if a robust controller is properly designed it can account for the error present in this analysis.

#### 2.3 Voltage Controller Design

Figure 2.16: Voltage Control Loop

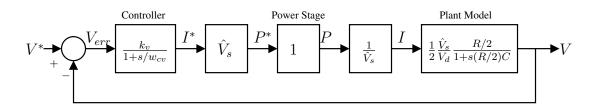

The voltage control loop is depicted in Fig. 2.16. This circuit is similar to a singlephase PFC in that the current into the RC circuit is of the form of a sinusoid squared. The power stage transfer function is shown in (2.31) and is derived in [47]

$$\frac{v_d(s)}{i_d(t)} = \frac{1}{2} \frac{\hat{V}_s}{V_d} \frac{R/2}{1 + s(R/2)C}$$

(2.31)

One approach to the voltage loop would be to select the controller as a low pass, as shown in (2.32). There will always be steady state error when this type of controller is used because the absence of a pole at the origin. Eq. (2.33) is defined to select the loop bandwidth and Eq. is defined to ensure 1.5% or less 2nd harmonic ripple in the output current command. These equations are solved as a system of equations to determine the gain  $k_v$  and pole  $w_{cv}$ .

$$G_v(s) = \frac{k_v}{1 + s/w_{cv}}$$

(2.32)

$$\left| \frac{k_v}{1 + s/w_{cv}} \frac{1}{2} \frac{\hat{V}_s}{V_c} \frac{R/2}{1 + s(R/2)C} \right|_{s = j2\pi f_{cv}} = 1$$

(2.33)

$$\left|\frac{k_v}{1+s/w_{cv}}\right|_{s=j2\pi 120} = \frac{.015\hat{I}_s}{V_{d,pp-ripple}}$$

(2.34)

The parameters used to solve for the pole and gain are shown in Table 2.4. The gain and pole are shown in Table 2.5. The whole system is simulated with aforementioned voltage controller and the results are investigated.

| Parameter               | Value   | Unit    |

|-------------------------|---------|---------|

| $\hat{V}_s$             | 170     | V       |

| $\hat{V}_d$             | 300     | V       |

| R                       | 45      | Ω       |

| C                       | 1000    | $\mu F$ |

| $f_{cv}$                | 10      | Hz      |

| $\hat{I}_s$             | 23.5294 | А       |

| $\hat{V}_{d,pp-ripple}$ | 8.84    | V       |

Table 2.4: Voltage Control Design Variables

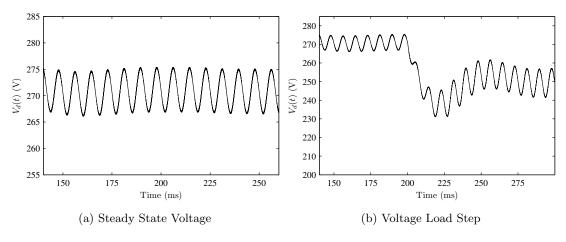

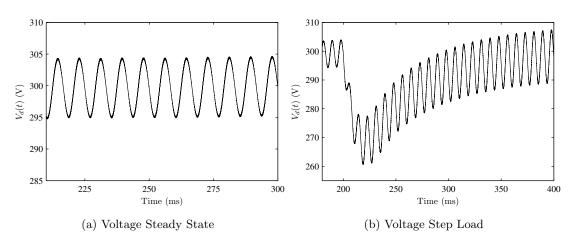

The voltage  $v_d(t)$  is plotted in Fig. 2.17. The voltage contains an expected 120Hz component and also has a steady state error of about 30 volts.

| Parameter | Value   |

|-----------|---------|

| $w_{cv}$  | 94.7329 |

| $k_v$     | 0.3259  |

Table 2.5: Voltage Control Loop Parameters

Figure 2.17: Output Voltage

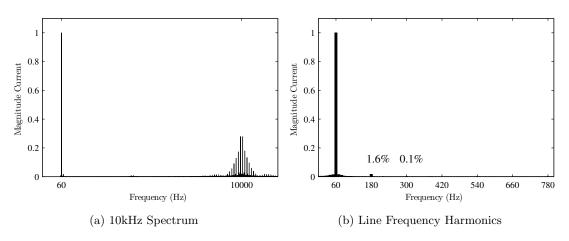

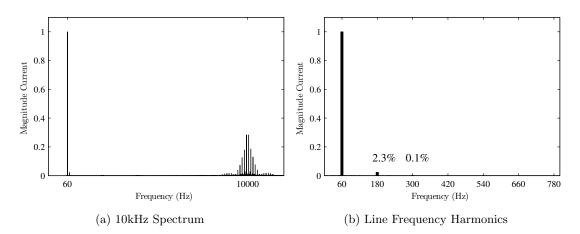

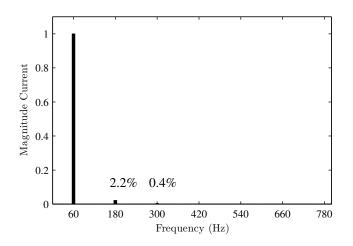

The input current spectrum of  $i_s(t)$  under steady state is shown in Fig. 2.18a and Fig. 2.18b. The input current contains the fundamental at 60Hz, some line frequency harmonics and the switching component at 10kHz. From the simulation data the magnitude of the third harmonic is 1.6% which matches closely with the designed value of 1.5%. If the application can work without closely tracking the 300 volts then the simple low pass controller will suffice.

#### 2.3.1 Voltage Controller Redesigned

In order to track the voltage command and not have steady state error one must introduce a pole at the origin. A proportional integral or PI controller is selected to obtain zero steady state error. The voltage control loop is shown in Fig. 2.19 with a PI controller instead of the low pass controller.

The controller gains  $k_i$  and  $k_p$  were selected by using the ratio of  $k_i$  and  $k_p$  to create a zero to cancel the pole of the plant at full load. Then  $k_i$  was adjusted to create of crossover frequency of 10Hz. The control parameters determined from the analysis are

Figure 2.18: Input Current Spectrum

Figure 2.19: Voltage Control Loop

shown in Table 2.6. The entire system is simulated using the controller in Fig. 2.19 and gains in Table 2.6. The output voltage is shown in Fig. 2.20a. The output voltage now tracks the 300 Volt command due to the presence of a pole at the origin.

| Parameter | Value  |

|-----------|--------|

| $k_i$     | 5      |

| $k_p$     | 0.2250 |

Table 2.6: Voltage Control Loop Parameters

The system is given a step load at 200ms in which R changes from  $90\Omega$  to  $45\Omega$  which is equal to a step load from 1kW to 2kW. The results of the voltage due to the step change are plotted in Fig. 2.20b. The voltage recovers to 300V in 200ms. The voltage ripple also is larger with a larger load. The input current is investigated for the PI controller. The input current spectrum is shown in Fig. 2.21a and 2.21b. The input

Figure 2.20: Output Voltage

current contains line 2.6% at the third harmonic, 0.1% at the fifth harmonic and the harmonics above the fifth are negligible. The total THD of the input current, neglecting the switching frequency harmonics, is 2.6% The third and fifth harmonics are higher than the low pass controller because the gain at those frequencies are higher and the design did not focus on reducing these. A PI controller with an additional pole past the cut-off frequency but before 120Hz would help reduce the third and fifth harmonics if it is desired to reduce the harmonics further but the harmonics present using the PI controller still conform to the IEEE 519 standard thus no further control will be investigated.

#### 2.3.2 Bidirectional Power Flow

The topology in Fig. 2.1 is changed to Fig. 2.22 for the purpose of simulating bidirectional power flow.

The DC source represents a battery pack or a bidirectional DC to DC converter boosting the battery pack voltage [48] [49] [50] [51]. The topology in Fig. 2.22 is simulated with DC bus of 300 Volts. The voltage loop is removed and only the power loop is used. The parameters in Table 2.1 and 2.2 are used for simulation. The power controller is given a command of -4kW which is equivalent to supplying 4kW to the AC source from the DC source. The results of the average current and input voltage are shown in Fig. 2.23.

Figure 2.21: Input Current Frequency Spectrum

Figure 2.22: Bidirectional Simulation Topology

The current is sinusoidal and 180 degrees out of phase with the input voltage proving that bidirectional power flow is possible with the given topology and control. The input current harmonics, normalized to the fundamental, are shown in Fig. 2.24.

The input current contains 2.2% at the third harmonic and 0.4% at the fifth harmonic. The rest of the harmonics are negligible. The total harmonic distortion of the input current is 2.23% which is with in IEEE-519 specifications [52]. The percentage of current at the third and fifth is also within IEEE-519 specification.

## 2.4 Conclusion

In this chapter the single phase bidirectional charger is proposed. First a power controller was analyzed and designed. The error between the plant model and the actual

Figure 2.23: Bidirectional Power Flow

Figure 2.24: Current Harmonics

system was investigated to determine the accuracy of the model. It was determined the model to be accurate enough to use for design of the power control loop. Next, steady state analysis was done to determine the output voltage equations. Lastly, two different voltage loop controllers we discussed, analyzed, and presented. The input current was analyzed during each controller design to maintain low line frequency harmonics and low THD.

# Chapter 3

# Power and Voltage Control with Three Phase Input

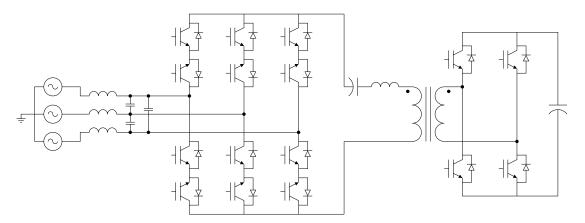

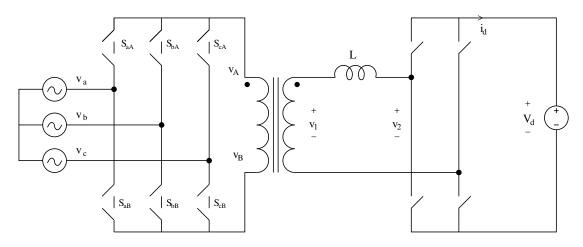

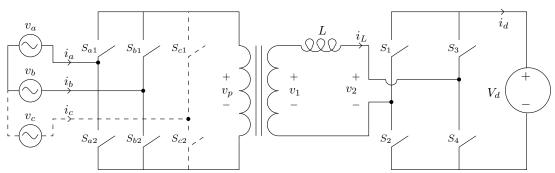

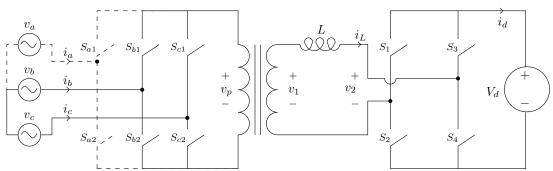

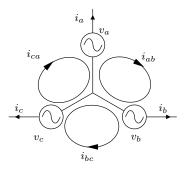

Figure 3.1: Three Phase Topology

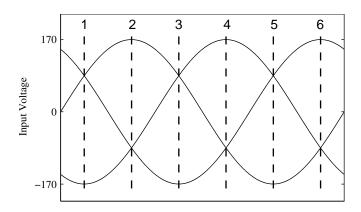

The topology in Fig. 3.1 is explored for three-phase input. The sinusoidal input sources are defined in (3.1) and have a magnitude of  $V_i$  at a frequency of  $\omega_i$ .

$$v_{a}(t) = V_{i} \sin(\omega_{i}t)$$

$$v_{b}(t) = V_{i} \sin(\omega_{i}t - \frac{2\pi}{3})$$

$$v_{c}(t) = V_{i} \sin(\omega_{i}t - \frac{4\pi}{3})$$

(3.1)

The switches  $S_{aA}$ ,  $S_{bA}$ ,  $S_{cA}$ ,  $S_{aB}$ ,  $S_{bB}$ , and  $S_{cB}$  are four quadrant switches comprised of two emitter tied insulated gate bipolar transistors. In this analysis the magnetizing inductance is neglected and the leakage inductance of the transformer is lumped to the secondary (3.2). The turns ratio of the transformer is assumed to be unity. The switches  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$  are reused from the motor inverter and are two quadrant switches realized as IGBT's. The DC bus capacitor for the inverter is reused as a DC source and the load resistance R is simulating charging a battery. The load resistance, R, and capacitor, C, will be replaced with a DC source when simulating supplying power to the grid.

$$L = n^2 L_p + L_s \tag{3.2}$$

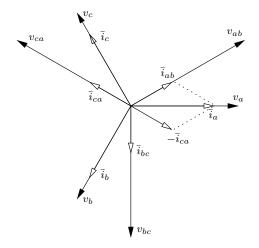

## 3.1 Analysis

The three-phase to single-phase matrix converter consists of switches  $S_{aA}$ ,  $S_{bA}$ ,  $S_{cA}$ ,  $S_{aB}$ ,  $S_{bB}$ , and  $S_{cB}$ . Each of the three switches  $S_{aA}$ ,  $S_{bA}$ , and  $S_{cA}$  are given a duty ratio defined in (3.3), (3.4), and (3.5) [53].

$$d_{aA}(t) = K_i \sin(\omega t) + \frac{1}{2} |\sin(\omega t)| + \frac{1}{6} \left[ 2 - |\sin(\omega t)| - |\sin(\omega t - \frac{2\pi}{3})| - |\sin(\omega t - \frac{4\pi}{3})| \right]$$

(3.3)

$$d_{bA}(t) = K_i \sin(\omega t - \frac{2\pi}{3}) + \frac{1}{2} |\sin(\omega t - \frac{2\pi}{3})| + \frac{1}{6} \left[ 2 - |\sin(\omega t)| - |\sin(\omega t - \frac{2\pi}{3})| - |\sin(\omega t - \frac{4\pi}{3})| \right]$$

(3.4)

$$d_{cA}(t) = K_i \sin(\omega t - \frac{4\pi}{3}) + \frac{1}{2} |\sin(\omega t - \frac{4\pi}{3})| + \frac{1}{6} \left[ 2 - |\sin(\omega t)| - |\sin(\omega t - \frac{2\pi}{3})| - |\sin(\omega t - \frac{4\pi}{3})| \right]$$

(3.5)

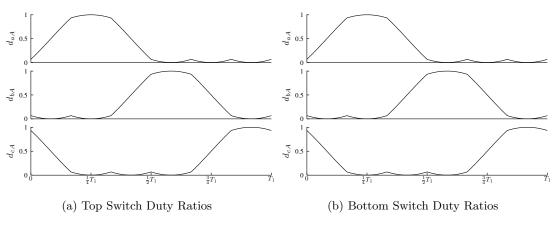

Similarly, the three switches  $S_{aB}$ ,  $S_{bB}$ , and  $S_{cB}$  are given a duty ratio defined in (3.6), (3.7), and (3.8). The only difference in duty ratios between the top switches and the bottoms switches is the sign of  $K_i$ . All six duty ratios are shown in Fig. 3.2a and Fig. 3.2b.

$$d_{aB}(t) = -K_{i}\sin(\omega t) + \frac{1}{2}|\sin(\omega t)| + \frac{1}{6}\left[2 - |\sin(\omega t)| - |\sin(\omega t - \frac{2\pi}{3})| - |\sin(\omega t - \frac{4\pi}{3})|\right]$$

(3.6)

$$d_{bB}(t) = -K_i \sin(\omega t - \frac{2\pi}{3}) + \frac{1}{2} |\sin(\omega t - \frac{2\pi}{3})| + \frac{1}{6} \left[ 2 - |\sin(\omega t)| - |\sin(\omega t - \frac{2\pi}{3})| - |\sin(\omega t - \frac{4\pi}{3})| \right]$$

(3.7)

$$d_{cB}(t) = -K_i \sin(\omega t - \frac{4\pi}{3}) + \frac{1}{2} |\sin(\omega t - \frac{4\pi}{3})| + \frac{1}{6} \left[ 2 - |\sin(\omega t)| - |\sin(\omega t - \frac{2\pi}{3})| - |\sin(\omega t - \frac{4\pi}{3})| \right]$$

(3.8)

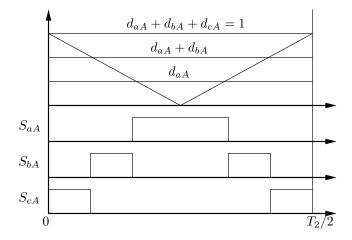

Now that each switch has been given a duty ratio, the actual switching signals must be generated. The duty ratios are compared to an inverter triangle ramp shown in Fig. 3.3. The switch  $S_{aA}$  is on when  $d_{aA}$  is greater than the ramp and is off otherwise (3.9). The switch  $S_{cA}$  is on when  $d_{aA} + d_{bA}$  is less than the ramp and is off otherwise (3.10). The switch  $S_{bA}$  is on when the ramp is greater than  $d_{aA}$  but less than  $d_{aA} + d_{bA}$  and is off otherwise (3.11).

$$S_{aA}(t) = \begin{cases} 0 & 0 < t < \frac{T_s}{2} \left[ 1 - d_{aA}(t) \right] \\ 1 & \frac{T_s}{2} \left[ 1 - d_{aA}(t) \right] < t < \frac{T_s}{2} \left[ 1 + d_{aA}(t) \right] \\ 0 & \frac{T_s}{2} \left[ 1 + d_{aA}(t) \right] < t < T_s \end{cases}$$

(3.9)

$$S_{bA}(t) = \begin{cases} 0 & 0 < t < \frac{T_s}{2} \left[ 1 - d_{aA}(t) - d_{bA}(t) \right] \\ 1 & \frac{T_s}{2} \left[ 1 - d_{aA}(t) - d_{bA}(t) \right] < t < \frac{T_s}{2} \left[ 1 - d_{aA}(t) \right] \\ 0 & \frac{T_s}{2} \left[ 1 - d_{aA}(t) \right] < t < \frac{T_s}{2} \left[ 1 + d_{aA}(t) \right] \\ 1 & \frac{T_s}{2} \left[ 1 + d_{aA}(t) \right] < t < \frac{T_s}{2} \left[ 1 + d_{aA}(t) \right] \\ 0 & \frac{T_s}{2} \left[ 1 + d_{aA}(t) \right] < t < \frac{T_s}{2} \left[ 1 + d_{aA}(t) + d_{bA}(t) \right] \\ 0 & \frac{T_s}{2} \left[ 1 + d_{aA}(t) + d_{bA}(t) \right] < t < T_s \end{cases}$$

(3.10)

$$S_{cA}(t) = \begin{cases} 1 & 0 < t < \frac{T_s}{2} \left[ 1 - d_{aA}(t) - d_{bA}(t) \right] \\ 0 & \frac{T_s}{2} \left[ 1 - d_{aA}(t) - d_{bA}(t) \right] < t < T_s \end{cases}$$

(3.11)

Figure 3.2: Duty Ratios

Figure 3.3: PWM Generation

The switching signals for the bottom three switches  $S_{aB}$ ,  $S_{bB}$ , and  $S_{cB}$  are generated the same exact way as previously discussed using there respective duty ratios.

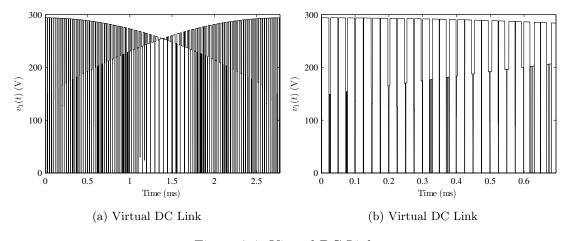

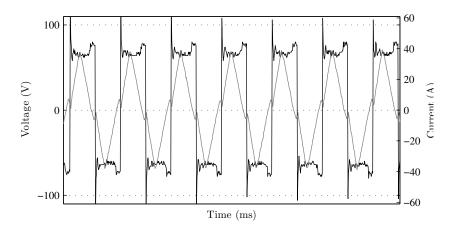

The modulation is simulated to determine the output at  $v_{AB}$ , using the values in Table 3.1. The output of the matrix converter at  $v_{AB}$  is shown in Fig. 3.4a and 3.4b. Calculating the average voltage at  $v_{AB}$  during any  $T_s$  time period would result in 255 volts (3.12).

$$\bar{v}_{AB} = V_i \frac{3\sqrt{2}}{2} \tag{3.12}$$

| $V_i$ | 170 | Volts |

|-------|-----|-------|

| $f_i$ | 60  | Hz    |

| $f_s$ | 10  | kHz   |

Table 3.1: Modulation Values

Figure 3.4: Virtual DC Link

The present modulation scheme creates a virtual DC bus but the goal is to create a square wave. The modulation index  $K_i$  will be modified in (3.13) to create a square wave. The modulation index  $K_i$  now switches signs every half cycle of  $f_s$ .

$$K_{i} = \begin{cases} +\frac{1}{2} & 0 < t < T_{s} \\ -\frac{1}{2} & T_{s} < t < 2T_{s} \end{cases}$$

(3.13)

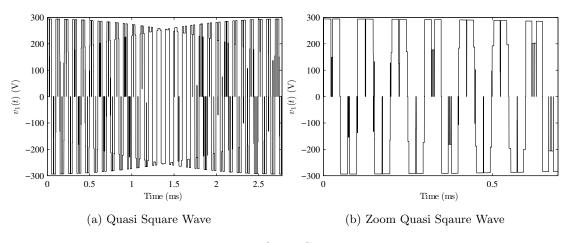

The simulation is run with the alternating modulation index and the results are shown in Fig. 3.5a and 3.5b.

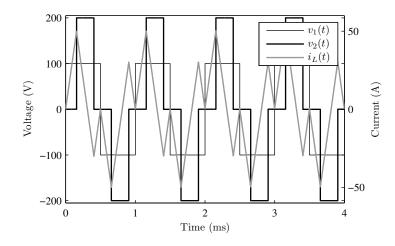

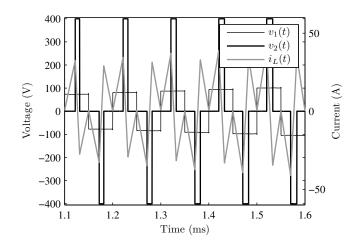

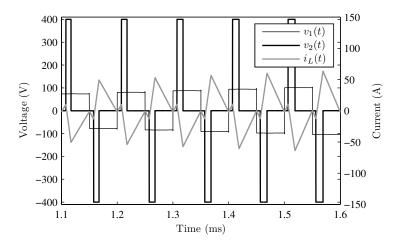

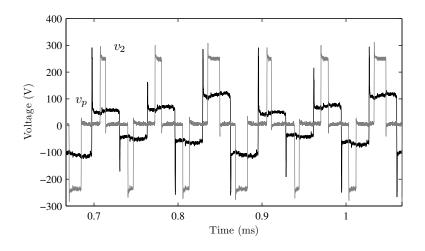

The voltage  $v_{AB}$  is now a quasi square wave with a magnitude on the average of  $3K_iV_i$ . Now that the square wave is generated at  $v_{AB}$  hence  $v_1$ , the next step is to generate a square wave at  $v_2$  with an equal average voltage during any  $T_s/2$  time period.

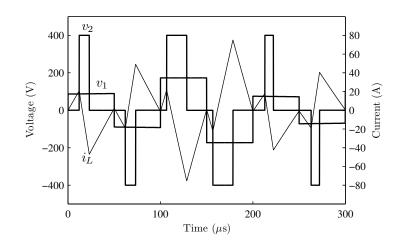

The average voltage at  $v_1$  will be constant  $3K_iV_i$ . The voltage at  $v_2$  will by synthesized as follows, if  $3K_iV_i > V_d$  then  $v_2$  will follow (3.14), otherwise if  $3K_iV_i < V_d$  the voltage  $v_2$  will follow (3.16). Theta is the phase shift of the waveform at  $v_2$  with respect to the waveform at  $v_1$  and phi controls the width of the square wave at  $v_2$ . The two

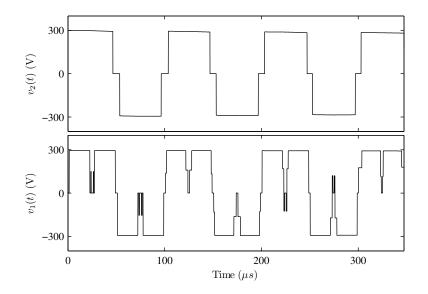

Figure 3.5: Quasi Square Wave

waveforms  $v_1$  and  $v_2$  are shown in Fig. 3.6. Note that the average voltage of  $v_1$  and  $v_2$  during any  $T_s/2$  time period are equal. Power is controlled by adjusting the phase shift of  $v_2$ .

$$v_2(t) = V_d \operatorname{sgn}\left[\sin(2\pi f_s t - \theta(t))\right]$$

(3.14)

$$\phi(t) = \frac{\pi}{2} \left[ 1 - \frac{3V_i}{2V_d} \right] \tag{3.15}$$

$$v_{2}(t) = \frac{V_{d}}{2} [\operatorname{sgn} [\sin(2\pi f_{s}t - \phi(t) - \theta(t))] + \operatorname{sgn} [\sin(2\pi f_{s}t + \phi(t) - \theta(t))]]$$

(3.16)

A controller to command the power into the RC network will be designed. With three-phase input, the average voltage at  $v_1$  doesn't change unlike the single phase case. This has a distinct advantage because now the gain of the power stage doesn't vary sinusoidally with the input voltage. The power stage will be modelled like a power flow in a power system (3.17). The equation in power systems for power flow is with two sinusoidal sources but these sources are square waves so the model is an approximation.

$$P = \frac{V_1 V_2}{\omega L} \sin \theta \tag{3.17}$$

Figure 3.6: Phase Shift Voltage Waveforms

#### 3.1.1 Modelling Error

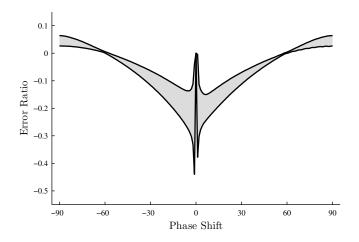

The power systems model is not an exact model of the current system but the difference between the two is investigated to determine the amount of error. The model power is calculated using (3.17) and the actual power is calculated through simulation. The value of  $\phi$  which determines the duty ratio of  $v_1$  is swept from 0 to  $\pi/2$  and  $\theta$  is swept from  $-\pi/2$  to  $\pi/2$ . The error ratio is calculated by subtracting the actual power from the first harmonic power and dividing by the first harmonic power. This error ratio only depends on  $\theta$  and  $\phi$  and is plotted in Fig. 3.7.

The black line envelops the extremes of the error at that specific  $\theta$  and the grey area represents possible error for all  $\theta$  and  $\phi$ . The graph shows that the error remains between +10% and -30% for all operating conditions and shows that the model is reasonable accurate. The power can be controlled and the error can be reduced to zero by using a PI controller with a robust design.

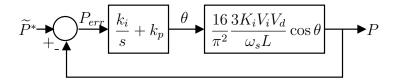

#### 3.1.2 Power Controller Design

With the model decided upon a power control loop must be designed. The power system equation (3.17) is given a perturbation about  $\theta$  and gives Eq. (3.18).

Figure 3.7: Modelling Error

$$\frac{\widetilde{P}}{\Delta\theta} = \frac{16}{\pi^2} \frac{3K_i V_i V_d}{\omega_s L} \cos\theta \tag{3.18}$$

The  $\frac{4}{\pi}$  factors come from the first harmonic of the square waves at  $v_1$  and  $v_2$ , the factor  $3K_iV_i$  determines the magnitude of  $v_1$  and  $V_d$  determines the magnitude of  $v_2$ . The equation is a constant therefore designing a PI controller is relatively simple. The power control loop design is shown in Fig. 3.8.

Figure 3.8: Three Phase Power Controller

The controller values  $k_i$  and  $k_p$  are calculated by solving two equations, the first one sets the open loop gain to 1 and the cross over frequency and the second sets the phase margin at the cross over frequency. The values in Table 3.2 are used to calculated the two controller gains.

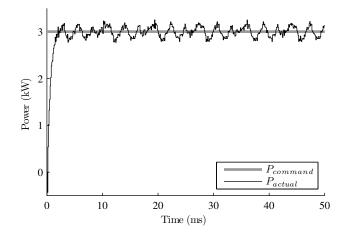

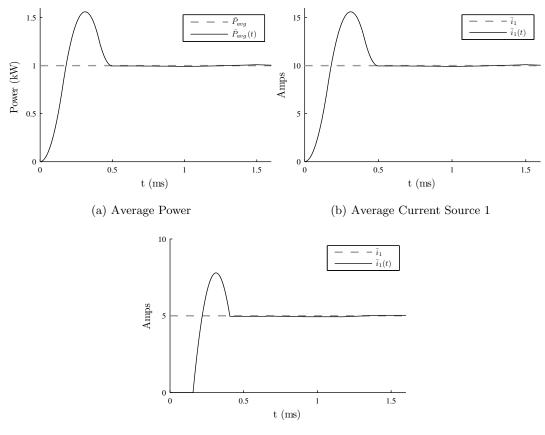

The calculated controller gains come out to  $k_i = 0.2293$  and  $k_p = 2.1e - 5$ . The controller is implemented on the real system and simulated. The load is 30 $\Omega$  and the capacitor is  $200\mu F$ . A power command of 3kW is given to the controller at system

| Parameter | Value | Unit    |

|-----------|-------|---------|

| $V_i$     | 170   | Volts   |

| $K_i$     | 0.5   |         |

| $V_d$     | 300   | Volts   |

| $f_s$     | 10    | kHz     |

| L         | 50    | $\mu H$ |

| $\theta$  | 45    | degrees |

| PM        | 60    | degrees |

Table 3.2: Power Control Loop Design Variables

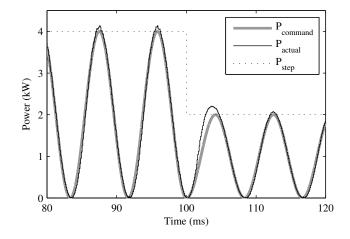

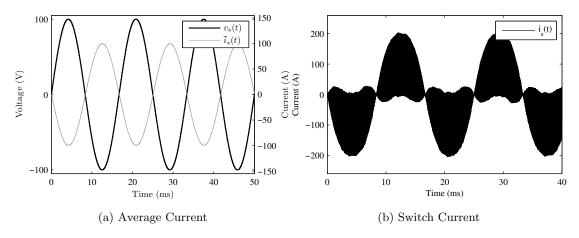

start up. The actual power and the command are plotted in Fig. 3.9. The actual power builds up to 3kW and tracks the command.

Figure 3.9: 3kW Power Command

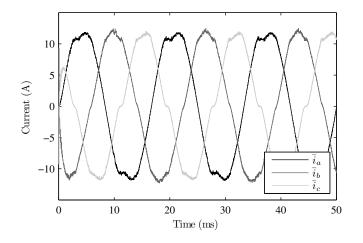

The average current from the voltage sources  $v_a$ ,  $v_b$ , and  $v_c$  are shown in Fig. 3.10. The currents are sinusoidal and in phase with the input voltage but one can determine that there are line frequency harmonics present. Ideally the currents would contain zero harmonics.

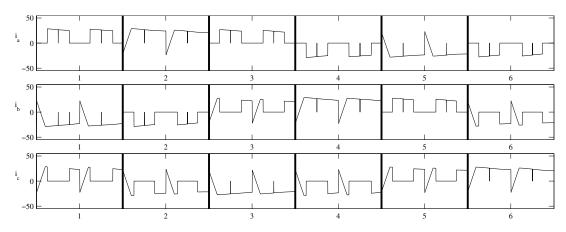

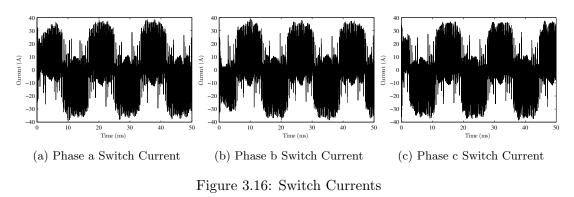

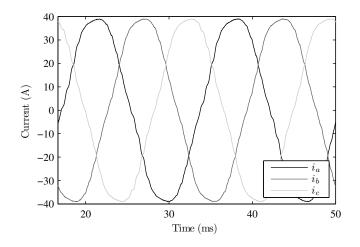

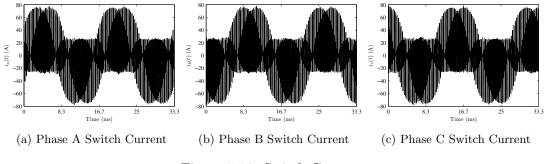

In order to give some insight, the switch currents for  $i_a$ ,  $i_b$ , and  $i_c$  are shown in Fig. 3.11a, 3.11b, and 3.11c. The currents have the high frequency component at 10kHz on top of the fundamental at 60Hz. The first observation is that the currents are unbalanced

Figure 3.10: Average Currents

and each have their own different harmonics.

Figure 3.11: Switch Currents

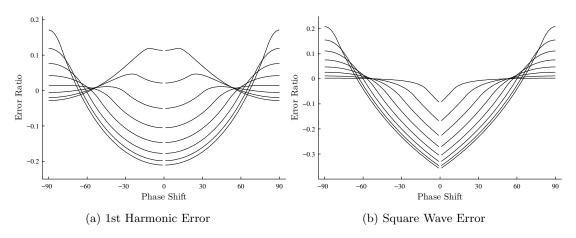

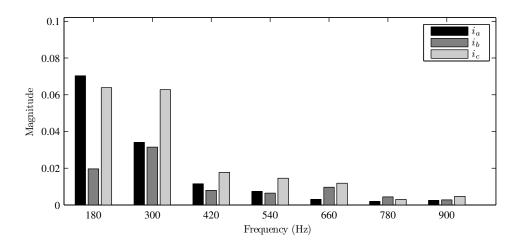

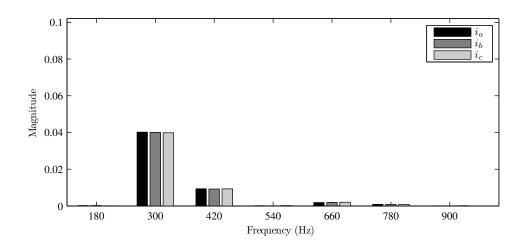

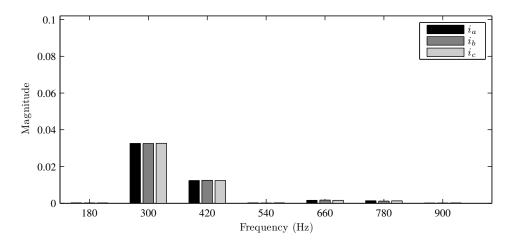

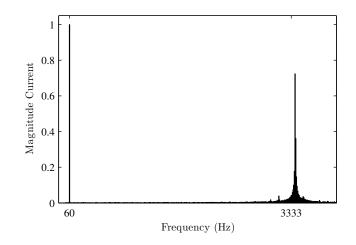

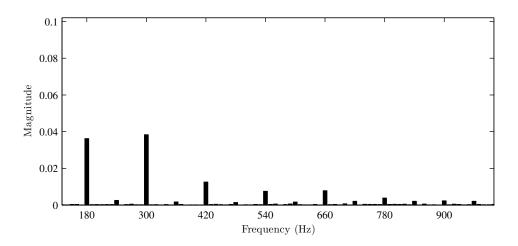

The Fourier spectrum is calculated on each of the three switching currents to determine the harmonic content of each. The spectra of all three currents is shown in Fig. 3.12. The harmonics are only shown up to 15th harmonic because the higher up harmonics can be attenuated with an input LC filter. The currents have a 180Hz component which is not normally possible in a balanced three phase system but is present because the converter is providing an unbalanced load. The 3rd and 5th harmonic are unbalanced and have a significant magnitude of 6%. The 7th up to 15th harmonics are unacceptable for IEEE-519 [52] specifications and are detrimental to the stability of the grid.

Figure 3.12: Current Harmonics

A solution to the harmonics and balancing of the load is needed before before hardware implementation.

#### 3.1.3 Balancing Currents and Reducing Harmonics

In three phase there are 6 distinct sectors. These sectors change when one of the voltage sources changes its voltage level respective to the other two sources. These six distinct sectors are shown in Fig. 3.13. In the first sector the voltage  $v_a$  is max,  $v_b$  is min, and  $v_c$  is mid. When  $v_b$  becomes greater than  $v_c$  the sector switches to sector two and  $v_b$  becomes mid,  $v_c$  becomes min, and  $v_a$  remains max. The duty ratios follow the input voltages and maintain this behaviour. The input currents during each of these six sectors will be investigated for the three phase currents.

The switching input currents under steady state are plotted for all three phases, for one switching cycle, in each of the six sectors, in Fig. 3.14. The current  $i_a$  has a notch missing in sector two and also in sector five. This notch is due to the phase shift of the two voltage waveforms  $v_1$  and  $v_2$  and the current through the leakage inductance L.

The current  $i_b$  has a notch missing in sector one, three, four, and six. The current  $i_c$  has a notch missing in sector one, two, three, four, five, and six. None of the three currents have notches in a determinable pattern and the notches are defiantly not balanced between the three phases.

Figure 3.13: Voltage Six Sectors

Figure 3.14: Input Current Sectors

One way to reduce the notches is to reduce the phase shift, but that is in contrast to power flow. If the allowable phase shift is reduced, then the available power flow reduces as well. Reducing the allowable phase shift is not a viable solution.

One solution is to switch the order in which the duty ratios are compared to the ramp, that way the notch comes out from each current the same amount of times irrespective of the sector. In the first switching cycle the switching signals would be generated as follows, when the ramp is less than  $d_{aA}$  then  $S_{aA}$  is on, otherwise, its off, when the ramp is greater than  $d_{aA}$  but less than  $d_{aA} + d_{bA}$  then  $S_{bA}$  is on, otherwise, its off, finally when the ramp is greater than  $d_{aA} + d_{bA}$  the switch  $S_{cA}$  is on other wise it is off. In the next switching cycle the switching signals would be generated as follows,

Figure 3.15: Average Three Phase Currents

when the ramp is less than  $d_{bA}$  then  $S_{bA}$  is on otherwise its off, when the ramp is greater than  $d_{bA}$  but less than  $d_{bA} + d_{aA}$  then  $S_{aA}$  is on otherwise its off, finally when the ramp is greater than  $d_{bA} + d_{aA}$  the switch  $S_{cA}$  is on other wise it is off. The first cycle is named abc and the second cycle is named bac because of the order in which they are compared to the ramp. The simulation is rerun with the same values but this time the duty ratios are compared in a different order each cycle. The duty ratios will be compared in a repeating six cycles. The six cycles in order are as follows, abc, bac, acb, cab, bca, and cba. The switching input current, average current, and input current harmonic content will be investigated for this new duty ratio switching scheme.

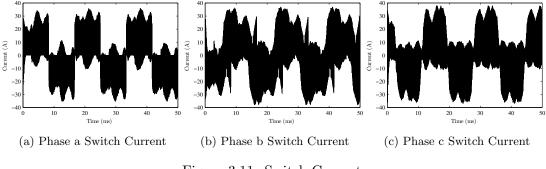

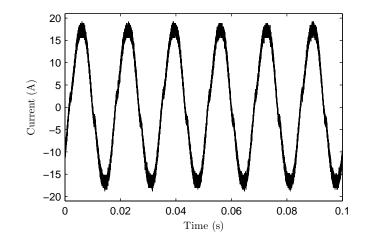

The average current for all three phases is presented in Fig. 3.15 using the duty ratio order swap. The average currents are now clearly balanced and sinusoidal. The average currents do contain some line frequency harmonics but they are perceived to be lower. The switching currents are plotted for all three phases in Fig. 3.16a, 3.16b, and 3.16c

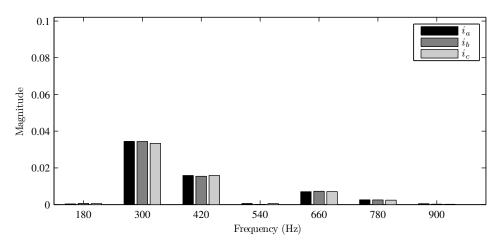

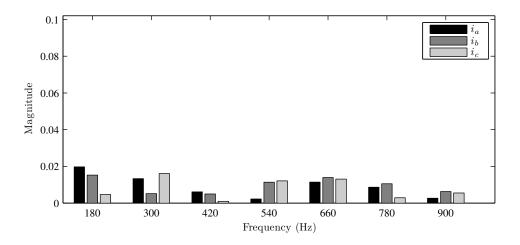

The switching currents for all three phases are balanced as well. The outline of the fundamental of 60Hz is easily observable in all three switching currents. The Fourier analysis is done on all three switching currents to determine the harmonic content of the input currents. The harmonic content of the input switching currents are normalized to the fundamental at 60Hz. The harmonic content of the three currents are shown in Fig. 3.17.

Figure 3.17: Input Current Harmonics

Clearly the third harmonic is gone from all three input switching currents contrary to the previous simulation where the harmonics were unbalanced and as high as 7% of the fundamental. The 5th harmonic is balanced and is less than 4% of the fundamental. The 7th harmonic is also balanced and less than 2% of the fundamental. The 9th harmonic is negligible compared to previously where it was 1-2% of the fundamental and unbalanced. The 11th harmonic is balanced and less that 1% of the fundamental. The 13th and 15th harmonic are negligible compared to 1% and unbalanced in case where the duty ratio comparison was done in the same order. The changing of the order in which the duty ratios are compared to the ramp resulted in a great reduction of the harmonics in the input currents. The input currents are balanced, the third, ninth, and fifteenth harmonic have been eliminated, and the harmonics in the fifth, seventh, eleventh, and thirteenth have been reduced.

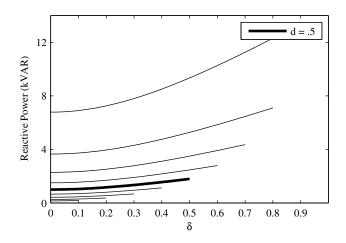

During simulation it was observed that the voltage level of the bus affects the magnitude of the harmonics. As the voltage of the bus increases and is farther from the average voltage applied at  $v_1$ ,  $3K_iV_i$ , the more the harmonics increase. The optimal value of the bus voltage is  $3K_iV_i$ .

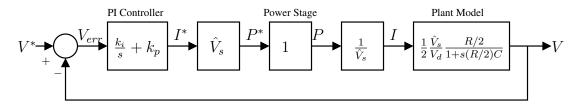

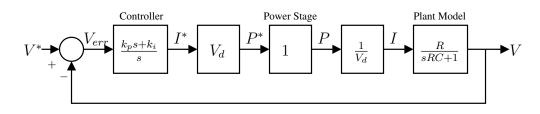

#### 3.1.4 Voltage Control

A voltage controller is designed to regulate the voltage at the DC bus. The RC network impedance is modelled in Eq. (3.19). The impedance gives the current to voltage transfer function. The controller will be designed to output a current reference which will be multiplied by the DC bus voltage to get a power command.

$$\frac{V(s)}{I(s)} = \frac{R}{sRC+1} \tag{3.19}$$

Figure 3.18: Three Phase Voltage Control Loop

The controller design is depicted in Fig. 3.18. A PI controller is selected as the controller and the plant is modelled as the impedance of the RC network (3.19). The power stage is considered to have a gain of one because the bandwidth of the controller will be smaller than the bandwidth of the power controller. The gains  $V_c$  and  $\frac{1}{V_c}$  are inserted to converter current to power command and power back to current. The controller gains  $k_i$  and  $k_p$  are found by selecting the bandwidth and phase margin, and solving the two equations (3.20) and (3.21).

$$\left|\frac{k_p s + k_i}{s} \frac{R}{sRC + 1}\right|_{s = j2\pi f_{co}} = 1 \tag{3.20}$$

$$\angle \left[\frac{k_p s + k_i}{s} \frac{R}{sRC + 1}\right]_{s = j2\pi f_{cp}} + 180 = \phi_{PM} \tag{3.21}$$

The values used to calculate the controller gains are shown in Table 3.3. The bandwidth is selected as 200Hz, and the phase margin is selected as 70 degrees.

| Parameter   | Value | Unit    |

|-------------|-------|---------|

| R           | 1     | Ohms    |

| C           | 200   | $\mu F$ |

| $f_{co}$    | 200   | Hz      |

| $\phi_{PM}$ | 70    | degrees |

Table 3.3: Voltage Control Loop Values

The calculated values of the controller gains are shown in Table 3.4.

| Parameter | Value  |

|-----------|--------|

| $k_i$     | 241.31 |

| $k_p$     | 0.2353 |

Table 3.4: Voltage Controller Gains

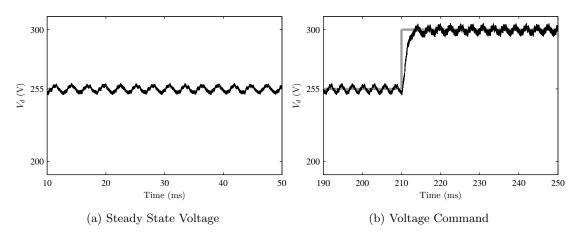

The controller is simulated on the actual system using MATLAB Simulink. The controller is given a voltage of command of 255 volts and the load is  $6.5\Omega$ . The steady state voltage is plotted in Fig. 3.19a. The DC bus voltage closely tracks the given voltage command.

At time 210ms the voltage controller is given a step command from 255 volts to 300 volts. The voltage command and actual voltage are plotted in Fig. 3.19b.

In most electric vehicles there is a bidirectional DC to DC converter between the DC bus and the battery. A more accurate simulation of actual conditions would be to change the load resistance at some instant of time and observe the voltage. The objective is to maintain the DC bus voltage constant irrespective of load.

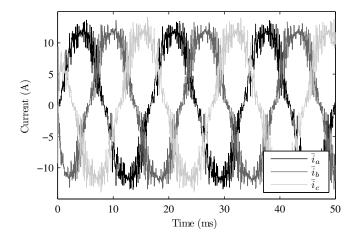

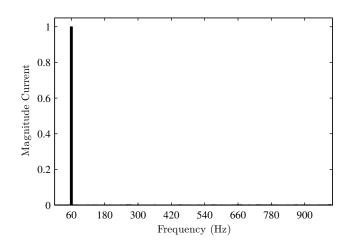

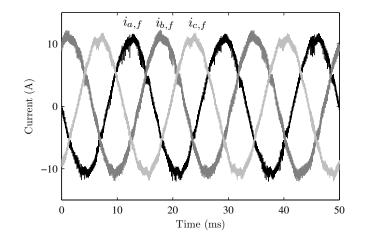

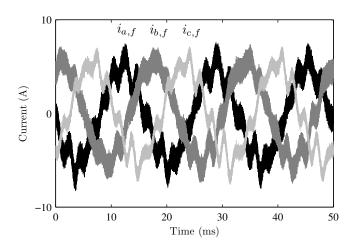

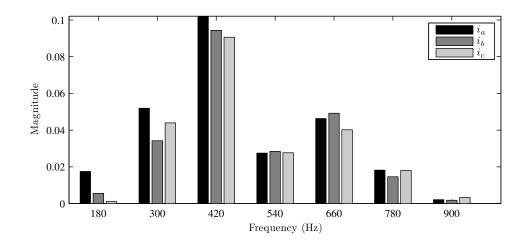

The input currents for a 10kW load, after the LC filter, are plotted in Fig. 3.20. The currents are sinusoidal, in phase with the input voltage, and contain harmonics but the magnitudes are with in IEEE-519 specifications. The current harmonics present in the

Figure 3.19: Capacitor Voltage

Figure 3.20: Filtered Currents for 10kW Load

inputs currents are shown in Fig. 3.21. The current contains 4% in the 5th harmonic and less than 1% in the 7th harmonic. The other line frequency harmonics are negligible. The total harmonic distortion in the current is 4.17%.

#### 3.1.5 Bidirectional Power Flow

The RC network in Fig. 3.1 is replaced by a DC source in order to simulate bidirectional power flow, as shown in Fig. 3.22.

Figure 3.21: Current Spectrum for 10kW Load

Figure 3.22: Bidirectional System Simulation

The RC network cannot be used when putting power back into the AC sources because the energy will be consumed by the resistor and putting power back into the grid, eventually decaying the capacitor to zero energy.

The DC source represents either a battery pack or a bidirectional DC to DC converter, between the battery pack and the DC bus, maintaining the voltage at a desired set point.

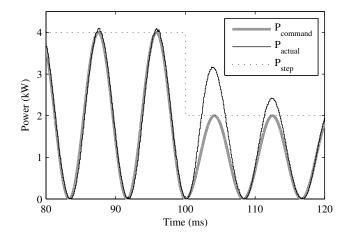

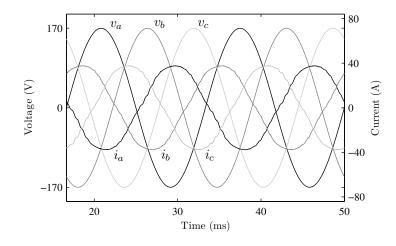

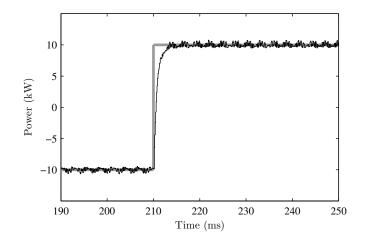

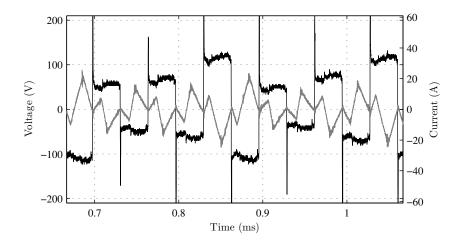

The system in Fig. 3.22 is simulated using only the power control loop with the values in Table 3.2. The DC bus is set to 255 Volts and the power controller is given a

-10kW command. The input voltages and currents after an LC filter are shown in Fig. 3.23.

Figure 3.23: Input Voltage and Filtered Current

The input currents are 180 degrees out of phase compared to the respective input voltages. The converter is providing 10kW of power from the DC to the AC sources. The input currents do contain some line frequency harmonics. The harmonic spectrum of the input current is shown for all three phases in Fig. 3.24.

Figure 3.24: Harmonic Content

The results are very similar to the charging 10kW simulation. The input currents

Figure 3.25: Power Step Command from -10kW to 10kW

contain zero third harmonic, 3.2% in the fifth harmonic, and 1.2% in the seventh harmonic. The higher harmonics are below 0.2% and negligible.

Finally a step power command from -10kW to 10kW is given to the controller in order to demonstrate the change from supplying power to the grid from the battery to charging the battery from the grid. The results of the step in power are shown in Fig. 3.25.

The actual power tracks the command and changes from supplying power to the grid to supplying power to the DC source from the grid. The converter can change modes from source to sink by a simple change of the power command.

### 3.2 Conclusion

In this chapter a control design was discussed and implemented for three phase input. A power controller was designed around the power systems model. It was shown that considering the model contained error with respect to the actual system, a properly designed PI controller is suitable for power control. The input current was analyzed and found to contain high line frequency harmonics and also contained unbalanced current harmonics. The source of the harmonics was discussed and a simple change to the strategy was implemented. After the modification to the strategy, the third and ninth harmonic are zero, the fifth, seventh, eleventh, and thirteenth are now balanced. The input currents still contain some harmonics but they are greatly reduced, below IEEE-519 specifications for harmonic content, and below total IEEE-519 THD requirements. The RC network was removed to demonstrate that the converter with the presented control strategy was capable of bidirectional power flow.

# Chapter 4

# Single-Phase Modulation using Dual Active Bridge Analysis

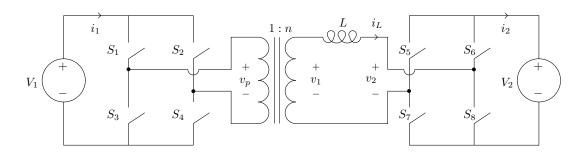

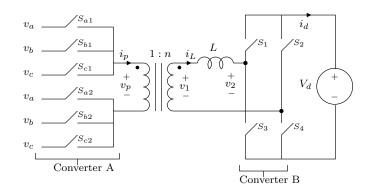

Figure 4.1: DC-DC Dual Active Bridge

This Chapter is put together with the collaboration of my colleagues Gysler and Kaushik. A paper, including this work, will be be submitted to a future conference.

### 4.1 Analysis

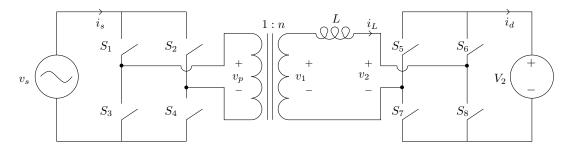

A DC to DC dual active bridge is depicted in Fig. 4.1. The magnetizing inductance of the transformer is neglected and the turns ratio is assumed to be 1:n. The leakage inductance of the transformer is lumped to the secondary side,  $L = L_p n^2 + L_s$ , for analysis.  $V_1$  and  $V_2$  and DC sources. In order to flow power between sources in a Dual Active Bridge, a square wave is applied to  $v_1$  and a phase shifted square wave is applied to  $v_2$ .

#### 4.1.1 DC - DC Dual Active Bridge Analysis

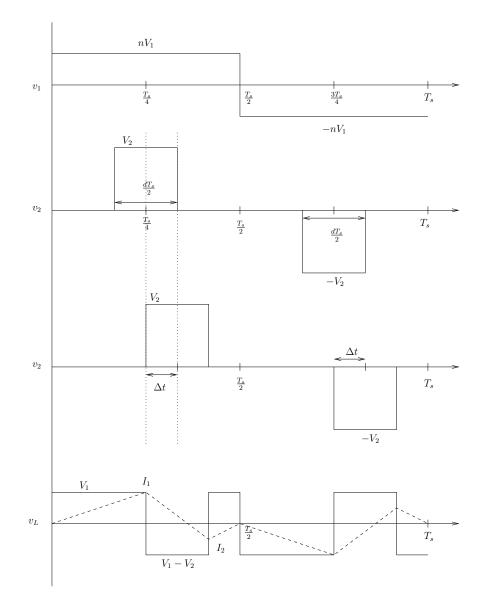

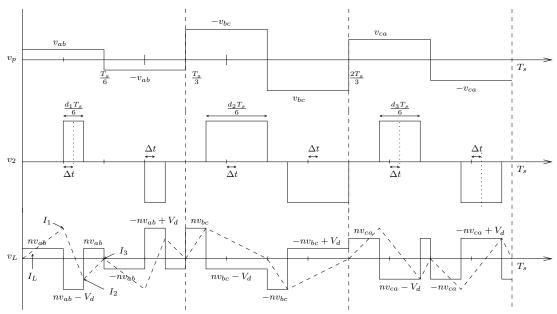

During the first  $T_s/2$  time period,  $S_1$  and  $S_4$  are closed,  $V_1$  is applied to  $v_p$  and  $nV_1$  is applied to  $v_1$ . During the second  $T_s/2$  time period,  $S_2$  and  $S_3$  are closed,  $-V_1$  is applied to  $v_p$  and  $-nV_1$  is applied to  $v_1$ . The two switching states are applied at a frequency of  $f_s$  and the waveform at  $v_1$  is shown in Fig. 4.2. The average voltage of  $v_2$  is synthesized to be equal to  $v_1$  during the time period of  $\frac{T_s}{2}$ . The width of the pulse at  $v_2$  is assigned the duty ratio in (4.1) and is depicted in the second waveform in Fig. 4.2. The leg with switches  $S_5$  and  $S_7$  are phase shifted from switches  $S_6$  and  $S_8$  in order to generate the duty ratio.

$$d = \frac{nV_1}{V_2} \tag{4.1}$$

In order to transfer power, the voltage waveform at  $v_2$  must be phase shifted from  $v_1$ . The phase shift in Fig. 4.1 is shown as  $\Delta t$  in the third waveform. Equation (4.2) imposes a condition on the maximum phase shift allowed to maintain the width of the  $v_2$  pulse within its respective  $T_s/2$  time period. Graphically it means that the pulse at  $v_2$  must stay inside the pulse at  $v_1$  as shown in Fig. 4.1. Equations (4.3) and (4.4) set up and impose the condition. Equation (4.3) defines the ratio  $\delta$  which is confined to -1 to 1 and controls the phase shift from -90 degrees to 90 degrees.

$$\frac{T_s}{4} + \Delta t + \frac{dT_s}{4} < \frac{T_s}{2} \tag{4.2}$$

$$\delta = \frac{\Delta t}{T_s/4} \tag{4.3}$$

$$|\delta| < 1 - d \tag{4.4}$$

In Fig. 4.2,  $v_L$  and the current in the inductor  $i_L$  are plotted for a phase shift of  $\Delta t$ . Assuming an initial condition of zero current through the inductor, the currents  $I_1$ ,  $I_2$ , and  $I_3$  are calculated in (4.5), (4.6), and (4.7).

$$I_1 = \frac{nV_1}{L} \left( \frac{T_s}{4} + \Delta t - \frac{dT_s}{4} \right) \tag{4.5}$$

J

$$I_2 = I_1 + \frac{nV_1 - V_2}{L} \frac{dT_s}{2}$$

(4.6)

Figure 4.2: DC-DC DAB Plots

$$I_{3} = I_{2} + \frac{nV_{1}}{L} \left(\frac{T_{s}}{4} - \Delta t - \frac{dT_{s}}{4}\right)$$

(4.7)

51