### Using Hardware Performance Events for Instruction-Level Monitoring on the x86 Architecture

#### Sebastian Vogl and Claudia Eckert {vogls,eckertc}@in.tum.de

Chair for IT Security Technische Universität München Munich, Germany

#### 10.04.2012

S. Vogl and C. Eckert (TUM)

10.04.2012 1/42

- Performance Monitoring Counters (PMCs)

- 8 PMC-based Instruction-level Monitoring (ILM)

- 4 Experiments & Results

### 5 Summary

- 2 Performance Monitoring Counters (PMCs)

- 3 PMC-based Instruction-level Monitoring (ILM)

- 4 Experiments & Results

### 5 Summary

• • • • • • • • • • • • •

### My Research

# Make use of full hardware virtualization to detect malware infections and **exploitation attempts**.

S. Vogl and C. Eckert (TUM)

10.04.2012 4 / 42

(I) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1))

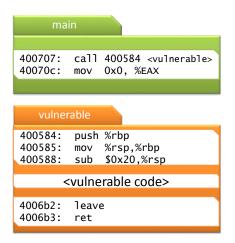

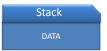

#### ▶ Why Instructions-Level Monitoring (ILM) ?

#### ▶ Why Instructions-Level Monitoring (ILM) ?

S. Vogl and C. Eckert (TUM)

#### ▶ Why Instructions-Level Monitoring (ILM) ?

#### Why Instructions-Level Monitoring (ILM) ?

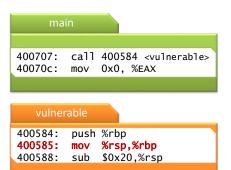

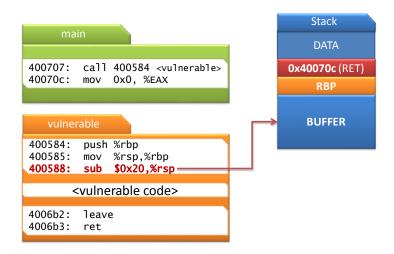

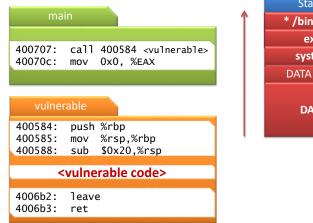

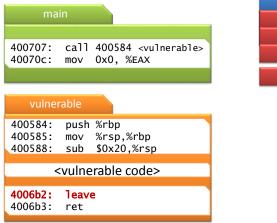

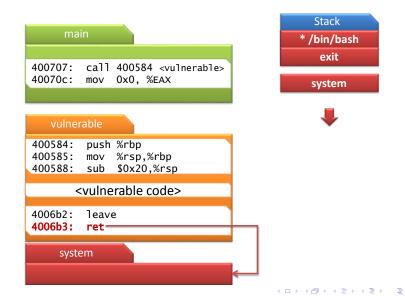

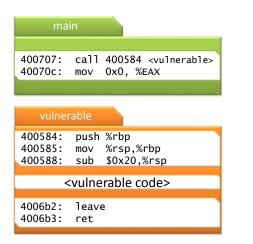

### <vulnerable code>

4006b2: leave 4006b3: ret

#### ▶ Why Instructions-Level Monitoring (ILM) ?

#### Why Instructions-Level Monitoring (ILM) ?

イロト イヨト イヨト イヨト

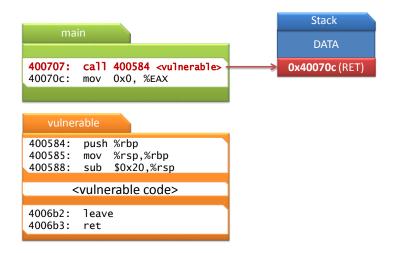

#### ▶ Why Instructions-Level Monitoring (ILM) ?

#### Why Instructions-Level Monitoring (ILM) ?

S. Vogl and C. Eckert (TUM)

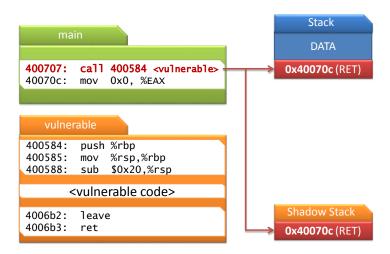

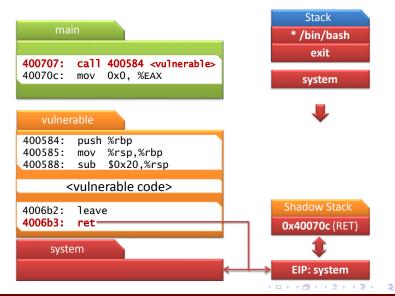

#### **One possible Solution**

Make use of a Shadow Stack to verify the target of return instructions.

S. Vogl and C. Eckert (TUM)

10.04.2012 13 / 42

• • • • • • • • • • • • • •

#### Why Instructions-Level Monitoring (ILM) ?

Shadow Stack

#### Why Instructions-Level Monitoring (ILM) ?

S. Vogl and C. Eckert (TUM)

#### Why Instructions-Level Monitoring (ILM) ?

S. Vogl and C. Eckert (TUM)

A Shadow Stack for **return addresses** can be implemented on the **hypervisor-level** by only trapping call and return instructions.

• • • • • • • • • • • •

10.04.2012

17/42

A Shadow Stack for **return addresses** can be implemented on the **hypervisor-level** by only trapping call and return instructions.

### **ILM Requirements**

Based on full hardware virtualization

A Shadow Stack for **return addresses** can be implemented on the **hypervisor-level** by only trapping call and return instructions.

### **ILM Requirements**

- Based on full hardware virtualization

- 2 Secure

A Shadow Stack for **return addresses** can be implemented on the **hypervisor-level** by only trapping call and return instructions.

### **ILM Requirements**

- Based on full hardware virtualization

- 2 Secure

- Flexible

• • • • • • • • • • • •

Why a new ILM mechanism?

### **Existing Approaches**

- Page-Fault (PF)-based ILM

- Obug Register (DR)-based ILM

- Trap Flag (TF)-based ILM

▶ Why a new ILM mechanism?

### **Existing Approaches**

- Page-Fault (PF)-based ILM

- Obug Register (DR)-based ILM

- Trap Flag (TF)-based ILM

< 4 →

▶ Why a new ILM mechanism?

### **Existing Approaches**

- Page-Fault (PF)-based ILM

- Obug Register (DR)-based ILM

- Trap Flag (TF)-based ILM

- Insecure

< 4 →

▶ Why a new ILM mechanism?

### **Existing Approaches**

- Page-Fault (PF)-based ILM

- Obbug Register (DR)-based ILM

- Trap Flag (TF)-based ILM

- Insecure

- Incomplete

A D M A A A M M

▶ Why a new ILM mechanism?

### **Existing Approaches**

- Page-Fault (PF)-based ILM

- Obbug Register (DR)-based ILM

- Trap Flag (TF)-based ILM

- Insecure

- Incomplete

- Inflexible

(I) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1))

▶ Why a new ILM mechanism?

#### **Existing Approaches**

- Page-Fault (PF)-based ILM

- Obug Register (DR)-based ILM

- Trap Flag (TF)-based ILM

- Insecure

- Incomplete

- Inflexible

$\Rightarrow$  None of the existing methods can provide the desired **flexbility**.

- Performance Monitoring Counters (PMCs)

- 3 PMC-based Instruction-level Monitoring (ILM)

- 4 Experiments & Results

- 5 Summary

• • • • • • • • • • • • •

Overview

### Performance Monitoring on the x86 architecture

Performance Events

S. Vogl and C. Eckert (TUM)

10.04.2012 21 / 42

• • • • • • • • • • • • • •

Overview

### Performance Monitoring on the x86 architecture

- Performance Events

- PMCs that count these events

S. Vogl and C. Eckert (TUM)

10.04.2012 21 / 42

• • • • • • • • • • • •

Overview

### Performance Monitoring on the x86 architecture

- Performance Events

- PMCs that count these events

- Which event is counted can be programmed.

A (10) F (10)

Overview

### Performance Monitoring on the x86 architecture

- Performance Events

- PMCs that count these events

- Which event is counted can be programmed.

- Can be set to raise an interrupt on overflow.

Performance Events

- All instructions

- All branch instructions

- All conditional branch instructions

- All near call instructions

- All near return instructions

- All **far branch** instructions

- A 🖻 🕨

- 2 Performance Monitoring Counters (PMCs)

- 8 PMC-based Instruction-level Monitoring (ILM)

- Experiments & Results

### 5 Summary

• • • • • • • • • • • •

### PMC-based Instruction-level Monitoring (ILM)

Trapping Performance Events

#### Question

How can we trap performance events to the hypervisor?

S. Vogl and C. Eckert (TUM)

10.04.2012 24 / 42

### PMC-based Instruction-level Monitoring (ILM)

Trapping Performance Events

#### Question

How can we trap performance events to the hypervisor?

### Challenges

Interrupt Generation: Generate an interrupt whenever the desired hardware performance event occurs.

イロン イ理 とくほとく ほ

### PMC-based Instruction-level Monitoring (ILM)

Trapping Performance Events

#### Question

How can we trap performance events to the hypervisor?

### Challenges

- Interrupt Generation: Generate an interrupt whenever the desired hardware performance event occurs.

- Ontrol Transfer: The emitted interrupt must lead to a VM Exit.

イロト イ団ト イヨト イヨト

Trapping Performance Events: Signal Generation

Set the PMC initially to

#### MAX\_PMC\_VALUE - X + 1

where X is the number of events that should occur before the interrupt.

10.04.2012

25/42

S. Vogl and C. Eckert (TUM)

▶ Trapping Performance Events: Signal Generation

Set the PMC initially to

#### MAX\_PMC\_VALUE - X + 1

where X is the number of events that should occur before the interrupt.

$\Rightarrow$  PMC will overflow after the desired number of events.

▶ Trapping Performance Events: Signal Generation

Set the PMC initially to

#### MAX\_PMC\_VALUE - X + 1

where X is the number of events that should occur before the interrupt.

- $\Rightarrow$  PMC will overflow after the desired number of events.

- $\Rightarrow$  An Interrupt will be generated.

Trapping Performance Events: Control Transfer

## **Interrupt Generation**

• The type of interrupt that is generated depends on the settings within the local Advanced Programmable Interrupt Controller (APIC).

< □ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □

Trapping Performance Events: Control Transfer

## **Interrupt Generation**

- The type of interrupt that is generated depends on the settings within the local Advanced Programmable Interrupt Controller (APIC).

- It is possible to generate a Nonmaskable Interrupt (NMI).

- NMIs lead to a VM Exit if the appropriate flag is set.

< □ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □

Trapping Performance Events: Control Transfer

## **Interrupt Generation**

- The type of interrupt that is generated depends on the settings within the local Advanced Programmable Interrupt Controller (APIC).

- It is possible to generate a Nonmaskable Interrupt (NMI).

- NMIs lead to a VM Exit if the appropriate flag is set.

- NMIs are immediately handled by the processor.

< □ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □

Trapping Performance Events: Control Transfer

### **Interrupt Generation**

- The type of interrupt that is generated depends on the settings within the local Advanced Programmable Interrupt Controller (APIC).

- It is possible to generate a Nonmaskable Interrupt (NMI).

- NMIs lead to a VM Exit if the appropriate flag is set.

- NMIs are immediately handled by the processor.

## **Problem: Interrupt Delivery**

There is a gap of time between the occurrence of a performance event and the interrupt delivery.

(I) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1))

Trapping Performance Events: Control Transfer

#### **Interrupt Generation**

- The type of interrupt that is generated depends on the settings within the local Advanced Programmable Interrupt Controller (APIC).

- It is possible to generate a Nonmaskable Interrupt (NMI).

- NMIs lead to a VM Exit if the appropriate flag is set.

- NMIs are immediately handled by the processor.

## **Problem: Interrupt Delivery**

- There is a gap of time between the occurrence of a performance event and the interrupt delivery.

- Other performance events may go unnoticed during this period of time.

Trapping Performance Events: Control Transfer

### **Interrupt Generation**

- The type of interrupt that is generated depends on the settings within the local Advanced Programmable Interrupt Controller (APIC).

- It is possible to generate a Nonmaskable Interrupt (NMI).

- NMIs lead to a VM Exit if the appropriate flag is set.

- NMIs are immediately handled by the processor.

## **Problem: Interrupt Delivery**

- There is a gap of time between the occurrence of a performance event and the interrupt delivery.

- Other performance events may go unnoticed during this period of time.

- Problem has to be solved on a case-by-case basis.

イロト イヨト イヨト イヨト

Instruction Reconstruction (IR)

#### Problem

- The number of selected instructions that are executed during interrupt delivery depend on the event that we monitor.

- If we set a PMC to count every instruction, about **6** instructions will be executed on the average before the interrupt is acknowledged.

Instruction Reconstruction (IR)

#### Problem

- The number of selected instructions that are executed during interrupt delivery depend on the event that we monitor.

- If we set a PMC to count every instruction, about **6** instructions will be executed on the average before the interrupt is acknowledged.

## Solution

The PMC will keep counting after an overflow occurred.

- ⇒ We know exactly how many instructions were executed before the interrupt was acknowledged.

- Reconstruct the instruction stream and obtain the instructions that we missed.

< □ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □

Instruction Reconstruction (IR)

### Approach

- Save the value of the instruction pointer on every overflow.

- Check the value of the PMC on overflow to determine how many instructions were missed if any.

- Oisassemble every instruction starting from the last saved instruction pointer till we reach the current instruction pointer.

|   | Example            |                          |                                                                    |

|---|--------------------|--------------------------|--------------------------------------------------------------------|

| 1 | 40f448: <b>mov</b> | %r12,%rdi                | ;                                                                  |

| 2 | 40f44b: <b>mov</b> | \$0x20,% <b>esi</b>      |                                                                    |

| 3 | 40f450: <b>mov</b> | %rbp,%rdx                |                                                                    |

| 4 | 40f453: <b>mov</b> | % <b>ecx</b> ,0x28(%rsp) |                                                                    |

| 5 | 40f457: <b>mov</b> | %r8b,0x10(%rsp)          |                                                                    |

| 6 | 40f45c: <b>mov</b> | %r9,0x20(%rsp)           |                                                                    |

| 7 | 40f461: <b>add</b> | %rbp,%r12                | ; <===== CURRENT EIP                                               |

|   |                    | •                        | ·<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・<br>・ |

10.04.2012

28/42

Instruction Reconstruction (IR)

#### What about branches?

| 1 | 40f24e: pop | %r12 |

|---|-------------|------|

| 2 | 40f250: pop | %r13 |

| 3 | 40f252: pop | %r14 |

| 4 | 40f254: pop | %r15 |

| 5 | 40f256: ret |      |

| ; <===== LAST EIP |

|-------------------|

|-------------------|

#### Problem

The target of a branch may depend on a memory operand that may have been overwritten in the meantime.

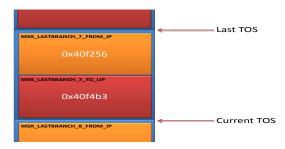

The Last Branch Record (LBR) Stack

## LBR Stack

- Records the last taken branches

- Set of MSRs

- A top-of-stack (TOS) pointer (MSR\_LASTBRANCH\_TOS)

- A pair of MSRs for each branch that the stack can record: MSR\_LASTBRANCH\_x\_FROM\_IP ⇒ MSR\_LASTBRANCH\_x\_TO\_LIP

- The size of the LBR stack depends on the microarchitecture

The Last Branch Record (LBR) Stack

## LBR Stack

- Records the last taken branches

- Set of MSRs

- A top-of-stack (TOS) pointer (MSR\_LASTBRANCH\_TOS)

- A pair of MSRs for each branch that the stack can record: MSR\_LASTBRANCH\_x\_FROM\_IP ⇒ MSR\_LASTBRANCH\_x\_TO\_LIP

- The size of the LBR stack depends on the microarchitecture

- $\Rightarrow$  Save the TOS pointer on each monitoring related interrupt.

The Last Branch Record (LBR) Stack

## LBR Stack

- Records the last taken branches

- Set of MSRs

- A top-of-stack (TOS) pointer (MSR\_LASTBRANCH\_TOS)

- A pair of MSRs for each branch that the stack can record: MSR\_LASTBRANCH\_x\_FROM\_IP ⇒ MSR\_LASTBRANCH\_x\_TO\_LIP

- The size of the LBR stack depends on the microarchitecture

- $\Rightarrow$  Save the TOS pointer on each monitoring related interrupt.

All taken branches are recorded between the last saved TOS and the current TOS.

< 同 ト < 三 ト < 三 ト

#### Instruction Reconstruction (IR)

#### Using the LBR Stack

| 1 | 40f24e: <b>pop</b> | %r12      | ;                    |

|---|--------------------|-----------|----------------------|

| 2 | 40f250: pop        | %r13      |                      |

| 3 | 40f252: <b>pop</b> | %r14      |                      |

| 4 | 40f254: pop        | %r15      |                      |

| 5 | 40f256: ret        |           |                      |

| 6 |                    |           |                      |

| 7 | 40f4b3: <b>mov</b> | %r12,%rdi | ; <===== CURRENT EIP |

|   |                    |           | ◆□▶ ◆□▶ ◆臣▶ ◆臣       |

### ==== LAST EIP

#### S. Vogl and C. Eckert (TUM)

イロト イ理ト イヨト イヨト

What about security?

- PMCs are MSRs

- All PMC control structures are MSRs as well

- Read/Write accesses to MSRs can be intercepted from the hypervisor

- $\Rightarrow$  An attacker cannot disable or manipulate the PMCs.

## Motivation

- 2 Performance Monitoring Counters (PMCs)

- 3 PMC-based Instruction-level Monitoring (ILM)

## Experiments & Results

## 5 Summary

- Experiments

- Monitored four common Linux applications at the instruction-level:

- ► Is (Argument: /usr/bin, 597 files)

- tar (Argument: Hello World.c, 10 LOC)

- cat (Argument: Hello World.c, 10 LOC)

- gcc (Argument: Hello World.c, 10 LOC)

(I) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1))

- Experiments

- Monitored four common Linux applications at the instruction-level:

- Is (Argument: /usr/bin, 597 files)

- tar (Argument: Hello World.c, 10 LOC)

- cat (Argument: Hello World.c, 10 LOC)

- gcc (Argument: Hello World.c, 10 LOC)

- Each application was executed multiple times using different monitoring modes:

- PMC ALL & IR: All instructions & Instruction Reconstruction

- TF ALL: All instructions

- PMC ALL: All instructions without Instruction Reconstruction

- PMC Branches: All branch instructions

- PMC Shadow Stack: Only call & return instructions

A (10) > A (10) > A (10)

- Experiments

- Monitored four common Linux applications at the instruction-level:

- ► Is (Argument: /usr/bin, 597 files)

- tar (Argument: Hello World.c, 10 LOC)

- cat (Argument: Hello World.c, 10 LOC)

- gcc (Argument: Hello World.c, 10 LOC)

- Each application was executed multiple times using different monitoring modes:

- PMC ALL & IR: All instructions & Instruction Reconstruction

- TF ALL: All instructions

- PMC ALL: All instructions without Instruction Reconstruction

- PMC Branches: All branch instructions

- PMC Shadow Stack: Only call & return instructions

- Measured the execution time from the hypervisor for each run

- Calculated the average slowdown factor

Results

| Mode             | ls         | tar         | cat        | gcc        |

|------------------|------------|-------------|------------|------------|

| PMC ALL & IR     | 755 (18s)  | 1002 (3.0s) | 334 (0.6s) | 1263 (92s) |

| TF ALL           | 310 (7.0s) | 415 (1.2s)  | 142 (0.3s) | 545 (40s)  |

| PMC ALL          | 273 (6.5s) | 403 (1.2s)  | 126 (0.3s) | 435 (32s)  |

| PMC Branches     | 163 (4.0s) | 259 (0.8s)  | 81 (0.2s)  | 281 (21s)  |

| PMC Shadow Stack | 95 (2.0s)  | 196 (0.6s)  | 31 (0.1s)  | 212 (15s)  |

Improving the Performance

#### Improving the Performance

The performance of the approach heavily depends on the number of the VM Exists.

< 17 ▶

Improving the Performance

#### Improving the Performance

- The performance of the approach heavily depends on the number of the VM Exists.

- The performance will increase by almost the same factor as the VM Exits are decreased.

Improving the Performance

#### Improving the Performance

- The performance of the approach heavily depends on the number of the VM Exists.

- The performance will increase by almost the same factor as the VM Exits are decreased.

- Possible Approaches

- Precise Event Based Sampling (PEBS)

- Branch Trace Store (BTS)

- E 🕨

Improving the Performance

#### Improving the Performance

- The performance of the approach heavily depends on the number of the VM Exists.

- The performance will increase by almost the same factor as the VM Exits are decreased.

- Possible Approaches

- Precise Event Based Sampling (PEBS)

- Branch Trace Store (BTS)

#### Security

The overall security of the mechanisms will decrease if the VM Exits are reduced.

## Motivation

- 2 Performance Monitoring Counters (PMCs)

- 3 PMC-based Instruction-level Monitoring (ILM)

- 4 Experiments & Results

## Summary

## Contributions

- PMC-based trapping

- A flexible and secure ILM mechanism

- Instruction Reconstruction

э

## Summary

## Contributions

- PMC-based trapping

- A flexible and secure ILM mechanism

- Instruction Reconstruction

## Performance

- The proposed ILM mechanism still leads to significant overhead.

- However, the mechanism can be significantly faster than existing hardwared-based mechanism on the x86 architecture.

- There is still a lot of room for improvements.

- More detailed experiments are needed.

< □ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □

## Contributions

- PMC-based trapping

- A flexible and secure ILM mechanism

- Instruction Reconstruction

## Performance

- The proposed ILM mechanism still leads to significant overhead.

- However, the mechanism can be significantly faster than existing hardwared-based mechanism on the x86 architecture.

- There is still a lot of room for improvements.

- More detailed experiments are needed.

→ We encourage other researchers to explore the possibilities of **PMC-based trapping** as well as **PMC-based ILM**.

▲ ■

■

• ●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

イロト イヨト イヨト イヨト

Lucas Davi, Ahmad-Reza Sadeghi, and Marcel Winandy. Ropdefender: a detection tool to defend against return-oriented programming attacks.

In Proceedings of the 6th ACM Symposium on Information, Computer and Communications Security, 2011.

- Artem Dinaburg, Paul Royal, Monirul Sharif, and Wenke Lee. Ether: Malware Analysis via Hardware Virtualization Extensions. In Proceedings of the 15th ACM conference on Computer and Communications Security, 2008.

- Tal Garfinkel, Keith Adams, and Andrew Warfield. Compatibility is not transparency.

In Proceedings of the 11th Workshop on Hot Topics in Operating Systems, 2007.

#### Intel Corporation.

Intel 64 and IA-32 Architectures Software Developer's Manual Volume 3: System Programming Guide, 2011.

Corey Malone, Mohamed Zahran, and Ramesh Karri. Are hardware performance counters a cost effective way for integrity checking of programs.

In Proceedings of the sixth ACM workshop on Scalable Trusted Computing, 2011.

Jonas Pfoh, Christian Schneider, and Claudia Eckert. Exploiting the x86 Architecture to Derive Virtual Machine State Information.

In Proceedings of the fourth international conference on Emerging Security Information, Systems and Technologies, 2010.

(I) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1)) < ((1))

Jonas Pfoh, Christian Schneider, and Claudia Eckert. Nitro: Hardware-based System Call Tracing for Virtual Machines. *Advances in Information and Computer Security*, 2011.