# USING SOFTWARE TRANSACTIONAL MEMORY IN INTERRUPT-DRIVEN SYSTEMS

by

MICHAEL J. SCHULTZ, B.S.

A Thesis submitted to the Faculty of the Graduate School, Marquette University, in Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE IN COMPUTER SCIENCE

Milwaukee, Wisconsin, USA

May 2009

#### Abstract

Transactional memory presents a new concurrency control mechanism to handle synchronization between shared data. Dealing with concurrency issues has always been a difficulty when writing operating system software and using transactions aims to simplify matters. This thesis presents a framework for understanding how interrupt-driven device drivers can benefit from using transactional memory. A method for integrating software transactional memory (STM) into an operating system kernel is also developed and applied. This kernel uses STM over hardware transactional memory (HTM) because HTM requires modifications only implemented in simulated systems. By using STM, it is possible to build upon existing kernels and deploy operating systems onto commodity machines with communication peripherals.

At the core is a modernized version of the Embedded Xinu operating system that has been ported to the Intel IA-32 architecture and modified to use a publicly available, production quality compiler and STM library available from Intel Corporation. The implementation of the Embedded Xinu kernel required several modifications to make use of the transactions offered by a library designed for use with user-level threads executing in Linux. Integrating the STM library into the kernel presents several challenges when dealing with a system that allows interrupts to enter at any time. By using transactions in device drivers, synchronization can be performed automatically and with greater granularity than traditional synchronizations methods. This may be used to to reduce the jitter—variations in interrupt handling—occurring in interrupt-driven device drivers when sharing data between the upper and lower halves, however this implementation does not show any conclusive results.

This thesis discusses and presents the prototype implementation of "Transactional Xinu." The prototype runs on standard hardware that exists today and provides a framework for future experimentation.

# Acknowledgments

Many thanks are due to the people who have been involved with me and this thesis over the past few years, so I would like to give thanks to the following people:

- Dennis Brylow, my imperious leader, a great researcher, friend, and advisor who gave me the opportunity to work on this interesting project;

- Praveen Madiraju and Craig Struble, my two committee members from Marquette who succeeded in pushing me to finish on time;

- Adam Welc, my external committee member who, despite living two timezones away, provided crucial support in integrating Intel's STM library with Embedded Xinu;

- Timothy Blattner, Aaron Gember, Paul Hinze, Adam Koehler, Zachary Lund, Adam Mallen, Mohammad "Meraj" Molla, Justin Picotte, and everyone else affiliated with the systems laboratory for listening to me and providing 100% awesome entertainment;

- My parents, Charles and Theresa, for offering support when I needed it; my sister and brotherin-law, Jennifer and Stefan, for giving me a place to sleep when I needed a break; and the rest of my family for not mocking me too much as I continue my educational endeavors; and finally,

- Lyndsie Schwanebeck, my fiancée and best friend, for her understanding when I worked late, constant support, and persistent belief that I could finish successfully and on time.

# Contents

|   |                                                                    | of Figures                                                                                                                                                                                                                                                                                             | iv                                                                                                                                             |

|---|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   | List                                                               | of Terminology                                                                                                                                                                                                                                                                                         | v                                                                                                                                              |

| 1 | Intro                                                              | oduction                                                                                                                                                                                                                                                                                               | 1                                                                                                                                              |

|   | 1.1                                                                | Thesis Statement                                                                                                                                                                                                                                                                                       | 1                                                                                                                                              |

|   | 1.2                                                                | Overview                                                                                                                                                                                                                                                                                               | 1                                                                                                                                              |

|   | 1.3                                                                | Operating Systems                                                                                                                                                                                                                                                                                      | 2                                                                                                                                              |

|   |                                                                    | 1.3.1 Interrupt-Driven Systems                                                                                                                                                                                                                                                                         | 3                                                                                                                                              |

|   | 1.4                                                                | Contributions                                                                                                                                                                                                                                                                                          | 4                                                                                                                                              |

| 2 | Rela                                                               | ited Work                                                                                                                                                                                                                                                                                              | 6                                                                                                                                              |

| - | 2.1                                                                | Atomic Regions                                                                                                                                                                                                                                                                                         | 6                                                                                                                                              |

|   | 2.2                                                                | Transactional Memory                                                                                                                                                                                                                                                                                   | 7                                                                                                                                              |

|   |                                                                    | 2.2.1 Hardware Transactional Memory                                                                                                                                                                                                                                                                    | 8                                                                                                                                              |

|   |                                                                    | 2.2.2 Software Transactional Memory                                                                                                                                                                                                                                                                    | 9                                                                                                                                              |

|   |                                                                    | 2.2.3 Hybrid Transactional Memory                                                                                                                                                                                                                                                                      | 10                                                                                                                                             |

|   | 2.3                                                                | Operating Systems                                                                                                                                                                                                                                                                                      | 10                                                                                                                                             |

|   | 2.4                                                                | Tools                                                                                                                                                                                                                                                                                                  | 11                                                                                                                                             |

|   | 2.5                                                                | Summary of Related Work                                                                                                                                                                                                                                                                                | 12                                                                                                                                             |

|   |                                                                    |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                |

| 3 | Frar                                                               | nework                                                                                                                                                                                                                                                                                                 | 14                                                                                                                                             |

| 3 |                                                                    | nework<br>Device Driver Structure                                                                                                                                                                                                                                                                      | 14<br>15                                                                                                                                       |

| 3 | 3.1                                                                | Device Driver Structure                                                                                                                                                                                                                                                                                | 15                                                                                                                                             |

| 3 | 3.1<br>3.2                                                         | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16                                                                                                                                       |

| 3 | 3.1<br>3.2<br>3.3                                                  | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17                                                                                                                                 |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                                           | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17<br>19                                                                                                                           |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                    | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17<br>19<br>19                                                                                                                     |

|   | 3.1<br>3.2<br>3.3<br>3.4                                           | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17<br>19<br>19<br>20                                                                                                               |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Imp                      | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17<br>19<br>19<br>20<br><b>22</b>                                                                                                  |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br><b>Imp</b><br>4.1        | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17<br>19<br>20<br>20<br><b>22</b><br>22                                                                                            |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Imp                      | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17<br>19<br>20<br>22<br>22<br>22                                                                                                   |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br><b>Imp</b><br>4.1        | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17<br>19<br>20<br>22<br>22<br>22<br>22<br>23                                                                                       |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br><b>Imp</b><br>4.1        | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17<br>19<br>20<br><b>22</b><br>22<br>22<br>22<br>23<br>27                                                                          |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br><b>Imp</b><br>4.1        | Device Driver Structure                                                                                                                                                                                                                                                                                | <ol> <li>15</li> <li>16</li> <li>17</li> <li>19</li> <li>20</li> <li>22</li> <li>22</li> <li>22</li> <li>23</li> <li>27</li> <li>28</li> </ol> |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br><b>Imp</b><br>4.1        | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17<br>19<br>20<br><b>22</b><br>22<br>22<br>23<br>27<br>28<br>28                                                                    |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br><b>Imp</b><br>4.1<br>4.2 | Device Driver StructureCritical SectionsInterrupt HandlingProgramming considerationsNon-Transactional Input/OutputSummary of FrameworkIementation NotesOriginal SystemTransactional System4.2.1Transactional Library4.2.2Interrupt-local storage4.2.3Additional ComponentsTransactional Device Drivers | 15<br>16<br>17<br>19<br>20<br><b>22</b><br>22<br>22<br>23<br>27<br>28<br>28<br>30                                                              |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br><b>Imp</b><br>4.1<br>4.2 | Device Driver Structure                                                                                                                                                                                                                                                                                | 15<br>16<br>17<br>19<br>20<br><b>22</b><br>22<br>22<br>23<br>27<br>28<br>28                                                                    |

| 5  | Performance Analysis                |                                 |    |  |  |

|----|-------------------------------------|---------------------------------|----|--|--|

|    | 5.1                                 | Measurements                    | 34 |  |  |

|    | 5.2                                 | Ethernet Device                 | 35 |  |  |

|    |                                     | 5.2.1 Ping Testing Methodology  | 35 |  |  |

|    |                                     | 5.2.2 Timing Test Methodology   | 40 |  |  |

|    | 5.3                                 | Summary of Performance Analysis | 41 |  |  |

| 6  | Sum                                 | nmary and Future Work           | 43 |  |  |

|    | 6.1                                 | Summary                         | 43 |  |  |

|    | 6.2                                 | Future Work                     | 46 |  |  |

| Bi | bliogr                              | raphy                           | 49 |  |  |

| A  | Ethe                                | ernet Read Source Listing       | 54 |  |  |

| B  | Ethe                                | ernet Write Source Listing      | 56 |  |  |

| С  | Ethernet Interrupt Source Listing 5 |                                 |    |  |  |

# **List of Figures**

| 1.1 | Example of a potentially unsafe memory access                            | 4  |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | Code from Figure 1.1 in MIPS assembly                                    | 4  |

| 3.1 | Logical separation of device driver halves                               | 15 |

| 3.2 | Circular deadlock caused by incorrect lock acquisition                   | 16 |

| 3.3 | Jitter introduced by disabled interrupts                                 | 18 |

| 4.1 | Code segment showing transactional to SGLA semantics                     | 24 |

| 4.2 | Reader and writer code examples                                          | 25 |

| 4.3 | POSIX Thread API under Transactional Xinu                                | 28 |

| 4.4 | Code snippet without synchronization                                     | 29 |

| 4.5 | Code snippet using traditional synchronization                           | 29 |

| 4.6 | Code snippet using transactional memory                                  | 30 |

| 4.7 | Transactional version of upper half Ethernet device                      | 30 |

| 4.8 | Transactional version of lower half Ethernet device                      | 30 |

| 4.9 | Kernel code size overhead incurred, in bytes                             | 32 |

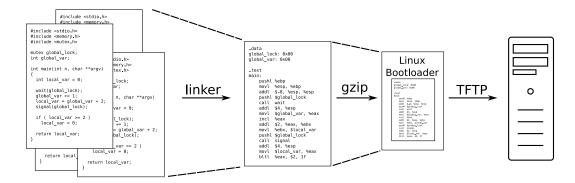

| 5.1 | Transferring the Transactional Xinu kernel to the back-end machine       | 34 |

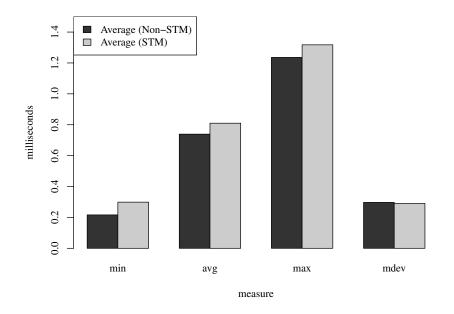

| 5.2 | Ping results after 100 pings with a 1000 millisecond interval            | 37 |

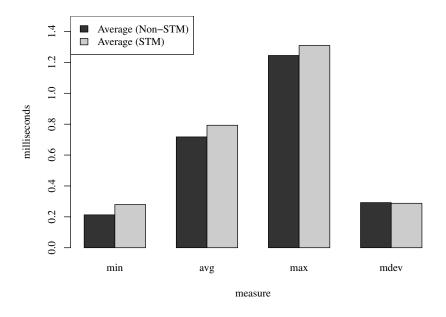

| 5.3 | Ping results after 100 pings with a 500 millisecond interval             | 37 |

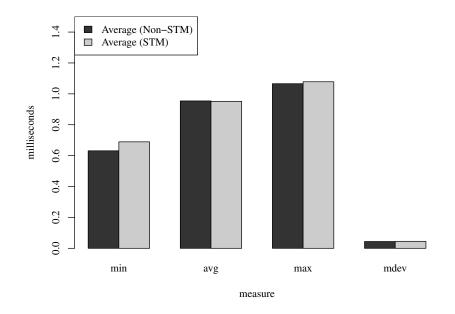

| 5.4 | Ping results after 100 pings with a minimal interval (flood ping)        | 38 |

| 5.5 | Roundtrip ping times measured in milliseconds                            | 38 |

| 5.6 | Timestamp counter measures for ping with a 1000 millisecond interval     | 39 |

| 5.7 | Timestamp counter measures for ping with a 500 millisecond interval      | 39 |

| 5.8 | Timestamp counter measures for ping with a minimal interval (flood ping) | 40 |

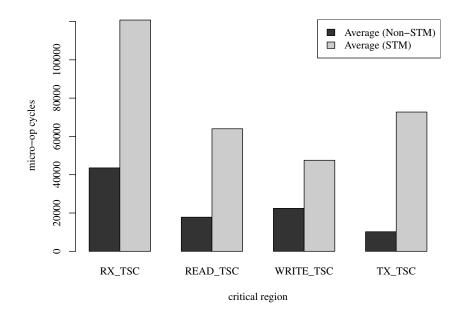

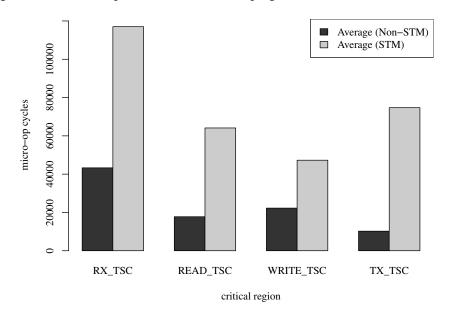

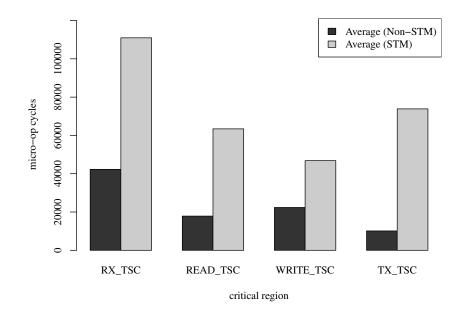

| 5.9 | Jitter Reduction measured in micro-operation cycles                      | 41 |

# **List of Terminology**

| 2PL      | Two-Phase Locking—A locking protocol that ensures the order of lock acqui-       |

|----------|----------------------------------------------------------------------------------|

|          | sition/release cannot cause deadlock.                                            |

| ACI      | Atomicity, Consistency, and Isolation—A subset of the ACID properties that       |

|          | TM system provide.                                                               |

| ACID     | Atomicity, Consistency, Isolation, and Durability—Properties that ensure a       |

|          | transaction is executed reliably.                                                |

| ANSI     | American National Standards Institute—Defines standards for various prod-        |

|          | ucts, such as the C programming language.                                        |

| API      | Application Programming Interface—A set of routines provided by the oper-        |

|          | ating system and software libraries.                                             |

| BIOS     | Basic Input/Output System—First stage of booting a personal computer, can        |

|          | run very basic services.                                                         |

| CAS      | Compare-and-Swap—An operation that atomically compares a single known            |

|          | value with the stored value and swaps in a new value if there is a match.        |

| DCAS     | Doubleword Compare-and-Swap—A CAS operation that works on two ma-                |

|          | chine words.                                                                     |

| DHCP     | Dynamic Host Configuration Protocol—A mechanism to automatically con-            |

|          | figure a network interface.                                                      |

| DMA      | Direct Memory Access—A mapping of physical memory addresses that is              |

|          | shared between the operating system and hardware devices.                        |

| ELF      | Executable and Linkable Format—Standard format for storing binary files.         |

| HTM      | Hardware Transactional Memory-Transactional memory that is imple-                |

|          | mented entirely in physical hardware.                                            |

| IA-32    | Intel Architecture, 32-bit—The 32-bit version of Intel's standard architecture,  |

|          | sometimes called x86, x86-32, or i386.                                           |

| ILS      | Interrupt-Local Storage—A private block of memory that every interrupt han-      |

|          | dler can access.                                                                 |

| I/O      | <b>Input/Output</b> —Communication between a computer and external manipulator.  |

| LL/SC    | Load Linked/Store Conditional—A set of opcodes that guarantees an atomic         |

|          | update of a memory location.                                                     |

| micro-op | Micro-operation Cycle—A subdivision of an operation that the processor rec-      |

|          | ognizes.                                                                         |

| opcode   | <b>Operation Code</b> —A single machine language instruction that specifies what |

|          | operation to perform.                                                            |

| O/S      | Operating System—The interface between hardware and application level            |

|          | code.                                                                            |

POSIX Portable Operating System Interface for Unix—A collection of operating system standards, available through an API. **SGLA** Single Global Lock Atomicity—A transaction semantic that allows a transaction to operate as though there is a single global lock in the system. SIMD Single Instruction, Multiple Data—Allows a streaming processor to execute a single instruction over many separate pieces of data, in parallel. SSE Streaming SIMD Extensions—An additional set of instructions on the IA-32 architecture that enables vector operations. STM Software Transactional Memory—Transactional memory that is implemented entirely in software libraries. TFTP Trivial File Transfer Protocol—Simple tool to send files across a network. TLS Thread-Local Storage—A private block of memory that every thread can access. ΤM Transaction Memory—A concurrency control mechanism that allows a set of memory instructions to occur in an atomic fashion. TSC Timestamp Counter-A performance measure on IA-32 that counts the number of micro-operation cycles since the processor reset.

# **Chapter 1**

# Introduction

# **1.1 Thesis Statement**

Software transactional memory can be used in interrupt-driven device drivers as a method to automate and provide fine-grained synchronization between the upper and lower halves.

# 1.2 Overview

In this thesis, a discussion of using *software transactional memory* (STM) in interrupt-driven device drivers is presented. This is substantial because software transactional memory has not (to this author's knowledge) been used at the operating system level before. One of the primary goals of this research is to implement a prototype operating system augmented with STM on actual hardware that can be purchased at the time of writing. Prior work has used *hardware transactional memory* to manage concurrency at the operating system level. These works, while novel, make use of hardware simulators and still rely on spinlocks in certain instances. One difficulty that arises from using transactions in interrupt-driven systems is non-linear code execution, where the operating system can arbitrarily change the code that the processor is executing.

This research presents three major outcomes. First, there is a discussion of how operating systems can benefit from applying a software transactional memory (STM) library to interruptdriven device drivers. Transactions were developed with multi-core systems in mind, but their properties also present a natural union with device driver structure in uniprocessor systems. Second, there is an explanation of methods for integrating an existing Linux based STM library into a non-Linux operating system kernel and drivers. While STM introduces a new set of problems to operating system design, it can minimize the difficulty in thinking about device drivers while increasing the scalability of operating system code as computing moves toward multi-core processors. Finally, there is a presentation of the performance results of using software transactional memory in an interrupt-driven device driver versus the non-transactional equivalent. These results demonstrate that transactional device drivers can be used without a significant impact to performance times.

The overall structure of this document is as follows.

- Chapter 1 is an introduction to the topics presented in this document and outlines the contributions of this work.

- Chapter 2 provides an overview of related work.

- Chapter 3 presents a framework for handling atomic sections in normal execution mode, interrupt handling, and input/output (non-revocable) portions of the O/S.

- Chapter 4 details the specifications and implementation process for "Transactional Xinu."

- Chapter 5 provides results and a discussion of the performance of the prototype system.

- Chapter 6 summarizes this work and discusses future research and contributions.

# 1.3 Operating Systems

An *operating system* (O/S) is software that runs at the lowest level of a computer once the system has completed the boot process. This software consists of two important sections: device drivers and the application programming interface.

A *driver* is the software that facilitates interaction between high-level O/S functions and low-level hardware communications. As such, the driver is broken down into two parts: the upper half and the lower half. The lower half interacts directly with the physical hardware and the upper half presents a standard programming model for an application developer to use to interact with the device. Drivers must communicate incoming data from the lower half to the upper half and vice versa for outgoing data. The *application programming interface* (API) provides the standard high-level methods that an application programmer can use as a means to interface with the O/S, to interact with a user of the system, or to obtain data that has been generated for the application to use.

### **1.3.1** Interrupt-Driven Systems

One class of operating systems is called *interrupt-driven* systems, which includes almost every modern system from desktop computers to embedded routers to computerized thermostats. These are capable of receiving signals from outside the processor and causing the operating system to change the current path of execution to the code for handling interrupts. The operating system is able to ignore an incoming interrupt if the O/S is processing something that cannot be interrupted. However, the incoming interrupt request may be more important than the non-interruptible process the O/S is currently executing, and this behavior can lead to a crucial interrupt handler being deferred for an arbitrary amount of time.

In operating system terms *jitter* refers to the variations in the delay of interrupt handling caused by deferral. Jitter should be avoided in systems programming because it adds unpredictable behavior to the system. Unpredictable behavior is particularly troublesome in *real-time* systems, when results must be achieved within some fixed amount of time; jitter in interrupt handling may cause a necessarily predictable system to miss deadlines.

One common avoidance method is to minimize the length of time and/or amount of code that must disable interrupts in the system. This takes the time and effort of a "good" systems programmer who may still make errors in situations that are difficult to reason about or in a sufficiently complex system. Since the definition of a "good" systems programmer is loose, computer scientists aim to find more concrete solutions to these problems to reduce programmer errors. One obvious solution is to simply never disable interrupts in the O/S, but this can cause problems in certain cases; the simple piece of code in Figure 1.1 exemplifies an error that is likely to occur with that approach.

On line (1), the programmer declares the variable our\_var to be global (i.e. it can be modified by any process at any time). On line (4), that variable is then incremented by 1. From a high level, this function may look safe. However, if the corresponding machine code (Figure 1.2) runs on a multi-threaded or multi-processing O/S, there is the possibility of a contention error. This

```

( 1) global integer our_var = 1

( 2)

( 3) function increment(void)

( 4) our_var++

```

Figure 1.1: Example of a potentially unsafe memory access

```

(1).data

(2)

.globl our_var

# stored at memory location 0x4c

( 3) our var: 0x0001

(4)

(5) .text

( 6) increment:

(7)

lw

s0, 0x4c(zero) # load 'our_var' into register 's0'

addiu s0, s0, 1

# increment value in `s0' by 1

(8)

(9)

s0, 0x4c(zero) # save register 's0' to 'our_var'

SW

(10)

j

ra

# return to calling functions

```

Figure 1.2: Code from Figure 1.1 in MIPS assembly

error is referred to as a "race-condition" where two separate instances of the code try modifying the same variable at the same time with unpredictable results.

In line (3), our\_var is created with a (fictional) location of  $0 \times 4c$  in main memory. In order to perform the increment operation, the processor must load the variable from main memory into a register, increment the register, and finally store the updated value back into main memory. In the interrupt-driven paradigm, if an interrupt is raised anywhere between lines (7) and (9), it is possible that the value stored in location  $0 \times 4c$  has changed. If this happens when the code from Figures 1.1 and 1.2 complete, the value saved in memory is not correct.

# 1.4 Contributions

This thesis provides a discussion about using software transactional memory in the interrupt-driven device drivers of an operating system. Software transactional memory (STM) provides a simple interface for handling concurrency issues between separate threads of execution while still allowing interruptions. Adding software transactions to an operating system allows the exploration of new

transactional technology in combination with existing operating system constructs with the goal of finding a balance between the two. Specifically, by using STM in device drivers, it may be possible to reduce jitter introduced by entering critical sections of code that have disabled interrupts. This allows the arrival time of interrupts into the system to be more predictable—a very useful property when dealing with system deadlines.

This theory is examined by developing a method for integrating a publicly available, production quality STM library—designed for Linux—into a small embedded operating system. This author ports Embedded Xinu—a modernized revision of the Xinu kernel—to the IA-32 architecture and augments the necessary components to transform the system into "Transactional Xinu." Transactional Xinu is a proof-of-concept prototype that is designed to actually run on real hardware and provides a strong framework for ongoing and future experiments on integrating transactional memory with core operating system components.

Finally, there is a direct evaluation of jitter reduction in asynchronous device drivers using STM-based language constructs to eliminate interrupt-blocking critical sections in the upper half of driver code. This evaluation is done through various performance measuring techniques to show differences between transactional and non-transactional code.

# **Chapter 2**

# **Related Work**

Concurrency control mechanisms are used to avoid inconsistency in shared data. In practice, the most common method of protecting shared data is to lock it, execute a read-modify-write sequence, and finally release the lock [11, 15, 22]. This forces any other process to wait until it can acquire the lock. In a uniprocessor system, waiting is not a significant problem because the operating system executes each process in a serialized fashion and continue progress. However, in the device drivers of multi-core systems the problem becomes more pronounced because every core must cease execution of device driver code and wait for the lock/unlock cycle to complete. It is in this context that lock-free implementations of concurrency control must be considered [26, 29, 34, 51].

### 2.1 Atomic Regions

Several methods for dealing with atomic regions of code have been developed over the years. The most popular is the use of the proberen (P-, wait) and verhogen (V-, signal) operations of semaphores [15]. These P- and V-operations provide a basis for monitor and mutual exclusion synchronization by acquiring and releasing locks as needed. Mutual exclusion, semaphores, and monitors can be considered as *traditional* synchronization mechanisms that provide the semantics needed to protect shared data from being accessed by multiple threads in the system. However, the P- and V-operations introduce problems such as deadlock, priority inversion, and an increase in programmer responsibility for correct code. A *deadlock* situation occurs when the programmer attempts to acquire two different semaphores in two processes in the opposite order, thus preventing

either process from continuing. Typically this is avoided through careful programming practices (such as always acquiring locks in a predefined order). *Priority inversion* is a much more cunning problem that occurs when a low priority process holds a lock that a high priority process must obtain before it can continue. Typical implementations of semaphores allow a low priority process to take processing time away from a high priority process. This falsifies the system invariant that at all times the highest priority process is executing. To avoid this scenario, priority inheritance protocols were developed [16,47]. These allow a low priority process to be temporarily given a higher priority so the semaphore can be released and given to the higher priority process. While these methods hold true to the properties of the system, they do not run the way the programmer intends with the original high priority process taking precedence.

The above practices are sub-optimal solutions to the problems of deadlock and priority inversion. By using traditional synchronization as a way to lock and unlock data, the programmer must take the time to carefully acquire and release all the locks before reading or modifying the data. This greatly constrains the granularity of accessing data; if shared data is accessed, the programmer must create and acquire a lock for any read or write operation. If this is not done, then the data becomes corrupt and the system is unstable or incorrect. To prevent this the programmer can denote an atomic region that can be preempted at any point and safely restart from the beginning [3, 53]. The idea of preemptible atomic regions is important because it allows programmer to assume that contention does not occur; but, if contention does arise, then the atomic operations are unseen until the entire region of code is allowed to occur atomically. This has been shown to reduce jitter and run faster when used with varying priority processes within the Java virtual machine [32, 53]. However, since these are build using the Java virtual machine, they cannot be directly applied to the operating system, as it does not have garbage collection or other high level operations.

### 2.2 Transactional Memory

A *transaction* (in computer science) was first defined in the realm of database management systems [18] as a way to safely update records in a shared environment. This is done be keeping track of changes and, at commit time, ensuring that all shared data still has the expected values and updates each value. Moreover, a transaction was defined to have the following properties: atomicity,

consistency, isolation, and durability (or the ACID properties) [17, 35]. *Atomicity* means that the process executes one or more operations that are indivisible from each other and occur "instantaneously" (or appear so) [36]. In a transactional system, this means that an atomic block either commits the changes or aborts the changes. The *consistency* property guarantees that a transaction takes a current consistent state and moves to a new consistent state. *Isolation* means that a transaction does not depend on or affect a separately executing process in the system. Finally, *durability* makes the transaction irrevocable once the commit has completed.

### 2.2.1 Hardware Transactional Memory

Herlihy and Moss brought the idea of arbitrary sized transactions into the systems community as a way to safely update shared data in a multiprocessor system [29]. Their simulated implementation showed promising results for hardware transactional memory (HTM) but relied on extending the underlying hardware to support the system. A similar implementation by Stone et al. extended the existing single word load-linked/store-conditional (LL/SC) operations into a multiple reservation system that effectively enabled multi-word atomic operations [51].

These hardware solutions place several restrictions on transactional memory. One such restriction is that the size of an object is bounded by hardware constraints. Several authors have developed potential solutions to this problem [2,21,40,42].

Ananian et al. describe an "Unbounded Transactional Memory" system that allows a transaction to grow as large as virtual memory. However, their implementation does not allow a transaction to grow as large as virtual memory and restricts the transaction size to that of physical memory [2]. Rajwar et al. created a virtual transactional memory system that is transparent to the user [42]. This system provides a consistent programming model to hide the details of hardware implementation from the software developer; this is promising because the programmer no longer must be concerned with the implementation details of the underlying system. Though these systems provide the functionality to have large transactions, which an O/S needs, they are still built using hardware simulators.

Hammond et al. developed a coherency and consistency protocol for transactional memory that extends existing hardware systems, in a simulator [21]. This system allows safe input/output (I/O) 'transactions' by guaranteeing that an I/O transaction never be allowed to revert to a previous state. Moore et al. use a log-based system to track old values of data to provide safe reversion of arbitrary sized transactions [40]. Each of these systems differ in implementation of version management and conflict detection algorithms. Again, these systems each make extensive use of hardware simulators to implement extra opcodes that do not exist normally.

#### 2.2.2 Software Transactional Memory

Hardware implementations of transactional memory have only existed as simulations; also, they are either bounded in transaction size or require a complex, inflexible system. As a solution to these problems, Shavit and Touitou proposed a software transactional memory (STM) system [48]. With this STM, the machine must implement the LL/SC operations—everything else to handle a transaction is done at the software level. As with hardware implementations, using software transactions is a non-blocking operation which allows software written using transactions to scale up to multi-core systems.

From this point there have been many improvements to software based transactional memory [1, 12, 14, 27, 28, 50]. Herlihy et al. built the first dynamic STM system to allow the size of a transaction to be defined during the run of a program. Both Saha et al. [1, 41, 45] and Harris et al. [23–25] have presented several papers exploring blocking STM implementations that are still quite efficient. Though the use of a blocking scheme seems to go against what transactional memory was developed for, the authors argue that by integrating their blocking implementation with a runtime scheduler and contention manager they are able to guarantee progress by aborting the transaction of another process if lock acquisition fails. This system also introduces either word- or objectsized conflict detection, allowing for less overhead when creating a transactional object because only one ownership of the object must occur instead of obtaining ownership of every item within the object. Dice et al. introduced improvements to how the system handles commits and version management and additionally implemented their STM system to work with malloc/free to allow an open memory system where transactional code can use the same memory as non-transactional code [14].

An article in *Communications of the ACM* discusses why STM has not become widely adopted by the programming community [8]. While some of the conclusions—lack of support for legacy code, baseline performance, and compiler instrumentation—are valid, a recent paper by Ni et

al. has provided some answers to the proposed problems [41]. These authors discuss the design and implementation of supporting legacy code, improving performance, and language constructs, for the Multi-Core RunTime STM system they developed [1,45]. In this McRT-STM environment, several modes of operation have been built to allow the safe integration of legacy code with STM-aware systems.

### 2.2.3 Hybrid Transactional Memory

Unsurprisingly, STM requires higher time and space requirements when compared to HTM. However, HTM needs hardware that has only existed in simulated environments and would need transactional semantics integrated into physical components of the system. Also, HTM would impose a certain level of machine-specific knowledge on the programmer, unless a software based virtual system is in place. As a compromise, several groups have developed hybrid transactional systems which take the advantages of both HTM and STM systems [9, 13, 33, 39]. Each of these systems puts a primary emphasis on performing the transaction at the hardware level to provide for fast transactions. If the hardware fails for some reason (large number or size of transactions occurring in parallel) then the system falls back to a software solution. While these systems provide the advantages of both HTM and STM they also get the disadvantages: code size must now incur the cost of software overhead and physical systems must have costly hardware.

In a similar line of thinking Saha et al. propose a purely software transactional system and add architectural acceleration to create a faster STM system [46]. This solution is interesting because it allows an existing STM system to remain unchanged while providing acceleration for common portions of library code. This gives a consistent system that can be improved transparently as improved hardware becomes available.

# 2.3 Operating Systems

Developing an operating system and associated structures utilizing transactional memory that are scalable and can perform on the same level as current systems is not a trivial task. One goal for these projects is to use lock-free structures so the kernel can execute on multi-core machines without running into a deadlock situation or becoming an inefficient, serially executing system. One example of this is the Synthesis kernel that makes use of specialized data structures and the atomic compare-and-swap (CAS) operation of the system [37]. At the time there were only a few atomic operations available, so they fit the most common data structures (stacks, queues, and linked lists) into one- or two-word pieces of data and used the atomic CAS or double-CAS operations. While the novelty of this system demonstrated the possibility of lock-free operating systems, the difficulty of being able to use arbitrarily sized structures remained a large challenge to scalable operating system structure.

A similar idea appears in the Cache Kernel implemented by Greenwald and Cheriton [19]. Here the authors emphasize the usage of non-blocking synchronization to mutate O/S structures and the use of double-CAS operations to make this a feasible task. This work differs from the Synthesis kernel because Cache tries to optimize against a general linked list structure instead of O/S specific structures, allowing application programmers to program against a more generic interface. Both the Synthesis and Cache kernels differ from Transactional Xinu in that they concentrate on using a single operation to atomically change one- or two-word sized memory locations. Unlike these kernels, Transactional Xinu allows an arbitrary amount of processing and data modification to occur in an atomic section.

In the transactional realm, Rossbach et al. have implemented TxLinux—a version of Linux that makes use of a hardware TM system [44]. This is the most comprehensive version of a transactional-based operating system to date; the system makes use of "cooperative transactional spinlocks" (*cxspinlocks*) to deal with managing I/O operations within a transaction. Cxspinlocks fall back to standard locking mechanisms so the I/O operations can complete safely and successfully. This system is based on MetaTM, the underlying hardware simulator that implements a hardware transactional memory design to work with TxLinux.

### 2.4 Tools

The core of Transactional Xinu is a stable, modern implementation of the Xinu operating system [4, 5, 7, 10]. Xinu has a long history in a university setting. Dr. Douglas Comer developed it at Purdue University over 25 years ago on the DEC LSI-11 for teaching operating systems courses. From there, Xinu made its way into research projects, commercial appliances, and has been ported

to several different architectures including the VAX platform, Sun-2 and Sun-3 workstations, and finally the Intel i386 architecture. After a period of disuse, the Embedded Xinu project was born with the fundamental idea of maintaining simplicity and updating the source code to ANSI C compliance. With this updated version, embedded MIPS based wireless routers were chosen as the target architecture; later this author built a modernized port for the Intel IA-32 architecture based on Embedded Xinu.

By using the minimalist design philosophy and extending key O/S components, Transaction Xinu builds up new device drivers and modifies interrupt handling routines. Now, Xinu interacts with an existing transactional memory library and allows the exploration and analysis of effects a STM has on O/S design.

For the transactional memory implementation, this author has chosen a publicly available, production quality STM library and C/C++ compiler developed by Intel Corporation [31]. This provides a well written, stable STM library. By using these freely available components future implementations can be build and extended with relative ease.

### 2.5 Summary of Related Work

With the transactional model of sharing data becoming more prolific, computer scientists are interested in seeing what advantages and disadvantages result [30]. This thesis is specifically focused on using transactional memory as a means of reducing the use of traditional locks at the operating system level. Of the several types of transactional memory systems available, this system makes use of the software transactional memory system built at Intel [1,41,45,54]. This software solution provides a working implementation that can be used on current generation machines that are readily available without the use of a hardware simulator. Also, the library provides a mode that can execute a serialized transaction (for use with I/O operations), and provides an obstinate mode for use in interrupt handlers that occur in such a way that no other transaction can execute in parallel.

Using this version of Intel's STM library raises a few issues with using a non-standard operating system such as Embedded Xinu [5,7] because the library is targeted towards the Linux operating system. By developing a system to show that Intel's library can be adapted to work with an embedded operating system, this author aims to demonstrate the possibility of using STM with only

slight programming overhead. This implementation of Transactional Xinu is significantly different than TxLinux which builds a simulated hardware transactional memory model and adds extensions to the Linux kernel. This author has developed Transactional Xinu to work with hardware and software solutions that exist today and that can be implemented on any platform that complies with the hardware requirements of Intel's library.

# Chapter 3

# Framework

The goal of this thesis is to develop an operating system kernel that supports device drivers with software transactional memory as a concurrency control mechanism. Specifically, this system is aimed at interrupt-driven device drivers and jitter caused by entering and exiting critical sections. A *critical section* is a piece of code that accesses shared data in the system and must not be accessed by two or more threads simultaneously. Within a critical section any action or state change in the system cannot be seen by a separate thread of execution during the changes, as this may cause the system to become unstable. These critical sections present an interesting problem with respect to the handling of interrupts. When the kernel enters a critical section, some action must be taken to prevent shared data from being accessed by separate threads of execution; in an interrupt-driven system it is possible for the kernel to switch threads of execution at any point.

In a transactional system there is the possibility that input/output operations occurring within a transaction are interrupted. This presents a dangerous situation. When a separate physical device has already begun reading and processing shared data, if a transaction fails these changes to shared data cannot be safely *rolled back* (so called "irrevocable" operations). A rollback refers to the act of reverting the state of memory to one that existed before any actions of the transaction had taken place. Rollbacks can be implemented by keeping a log of changes that have been made or by not modifying memory until a commit operation takes place.

This chapter discusses options for handling critical sections in interrupt-driven devices drivers. Building upon these ideas, this author discusses how to apply transactional memory concepts to these device drivers to avoid the pitfalls of irrevocable operations.

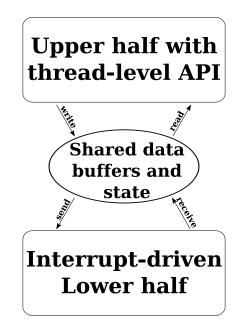

Figure 3.1: Logical separation of device driver halves

# **3.1 Device Driver Structure**

Typical device drivers are separated into two logical halves: an upper half and a lower half. Interaction between the two halves occur as seen in Figure 3.1.

In the upper half of the device driver thread-level API calls are available to create a simple and standard way for the programmer to interact with device drivers. The programmer calls read and write on specific instances of a device which results in a transfer of data either from or to the device driver. Since read and write calls are done at the thread-level, the execution is temporally decoupled from the interrupt-driven lower half; thus, the shared data can be accessed at any point during execution.

In order for a thread to send data through the device, several steps must take place. The data begins by entering the device driver from the upper half. It is placed in a buffer shared between the two halves of the driver and the state of the driver is changed to reflect the amount of data now available to the lower half. When an interrupt enters the system the data can be transferred out of the shared buffer and sent via a hardware interface. This process is reversed when data arrives—the data is copied from the physical hardware to a shared buffer. The driver state is updated. Then, when the programmer wants to read data it is copied from the shared buffer into a user buffer. And again the driver state is updated. It is within the device driver that data is shared between the two

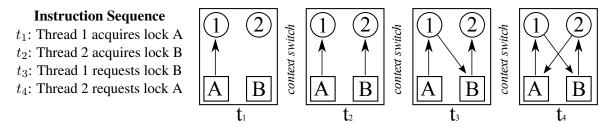

Figure 3.2: Circular deadlock caused by incorrect lock acquisition

separate halves and concurrency issues must be handled to maintain a correct state and provide the correct data to either half when needed.

## **3.2** Critical Sections

As touched on at the beginning of this chapter, critical sections of code exist when the machine must appear to execute multiple lines of code in a single operation. While the actual processor takes several instruction cycles to complete different operations, from the perspective of the kernel and other threads, the operations occur instantaneously or *atomically* within system. At the completion of a critical section, the kernel maintains a *consistent* state—no illegal or unknown states exist. The critical section occurs in *isolation* so that no other thread of execution is able to see or use an intermediate state. While not applicable to the systems community, *durability* ensures that once the data is committed it is not possible to return to a previous version of the data. In database systems, this collection is referred to as the ACID properties [20]; from an operating systems perspective only the ACI properties are necessary to guarantee the system remains in a safe and known state upon completion of the critical section.

In essence, a critical section requires some sort of concurrency control mechanism to ensure that the kernel does not enter an inconsistent state. Existing concurrency controls—including mutual exclusion, semaphores, and disabling/restoring interrupts—can provide the ACI properties in certain cases.

In the normal case when the kernel is switching between threads of execution, mutual exclusion and semaphores allow critical sections to follow the ACI properties because there is no way for a thread to execute code in a critical section when another thread has locked that data. However, this paradigm introduces the possibility of deadlock in the system if two threads acquire separate locks in the opposite order. For example, thread 1 acquires lock A, followed by thread 2 acquiring lock B. Now thread 1 wants lock B and thread 2 wants lock A, but neither can proceed since the other has the necessary data lock. This instance of deadlock can be seen in Figure 3.2, where the circles represent threads, squares represent locks, an arc from a lock to a thread shows lock acquisition, and an arc from a thread to a lock is a request. Mutual exclusion also brings priority inversion into the system by allowing a low priority thread to be given processor time. When a low priority thread has acquired a lock that a high priority thread wants, the high priority thread yields the processor to the lower priority thread. Moreover, when interrupts are added into a system, it is possible for a thread of execution to acquire a lock, get interrupted, and have the important interrupt handler yield to the thread holding the lock. Alternatively, the handler could not defer to the thread, fail to acquire the lock correctly, and violate the ACI properties. Either of these cases result in an unpredictable system that cannot guarantee timeliness or even correctness. While there are ways to avoid these problems—like acquiring locks in a consistent order [52] or implementing a priority inheritance scheme [16, 47]—there are still problems when dealing with a system that can handle interrupts.

For an interrupt-driven system, it is clear that mutual exclusion brings many problems and greatly increase the complexity of the system in order to protect a critical section. To ensure the ACI properties, the kernel must use a more aggressive tactic—disabling interrupts. By disabling interrupts when entering a critical section, it is guaranteed that nothing can cause the processor to change threads of execution while executing code in a critical section. Once the critical section is completed, the kernel can restore the interrupts and replay any that were delayed while processing the critical section. While this solution works, it introduces interrupt jitter and does not scale well as multi-core processors enter into the computing field.

### 3.3 Interrupt Handling

As mentioned, interrupt-driven systems complicate matters in handling concurrency issues, since using locking synchronization methods introduces various problems and disabling interrupts introduces *jitter* into the system. Jitter is created when there are variations in the amount of time the system takes to respond to interrupts entering the system. If interrupts are disabled during critical

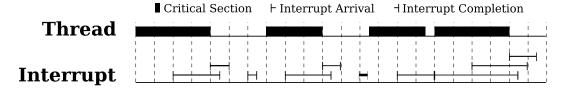

Figure 3.3: Jitter introduced by disabled interrupts

section execution, jitter occurs when an interrupt is raised but cannot begin processing until the critical section completes. This can be seen in Figure 3.3, where interrupts consistently arrive every two time intervals, but the completion time is not predictable due to critical code execution at arrival time. In an interrupt-driven system, the handling of interrupts is of utmost importance since a delay in handling could result in out-of-date or incorrect data. To avoid this issue the kernel can implement a fine-grained interrupt system that only disables certain interrupts when entering corresponding critical sections. Having fine grained control only minimizes the number of interrupts that experience jitter and increase the complexity of the code the programmer has to think about and develop.

Exploring software transactional memory (STM) as a concurrency control mechanism for interrupt-driven device drivers is an intriguing idea. STM offers a different method of concurrency control that allows the programmer to annotate the source code by inserting an "atomic" block around code in a critical section. By using an atomic block in a critical section, the STM library provides the assurance that the ACI properties are obeyed upon the completion of the transaction. This assurance can be extended to interrupt-driven system with ease. If an interrupt enters the system, it is implicitly given the highest priority so it is allowed to execute through to completion. By using this fact, it is possible to reason that the entire handler can be labeled as a critical section. Thus, if the interrupt handling code is annotated as an "atomic" block, it too maintains the ACI properties. Additionally, when the interrupt handler begins execution, it works with the STM library to invalidate any competing transactions that occur in the upper half of the driver.

Unlike mutual exclusion, STM does not transfer execution away from the interrupt handler, so the interrupt still completes in a predictable amount of time. Using STM also does not require the programmer to disable interrupts when entering a critical section. This allows the kernel to begin handling an interrupt immediately when the interrupt enters the system. Combining these two observations, this thesis argues that using software transactional memory eliminates a major source of jitter from interrupt-driven device drivers.

# 3.4 Programming considerations

Adding transactional memory to any piece of software comes with some programming considerations. One appealing aspect of transactions is that the programmer no longer has to carefully reason about how the concurrency control works, or if the system can deadlock under certain conditions. The STM library and compiler inserts the code and synchronize data at runtime. The programmer is then freed from dealing with tedious synchronization issues and can concentrate on developing a better system.

Another difference is that transactions provide automatic and more fine-grained concurrency control to the programmer that traditional synchronization. If a programmer needs to access shared data, then a lock for that data must exist and the system must acquire that lock before reading or writing the data. With transactional memory, the locks exist at the machine-word level and do not need to be acquired when a read occurs. This allows a write transaction to acquire only the locks that are needed for that block of code, not a lock on the entire object or a region of memory. Also, when contention does occur on a lock the TM system is able to execute faster since it does not have to wait for the thread holding the lock to release allowing the current critical section to begin execution. This contrasts with traditional synchronization where an overzealous lock protects more data than needed in the critical section. When lock contention does arise under traditional synchronization, the thread must wait until the lock is released before it can enter the critical section.

### **3.5** Non-Transactional Input/Output

One problem that manifests by using transactions with interrupt-driven device drivers is input/output (I/O) operations. I/O operations make use of direct memory access (DMA) space that shares memory addresses between the operating system and a physical hardware device. This makes for more efficient data transfer because the processor does not have to write every word to the physical hardware, but can instead use memory to write to a common space. Once the data is written to DMA

space, the kernel can send a signal to the physical hardware to begin using the data stored at a specified memory location.

In a transactional system, this causes problems if a transaction fails during the commit phase because the library rolls back any changes made. If the physical hardware had already been notified that new data was available and began reading when the rollback occurs, there are no guarantees that the data is correct. This has long been a problem with merging transactional memory and operating systems, because one of the common places for shared data is in device drivers that share memory space with independent hardware systems. When an interrupt enters the system it is implicitly given the highest priority and does not allow other threads to run. Thus, any conflicting transaction in the system have already begun and no new conflicts can arise during interrupt processing.

From this fact, all that the STM library needs to know is that when an interrupt handler enters the critical section, it must allow the transaction to succeed and invalidate all other related transactions. If both the upper and lower halves of a device driver are written with critical sections protected by an atomic block, then in an interrupt-driven device driver the upper half does not lock the data or delay interrupts allowing the interrupt to begin processing immediately. In the lower half of the driver, the atomic block always beats other competing transactions and invalidate any transactions occurring in the upper half when the interrupt entered. This means that interrupts can be handled immediately by the operating system, thereby reducing the jitter for the device driver, while still performing correctly with thread-level API calls that are interacting with the upper half of the driver. As a consequence of reducing the jitter and adding a STM library, the time it takes to perform upper half reads and writes, as well as lower half sending and receiving, is increased. Despite this slow down, the increase in system predictability and simplification of reasoning about device driver concurrency make software transactional memory a useful tool for interrupt-driven systems.

### **3.6 Summary of Framework**

This chapter has discussed various concurrency control mechanisms that are used in operating system design and how those traditional methods work with respect to an interrupt-driven device driver. A device driver consists of two halves—an upper and lower—that interact with each other through shared memory buffers and state information. In this device driver the shared data must be protected against inconsistency. This is done through critical sections of code that must complete atomically, end in a consistent state, and occur in isolation. By disabling interrupts in device driver critical sections these properties are maintained, but this action does not scale well and introduces jitter into the system.

Transactional memory is a different form of concurrency control that has not been explored in this context and can guarantee that the ACI properties are maintained. This thesis has presented a method to use STM-based atomic blocks to coordinate between the upper and lower halves of the device driver. Because the interrupt-driven lower half always wins if a transaction is occurring in the upper half at the same time as the lower half, the interrupt still succeeds. Since the interrupt succeeds, the upper half must rollback the changes and try again—this is acceptable because the upper half does not cause the lower half to wait, thereby theoretically reducing interrupt jitter.

# **Chapter 4**

# **Implementation Notes**

This chapter presents specific information regarding the integration of the Embedded Xinu operating system with a publicly available, production quality STM library and compiler from Intel [31]. The Intel STM library was designed for software running under the Linux kernel so several modifications must be made to Embedded Xinu to mimic the expectations of the runtime library.

## 4.1 Original System

At the core of Transactional Xinu is the Embedded Xinu kernel [5, 7]. This thesis makes use of the Xinu kernel because it is an excellent research platform with under 20,000 total lines of code making it simple to understand and extend, while still providing a rich environment for experimentation. As a system, Embedded Xinu has a lightweight thread model with a shared memory space, a fully-preemptive multitasking priority scheduler, synchronization primitives, inter-process communications, and a variety of device drivers.

## 4.2 Transactional System

Extending the base system to include transactional components requires careful design and implementation. Since Transactional Xinu revolves around a software transactional memory implementation, the first step was to find a STM library capable of dealing with low level operating system tasks. This author chose a publicly available, production quality STM library and compiler from Intel because the library offers several modes of operation and is capable of working with legacy code (code that was not written with transactions in mind). Because this library was designed for Linux, Transactional Xinu must be capable of supporting the threading functionality and transparent thread-level storage similar to Linux.

#### 4.2.1 Transactional Library

Intel's STM library and compiler were selected because they offer different modes of operation: optimistic, pessimistic, obstinate, and serial [41]. Optimistic transactions make the assumption that no conflict occurs during the lifetime of the transaction, but if contention arises a rollback provides the correctness guarantees required of the library. Conversely, a pessimistic transaction must assume a conflict occurs and take precautions against such a case (like typical locking systems). The Intel STM library is the first STM implementation to allow both these modes of operation at the same time. Additionally, there is an obstinate mode that allows certain transactions in the system to be stubborn. If an obstinate transaction conflicts with a non-obstinate transaction the contention manager lets the obstinate transaction win. Lastly, serial mode allows integration with legacy and input/output code.

In Transactional Xinu, serial mode allows interrupt handlers to take advantage of certain properties in the STM library. As mentioned, the serial mode of transaction handling exists for legacy (non-transactional) functions to be used in a transaction. This ensures that global variables used in the legacy code safely update without risking data inconsistencies with other transactions. Once a serialized transaction begins execution, it runs through to completion—even if another transaction competes for the shared data.

#### Single Global Lock Atomicity

Intel's library provides single global lock atomicity (SGLA) semantics to all transactions that are in the system [38, 41]. SGLA semantics create an equivalence between every \_\_tm\_atomic code block and the same program with every atomic section occurring after a global lock was acquired. This SGLA equivalence property can be seen in the code segments found in Figure 4.1. Thus, a program that uses transactions behaves the same as if each atomic block were guarded by a single

| ( 1) | tm_atomic { |                   | (1) | <pre>wait(global_lock);</pre>   |

|------|-------------|-------------------|-----|---------------------------------|

| (2)  | Statements; | $\longrightarrow$ | (2) | Statements;                     |

| (3)  | }           |                   | (3) | <pre>signal(global_lock);</pre> |

Figure 4.1: Code segment showing transactional to SGLA semantics

global lock. By doing this, the library can guarantee that if the program is race free under a single global lock, then the transactional equivalent is also race free. It is important to understand precisely what this property is saying. The guarantee is only valid if the program is race free under a single global lock, if a race condition exists—say between transactional and non-transactional code—then no guarantee is made. While the transactional code may see consistent values for shared variables, the non-transactional code accessing the same variable sees intermediate or inconsistent values. Moreover, the non-transactional code can violate the isolation property of a transaction by modifying data the transaction accesses. Thus, Intel's STM library and compiler can guarantee that no race conditions are introduced to the code, assuming there were no race conditions before.

#### **Obstinate Transactions**