Rochester Institute of Technology

## **RIT Scholar Works**

Theses

5-2018

## UVM Verification of an SPI Master Core

Deepak Siddharth Parthipan dp9040@rit.edu

Follow this and additional works at: https://scholarworks.rit.edu/theses

#### **Recommended Citation**

Parthipan, Deepak Siddharth, "UVM Verification of an SPI Master Core" (2018). Thesis. Rochester Institute of Technology. Accessed from

This Master's Project is brought to you for free and open access by RIT Scholar Works. It has been accepted for inclusion in Theses by an authorized administrator of RIT Scholar Works. For more information, please contact ritscholarworks@rit.edu.

#### UVM VERIFICATION OF AN SPI MASTER CORE

by

Deepak Siddharth Parthipan

#### GRADUATE PAPER

Submitted in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE in Electrical Engineering

Approved by:

Mr. Mark A. Indovina, Lecturer Graduate Research Advisor, Department of Electrical and Microelectronic Engineering

Dr. Sohail A. Dianat, Professor Department Head, Department of Electrical and Microelectronic Engineering

DEPARTMENT OF ELECTRICAL AND MICROELECTRONIC ENGINEERING KATE GLEASON COLLEGE OF ENGINEERING ROCHESTER INSTITUTE OF TECHNOLOGY ROCHESTER, NEW YORK

May, 2018

I would like to dedicate this work to my family, my father Parthipan Kempanna Gowder, my mother Malarmathy Parthipan, my sister Vaishnavi Parthipan, and friends for their love and support during my thesis.

## Declaration

I hereby state that except where explicit references are made to the work of others, that all work and contents of this Graduate Paper are original and have not been submitted in part or whole for consideration for any other qualification in this, or any other University. This UVM Verification of an SPI Master Core Graduate Paper is the result of my work and not a collaborative work, except where explicit references are mentioned.

> Deepak Siddharth Parthipan May, 2018

## Acknowledgements

I would like to thank my advisor, Professor Mark A. Indovina, for his support, guidance, feedback, and encouragement which helped in the successful completion of my graduate research.

### Abstract

In today's world, more and more functionalities in the form of IP cores are integrated into a single chip or SOC. System-level verification of such large SOCs has become complex. The modern trend is to provide pre-designed IP cores with companion Verification IP. These Verification IPs are independent, scalable, and reusable verification components. The SystemVerilog language is based on object-oriented principles and is the most promising language to develop a complete verification environment with functional coverage, constrained random testing and assertions. The Universal Verification Methodology, written in SystemVerilog, is a base class library of reusable verification components. This paper discusses a Universal Verification Methodology based environment for testing a Wishbone compliant SPI master controller core. A multi-layer testbench was developed which consists of a Wishbone bus functional model, SPI slave model, driver, scoreboard, coverage analysis, and assertions developed using various properties of SystemVerilog an the UVM library. Later, constrained random testing using vectors driven into the DUT for higher functional coverage is discussed. The verification results shows the effectiveness and feasibility of the proposed verification environment.

## Contents

| Co                    | ontent  | ts                      | V  |  |  |  |  |

|-----------------------|---------|-------------------------|----|--|--|--|--|

| Li                    | st of I | igures                  | xi |  |  |  |  |

| Li                    | st of ] | Tables     x            | ii |  |  |  |  |

| 1 Introduction        |         |                         |    |  |  |  |  |

|                       | 1.1     | Research Goals          | 2  |  |  |  |  |

|                       | 1.2     | Contributions           | 3  |  |  |  |  |

|                       | 1.3     | Organization            | 3  |  |  |  |  |

| 2                     | Bibl    | iographical Research    | 5  |  |  |  |  |

| 3 System Verification |         |                         |    |  |  |  |  |

|                       | 3.1     | State of the art        | 8  |  |  |  |  |

|                       | 3.2     | UVM Overview            | 9  |  |  |  |  |

|                       | 3.3     | UVM Class Hierarchy     | 9  |  |  |  |  |

|                       |         | 3.3.1 UVM Testbench Top | 0  |  |  |  |  |

|                       |         | 3.3.2 UVM Test          | 1  |  |  |  |  |

|                       |         | 3.3.3 UVM Environment   | 1  |  |  |  |  |

|     | 3.3.4  | UVM Age      | nt                           | 11 |

|-----|--------|--------------|------------------------------|----|

|     | 3.3.5  | UVM Sequ     | uence Item                   | 12 |

|     | 3.3.6  | UVM Sequ     | lence                        | 12 |

|     | 3.3.7  | UVM Driv     | er                           | 13 |

|     | 3.3.8  | UVM Sequ     | lencer                       | 13 |

|     | 3.3.9  | UVM Mon      | nitor                        | 13 |

|     | 3.3.10 | UVM Scor     | eboard                       | 14 |

| 3.4 | UVM    | Fransaction  | Level Communication Protocol | 14 |

|     | 3.4.1  | Basic Tran   | saction Level Communication  | 14 |

|     | 3.4.2  | Analysis p   | orts and Exports             | 15 |

| 3.5 | UVM I  | Phases       |                              | 15 |

|     | 3.5.1  | Build Phas   | e                            | 15 |

|     | 3.5.2  | Connect Pl   | hase                         | 16 |

|     | 3.5.3  | End of Ela   | boration Phase               | 17 |

|     | 3.5.4  | Start of Sir | nulation Phase               | 17 |

|     | 3.5.5  | Normal Ru    | In Phase                     | 17 |

|     | 3.5.6  | Scheduled    | Run Phase                    | 17 |

|     |        | 3.5.6.1 I    | Pre Reset Phase              | 17 |

|     |        | 3.5.6.2 I    | Reset Phase                  | 18 |

|     |        | 3.5.6.3 I    | Post Reset Phase             | 18 |

|     |        | 3.5.6.4 I    | Pre Configure Phase          | 18 |

|     |        | 3.5.6.5      | Configure Phase              | 18 |

|     |        | 3.5.6.6 I    | Post Configure Phase         | 18 |

|     |        | 3.5.6.7 I    | Pre Main Phase               | 18 |

|     |        | 3.5.6.8      | Main Phase                   | 18 |

|      |                | 3.5.6.10 Pre Shutdown Phase                                                                                                                                        | 9                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                | 3.5.6.11 Shutdown Phase                                                                                                                                            | 9                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                | 3.5.6.12 Post Shutdown Phase                                                                                                                                       | 9                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.5.7          | Extract Phase                                                                                                                                                      | 9                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.5.8          | Check Phase                                                                                                                                                        | 9                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.5.9          | Report Phase         20                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.5.10         | Final Phase                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.6  | UVM            | Aacros                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Syst | em <b>A</b> rc | itecture 2                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                               |

| •    |                |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.1  |                | SONE Interface                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.2  | WISH           | SONE I/O Registers                                                                                                                                                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.3  | Serial         | Peripheral Interface                                                                                                                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.4  | Data T         | ansmission                                                                                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.5  | Hardw          | re Architecture                                                                                                                                                    | 7                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 4.5.1          | Design of Clock Generation module (spi_clk_gen)                                                                                                                    | 7                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 4.5.2          | Serial data transfer module design (spi_shift)                                                                                                                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 4.5.3          | Top-level module (spi)                                                                                                                                             | 9                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.6  | SPI Re         | gisters                                                                                                                                                            | 9                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 4.6.1          | RxX Register                                                                                                                                                       | 9                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 4.6.2          | TxX Register                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 4.6.3          | ASS Register                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 464            | DIVIDED Pagistar 3                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | т.0.т          |                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 4.4<br>4.5     | <ul> <li>4.4 Data Tr</li> <li>4.5 Hardwa</li> <li>4.5.1</li> <li>4.5.2</li> <li>4.5.3</li> <li>4.6 SPI Reg</li> <li>4.6.1</li> <li>4.6.2</li> <li>4.6.3</li> </ul> | 4.4       Data Transmission       24         4.5       Hardware Architecture       27         4.5.1       Design of Clock Generation module (spi_clk_gen)       27         4.5.2       Serial data transfer module design (spi_shift)       27         4.5.3       Top-level module (spi)       29         4.6       SPI Registers       29         4.6.1       RxX Register       29         4.6.2       TxX Register       30 |

|   |      | 4.6.6   | IE Register                                     |   |

|---|------|---------|-------------------------------------------------|---|

|   |      | 4.6.7   | LSB Register                                    |   |

|   |      | 4.6.8   | Tx_NEG Register         32                      | ļ |

|   |      | 4.6.9   | Rx_NEG Register                                 | ļ |

|   |      | 4.6.10  | GO_BSY Register                                 | ļ |

|   |      | 4.6.11  | CHAR_LEN Register                               | ļ |

|   | 4.7  | Limitat | tion of Standard SPI and Advancements           | ; |

| 5 | Test | Method  | lology and Results 34                           | ŀ |

|   | 5.1  | Testber | hch Components                                  | ł |

|   |      | 5.1.1   | Test top                                        | ł |

|   |      | 5.1.2   | spi_interface                                   | , |

|   |      | 5.1.3   | spi_package                                     | ) |

|   |      | 5.1.4   | spi_test                                        | ) |

|   |      | 5.1.5   | spi_environment                                 | ) |

|   |      | 5.1.6   | spi_agent                                       | ) |

|   |      | 5.1.7   | spi_sequence_item                               | ļ |

|   |      | 5.1.8   | spi_sequence                                    | , |

|   |      | 5.1.9   | spi_sequencer                                   | , |

|   |      | 5.1.10  | spi_driver                                      | ) |

|   |      | 5.1.11  | spi_monitor                                     | ) |

|   |      | 5.1.12  | spi_scoreboard                                  | ) |

|   |      | 5.1.13  | wishbone_bfm                                    | ) |

|   | 5.2  | Testber | hch Results                                     | ) |

|   |      | 5.2.1   | SPI Master Controller Synthesis Benchmarking 40 | ) |

|    |       | 5.2.2   | Data Trai | ansactions                                     | <br>41    |

|----|-------|---------|-----------|------------------------------------------------|-----------|

|    |       |         | 5.2.2.1   | WISHBONE to SPI Master communication using BFM | <br>41    |

|    |       |         | 5.2.2.2   | SPI Master-Slave communication                 | <br>41    |

|    |       | 5.2.3   | Coverage  | ge                                             | <br>42    |

|    |       |         | 5.2.3.1   | Code Coverage                                  | <br>43    |

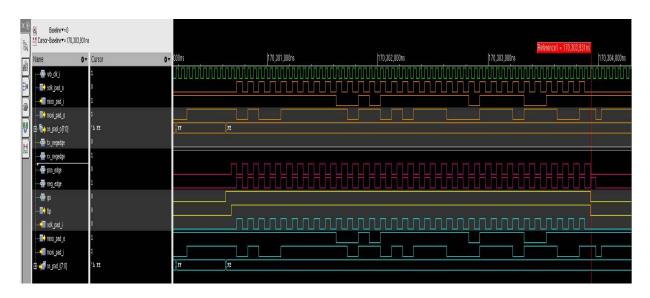

|    |       |         | 5.2.3.2   | Functional Coverage - Signal Level             | <br>44    |

|    |       |         | 5.2.3.3   | Functional Coverage - Transaction Level        | <br>45    |

| 6  | Con   | clusion |           |                                                | <b>48</b> |

|    | 6.1   | Future  | Work      |                                                | <br>49    |

| Re | feren | ces     |           |                                                | 50        |

| Ι  | Sour  | ce Cod  | e         |                                                | 54        |

|    | I.1   | SPI To  | р         |                                                | <br>54    |

|    | I.2   | SPI Cl  | ock       |                                                | <br>69    |

|    | I.3   | SPI Sh  | ift       |                                                | <br>73    |

|    | I.4   | Define  | s         |                                                | <br>83    |

|    | I.5   | Test To | р         |                                                | <br>90    |

|    | I.6   | Interfa | ce        |                                                | <br>96    |

|    | I.7   | Packag  | ge        |                                                | <br>98    |

|    | I.8   | Test .  |           |                                                | <br>100   |

|    | I.9   | Enviro  | nment     |                                                | <br>103   |

|    | I.10  | Agent   |           |                                                | <br>105   |

|    | I.11  | -       |           |                                                |           |

|    | I.12  | -       |           |                                                |           |

| I.13 | Sequencer                  |

|------|----------------------------|

| I.14 | Driver                     |

| I.15 | Monitor                    |

| I.16 | Wishbone Bus Funtion Model |

| I.17 | Scoreboard                 |

| I.18 | Coverage                   |

| I.19 | SPI Slave Model            |

| I.20 | Test defines               |

# **List of Figures**

| 3.1 | UVM hierarchy                      | 10 |

|-----|------------------------------------|----|

| 3.2 | UVM Phases                         | 16 |

| 4.1 | Wishbone Interface                 | 22 |

| 4.2 | SPI Protocol                       | 25 |

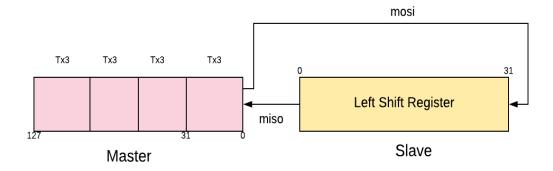

| 4.3 | Shift Register                     | 27 |

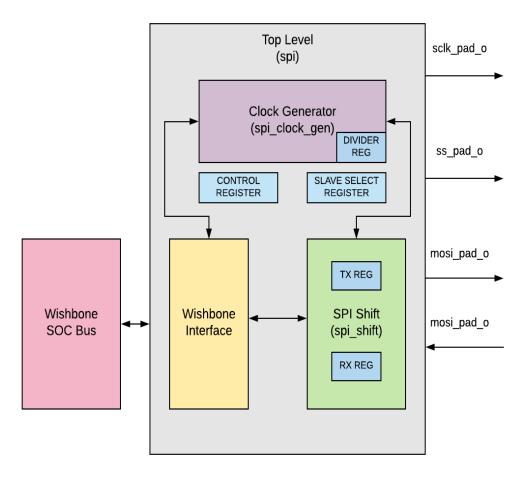

| 4.4 | SPI Master Architecture            | 28 |

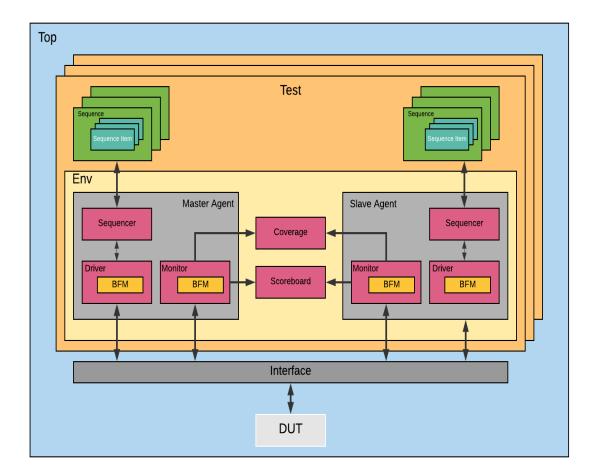

| 5.1 | UVM Testbench model                | 35 |

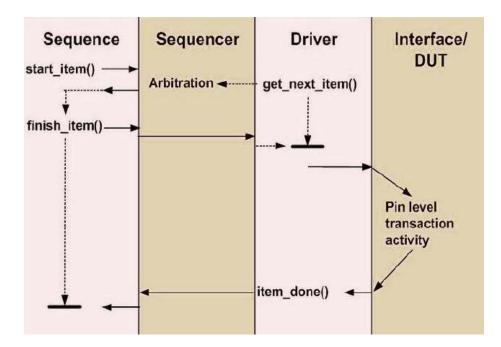

| 5.2 | UVM Sequencer Driver Communication | 38 |

| 5.3 | WISHBONE to SPI communication      | 42 |

| 5.4 | SPI Master - Slave communication   | 43 |

| 5.5 | Top Level Code Coverage            | 43 |

| 5.6 | Clock Level Code Coverage          | 44 |

| 5.7 | Shift Level Code Coverage          | 44 |

| 5.8 | Signal Coverage                    | 45 |

| 5.9 | Transaction Coverage               | 46 |

## **List of Tables**

| 4.1 | WISHBONE I/O Ports        | 23 |

|-----|---------------------------|----|

| 4.2 | SPI Master core registers | 30 |

| 5.1 | Synthesis Report          | 40 |

| 5.2 | Test Configuration        | 41 |

## Chapter 1

## Introduction

The rapid development of modern integrated circuits not only increased the complexity of integrated circuit (IC) design, but also made the IC verification equally challenging. Around 70% to 80% of the entire design cycle time is allotted to verification, and traditional verification methodologies are no longer able to support current verification requirements [1]. In 2002, the Accellera Systems Initiative released SystemVerilog (SV) a a unified hardware design and verification language. SystemVerilog language was an amalgamation of constructs from different languages such as Vera, Super Log, C, Verilog and VHDL languages. Moreover, in 2005 IEEE standardized (1800-2005) SystemVerilog. SystemVerilog supports behavioral, register transfer level, and gate level descriptions. SystemVerilog also supports testbench development by the inclusion of object-oriented constructs, cover groups, assertions, constrained random constructs, application specific interface to other languages [2].

Universal Verification Methodology (UVM) is a standardized verification methodology for testbench creation an is derived form the Open Verification Methodology (OVM), and also inherits some features from Verification Methodology Manual (VMM). Use of the UVM standard enables an increase in verification productivity by creating a reusable verification platform and verification components. The verification results of this work show the effectiveness and feasibility of the proposed verification environment [3]

System on Chip (SoC) is used for intelligent control feature with all the integrated components connected to each other in a single chip. To complete a full system, every SoC must be linked to other system components in an efficient way that allows a faster error-free communication. Data communication between core controller modules and other external devices like external EEPROMs, DACs, ADCs. is critical. Different forms of communication protocols exist such as high throughput protocols like Ethernet, USB, SATA, PCI-Express which are used for data exchanges between whole systems. The Serial Peripheral Interface (SPI) is often considered as light weight communication protocol. The primary purpose of the protocol is that it is suited for communication between integrated circuits for low and medium data transfer rates with onboard peripherals and the serial bus provides a significant cost advantage.

### **1.1 Research Goals**

The goal of this research work is to build a effective test bench that validates the SPI master controller with the help of the WISHBONE bus function model and SPI slave model. The goal is achieved with the following objectives:

- To understand SPI protocol architecture and WISHBONE specific requirements, to establish a connection between the test bench components and core controller.

- To apply advanced verification techniques such as Universal Verification Methodology and Coverage Driven Functional Verification.

- To develop a reusable Verification IP for WISBONE compliant SPI master core.

### **1.2** Contributions

The major contributions if this work include:

- 1. Research the SPI sub-system architecture, the Universal Verification Methodology, and SystemVerilog.

- Development of a WISBONE bus function model acting as an interface between the test bench and the SPI master device under test (DUT) and SPI slave model in order to make the verification closed loop testing.

- 3. Build hierarchical testbench components using UVM libraries and SystemVerilog constructs, constrained random stimulus, coverage and assertions.

- 4. Verify transmission of data with different character width and data formats.

## 1.3 Organization

The structure of the thesis is as follows:

- Chapter 2: This chapter consists majorly of articles/journals/books that are referred to provide a foundation for building a layered test bench. It also discusses some of the new methodologies and techniques for controller verification.

- Chapter 3: This chapter briefly describes the system verification, various components and methodology associated with it.

- Chapter 4: The system architecture, theory of operation, controller configuration registers of both WISHBONE and SPI described.

- Chapter 5: SPI test methodology, test bench components and bus function model are discussed in this chapter.

- Chapter 6: This chapter comprises of the verification results, conclusion and possible future work.

## Chapter 2

## **Bibliographical Research**

SPI protocol is one of the widely used serial protocols used in a SoC compared to other protocols such UART and I2C simply because SPI can operate in higher bandwidth and throughput [4]. SPI Protocol typically provides communication between the hosts side microcontroller and slave devices. It is widely used owing to fewer control signals to operate with [5]. At the host side, the specific SPI core studied in this work acts like a WISHBONE compliant slave device. The SPI master core controller consists of three main parts, Serial shift interface, clock generator and WISHBONE interface. The SPI core controller has five 32-bit registers which can be configured through the WISHBONE interface. The serial interface consists of slave select lines, serial clock lines, as well as input and output data lines. The data transfers are full duplex in nature and number of bits per transfer is programmable [6].

It is possible to have high speed SPI Master/Slave Implementation of range 900 – 1000 MHz. The core can be designed with greater ways to control SPI-bus such as the flexibility of handling two slaves at a time. One important feature is configured by programming the control register of the core through which the SPI module can be made to either operate in master or slave mode. During operation, the SPI status register gives information such as the current position of the data transfer operation, whether the data transfer has completed or not, etc. [7]. Another key feature is the flexibility of designing the SPI Interface IPs for multiple devices using parameterization method. Advanced design techniques, such as Time Sharing Multiplex (TSM), is used to automatically identify the master/slave devices and achieve multi-master devices. Using TSM the disadvantage of communication among multiple devices are overcome [8].

Owing to the increasing complexity of the modern SoC, the verification has become more challenging. In fact 70% of the product development time is spent on complex SoC verification. Reducing the verification effort is the key for time to market challenge. In order to cater to such growing complexity advanced verification methodologies are employed. IP verification requires in depth functional coverage with constraint random simulation technique. Various components such as coverage monitors and scoreboards are used for this purpose [9]. For a communication protocol like the SPI communication protocol, it has to be verified as per the design specifications. Applying constrained random technique for higher functional coverage provides effective verification result [10].

For many years, EDA vendors have been proposing newer verification methodologies and languages. For any system level verification methodology and language to be successful, the key lies in the scalability and reusability of the verification components developed. SystemVerilog with object-oriented programming is considered as one of the most promising techniques for high level function verification for current complex SOC designs. SystemVerilog provide complete verification environment, with direct and constrained random generation, assertion based verification and coverage driven metrics [11].

The Universal Verification Methodology (UVM) is the latest functional verification methodology, it uses base class libraries coded in SystemVerilog. UVM is built upon previous methodology libraries such as Mentor's AVM, Mentor & Cadence's OVM, Verisity's eRM, and Synopsys's VMM-RAL. This standardization allows users to implement verification modules that are portable and highly compatible. Such modules are called as Verification components. They are encapsulated and made ready to use configurable verification environments for full systems, submodules, or protocols. The comprehensive base class library forms the foundation for such applications. It is simulation-oriented, and performs coverage-driven constrained random verification, assertion-based verification, hardware acceleration or emulation [12].

Pre-designed and pre-verified is the corner stone of any new modern SoC development. IP blocks developed are reusable in nature and for most blocks one or more bus protocols play a very important role to make these IPs to adapt to a plug and play concept thereby increasing the productivity with a reduction in design time. The WISHBONE System on Chip interconnection is a method to connect different IP cores to form integrated circuits. The core objective behind the WISHBONE bus is to create a standard, portable interface that supports both ASIC and FPGA and technology independent [13]. The SPI protocol is developed using other bus protocols such as On-Chip Peripheral Bus [14]. A Bus Function Model (BFM) is use to verify IPs that are compatible with bus protocol such as the WISHBONE bus. The need for such models is to create a standalone interface that can receive transaction from the test bench from one side and on the other side operate as a master device on the bus an behave and send commands to the device under test [15].

## Chapter 3

## **System Verification**

### **3.1** State of the art

Hardware description languages are tools used by engineers to specify abstract models of digital circuits to translate them into real hardware, as the design progresses towards completion, hardware verification is performed using Hardware verification languages like SystemVerilog. The purpose of verification is to demonstrate the functional correctness of a design. Verification is achieved by means of a testbench, which is an abstract system that provides stimulus to the inputs of design under test (DUT). Functional verification shows that design implementation is in correspondence to the specification. Typically, the testbench implements a reference model of the functionality that needs to be verified and compare the results from that model with the results of the design under test. The role of functional verification is to verify if the design meets the specification but not to prove it [16].

The traditional approach to functional verification relies on directed tests. Verification engineers conceive and apply a series of critical stimulus directly to the device under test, and check if the result is the expected one. This approach produces quick initial results because little effort is required for setting up the verification infrastructure. But as design complexity grows, it becomes a tedious and time-consuming task to write all the tests needed to cover 100% of the design. Random stimuli help to cover the unlikely cases and expose the bugs. However, in order to use random stimuli, the test environment requires automating process to generate random stimulus, there is a need of a block that predicts, keeps track of result and analyses them: a scoreboard. Additionally, functional coverage is a process used, to check what cases of the random stimulus were covered and what states of the design have been reached. This kind of testbench may require a longer time to develop, however, random based testing can actually promote the verification of the design by covering cases not achieved with directed tests [16].

### 3.2 UVM Overview

The UVM methodology is as a portable, open-source library from the Accellera Systems Initiative, and it should be compatible with any HDL simulator that supports SystemVerilog. UVM is also based on the OVM library which provides some background and maturity to the methodology. A key feature of UVM includes re-usability though the UVM API and guidelines for a standard verification environment. The environment is easily modifiable and understood by any verification engineer that understands the methodology behind it [17].

### **3.3 UVM Class Hierarchy**

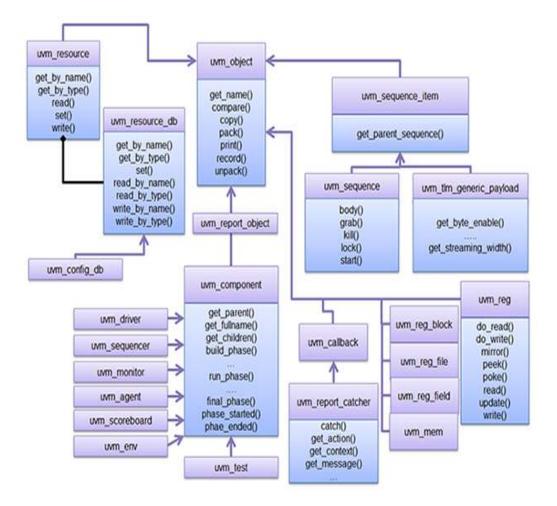

Figure 3.1 shows a simple UVM testbench class hierarchy. The following UVM components make up the hierarchy.

Figure 3.1: UVM hierarchy

### 3.3.1 UVM Testbench Top

The UVM testbench typically includes one or more instantiations design under test modules and interfaces which connect the DUT with the testbench. Transaction Level Modeling (TLM) interfaces in UVM provide communication methods for sending and receiving transactions between components. A UVM Test is dynamically instantiated at run-time, allowing the UVM testbench to be compiled once and run with many different tests [18].

#### **3.3.2 UVM Test**

The UVM test is the top-level UVM component class under UVM testbench. The UVM Test typically performs keys tasks like: configures values in config class and apply appropriate stimulus by invoking UVM sequences through the environment to the DUT. Base test class instantiates and configure the top-level environment; further individual tests will extend the base test to define scenario-specific environment configurations such as which sequences to run, coverage parameters, etc [18].

#### **3.3.3 UVM Environment**

The UVM environment is a container component class that groups together interrelated UVM verification components such as scoreboards, agents or even other environments. The top-level environment is a reusable component that encapsulates all the lower level verification components are targeting the DUT. There can be multiple tests that can instantiate the top-level environment class to generate and send different traffic for the selected configuration. UVM Test can override the default configuration of the top-level environment. Master UVM environment can also instantiate other child environments. Each interface to the DUT can have the separate environment. For example, UVM would be used to create reusable interface environment, IP interface environment, etc [18].

#### 3.3.4 UVM Agent

The UVM agent is a container component class. Agent groups together different verification components that are dealing with a particular interface of DUT. The Agent includes other components such as sequencer that manages stimulus flow, the driver that applies stimulus to the

DUT input and monitor that senses the DUT outputs. UVM agents can also include other components, like a TLM model, protocol checkers, and coverage collectors. The sequencer collects the sequences and sends to the driver. The driver then converts a transaction sequence into signallevel at DUT interface. Agent can operate in two kinds of mode active agent and passive agent. Active agent can generate stimulus, whereas passive agents only sense the DUT (sequencer and driver are disabled). Driver has a bidirectional interface to the DUT, while the Monitor has only unidirectional interface[18].

#### 3.3.5 UVM Sequence Item

A UVM sequence item is the lowest object present under the UVM hierarchy. The sequence-item defines the transaction data items and constraints imposed on them; for example, AXI transaction and it is used to develop sequences. The concept of the transaction was created to isolate Driver from data generation but to deal with DUT interface pin wiggling activities at the bit level. UVM sequence items can include variables, constraints, and even function call for operating on themselves[18].

#### 3.3.6 UVM Sequence

After creating a UVM sequence item, the verification environment has to generate sequences using the sequence item that could be sent to the sequencer. Sequences are a collection of ordered sequence items. The transactions are generated based on the need. Since the sequence item variables are typically random type, sequence helps to constrain or restrict the set of values sent to the DUT. Ultimately helps is reducing simulation time [18].

#### 3.3.7 UVM Driver

A UVM Driver is a component class where the transaction-level sequence item meets the DUT clock/ bit/ pin-level activities. Driver pulls sequences from sequencer as inputs, then converts those sequences into bit-level activities, and finally drive the data onto the DUT interface according to the standard interface protocol. The functionality of driver is restricted to send the appropriate data to the DUT interface. Driver can well off course monitor the transmitted data, but that violates modularity aspects of UVM. Driver uses TLM port (seq\_item\_port) to receive transaction items from sequencer and use interface to drive DUT signals[18].

#### 3.3.8 UVM Sequencer

The UVM sequencer controls request and response flow of sequence items between sequences generated and the driver component. UVM sequencer acts like an arbiter to control transaction flow from multiple sequences. UVM sequencer use TLM interface method seq\_item\_export and UVM driver use TLM interface method seq\_item\_import to connect with each other [18].

#### **3.3.9 UVM Monitor**

The UVM monitor does things opposite to that of UVM driver. Monitor takes the DUT signallevel/bit-level values and converts into transactions to needs to be sent to the rest of the UVM components such as scoreboard for analysis. Monitor uses analysis port to broadcasts the created transactions. In order to adhere to the modularity of the UVM testbench, comparison with expected output is usually performed in a different UVM component usually scoreboard. UVM monitor can also perform processing on post converted transaction such as collecting the coverage, recording, logging, checking, etc. or delegate the work to other components using monitor's analysis port [18].

#### 3.3.10 UVM Scoreboard

The UVM scoreboard implements checker functionality. The checker usually verifies the DUT response against an expected DUT response. The scoreboard receives output transactions from the monitor through agent analysis ports, and can also receive expected output from a reference module. Finally, the scoreboard compares both received DUT output data versus expected data. A reference model can be written in C, C++, SystemC, or simply a SystemVerilog model. The SystemVerilog Direct Programming Interface (SystemVerilog-DPI) API is used integrate reference models written in C, C++, etc., and allows them to communicate with the scoreboard [18].

## 3.4 UVM Transaction Level Communication Protocol

Transaction refers to a class object that includes necessary information needed for communication between two components. Simple example could be a read or write transaction on a bus. Transaction-level modeling (TLM) is an approach that consists of multiple processes communication with each other by sending transaction back and forth through channels. The channels could be FIFO or mailbox or queue. The advantages of TLM are it abstracts time, abstracts data and abstracts function.

#### 3.4.1 Basic Transaction Level Communication

TLM is basis for modularity and reuse in UVM. The communication happens through method calls. A TLM port specifies the API or function call that needs to be used. A TLM export supplies the implementation of the methods. Connections are between ports and exports and not between components. The ports and exports are parameterized by the transaction type being communicated. TLM supports both blocking (put, get/peek) and non-blocking (try\_put, try\_get/

try\_peek) methods. If there are multiple transaction that needs to be communicated TLM FIFO are used. In this way the producer need not wait until consumer consumes each transaction.

#### **3.4.2** Analysis ports and Exports

Analysis ports supports communication between one to many components. These are primarily used by coverage collectors and scoreboards. The analysis port contains analysis exports connected to it. When a UVM component class calls analysis port write method, then the analysis port iterates through the lists and calls write method of appropriate connected export. Similar to that of TLM FIFO Analysis ports also extends the feature to support multiple transaction.

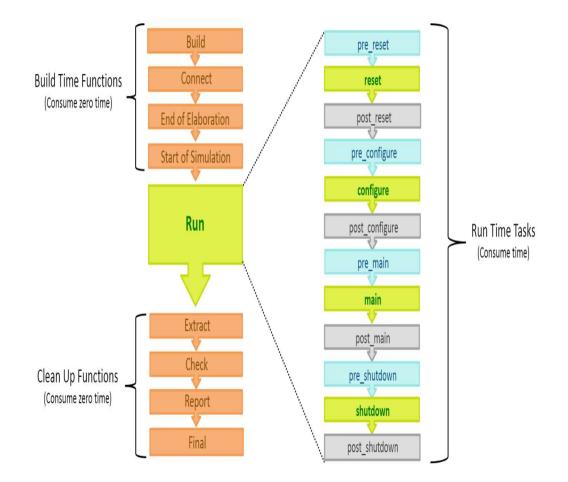

### 3.5 UVM Phases

All the UVM classes in section 3.3 have different simulation phases. UVM uses phases as ordered steps of execution. Phases are implemented as methods. When deriving a new component class, the testbench simulation will go through different steps to connect, construct and configure each components of the testbench component hierarchy. Moreover, if a particular phase is not needed in some of the component class, it is possible to ignore that particular phase, and the compiler will include in its compilation process. UVM phases are represented in Figure 3.2 [19].

#### **3.5.1 Build Phase**

The build phase instantiate UVM components under the hierarchy. Build phase is the only topdown phase among all other UVM phases. For example, the build phase of the env class will construct the classes for the agent and scoreboard [19].

Figure 3.2: UVM Phases

### 3.5.2 Connect Phase

The connect phase connects UVM subcomponents of a class. Connect phase is executed from the bottom up. In this phase, the testbench components are connected using TLM connections. Agent connect phase would connect the monitor to the scoreboard.

#### **3.5.3 End of Elaboration Phase**

Under this phase actions such as checking connections, setting up address range, initializing values or setting pointers and printing UVM testbench topology etc. are performed.

#### **3.5.4** Start of Simulation Phase

During start of simulation environment is already configured and ready to simulate. In this phase actions such as setting initial runtime configurations, setting verbosity level of display statements, orienting UVM testbench topology to check for correctness etc., are performed.

#### 3.5.5 Normal Run Phase

The run phase is the main execution phase, actual simulation of code will happen here. Run phase is a task and it will consume simulation time. The run phases of all components in an environment run in parallel. Any component can use either the run phase or the 12 individually scheduled phase. This phase starts at time 0. It is a better practice to use normal run phase task for drivers, monitors and scoreboards.

#### 3.5.6 Scheduled Run Phase

Any component can use either the run phase or the 12 individually scheduled phase.

#### 3.5.6.1 Pre Reset Phase

Actions that need to be performed before the DUT is reset are done in this phase. Starts at Ons and coincides with the run phase start time.

#### 3.5.6.2 Reset Phase

In this phase, the actual reset of the DUT occurs. This can be accomplished by running a sequence at the reset interface agent. Often, the reset logic is driven from the top level itself.

#### **3.5.6.3** Post Reset Phase

Post reset actions are done in this phase, like verifying that the device under test is in a specific state.

#### 3.5.6.4 Pre Configure Phase

This phase determines the configuration of the device under test.

#### 3.5.6.5 Configure Phase

Sets the device under test to the desired state as determined in pre configure phase. This would typically be register writes, table writes, memory initialization required for the device under test.

#### 3.5.6.6 Post Configure Phase

Follows the configure phase.

#### 3.5.6.7 Pre Main Phase

This phase executes before the main phase.

#### 3.5.6.8 Main Phase

This phase executes and runs the actual test cases.

#### 3.5.6.9 Post Main Phase

Post main phase performs additional tests to verify that device under test behaved correctly based on the main phase.

#### 3.5.6.10 Pre Shutdown Phase

This phase gets ready for shutdown.

#### 3.5.6.11 Shutdown Phase

Shutdown phase performs all end of test checks.

#### 3.5.6.12 Post Shutdown Phase

This phase performs anything that needs to happen after the end of checks are done. Components running in the run phase would end at the same time as the post-shutdown phase of components running in the scheduled phase mode.

#### 3.5.7 Extract Phase

In this phase, actions such as extracting data from scoreboard and DUT (zero-time back door), preparing final statistics and closing file handlers etc. are performed.

#### 3.5.8 Check Phase

Check phase checks the emptiness of the scoreboard, expected FIFOs and any backdoor accesses to memory content.

#### **3.5.9** Report Phase

The reporting phase is used to furnish simulation results, also write the outputs to file.

#### 3.5.10 Final Phase

Finally, this phase closes all file handles and display any messages.

## 3.6 UVM Macros

UVM macros are important aspect of the methodology. It is basically implemented methods that are useful in classes and in variables. Some of the most commonly used Marcos are:

- 'uvm\_component\_utils This macro registers is used when new 'uvm\_component classes are derived.

- 'uvm\_object\_utils Similar to 'uvm\_component\_utils but instead used with 'uvm\_object.

- 'uvm\_field\_int Registers a variable into factory. And implements functions like compare(), print(), and copy().

- 'uvm\_info During simulation time this macro is used to print useful messages from the UVM environment .

- 'uvm\_error Sends messages with an error tag to the output log.

## Chapter 4

## **System Architecture**

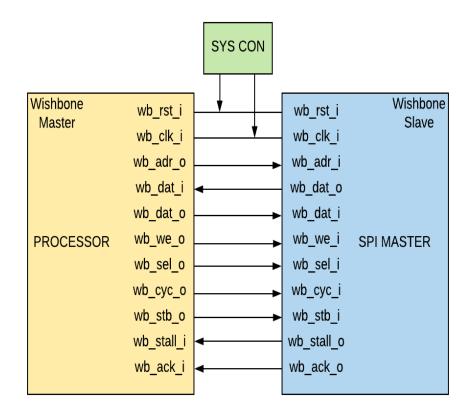

### 4.1 WISHBONE Interface

The WISHBONE System-on-Chip Interconnection Architecture shown in Figure 4.1 for portable and flexible IP Cores enables a design methodology for use with semiconductor IP cores. The WISHBONE interface alleviates System-on-Chip integration problems and results in faster design reuse by allowing different IP cores are connected to form a System-on-Chip. As defined, the WISHBONE bus uses both MASTER and SLAVE interfaces as part of the architecture. IP cores with MASTER interfaces initiate bus cycle transactions, and the participating IP cores with SLAVE interfaces can receive the designated bus cycles transactions. MASTER and SLAVE IP cores communicate through an interconnection interface called the INTERCON. The IN-TERCON is best thought of as a cloud that contains circuits and allows the communication with SLAVEs. INTERCON includes Point-to-point interconnection, Data flow interconnection, Shared bus interconnection and Crossbar switch interconnection [6]. WISHBONE Bus protocols include the implementation of an arbitration mechanism in centralized or distributed bus arbiters. The bus contention issue during the configuration of WISHBONE bus protocol is settled with

Figure 4.1: Wishbone Interface

the help of a Handshaking protocol and through the deployment of various arbitration schemes such as TDMA, Round Robin, CDMA, Token Passing, Static Priority etc. These strategies are applied based on the specific application in WISHBONE Bus [20].

### 4.2 WISHBONE I/O Registers

Table. 4.1 refers to the wishbone interface signals used for our Serial Peripheral Interface communication.

wb\_clk\_i: All internal WISHBONE logic are sampled at the rising edge of the wb\_clk\_i clock input.

| Port       | Width | Direction | Description                   |

|------------|-------|-----------|-------------------------------|

| wb_clk_i   | 1     | Input     | Master clock input            |

| wb_rst_i   | 1     | Input     | Asynchronous active low reset |

| wb_int_o   | 1     | Output    | Interrupt signal request      |

| wb_cyc_i   | 1     | Input     | Valid bus cycle               |

| wb_stb_i   | 1     | Input     | Strobe/core select            |

| wb_adr_i   | 32    | Input     | Address bit                   |

| wb_we_i    | 1     | Input     | Write enable                  |

| wb_dat_i   | 32    | Input     | Data input                    |

| wb_dat_o   | 32    | Output    | Data output                   |

| wb_ack_o   | 1     | Output    | Normal bus termination        |

| wb_stall_o | 1     | Output    | Stall communication           |

Table 4.1: WISHBONE I/O Ports

- wb\_rst\_i: wb\_rst\_i is active low asynchronous reset input and forces the core to restart. All internal registers are preset, to a default value and all state-machines are set to an initial state.

- wb\_int\_o: The interrupt request output is asserted back to the host system when the core needs its service.

- wb\_cyc\_i: When the cycle input wb\_cyc\_i is asserted, it indicates that a valid bus cycle is in progress. It needs to become true on (or before) the first wb\_stb\_i clock and stays true until the last wb\_ack\_o. The logical AND function of wb\_cyc\_i and wb\_stb\_i indicates a valid transfer cycle to/from the core. This logic is usually taken care of by the bus master.

- wb\_stb\_i: The strobe input wb\_stb\_i is true for any bus transaction request. While wb\_stb\_i is true, the other wishbone slave inputs wb\_we\_i, wb\_addr\_i, wb\_data\_i, and wb\_sel\_i are valid and reference the current transaction. The transaction is accepted by the slave core any time when wb\_stb\_i is true, and at the same time, wb\_stall\_o is false.

- wb\_adr\_i: The address array input wb\_adr\_i passes the binary coded address to the core. The MSB is at the higher number of the array. Of the all possible 32 address lines, the slave might only be interested in the relevant slave address

- wb\_we\_i: When the signal wb\_we\_i asserted, it indicates that the current bus cycle is a write cycle. When de-asserted, it indicates that the current bus cycle is a read cycle.

- wb\_dat\_i: The data array input wb\_dat\_i is used to pass binary data from the current WISHBONE Master to the core.

- wb\_dat\_o: The data array output wb\_dat\_o is the data returned by the slave to the bus master as a result of any read request.

- wb\_ack\_o: When asserted, the acknowledge output wb\_ack\_o indicates the normal termination of a valid bus cycle. There must be only one clock cycle with wb\_ack\_o high.

- wb\_stall\_o: Controls the flow of data into the slave. It will be true in any cycle when the slave can't accept a request from the bus master, and false any time a request can be accepted. It allows the slave core to control the flow of requests that need to be serviced based on master inputs.

# 4.3 Serial Peripheral Interface

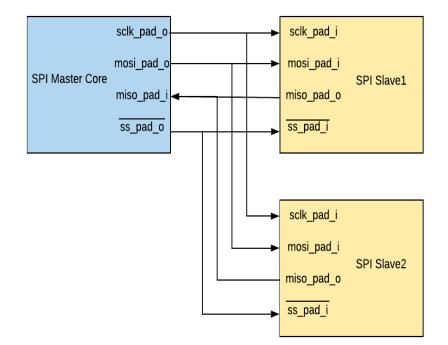

A Serial Peripheral Interface (SPI) module allows synchronous, serial and full duplex communication between a Microcontroller unit and peripheral devices and was developed by Motorola in the mid 1980s. Figure 4.2 represents the structural connection between master and slave core. The SPI bus is usually used to send and receive data between microcontrollers and other small peripherals units such as shift registers, sensors, SD cards, etc. When compared to other proto-

Figure 4.2: SPI Protocol

cols, the SPI protocol has the advantage of relatively high transmission speed, simple to use, an uses a small number of signal pins. Usually, the protocol divides devices into master and slave for transmitting and receiving the data. The protocol uses a master device to generate separate clock and data signal lines, along with a chip-select line to select the slave device for which the communication has to be established. If there is more than a slave device present, the master device must have multiple chip select interfaces to control the devices [21].

# 4.4 Data Transmission

The SPI bus interface consists of four logic signals lines namely Master Out Slave In (MOSI), Master In Slave Out (MISO), Serial Clock (SCLK) and Slave Select (SS).

Master Out Slave In (MOSI) - The MOSI is a unidirectional signal line and configured as an

output signal line in a master device and as an input signal line in a slave device. It is responsible for transmission of data in one direction from master to slave.

Master In Slave Out (MISO) - The MOSI is a unidirectional signal line and configured as input signal line in a master device and as an output signal line in a slave device. It is responsible for transmission of data in one direction from slave to master. When a particular slave is not selected, the MISO line will be in high impedance state.

Slave Select (SS) - The slave select signal is used as a chip-select line to select the slave device. It is an active low signal and must stay low for the duration of the transaction.

Serial Clock (SCLK) - The serial clock line is used to synchronize data transfer between both output MOSI and input MISO signal lines. Based on the number of bytes of transactions between the Master and Slave devices, required number of bit clock cycles are generated by the master device and received as input on a slave device [3].

In the standard SPI protocol, when the communication is initiated, the master device configures the system clock (known as SCLK) to a frequency less than or equal to the maximum possible frequency the slave device supports. The usual frequencies for the communication are in the range of 1-100 MHz. Standard SPI protocol supports single master and multiple devices. The master then transmits appropriate chip-select bit to Logic 0 to select the slave device, since the chip-select line is active low. Thus the communication between master and slave is established, unless the current communication cycle is discarded by the master controlling of slave devices are not possible. The clock (SCLK) is used by all the SPI signals to synchronize. The transmissions involve two shift register of a pre-configured word size are present one each at master and slave ends. As shown in Figure 4.3 both the shift registers act as a ring buffer [22]. While shifting out the data usually the least significant bit from the master is sent to the most significant bit position of the slave receive register, and at the same time, the least significant bit of the slave goes to the vacant least significant bit. Both master and slave register acting in a left

Figure 4.3: Shift Register

shift register fashion and the register values are exchanged with respect to SCLK [6]. If more data needs to be exchanged, then the shift registers are loaded with new data, the and the process is repeated. Finally, after the data values are transmitted then master stops toggling the SCLK and it deselects the slave [22].

# 4.5 Hardware Architecture

The designed SPI Master IP core is compatible with the SPI protocol and bus principle. At the host side, the design is equivalent to the slave devices of wishbone bus specification complaint. The overall structure of the Wishbone complaint SPI Master core device can be divided into three functional units(Figure 4.4): Clock generator, Serial Interface and Wishbone Interface [23].

## 4.5.1 Design of Clock Generation module (spi\_clk\_gen)

The clk\_gen is responsible for the generation of the clock signal from the external system clock wb\_clk\_i, in accordance with different frequency factor of the clock register and produce the output signal s\_clk\_o. Since there is no response mechanism for Serial Peripheral Interface, in

Figure 4.4: SPI Master Architecture

order to ensure the reliability of timing, the clk\_gen module can generate reliable serial clock transmission with odd or even frequency division in the register. Clock divider is essential part of digital ASIC and FPGA design, the idea here is to produce frequency relevant to the communication system. Even frequency division is achieved in order to save resources. The core generates the s\_clk\_o by dividing the wb\_clk\_i; Arbitrary clock output frequency is achieved by changing the value of the divider. The expression of s\_clk\_o and wb\_clk\_i is as follows [22].

$$f_{sclk} = f_{wbclk} / (DIVIDER + 1) * 2$$

#### **4.5.2** Serial data transfer module design (spi\_shift)

Serial data transfer module forms the data transfer core module. It is responsible for converting input parallel data into serial output data to transmit at MOSI and convert input MISO serial data into parallel out. The Receive and Transmit register share same flip-flops. It means that what data is received from the input data line in one data transfer will be transmitted on the output line in the next transfer if no write access to the transmit register was performed between the transfers. The advantage of this is it uses fewer hardware resources, therefore, lesser power consumption. [27] SPI Master core in host side acts as a slave device to receive input data, and at the same time as the master device transmits output data [22].

#### 4.5.3 Top-level module (spi)

The role of the top-level module is to get the basic structure of high-speed reusable SPI bus sub-components to work smoothly. Therefore, the top-level of the SPI module controls normal operation of clock generator module and serial data transmission module [22].

## 4.6 SPI Registers

The SPI master core uses the register [24] mentioned in the Table 4.2

#### 4.6.1 RxX Register

The Data Receive registers hold the value of data received from the last executed transfer. CTRL register holds the character length field for example if CTRL [9:3] is set to 0x10, bit RxL[15:0] holds the received data. Registers Rx1, Rx2 and Rx3 are not used If character length is less or equal to 32 bits, likewise Registers Rx2 and Rx3 are not used if character length is less than 64

| Name    | Address | Width | Access | Description                 |

|---------|---------|-------|--------|-----------------------------|

| Rx0     | 0x00    | 32    | R      | Data receive register 0     |

| Rx1     | 0x04    | 32    | R      | Data receive register 1     |

| Rx2     | 0x08    | 32    | R      | Data receive register 2     |

| Rx3     | 0x0C    | 32    | R      | Data receive register 3     |

| Tx0     | 0x00    | 32    | R/W    | Data transmit register 0    |

| Tx1     | 0x04    | 32    | R/W    | Data transmit register 1    |

| Tx2     | 0x08    | 32    | R/W    | Data transmit register 2    |

| Tx3     | 0x0C    | 32    | R/W    | Data transmit register 3    |

| CTRL    | 0x10    | 32    | R/W    | Control and status register |

| DIVIDER | 0x14    | 32    | R/W    | Clock divider register      |

| SS      | 0x18    | 32    | R/W    | Slave select register       |

Table 4.2: SPI Master core registers

bits and so on.

## 4.6.2 TxX Register

The Data Receive registers hold the value of data transmitted from the transfer. CTRL register holds the character length field for example if CTRL [9:3] is set to 0x10, bit TxL[15:0] holds the received data. Registers Tx1, Tx2 and Tx3 are not used If character length is less or equal to 32 bits, likewise Registers Tx2 and Tx3 are not used if character length is less than 64 bits and so on.

## 4.6.3 ASS Register

If ASS bit is set, the ss\_pad\_o signal is generated automatically. When the transfer is started by setting CTRL[GO\_BSY], the slave select signal which is selected in SS register is asserted by the SPI controller and is de-asserted after the transfer is finished. If ASS bit is cleared, then the

slave select signals are asserted and de-asserted by writing and clearing the bits in SS register.

### 4.6.4 **DIVIDER Register**

The value in this field divides the frequency of the system clock (wb\_clk\_i) to generate the serial clock(s\_clk) on the output sclk\_pad\_o. The desired frequency is obtained according to equation 1.

### 4.6.5 SS Register

When CTRL[ASS] bit is cleared, writing 0x1 to any of the bit locations of this field sets the proper ss\_pad\_o line to an active state and writing 0x0 sets the line back to the inactive state. When CTRL [ASS] bit is set, writing 1 to any bit location of this field will select appropriate ss\_pad\_o line to be automatically driven to an active state for the duration of the transfer, and will be driven to an inactive state for the rest of the time.

### 4.6.6 IE Register

When this bit is set, the interrupt output is set active once after a transfer is finished. The Interrupt signal is cleared after a Read or Write to any register.

#### 4.6.7 LSB Register

When LSB bit is set to 0x1, the least significant bit is sent first on the line (bit TxL[0]), and the first bit received from the line will be put in the least significant bit position in the Rx register (bit RxL[0]). When this bit is cleared, the MSB is transmitted /received first (CHAR\_LEN field in the CTRL register selects which bit in TxX/RxX register).

### 4.6.8 Tx\_NEG Register

When Tx\_NEG bit is set, the mosi\_pad\_o signal is sent on the falling edge of a sclk\_pad\_o clock signal, or otherwise, the mosi\_pad\_o signal is sent on the rising edge of sclk\_pad\_o.

## 4.6.9 Rx\_NEG Register

When Rx\_NEG bit is set, the miso\_pad\_i signal is received on the falling edge of a sclk\_pad\_o clock signal, or otherwise, the miso\_pad\_i signal is received on the rising edge of sclk\_pad\_o.

## 4.6.10 GO\_BSY Register

Writing 0x1 to this bit starts the transfer and remains set during the transfer. Automatically cleared after the transfer is finished. Writing 0x0 to this bit has no effect.

## 4.6.11 CHAR\_LEN Register

This field specifies the number of bits to be transmitted in one transfer. Can send up to 64 bits in one transfer.

CHAR\_LEN =  $0x01 \dots 1$  bit CHAR\_LEN =  $0x02 \dots 2$  bits  $\dots$ CHAR\_LEN =  $0x7f \dots 127$  bits CHAR\_LEN =  $0x00 \dots 128$  bits

# 4.7 Limitation of Standard SPI and Advancements

Standard SPI communication is a single-master communication. Therefore all the communication can only have one master device active at any time. This limits the functional aspects of the devices that are connected to the SPI topology. To overcome this more advanced designs adopt the parameterization method, identify the master/slave devices automatically and use Time Sharing Multiplex (TSM) technology to control the same slave device at the same time [25].

# Chapter 5

# **Test Methodology and Results**

# 5.1 Testbench Components

The SPI master core is verified along with the SPI slave model. Initially, the SPI master and slave have configured appropriately (for example at the master end no. of bits-32, transmit-posedge, receive-negedge). The basic idea of the verification is to send data from both master and slave ends. And after the transfer is completed verify the exchanged data at both the ends. The Figure. 5.1 shows the testbench module approach. Below each of the components is explained.

## 5.1.1 Test top

The top-level module is responsible for integrating the testbench module with the device under test. This module instantiates two interfaces, one for the master and another for the slave. Then the master interface is wired with SPI master core and likewise slave interface with SPI slave model. The top module also generates the clock and registers the interface into the config database so that other subscribing blocks can retrieve. Finally, the module calls the run\_test function which starts to run the uvm\_root.

Figure 5.1: UVM Testbench model

# 5.1.2 spi\_interface

The interface block declares all the WISHBONE slave logic signals. The communication with the master and slave core happens through WISHBONE bus function model. The block also samples the input and output signals using two different clocking blocks, one for driver and another for the monitor. Clocking block helps to synchronize all logic signals to a particular clock. It also helps to separate the timing details from the structural, functional and procedural elements of the testbench.

#### 5.1.3 spi\_package

The package class typically includes all SystemVerilog testbench components and make the scope available to the entire build process.

### 5.1.4 spi\_test

The test class is created by extending the uvm\_test class. Then the class is registered to factory using uvm\_component\_utils macro. In the build phase, the lower level SPI environment class is created and configured. Instead of the run phase, the test class contains two of the twelve scheduled phases. Reset phase typically resets the device under test. The main phase used to create the sequences and start running the sequencer for the required number of tests. Whenever there needs to be a blocking phase execution, phase raise objection is invoked and like to unblock phase drop objection is used.

## 5.1.5 spi\_environment

SPI environment is a container component containing the agent and scoreboard. It is created using uvm\_env virtual base class. In the build phase components within the environment are instantiated. And in the connect phase, the connections are made between components.

## 5.1.6 spi\_agent

Currently, there is only one agent container component is used within the project. The SPI agent container is configured as an active component. SPI agent is created using uvm\_agent virtual base class. In the build phase, the agent builds Sequencer, Driver and Monitor components. In the connect phase, the driver and sequencer are connected.

#### 5.1.7 spi\_sequence\_item

The data flows through the testbench from component to component in the form of packets called as transaction class or sequence item. The SPI sequence item class is created by extending the uvm\_sequence\_item class. The transaction packet consists of register configuration items (control, divider, and slave select) and data items (input, output and expected) for both master and slave. Then register the class and properties to factory using uvm\_object\_utils macro. A constructor function is defined for the sequence item. Randomization is applied to sequence items.

#### 5.1.8 spi\_sequence

The user-defined SPI sequence class uses uvm\_sequence as its virtual base class. This class is a parameterized class with the parameter being the SPI sequence item associated with this sequence. Body() method is called, and code within this method gets executed when the sequence is run. Objections are typically raised and dropped in the pre\_body() and post\_body() methods of a sequence. Within the body() method the register sequence items and the data sequence items are constrained randomized.

### 5.1.9 spi\_sequencer

SPI sequencer is the component that runs the sequences. The sequencer has a built-in port called sequence\_item\_export to communicate with the driver. Through this port, the sequencer can send a request item to the driver and receive a response item from the driver. This class is parameterized with SPI sequence item.

Figure 5.2: UVM Sequencer Driver Communication

## 5.1.10 spi\_driver

SPI driver is the component along with WISHBONE bus function model that takes the generated sequence item from the sequencer and drives it into the DUT according to WISHBONE protocol. The driver is created extending uvm\_driver. In order to drive the data virtual interface handle is passed to the driver during the build phase. The SPI driver initially calls the WISHBONE reset method. Then a forever thread is created. In this thread initially, the driver gets the next sequence item from sequencer using the seq\_item\_port method. This synchronizes with the body function of the sequence as given in the Figure 5.2 and packet is driven into the DUT using the bus function model. In the end, the driver waits for transfer complete interrupt to repeat the thread loop.

#### 5.1.11 spi\_monitor

SPI monitor senses the response from the DUT. In order to monitor the data, virtual interface handle is passed to monitor during the build phase. The monitor is created extending uvm\_monitor. Initially, the monitor waits for the first SPI data transfer to begin. Then In the forever thread, the monitor waits for the SPI data transfer to complete. SPI monitor uses WISHBONE bus function model to read the response data from DUT. The sequence-item data packet containing the actual and expected output is now broadcast to the environment using analysis write port. The monitor then waits again for a new transfer to being, and this process repeats in a loop.

#### 5.1.12 spi\_scoreboard

SPI scoreboard is the component which has transaction level checkers and coverage collectors to verify the functional correctness of a given DUT. Scoreboard class is extended from the uvm\_scoreboard base class. TLM analysis FIFOs to connect to the monitor. In the run phase, the input packet is retrieved from the driver, while the output packet is retrieved from the monitor. Then the transaction level functional coverage method is performed using a sampling method to get the coverage. In the end, then when the report phase is invoked the results are displayed.

#### 5.1.13 wishbone\_bfm

The WISHBONE bus function model at the driver side transfers the transaction level packets into WISHBONE specific pin level data. At the monitor side, it receives the pin level activities WISHBONE and wraps into transaction packets for higher level modules to use. WISHBONE bus function module implements three methods write, read and reset. The bus function module is non-synthesizable code and written using SystemVerilog.

# 5.2 Testbench Results

The functional verification of the SPI core controller was carried out successfully with the following results.

# 5.2.1 SPI Master Controller Synthesis Benchmarking

The project aims to create a functional verification environment for SPI controller. For this purpose the IP core was reused from Opencores, but with some modification. The logic synthesis of the module was performed in the TSMC 180nm, 65nm and SAED 32nm technology. Area, Power and Timing of the final module were captured Table 5.1

| Туре                   | Technology node                | 32 nm   | 65 nm   | 180 nm   |