# Variation-sensitive Monitor Circuits for Estimation of Die-to-Die Process Variation

Islam A.K.M Mahfuzul<sup>\*</sup>, Akira Tsuchiya<sup>\*</sup>, Kazutoshi Kobayashi<sup>†</sup> and Hidetoshi Onodera<sup>\*‡</sup> <sup>\*</sup> Graduate School of Informatics, Kyoto University, Yoshida-honmachi, Sakyo-ku, Kyoto 606-8501, JAPAN

<sup>†</sup>Graduate School of Science and Technology, Kyoto Institute of Technology, Kyoto, JAPAN

<sup>‡</sup> JST, CREST

email: {mahfuz,tsuchiya,kobayasi,onodera}@vlsi.kuee.kyoto-u.ac.jp Tel: +81-75-753-5353, Fax: +81-75-753-5343

Abstract—We propose a set of variation-sensitive ring oscillators (RO) to estimate Die-to-Die process parameter variation. ROs are designed to have different sensitivity to each parameter variation. A method suitable to estimate variation from different ROs is proposed. We have fabricated test chip and successfully estimated process parameter variation. Variation results are correlated with that in Process Control Module data.

# I. INTRODUCTION

As the scaling of Silicon CMOS process technology progresses, variation in transistor performance has been becoming serious problem. In 65nm process and beyond, this variability plays a major role in chip performance. To improve yield under PVT (Process, Voltage and Temperature) fluctuation, worst case design methodology is being followed which results in suboptimal chip performance [1]. As variation increases with every new process node and impact of variation increases under low supply voltage operation, we are facing a serious problem that is how to get maximum benefit from the future nodes. A solution to this scenario can be to tune chip performance in post-silicon. Adaptive techniques such as Adaptive Body Bias (ABB) and Adaptive Supply Voltage (AVS) have been proposed to reduce design margin and control chip performance [2], [3].

Variation in CMOS transistor performance can be divided into die-to-die (D2D) and within-die (WID) variation. As the technology scaling continues, WID variation is becoming more significant [4]. However, WID variation is mainly random and thus its impact gets reduced by the number of stages. On the other hand, D2D variation affects the performances of all transistors in a chip in the same direction (fast or slow) and therefore, D2D variation plays major role in determining chip performance such as leakage current, frequency etc. Major of the D2D Variation in CMOS transistor performance are mainly due to MOS gate length and threshold voltage variation [5]. For fine tuning of chip performance using adaptive techniques, on-chip measurement of process parameters such as threshold voltage and gate length are needed.

Many of the monitor circuits proposed so far to monitor process variation use either device arrays [6] or op-amps [7] and thus require huge area and measurement time that makes them unsuitable for on-chip parameter estimation. A method to calculate the saturated current of each MOS transistor is also proposed [8]. But, to compensate chip performance we need to know the variation of individual process parameter. Because of easy implementation and fast on-chip measurement RO is a good choice for this purpose [9]. But, RO frequency is affected by many process parameter variations simultaneously and thus it is difficult to extract single parameter variation. This paper proposes a set of variation-sensitive ROs to estimate D2D process variation from on-chip measurement values. We fabricate test chip in 65nm process and are able to estimate variation of each process parameter from measured values. Our estimation results are well within the SPICE corner model and correlated with that in PCM data.

The remainder of this paper is organized as follows. In section II, an estimation method to extract process parameter variation is proposed. In section III, some design techniques to realize variation-sensitive ROs is demonstrated. In section IV, test chip structure and measurement results are discussed. Estimation results and their validation are also discussed here. Finally, section V concludes our discussion.

# **II. PROPOSED ESTIMATION METHOD**

In order to estimate process parameter variations simultaneously, an estimation method is needed. We propose an estimation method which combines circuit technique and transistor model for estimation. Monitor circuits suitable for this method will be discussed in section III.

## A. RO Frequency Model

In this work, we focus on the estimation of D2D variation in three key parameters of pMOS threshold voltage ( $V_{\rm THP}$ ), nMOS threshold voltage ( $V_{\rm THN}$ ) and gate length (L). Suppose  $\Delta V_{\rm THP}$ ,  $\Delta V_{\rm THN}$  and  $\Delta L$  are D2D variations of those parameters to be estimated and  $\Delta f$  is the corresponding frequency shift that we can measure. If  $\Delta V_{\rm THP}$ ,  $\Delta V_{\rm THN}$  and  $\Delta L$  are small, those variations can be related in a linear equation as shown in Eq. (1) where  $k_{\rm P}$ ,  $k_{\rm N}$  and  $k_{\rm L}$  are sensitivity coefficients.

$$\Delta f = f_{\rm M} - f_{\rm Ref} = k_{\rm P} \Delta V_{\rm THP} + k_{\rm N} \Delta V_{\rm THN} + k_{\rm L} \Delta L \quad (1)$$

Here,  $f_M$  is measured frequency and  $f_{\text{Ref}}$  is reference or nominal frequency. We can get  $f_{\text{Ref}}$  by SPICE simulation

using RC extracted netlist from layout. In order to cancel within-die random effect, RO with large number of stages or average value from many ROs should be used. Sensitivity coefficients can be calculated from SPICE simulation. RC extracted netlist should be used because parasitic capacitances affect frequency sensitivity.

# **B.** Estimation Procedure

In Eq. (1), there are three unknown parameters. So, at least three equations are needed to extract variation of these three unknown values. The three equations can be derived from three ROs whose sensitivity vectors form a non-singular matrix and have small condition number. The amount of variation of each process parameter will be calculated by solving Eq. (2).

$$\vec{V} = \mathbf{S}^{-1}\vec{F} \tag{2}$$

where

$$\vec{V} = \begin{pmatrix} \Delta V_{\text{THP}} \\ \Delta V_{\text{THN}} \\ \Delta L \end{pmatrix}, \mathbf{S} = \begin{pmatrix} k_{\text{P1}} & k_{\text{N1}} & k_{\text{L1}} \\ k_{\text{P2}} & k_{\text{N2}} & k_{\text{L2}} \\ k_{\text{P3}} & k_{\text{N3}} & k_{\text{L3}} \end{pmatrix}, \vec{F} = \begin{pmatrix} \Delta f_1 \\ \Delta f_2 \\ \Delta f_3 \end{pmatrix}$$

(3)

Here,  $\vec{V}$  is the vector for the variations of  $V_{\text{THP}}$ ,  $V_{\text{THN}}$ and L. **S** is the sensitivity matrix and  $\vec{F}$  is the vector for the frequency shift from the nominal value.  $(k_{\text{P1}}, k_{\text{N1}}, k_{\text{L1}})$ ,  $(k_{\text{P2}}, k_{\text{N2}}, k_{\text{L2}})$  and  $(k_{\text{P3}}, k_{\text{N3}}, k_{\text{L3}})$  are sensitivity vectors for three ROs. By considering the effects of other parameters and the error in the measurement, the vectors should separate from each other sufficiently.

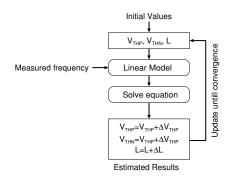

Solving Eq. (2) may not give us accurate result because of the non-linear nature of RO frequency according to process variation. In order to cope with this non-linear nature, we propose an iterative estimation method shown in Fig. 1. Here, we guess the initial values for each process parameter and simulate the corresponding frequencies for the ROs. Initial values for these parameters can be derived from SPICE model. We then get the measured values from chip and build linear models for each circuit. We get estimated variations by solving Eq. (2). In the next iteration, initial values are updated by adding the estimation results from the previous iteration. This procedure is then iterated until the result convergences (difference between measured value and simulated value is zero). From experiments, we found that this method convergences after 4 iterations in most of the cases.

#### **III. ROS FOR ESTIMATION OF PROCESS VARIATION**

In this section, we demonstrate some design techniques to realize variation-sensitive ROs. Sensitivities are checked by SPICE simulation. Commercial 65nm process technology is assumed in our simulation. Based on the simulation results, we propose a set of ROs which is best suited for estimation.

# A. RO Design

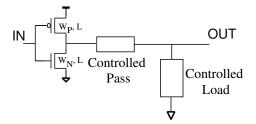

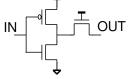

A general guideline to design ROs with enhanced sensitivities is demonstrated in Fig. 2. We can modify the transistors in an inverter or control the passing current while charging

Fig. 1. Proposed estimation procedure of process parameters

Fig. 2. Tunable parameters in a inverter structure

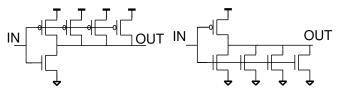

Fig. 3. pMOS rich inverter Fig. 4. nMOS rich inverter

and discharging the output load to get enhanced process sensitivity. We can control the output load also to change the sensitivities. Changing the gate length will affect the sensitivity to gate length variation. However, in order to avoid unnecessary influence from unknown sources, we have used MOS transistors with identical layout. Therefore, we avoided changing gate length in our design. Modifying gate width changes the charging and discharging current flow and thus the sensitivities change. Below are some examples of inverter structures to realize several variation-sensitive ROs.

1) RO with Parallel MOS: Increasing pMOS transistor's size in the inverter structure will make the RO frequency more sensitive to nMOS parameters. We can increase gate width of pMOS transistor or we can place multiple pMOS transistors in parallel. In order to maintain regularity, we have designed inverters with parallel pMOS transistors. Fig. 3 shows an inverter where pMOS is 4 times larger than that of the standard cell. Similarly, inverter structure shown in 4 will be more sensitive to pMOS parameters. From simulation results for a pMOS rich inverter cell RO, 21% increase in  $V_{\rm THN}$  sensitivity and 20% decrease in  $V_{\rm THP}$  sensitivity is calculated compare to that of the standard inverter cell RO.

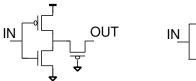

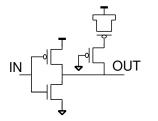

2) RO with Pass Gate: Authors in [9] used ROs with pass gates for estimation of threshold voltage variation since this kind of structure makes RO frequency highly sensitive to

Fig. 6. Inverter with a nMOS pass

Fig. 5. Inverter with a pMOS pass gate

Fig. 7. Inverter with pMOS controlled load

Fig. 8. Inverter with nMOS controlled load

TABLE I SENSITIVITY COEFFICIENTS OF ROS

gate

| RO Type        | Gate Length[nm] | $k_P$  | $k_N$  | $k_L$  |

|----------------|-----------------|--------|--------|--------|

| Standard       | 60              | -0.038 | -0.035 | -0.026 |

| pMOS pass gate | 60              | -0.24  | 0.052  | -0.085 |

| nMOS pass gate | 60              | 0.054  | -0.34  | -0.029 |

| pMOS rich      | 60              | -0.031 | -0.041 | -0.026 |

| nMOS rich      | 60              | -0.046 | -0.034 | -0.027 |

| pMOS load      | 60              | -0.020 | -0.048 | -0.023 |

| nMOS load      | 60              | -0.044 | -0.022 | -0.027 |

threshold voltage change. We therefore have used pass gates to increase sensitivity to threshold voltage. Figs. 5 and 6 show inverters with a pMOS and a nMOS pass gates. For a RO with pMOS pass gate,  $V_{\text{THP}}$  sensitivity increases by 5 times than that of a standard cell RO. For a RO with a nMOS pass gate  $V_{\text{THN}}$  sensitivity increases by 7 times than that of a standard cell RO.

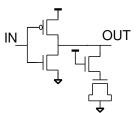

3) RO with MOS Controlled Load: Figs. 7 and 8 are ROs with an extra load in the output. Here, the extra load is controlled by MOS pass gate. For Fig. 7, when  $V_{\text{THP}}$ increases, resistance for the pMOS pass gate increases. As a result, the inverter sees smaller load and hence delay decreases. Thus, the effect of  $V_{\text{THP}}$  variation gets reduced. Sizing of the load determines the sensitivity for this structure. For RO in Fig. 7 where the extra load is equivalent to 4 inverter cells, sensitivity to  $V_{\text{THP}}$  decreases by 45% than that of a standard cell RO.

Table I summarizes sensitivity coefficients for these ROs to  $V_{\text{THP}}$ ,  $V_{\text{THN}}$  and L.

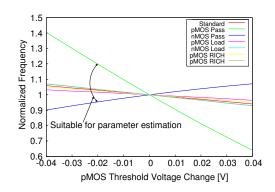

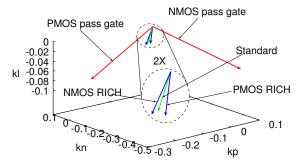

# B. RO Set for Process Parameter Estimation

Fig. 9 shows frequency changes for various types of ROs according to  $V_{\rm THP}$  variation. The question is how to choose the ROs for process parameter estimation. ROs whose sensitivity vectors form large angles between them are most suitable for this. Fig. 10 shows sensitivity vectors for ROs with pass gates and rich inverters along with a standard inverter. From Fig. 10, we observe that ROs with pass gates are suitable for monitoring threshold voltage variation. But, to get gate length variation

TABLE II Condition Number of Sensitivity Matrices for different RO sets

|     |          | RO Set    |           |                  |

|-----|----------|-----------|-----------|------------------|

| No. | RO #1    | RO #2     | RO #3     | Condition Number |

| 1   | Standard | pMOS Pass | nMOS Pass | 34.2             |

| 2   | Standard | pMOS rich | nMOS rich | 126.6            |

| 3   | Standard | pMOS Load | nMOS Load | 40.0             |

Fig. 9. Frequency changes for ROs to pMOS threshold voltage change

Fig. 10. Sensitivity vectors of various types of ROs

also we need another RO along with ROs with pass gates to form Eq. (2). A well-conditioned sensitivity matrix is needed so that estimation result will be robust against uncertainties. Table II shows condition numbers of sensitivity matrices for different RO sets. Condition number is a good indicator on how robust estimation result will be against the uncertainties in sensitivity coefficients or in measurement values. In Table II, RO set with ROs with pass gates and a standard cell RO has the smallest condition number. Considering layout complexity and area, the combination of a standard inverter RO and ROs with pass gates are the best choice for process parameter estimation.

#### C. Validation by Simulation

We propose a standard inverter RO and ROs with pass gates as monitor circuits for process parameter estimation. We need to check how accurate estimation results will be when some uncertainties are there in measurement or when some effect of parameters other than our interest are involved. In order to show validity, we first show that our monitor circuits can estimate process variation correctly even if some amount of error exists in the measurement. Next, we show that by doing iteration error becomes less.

1) Simulation Setup: To emulate real chip condition where some amount of variation in process parameters are involved, experiment based on SPICE simulation is conducted. First, some amount of variation in each process parameter is inserted in SPICE model and the corresponding frequencies for our circuits are simulated. Simulated frequencies are then assumed to be the measured values. Next, our proposed monitor circuits are used to estimate the inserted amount of variation for each parameter. Finally, estimated results are compared with the inserted values. Following two scenarios are considered in the experiment.

- 1) Effect of error in RO frequency measurement

- 2) Effect of non-linearity in RO frequency to process variation

For simplicity, we demonstrate experimental results for  $(\pm \sigma, \pm \sigma)$  variation for  $V_{\text{THP}}$  and  $V_{\text{THN}}$  only.

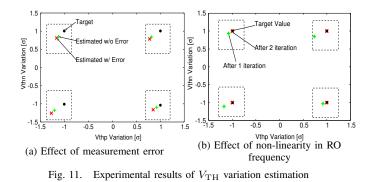

2) Simulation Results: Fig. 11 shows the estimation results for our proposed set of ROs. In Fig. 11 X-axis and Y-axis refer to  $V_{\text{THP}}$  and  $V_{\text{THN}}$  variation respectively. "•" points are the inserted variations. In Fig. 11(a) "+" points are estimated variations when no error exists in measurement and "×" points are estimated results when 1% error exists in measurement. In Fig. 11(b) "+" and " $\times$ " points are estimated variations after 1 and 2 iterations. In Fig. 11 we see that target variation is achieved with maximum error of 25% when no error exists in the measured value. This error is due to the non-linear nature of RO frequency. The important thing here is in spite of 1%error in the frequency, estimation results do not move from the original values. Fig. 11(b) shows that after 2 iterations the error improves from 25% to 1%. So, our proposed circuits are able to estimate process variations correctly even if some error exists in the measurement.

## IV. ESTIMATION RESULT FROM TEST CHIP

We fabricated test chip in 65nm process to check our proposed monitor circuits. In this section, we describe our test structure and estimation results.

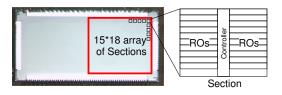

#### A. Chip Design

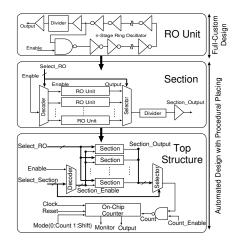

We designed the ROs of various types described in Section III. We put 270 sections in the chip in an array of  $15 \times 18$  sections. Each section contains various types of ROs. Therefore, 270 ROs of the same type are integrated in a single die. Fig. 12 shows the layout of our chip. Fig. 13 shows the

Fig. 12. Test chip in 65nm process

Fig. 13. Block diagram of test structure

TABLE III SIMULATION AND MEASUREMENT RESULT OF RO FREQUENCIES

|           | Simulation[at TT] | Measurement | Variation( $\sigma/\mu$ )[%] |      |

|-----------|-------------------|-------------|------------------------------|------|

| RO Type   | [MHz]             | [MHz]       | WID                          | D2D  |

| Standard  | 2583              | 2976        | 1.05 - 1.2                   | 1.47 |

| pMOS Pass | 546               | 613         | 3.73 - 4.72                  | 4.34 |

| nMOS Pass | 446               | 674         | 4.24 - 5.32                  | 3.26 |

| pMOS Load | 1558              | 1805        | 1.09 - 1.32                  | 1.27 |

| nMOS Load | 1573              | 1839        | 1.05 - 1.26                  | 1.30 |

| pMOS Rich | 1731              | 1881        | 0.939-1.14                   | 1.30 |

| nMOS Rich | 1590              | 1879        | 0.919-1.13                   | 1.26 |

block diagram of our test structure. On-chip counter is used to capture RO frequency. RO are frequencies are divided by 64 to capture on-chip. Each RO is 13 staged. The purpose of this kind of design is to get both WID and D2D variation. D2D variation is used to estimate D2D process parameter variation and WID variation will be used to determine the number of stages needed for each RO to estimation variation correctly.

# B. Measurement Result

Table III shows measured data from our test chip. Measurement value shown in Table III is the average of all frequency measurements from 20 chips. SPICE simulation results of our ROs at TT (Typical-Typical) corner model are also presented. Large difference between simulated and measured values are observed. These differences are caused because of variation in process parameters. The amount of difference varies from RO-structure to RO-structure which suggests that process parameter the variation have different impacts on circuits based on their structure. WID and D2D variations are also shown in Table III. Large variation in frequency for ROs with pass gates are observed because these ROs are highly sensitive to threshold voltage variation.

Fig. 14. Comparison between process parameter variation in our estimation result and that in PCM data

#### C. Estimation Result

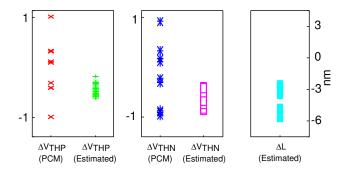

Values of  $\Delta V_{\text{THP}}$ ,  $\Delta V_{\text{THN}}$  and  $\Delta L$  are estimated using our proposed monitor circuits for 20 chips. In this fabrication, 9 PCM (Process Control Module) transistor performance are provided from the foundry. We therefore compared our estimated D2D variation of  $V_{\text{THP}}$  and  $V_{\text{THN}}$  with those in PCM data. Fig. 14 shows the estimated D2D variation and those in PCM data. Y-axis is normalized to -1 to 1 by the variation in PCM data. From Fig. 14 we see that the estimated variation is within the variation range of PCM data. PCM data contains both the D2D and WID variation. As we estimated only D2D variation, our estimated variation range is smaller than that in PCM data. Fig. 14 also shows the estimated amount of gate length variation which spans from -6nm to -2.5nm.

Our method takes the difference between measured value and simulated value of RO frequencies at TT SPICE model and extract process parameter variation from these differences. Our estimation method is iterated until this difference becomes zero. So, simulation results using estimation result should match with measurement values. Table IV shows comparison between measurement and simulation values for all RO frequencies for a particular chip. Estimated amount of variation for each parameter is inserted in SPICE model during simulation. As first three ROs in Table IV are used for estimation, simulation and measurement results for the first three ROs match completely. This validates that our proposed estimation technique works correctly. If the estimations are correct and major of the D2D variation can be expressed by the variation in the parameters of our interest, then we should get close values between measurement and simulation for other ROs also. Small amount of difference is there for other ROs in Table IV which suggest that major of the D2D variation can be expressed by  $V_{\text{THP}}$ ,  $V_{\text{THN}}$  and L variation. However, relatively large difference is observed for pMOS rich RO. One possible reason for this difference may be the effect of strain in nMOS transistors. This is because in the pMOS rich inverter cell design, we made a mistake by not placing dummy transistors below the duplicated pMOS transistors, and hence there are wide STI regions between nMOS transistors which may affect nMOS characteristics.

TABLE IV COMPARISON BETWEEN MEASUREMENT AND SIMULATION USING ESTIMATED RESULTS FROM OUR PROPOSED ROS

| RO Type   | Measurement[MHz] | Simulation[MHz] | Difference[%] |

|-----------|------------------|-----------------|---------------|

| Standard  | 2934             | 2934            | 0.0           |

| pMOS Pass | 586              | 586             | 0.0           |

| nMOS Pass | 673              | 673             | 0.0           |

| pMOS Load | 1777             | 1773            | -0.3          |

| nMOS Load | 1813             | 1774            | -2.2          |

| pMOS Rich | 1849             | 1922            | 4.0           |

| nMOS Rich | 1856             | 1840            | -0.8          |

# V. CONCLUSION

In this paper, we propose a set of variation-sensitive ROs for estimation of  $V_{\rm THP}$ ,  $V_{\rm THN}$  and L variation. We develop a method based on linear model to extract process parameter variation from these ROs. General guideline on how to design variation-sensitive ROs is demonstrated. Experimental results based on SPICE simulation show that our proposed circuits are suitable for process parameter estimation under the presence of uncertainties. We fabricate test chip to verify our circuits and successfully estimated process variation.  $V_{\rm THP}$  and  $V_{\rm THN}$  variation range in our estimated result is within the variation range in PCM data. SPICE simulation results using our estimated amount of variation match closely with measured values for all ROs. In future, we will define the number of stages needed for on-chip parameter estimation correctly.

#### **ACKNOWLEDGMENTS**

The authors acknowledge the support of VLSI Design and Education Center (VDEC), the University of Tokyo. The authors are also grateful to STARC, E-shuttle Inc. and Fujitsu Ltd.

#### REFERENCES

- B. Calhoun, Y. Cao, X. Li, K. Mai, L. Pileggi, R. Rutenbar, and K. Shepard, "Digital circuit design challenges and opportunities in the era of nanoscale CMOS," *Proceedings of the IEEE*, vol. 96, pp. 343– 365, March 2008.

- [2] T. Mudge, K. Flautner, D. Blaauw, and S. M. Martin, "Combined dynamic voltage scaling and adaptive body biasing for lower power microprocessors under dynamic workloads," *International Conference on Computer-Aided Design*, vol. 0, pp. 721–725, 2002.

- [3] J. Tschanz, S. Narendra, R. Nair, and V. De, "Effectiveness of adaptive supply voltage and body bias for reducing impact of parameter variations in low power and high performance microprocessors," *IEEE Journal of Solid-State Circuits*, vol. 38, pp. 826–829, May 2003.

- [4] H. Onodera, "Variability: Modeling and its impact on design," IEICE transactions on electronics, vol. E89-C, p. 342, 2006.

- [5] S. Borkar, T. Karnik, S. Narendra, J. Tschanz, A. Keshavarzi, and V. De, "Parameter variations and impact on circuits and microarchitecture," in *Proceedings of the 40th annual Design Automation Conference*, pp. 338– 342, 2003.

- [6] K. Agarwal, S. Nassif, F. Liu, J. Hayes, and K. Nowka, "Rapid characterization of threshold voltage fluctuation in mos devices," in *Proceedings* of *IEEE International Conference on Microelectronic Test Structures*, pp. 74–77, March 2007.

- [7] B. Ji, D. Pearson, I. Lauer, F. Stellari, D. Frank, L. Chang, and M. Ketchen, "Operational amplifier based test structure for transistor threshold voltage variation," in *Proceedings of IEEE International Conference on Microelectronic Test Structures*, pp. 3 –7, 2008.

- [8] H. Notani, M. Fujii, H. Suzuki, H. Makino, and H. Shinohara, "On-chip digital idn and idp measurement by 65 nm CMOS speed monitor circuit," in *IEEE Asian Solid-State Circuits Conference*, pp. 405–408, Nov. 2008.

- [9] M. Bhushan, M. Ketchen, S. Polonsky, and A. Gattiker, "Ring oscillator based technique for measuring variability statistics," in *Proceedings* of *IEEE International Conference on Microelectronic Test Structures*, pp. 87–92, March 2006.