## Verification of Branching-Time and Alternating-Time Properties for Exogenous Coordination Models

### **Dissertation**

zur Erlangung des akademischen Grades Doktoringenieur (Dr.-Ing.)

vorgelegt an der Technischen Universität Dresden Fakultät Informatik

eingereicht von

Sascha Klüppelholz

geboren am 21.10.1976 in Haan

#### **Gutachter:**

Prof. Dr. rer. nat. Christel Baier Technische Universität Dresden

Prof. Dr. Farhad Arbab Universität Leiden, Niederlande

Tag der Verteidigung: 19. März 2012

### **Abstract**

Information and communication systems enter an increasing number of areas of daily lives. Our reliance and dependence on the functioning of such systems is rapidly growing together with the costs and the impact of system failures. At the same time the complexity of hardware and software systems extends to new limits as modern hardware architectures become more and more parallel, dynamic and heterogenous. These trends demand for a closer integration of formal methods and system engineering to show the correctness of complex systems within the design phase of large projects.

The goal of this thesis is to introduce a formal holistic approach for modeling, analysis and synthesis of parallel systems that potentially addresses complex system behavior at any layer of the hardware/software stack. Due to the complexity of modern hardware and software systems, we aim to have a hierarchical modeling framework that allows to specify the behavior of a parallel system at various levels of abstraction and that facilitates designing complex systems in an iterative refinement procedure, in which more detailed behavior is added successively to the system description. In this context, the major challenge is to provide modeling formalisms that are expressive enough to address all of the above issues and are at the same time amenable to the application of formal methods for proving that the system behavior conforms to its specification. Our focus in this thesis will be on model checking which yields an algorithmic approach to show the correctness of a system with respect to its specification. For the modeling, we are interested in specification formalisms that allow to apply formal verification techniques such that the underlying model checking problems are still decidable within reasonable time and space bounds.

The presented work relies on an exogenous modeling approach that allows a clear separation of coordination and computation and provides an operational semantic model where formal methods such as model checking are well suited and applicable. The channel-based exogenous coordination language Reo is used as modeling formalism as it supports hierarchical modeling in an iterative top-down refinement procedure. It facilitates reusability, exchangeability, and heterogeneity of components and forms the basis to apply formal verification methods. At the same time Reo has a clear formal semantics based on automata, which serve as foundation to apply formal methods such as model checking.

In this thesis new modeling languages are presented that allow specifying complex systems in terms of Reo and automata models which yield the basis for a holistic approach on modeling, verification and synthesis of parallel systems. The second main contribution of this thesis consists of tailored branching-time and alternating time temporal logics as well as corresponding model checking algorithms. The thesis includes results on the theoretical complexity of the underlying model checking problems as well as practical results. For the latter the presented approach has been implemented in the symbolic verification tool set Vereofy. The implementation within Vereofy and evaluation of the branching-time and alternating-time model checker comprise the third main contribution of this thesis.

### **Acknowledgements**

First and foremost I want to thank my advisor *Christel Baier* for giving me the opportunity to be a member of her group for many years. I am very thankful for all her encouragement and contributions of ideas, time and funding which made my PhD experience a wonderful, productive and stimulating time. It is only due to her geniality, ingenuity and guidance that I was able to successfully complete my PhD. I want to thank her from the bottom of my heart.

I also want to thank my parents and their new marriage partners, *Monika* and *Peter Pietzsch*, *Klaus* and *Urszula Klüppelholz*, my grandparents *Katharina* and *Paul Wahler* and the whole family for proving me any imaginable kind of support. I owe special gratitude to my caring mother *Monika* who worked hard and provided continuous and unconditional support.

I wish to thank my girlfriend *Claudia Engler* for her love, devotion and unstinting support after all those busy weekends and evenings. I also want to thank the Engler family for warmly welcoming me. I would also like to express my warm thanks to my extremely-long-standing friends together with their family members who have always been there when I needed them the most, as there are *Bettina* and *Christian Wunner*, *Christoph Münch*, *David Calaminus*, *Frank Birkenbeil*, *Nora Timmerbeil* and *Ricarda Essrich* as well as long and outstanding friends from Bonn like *Andreas Niers* and his family, *Arthur Glogowski*, *Jan Tietjen* and family, *Kristina* and *Sebastian Lützeler-Gerhards*, *Kristina Judith*, and many many more. I also want to thank all the wonderful people from Villigst and especially *André Koch* who also finished his PhD recently. Thank you for all your love and support and thank you *Ricarda* and *Bettina* for all the proofreading of my thesis.

It was a pleasure to share doctoral studies and life in Dresden and Bonn with wonderful people like *Tobias Blechmann*, *Frank Ciesinski*, *Marcus Größer* and *Joachim Klein*, who shared this exiting adventure starting from the early days in Bonn. In the final phase of this thesis I very much appreciated the help of *Joachim Klein* who constantly gave very helpful comments, reviewed many things with me at the whiteboard, implemented some nifty helper scripts for efficiently running the case studies and kept poking me to work thoroughly on the remaining parts.

I was also very lucky to meet and get to know some delightful and knowledgeable colleagues in Dresden like *Manuela Berg*, *Clemens Dubslaff*, *Markus Daum*, *Steffen Märcker*, *Michael Ummels*, and all the others who joined (and left) our group in the recent years and of course all the other nice people I met at the institute for theoretical computer science and the faculty of computer science. A very special thanks I want to express to *Kerstin Achtruth* for just everything that she did for us. I would also like to thank the professors forming the committee of the doctoral examination procedure. *Prof. Uwe Assmann* and *Prof. Hermann Härtig* for forming and leading the committee, *Prof. Christel Baier* for supervising and reviewing the thesis, *Prof. Farhad Arbab* for all his effort he spent on reviewing the thesis as well as for the traveling, and *Prof. Heiko Vogler* for giving very helpful comments in preparation of the defense.

In the context of a collaboration within the former EU project CREDO and the bilateral DFG/NWO project SYANCO I had the opportunity to travel a lot, see different places and meet wonderful people. Working with them has been a great pleasure and beyond the project scope I still feel grateful to people like Bernhard Aichernig, Farhad Arbab, Frank de Boer, David Clarke, David Costa, Immo Grabe, Andreas Griesmayer, Mahdi Jaghouri, Einar Broch Johnsen, Stephanie Kemper, Jetty Kleijn, Christian Krause, Marcel Kyas, Wolfgang Leister, Xuedong Liang, Bjarte Østvold, Olaf Owe, Jose Proenca, Willem-Paul de Roever, Jan Rutten, Alfons Salden, Rudolph Schlatte, Andries Stam, Martin Steffen, Simon Tschirner, and Wang Yi.

Unfortunately, some of my closest people cannot witness the end of this experience. I feel very certain that my late father *Klaus Klüppelholz* and his wife *Urszula Klüppelholz*, who died just six days after him, would be very proud seeing this. We all miss *Tobias Blechmann* our dear colleague and friend who passed away much too early. Some of the work presented in this thesis has been created in collaboration with him within endless working sessions on the whiteboard. Just to mention two of his contributions: some important language features and the name of our modeling language CARML were originally proposed by him and the bisimulation engine he created is still part of our model checking tool set Vereofy. We should have pushed this much further – together. Lastly, and most importantly, I want to thank a very special person. My grandfather *Paul Wahler* was and is one of my major role models from whom I learned a lot for life. I dedicate this thesis to him.

## Contents

| Снарт | ER 1 Introduction                                           | 1   |

|-------|-------------------------------------------------------------|-----|

| Снарт | ER 2 Constraint automata                                    | 9   |

| 2.1.  | Introduction                                                | 9   |

| 2.2.  | Symbolic representation of constraint automata              | 16  |

| 2.3.  | Data types and polarity                                     | 18  |

| Снарт | ER 3 Modeling formalism and languages                       | 23  |

| 3.1.  | The coordination language Reo                               | 23  |

| 3.2.  | The modeling languages RSL and CARML                        | 34  |

|       | 3.2.1. Reo scripting language (RSL)                         | 35  |

|       | 3.2.2. Constraint automata reactive module language (CARML) | 46  |

| Снарт | ER 4 Alternating-time stream logic                          | 53  |

| 4.1.  | Constraint automata as multi-player games                   | 53  |

| 4.2.  | Syntax and semantics                                        | 58  |

| 4.3.  | Branching-time and alternating-time model checking          | 66  |

|       | 4.3.1. BTSL model checking                                  | 67  |

|       | 4.3.2. ASL model checking                                   | 71  |

| 4.4.  | Complexity of the ASL model-checking problem                | 88  |

| 4.5.  | ASL with fairness                                           | 95  |

| Снарт | ER 5 Implementation                                         | 99  |

| 5.1.  | The model-checking tool Vereofy                             | 99  |

| 5.2.  | BDD-based model checking                                    | 102 |

| 5.3.  | Tool evaluation                                             | 109 |

|       | 5.3.1. Tic-Tac-Toe                                          | 110 |

|       | 5.3.2. Other game examples                                  | 130 |

|       | 5.3.3. A dining philosophers example                        | 130 |

| Rihliogr | onhv      |                              | 151 |

|----------|-----------|------------------------------|-----|

|          | CHAPTER 6 | Conclusion                   | 147 |

|          | 5.3.5.    | The ASK communication system | 138 |

|          | 5.3.4.    | Other protocol examples      | 138 |

# List of Figures

| 2.1.  | Constraint automaton for a component or connector                                            | 11 |

|-------|----------------------------------------------------------------------------------------------|----|

| 2.2.  | Product automaton of two FIFO channels with capacity one and $Data = \{0\}$                  | 14 |

| 2.3.  | Hiding variants applied to the constraint automaton from Example $2.1.9$                     | 15 |

| 2.4.  | Constraint automaton for a component or connector (IOC-syntax)                               | 17 |

| 2.5.  | Constraint automaton with memory for a component or connector                                | 18 |

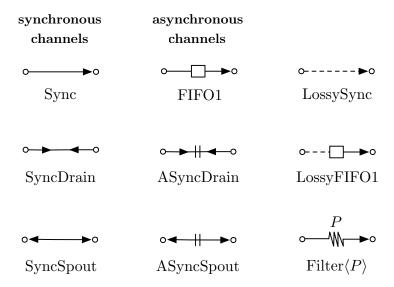

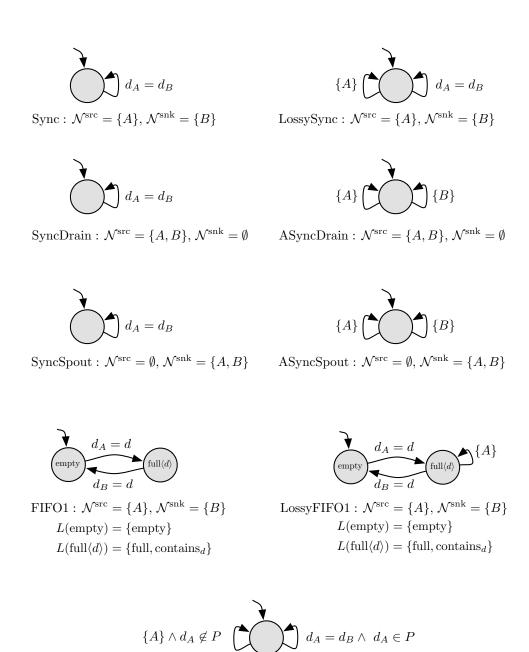

| 3.1.  | Basic set of Reo channels                                                                    | 24 |

| 3.2.  | Constraint automata for Reo channels                                                         | 27 |

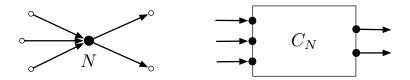

| 3.3.  | Reo nodes: a) sink node, b) source node, and c) mixed Reo node                               | 28 |

| 3.4.  | Replacement of a Reo node $N$ by a component $C_N$                                           | 29 |

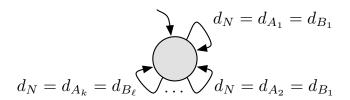

| 3.5.  | Constraint automata for a standard Reo node $N \ \dots \dots \dots$                          | 29 |

| 3.6.  | Constraint automata for a Reo route node $N  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots$ | 30 |

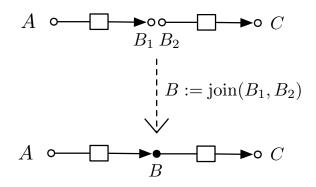

| 3.7.  | Reo join for two FIFO channels                                                               | 30 |

| 3.8.  | Automata for two FIFO1 channels, the standard Reo node and their product                     | 31 |

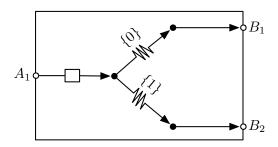

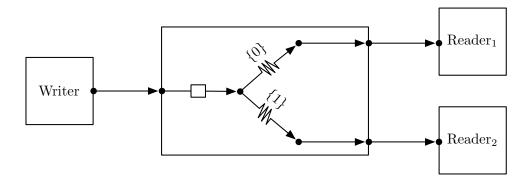

| 3.9.  | Reo component connector for data-dependent routing                                           | 32 |

| 3.10. | A writer and two readers connected by a data-dependent router                                | 32 |

| 3.11. | Constraint automaton (after hiding the internals) for a data-dependent router                | 33 |

| 3.12. | Schema of an RSL circuit                                                                     | 36 |

| 3.13. | Two RSL scripts composing the same connector                                                 | 40 |

| 3.14. | An RSL main program to compose the Reo network of Example 3.1.5 $$                           | 41 |

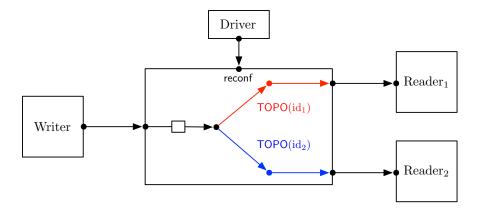

| 3.15. | Schema for RSL scripts with dynamic reconfiguration                                          | 42 |

| 3.16. | A dynamic router used in a simple Reo network                                                | 43 |

| 3.17. | Schema of a CARML module                                                                     | 47 |

| 3.18. | CARML module for a FIFO1 channel with initial value <code>init_value</code>                  | 50 |

| 3.19. | Induced constraint automaton for the CARML module of Figure 3.18 $$                          | 51 |

| 3.20. | CARML module for a stack with capacity $cap \dots \dots \dots \dots$                         | 51 |

| 4.1.  | Constraint automaton and a finite-memory $N$ -strategy                                       | 57 |

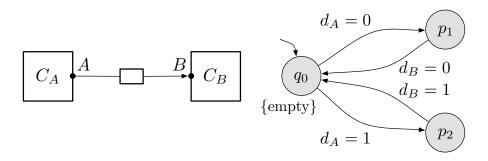

| 4.2.  | Two components connected via a FIFO channel                                                  | 62 |

LIST OF FIGURES LIST OF FIGURES

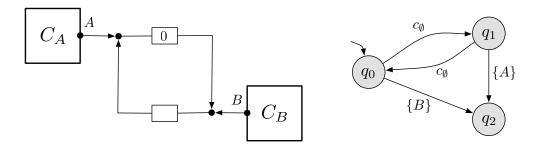

| 4.3.  | Network (left) and constraint automaton (right)                                                         | 63  |

|-------|---------------------------------------------------------------------------------------------------------|-----|

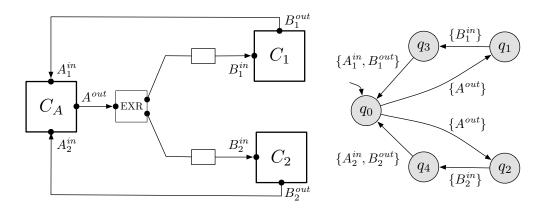

| 4.4.  | Network with three components and its constraint automaton $\ldots \ldots$                              | 64  |

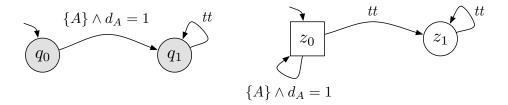

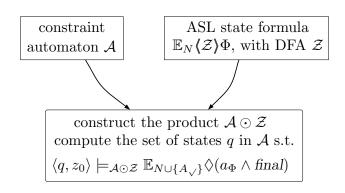

| 4.5.  | Constraint automaton ${\mathcal A}$ and NFA ${\mathcal Z}$ with ${\mathcal L}({\mathcal Z})=(c(A)=1)^*$ | 70  |

| 4.6.  | Product automaton $\mathcal{A} \otimes \mathcal{Z}$                                                     | 71  |

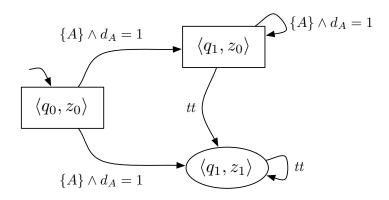

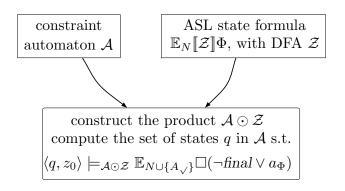

| 4.7.  | Schema for the treatment of $\mathbb{E}_N\langle\mathcal{Z}\rangle\Phi$                                 | 77  |

| 4.8.  | Schema for the treatment of $\mathbb{E}_N[\![\mathcal{Z}]\!]\Phi$                                       | 85  |

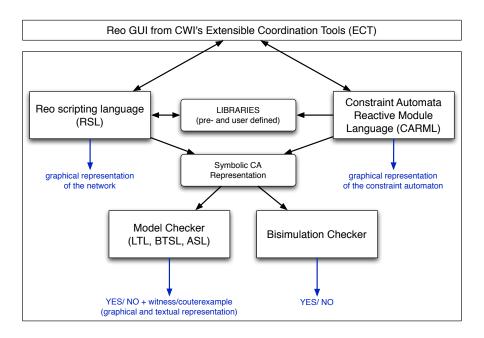

| 5.1.  | Main elements of the Vereofy tool set                                                                   | 100 |

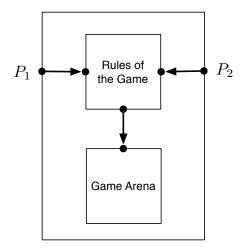

| 5.2.  | Component model for a two-player game                                                                   | 109 |

| 5.3.  | RSL declarations for the Tic-Tac-Toe game                                                               | 111 |

| 5.4.  | CARML module for the rules of the Tic-Tac-Toe game                                                      | 111 |

| 5.5.  | CARML module for the game arena of the Tic-Tac-Toe game                                                 | 112 |

| 5.6.  | RSL circuit composing the Tic-Tac-Toe game                                                              | 113 |

| 5.7.  | Executing Vereofy for the Tic-Tac-Toe game and formula $\Phi_4$                                         | 116 |

| 5.8.  | Tic-Tac-Toe draw configuration as reached in the witness path in Figure 5.7                             | 117 |

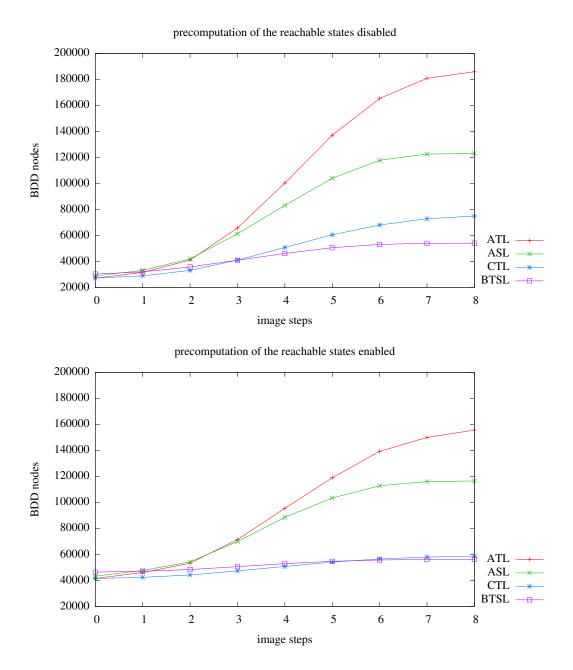

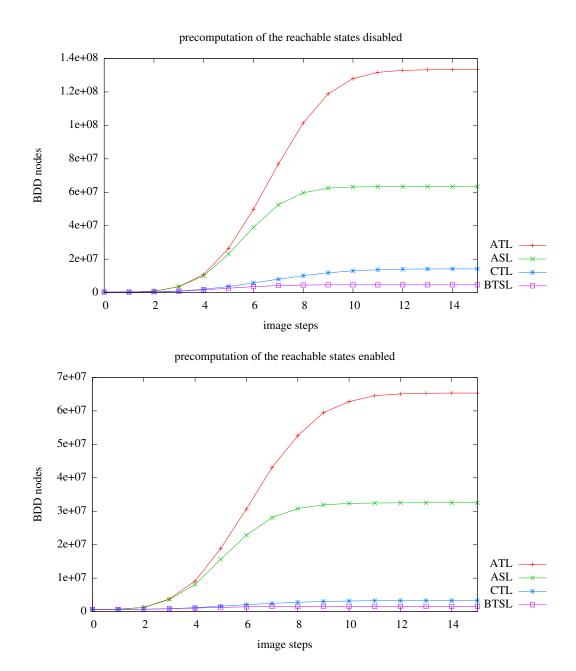

| 5.9.  | BDD nodes during fixpoint computation for Tic-Tac-Toe $3\times3$ (gcd=default)                          | 124 |

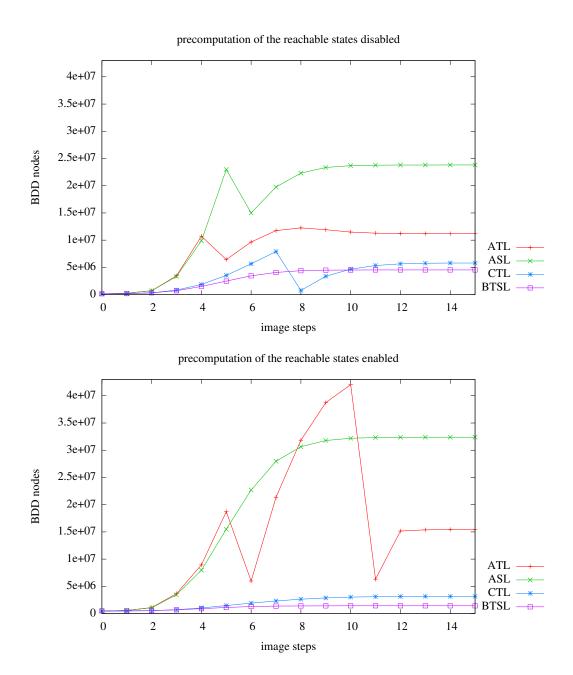

| 5.10. | BDD nodes during fixpoint computation for Tic-Tac-Toe $4{\times}4$ (gcd=default)                        | 125 |

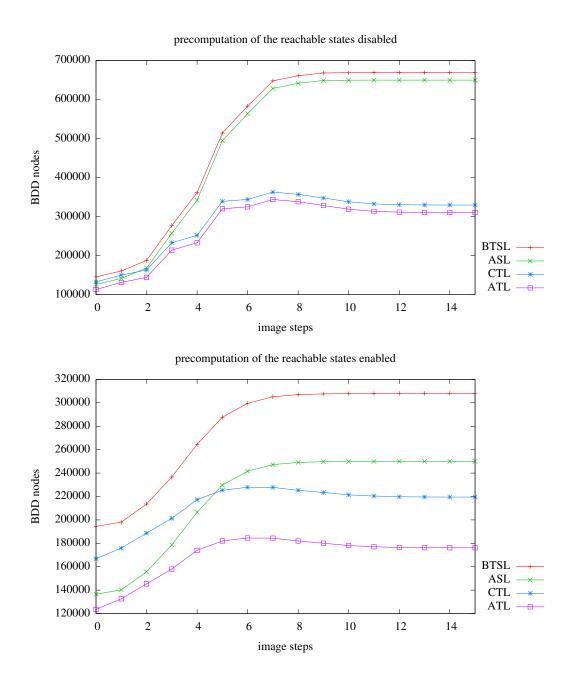

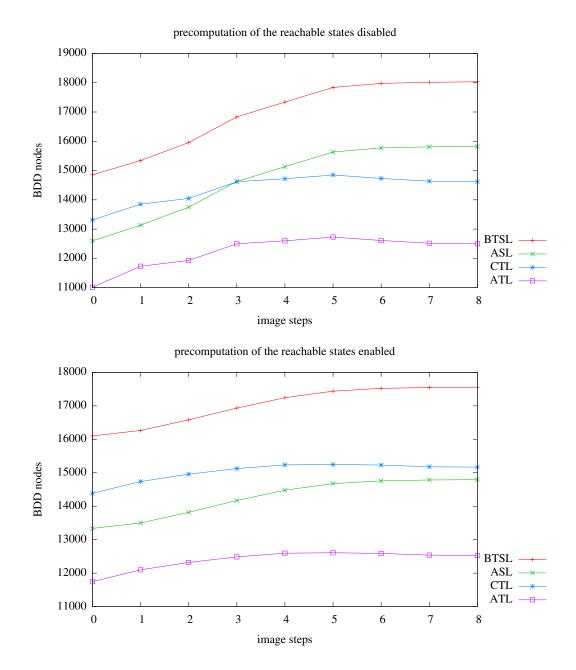

| 5.11. | BDD nodes during fixpoint computation for Tic-Tac-Toe $4{\times}4~(\mbox{gcd=inf})~$ .                  | 126 |

| 5.12. | BDD nodes during fixpoint computation for Tic-Tac-Toe $4{\times}4~(\mbox{gcd}{=}0)$                     | 127 |

| 5.13. | BDD nodes during fixpoint computation for Tic-Tac-Toe $3{\times}3~(\mbox{gcd}{=}0)$                     | 128 |

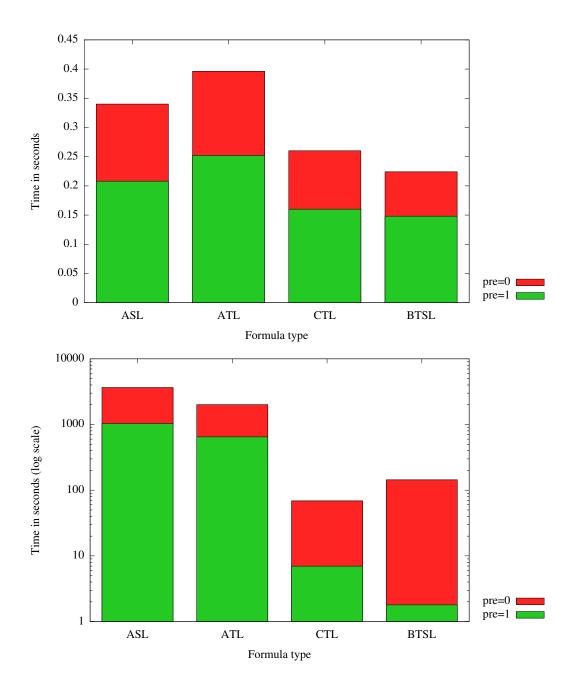

| 5.14. | Time needed for fixpoint computation in Tic-Tac-Toe (gcd=inf) $\dots \dots$                             | 129 |

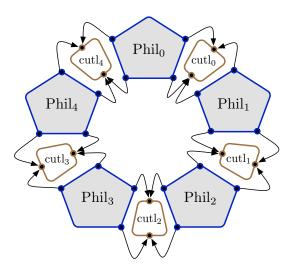

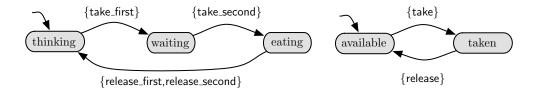

| 5.15. | Component model for the dining philosophers                                                             | 131 |

| 5.16. | Constraint automata for the dining philosophers components                                              | 131 |

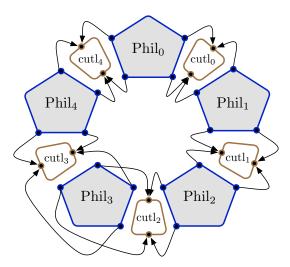

| 5.17. | Alternative component model for the dining philosophers without deadlock                                | 132 |

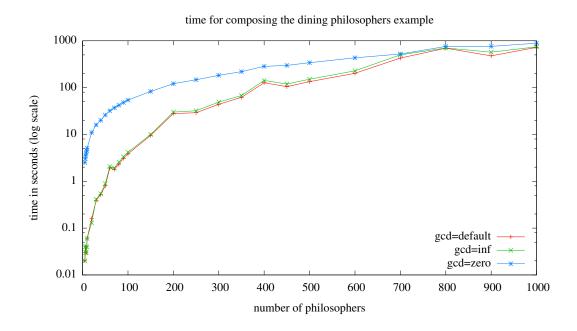

| 5.18. | Composition time in seconds for the dining philosophers protocol                                        | 134 |

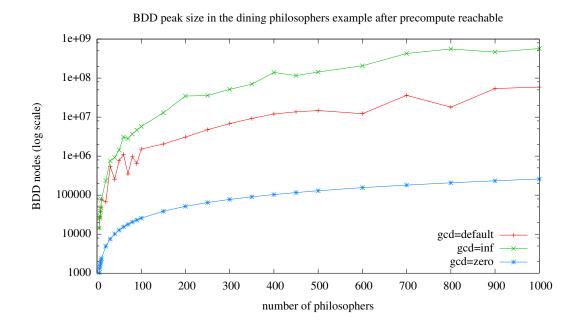

| 5.19. | BDD nodes: precomputing reachable states of the dining philosophers                                     | 135 |

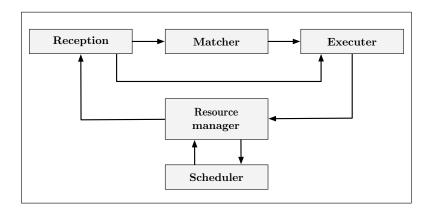

| 5.20. | ASK core overview                                                                                       | 139 |

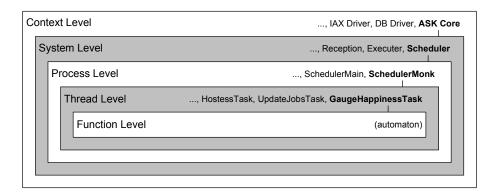

| 5.21. | Abstraction levels in the ASK model and components contained in the level                               | 140 |

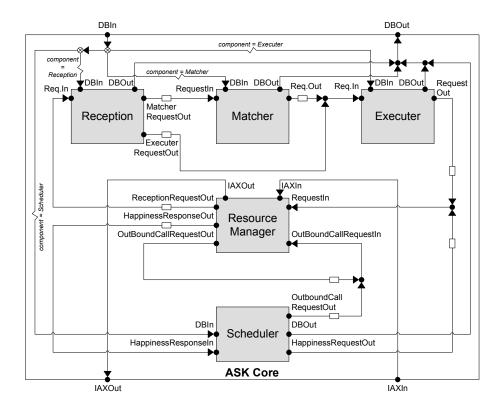

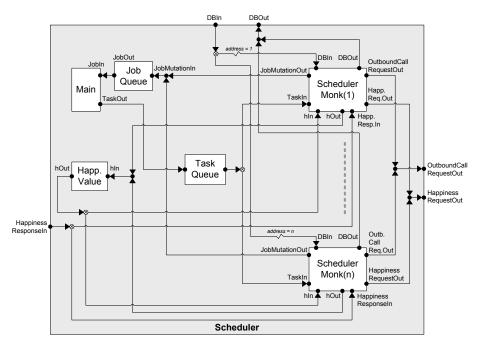

| 5.22. | Reo network for the ASK core                                                                            | 141 |

| 5.23. | Reo network for the scheduler process                                                                   | 142 |

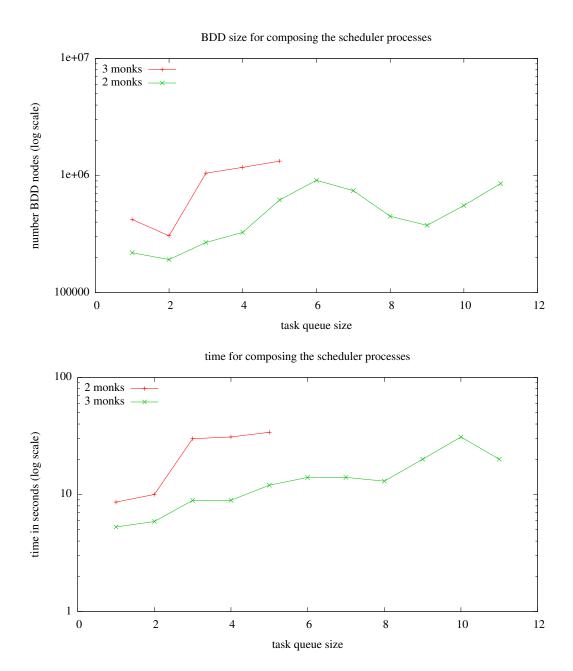

| 5.24. | Time and memory usage for the scheduler process                                                         | 144 |

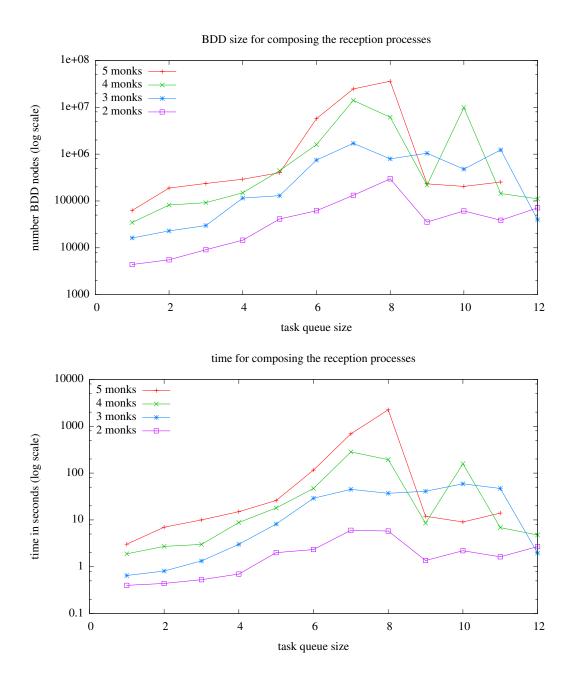

| 5.25. | Time and memory usage for the reception process                                                         | 146 |

# 1 Introduction

In our everyday life we observe that information and communication systems enter an increasing number of areas. Our reliance and dependence on the functioning of such systems are rapidly growing, and so are the costs and the impact of system failures. At the same, time the complexity of hardware and software systems extends to new limits. In the last decades the performance of hardware systems was mainly improved by integrating more transistors on an integrated circuit and increasing the processor frequency.

This process has reached its physical limitations for current CMOS-based technology. Continuing Moore's Law in the future demands for new designs and technologies [BC11]. Current hardware multi- and many-core architectures are providing more and more resources available for parallel and asynchronous computing. Instead of synchronizing on a single global clock whose frequency is increased to gain more performance, modern architectures tend to be more and more asynchronous. Given the fact that local hardware components still work in a synchronized way it is rather natural to design systems following GALS paradigm [Cha84] (globally asynchronous and (only) locally synchronous). Better performance can now potentially be achieved by increasing the number of cores. Together with the growing number of cores, future hardware becomes more flexible with respect to dynamic reconfiguration and runtime adaptations. Notable improvements can be achieved when changing the communication from classical bus- or crossbar-based interconnects to network-on-chip (NoC) communication which is more eligible for flexible adaptations at runtime. Hence, reconfigurable hardware has the chance of achieving a better performance at a lower energy consumption. The latter has become a very important issue not only for mobile devices and large server farms. Another important aspect results from the development of promising alternative material such as silicon nanowires. Current hardware architectures are heterogenous only in the sense that they may for example use graphics processing units (GPUs) for computations instead of the CPU. In the future we expect more heterogenous hardware systems that may contain special-purpose hardware based on alternative materials. This makes future hardware platforms even more flexible and provides another opportunity for improving the overall computing performance. Despite the fact that the performance of future hardware increases by providing more flexible parallel and heterogenous hardware resources, the overall performance of a system will not benefit from these developments automatically. We see already today that our static sequential programs do not profit in full from CPUs with four or even more cores. An integrated approach is needed that covers the hardware, the operating system, programming languages and compilers, libraries and middle-ware as well as aspects of the application layer.

These developments show that future hardware and hence the software will be even more complex and error-prone. It will become more difficult to build systems that behave correctly with respect to their specification. This demands for a closer integration of systems engineering and formal methods, i.e., applied mathematics for modeling and analyzing information and communication systems, to show the correctness of complex systems within the early design phase of large projects.

The goal of this thesis is to present a holistic approach for the modeling, analysis and synthesis of complex current and future hardware and software systems. The proposed approach should be applicable at any layer of the hardware/software stack (and even across layers) and support heterogeneity. Moreover, the proposed approach should be compositional and support hierarchical modeling of parallel systems by means of a stepwise refinement procedure that facilitates reusability, interchangeability, and system maintenance. To achieve this goal, we plan to inspect well-known concepts, methods, and techniques from the literature and combine them into a holistic framework. To obtain efficiency in this framework, this surely involves some nontrivial adaptions and modification. The main challenge in developing such a holistic approach is to find a reasonable balance between different aspects. We demand for modeling languages that are comprehensive and expressive and at the same time simple, elegant, intuitive and easy to learn. The underlying semantics of the modeling formalisms needs to capture all the relevant aspects and details of the system. Also the formal methods that are applied to show the correctness of a parallel system model should be powerful enough to address all relevant aspects, e.g., functionality, costs, time, utility and various types of system properties from the safety-liveness spectrum. On the other hand, the proposed combination of languages, their operational semantics, and formal methods should still be eligible for systematic verification and synthesis supported by tools, and the algorithmic problems should still be efficiently decidable.

In this respect, component-based modeling is a promising approach facilitating the vision of "correctness by construction" [Hal02, HC02, Hal05, GS05]. In the component-based modeling approach the basic principle is (as in software engineering) to divide a complex system into logical entities. These entities are called *components*. In principle, components are abstract entities that have a well-defined interface consisting of (input and output) ports which they use for communication and interaction. At each layer of the hardware/software stack components can stand for different parts of the system. E.g., at the hardware level, the components of a component-based system model could stand for different parts of hardware such as the CPU or the memory. At the programming language layer, components could model the behavior of objects or method calls. Hence, the component-based view can in principle be applied at any layer or even across layers of the hardware/software stack. Component-based modeling also allows and facilitates a systematic hierarchical system design, as modeling complex systems can be done in an iterative top-down refinement procedure. Starting from a rather abstract, purely structural component-model, one can successively provide details of the concrete implementation for each of the components. On the other hand, starting with fully specified (and verified) components, one can compositionally build complex systems in a bottom-up manner.

A multitude of component-based modeling formalisms have been proposed in the literature. They are based on different formalisms to describe the components themselves and a variety of paradigms for interaction and communication of the components. One of the most simple types of synchronization relies on the principle of synchronized parallelism that has been suggested by Milner [Mil83], and is used, e.g., to model the communication between transition systems [Arn94]. Famous examples of communication paradigms are based on *shared* variables which were originally proposed by Dijkstra [Dij65] in 1965 or handshake communication as it is the case in process algebras such as CSP (Communicating Sequential Processes) [Hoa78, Hoa85], CCS (Calculus of Communicating Systems) [Mil89, Mil99], ACP (Algebra of Communicating Processes) [BK85],  $\pi$ -Calculus [MPW92], etc., where parallel processes communicate over synchronous and asynchronous channels. While process algebras are very expressive, their view is action-based and focuses on algebraic reasoning about equivalence, simulation, bisimulation, or trace-based refinement relations. Coordination languages have a different focus which is on the glue code that coordinates and orchestrates the components. Coordination languages aim for a clear separation between coordination and computation. Moreover, coordination languages potentially allow for the application of iterative and hierarchical refinement procedures as needed when modeling complex parallel software and hardware systems and they align perfectly with refinement procedures known from the software engineering and hence do facilitate reusability and exchangeability of components (and the orchestrating structures as well).

A variety of coordination models and languages have been introduced. In general they can be categorized by the following two aspects. Coordination languages are either *control-oriented* or *data-oriented*. Whereas control-oriented languages have a data-abstract perspective and tend to center around the control-flow between components (only), the data-oriented languages tend to manage the dataflow of communicating components. The second aspect is *exogenous* vs. *endogenous* coordination. Endogenous coordination languages require to incorporate coordination primitives within the code that specifies the behavior of the components. A typical example is the data-oriented and endogenous coordination language *Linda* [GCCC85] where components are described in a computational language extended by operators to store or retrieve data objects from a global tuple space. A cleaner separation of computation and coordination is provided by exogenous coordination models where the components do not need to be aware of each other. Instead, they are controlled from "outside" via their interfaces.

Several approaches for exogenous coordination have been suggested, e.g., an aspect-oriented approach [KLM $^+$ 97, CSZ04], a variant of the  $\pi$ -calculus with anonymous peer-to-peer communication [GSAdBB05, GS07], glue code provided by scripting languages [SLN01, ALSN01], and formalism that rely on the construction of component connectors, such as interaction systems [GS03, MCM08] or the declarative channel-based language Reo [Arb04]. In this thesis we will use the exogenous coordination language Reo for specifying the communication, synchronization and interaction of components. Reo is based on the ideal worker ideal manager (IWIM) model [Arb96], extending classical models such as Kahn networks and dataflow languages. Reo allows any kind of peer-to-peer communication, hierarchical modeling and provides support for dynamic reconfiguration. Reo is more expressive than, e.g., dataflow models, workflow models, and Petri nets [Pet77, Pet81]. In particular, standard CCS-like handshaking via synchronous channels can be modeled in Reo.

The interface behavior of the components as well as the behavior of the basic Reo channels are described in terms of automata models. Constraint automata [BSAR06] serve for both, as an operational semantics for Reo which supports composition of channels and at the same time constraint automata are used to describe the interface behavior of components. This approach is fully compositional and yields the basis for analyzing the components in isolation (which carry out the computation), the orchestrating Reo network in isolation (which is responsible for communication and interaction between components), or the entire system model. The underlying operational semantics for components and their interactions is now based on an automata model that yields the perfect basis for applying formal methods to show the correctness of a system with respect to its specification.

In general there are different ways to validate the correctness of a designed system. With *testing* and *simulation* one can find many types of failures and errors within existing systems and system models respectively. However, testing and simulation come with the drawback of incompleteness as neither of the two methods formally proves the absence of system errors. In contrast *theorem proving* and *model checking* are complementary verification methods that are complete in the sense that properties which have been proven to hold, do hold for all possible system behavior. Whereas theorem proving is a semi-automatic deductive technique which requires expert knowledge to operate, model checking is a fully automatic and algorithmic approach. Theorem proving, model checking, testing and simulation form a useful toolbox of complementary methods that can be used to validate the correctness of future hardware and software systems. In this thesis we will consider model checking techniques which target towards a closer integration in the system design phase of complex parallel (and distributed) systems.

The term model checking was introduced [CE81] in 1981 and about the same time a similar technique was suggested in [QS82]. In model checking the operational behavior of a system is given in terms of an automata-based model and we check the specification, which is usually given in terms of a temporal logic formula. In the early days, model checking was mostly applied for verifying hardware circuits and protocols where exhaustive testing is not feasible due to the huge number of test cases. Later, model checking has also been successfully applied to software systems, e.g. [Hol93]. An introduction to model checking can be found, e.g., in [CK96, CS00, CW96, Mer01, Wol95]. Extensive knowledge about model checking can be found in the early books [Hol90, McM93, Kur94], the 1999 book *Model Checking* [CGP99], which serves as a standard reference, and other books [HR99, Sch04a, BBF+01] as well as the book [BK08] from 2008.

The major challenge in the classical model checking approach arises from the fact that the corresponding algorithms work on the representation of the entire systems, whose size becomes huge and reaches (or even extends) the memory limitations of modern computer systems very quickly. This challenge is known as the *state-explosion problem* and demands for additional techniques to handle gigantically large state spaces, see e.g. [AK86]. Many techniques have been proposed to overcome the state-space-explosion problem such as partial order reduction [Val92, God96, Pel93], symmetry reduction [CEFJ96], slicing for concurrent programs [Wei84, Kri03], (learning-based) assume-guarantee reasoning [Pnu85, HQR98, CCF<sup>+</sup>10], bounded and unbounded SAT-based model checking as in [BCCZ99] and [WBCG00], iterative (and counterexample-guided) abstraction-refinement algorithms

[GS97, CGJ<sup>+</sup>00], as well as symbolic model checking based on *binary decision diagrams* (BDDs) [BCM<sup>+</sup>92].

Many instances of model checking have been studied in the literature. They vary in the way the behavior of the system is specified, the underlying operational model and the type of properties that can be checked. One of the most prominent candidates to formally describe the behavior of systems are variants of transition systems [Kel76], which do serve as a semantic model for formalisms such as process algebras [Hoa85, Mil89, Mil99, BPe01], Petri nets [Pet77, Pet81], UML [RJB99], statecharts [Har87], finite-state Mealy and Moore automata [Kro99], program graphs [MP92], etc. Transition systems form the basis for most model checkers.

Over the years, a large number of model checkers have been developed in academia and industry<sup>1</sup>. We now look at some of the most prominent formalisms and model checkers in more detail. SPIN [Hol97] is a tool for protocol design and validation that targets on efficient software verification, not hardware verification. SPIN supports LTL (*linear temporal logic*) [Pnu77] model checking [VW86, Var96] by an on-the-fly exploration of the state space. The input language of SPIN is Promela – a nondeterministic guarded command language. The communication between components is limited to simple synchronous and asynchronous channels. Hence, Promela and SPIN hardly support hierarchical top-down or bottom-up modeling. SMV (*symbolic model verifier*) [McM93] was the first BDD-based CTL (*computation tree logic*) model checker. SMV is designed for hardware verification and its capability of handling complex data structures is limited. A recent variant of SMV is the model checker NuSMV [CCGR00] which now also supports LTL. Modeling complex software systems with NuSMV leads to rather artificial models which are not close to the real system. MOCHA [AHM<sup>+</sup>98] supports alternating-time symbolic model checking, e.g., ATL [AHK02] model checking of reactive modules [AH99].

The above model checkers, SPIN, NuSMV, and MOCHA, are very limited in communication and coordination between components directly and none of them treats exogenous coordination as a first class citizen. Hence, the compositional and hierarchical modeling approach is hardly supported by any of the above model checkers. In contrast, there are other formalisms like classical process algebras and corresponding tools that in principle would provide this support. E.g, CADP [GLMS11] is a powerful set of tools to design communication protocols and distributed systems. It is connected to various complementary tools and widely used in (industrial) projects. CADP uses the process algebra LOTOS (Language of Temporal Ordering Specification) [BB87] as the modeling language, which then is translated into a simplified process algebra called SUBLOTOS. From that an intermediate Petri Net model [Pet77, Pet81] is generated and in the end the labeled transition system (LTS) is produced by performing a reachability analysis on the Petri net. The LTS are stored in an explicit manner and CADP uses XTL (eXecutable Temporal Language), a functional-like programming language designed for the implementation of user defined temporal logics. FDR2 (Failures-Divergence Refinement Tool) is a refinement checker, whose modeling formalism is based on Hoare's process algebra CSP. It is used primarily for checking security properties.

<sup>&</sup>lt;sup>1</sup>An incomplete overview is given e.g. at http://anna.fi.muni.cz/yahoda/

There are many more tools from the process algebra community like the *concurrency work bench* (CWB) [Ste97, CPS89] based on Milner's CCS for bisimulation checking and  $\mu$ -calculus model checking, and  $\mu$ CRL [DG95, Wou01, vdP01, KKdV12] for  $\mu$ -calculus model checking of process algebras, but none of them treats coordination as first class object in the first place. Although it is possible to specify coordination within by means of special operators, the specification becomes rather complex and artificial. In contrast, the declarative nature of Reo promotes specifying the coordination glue code in a very intuitive and flexible manner. The goal of this thesis is to introduce a model checker that directly supports the constructs of Reo and hence allows to link back counter examples and other properties to the original model effectively.

Goal of the thesis. The major goal of this thesis is to introduce a holistic approach for the modeling, analysis, and synthesis of component-based system models with exogenous coordination, which includes input languages that are expressive and simple, allow a clear separation of computation and coordination, support compositional and hierarchical modeling, allow specifying systems at any layer of the hardware/software stack, have clear formal semantics eligible to formal methods as well as temporal logics and model checking algorithms that treat exogenous coordination in component-based systems as a first class citizen, allow reasoning about aspects of coordination and dataflow, allow reasoning about alternating-time aspects such as controllability, and are decidable within reasonable time and space bounds. It is intended to evaluate the introduced techniques and methods for modeling, analysis, and synthesis within a newly implemented tool set.

Contribution. In this thesis we will introduce the syntax and formal semantics of two modeling languages CARML and RSL. CARML (Constraint Automata Reactive Module Language) is a guarded command language [Dij76] which is inspired by reactive modules [AH99] and serves for the specification of the interface behavior of components and Reo channels. RSL (Reo scripting language) is a scripting language that allows to create new instances of Reo channels and components specified in CARML and compositionally build larger networks and systems. Combining the two languages yields a compositional and hierarchical modeling framework. The combination of guarded command languages together with synchronous and asynchronous channel-based communication is also used in Promela [Hol93], the input language of the model checker SPIN [Hol97, Hol03], but Reo facilities a clear distinction between coordination and computation.

In this thesis we will present a branching-time and an alternating-time temporal logic tailored to our modeling framework based on Reo and constraint automata [BSAR06]. The branching-time logic BTSL combines standard features known from CTL [CE81, CGP99] with modalities from *propositional dynamic logics* like PDL [FL79] and the *timed data stream logic* (TDSL) [ABdBR04, CCA04] for reasoning about the observable dataflow at interface ports of Reo channels and components. The presented alternating-time logic ASL is inspired by classical alternating-time logics such as ATL [AHK02]. In this thesis a two-player game-based interpretation of constraint automata is proposed that allows reasoning about strategies in the Reo and constraint automata framework. Furthermore, we present the algorithms for the corresponding model checking problems and analyze them with respect to their theoretical complexity. For a practical evaluation of the model checking algorithms we implemented them within the model checking tool set Vereofy.

Vereofy is a tool set developed in our group at the TU Dresden that uses CARML and RSL as input languages and supports the introduced branching-time and alternating-time model checking as well as linear-time model checking and equivalence checking using bisimulation. To overcome the state-space explosion problem, Vereofy uses BDDs as data structures to represent constraint automata compactly. Also, the implementation of the model checking algorithms is based on BDDs. In this thesis we present the relevant implementation details of Vereofy as well as practical results achieved in a number of case studies.

Outline. Chapter 2 will give an overview on constraint automata and basic notations used throughout this thesis. In Chapter 3 we introduce our modeling framework based on Reo and constraint automata as well as syntax and semantics of our modeling languages CARML and RSL. The main contribution of this thesis can be found in Chapter 4 where syntax and semantics of our branching-time logic BTSL and the alternating-time logic ASL are presented. In this chapter we provide the model checking algorithms together with results on the complexity of the model checking problems. In Chapter 5 the details on the symbolic implementation within our verification tool set Vereofy are given. In this chapter we provide examples and case studies that have been carried out with Vereofy and present practical results. Chapter 6 concludes this thesis and presents ideas for future work.

# 2 Constraint automata

Constraint automata [BSAR06] provide a generic operational model to formalize the behavioral interfaces of the components, the network (i.e., the glue code or connector) that coordinates a set of components, and a composite system consisting of components and the glue code. Constraint automata are variants of labeled transition systems (LTS) where the labels of the transitions represent the (possibly data-dependent) I/O-operations of the components and the network. Constraint automata are adequate to represent any kind of synchronous and asynchronous peer-to-peer communication. The states of a constraint automaton represent the local states of components and/or configurations of a connector. The transition labels characterize the possible I/O-activities at the dataflow locations where I/O-operations can take place, such as the interface ports of components, nodes in the connector network, etc. Constraint automata will also serve as a formal semantics for our input languages RSL and CARML [BBKK09a, BKK12] as introduced in Section 3.2.

*Organization.* Section 2.1 provides the basic notation of constraint automata, executions, paths and operators used for composition. In Section 2.2 we present an alternative syntax for constraint automata. This symbolic characterization is closer to what is used in the implementation and allows a more compact (graphical) representation. In Section 2.3 the concept of constraint automata will be enriched with polarity and type information.

#### 2.1. Introduction

To formalize the I/O-activity, constraint automata use a finite set  $\mathcal{N}$  of names for *dataflow locations*. Dataflow locations are points in the network where dataflow is observable, e.g., the I/O-ports of components or nodes of the network that serve as a router. We assume here that the data domain Data is a fixed and finite set of data items that can be observed at the dataflow locations.

For the syntax of constraint automata we slightly depart from the original one presented in [BSAR06]. Instead of having guard conditions on the possible dataflow as transition labels, the observable dataflow in a constraint automaton is in the first place formalized by means of concurrent I/O-operations (ClOs). ClOs can be understood as the possible actions of a component, a connector, or as interactions between several components and the connector in a composite system. The meaning of a transition instance  $q \xrightarrow{c} p$  is that in configuration q, the concurrent I/O-operation c is enabled and state p is a possible successor configuration of q executing c. A concurrent I/O-operation specifies the dataflow locations, where at some specific time instance dataflow can be observed simultaneously.

**Definition 2.1.1** (Concurrent I/O-operations). Let  $\mathcal{N}$  be a finite, nonempty set of names for dataflow locations. We define a concurrent I/O-operation as a function

$$c: \mathcal{N} \to \mathsf{Data} \cup \{\bot\},\$$

where the symbol  $\bot$  means that there is no dataflow at the corresponding dataflow location. We write  $\operatorname{active}(c)$  for the set of names of dataflow locations  $A \in \mathcal{N}$  such that  $c(A) \in \mathsf{Data}$ , where  $\mathsf{Data}$  is the data domain. For technical reasons, we also allow the *empty* concurrent  $\mathsf{I/O}$ -operation  $c_\emptyset$  with  $\operatorname{active}(c_\emptyset) = \emptyset$ . It represents either an internal step of some component, or an unobservable step of a connector, where dataflow appears at some hidden (invisible) dataflow locations only. We refer to  $\mathsf{CIO}$  as the set of all concurrent  $\mathsf{I/O}$ -operations (including  $c_\emptyset$ ). As we suppose  $\mathcal N$  and  $\mathsf{Data}$  to be finite, the set  $\mathsf{CIO}$  of concurrent  $\mathsf{I/O}$ -operations is finite as well. When reasoning about finite behavior we will also need a special symbol  $\sqrt{}$  that indicates that dataflow has stopped. The set  $\mathsf{CIO}_{\sqrt{}}$  stands for  $\mathsf{CIO} \cup \{\sqrt{}\}$ .

**Definition 2.1.2** (Constraint automata [BSAR06]). A constraint automaton is a tuple

$$\mathcal{A} = \langle Q, \mathcal{N}, \longrightarrow, Q_0, \mathcal{Q}, AP, L \rangle,$$

where Q is a finite and nonempty set of states,  $\mathcal{N}$  a finite set of port names, and  $\longrightarrow$  is a subset of  $Q \times \text{CIO} \times Q$  called the transition relation of  $\mathcal{A}$ . We will write  $q \stackrel{c}{\longrightarrow} p$  instead of  $\langle q,c,p\rangle \in \longrightarrow$ . The set  $Q_0 \subseteq Q$  is a nonempty set of initial states, AP a finite set of atomic propositions,  $L:Q \to 2^{AP}$  a labeling function, and  $\mathcal{Q} \subseteq Q$  a set of so called *quiescent states* such that  $\{q \in Q \mid \text{there is no transition } q \stackrel{c}{\longrightarrow} q'\} \subseteq \mathcal{Q}$ .

The set Q of quiescent states characterizes those states  $q \in Q$  where dataflow can stop completely (although there might be outgoing transitions).

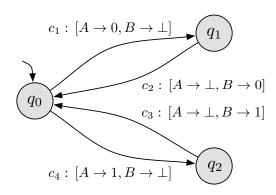

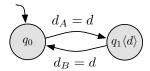

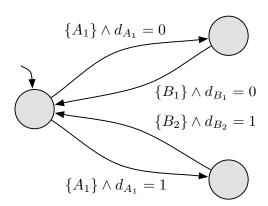

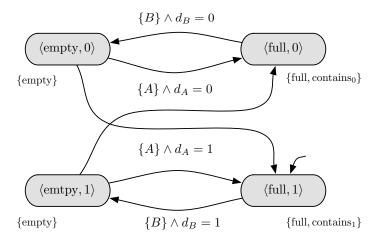

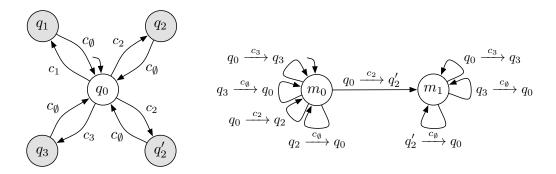

**Example 2.1.3** (Constraint automata). Figure 2.1 shows an example of a constraint automaton providing the interface behavior of a component or a connector with two dataflow locations. The constraint automaton consists of the three states  $Q = \{q_0, q_1, q_2\}$ , the set  $\mathcal{N} = \{A, B\}$  of names for the dataflow locations, and the depicted transition relation. The set of starting states  $Q_0 = \{q_0\}$  is a singleton and contains the state  $q_0$  only. As all states  $q \in Q$  have outgoing transitions we can assume here, that the set of quiescent states is empty, i.e.,  $Q \stackrel{\text{def}}{=} \emptyset$ .

Assuming that A is an input port and B is an output port, the given behavior agrees with the behavior of a FIFO channel with capacity one which can store the two values of the data domain  $\mathsf{Data} = \{0,1\}$ .

For the atomic propositions we define the set

$$AP = \{\text{empty}, \text{full}, \text{contains}_0, \text{contains}_1\}$$

and the labeling function as follows:

$$\begin{array}{lcl} L(q_0) &=& \{ \mathrm{empty} \} \\ L(q_1) &=& \{ \mathrm{full}, \mathrm{contains}_0 \} \\ L(q_2) &=& \{ \mathrm{full}, \mathrm{contains}_1 \}. \end{array}$$

Figure 2.1: Constraint automaton for a component or connector

**Definition 2.1.4** (Enabledness). Let  $\mathcal{A} = \langle Q, \mathcal{N}, \longrightarrow, Q_0, \mathcal{Q}, AP, L \rangle$  be a constraint automaton as in Definition 2.1.2,  $q \in Q$  a state, and  $c \in \mathsf{CIO}$  a concurrent I/O-operation. We call c to be *enabled* in q iff c can take place in q and define the set of all I/O-operations enabled in q as

$$\mathsf{CIO}(q) \ \stackrel{\scriptscriptstyle \mathrm{def}}{=} \ \big\{\, c \in \mathsf{CIO} \, : \, q \xrightarrow{c} p \text{ for some } p \in Q \,\big\}.$$

State q is called *terminal* iff  $CIO(q) = \emptyset$ .

**Definition 2.1.5** (Execution, completeness of executions). Let  $\mathcal{A}$  be a constraint automaton. An *execution* in  $\mathcal{A}$  is a finite or infinite sequence built of consecutive transitions:

$$\eta = q_0 \xrightarrow{c_1} q_1 \xrightarrow{c_2} \dots$$

where  $q_0, q_1, \ldots \in Q$ ,  $c_1, c_2, \ldots \in CIO$ , and  $q_i \xrightarrow{c_{i+1}} q_{i+1}$  for all  $i \geq 0$ . An execution is said to be *complete* if it is either infinite or it is finite and ends in a quiescent state  $q_n \in Q$ .

The notion of complete executions serves to reason about "maximal" behaviors of constraint automata, called paths. A *path* of  $\mathcal{A}$  is either an infinite execution or arises from a finite complete execution by adding a special transition symbol  $\sqrt{}$  to denote termination.

**Definition 2.1.6** (Path). Each infinite execution of  $\mathcal{A}$  is called an infinite *path*. Finite *paths* in  $\mathcal{A}$  have the form

$$\pi = q_0 \xrightarrow{c_1} \dots \xrightarrow{c_n} q_n \xrightarrow{\sqrt{}} q_n$$

where  $q_n$  is a quiescent state.

In the sequel, we shall use the symbol  $\eta$  for executions and the symbol  $\pi$  to range over paths. We write  $\mathsf{Paths}(q)$  to denote the set of all paths starting in q and  $\mathsf{Exec}_\mathsf{fin}(q)$  for the set of all finite executions starting in q. The  $\mathsf{length}\ |\pi|$  of a path  $\pi$  is the total number of transitions taken in  $\pi$  (including the pseudo-transition with label  $\sqrt{}$ ). Thus, the length of an infinite path is  $\infty$ , while the length of a finite path  $\pi$  as in Definition 2.1.6 is n+1.

Let  $\pi = q_0 \xrightarrow{c_1} q_1 \xrightarrow{c_2} \dots$  be a path and  $0 \le n < |\pi|$ . Then  $\pi \downarrow n$  denotes the prefix of path  $\pi$  with length n. Thus,

$$\pi \downarrow n \stackrel{\text{def}}{=} q_0 \xrightarrow{c_1} \dots \xrightarrow{c_n} q_n$$

is an execution. For finite paths of length n, the n-th prefix is defined to be  $\pi$ . In particular, if  $n = |\pi|$  then  $\pi \downarrow n = \pi$  is a path.

The I/O-stream ios $(\eta)$  of a finite execution  $\eta$  is the finite word over CIO that is obtained by taking the projection to the labels of the transitions. Similarly, for finite paths the I/O-stream is a finite word over CIO $_{\checkmark}$ .

**Definition 2.1.7** (I/O-stream (IOS)). If  $\eta = q_0 \xrightarrow{c_1} \dots \xrightarrow{c_n} q_n$  is a finite execution then  $\log(\eta) \stackrel{\text{def}}{=} c_1 \dots c_n \in \text{CIO}^*$ . The associated I/O-stream for a finite path

$$\pi = q_0 \xrightarrow{c_1} \dots \xrightarrow{c_n} q_n \xrightarrow{\sqrt{}} q_n$$

is defined by  $\mathsf{ios}(\pi) \stackrel{\text{def}}{=} c_1 \dots c_n \checkmark \in \mathsf{CIO}^* \checkmark$ . The set of all I/O-streams is denoted by  $\mathsf{IOS} \stackrel{\text{def}}{=} \mathsf{CIO}^* \cup \mathsf{CIO}^* \checkmark$ . The associated I/O-stream for an infinite execution or path  $\pi' = q_0 \stackrel{c_1}{\longrightarrow} q_1 \stackrel{c_2}{\longrightarrow} \dots$  is defined by  $\mathsf{ios}(\pi') \stackrel{\text{def}}{=} c_1 c_2 \dots \in \mathsf{CIO}^\omega$ .

**Composition.** Constraint automata provide a compositional semantics which is based on a parallel operator that allows synchronous and asynchronous I/O-activity. We present here a basic version of the product for arbitrary constraint automata. In the later chapters we will use a refined version of product that allows the product operator to be applied for *composable* constraint automata  $A_1$  and  $A_2$  only. The formal definition of composability will be given at the end of this section.

**Definition 2.1.8** (Constraint automata product [BSAR06]). The product automaton of two constraint automata  $A_i = \langle Q_i, \mathcal{N}_i, \longrightarrow_i, Q_{0,i}, \mathcal{Q}_i, AP_i, L_i \rangle$  for  $i \in \{1, 2\}$  is

$$\mathcal{A}_1 \bowtie \mathcal{A}_2 = \langle Q_1 \times Q_2, \mathcal{N}_1 \cup \mathcal{N}_2, \longrightarrow, Q_{0,1} \times Q_{0,2}, \mathcal{Q}, AP_1 \cup AP_2, L \rangle,$$

where  $\longrightarrow$  is defined by the following two rules for the asynchronous behavior

$$\frac{q \xrightarrow{c}_1 q' \land \mathsf{active}(c) \cap \mathcal{N}_2 = \emptyset}{\langle q, p \rangle \xrightarrow{c} \langle q', p \rangle} \qquad \frac{p \xrightarrow{c}_2 p' \land \mathsf{active}(c) \cap \mathcal{N}_1 = \emptyset}{\langle q, p \rangle \xrightarrow{c} \langle q, p' \rangle} \tag{2.1}$$

and one synchronization rule

$$\frac{q \xrightarrow{c_1}_1 q' \land p \xrightarrow{c_2}_2 p' \text{ with } c_1|_{\mathcal{N}_1 \cap \mathcal{N}_2} = c_2|_{\mathcal{N}_1 \cap \mathcal{N}_2}}{\langle q, p \rangle \xrightarrow{c_1 \oplus c_2}_{} \langle q', p' \rangle}$$

(2.2)

where

$$c|_{N}(A) \stackrel{\text{def}}{=} \begin{cases} c(A) & \text{for all } A \in N \\ \bot & \text{else} \end{cases}$$

and  $c_1 \oplus c_2$  is the unique concurrent I/O-operation with

$$\mathsf{active}(c_1 \oplus c_2) = \mathsf{active}(c_1) \cup \mathsf{active}(c_2) \text{ and } (c_1 \oplus c_2)|_{\mathcal{N}_i} = c_i.$$

The set of quiescent states in the product is defined as follows

$$\mathcal{Q} \stackrel{\text{def}}{=} \mathcal{Q}_1 \times \mathcal{Q}_2 \ \cup \ \{ \langle q, p \rangle \in Q_1 \times Q_2 \mid \mathsf{CIO}(\langle q, p \rangle) = \emptyset \}$$

and the labeling function L of the product automaton is given by

$$L(\langle p, q \rangle) \stackrel{\text{def}}{=} L_1(p) \cup L_2(q).$$

The constraint automaton product operator is commutative and associative.

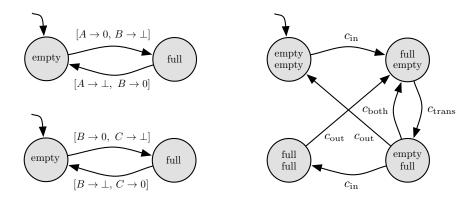

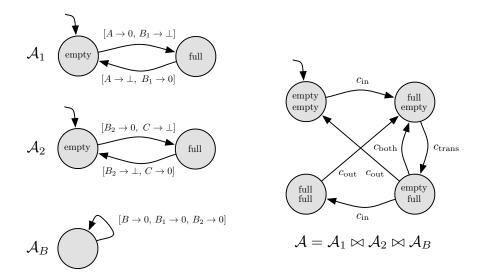

**Example 2.1.9** (Product automaton). On the left of Figure 2.2 the two constraint automata (without labels) of two FIFO channels with capacity one are depicted. Both automata are similar to the automaton shown in Example 2.1.3, but now for the singleton data domain Data  $= \{0\}$ . Here, we assume that the two automata share and synchronize on dataflow location B. The product of these two automata shown on the right of Figure 2.2 can be interpreted as a FIFO channel with capacity two.

The concurrent I/O-operations of the product automaton are defined as follows:

where  $c_{\rm in}$  stands for the concurrent I/O-operation when the data item will be written to the first FIFO (via port A),  $c_{\rm trans}$  describes the transfer of the data item from the first to the second FIFO via their shared dataflow location B and  $c_{\rm out}$  stands for a read operation from the second FIFO (via port C). The remaining  $c_{\rm both} \in \text{CIO}$  stands for the possibility that the read from the second FIFO and the write to the first FIFO can happen in the same time step.

13

Figure 2.2: Product automaton of two FIFO channels with capacity one and  $Data = \{0\}$

*Hiding.* The hide operator for constraint automata provides a means to declare certain dataflow locations as local and non-observable from outside. This can, e.g., be used to abstract from internal behavior of a component connector or coordinating network or remove information about the channel-ends.

For the hiding there are two important variants. The first one is the *structure-preserving hide* which simply removes all names for dataflow locations  $N \subseteq \mathcal{N}$  which should be hidden from the transition labels. The hiding in constraint automata is achieved by applying a projection  $c|_{\mathcal{N} \setminus N}$  on all transitions.

**Definition 2.1.10** (Structure-preserving hide). Let  $\mathcal{A} = \langle Q, \mathcal{N}, \longrightarrow, Q_0, \mathcal{Q}, AP, L \rangle$  be a constraint automaton. The result of hiding some dataflow locations  $N \subseteq \mathcal{N}$  from  $\mathcal{A}$  is the constraint automaton

$$\mathcal{A}_{\backslash N} = \langle Q, \mathcal{N} \setminus N, \longrightarrow_{\backslash}, Q_0, \mathcal{Q}_{\backslash}, AP, L \rangle,$$

where the transition relation  $\longrightarrow_{\setminus}$  is given by  $q \xrightarrow{c} q'$  iff  $q \xrightarrow{-c|_{\mathcal{N} \setminus N}}_{\setminus} q'$ . The set of quiescent states  $\mathcal{Q}$  is defined as

$$\mathcal{Q}_{\backslash} \stackrel{\mathrm{def}}{=} \mathcal{Q} \setminus \{q \in \mathcal{Q} \mid \text{there exists some } q \xrightarrow{c} q' \text{ with } \emptyset \neq \mathsf{active}(c) \subseteq N\}.$$

Hence, dataflow must not stop in states with newly introduced  $c_{\emptyset}$ -transitions.

Note that, for transitions in  $\mathcal{A}$  of the form  $q \xrightarrow{c} q'$  with  $\operatorname{active}(c) \subseteq N$ , the structure-preserving hide will produce transitions of the form  $q \xrightarrow{c_{\emptyset}} q'$ , but the structure of the constraint automaton remains unchanged. Although there are other variants of hiding, the structure-preserving hide will be the most relevant in the context of this thesis as it preserves the structure and hence the branching behavior of the underlying constraint automaton.

Another important variant of hiding, called aggregating hide also uses the projection  $c|_{\mathcal{N}\backslash N}$ , but it removes newly introduced  $c_{\emptyset}$ -transitions. Let  $\mathcal{A}=\langle Q,\mathcal{N},\longrightarrow,Q_0,\mathcal{Q},AP,L\rangle$  be a constraint automaton. The result of hiding some dataflow locations  $N\subseteq\mathcal{N}$  from  $\mathcal{A}$  is the constraint automaton

$$\mathcal{A}_{\times N} = \langle Q, \mathcal{N} \setminus N, \longrightarrow_{\times}, Q_0, \mathcal{Q}_{\times}, AP, L \rangle,$$

where the transition relation  $\longrightarrow_{\times}$  is given by:

$$\longrightarrow_{\times} \stackrel{\text{def}}{=} \bigcup_{i \in \mathbb{N}} R^{(i)},$$

where the  $R^{(i)}$  are defined as follows

$$\begin{array}{ll} R^{(0)} & \stackrel{\mathrm{def}}{=} & \left\{ \langle q, c|_{\mathcal{N} \backslash N}, p \rangle \mid \text{there exists a transition } q \stackrel{c}{\longrightarrow} q' \right\} \text{ and } \\ R^{(i+1)} & \stackrel{\mathrm{def}}{=} & \left\{ \langle q, c_2, q' \rangle \mid \text{there exists } q \stackrel{c_1 \in \mathsf{CIO}_N}{\longrightarrow} p \text{ and } \langle p, c_2, q' \rangle \in R^{(i)} \right\} \ \cup \\ & \left\{ \langle q, c_1, q' \rangle \mid \text{there exists } p \stackrel{c_2 \in \mathsf{CIO}_N}{\longrightarrow} q' \text{ and } \langle q, c_1, p \rangle \in R^{(i)} \right\}. \end{array}$$

Here,  $\mathsf{CIO}_N$  denotes the set of all concurrent I/O-operations  $c \in \mathsf{CIO}$  with  $\mathsf{active}(c) \subseteq N$ . The set of quiescent states  $\mathcal Q$  is defined as for the structure-preserving hide:

$$\mathcal{Q}_{\backslash} \stackrel{\text{def}}{=} \mathcal{Q} \setminus \{q \in \mathcal{Q} \mid \text{there exists some } q \stackrel{c}{\longrightarrow} q' \text{ with } \emptyset \neq \mathsf{active}(c) \subseteq N\}.$$

Note that applying the aggregating hide operator may change the branching behavior of the underlying constraint automaton.

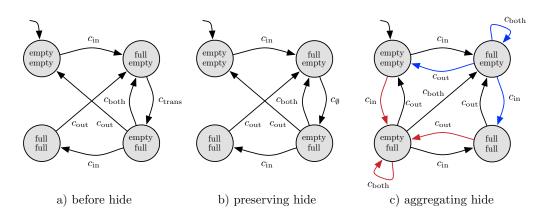

**Example 2.1.11** (Hiding variants). Figure 2.3 a) shows the constraint automaton  $\mathcal{A}$  for a FIFO channel with capacity two as considered in Example 2.1.9.

Figure 2.3: Hiding variants applied to the constraint automaton from Example 2.1.9

The transition labels are as before:

Figure 2.3 b) shows the constraint automaton  $\mathcal{A}_{\backslash N}$  for the port-set  $N=\{B\}$ . Hence, port B will be removed from all transitions  $q \xrightarrow{c} q'$  with  $c(B) \neq \bot$ . For the given constraint automaton  $\mathcal{A}$  this affects the  $c_{\text{trans}}$  transition only.

Figure 2.3 c) depicts the constraint automaton  $\mathcal{A}_{\times N}$  for the same port-set  $N=\{B\}$ . The newly added transitions  $q \xrightarrow{c}_{\times} q'$  result from combining "regular transitions" in  $\mathcal{A}$  (where  $c \neq c_{\emptyset}$ ) with  $c_{\emptyset}$ -transitions, either of the form  $q \xrightarrow{c} p \xrightarrow{c_{\emptyset}} q'$  or  $q \xrightarrow{c_{\emptyset}} p \xrightarrow{c} q'$  with  $c \neq c_{\emptyset}$ .

#### 2.2. Symbolic representation of constraint automata

Sometimes it is advantageous to use a symbolic representation of the transition relation by combining transitions with the same starting and target state (e.g., in our implementation of the model checker). For this purpose, we deal with I/O-constraints, i.e., propositional formulas in positive normal form that stand for *sets* of concurrent I/O-operations. The I/O-constraints may impose conditions on the dataflow locations that may or may not be involved and on the data items written on or read from them.

**Definition 2.2.1** (I/O-constraints (IOC)). The abstract syntax of I/O-constraints is given by the grammar:

ioc ::=

$$tt \mid ff \mid A \mid \neg A \mid (d_{A_1}, \dots, d_{A_k}) \in D \mid \text{ioc}_1 \wedge \text{ioc}_2 \mid \text{ioc}_1 \vee \text{ioc}_2$$

where  $A \in \mathcal{N}, A_1, \dots, A_k$  are pairwise distinct dataflow locations in  $\mathcal{N}$  and  $D \subseteq \mathsf{Data}^k$ .

The meaning of an I/O-constraint ioc is a subset  $\lceil ioc \rceil$  of CIO defined in the expected way. We define  $\lceil tt \rceil \stackrel{\text{def}}{=} \text{CIO}$ ,  $\lceil ff \rceil \stackrel{\text{def}}{=} \emptyset$ , and for the literals  $A \in \mathcal{N}$  and their negations  $\neg A$ :

The I/O-constraints  $(d_{A_1}, \ldots, d_{A_k}) \in D$  impose conditions for the written and read data items. That is,  $\lceil (d_{A_1}, \ldots, d_{A_k}) \in D \rceil$  agrees with the set

$$\{c \in CIO : \{A_1, \dots, A_k\} \subseteq active(c) \text{ and } (c(A_1), \dots, c(A_k)) \in D\}.$$

Conjunction and disjunction have their standard meaning, i.e.,

We often use simplified notations for the IOC of the form  $(d_{A_1},\ldots,d_{A_k})\in D$ . E.g., the notation  $d_A=d_B$  is a shorthand for  $(d_A,d_B)\in\{(d_1,d_2)\in \mathsf{Data}^2:d_1=d_2\}$ , while  $A\wedge(d_B\in D)$  stands for the set  $\{c\in\mathsf{CIO}:\{A,B\}\subseteq\mathsf{active}(c)\wedge c(B)\in D\}$ . The notation  $\{A,B\}$  is used as a shorthand for the set  $\{c\in\mathsf{CIO}:\mathsf{active}(c)=\{A,B\}\}$ . Let IOC denote the set of IO-constraints.

**Definition 2.2.2** (Constraint automata (IOC-syntax)). A constraint automaton in IOC-syntax is a tuple  $\mathcal{A} = \langle Q, \mathcal{N}, \longrightarrow, Q_0, \mathcal{Q}, AP, L \rangle$ , where Q is a finite and nonempty set of states,  $\mathcal{N}$  a finite set of port names,  $\longrightarrow$  is a subset of  $Q \times \mathsf{IOC} \times Q$  called the transition relation of  $\mathcal{A}$ ,  $Q_0 \subseteq Q$  a nonempty set of initial states, AP a finite set of atomic propositions, and  $L: Q \to 2^{AP}$  a labeling function. We write  $q \xrightarrow{g} p$  instead of  $\langle q, g, p \rangle \in \longrightarrow$ .

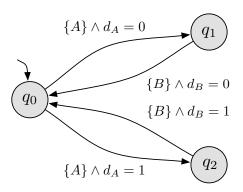

**Example 2.2.3** (Constraint automata (IOC-syntax)). As an example we revisit the constraint automaton from Example 2.1.3 and present it using the IOC-syntax (cf. Figure 2.4).

Figure 2.4: Constraint automaton for a component or connector (IOC-syntax)

The IOC-syntax equates to the original syntax of constraint automata as introduced in [BSAR06]. The use of this alternative syntax allows a (graphical) representation of constraint automata which is more compact and independent from a specific data domain. The same idea can be applied to states rather than on transition labels. By adding variables to states we can avoid the explicit enumeration of states for different data values. Figure 2.5 depicts a parameterized version of the constraint automata from Example 2.2.3 in IOC-syntax.

Here, the state  $q_1\langle d\rangle$  is equipped with memory. The variable  $d\in \mathsf{Data}$  is holding the value of the buffer. Incoming and outgoing transitions of state  $q_1\langle d\rangle$  can refer to the actual value of d whereas the value is irrelevant for other states. This idea allows prototype definitions of components and connectors for arbitrary data domains. Our specification language CARML, which will be introduced in Subsection 3.2.2, makes use of this feature. E.g., FIFO1 channels can be defined to store arbitrary values without knowing the data domain in advance.

Figure 2.5: Constraint automaton with memory for a component or connector

The IOC-syntax uses I/O-constraints rather than concurrent I/O-operations for the transition labels, i.e., the labels are now Boolean conditions on active ports and the dataflow, which serve as guards. The I/O-constraints can immediately be translated into a symbolic representation as it is used in our implementation of the model checker (cf. Section 5.2). For this thesis we will similarly use both notions when adequate as they are equally expressive.

The basic definition of constraint automata as presented by now lacks some important information which will be added to the concept of constraint automata in the next section. We will add the concepts of *polarity*, as the direction in which data flows plays a crucial role for the composition in Reo. The second information added to constraint automata are *data types* which play an important role for defining the state space of a constraint automaton as well for specifying the domain for the observable data at dataflow locations.

### 2.3. Data types and polarity

Data types will play an important role for the syntax and semantics of our modeling languages RSL and CARML as they support variables, messages and ports that may have different types. We will now provide the basic terminology for data types and related notions that will be used throughout this thesis. First we will look at the set DT of data types with a fixed semantics. When using our modeling languages RSL and CARML the set DT consists of Booleans, finite integer ranges, enumerations, and structured data types such as arrays and unions. For the concepts introduced throughout this section the precise definition of the data types in DT is not required.

Data types with fixed semantics. Let DT denote a set of data types covering standard data types, such as Booleans or finite integer ranges, or user-defined data types with a fixed semantics, such as arrays and unions over elements of a predefined data type or enumeration types. Let Op denote a set of operators on the data types in DT such as conjunction, disjunction, negation for Booleans and arithmetic operations like addition and multiplication for integers. Furthermore, Pred denotes a set of predicates, such as the standard binary comparison predicates =, <,  $\le$ , and so on.

Formally, the elements of DT are fixed finite non-empty sets and each operator  $op \in \mathsf{Op}$  is a function

$$op: T_1 \times \ldots \times T_k \to T$$

where  $(T_1, \ldots, T_k, T) \in \mathsf{DT}^{k+1}$  and  $k \in \mathbb{N}$ . The tuple  $\langle T_1, \ldots, T_k, T \rangle$  is called the type of

op, denoted  $\mathfrak{type}(op)$ . Each predicate  $pr \in \mathsf{Pred}$  is a subset of  $T_1 \times \ldots \times T_k$  where  $k \geq 1$  and  $T_1, \ldots, T_k \in \mathsf{DT}$ . We write  $\mathfrak{type}(pr)$  for the tuple  $\langle T_1, \ldots, T_k \rangle$ .

**Definition 2.3.1** (Signature). A signature is a tuple  $\mathfrak{Sig} = \langle \mathfrak{DT}, \mathfrak{Op}, \mathfrak{Pred}, \mathfrak{Dar} \rangle$  where DT  $\subseteq \mathfrak{DT}$ , Op  $\subseteq \mathfrak{Op}$ , Pred  $\subseteq \mathfrak{Pred}$  and  $\mathfrak{Var}$  is a set of typed variables, i.e., for each variable  $V \in \mathfrak{Var}$  its type, which is denoted by  $\mathfrak{type}(V)$ , is an element of  $\mathfrak{DT}$ .

**Terms and atomic propositions.** Terms over Sig are built by variables, constants, and operator symbols in a type-consistent manner. Formally, terms over Sig are defined recursively according to the following statements:

- (1) Each variable  $V \in \mathfrak{Var}$  is a term of type  $\mathfrak{type}(V)$  and each constant  $op \in \mathfrak{Op}$  (i.e., 0-ary operator in  $\mathfrak{Op}$ ) is a term of type  $\mathfrak{type}(op)$ .

- (2) If  $t_1, \ldots, t_k$  are terms such that the type of  $t_i$  is  $T_i$  and  $op \in \mathfrak{Op}$  with  $\mathfrak{type}(op) = (T_1, \ldots, T_k, T)$  then  $op(t_1, \ldots, t_k)$  is a term of type T.

Atomic propositions over  $\mathfrak{Sig}$  are type-consistent expressions stating that a certain tuple of terms is an element of a predicate in  $\mathfrak{Pred}$ .

Formally, if  $pr \in \mathfrak{Pred}$  with  $\mathfrak{thpe}(pr) = (T_1, \ldots, T_k)$  and  $t_1, \ldots, t_k$  are terms over  $\mathfrak{Sig}$  such that  $t_i$  is of type  $T_i$  then  $pr(t_1, \ldots, t_k)$  is called an atomic proposition over  $\mathfrak{Sig}$ .

Interpretations of signatures. For the semantics of terms and atomic propositions over a signature, we have to consider an interpretation  $\mathcal I$  that provides type-consistent meanings for the uninterpreted data types  $T \in \mathfrak{DT} \setminus \mathsf{DT}$ , operator symbols  $op \in \mathfrak{Dp} \setminus \mathsf{Op}$ , predicate symbols  $pr \in \mathfrak{Pred} \setminus \mathsf{Pred}$ , and the variables  $V \in \mathfrak{Dar}$ . That is,  $\mathcal I$  assigns a finite set  $T^{\mathcal I} \neq \emptyset$  to each data type symbol T, an element of  $V^{\mathcal I} \in T^{\mathcal I}$  to each variable of type T, a function  $op^{\mathcal I}: T_1^{\mathcal I} \times \ldots \times T_k^{\mathcal I} \to T^{\mathcal I}$  to each operator symbol op of type  $(T_1, \ldots, T_k, T)$  and a predicate  $pr^{\mathcal I} \subseteq T_1^{\mathcal I} \times \ldots \times T_k^{\mathcal I}$  to each predicate symbol pr of type  $(T_1, \ldots, T_k)$ .

We treat  $\mathcal{I}$  as an interpretation for all symbols of  $\mathfrak{Sig}$  by putting  $S^{\mathcal{I}} = S$  for all predefined symbols  $S \in \mathsf{DT} \cup \mathsf{Op} \cup \mathsf{Pred}$ . The semantics  $t^{\mathcal{I}} \in T^{\mathcal{I}}$  of a term of type T and the truth value  $pr(t_1,\ldots,t_k)^{\mathcal{I}} \in \{\mathsf{true},\mathsf{false}\}$  for an interpretation  $\mathcal{I}$  and an atomic proposition  $pr(t_1,\ldots,t_k)$  are defined in the obvious way.

Apart from the type information, we require to add information about the polarity of the dataflow locations, i.e., whether the dataflow locations serve for input or output. For this, we will add the sets  $\mathcal{N}^{\rm src}$  and  $\mathcal{N}^{\rm snk}$  which are disjoint subsets of  $\mathcal{N}$ . Intuitively,  $\mathcal{N}^{\rm src}$  stands for the set of input ports (so called *sources*) and  $\mathcal{N}^{\rm snk}$  for the set of output ports (called *sinks*). With the help of *dataflow vocabulary* we may add type and polarity information to the concept of constraint automata.

**Definition 2.3.2** (Dataflow vocabulary). A dataflow vocabulary over a signature  $\mathfrak{Sig}$  is a tuple  $\mathfrak{Voc} = \langle \mathcal{N}, \mathcal{N}^{\mathrm{src}}, \mathcal{N}^{\mathrm{snk}}, \lambda \rangle$  where  $\mathcal{N}^{\mathrm{src}} \cup \mathcal{N}^{\mathrm{snk}} \subseteq \mathcal{N}$  is a set of dataflow locations containing all source and sink locations such that  $\mathcal{N}^{\mathrm{src}} \cap \mathcal{N}^{\mathrm{snk}} = \emptyset$  and  $\lambda : \mathcal{N} \to \mathfrak{DT}$  is a function that assigns to each dataflow location A its message-type  $\lambda(A)$ , i.e., the type of data items that can be passed via dataflow location A.

**Definition 2.3.3** (Extended constraint automaton). An *extended constraint automaton* is a tuple  $\langle \mathcal{A}, \mathfrak{Voc} \rangle$  where  $\mathcal{A} = \langle Q, \mathcal{N}, \longrightarrow, Q_0, \mathcal{Q}, AP, L \rangle$  is a constraint automaton and  $\mathfrak{Voc} = \langle \mathcal{N}, \mathcal{N}^{\mathrm{src}}, \mathcal{N}^{\mathrm{snk}}, \lambda \rangle$  its associated dataflow vocabulary. Then, adding type information to ports of  $\mathcal{A}$  imposes some obvious side conditions on the possible transitions. That is, any concurrent I/O-operation c that appears in a transition  $q \stackrel{c}{\longrightarrow} q'$  maps some  $A \in \mathcal{N}$  to an element of its type  $\lambda(A)$ , i.e.,

if

$$c(A) = d \neq \bot$$

then  $d \in \lambda(A)$  for all  $A \in \mathcal{N}$ .

A concurrent I/O-operation  $c \in \text{CIO}$  is called type-safe with respect to  $\mathfrak{Voc}$  if it satisfies the above condition. For an extended constraint automaton  $\langle \mathcal{A}, \mathfrak{Voc} \rangle$  where  $\mathcal{A}$  is specified in IOC-syntax this means that for a given transition  $q \stackrel{g}{\longrightarrow} q'$  in  $\mathcal{A}$  we allow only type-safe concurrent IO-operations to fire when reasoning about runs in  $\mathcal{A}$ , i.e.,  $q \stackrel{c}{\longrightarrow} q'$  if  $c \in \lceil g \rceil$  and  $c \in [g]$  and  $c \in [g]$  and  $c \in [g]$

**Definition 2.3.4** (Composability). Let  $\langle \mathcal{A}_i, \mathfrak{Voc}_i \rangle$ ,  $i \in \{1,2\}$  be two extended constraint automata with constraint automata  $\mathcal{A}_i = \langle Q_i, \mathcal{N}_i, \longrightarrow_i, Q_{0,i}, \mathcal{Q}_i, AP_i, L_i \rangle$  and associated dataflow vocabularies  $\mathfrak{Voc}_i = \langle \mathcal{N}_i, \mathcal{N}_i^{\mathrm{src}}, \mathcal{N}_i^{\mathrm{snk}}, \lambda_i \rangle$ . The two extended constraint automata  $\langle \mathcal{A}_1, \mathfrak{Voc}_1 \rangle$  and  $\langle \mathcal{A}_2, \mathfrak{Voc}_2 \rangle$  are called *composable* if the following conditions hold for all dataflow locations  $A \in \mathcal{N}_1 \cap \mathcal{N}_2$ :

i)

$$AP_1 \cap AP_2 = \emptyset$$

ii)

$$A \in \mathcal{N}_1^{\mathrm{src}} \cap \mathcal{N}_2^{\mathrm{snk}}$$

or  $A \in \mathcal{N}_2^{\mathrm{src}} \cap \mathcal{N}_1^{\mathrm{snk}}$

iii)

$$\lambda_1(A) = \lambda_2(A)$$

Please note, that here we require strict type consistency in the third condition to simplify the presentation throughout the next chapters. In the implementation that is presented in Chapter 5 we support some implicit casts for simple data types.

**Definition 2.3.5** (Extended product). Let  $\langle \mathcal{A}_i, \mathfrak{Voc}_i \rangle$ ,  $i \in \{1,2\}$  be two composable extended constraint automata as in Definition 2.3.4. The *extended product automaton* is defined as  $\langle \mathcal{A}_1 \bowtie \mathcal{A}_2, \mathfrak{Voc} \rangle$ , where  $\mathfrak{Voc} = \langle \mathcal{N}, \mathcal{N}^{\mathrm{src}}, \mathcal{N}^{\mathrm{snk}}, \lambda \rangle$  is the associated dataflow vocabulary with

$$\begin{array}{cccc} \mathcal{N} & \stackrel{\mathrm{def}}{=} & \mathcal{N}_1 \cup \mathcal{N}_2, \\ \mathcal{N}^{\mathrm{src}} & \stackrel{\mathrm{def}}{=} & (\mathcal{N}_1^{\mathrm{src}} \cup \mathcal{N}_2^{\mathrm{src}}) \setminus (\mathcal{N}_1 \cap \mathcal{N}_2), \\ \mathcal{N}^{\mathrm{snk}} & \stackrel{\mathrm{def}}{=} & (\mathcal{N}_1^{\mathrm{snk}} \cup \mathcal{N}_2^{\mathrm{snk}}) \setminus (\mathcal{N}_1 \cap \mathcal{N}_2), \text{ and} \\ \lambda(A) & \stackrel{\mathrm{def}}{=} & \begin{cases} \lambda_1(A) & \text{if } A \in \mathcal{N} \setminus \mathcal{N}_2 \\ \lambda_2(A) & \text{else} \end{cases}$$

In the next chapter we will look at the modeling formalism and languages used throughout this thesis. To keep notations simple we will identify extended constraint automata  $\langle \mathcal{A}, \mathfrak{Voc} \rangle$  with  $\mathcal{A}$  whenever possible. Furthermore, we assume that  $\langle \mathcal{A}_1, \mathfrak{Voc}_1 \rangle$  and  $\langle \mathcal{A}_2, \mathfrak{Voc}_2 \rangle$  are composable (with respect to Definition 2.3.4) whenever applying the constraint automata product to  $\mathcal{A}_1$  and  $\mathcal{A}_2$ .

# 3 | Modeling formalism and languages

Reo [Arb04] is a declarative modeling language for specifying the glue code for coordinating components from outside. In this *exogenous* approach, the components do not need to be aware of the presence of each other. The components communicate by sending and receiving their data via a network of channels.

The *Reo scripting language* (RSL) [BBKK09a, BKK12] is inspired by Reo and yields an elegant declarative framework for the compositional construction of connectors by creating instances of components and channels and then glueing their channels-ends, the I/O-ports of components, or sub-connectors together. This is done via join operations, resulting in a network called *Reo circuit*. RSL mainly serves as a specification language for Reo component connectors and networks. The formal semantics of RSL is (and Reo itself) based on constraint automata [BBKK09a], which can be constructed in a compositional way by providing constraint automata models for each channel and component and mimicking Reo's operators by corresponding operators for constraint automata [BSAR06].

The interface behavior of components, channels, and connectors instantiated and composed by RSL scripts can be specified within our second modeling language CARML (constraint automata reactive module language). CARML uses features of reactive modules [AH99] and together with RSL the two languages form a hybrid modeling approach. As the two languages are based on the same operational semantic model, this hybrid modeling approach allows to either specify the interface behavior of any entity of a component-based system by providing a CARML module or by providing an RSL script composing the entity from smaller building blocks.

*Organization.* Section 3.1 summarizes the syntax, semantics and main concepts of the coordination language Reo as introduced in [Arb04]. Section 3.2 we will introduce syntax and semantics of our modeling languages RSL and CARML.

The work presented in the latter section has partially been published in [BBKK09a, BKK12].

### 3.1. The coordination language Reo

In this section we give a brief introduction the channel-based coordination language Reo as introduced in [Arb04]. The primitives in Reo are channels. A Reo channel consists of exactly two *channel-ends* which are either declared to be *source-end* if they permit writing of data or *sink-end* if they allow the reading of data.