# Vertical Enhancement-Mode InAs Nanowire Field-Effect Transistor With 50-nm Wrap Gate

Claes Thelander, Linus E. Fröberg, Carl Rehnstedt, Lars Samuelson, and Lars-Erik Wernersson

Abstract—We present results on fabrication and dc characterization of vertical InAs nanowire wrap-gate field-effect transistor arrays with a gate length of 50 nm. The wrap gate is defined by evaporation of 50-nm Cr onto a 10-nm-thick  $HfO_2$  gate dielectric, where the gate is also separated from the source contact with a 100-nm SiO<sub>x</sub> spacer layer. For a drain voltage of 0.5 V, we observe a normalized transconductance of 0.5 S/mm, a subthreshold slope around 90 mV/dec, and a threshold voltage just above 0 V. The highest observed normalized on current is 0.2 A/mm, with an off current of 0.2 mA/mm. These devices show a considerable improvement compared to previously reported vertical InAs devices with SiN<sub>x</sub> gate dielectrics.

Index Terms-Field-effect transistor (FET), InAs, nanowires.

# I. INTRODUCTION

**D** EVELOPMENT of lithographic techniques has given access to shorter gate lengths in transistor processing, and thus, higher possible switching frequencies. However, the aggressive scaling of the gate length comes at the expense of control of the charges in the transistor channel. As a consequence, short-channel effects such as high off currents and poor subthreshold slopes are becoming problematic. The design of the field-effect transistors (FETs) is therefore rapidly moving toward the use of high- $\kappa$  dielectrics and geometries, where the gate partially, or fully, wraps around the transistor channel [1]. In addition, there is a strong interest in introducing III–V channels to boost the drive current.

Wrap-gate FETs show the possibility of high scalability [2], and the concept has recently been demonstrated with both lateral and vertical channel geometries. Suk *et al.* have shown transistor data for 10-nm lateral Si wires with a full wrap gate using SiO<sub>2</sub> as gate dielectric [3]. In the vertical geometry, many groups are currently working with epitaxially grown nanowires [4]–[7]. An important motivation here is the possibility of growing group III–V nanowires directly on Si, as well as highly lattice-mismatched semiconductor heterostructures within a wire [8]–[10]. Successful integration of vertical nanowires as active element in transistors may offer consid-

Manuscript received October 10, 2007; revised December 6, 2007. This work was supported by the Swedish Foundation for Strategic Research (SSF), by the Knut and Alice Wallenberg Foundation, by the Swedish Research Council (VR), and by the EU-project NODE 015783. The review of this letter was arranged by Editor J. Del Alamo.

C. Thelander and L. E. Fröberg are with the Solid State Physics, Lund University, 221 00 Lund, Sweden, and also with Qumat Technologies AB, 222 24 Lund, Sweden (e-mail: claes.thelander@ftf.lth.se).

C. Rehnstedt, L. Samuelson, and L.-E. Wernersson are with the Solid State Physics, Lund University, 221 00 Lund, Sweden.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2007.915374

erable improvement in device performance and may also give rise to new device concepts. Engineering of the band structure in a nanowire could improve breakdown voltages, give rise to higher mobilities, and substantially reduce power consumption by lowering the drive voltage. However, postgrowth processing on vertical wires is challenging as they are less mechanically stable than their lateral counterparts, and it is difficult to accurately control the vertical position and length of a wrap gate and the surrounding dielectric layers. Moreover, doping is not fully understood for nanowires, and radio frequencycompatible devices have not yet been realized.

In this letter, we report on fabrication of vertical wrap-gate FETs based on InAs nanowires with an average diameter of 50 nm. The length of the wrap gate is set by the thickness of the evaporated Cr (50 nm), which means that the process is scalable to shorter gate lengths. The Cr layer is separated from the nanowire channel by a 10-nm-thick HfO<sub>2</sub> gate dielectric and from the source contact with 100-nm SiO<sub>x</sub>. We observe a considerable improvement in on/off current ratio  $(I_{\rm ON}/I_{\rm OFF})$  and maximum transconductance  $g_m$  compared to previous work, where Au/SiN<sub>x</sub> was used as gate metal/dielectric [11].

## II. NANOWIRE GROWTH AND PROCESSING

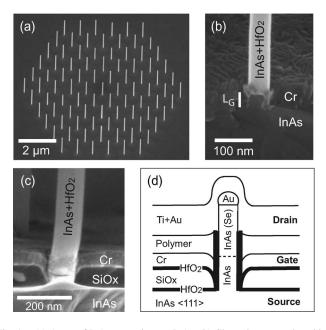

Arrays of nanowires are obtained by first fabricating ordered Au seeds by electron-beam lithography and metal evaporation/ liftoff of Au onto InAs  $\langle 111 \rangle$ B substrates. Each sample has 120 arrays, with various selected seed diameters and array sizes. InAs nanowires are grown by chemical beam epitaxy at a temperature of 425 °C, using trimethylindium and tertiarybutylarsine as precursors. During the last stage of the growth, the sample is also exposed to ditertiarybutylselenium, which results in n-type (Se) doping of the top segment of the wires. An example of the largest array, having 91 nanowires, is shown in Fig. 1(a). The diameter spread was rather large for the sample studied here, around 50  $\pm$  10 nm, which is mainly caused by uncompensated proximity effects in the electronbeam exposure.

The first processing step after growth is deposition of 5-nm HfO<sub>2</sub> by atomic layer deposition (ALD) at 250 °C, using tetrakis (dimethylamido)hafnium(IV) and H<sub>2</sub>O as precursors. This is followed by tilted evaporation of 100-nm SiO<sub>x</sub> with the samples rotating. The purpose of the SiO<sub>x</sub> layer is to lift the gate layer from the substrate. Excess SiO<sub>x</sub>, which is deposited onto the sides of the nanowires, is removed with hydrogen fluoride (HF). This is followed by ALD of another 5-nm HfO<sub>2</sub>; the total thickness of the HfO<sub>2</sub> gate dielectric is thus 10 nm.

A gate-metal layer is deposited by tilted evaporation of 50-nm Cr onto rotating samples. This gives a high precision

Fig. 1. (a) Array of InAs nanowires on InAs. (b) Cleaved test sample, which shows that the thickness of the Cr gate layer around the base of the nanowire is around 50 nm ( $52^{\circ}$  tilt). (c) Side view of a cleaved test sample where a (dark) SiO<sub>x</sub> layer lifts the gate pad from the InAs source contact. (d) Schematic side view of the device.

in the resulting gate length. Excess material on the sides of the nanowires is removed by a short selective Cr etch. Fig. 1(b) shows the gate after removal of the side deposits for a cleaved test sample without the  $SiO_x$  source–gate spacer layer. The brighter contrast around the wire in Fig. 1(b) corresponds to the 10-nm-thick HfO<sub>2</sub>. When the sample was cleaved, the Cr removed the HfO<sub>2</sub> with which it was in contact. This reveals the effective nanowire gate length  $L_G$ , which in Fig. 1(b) is 50 nm. Fig. 1(c) shows another cleaved test sample, in this case with a SiO<sub>x</sub> spacer layer. It should be pointed out that both the SiO<sub>x</sub> and the Cr layers have downslopes close to the wire base in this case. Gate pads are formed from the Cr layer by resist deposition, ultraviolet (UV) lithography, Cr etching in HCl, and resist removal.

An organic insulating layer based on a cross-polymerized photoresist is used as gate–drain separation. A gate-via is first formed with UV lithography, and the resist is then cured and dry-etched to a desired thickness using oxygen plasma. Typically, the gate–drain separation is 100–200 nm, depending on the time used for etch back. The polymer layer is used as an etch mask when removing the HfO<sub>2</sub> from the top of the nanowires in buffered HF. The sample is then exposed to diluted NH<sub>4</sub>S<sub>x</sub>, and a thick Ti/Au layer is evaporated with the sample rotating with a large tilt angle. Finally, the drain and gate pads are formed by resist coating, optical lithography, and wet etching. Fig. 1(d) shows a schematic side view of the device.

# III. DC CHARACTERIZATION

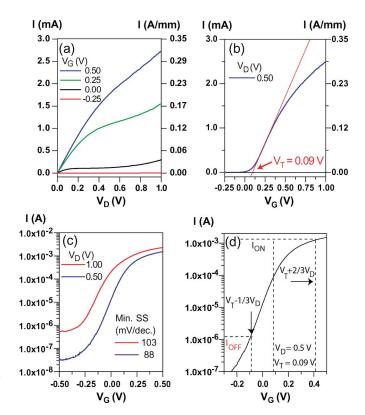

Electrical measurements [Fig. 2(a)-(d)] are carried out using a probe station, where the InAs substrate acts as a source, the intermediate metal layer in Fig. 1(d) connects to the wrap gate, and the upper metal contact acts as a drain. The transistors

Fig. 2. Data in (a)–(d) were obtained for a nanowire array with nominally 61 nanowires (yield ~90% estimated from scanning electron microscopy inspection after the measurements) and diameters around 50 nm. (a) Output characteristics for different wrap-gate voltages. (b) Transfer characteristics for  $V_D = 0.50$  V. (c) Transfer characteristics plotted in a logarithmic scale for  $V_D = 0.50$  and 1.0 V. (d) Extraction of  $I_{\rm ON}$  and  $I_{\rm OFF}$  using the metrics defined in [12].

operate as n-type MISFET accumulation devices, where a positive gate voltage leads to an increased carrier concentration in the channel. The threshold voltage  $V_T$  is extracted by a linear extrapolation from the point of the highest transconductance [Figs. 2(b) and 3(a)].  $V_T$  is very close to 0 V for most devices and shows a shift in  $V_D$  (drain-induced barrier lowering) of approximately 60 mV/V for  $V_D$  between 0.10 and 0.70 V.

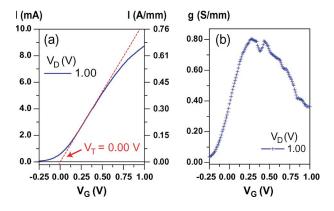

The average subthreshold slope minimum is around 100 mV/dec ( $V_D = 0.50$  V) and shows a small dependence on  $V_D$  between 0.10 and 0.70 V. However, at  $V_D = 1.0$  V, the minimum slope value has substantially increased for most arrays [Fig. 2(c)]. For  $V_D = 0.50$  V and a  $V_G$  swing of 0.50 V, we observe  $I_{\rm ON}/I_{\rm OFF}$  ratios around 10<sup>3</sup> ( $I_{\rm ON}$  obtained at  $V_G = V_T + 2/3V_D$  and  $I_{OFF}$  obtained at  $V_G = V_T - 1/3V_D$ in accordance with the metrics defined in [12]) [Fig. 2(d)]. The highest observed normalized  $g_m$  is 0.52 S/mm for  $V_D =$ 0.50 V, and 0.80 S/mm at  $V_D = 1.0$  V [Fig. 3(a) and (b)], where the values have been normalized by the total nanowire circumference and also adjusted for missing wires. It should be noted that the  $g_m$  values we report here, for large arrays of wires with a 50-nm gate length (0.80 S/mm), are comparable to previously reported values for individual InAs wires with a 2- $\mu$ m gate length, taking into consideration a difference in  $\pi$  in the definition of gate width [13].

In arrays with very few and thin wires, it is possible to find minimum values of the subthreshold slope approaching the limit of 60 mV/dec. However, such low values come at the

Fig. 3. (a) Transfer characteristics at  $V_D = 1.0$  V for an array with nominally 91 wires (yield ~90%). (b) Normalized transconductance plotted as a function of  $V_G$ .

TABLE IDATA FOR NANOWIRE ARRAYS WITH WIRE DIAMETERS AROUND 50 nm.THE VALUES FOR  $g_m$  HAVE BEEN NORMALIZED TO THE TOTALNANOWIRE CIRCUMFERENCE AND ALSO COMPENSATED FOR MISSINGWIRES. STANDARD DEVIATION IS SHOWN FOR THE AVERAGED DATA.SS: SUBTHRESHOLD SLOPE

| <i>V<sub>D</sub></i> (V) | $V_T$ (V)       | g <sub>m</sub><br>(S/mm) | Max. g <sub>m</sub><br>(S/mm) | SS<br>(mV/dec.) | Min. SS<br>(mV/dec.) |

|--------------------------|-----------------|--------------------------|-------------------------------|-----------------|----------------------|

| 0.50                     | $0.05\pm0.05$   | $0.44\pm0.06$            | 0.52                          | $100\pm 8$      | 88                   |

| 1.00                     | $0.00 \pm 0.04$ | $0.58\pm0.12$            | 0.80                          | $150 \pm 43$    | 103                  |

expense of a low  $g_m$ , which probably is a result of a large series resistance due to the small diameter at the source- and drain-side.

Overall, we observe gate leakage currents on the order of picoamperes, which correspond to a current density of  $10^{-4}$  A/cm<sup>2</sup> for the vertical gate–nanowire interface. The hysteresis in the drain current for  $V_G$  sweeps from -0.50 to 0.50 V is about 20 mV. However, it increases as the gate voltage is swept to more negative values than -0.50 V, which indicates a threshold voltage for charge trapping; for sweeps to  $V_G = -1.0$  V, the hysteresis has increased to around 200 mV.

It is important to note that some figures-of-merit for the devices, such as the subthreshold slope and the  $I_{\rm ON}/I_{\rm OFF}$  ratio, can become very poor even if only one individual wire in a 91-wire array has a failed wrap gate. Still, we observe surprisingly uniform values, indicating that the processing is stable over a large area of the sample and within the arrays. In Table I, averaged data are shown for nine functional nanowire arrays with wire diameters around 50 nm. The total number of wires included in the study is more than 700.

## IV. CONCLUSION

A fabrication process has been developed for the formation of wrap gates to InAs nanowires with a gate length of only 50 nm, where HfO<sub>2</sub> is used as a gate dielectric. The  $I_{\rm ON}/I_{\rm OFF}$  ratio is around 10<sup>3</sup>, and the minimum subthreshold slope is, on average, 100 mV/dec. We observe normalized  $g_m$  values up to 0.80 S/mm for  $V_D = 1.0$  V, which is comparable to what has been reported in literature for lateral InAs wires with a much longer gate length. Since the vertical wrap-gate formation reported here is made by metal evaporation, we expect that we would be able to further scale the gate length.

#### ACKNOWLEDGMENT

The authors would like to thank T. Löwgren, J. Ohlsson, and E. Lind for their valuable contributions.

#### REFERENCES

- [1] S. E. Thompson, R. S. Chau, T. Ghani, K. Mistry, S. Tyagi, and M. T. Bohr, "In search of 'Forever,' continued transistor scaling," *IEEE Trans. Semicond. Manuf.*, vol. 18, no. 1, pp. 26–36, Feb. 2005.

- [2] C. P. Auth and J. D. Plummer, "Scaling theory for cylindrical, fullydepleted, surrounding-gate MOSFET's," *IEEE Electron Device Lett.*, vol. 18, no. 2, pp. 74–76, Feb. 1997.

- [3] S. D. Suk, S.-Y. Lee, S.-M. Kim, E.-J. Yoon, M.-S. Kim, M. Li, C. W. Oh, K. H. Yeo, S. H. Kim, D.-S. Shin, K.-H. Lee, H. S. Park, J. N. Han, C. J. Park, J.-B. Park, D.-W. Kim, D. Park, and B.-I. Ryu, "High performance 5 nm radius twin silicon nanowire MOSFET (TSNWFET): Fabrication on bulk Si wafer, characteristics, and reliability," in *IEDM Tech. Dig.*, 2005, pp. 717–720.

- [4] T. Bryllert, L.-E. Wernersson, L. E. Froberg, and L. Samuelson, "Vertical high-mobility wrap-gated InAs nanowire transistor," *IEEE Electron Device Lett.*, vol. 27, no. 5, pp. 323–325, May 2006.

- [5] H. T. Ng, J. Han, T. Yamada, P. Nguyen, Y. P. Chen, and M. Meyyappan, "Single crystal nanowire vertical surround-gate field-effect transistor," *Nano Lett.*, vol. 4, no. 7, pp. 1247–1252, Jul. 2004.

- [6] M. T. Bjork, O. Hayden, H. Schmid, H. Riel, and W. Riess, "Vertical surround-gated silicon nanowire impact ionization field-effect transistors," *Appl. Phys. Lett.*, vol. 90, no. 14, p. 142 110, Apr. 2007.

- [7] V. Schmidt, H. Riel, S. Senz, S. Karg, W. Riess, and U. Gösele, "Realization of a silicon nanowire vertical surround-gate field-effect transistor," *Small*, vol. 2, no. 1, pp. 85–88, Jan. 2006.

- [8] M. T. Bjork, B. J. Ohlsson, T. Sass, A. I. Persson, C. Thelander, M. H. Magnusson, K. Deppert, L. R. Wallenberg, and L. Samuelson, "One-dimensional heterostructures in semiconductor nanowhiskers," *Appl. Phys. Lett.*, vol. 80, no. 6, pp. 1058–1060, Feb. 2002.

- [9] M. S. Gudiksen, L. J. Lauhon, J. Wang, D. C. Smith, and C. M. Lieber, "Growth of nanowire superlattice structures for nanoscale photonics and electronics," *Nature*, vol. 415, no. 6872, pp. 617–620, Feb. 2002.

- [10] T. Mårtensson, J. B. Wagner, E. Hilner, A. Mikkelsen, C. Thelander, J. Stangl, B. J. Ohlsson, A. Gustafsson, E. Lundgren, L. Samuelson, and W. Seifert, "Epitaxial growth of indium arsenide nanowires on silicon using nucleation templates formed by self-assembled organic coatings," *Adv. Mater.*, vol. 19, no. 14, pp. 1801–1806, Jul. 2007.

- [11] L.-E. Wernersson, E. Lind, L. Samuelson, T. Lowgren, and J. Ohlsson, "Nanowire field-effect transistor," *Jpn. J. Appl. Phys.*, vol. 46, no. 4b, pp. 2629–2631, Apr. 2007.

- [12] R. Chau, S. Datta, M. Doczy, B. Doyle, B. Jin, J. Kavalieros, A. Majumdar, M. Metz, and M. Radosavljevic, "Benchmarking nanotechnology for high-performance and low-power logic transistor applications," *IEEE Trans. Nanotechnol.*, vol. 4, no. 2, pp. 153–158, Mar. 2005.

- [13] Q.-T. Do, K. Blekker, I. Regolin, W. Prost, and F. J. Tegude, "High transconductance MISFET with a single InAs nanowire channel," *IEEE Electron Device Lett.*, vol. 28, no. 8, pp. 682–684, Aug. 2007.