# Vertical GaN-on-Si MOSFETs with Monolithically Integrated Freewheeling Schottky Barrier Diodes

Chao Liu, Riyaz Abdul Khadar, and Elison Matioli, Member, IEEE

Abstract—We demonstrate for the first time the monolithic integration of vertical GaN MOSFETs with freewheeling Schottky barrier diodes (SBD), based on a 6.7-µm-thick n-p-n heterostructure grown on 6-inch silicon substrates by metal organic chemical vapor deposition. The anode of the SBD is integrated in the source pad of the MOSFET and the cathode is directly connected to the MOSFET drain through the bottom n<sup>+</sup>-GaN layer, eliminating the need of any metal wire interconnection. This monolithic integration scheme offers reduced footprint, minimized parasitic components and simplified packaging. The integrated MOSFET-SBD showed enhancement-mode operation with a threshold voltage of 3.9 V, an on/off ratio of over 10<sup>8</sup> and a dramatic improvement in reverse conduction, without degradation in on-state performance from the integration of the SBD. The integrated GaN-on-Si vertical SBD exhibited excellent performance, with a specific on-resistance of 1.6 m $\Omega \cdot cm^2$ , a turn-on voltage of 0.76 V, an ideality factor of 1.5, along with a breakdown voltage of 254 V. These results reveal the promising potential of emerging GaN vertical devices for future power converters.

*Index Terms* – Gallium nitride, vertical, quasi-vertical transistors, GaN-on-Si, power, semiconductor, MOSFETs, freewheeling, SBDs, diodes.

## I. INTRODUCTION

G AN-BASED lateral and vertical devices have emerged as excellent candidates for high-efficiency power converters. While the lateral AlGaN/GaN high electron mobility transistors (HEMTs) continue to penetrate the 600 V -class medium-power electronics market, vertical GaN devices are developed for high-voltage high-current applications. In the past few years, numerous GaN vertical power transistors have been reported on freestanding GaN substrates [1-9]. However, the high cost and small available size of bulk GaN substrates could limit the widespread commercial adoption of vertical power devices on bulk GaN.

GaN-on-Si offers a cost-effective alternative for vertical GaN power devices, due to its large-scale availability, low cost, and a mature fabrication technology. Vertical GaN-on-Si P-i-N and Schottky diodes [10-18], and more recently, the first vertical transistor have been demonstrated on 6-inch Si

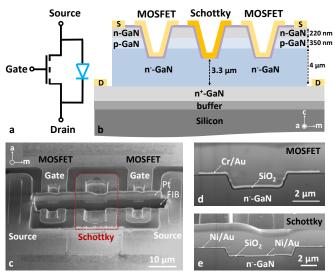

Fig. 1. (a) Equivalent circuit, (b) Schematic of integrated vertical MOSFET-Schottky barrier diode (SBD). (c) SEM image of integrated vertical MOSFET-SBD, (d) Cross-sectional SEM image of the integrated vertical MOSFET, and (e) of the integrated vertical SBD.

substrates [19]. For practical use of the emerging vertical transistors in several topologies of power converters, such as buck/boost converters, voltage-source inverters, and resonant converters, an extra freewheeling diode is required to allow a reverse flow of current during off-state [20-22]. The intrinsic body P-i-N diode embedded in GaN vertical MOSFETs could work as a freewheeling diode. However, its large turn-on voltage would increase the losses during switching events. One solution lies on the integration of a Schottky barrier diode (SBD) with the MOSFET, which would be preferable for efficient converter topologies due to its much smaller turn-on voltage, lower resistance, and faster switching properties [23]. Nevertheless, the large parasitic inductance of an externally connected SBD would result in circuit ringing and system instability due to the external wiring. A monolithic integration of these devices would be very desirable for a reduced footprint, smaller parasitic components, and simplified packaging [24]. But so far there have been no reports on GaN vertical transistors with monolithically integrated SBDs.

In this work, we demonstrate the first vertical GaN MOSFET with monolithically-integrated freewheeling SBD on 6-inch silicon substrates. The integrated MOSFET-SBD exhibited enhancement-mode (E-mode) operation with a threshold voltage ( $V_{TH}$ ) of 3.9 V, an on/off ratio of over  $10^8$ , and a drastic improvement in reverse conduction, without degradation in on-state performance of the MOSFET. The integrated SBD

This work was supported the European Research Council (ERC) under the ERC Grant Agreement 679425. The authors are with the Power and Wide-band-gap Electronics Research Laboratory (POWERlab), École Polytechnique Fédérale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland (e-mail: chao.liu@epfl.ch; elison.matioli@epfl.ch).

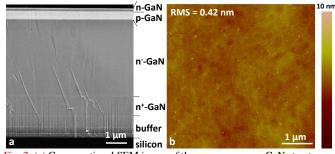

Fig. 2. (a) Cross-sectional SEM image of the as-grown n-p-n GaN structure on 6-inch silicon, (b) AFM image of the Schottky region after dry-etching to reach the n-GaN layer, followed by 25% TMAH treatment at 85 °C for 90 min.

exhibited excellent performance, with a specific on-resistance  $(R_{ON,SP})$  of 1.6 m $\Omega$ ·cm<sup>2</sup>, a turn-on voltage of 0.76 V, an ideality factor of 1.5, along with a state-of-the-art breakdown voltage of 254 V compared to vertical GaN-on-Si SBDs. These results reveal the great potential of GaN-on-Si vertical MOSFETs with integrated freewheeling SBD for power converters.

## II. DEVICE STRUCTURE AND FABRICATION

Fig. 1 (a) depicts an equivalent circuit of the monolithically integrated vertical MOSFET-SBD, along with a cross-sectional schematic presented in Fig. 1 (b). Both the integrated vertical MOSFET and SBD feature a trench structure along the a-axis of GaN. A tilted-view scanning electron microscope (SEM) image of the integrated vertical MOSFET-SBD is shown in Fig. 1 (c). The etched middle region corresponds to a cross-sectional cut by focused ion beam (FIB). It shows the anode of the SBD integrated in the source pad of the MOSFET, while the cathode is directly connected to the MOSFET drain through the bottom n<sup>+</sup>-GaN layer. As a result, the interconnection metal wires between the MOSFET and SBD could be eliminated, leading to a minimized footprint, reduced parasitic components, and enhanced switching speed. Fig. 1 (d) and (e) show the cross-sectional SEM images of the integrated MOSFET and SBD, respectively. The depth of the etched trench was 1.3 µm for both devices, which was sufficient to reach the n<sup>-</sup>-GaN drift layer. A direct contact of the Schottky metal (Ni/Au) to the n<sup>-</sup>-GaN drift layer can be observed in Fig. 1 (e), which forms the integrated vertical SBD.

The cross-sectional SEM image of the n-p-n epitaxial structure grown on 6 inch Si (111) in Fig. 2 (a) shows a total thickness of 6.7  $\mu$ m, with abrupt junction interfaces and a drift layer thickness of 4  $\mu$ m. The device fabrication started with a plasma-based dry etching process to form the trench structures for the vertical MOSFET and SBD. The samples were then treated with a 25% Tetra Methyl Ammonium Hydroxide (TMAH) solution at 85°C for 90 minutes to smooth the sidewall and bottom of the etched trenches [25]. Fig. 2 (b) reveals the very smooth surface morphology of the trench bottom after TMAH treatment, with a root-mean-square (RMS) roughness of 0.42 nm, which is crucial to achieve good Schottky contacts. More details of the epitaxial structure and fabrication process used in this work can be found in Ref. [19].

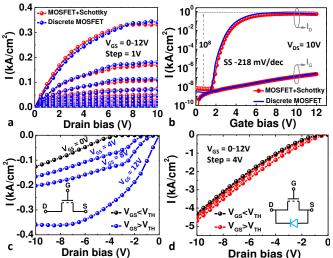

Fig. 3. (a) Output and (b) Transfer characteristics of the vertical MOSFET with/without integrated freewheeling SBD. Reverse-bias characteristics of (c) the discrete vertical MOSFET and (d) integrated vertical MOSFET-SBD.

#### **III. RESULTS AND DISCUSSION**

The output characteristics (I<sub>D</sub>-V<sub>DS</sub>) of the integrated MOSFET-SBD and discrete reference MOSFET are shown in Fig. 3 (a). Both devices presented good saturation behavior, an on-state current density of ~ 0.35 kA/cm<sup>2</sup>, and a similar  $R_{ON,SP}$ (10.1 m $\Omega$ ·cm<sup>2</sup> and 12.6 m $\Omega$ ·cm<sup>2</sup>, normalized by the trench area [26]). The difference in  $R_{ON,SP}$  is within the variation observed for devices of the same kind in this wafer. Fig. 3 (b) plots the of the characteristics  $(I_D - V_{GS})$ transfer integrated MOSFET-SBD and discrete MOSFET at  $V_{DS} = 10$  V. Both devices exhibited E-mode operation with a  $V_{TH}$  (obtained by linear extrapolation) of ~ 3.9 V, a current on/off ratio of over  $10^8$ , and a sub-threshold swing (SS) of ~ 218 mV/dec. The off-state leakage current level of the integrated MOSFET-SBD is slightly higher as compared to the discrete MOSFET. This can be attributed to the integrated SBD, which is under reverse bias during forward operation of the integrated MOSFET. Despite this, the overall leakage current level value for the integrated MOSFET-SBD was below 10<sup>-8</sup> kA/cm<sup>2</sup>, revealing a very effective current blocking from the integrated MOSFET-SBD in off state. The minor gate leakage increase, from  $6 \times 10^{-10} \text{ kA/cm}^2$  at  $V_{GS} = 0 \text{ V}$  to  $2 \times 10^{-7} \text{ kA/cm}^2$  at  $V_{GS} =$ 12 V, can be eliminated by improving the quality and conformity of gate dielectric.

Fig. 3 (c) illustrates the reverse characteristics of the discrete vertical MOSFETs. In the on-state ( $V_{GS} > V_{TH}$ ), the current flows through the MOSFET channel from source to the drain with an  $R_{ON,SP}$  of 9.5 m $\Omega$ ·cm<sup>2</sup>, comparable to that in the forward conduction. In the off-state ( $V_{GS} < V_{TH}$ ), the current in the MOSFET channel is blocked, resulting in a large  $V_{ON}$  of -3.7 V, corresponding to the built-in P-i-N diode, as well as a high resistance in the reverse current path. In this case, a voltage spike could occur during switching, causing arcing on contacts or possibly destroying transistors. The reverse characteristics of the integrated MOSFET-SBD are depicted in Fig. 3 (d). A drastically improved reverse conduction is observed in off-state ( $V_{GS} < V_{TH}$ ), thanks to the integrated anti-parallel SBD. In the reverse condition, the electrons can flow through the drift

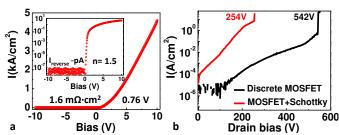

Fig. 4. (a) I-V characteristics of the integrated SBD. The inset shows semi-log scale of the I-V curves, and (b) Off-state breakdown characteristics of the integrated vertical MOSFET-SBD and of discrete MOSFET.

region via the Schottky contacts to the source, even if the channel under the MOSFET gate is pinched-off. In on-state ( $V_{GS} > V_{TH}$ ) of the integrated MOSFET, an additional current can flow through the MOSFET channels from drain to source, which explain the minor gate modulation observed and adds to the forward current of the integrated SBD.

Fig. 4 (a) shows the forward current density (normalized by the anode area) versus voltage (J-V) characteristics of the SBD. The V<sub>ON</sub>, extracted at a current density of 20 A/cm<sup>2</sup> was 0.76 V, which is among the lowest values reported in vertical GaN diodes so far [27]. The  $R_{ON,SP}$  extracted from the forward J-V plot at 8.7 V was 1.6 m $\Omega \cdot cm^2$ . The inset plots the forward current density J in logarithmic scale as a function of bias. A small ideality factor of 1.5 was extracted at a forward voltage of 0.4 V, together with an extremely low reverse current, in the range of pA. A combination of such low  $R_{ON,SP}$  and good ideality factor is a result of the excellent drift-layer quality with low defect density, high electron mobility [10], as well as excellent Schottky contact formed on the smooth n<sup>-</sup>-GaN surface subject to TMAH treatment.

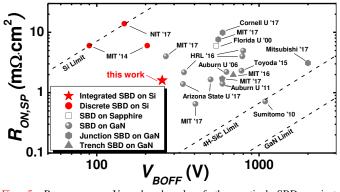

Fig. 4 (b) plots the off-state I-V characteristics measured at  $V_{GS} = 0$  V for the discrete vertical MOSFET and integrated vertical MOSFET-SBD. The discrete vertical MOSFETs exhibited a large breakdown voltage ( $V_{BR}$ ) of 542 V, while the integrated vertical MOSFET-SBD presented a  $V_{BR}$  of 254 V, which was limited by the  $V_{BR}$  of the integrated SBD. The integrated SBD in this work was benchmarked against state-of-the-art vertical SBDs on silicon, sapphire and GaN substrates in Fig. 5, revealing state-of-the-art performance compared to vertical GaN-on-Si SBDs [17], [18], [27-38]. The  $V_{BR}$  of the integrated MOSFET-SBD can be significantly improved: 1. By using low-defect-density GaN substrates [27], [29], [30]; 2. By increasing the drift layer thickness and further

Fig. 5.  $R_{\rm ON,SP}$  versus  $V_{\rm Boff}$  benchmark of the vertical SBD against state-of-the-art vertical SBDs on Si, sapphire and GaN substrates.

reducing the background carrier concentration from  $2 \times 10^{16}$  cm<sup>-3</sup> in this work to  $\sim 10^{15}$  cm<sup>-3</sup> [30], [31]; 3. By employing field plate, edge termination, and guard ring technologies [32-34]; 4. By utilizing trench or junction SBD architecture [35-39]. This excellent performance shows the great potential of GaN vertical devices for future power converters.

3

## IV. CONCLUSION

In summary, we have demonstrated the first GaN vertical MOSFETs with monolithically integrated freewheeling SBDs. The integrated GaN-on-Si MOSFET-SBD exhibited E-mode operation with a threshold voltage of 3.9 V, an on/off ratio of over  $10^8$  and a drastic improvement in reverse conduction, without degradation in on-state performance from the integration of the SBD. These results mark a major step forward for GaN-on-Si vertical transistors for cost-effective high-voltage and high-power electronic applications.

#### ACKNOWLEDGEMENT

We would like to thank Minghua Zhu, Nirmana Perera, and Armin Jafari for fruitful discussions, Dr. Kai Cheng from Enkris Semiconductor, Inc. for the collaboration on the growth of high-quality customized wafers, as well as the staff at CMi and ICMP of EPFL for technical support.

#### REFERENCES

- H. Otake, K. Chikamatsu, A. Yamaguchi, T. Fujishima, and H. Ohta, "Vertical GaN-based trench gate metal oxide semiconductor field-effect transistors on GaN bulk substrates," Appl. Phys. Exp., vol. 1, no. 1, p. 011105, Jan. 2008, doi: 10.1143/APEX.1.011105.

- [2] C. Gupta, C. Lund, S. H. Chan, A. Agarwal, J. Liu, Y. Enatsu, S. Keller and U.K. Mishra, "In-situ Oxide, GaN interlayer based vertical trench MOSFET (OG-FET) on bulk GaN substrates", IEEE Electron Device Lett., vol. 38, no. 3, pp. 353–356, Mar. 2017. doi: 10.1109/LED.2017.2649599.

- [3] M. Sun, Y. Zhang, X. Gao and T. Palacios, "High performance GaN vertical fin power transistors on bulk GaN substrate", IEEE Electron Device Lett., vol. 38, no. 4, pp. 509–512, Apr. 2017, doi: 10.1109/LED.2017.2670925.

- [4] T. Oka, T. Ina, Y. Ueno and J. Nishii, "1.8 mΩ·cm<sup>2</sup> vertical GaN-based trench metal–oxide–semiconductor field-effect transistors on a freestanding GaN substrate for 1.2-kV-class operation," Appl. Phys. Exp., vol. 8, no. 5, pp. 054101-1–054101-3, May. 2015, doi:10.7567/APEX.8.054101.

- [5] R. Li, Y. Cao, M. Chen and R. Chu, "600V/1.7Ω Normally-Off GaN Vertical Trench Metal-Oxide-Semiconductor Field-Effect Transistor", IEEE Electron Device Lett., vol. 37, no. 11, pp.1466–1469, Nov. 2016, doi: 10.1109/LED.2016.2614515.

- [6] H. Nie, Q. Diduck, B. Alvarez, A. P. Edwards, B. M. Kayes, M. Zhang, G. Ye, T. Prunty, D. Bour and I. C. Kizilyalli, "1.5-kV and 2.2-mΩ.cm<sup>2</sup> vertical GaN transistors on bulk-GaN substrates," IEEE Electron Device Lett., vol. 35, no. 9, pp. 939–941, Sep. 2014, doi: 10.1109/LED.2014.2339197.

- [7] D. Shibata, R. Kajitani, M. Ogawa, K. Tanaka, S. Tamura, T. Hatsuda, M. Ishida, and T. Ueda, "1.7 kV/1.0 mΩ·cm<sup>2</sup> normally-off vertical GaN transistor on GaN substrate with regrown p-GaN/AlGaN/GaN semipolar gate structure," in IEDM Tech. Dig., 2016, pp. 10.1.1–10.1.4, doi: 10.1109/IEDM.2016.7838385.

- [8] Y. Zhang, M. Sun, D. Piedra, J. Hu, Z. Lin, X. Cao, K. Shepard, and T. Palacios, "1200 V GaN Vertical Fin Power Field-Effect Transistors," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Dec. 2017, pp. 9.2.1 9.2.4, doi: 10.1109/IEDM.2017.8268357.

- [9] D. Ji, C. Gupta, S. H. Chan, A. Agarwal, W Li, S. Keller, U. K. Mishra, S. Chowdhury, "Demonstrating >1.4 kV OG-FET performance with a novel double field-plated geometry and the successful scaling of large-area devices," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Dec. 2017, pp. 9.4.1 9.4.4, doi: 10.1109/IEDM.2017.8268359.

- [10] R. A. Khadar, C. Liu, and E. Matioli, "820 V GaN-on-Si Quasi-Vertical PiN Diodes with BFOM of 2.0 GW/cm<sup>2</sup>," IEEE Electron Device Lett., vol. 39, no. 3, pp. 401–404, Mar. 2018, doi: 10.1109/LED.2018.2793669.

- [11] X. Zhang, X. Zou, X. Lu, C. W. Tang, and K. M. Lau, "Fully- and Quasi-Vertical GaN-on-Si p-i-n Diodes: High Performance and Comprehensive Comparison," IEEE Trans. Electron Devices, vol. 64, no. 3, pp. 809–815, Mar. 2017, doi: 10.1109/TED.2017.2647990.

- [12] X. Zou, X. Zhang, X. Lu, C. W. Tang, and K. M. Lau, "Fully Vertical GaN p-i-n Diodes Using GaN-on-Si Epilayers," IEEE Electron Device Lett., vol. 37, no. 5, pp. 636–639, May. 2016, doi: 10.1109/LED.2016.2548488.

- [13] S. Mase, Y. Urayama, T. Hamada, J. J. Freedsman, and T. Egawa, "Novel fully vertical GaN p-n diode on Si substrate grown by metalorganic chemical vapor deposition," Appl. Phys. Exp., vol. 9, no. 11, p. 111005, Nov. 2016, doi: 10.7567/APEX.9.111005.

- [14] Y. Zhang, D. Piedra, M. Sun, J. Hennig, A. Dadgar, L. Yu, and T. Palacios, "High-Performance 500 V Quasi- and Fully- Vertical GaN-on-Si pn Diodes," IEEE Electron Device Lett., vol. 38, no. 2, pp. 248–251, Feb. 2017, doi: 10.1109/LED.2016.2646669.

- [15] Y. Zhang, M. Sun, H. Wong, Y. Lin, P. Srivastava, C. Hatem, M. Azize, D. Piedra, L. Yu, T. Sumitomo, N. A. Braga, R. V. Mickevicius, T. Palacios, "Origin and Control of OFF-State Leakage Current in GaN-on-Si Vertical Diodes," IEEE Trans. Electron Devices, vol. 62, no. 7, pp. 2155–2161, Jul. 2015, doi: 10.1109/TED.2015.2426711.

- [16] Y. Zhang, M. Yuan, N. Chowdhury, K. Cheng, T. Palacios, "720-V/0.35cm Ω·cm<sup>2</sup> Fully Vertical GaN-on-Si Power Diodes by Selective Removal of Si Substrates and Buffer Layers," IEEE Electron Device Lett., vol. 39, no. 5, pp. 715–718, May. 2018, doi: 10.1109/LED.2018.2819642.

- [17] Y. Zhang, M. Sun, D. Piedra, M. Azize, X. Zhang, T. Fujishima, and T. Palacios, "GaN-on-Si Vertical Schottky and p-n Diodes," IEEE Electron Device Lett., vol. 35, no. 6, pp. 618–620, Jun. 2014, doi: 10.1109/LED.2014.2314637.

- [18] K. Zhang, S. Mase, K. Nakamura, T. Hamada and T. Egawa, "Demonstration of fully vertical GaN-on-Si Schottky diode," Electron. Lett., vol. 53, no. 24, pp. 1610-1611, Nov. 2017, doi: 10.1049/el.2017.3166.

- [19] C. Liu, R. A. Khadar, and E. Matioli, "GaN-on-Si Quasi-Vertical Power MOSFETs," IEEE Electron Device Lett., vol. 39, no. 1, pp. 71-74, Jan. 2018, doi: 10.1109/LED.2017.2779445.

- [20] H. Han, R. Tan, J. Yang, H. Wang, S. Ning, and M. Shen, "A Novel Efficient Tri-State Boost Converter," in IEEE Electrical Power and Energy Conference (EPEC), Oct. 2017, pp. 1-6, doi: 10.1109/EPEC.2017.8286197.

- [21] B. Weiss, R. Reiner, P. Waltereit, R. Quay, and O. Ambacher, "Operation of PCB-Embedded, High-Voltage Multilevel-Converter GaN-IC," in IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Oct, 2017, pp. 398-403, doi: 10.1109/WiPDA.2017.8170580.

- [22] T. Morita, S. Ujita, H. UMEDA, Y. Kinoshita, S. Tamura, Y. Anda, T. Ueda, and T. Tanaka, "GaN Gate Injection Transistor with Integrated Si Schottky Barrier Diode for Highly Efficient DC-DC Converters," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Dec. 2012, pp. 7.2.1–7.2.4, doi: 10.1109/IEDM.2012.6478996.

- [23] Y. Kobayashi, N. Ohse, T. Morimoto, M. Kato, T. Kojima, M. Miyazato, M. Takei, H. Kimura, and S. Harada, "Body PiN diode inactivation with low on-resistance achieved by a 1.2 kV-class 4H-SiC SWITCH-MOS", in Proc. IEEE Int. Electron Devices Meeting (IEDM), Dec. 2017, pp. 9.1.1– 9.1.4, doi: 10.1109/IEDM.2017.8268356.

- [24] F. Hsu, C. Yen, C. Hung, H. Hung, C. Lee, L. Lee, Y. Huang, T. Chen, P. Chuang, "High Efficiency High Reliability SiC MOSFET with Monolithically Integrated Schottky Rectifier," in Proc. 29th Int. Symp. Power Semiconductor Devices ICs (ISPSD), May. 2017, pp. 45–48, doi: 10.23919/ISPSD.2017.7988889.

- [25] M. Kodama, M. Sugimoto, E. Hayashi, N. Soejima, O. Ishiguro, M. Kanechika, K. Itoh, H. Ueda, T. Uesugi, and T. Kachi, "GaN-Based Trench Gate Metal Oxide Semiconductor Field-Effect Transistor Fabricated with Novel Wet Etching," Appl. Phys. Exp., vol. 1, no. 2, pp. 021104-1 021104-3, Feb. 2008, doi: 10.1143/APEX.1.021104.

- [26] W. Li, K. Nomoto, K. Lee, S. Islam, Z. Hu, M. Zhu, X. Gao, M. Pilla, D. Jena, and H. G. Xing, "600 V GaN vertical V-trench MOSFET with MBE regrown channel," in Proc. 75th Annu. Device Res. Conf. (DRC), Jun 2017, pp. 1–2, doi: 10.1109/DRC.2017.7999414.

- [27] Y. Cao, R. Chu, R. Li, M. Chen, R. Chang, and B. Hughes, "High-voltage vertical GaN Schottky diode enabled by low-carbon metal-organic

chemical vapor deposition growth," Appl. Phys. Lett., vol. 108, no. 6, pp. 062103-1–062103-4, Feb. 2016, doi: 10.1063/1.4941814.

- [28] G. T. Dang, A. P. Zhang, F. Ren, X. A. Cao, S. J. Pearton, H. Cho, J. Han, J. Chyi, C. M. Lee, C. C. Chuo, S. N. G. Chu, and R. G. Wilson, "High Voltage GaN Schottky Rectifiers," IEEE Trans. Electron Devices., vol. 47, no. 4, pp. 692–696, Apr. 2000, doi: 10.1109/16.830981.

- [29] Y. Saitoh, K. Sumiyoshi, M. Okada, T. Horii, T. Miyazaki, H. Shiomi, M. Ueno, K. Katayama, M. Kiyama, and T. Nakamura, "Extremely low on-resistance and high breakdown voltage observed in vertical GaN Schottky barrier diodes with high-mobility drift layers on low dislocation-density GaN substrates," Appl. Phys. Exp., vol. 3, no. 8, p. 081001, Jul. 2010, doi: 10.1143/APEX.3.081001.

- [30] H. Fu, X. Huang, H. Chen, Z. Lu, I. Baranowski, and Y. Zhao, "Ultra-low turn-on voltage and on-resistance vertical GaN-on-GaN Schottky power diodes with high mobility double drift layers," Appl. Phys. Lett., vol. 111, no. 15, pp. 152102 -1–152102 -4, Oct. 2017, doi: 10.1063/1.4993201.

- [31] Y. Cao, R. Chu, R. Li, M. Chen, and A. J. Williams, "Improved performance in vertical GaN Schottky diode assisted by AlGaN tunnelling Barrier," Appl. Phys. Lett., vol. 108, no. 11, pp. 112101-1– 112101-4, Mar. 2016, doi: 10.1063/1.4943946.

- [32] N. Tanaka, K. Hasegawa, K. Yasunishi, N. Murakami, and T. Oka, "50 A vertical GaN Schottky barrier diode on a free-standing GaN substrate with blocking voltage of 790 V," Appl. Phys. Exp., vol. 8, no. 7, p. 071001-1-071001-3, Jul. 2015, doi: 10.7567/APEX.8.071001.

- [33] Y. Zhou, D. Wang, C. Ahyi, C.-C. Tin, J. Williams, M. Park, N. M. Williams, and A. Hanser, "High breakdown voltage Schottky rectifier fabricated on bulk n-GaN substrate," Solid-State Electron., vol. 50, nos. 11–12, pp. 1744–1747, Nov. 2006, doi: 10.1016/j.sse.2006.09.009.

- [34] Y. Wang, S. Alur, Y. Sharma, F. Tong, R. Thapa, P. Gartland, T. Issacs-Smith, C. Ahyi, J. Williams, M. Park, M. Johnson, T. Paskova, E. A. Preble, and K. R. Evans, "Ultra-low leakage and high breakdown Schottky diodes fabricated on free-standing GaN substrate," Semicond. Sci. Technol., vol. 26, no. 2, p. 022002, Feb. 2011, doi: 10.1088/0268-1242/26/2/022002.

- [35] Y. Zhang, Z. Liu, M. Tadjer, M. Sun, D. Piedra, C. Hatem, T. Anderson, L. Luna, A. Nath, A. Koehler, H. Okumura, J. Hu, X. Zhang, X. Gao, B. Feigelson, K. Hobart, T. Palacios, "Vertical GaN Junction Barrier Schottky Rectifiers by Selective Ion Implantation," IEEE Electron Device Lett., vol. 38, no. 8, pp. 1097-1100, Aug. 2017, doi: 10.1109/LED.2017.2720689.

- [36] T. Hayashida, T. Nanjo, A. Furukawa, and M. Yamamuka, "Vertical GaN merged PiN Schottky diode with a breakdown voltage of 2 kV," Appl. Phys. Exp., vol. 10, no. 6, pp. 061003-1-061003-3, May. 2017, doi: 10.7567/APEX.10.061003.

- [37] W. Li, K. Nomoto, M. Pilla, M. Pan, X. Gao, D. Jena, H. Xing, "Design and Realization of GaN Trench Junction-Barrier-Schottky-Diodes," IEEE Trans. Electron Devices.,vol. 64, no. 4, pp. 1635–1641, Apr. 2017, doi: 10.1109/TED.2017.2662702.

- [38] Y. Zhang, M. Sun, Z. Liu, D. Piedra, M. Pan, X. Gao, Y. Lin, A. Zubair, L. Yu, and T. Palacios, "Novel GaN trench MIS barrier Schottky rectifiers with implanted field rings," in IEDM Tech. Dig., Dec. 2016, pp. 10.2.1–10.2.4, doi: 10.1109/IEDM.2016.7838386.

- [39] Y. Zhang, M. Sun, Z. Liu, D. Piedra, J. Hu, X. Gao, and T. Palacios, "Trench formation and corner rounding in vertical GaN power devices," Appl. Phys. Lett., vol. 110, no. 19, pp. 193506-1–193506-4, May. 2017, doi: 10.1063/1.4983558.