View-Oriented Parallel Programming and its Performance Evaluation on Multicore Architectures

Kai-Cheung Leung (梁啓昌)

a thesis submitted for the degree of Doctor of Philosophy at the University of Otago, Dunedin, New Zealand.

$17^{\text{th}}$  August, 2013

#### Abstract

Shared-memory multicore architectures have become pervasive, and there is a pressing need for parallel programming models to facilitate both performance and convenience. However, most existing shared-memory programming models are tedious for programming and are prone to errors such as data race, which are difficult to debug.

To solve this problem, this thesis proposes a data race prevention scheme in the View-Oriented Parallel Programming (VOPP) paradigm. VOPP was proposed for distributed shared memory systems. It is adapted to shared-memory multicore architectures in this thesis. VOPP is a sharedmemory data-centric parallel programming model, which uses views to bundle mutual exclusion with data access. In VOPP, programmers partition the shared memory into "views", which are non-overlapping sets of shared data objects. The data race prevention scheme proposed for VOPP can prevent data race through the memory protection mechanism while keeping the extra overhead low.

To improve the programmability of VOPP, this thesis proposes an automatic view access management scheme where a view is automatically acquired upon its first access, and automatically released when no longer needed, thus relieving programmers from arranging locks to protect critical sections.

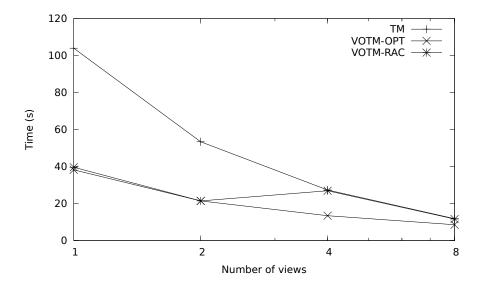

To further improve performance and programmability, this thesis proposes the View-Oriented Transactional Memory (VOTM) system, which uses Restricted Admission Control (RAC) to manage the number of processes holding each view according to its contention. In VOTM, RAC can restrict the number of processes holding the view when its contention is high, and in extreme cases, RAC can fall back to the locking mode, in order to avoid abort overheads of transactions. On the other hand, RAC allows unlimited concurrent access to other low-contention views to maximize concurrency, just as in transactional memory. Therefore, VOTM has the merits of both the locking mechanism and the transactional memory (TM) and integrated them nicely through RAC.

This thesis has also provided a theoretical analysis for RAC to investigate factors that indicate performance gain by restricting admission to a view, including disproportionately large portion of time spent in aborted transactions due to high contention and excessive TM mechanism overheads. Experimental results demonstrate that in many cases, RAC correctly responds to these situations by restricting admission to a view, thus improves the performance.

Apart from the improvements of programmability in VOPP, this thesis has done extensive experiments on two multicore architectures, a 16-core machine and a 64-core machine. Experimental results demonstrate that VOPP can provide a data race free environment with low overheads on multicore architectures, and VOTM outperforms both traditional transactional memory models and lock-based models in most benchmark applications.

### Acknowledgements

There have been many people who have helped me throughout my PhD candidature. The completion of this thesis would not have been possible without the support and guidance of Associate Professor Zhiyi Huang, my primary supervisor. Throughout my time at the Department of Computer Science, Professor Huang helped me to grow as both a researcher, and more importantly, as an all-rounded person.

I am also very grateful to Dr Yawen Chen, who analyzed works carried in this thesis with a fresh pair of eyes at the statistician's point of view, and collaborated with Professor Huang and me to develop the RAC theoretical model.

I would also like to thank Dr Richard O'Keefe (my co-supervisor), Dr David Eyers, Dr Haibo Zhang and Cameron Kerr for training my programming skills and knowledge in operating systems, which are crucial in both this thesis as well as my future career. In addition, I would like to thank my postgraduate advisors Professor Mike Atkinson and Associate Professor Alistair Knott, and our Head of Department Associate Professor Brendan McCane for their academic and career guidance.

During my time in this department, I was very fortunate to have Jason, Manish, Qihang, Ayesha, Yan, Adeel, Bhaskar, Sheetal, Faisal, Jay, Umair, Nabeel, Reece, Hamza, Lynn, Azam, Maryam, Jie, Nick and all the people at the System Lab for all the advice, fun and great time shared.

Finally, I would like to acknowledge the love and support of my friends and family, and particularly my parents while I pursued my extended education. I cannot thank you all enough.

# Contents

| 1        | $\mathbf{Intr}$ | roduction                                                          | 1               |

|----------|-----------------|--------------------------------------------------------------------|-----------------|

|          | 1.1             | Concurrency Control in Shared Memory                               | 2               |

|          |                 | 1.1.1 Locking                                                      | 3               |

|          |                 | 1.1.2 Transactional Memory                                         | 4               |

|          | 1.2             | Motivation                                                         | 5               |

|          | 1.3             | Contributions of this Thesis                                       | 6               |

|          | 1.4             | Thesis Structure                                                   | 8               |

| <b>2</b> | Tan             | ning the Data Race                                                 | 9               |

|          | 2.1             | Data Race Prevention                                               | 10              |

|          |                 | 2.1.1 Implementation                                               | 12              |

|          | 2.2             | Performance Evaluation with Other Models                           | 14              |

|          |                 | 2.2.1 Experimental Results                                         | 16              |

|          |                 | 2.2.2 Discussion                                                   | 20              |

|          | 2.3             | Advanced Features in Maotai 2.0                                    | 22              |

|          |                 | 2.3.1 Deadlock Avoidance                                           | 22              |

|          |                 | 2.3.2 Producer/Consumer View                                       | 23              |

|          |                 | 2.3.3 System Queues                                                | 25              |

|          | 2.4             | Concluding Remarks                                                 | 25              |

| 3        | Δ 11†           | tomatic Detection of View Access                                   | 26              |

| J        | 3.1             | The Programming Model and Implementation Details                   | 27              |

|          | 0.1             | 3.1.1 Automatic Detection of View Access                           | $\frac{21}{28}$ |

|          |                 | 3.1.2 View Scope Construct                                         | $\frac{20}{31}$ |

|          |                 | 3.1.3 Deadlock Free Mode                                           | 34              |

|          |                 | 3.1.4 The Maotai 3.0 API                                           | 36              |

|          |                 | 3.1.5 Implementation Details and Overheads                         | 37              |

|          | 3.2             | Programmability of Maotai 3.0 and Transactional Memory Models      | 39              |

|          | 3.3             | Performance Evaluation and Discussion                              | 43              |

|          |                 | 3.3.1 Maotai 3.0 Outperforms TL-2 in High-Contention Cases TSP,    |                 |

|          |                 | LL and BT                                                          | 43              |

|          |                 | 3.3.2 PNN - Multiple Iteration Algorithm Updating a Shared Array . | 45              |

|          |                 | 3.3.3 Barnes-Hut, Raytrace and Mergesort - Low to Moderate Con-    |                 |

|          |                 | tention Cases Shows Very Little Overhead in Maotai 3.0 Auto-       |                 |

|          |                 | matic View Access Detection                                        | 46              |

|          | 3.4             | Concluding Remarks                                                 | 48              |

| 4            | Vie            | w-Oriented Transactional Memory                                   | 50  |

|--------------|----------------|-------------------------------------------------------------------|-----|

|              | 4.1            | The VOTM Programming Model                                        | 51  |

|              |                | 4.1.1 The VOTM Programming Interface                              | 51  |

|              |                | 4.1.2 Restricted Admission Control (RAC) Scheme                   | 54  |

|              |                | 4.1.3 Origin of Performance Gain in VOTM                          | 56  |

|              | 4.2            | Overview of Transactional Memory Algorithms                       | 57  |

|              |                | 4.2.1 The TinySTM Algorithm                                       | 59  |

|              |                | 4.2.2 NOrec                                                       | 64  |

|              | 4.3            | Implementation                                                    | 68  |

|              | 4.4            | Performance Evaluation                                            | 69  |

|              |                | 4.4.1 How RAC Improves Performance                                | 73  |

|              |                | 4.4.2 View Partitioning Improves Performance                      | 75  |

|              | 4.5            | Concluding Remarks                                                | 76  |

| <b>5</b>     | Imr            | provements on the RAC Algorithm                                   | 79  |

|              | 5.1            | The Restricted Admission Control Theoretical Model                | 80  |

|              | 5.2            | Implementation                                                    | 84  |

|              | 5.3            | Experimental Design                                               | 85  |

|              |                | 5.3.1 Eigenbench                                                  | 86  |

|              |                | 5.3.2 MultiRBTree                                                 | 89  |

|              | 5.4            | Experimental Results                                              | 89  |

|              | 0.1            | 5.4.1 Performance of VOTM-OrecEagerRedo                           | 89  |

|              |                | 5.4.2 Performance of VOTM-NOrec                                   | 91  |

|              | 5.5            | Refinements on the RAC Model                                      | 93  |

|              | 5.6            | Experimental Results of the Refined RAC Model                     | 95  |

|              | 0.0            | 5.6.1 Performance of VOTM-OrecEagerRedo                           | 95  |

|              |                | 5.6.2 Performance of NOrec                                        | 100 |

|              | 5.7            | Concluding Remarks                                                | 100 |

|              |                |                                                                   |     |

| 6            | Rel            | ated Work                                                         | 107 |

|              | 6.1            | Programming Models                                                | 107 |

|              |                | 6.1.1 Deterministic Parallel Java                                 | 107 |

|              |                | 6.1.2 Colorama                                                    | 112 |

|              |                | 6.1.3 Dthreads                                                    | 113 |

|              | 6.2            | Concurrency Control Models in Modern Transactional Memory Systems | 114 |

|              |                | 6.2.1 In-Transactional Conflict Resolution                        | 114 |

|              |                | 6.2.2 Transactional Scheduling                                    | 114 |

|              |                | 6.2.3 Adaptive Locks                                              | 115 |

|              |                | 6.2.4 Adaptive Transactional Memory                               | 116 |

|              | 6.3            | Non-Blocking Algorithms                                           | 116 |

| 7            | Con            | clusions and Future Work                                          | 119 |

|              | $\mathbf{Ref}$ | erences                                                           | 123 |

| $\mathbf{A}$ | Cor            | atents of the Source Code CD-ROM                                  | 134 |

|              |                |                                                                   |     |

# List of Tables

| 2.1  | Breakdown of view primitive costs (in $\mu s$ )                                                                                          | 13  |

|------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2  | Effects of memory protection on benchmark application speedups with                                                                      |     |

|      | $32 \text{ processes} \dots \dots$ | 13  |

| 2.3  | Requested vs actual VOPP shared size (in Kbytes) in different applications                                                               | 14  |

| 2.4  | Combined startup and finalization time (in $ms$ ) for different number of                                                                |     |

|      | processes/threads on a Sun T2000 server                                                                                                  | 19  |

| 3.1  | Breakdown of view primitive costs (in $\mu s$ )                                                                                          | 38  |

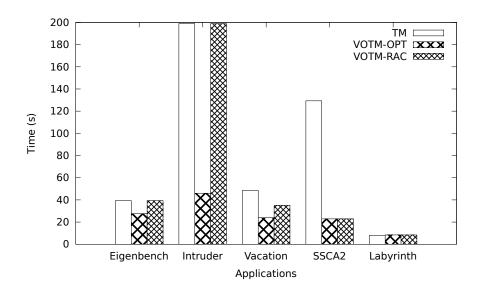

| 4.1  | Application runtime (s) at $N = 16$                                                                                                      | 71  |

| 4.2  | Number of transactions and aborts at $N = 16$                                                                                            | 71  |

| 4.3  | Performance of TSP at $N = 16$                                                                                                           | 72  |

| 4.4  | Overhead of transactions with different sizes                                                                                            | 73  |

| 4.5  | Runtime and number of aborts of Bayes at different $Q$                                                                                   | 74  |

| 4.6  | Performance of VOTM and TinySTM + RAC at $N = 16 \dots \dots \dots$                                                                      | 76  |

| 5.1  | Eigenbench parameters for the 2-view version                                                                                             | 87  |

| 5.2  | Single-view applications with VOTM-OrecEagerRedo                                                                                         | 90  |

| 5.3  | Single-view applications in VOTM-NOrec                                                                                                   | 92  |

| 5.4  | Single-view applications with VOTM-OrecEagerRedo                                                                                         | 96  |

| 5.5  | Eigenbench in VOTM-OrecEagerRedo                                                                                                         | 98  |

| 5.6  | Intruder with VOTM-OrecEagerRedo                                                                                                         | 98  |

| 5.7  |                                                                                                                                          | 100 |

| 5.8  | Single-view applications in VOTM-NOrec                                                                                                   | 101 |

| 5.9  |                                                                                                                                          | 103 |

| 5.10 | Intruder with VOTM-NOrec                                                                                                                 | 103 |

| 5.11 | MultiRBTree in VOTM-NOrec (In all RAC cases, all views settled to                                                                        |     |

|      | the same $Q$ )                                                                                                                           | 104 |

# List of Figures

| 1.1  | Code snippet demonstrating data race bug in two non-atomic operations not protected by a critical section         | 3  |

|------|-------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Code snippet demonstrating a deadlock situation resulting from pro-<br>cesses acquiring locks in different orders | 4  |

| 2.1  | An example of VOPP code                                                                                           | 11 |

| 2.2  | Speedup of SOR                                                                                                    | 16 |

| 2.3  | Speedup of GE                                                                                                     | 17 |

| 2.4  | Speedup of IS                                                                                                     | 17 |

| 2.5  | Speedup of NN                                                                                                     | 18 |

| 2.6  | Speedup of Mandelbrot                                                                                             | 18 |

| 2.7  | Speedup of Mergesort                                                                                              | 19 |

| 2.8  | Code snippet showing how multiple views are acquired together in VOPP                                             | 22 |

| 2.9  | Speedup of SOR in VOPP                                                                                            | 24 |

| 2.10 | Speedup of GE in VOPP                                                                                             | 24 |

| 3.1  | Code snippets comparing serial and Maotai 2.0 implementations of the list traversal function                      | 26 |

| 3.2  | A simple example illustrating when a view is automatically acquired<br>and released under Maotai 3.0              | 28 |

| 3.3  | List traversal in Maotai 3.0                                                                                      | 29 |

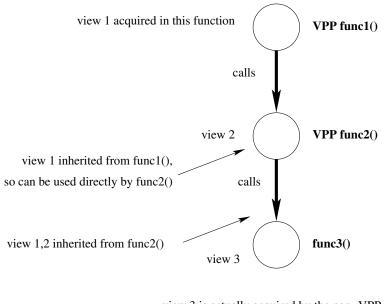

| 3.4  | Code snippet illustrating the inheritance of views acquired by VPP func-<br>tions                                 | 30 |

| 3.5  | Inheritance of views acquired by VPP functions                                                                    | 31 |

| 3.6  | An example illustrating how views acquired by a callee function can be<br>unwittingly released                    | 32 |

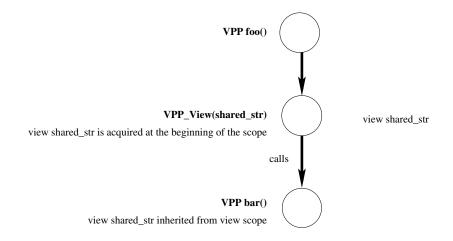

| 3.7  | A code snippet illustrating the use of a view scope to specify when a                                             |    |

|      | view is acquired and released                                                                                     | 33 |

| 3.8  | Inheritance of views acquired by VPP functions and view scopes                                                    | 34 |

| 3.9  | A deadlock between two processes accessing views in different orders .                                            | 35 |

| 3.10 | List traversal in Maotai 2.0                                                                                      | 40 |

| 3.11 | List traversal in Maotai 3.0                                                                                      | 41 |

| 3.12 | List traversal in TM                                                                                              | 42 |

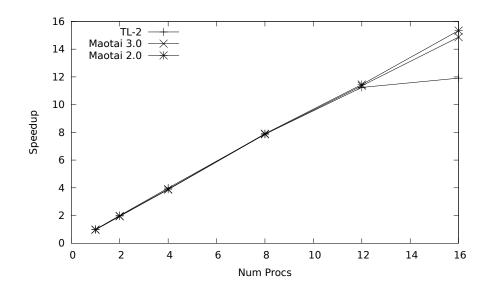

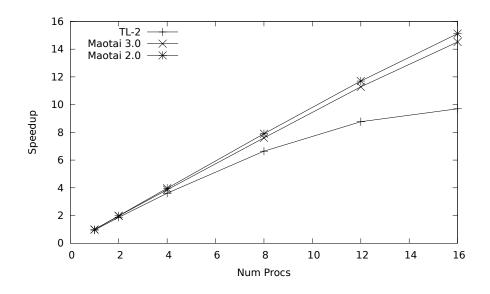

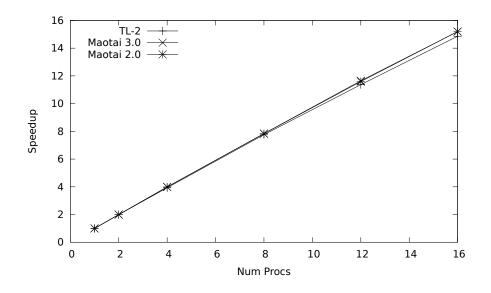

| 3.13 | Speedup of TSP                                                                                                    | 44 |

| 3.14 | Speedup of LL                                                                                                     | 45 |

|      | Speedup of BT                                                                                                     | 46 |

| 3.16 | Speedup of PNN                                                                                                    | 47 |

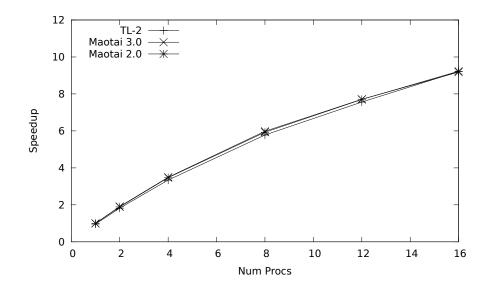

| 3.17 | Speedup of Barnes-Hut                                                                  | 47  |

|------|----------------------------------------------------------------------------------------|-----|

| 3.18 | Speedup of Raytrace                                                                    | 48  |

|      | Speedup of Mergesort                                                                   | 49  |

| 4.1  | Code snippet of list initialization in VOTM                                            | 52  |

| 4.2  | Code snippet of list insertion in VOTM                                                 | 53  |

| 4.3  | Transactions T1 and T2 livelock in ETL                                                 | 58  |

| 4.4  | Time wasted by ultimately-doomed transactions in CTL                                   | 59  |

| 4.5  | TinySTM metadata                                                                       | 60  |

| 4.6  | TinySTM TxStart() pseudocode                                                           | 60  |

| 4.7  | TinySTM TxWrite() pseudocode                                                           | 61  |

| 4.8  | TinySTM TxRead() pseudocode                                                            | 62  |

| 4.9  | TinySTM TxCommit() pseudocode                                                          | 63  |

| 4.10 | TinySTM TxAbort() pseudocode                                                           | 63  |

|      | Pseudocode of the read-set validation algorithm of TinySTM                             | 64  |

| 4.12 | NOrec metadata                                                                         | 64  |

| 4.13 | NOrec TxBegin() pseudocode                                                             | 64  |

|      | NOrec TxWrite() pseudocode                                                             | 65  |

| 4.15 | NOrec TxRead() pseudocode                                                              | 66  |

|      | NOrec TxCommit() pseudocode                                                            | 67  |

|      | NOrec TxAbort() pseudocode                                                             | 67  |

| 4.18 | Pseudocode of the read-set validation algorithm of NOrec                               | 68  |

| 4.19 | RAC implementation over TinySTM                                                        | 75  |

| 5.1  | Pseudocode of the modified Eigenbench application $\ldots \ldots \ldots \ldots$        | 88  |

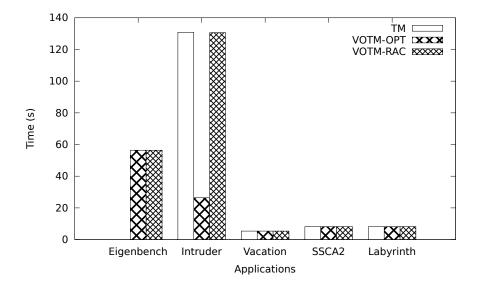

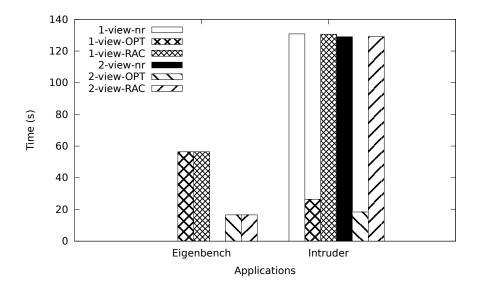

| 5.2  | Single-view applications in VOTM-OrecEagerRedo                                         | 90  |

| 5.3  | Single-view applications in VOTM-NOrec                                                 | 91  |

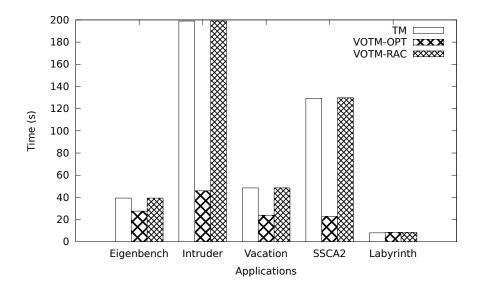

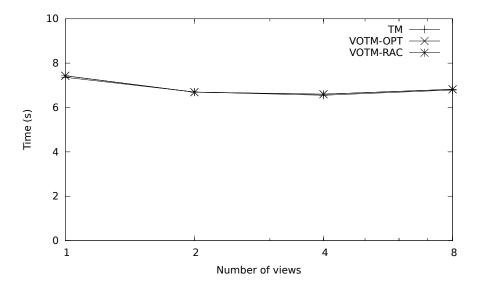

| 5.4  | TM mechanism overhead of Vacation in VOTM-NOrec                                        | 94  |

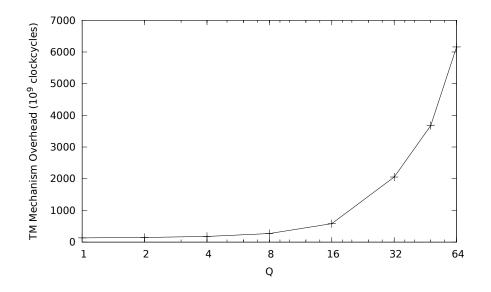

| 5.5  | Single-view applications in VOTM-OrecEagerRedo                                         | 96  |

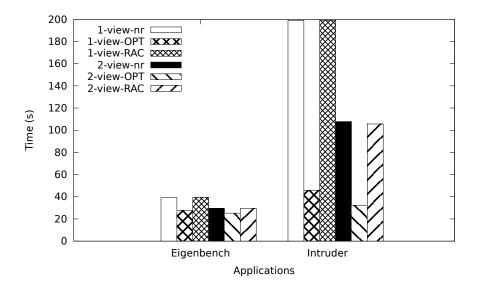

| 5.6  | Two-view applications on VOTM-OrecEagerRedo                                            | 97  |

| 5.7  | MultiRBTree in VOTM-OrecEagerRedo                                                      | 99  |

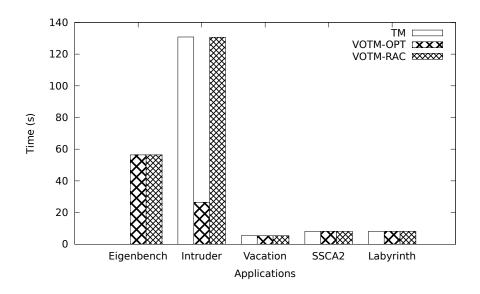

| 5.8  | Single-view applications in VOTM-NOrec                                                 | 101 |

| 5.9  | Two-view applications in VOTM-NOrec                                                    | 102 |

| 5.10 | MultiRBTree in VOTM-NOrec                                                              | 104 |

| 6.1  | Code snippet of a concurrent Pair class in DPJ [11]                                    | 108 |

| 6.2  | Code snippet of a concurrent binary search tree in DPJ using the region path list [11] | 109 |

| 6.3  | Code snippet showing two tasks executed concurrently in a cobegin_nd                   | 100 |

| 0.0  | block in DPJ                                                                           | 111 |

| 6.4  | Automatic critical section inference in Colorama                                       | 112 |

## List of Publications

Part of this manuscript have already appeared as:

### Journal Papers

- 1. Huang, Z. and Leung, K. Performance Evaluation of View-Oriented Transactional Memory. To appear in *Parallel Computing*.

- Leung, K., Chen, Y., and Huang, Z. (2013). Restricted Admission Control in View-Oriented Transactional Memory. *The Journal of Supercomputing*, 63(2), 348–366.

- Leung, K., Huang, Z., Huang Q., and Werstein, P. (2010). Data Race: Tame the Beast. The Journal of Supercomputing, 51(3), 258–278.

#### **Conference** Papers

- Leung, K., Chen, Y., and Huang, Z. (2012). When and how VOTM can improve performance in contention situations. In *The Fifth International Workshop on Parallel Programming Models and Systems Software for High-end Computing, in Proceedings of the 41st International Conference on Parallel Processing.*

- Leung, K. and Huang, Z. (2011). View-Oriented Transactional Memory. In The Fourth International Workshop on Parallel Programming Models and Systems Software for High-end Computing, in Proceedings of the 40th International Conference on Parallel Processing.

- Leung, K. and Huang, Z. (2010). Maotai 3.0: Automatic Detection of View Access in VOPP. In Proceedings of the 11th International Conference on Parallel and Distributed Computing, Applications and Technologies.

- 4. Mair, J., Leung, K., and Huang, Z. (2010). Metrics and task scheduling policies for energy saving in multicore computers. In *Proceedings of the 2010 11th*

IEEE/ACM International Conference on Grid Computing, Brussels, Belgium, October 25–29, 2010, 266–273. IEEE.

Leung, K., Huang, Z., Huang, Q., and Werstein, P. (2009). Maotai 2.0: Data Race Prevention in View-Oriented Parallel Programming. In Proceedings of the 10th International Conference on Parallel and Distributed Computing, Applications and Technologies, 263–271. IEEE Computer Society.

## Chapter 1

## Introduction

Parallel programming has become pervasive with the advent of multicore and chipmultithreading (CMT) technologies [57, 90]. These technologies allow multiple processors to be packed into a chip, and multiple multicore chips often share memory and cache. Apart from servers and workstations, multicore CPUs also become prevalent in consumer devices, including laptops as well as mobile devices such as tablets and smartphones [87]. However, to utilize the benefits of multicore architectures, there is a pressing need for parallel programming models to facilitate both performance and convenience.

Currently, there are two camps of parallel programming models – message passing and shared memory. In the message passing paradigm, memory is private to each process, and processes share data by sending and receiving messages. Examples of this paradigm include PVM [36], MPI [3], Occam [16] and the Akka Framework [42] as well as modern agent-oriented models such as Erlang [4] and Charm++ [55].

Message passing is an efficient means of communication between different computing nodes in distributed environments such as cluster and grid where memory is not physically shared across computers. It allows programmers to finely tune the algorithm using the low-level message passing mechanism. Since there are no shared variables between processes, message passing models are data race free. However, models like MPI force the communication mechanism into the application algorithm, which makes data sharing tedious due to message passing, especially when the number of processes becomes large. Since programmers are forced to manually code the interprocess communication protocol, errors in the communication protocol can easily lead to *communication deadlock*, which can be difficult to debug [54, 68].

On the other hand, message passing is not the most efficient way for data sharing

in multicore architectures with shared memory. In these increasingly prevalent architectures, message passing between processes residing on the same multicore machine results in unnecessary memory copying, which can be eliminated when shared memory is used for communication in the multicore architectures [108].

Due to these reasons, the scope of this thesis will focus on the issues such as data race and concurrency control in shared memory parallel programming models which share data directly through physical memory of the multicore architectures.

## 1.1 Concurrency Control in Shared Memory

In shared memory programming models, variables could be shared among processes. However if multiple processes access a variable at the same time, and at least one of the processes writes to the variable, such a so-called data race condition can incur unexpected results [47].

For example, although incrementation is only a single statement:

#### x++;

If two processes increment the variable  $\times$  concurrently, programmers would expect that at the end,  $\times$  would be incremented by 2. However, the incrementation is not atomic. It is in fact carried out by the following three instructions:

load x R; add 1 R; store R x;

Since the two processes increment the variable x concurrently, the above instructions from the two processes may interleave in an order as shown in Figure 1.1, where P2 reads x into its register R, before P1 updates x. However, after P1 updates x, the register R of P2 still has the *old value* of x as 0, which it increments. When P2 writes its R to x, it tramples the result calculated by P1, which results in a data race bug. The final result of x is 1 in this scenario, rather than the expected 2.

| x = 0;     |            |                                |

|------------|------------|--------------------------------|

| P1         | P2         |                                |

| load x R;  |            | // P1's register $R = 0 = 0$   |

|            | load x R;  | // P2's register $R = 0 = 0$   |

| add 1 R;   |            | // P1's register $R = 1 x = 0$ |

| store R x; |            | // x = P1's register R (= 1)   |

|            | add 1 R;   | // P2's register R = 1 $x = 1$ |

|            | store R x; | // x = P2's register R (= 1)   |

Figure 1.1: Code snippet demonstrating data race bug in two nonatomic operations not protected by a critical section

The Sequential Consistency (SC) model requires that "the result of any execution is the same as if the operations of all the processes were executed in some (global) sequential order, and the operations of each individual process appear in this sequence in the order determined by its (own) program" [60]. In the above case, "x++;" is supposed to be an atomic operation, and SC requires that the effect of the parallel execution be consistent with the result of a sequential execution of all operations. If the operations of "x++;" were to be executed sequentially, the result of Figure 1.1 would be 2 regardless of which incrementation is executed first.

To guarantee the sequential order of the operations on the same variable or data object, a critical section (also known as "atomic section" in transactional memory models to be described shortly) is needed to make sure an operation be performed atomically. The size of a critical section can range from a single statement, as in the above example, to a large code block that may take a significant portion of program execution time.

To implement the critical sections and guarantee their atomicity, traditionally there are two approaches: locking and transactional memory (TM).

## 1.1.1 Locking

Traditionally locking [59, 77] is used for concurrency control, where multiple processes <sup>1</sup> have to access a shared data object in an exclusive way. Locking is used in many shared memory programming models, including Java [37], C# [38], Python [93], Ruby [98], Scala [73, 91], Pthreads [72], Ada [17], Cilk [96], as well as modern partitioned global address space (PGAS) models such as UPC [30] and Chapel [21]. Atomic

<sup>&</sup>lt;sup>1</sup>In the rest of the thesis, we use "process" to mean both process and thread for simplicity since they are identical in terms of concurrency control.

access to a shared object is achieved through a locking mechanism. This lock-based concurrency control is generally regarded as a pessimistic approach [97] where conflicts are prevented before they are allowed to happen. Even though locking is an effective mutual exclusive mechanism for concurrency control, it could result in the deadlock problem if multiple objects are locked in different orders by multiple processes, as shown in Figure 1.2.

```

P1

P2

acquire_lock(1);

acquire_lock(2);

acquire_lock(2);

acquire_lock(1);

/* here P1 holding lock 1 waits for lock 2

which is held by P2, but P2 will not

release lock 2 until it gets lock 1

----> DEADLOCK */

. . . . .

. . . . . .

release_lock(2);

release_lock(1);

release_lock(1);

release_lock(2);

```

Figure 1.2: Code snippet demonstrating a deadlock situation resulting from processes acquiring locks in different orders

Moreover, apart from the deadlock problem, fine-grained locks are often tedious for programming, while coarse-grained locks often suffer from poor performance due to lack of concurrency, especially when a large portion of program execution is spent in critical sections. For example, the Ruppert's Algorithm [85] has a central lock that protects a critical section which takes most of the execution time of the program. A total redesign of the algorithm would be required to break the central lock into multiple fine-grained locks to extract concurrency, which would require expert knowledge in parallel programming.

In addition, when a lock is acquired very frequently, which is common in applications with fine-grained locks, the lock itself can become a cache contention hotspot, especially on hardware with a large number of cores. This locking hotspot can severely impact the performance and scalability of an application [47].

## 1.1.2 Transactional Memory

To avoid the deadlock problem as well as to increase concurrency, Transactional Memory (TM) [46, 66] was proposed for shared-memory programming. In TM, atomic

access to shared objects is achieved through transactions. All processes can freely enter a transaction, access the shared objects, and commit the accesses at the end of the transaction. If there are conflicts of access among processes, one or more transactions will be aborted and rolled back. TM will undo the effects of the rolled-back transactions and restart them from the beginning. This transaction based concurrency control is labelled as an optimistic approach [9, 58] where it is assumed nothing will go wrong, and if it does go wrong deal with it later.

In terms of performance, both lock-based and TM-based approaches have their own merits in different situations. When access conflicts are rare, the TM-based approach has little roll-back overhead and encourages high concurrency since multiple processes can access different parts of the shared data simultaneously. In this situation, however, the lock-based approach has little concurrency due to the sequential access to the shared data, which results in low performance. To increase concurrency and performance, the programmer has to break the shared data into finer parts and use a different lock for each part. This solution using fine-grained locks often complicates the already-complex parallel programs and could incur deadlocks.

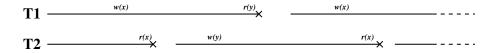

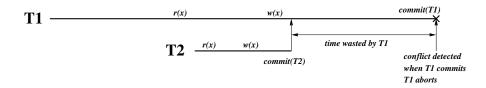

On the other hand, when access conflicts are frequent, the TM-based approach could have staggering roll-back overheads and is not scalable due to a large number of aborts of transactions. In the worst case, transactions can abort each other, and result in livelocks [19, 63, 99]. In such a situation, it is more effective to use the pessimistic lock-based approach to avoid the excessive operational overheads of transactions.

## 1.2 Motivation

This thesis investigates the issues of data race and concurrency control under the View-Oriented Parallel Programming (VOPP) paradigm [49, 52, 108].

VOPP is a novel data-centric model that bundles mutual exclusion and data access together. In VOPP, shared data is partitioned into non-overlapping *views*. The grain (size) and content of a view are decided by the programmer as part of the programming task, which is as easy as declaring a shared data structure or allocating a block of memory space. Each view can be dynamically created, merged, and destroyed. The most important property for views is that they do not intersect with each other. Before a view is accessed (read or written), it must be acquired; after the access of a view, it must be released. In this way, programmers only need to consider which data needed to access atomically, acquire the view as needed and leave the underlying system to control the concurrency and grant access to the view.

Data-centric models like VOPP are safer for parallel programming. Traditionally concurrency control in parallel programming is code-centric, where lock primitives are used to demarcate critical code sections. Mistakes in the demarcation of critical sections using locks can result in problems like data race. In contrast, data-centric models [20] are only concerned with which shared object is used and thus lock it when it is being used. Since the shared object to be locked is known, the locking process could be done automatically by the underlying system.

For instance, since VOPP has the information of the views such as size and location, it becomes possible to automatically detect accesses to them. In this way, the programmability of VOPP can be improved. For example, a view can be automatically acquired upon its first access, and later released when the control flow of the execution leaves the scope of the view acquisition. This kind of extension of VOPP would relieve programmers from manually acquiring/releasing the views, and avoid mistakes such as missing acquiring/releasing primitives in the program and their related issues such as data race and deadlock.

Moreover, since access control of each view is independent from each other, it also becomes possible to individually control access of each view according to its own contention to maximize the performance. For example, if a view has very high contention, it can switch to the locking mode and only allow one process accessing it to stem the contention overhead, while another view with low contention can allow concurrent access by multiple processes without limitations, like traditional TM models, to maximize concurrency.

This thesis will build upon the VOPP paradigm to investigate its strengths and issues as a data-centric model, such as data race freedom, concurrency control, and performance evaluation on multicore architectures.

## **1.3** Contributions of this Thesis

The VOPP paradigm was originally proposed for distributed shared memory systems [50–52]. Its features as a data-centric model have never been explored on sharedmemory multicore architectures.

This thesis first proposes a data race prevention scheme for VOPP, which can prevent data race from occurring in the first place. The efficiency of the scheme is evaluated experimentally against other parallel programming models. A shared-memory parallel programming system, called Maotai 2.0, is implemented for VOPP on multicore architectures. Maotai 2.0 has enhanced VOPP with advanced features such as deadlock avoidance and producer/consumer view.

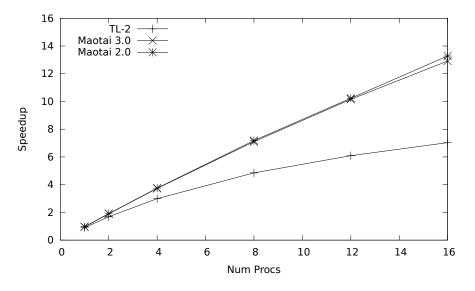

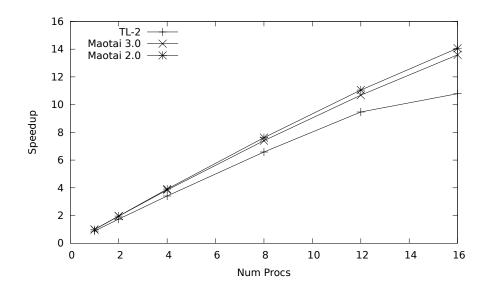

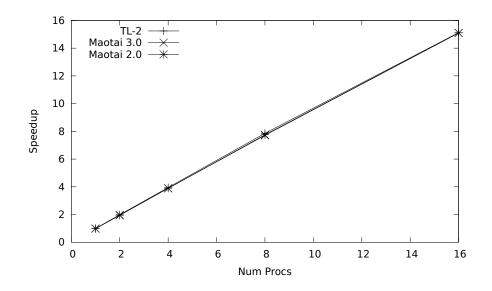

To further improve the programmability of VOPP, this thesis proposes and implements a scheme for automatic detection of view access, which no longer requires programmers to use explicit view acquire/release primitives. A view is automatically acquired when it is first accessed and released when the execution flow leaves the scope of the view acquisition. The thesis shows the automatic detection scheme improves the programming convenience of VOPP, and its programmability is similar to transactional memory models in many cases. The parallel programming system with automatic view detection is implemented and codenamed Maotai 3.0. Performance results show that Maotai 3.0 has superior performance over transactional memory models like TL-2 0.9.6 [26].

Then this thesis proposes a novel View-Oriented Transactional Memory (VOTM) paradigm that seamlessly integrates the merits of locking and TM into the same programming model. VOTM is designed based on the generic principle of VOPP. This data-centric model bundles concurrency control and data access together and therefore relieves the programmer from controlling concurrent data access directly with either locks or transactions. When a shared object (i.e. a view) is to be accessed, the programmer just simply uses **acquire\_view** to inform the system that the corresponding view is going to be accessed. It is up to the system to decide whether the locking mechanism should be adopted or a transaction should be started for the concurrent access of the shared data.

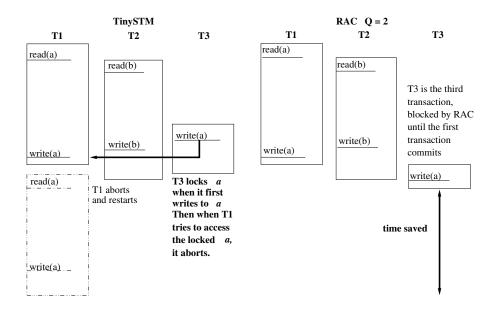

This thesis also proposes an original Restricted Admission Control (RAC) scheme for VOTM that can dynamically adjust the number of processes allowed to access the same view. With the RAC scheme, a view in VOTM is restricted to be accessed by a limited number of processes Q (called admission quota) whose value ranges from 1 to the maximum number of processes (N). If Q is 1, the processes access the set of data objects sequentially as in the lock-based approach. If Q equals N, the RAC scheme behaves like the conventional TM systems where any process is allowed to start a transaction to access the data objects of the view. However, if Q is greater than 1 but smaller than N, only Q processes are allowed to access the data objects concurrently through transactions. If there are already Q processes accessing the data objects inside uncommitted transactions, other processes are excluded from accessing the set of data objects and have to wait until some existing transactions commit. In addition, RAC can flexibly adjust Q at runtime according to the contention situation, e.g., the number of transactional aborts, to achieve optimal performance. This thesis proposes a theoretical model for RAC to measure the contention levels and decide when Q should be adjusted to achieve optimal performance for TM applications. As far as we know, this is the first time that a theoretical analysis is applied to model admission control of transactions. The RAC model is evaluated with microbenchmarks and show the model can correctly decide if Q should be adjusted at various contention levels. The experiment shows that this theoretical model is general enough to help measure the contentions for various TM systems.

## 1.4 Thesis Structure

The rest of the thesis is organized as follows.

Chapter 2 presents the data race prevention scheme for VOPP. The scheme is implemented using the memory protection mechanism (mprotect()) to guard against improper access of shared data. Experimental evaluation is carried out to show the performance of the scheme and its limitations.

Chapter 3 extends the VOPP paradigm with automatic view access semantics to further improve programmability. It also provides an experimental evaluation on the performance and programmability of this scheme.

Chapter 4 discusses the novel VOTM system, and presents a performance evaluation on VOTM, lock-based, and TM-based systems. It also gives an analysis on the benefits of VOTM over both lock-based and TM-based models.

Chapter 5 provides a theoretical analysis of the RAC algorithm used for concurrency control in VOTM. It gives discussion on how the contention among transactions should be modelled, in order to restrict the number of processes concurrently accessing the same view by setting the proper admission quota to the optimal value.

Chapter 6 discusses related work on other data-centric programming models and concurrency control mechanisms.

Finally, Chapter 7 concludes the thesis and sheds light on potential future work.

## Chapter 2

## Taming the Data Race

As mentioned in Introduction, data race is an important problem in shared memory programming models. A software bug caused by data race is often called *Heisenbug* [75] because it often disappears when one attempts to find it. There have been many studies on debugging data races. Some perform a post-mortem analysis based on program execution traces [22, 31, 44, 70, 71], while others perform on-the-fly analysis during program execution [8, 28, 69, 88]. Among modern shared-memory parallel programming models [23, 72, 74, 80], only Cilk++ [23] provides a data race detector called Cilkscreen [8, 23, 56].

Even though race detectors can help debug some data races, they often have the following problems:

- Race detectors are often expensive to run, both in terms of computation and memory space. For example, Cilkscreen can take up to 30 times the normal execution time of the debugged program to run and the memory footprint can be "several times" the memory footprint of the original application [23].

- Race detectors can only detect data races for one given input of a program. If data races do not occur when the program is run with a given input, this does not imply the program is data race free. The reason is that a different input may result in threads being executed in different order, and the resultant interaction may cause data races.

- To a novice programmer, race detectors can be difficult to use. For example, Cilkscreen gives a detailed trace of memory addresses and their associated function names and line numbers, which can be very scary and confusing to inexperienced programmers. In addition, this trace is of little help to programmers about

the dynamic nature of the data races, e.g. when and how the data races happen.

Instead of data race detection, this chapter proposes a data race prevention scheme in VOPP, which can prevent data races from occurring in the first place. It also presents an implementation of VOPP, Maotai 2.0, with a data race prevention scheme on multicore architectures.

The rest of this chapter is organized as follows: Section 2.1 describes a data race prevention scheme that can eliminate data races in VOPP. Section 2.2 presents the performance evaluation of Maotai 2.0 against other lock-based models including Cilk, OpenMP and Pthreads. Section 2.3 briefly introduces the advanced features of Maotai 2.0 for improving programmability and performance. Finally, Section 2.4 concludes this chapter.

## 2.1 Data Race Prevention

In VOPP, shared data is defined through views. Unlike most shared memory parallel programming models, variables are private to a process by default in VOPP. Shared objects must be *explicitly* defined as "views".

Views can be created, destroyed, merged, or resized, but a process must acquire a view (read-only or read-write) before accessing it and must release it after finishing with the view. The current VOPP implementation adopts the Single-Writer Multiple-Reader (SWMR) as its concurrency control model. At any given time, a view can either be read/written by one process or allow read-only access to multiple processes. In the current implementation, a view uses a contiguous memory space to store shared variables. Below is a simple example of VOPP in C.

Figure 2.1: An example of VOPP code

As illustrated in Figure 2.1, if a data structure should be shared by multiple processes, a view has to be created for it with Vpp\_alloc\_view. For exclusive access to the view, the view type is SWV, which means "Single Writer View". However, VOPP also provides other advanced views to enhance the programmability and flexibility (refer to Section 2.3).

If a process wants access to a view, the view must be acquired with Vpp\_acquire\_view (or Vpp\_acquire\_Rview for read-only access). The view must be released with Vpp\_release\_view after accessing it.

A summary of the VOPP API is shown below:

### int Vpp\_alloc\_view(int vid, size\_t size, view\_type type)

Creates a view with ID vid, and size size. If vid is a negative value, the system will allocate a free view ID. The view type type can be SWV (single writer view), MWV (multiple-writer view) or PCV (producer-consumer view). MWV and PCV will be discussed in detail in Section 2.3. This function will return the view ID of the allocated view. On failure, this function will return -1.

### void Vpp\_free\_view(int vid)

Frees the view  $\mathsf{vid}.$

#### void \*Vpp\_acquire\_view(int vid)

Acquires read-write access to the view vid and return its base address. Upon failure, NULL will be returned.

#### void \*Vpp\_acquire\_Rview(int vid)

Acquires read-only access to the view vid and return its base address. Upon failure, NULL will be returned.

#### void Vpp\_release\_view(int vid)

Release access to the view vid.

### void Vpp\_barrier()

Block the process until all processes reach this barrier.

## 2.1.1 Implementation

In the data race prevention scheme, data races are prevented by a memory protection mechanism available in most UNIX systems. All views are initially protected from access using system calls such as mprotect(). mprotect() can deny access to a page, or allows read-only access to a page, or allows read/write access to a page. This mechanism is used to prevent a view from illegal accesses. Only after a view is acquired is a process allowed to access the memory pages of the view via mprotect(). When a view is released, the process is again denied access to the view.

If a process accesses a view before Vpp\_acquire\_view or after Vpp\_release\_view, the pages of the view would not have the necessary access permission and thus a segmentation fault will occur. The system will handle the fault, send a warning message to the programmer that a view is accessed without acquisition, and quit the program execution.

In this way, a view can either be written to by one process or read by multiple processes at a time. Programmers do not need to worry about the data race bugs. If a view is accessed by calling Vpp\_acquire\_view, mutual exclusion of the view access is automatically done by the system. If a view is accessed without view acquisition, a segmentation fault will occur, and the system will alert the programmer about which view is accessed without acquisition. The programmer can easily fix the bug by inserting Vpp\_acquire\_view and Vpp\_release\_view into the faulted code section.

The extra cost of this data race prevention scheme is the overhead of the memory protection. In the VOPP implementation Maotai 2.0, this cost is very low. On a Sun T2000 Server equipped with a 1GHz UltraSPARC T1 processor [94], micro-benchmarking results demonstrate that the overhead of memory protection added to the view primitives is generally very low (around  $2-3\mu s$ ). The exception is Vpp\_acquire\_view, requiring up to  $35\mu s$  extra, which covers the essential overhead of the memory protection mechanism(see Table 2.1). Note that Vpp\_acquire\_Rview and Vpp\_release\_Rview means acquiring and releasing views as read-only.

| Primitive           | no prot | prot  | $\cos t$ |  |  |  |

|---------------------|---------|-------|----------|--|--|--|

| Vpp_acquire_view()  | 3.14    | 39.08 | 35.94    |  |  |  |

| Vpp_acquire_Rview() | 3.60    | 6.32  | 2.72     |  |  |  |

| Vpp_release_view()  | 1.91    | 4.54  | 2.63     |  |  |  |

| Vpp_release_Rview() | 1.99    | 4.64  | 2.65     |  |  |  |

Table 2.1: Breakdown of view primitive costs (in  $\mu s$ )

However, in application benchmarks, this overhead does not cause noticeable difference in application speedup. Table 2.2 shows the speedups (at 32 processes) of different applications with and without memory protection in Maotai 2.0. This experiment has six benchmark applications: Successive Over-Relaxation (SOR), Gaussian Elimination (GE), Integer Sort (IS), Neural Network (NN), Mandelbrot, and Mergesort, which typically represent a wide variety of parallel applications. For details of these applications, refer to Section 2.2. As we can see from Table 2.2, in all 32-process benchmark cases, the difference is around 0.5%. Therefore, the overhead introduced by data race prevention is trivial.

Table 2.2: Effects of memory protection on benchmark application speedups with 32 processes

| <u> </u>                             |         |       |  |  |  |  |  |

|--------------------------------------|---------|-------|--|--|--|--|--|

| Application                          | no prot | prot  |  |  |  |  |  |

| SOR                                  | 16.82   | 16.77 |  |  |  |  |  |

| GE                                   | 22.41   | 22.36 |  |  |  |  |  |

| IS                                   | 16.51   | 16.47 |  |  |  |  |  |

| NN                                   | 16.98   | 16.92 |  |  |  |  |  |

| Mandelbrot <sup><math>a</math></sup> | 7.61    | 7.60  |  |  |  |  |  |

| Mergesort                            | 12.52   | 12.50 |  |  |  |  |  |

<sup>a</sup>speedup with eight processes

One issue about the implementation is that memory protection such as **mprotect** is

page-based. Therefore, in order to protect view data properly, memory space allocated to a view is aligned by pages. This can result in memory space wastage. Table 2.3 shows the requested and actual sizes of the memory space allocated by VOPP in the benchmark applications. The page size is 8kB and 32 processes are used when the data of the table are collected. From this table, it can be seen that some applications like GE and Mandelbrot, which have many views that do not exactly fit a page, have a higher proportion of memory wastage (up to 51%), though other applications have less than 7% wastage. However, this memory wastage is much smaller than the memory footprint of race detectors, which can be "several times" the memory footprint of the original applications.

| Algorithm  | Requested     | Actual                | Wasted      | Percent wasted |

|------------|---------------|-----------------------|-------------|----------------|

| SOR        | 4,097,024     | 4,194,304             | 97,280      | 2.32           |

| GE         | 64,016,004    | 98,328,576            | 34,312,572  | 34.9           |

| IS         | 4,194,304     | 4,194,304             | 0           | 0              |

| NN         | 271,612       | 294,912               | 23,300      | 7.90           |

| Mandelbrot | 2,000,000     | 4,096,000             | 2,096,000   | 51.2           |

| Mergesort  | 1,600,001,280 | $1,\!600,\!274,\!432$ | $273,\!152$ | 0.0171         |

Table 2.3: Requested vs actual VOPP shared size (in Kbytes) in different applications

Fortunately, with architectural support of variable-size pages [15, 104], this memory wastage can be greatly reduced.

## 2.2 Performance Evaluation with Other Models

This section compares the performance of Maotai 2.0 with other modern shared memory parallel programming models OpenMP and Cilk. These models are evaluated in benchmark applications from the SPLASH-2 benchmark suite [105] including Successive Over-Relaxation (SOR), Integer Sort (IS), Gaussian Elimination (GE), Neural Network (NN) and Mandelbrot, as well as Mergesort adapted from the Cilk-5.4.6 benchmark [96]. The SPLASH-2 benchmark suite represent different classes of parallel algorithms commonly found in real-life applications. The experiments are carried out on a Sun T2000 server with an UltraSPARC T1 processor and 16GB memory. The UltraSPARC T1 has eight cores, each of which is clocked at 1GHz and supports four hardware threads. In total, the UltraSPARC T1 processor supports up to 32 hardware threads [94]. Linux kernel 2.6.24-sparc64-smp and the compiler gcc-4.4 are used during benchmarking. The benchmark applications are implemented on Maotai 2.0, Cilk-5.4.6 [96], and OpenMP 3.0 [74], respectively. All programs are compiled with the optimization flag "-O2". In each case, speedup is measured against the serial implementation of the benchmark algorithm. The elapsed time calculated in each case excludes initialization and finalization costs, because they are one-off and are difficult to measure within the program in models that involve source-translation, such as Cilk and OpenMP. Instead, startup and finalization times for each model are measured separately. Runtime of functions that are irrelevant to the original application, such as generation of random sequences and result-verification, are also excluded.

Successive Over-relaxation (SOR) is a multiple-iteration algorithm where each element is updated by the values of the neighbouring elements from the last iteration. In this experiment, the implementation is adapted from [108]. Matrix size is set to  $8000 \times 4000$  and 40 iterations are performed.

The Integer Sort (IS) algorithm used in this experiment is based on the NPB version [101]. This is a counting-sort algorithm. In this experiment, the problem size is  $2^{26}$  integers with a  $B_{max}$  of  $2^{15}$  and 40 repetitions are performed.

The Gaussian Elimination (GE) implementation from [108] is used in this experiment and the matrix size is set to  $4000 \times 4000$ .

The parallel Neural Network (NN) algorithm is based on [78]. This algorithm trains a back-propagation neural network in parallel using a training data set. In this experiment, the size of the neural network is set to  $9 \times 40 \times 1$  and the number of epochs is set to 200.

The Mandelbrot algorithm is embarrassingly-parallel. However, the workload of pixels is extremely uneven, and thus requires a load-balancing mechanism to prevent process starvation [39, 103]. In this experiment, the size of the screen is set to  $500 \times 500$ , the maximum number of iterations is set to 500 and each pixel is calculated 5000 times. The maximum number of processes / threads is set to eight for this experiment because hyperthreading relies on memory latency. Since this application has very few memory accesses, there is little speedup when more processes / threads than the number of CPU cores are used (The UltraSparc T1 has eight cores).

The parallel Mergesort algorithm is recursive [61, 96] and is implemented verbatim in Cilk and OpenMP to test performance of the newly-available task-parallelism feature in OpenMP [7]. The array consists of 200 million integers. This algorithm is converted to the iterative version for VOPP. The iterative version requires the number of processes to be a power of 2. This version first divides the array equally between the processes and each process sorts its own subarray. Then the merge procedure largely models the recursive version of the parallel merge algorithm.

Since the UltraSPARC T1 has only one floating-point unit, all floating-point calculations in the above algorithms are converted to integer calculation to avoid the bottleneck at the floating-point unit. Removal of floating point calculations is done in all implementations and does not affect the scalability of the algorithm or the fairness of the comparison.

## 2.2.1 Experimental Results

The experimental results are illustrated with speedup curves. Speedup curves on Maotai 2.0, Cilk, and OpenMP are given for each application. In the discussion below, n refers to the number of processes / threads.

Speedup is calculated by:

$$speedup = \frac{time_{serial.implementation}}{time_{parallel.implementation}}$$

(2.1)

To ensure fair comparison, the same serial implementation of each benchmark application is used as a baseline for calculating speedups of all parallel programming models.

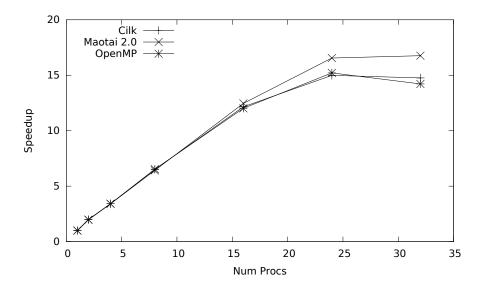

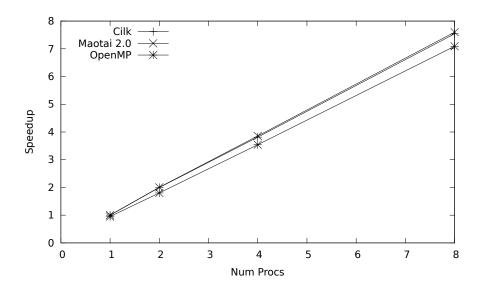

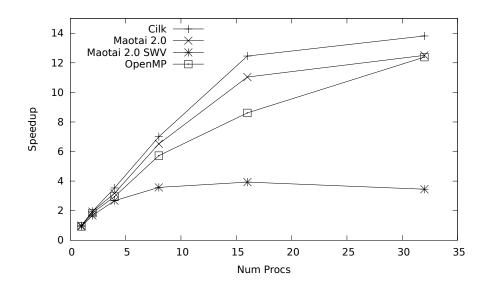

For SOR (Figure 2.2), Maotai 2.0 has the best performance. At n = 32, Maotai 2.0 is 13.6% better than Cilk and 17.9% better than OpenMP.

Figure 2.2: Speedup of SOR

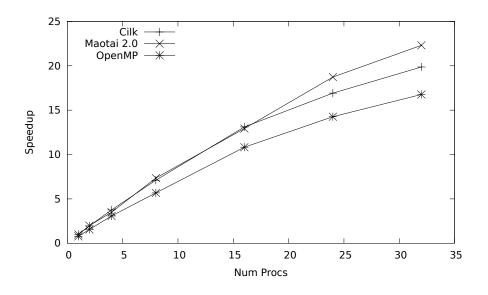

For GE (Figure 2.3), Maotai 2.0 again has the highest speedup. At n = 32, Maotai 2.0 is 7.4% better than Cilk and 33% better than OpenMP.

Figure 2.3: Speedup of GE

In IS (Figure 2.4), there are less variations in speedups in different models. However at n = 32, Maotai 2.0 is 5% faster than Cilk and 15% faster than OpenMP.

Figure 2.4: Speedup of IS

In NN (Figure 2.5), all models have similar speedups. Maotai 2.0 is 3.1% faster than OpenMP, but it is 1.8% slower than Cilk.

Figure 2.5: Speedup of NN

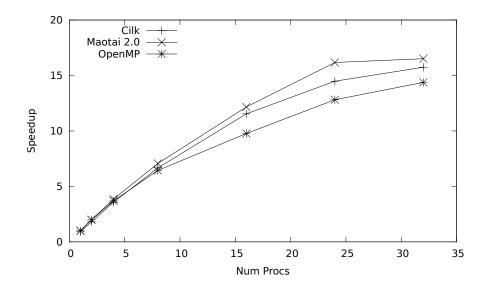

In Mandelbrot (Figure 2.6), there are relatively little differences between speedups of different models. At n = 8, Maotai 2.0 is 0.8% faster than Cilk and 7.2% faster than OpenMP.

Figure 2.6: Speedup of Mandelbrot

For Mergesort, Figure 2.7 shows speedup of Maotai 2.0 is relatively slower. This issue will be addressed in Section 2.2.2.

Figure 2.7: Speedup of Mergesort

Note that, in the above collected results, the standard deviations of the elapsed time at n = 32 for Maotai 2.0 and Cilk cases are less than 0.1s, but the standard deviations of the elapsed time for OpenMP are between 0.2 to 0.5s, which may be due to the random nature of the OpenMP task scheduler.

Table 2.4 presents the startup and finalization time of each system. As expected, startup and finalization costs for thread-based models including Cilk and OpenMP are lower than process-based system like Maotai 2.0.

|            | 1 | 2  | 4  | 8  | 16 | 24 | 32 |

|------------|---|----|----|----|----|----|----|

| Cilk       | 2 | 2  | 2  | 2  | 2  | 2  | 2  |

| OpenMP     | 2 | 2  | 2  | 2  | 2  | 2  | 2  |

| Maotai 2.0 | 9 | 10 | 11 | 13 | 15 | 19 | 22 |

| Serial     | 2 |    |    |    |    |    |    |

Table 2.4: Combined startup and finalization time (in ms) for different number of processes/threads on a Sun T2000 server

All thread-based models have the same combined startup and finalization time as the serial version regardless of the number of threads. Maotai 2.0 has a startup/finalization cost of 9ms (at n = 1) and the cost grows to 22ms at n = 32, almost linear to the number of processes. Despite Maotai 2.0 having a larger startup/finalization overhead, the 22ms is still negligible compared to the time consumed in n = 32 cases, which is at least 10 seconds. Also the startup/finalization time in Maotai 2.0 is only a one time event, therefore, this overhead should have negligible effect on the speedup curves.

### 2.2.2 Discussion

The following is an analysis on why Maotai 2.0 performs better or worse than other systems.

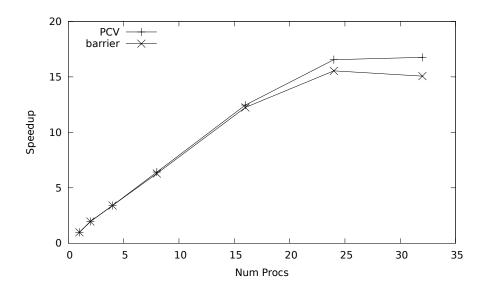

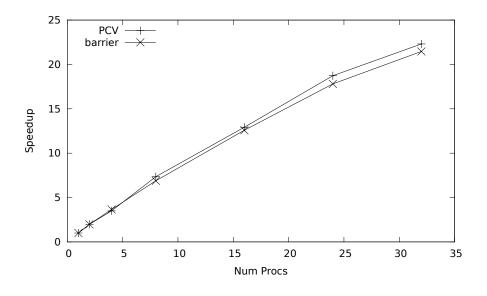

The producer/consumer view (PCV) in Maotai 2.0 enhances both programmability and performance of SOR and GE. In SOR, PCV is used to pass boundary rows to neighbour processes, thus allowing the natural expression of the message-passing relationship without the use of barrier, which would hold up irrelevant processes. Apart from programmability, the resultant performance gain is reflected in Figure 2.9, where the PCV VOPP version is 11.2% faster than the barrier-based SOR version. More detailed reason regarding why PCV is more efficient than barrier will be explained in Section 2.3.2.

Similarly in GE, PCV is used to *broadcast* the pivot row and the swap index, which improves programmability by mimicking the broadcasting semantics in the parallel algorithm. Also the removal of barriers by PCV improves the VOPP performance by 4.2% (Figure 2.10). Time is saved by replacing lock and barrier primitives with a PCV primitive.

Multiple-Program Multiple-Data (MPMD) models such as Cilk/Cilk++ and OpenMP do *not* have barriers because in this case, the parallel calculation part is conveniently expressed by parallel for-loop (or in case of Cilk, spawn recursive task decomposition threads and sync at end of parallel calculation) and the pivot part is run serially. Synchronization is implicit in the parallel for-loop construct, where tasks are forked at the beginning of the loop and joined at the end of the loop, therefore these fork-join actions are essentially barriers and have the similar overhead to the barriers in VOPP. In multiple-iterative cases such as GE and SOR, the cumulative task scheduling and synchronization overheads can be considerable. Therefore, the Maotai model would be more suited for these problems.

Mandelbrot is an embarrassingly-parallel algorithm. This application demonstrates the slight performance advantage of the VOPP single-program multiple-data (SPMD) model, in which a task queue is used to balance workload in the program, instead of using general runtime schedulers as in OpenMP and Cilk. This result has also demonstrated that the implementation of the system queue is efficient.

In IS, the performance advantage seen in Maotai 2.0 over other models can be

attributed to the split of global keyden array into N views, where N is the number of processes. In the global keyden construction step, each process updates *all* global keyden parts in the round-robin fashion, starting from the *proc\_id<sup>th</sup>* part. Here, the SWMR view access pattern removes the need for barriers for preventing data race due to multiple processes updating an element simultaneously. This removal of barriers can contribute to the performance gain by the VOPP program.

In NN, since multiple items are updated by multiple processes at the end of the iteration, barriers are still used in the VOPP program. Therefore, it has the same synchronization overhead of other models. However the performance of Maotai 2.0 is still comparable to other models, which shows that being data race free has little impact on performance.

However, the SWMR model in VOPP does have its limitations in cases where the access pattern changes in every iteration. In those cases, view data must be copied to a local buffer of a process, where the process works on the data. After the data is processed, the view is acquired again by the process and the results copied back to the view. In applications tested in this chapter, Mergesort is such an example. In Mergesort, the resultant excessive memory-copying renders the implementation unscalable (Refer to VOPP-SWV in Figure 2.7). For this application, VOPP does trade off some programming convenience and performance for data race prevention. However, Maotai 2.0 has provided a Multiple Writer View (MWV) to offer the programming convenience for experienced programmers. A MWV is a view that can be accessed at *different lo*cations simultaneously by multiple processes. Therefore, it is up to the programmer to make sure there is no data race in a MWV. In contrast to other programming models, the data races of a MWV are *confined* inside the view should they occur. This alternative MWV implementation allows multiple processes to work directly on the view and avoid memory copying. With MWV, the speedup of Mergesort in Maotai 2.0 is comparable to other shared-memory models. Figure 2.7 shows, at n = 32, Maotai 2.0 (refer to VOPP-MWV) is 1% faster than OpenMP, but 9% slower than Cilk.

Cilk performs very well in cases like Mergesort and NN. This can be attributed to its recursive task decomposition that ensures cache locality [61].

The parallel for-loop in OpenMP allows easy specification of data-parallelism. However, it would introduce a task-scheduling cost, especially when the workload is fixed and no load-balancing is required. The lower speedups of GE, SOR and NN of OpenMP can be attributed to this parallel for-loop overhead. Although Cilk++ cannot be benchmarked in this experiment because it does not support sparc64-smp, its equivalent construct cilk\_for can also have the similar task-scheduling overhead.

## 2.3 Advanced Features in Maotai 2.0

In addition to data race prevention, Maotai 2.0 also offers primitives for acquiring multiple views in order to avoid deadlocks, producer/consumer views, and system queues to enhance programmability and performance. These features are discussed below.

## 2.3.1 Deadlock Avoidance

Similar to data race, deadlock is another pain that can happen easily but is difficult to debug in shared-memory parallel programming. In VOPP, deadlock can happen if views are acquired in a nested way and different processes acquire them in different orders.

To avoid deadlocks due to acquiring multiple views in different orders, Maotai 2.0 offers primitives for acquiring multiple views. Programmers can list all views to be acquired with these primitives which will acquire the views in a specific, same order. In this way, there is no chance for deadlocks to happen.

An example illustrating the use of the primitives for acquiring multiple views is shown in Figure 2.3.1

```

/* acquire access to both view 0 and 1 */

Vpp_acquire_multiviews(0, &ptr0, 1, &ptr1);

ptr0->result += compute0(ptr0->a, ptr1->a);

ptr1->result += compute1(ptr1->a, ptr0->a);

Vpp_release_view(); /* release all views */

```

Figure 2.8: Code snippet showing how multiple views are acquired together in VOPP

In the above example, the process acquires both view 0 and 1 with Vpp\_acquire\_multiviews which puts the view base addresses into ptr0 and ptr1. Finally the process releases both views with Vpp\_release\_view.

Note that the above solution cannot eliminate deadlocks from VOPP programs as the data race prevention scheme does data races. There are two reasons: first, the programmer may choose not to use Vpp\_acquire\_multiviews for nested view acquisition; second, even if the programmer would like to use the primitive, it is difficult to know which views to acquire in advance in some programs where inner views can only be decided after the outer views are processed.

Nevertheless, the above primitives provide an avenue for novice programmers to avoid unnecessary deadlocks.

## 2.3.2 Producer/Consumer View

A Producer/Consumer View (PCV) is provided to allow direct expression of producer/consumer relationships in parallel algorithms. Traditionally barriers are used to synchronize the producers and the consumers in shared memory parallel programming. Barriers are expensive because they make all processes wait, which causes unnecessary waiting in applications where producer/consumer processes can be individually synchronized. Moreover, the cost of barriers would increase with increasing number of processes. With the introduction of PCV, programming with producer/consumer problem is more straightforward and thus increases programmability. Additionally PCV can avoid expensive synchronization overhead since a consumer process only synchronizes with its producer process.

PCV is implemented as a queue. The producer enqueues a new version of the view by acquiring the view, producing the data, and finally releasing the view. The consumer dequeues a version of the view by acquiring read-only access to the view. After it finishes with the view, it releases the view whose buffer may be recycled by the producer.

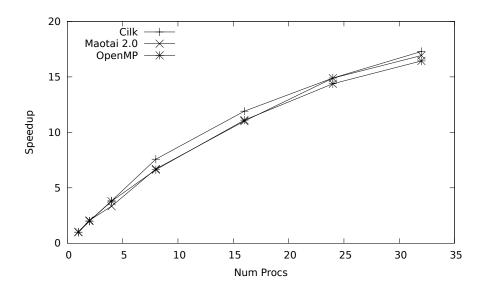

In this experiment, the SOR and GE benchmark applications demonstrate that PCVs give a better speedup than barrier based implementations. Figure 2.9 and 2.10 shows the speedup difference between applications using barriers and those using PCVs.

Figure 2.9: Speedup of SOR in VOPP

Figure 2.9 shows the speedup of SOR which uses PCV to improve its performance. Compared with its barrier implementation, the improvement of speedup is 11.2% at 32 processes.

Figure 2.10: Speedup of GE in VOPP

Figure 2.10 shows the speedup of GE which uses  $\mathsf{PCV}$  to improve its performance. Compared with its barrier implementation, the improvement of speedup is 4.2% at 32 processes.

### 2.3.3 System Queues

System queues are provided in Maotai 2.0 to store view IDs. This facility allows easy implementations of task queues. Task queues are good for load balancing parallel applications (e.g. Mandelbrot and tree search algorithms), where the data for each job or node can be put in a view and its ID is simply enqueued in a system queue for other processes to work on.

In Maotai 2.0, the enqueue and dequeue calls are efficient. In a microbenchmark test on a Sun T2000 server, an enqueue call only takes  $2.65\mu s$  and a dequeue call takes  $2.56\mu s$ .

## 2.4 Concluding Remarks

The data race prevention scheme based on views is shown to be efficient and adds little extra overhead to parallel programming systems. Though there is some memory wastage due to page alignment in the implementation, architectural support for variable-size pages will significantly reduce the wastage. Even with a fixed page size, view constructs are useful to remove data races. Moreover, "big data" applications tend to have huge data sets, which means the size of a view will become much larger and can easily surpass several pages. This trend will make the memory wastage proportionally small.

With the advanced features in Maotai 2.0, the performance and programmability of VOPP are enhanced. Though strict SWV views are rigid for some applications like Mergesort, Maotai 2.0 offers MWV views to allow programmers to fall back to traditional shared memory programming, with the risk of data races that are confined in a single MWV view.

Performance results demonstrate that Maotai 2.0 is very competent among modern parallel programming models, especially with the unique data race prevention scheme.

To further improve the programmability of VOPP, the next chapter will propose an automatic detection scheme for view access, which will free the programmers from manually acquiring/releasing views.

# Chapter 3

# Automatic Detection of View Access

As discussed in Chapter 2, Maotai 2.0 provides a data race free parallel programming model based on VOPP. However, in Maotai 2.0, views must be explicitly acquired before access and released after access. It is often troublesome to manage view acquiring/releasing constructs.

For example, Figure 3.1 shows a serial version of a list traversal program and its Maotai 2.0 version.

```

/* serial version */

/* Maotai 2.0 */

typedef struct Node_rec Node;

typedef struct Node_rec Node;

struct Node_rec {

struct Node_rec {

Node *next;

Node *next;

Elem elem;

Elem elem;

};

};

Node *list_search(Elem elem, Node *list) {

Node *list_search(Elem elem, int vid) {

while (NULL != list) {

Node *list = Vpp_acquire_view(vid);

if (elem == list->elem) {

while (NULL != list) {

return list;

if (elem == list->elem) {

}

Vpp_release_view();

list = list->next;

}

return list;

return NULL;

}

}

list = list->next;

}

Vpp_release_view();

return NULL;

}

```

Figure 3.1: Code snippets comparing serial and Maotai 2.0 implementations of the list traversal function In the above list traversal in Maotai 2.0, the view is first acquired by Vpp\_acquire\_view, which returns the base address of the list, then the while loop traverses the list until the element elem is found. When elem is found (within the while loop), the view must be manually released by Vpp\_release\_view before returning the current element. If the element cannot be found, then the view will be released and the search function will return NULL. The code in the while loop is prone to error, because it is easy to forget to release the view before calling return within the while loop. If that happens, the next process that is acquiring the view will wait forever.

To solve this problem, this chapter proposes a scheme for automatic detection of view access which has greatly improved the programming interface of VOPP (refer to Section 3.1 for details), as VOPP no longer requires programmers to use explicit view acquire/release constructs. In this scheme, a view is automatically acquired when first accessed and released when leaving the scope of the view acquisition. The automatic view access detection scheme is shown to improve the programming convenience of VOPP, the programmability of which is similar to transactional memory models in many cases.

This chapter presents the parallel programming system, Maotai 3.0, which is based on the VOPP paradigm with the automatic detection scheme that supports both C and C++. Performance results show that the cost for the automatic detection is relatively small, and Maotai 3.0 has superior performance over transactional memory models like TL-2 0.9.6 [26], which provides a similar programming interface as Maotai 3.0.