# VLSI Architectures and Arithmetic Operations with Application to the Fermat Number Transform

Lars-Inge Alfredsson

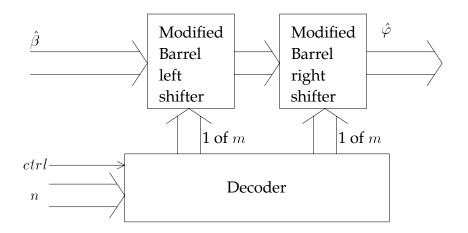

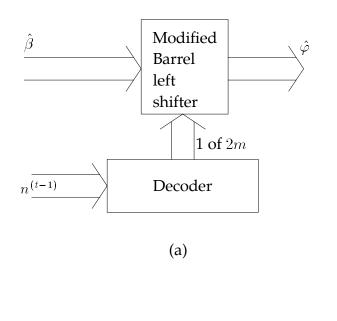

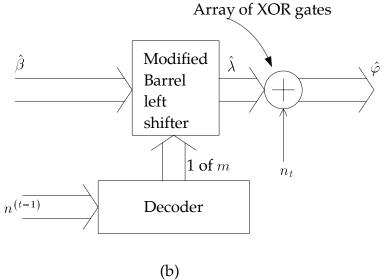

Department of Electrical Engineering Linköping University, S-581 83 Linköping, Sweden

Linköping 1996

ISBN 91-7871-694-2

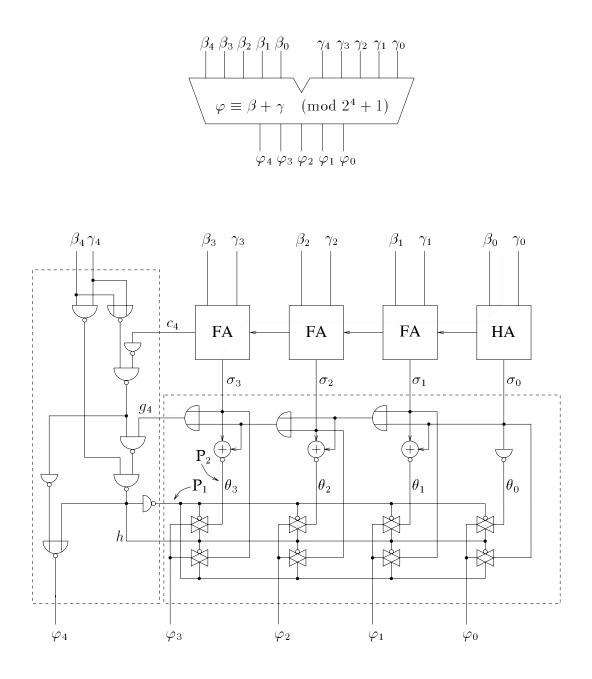

ISSN 0345-7524

Printed in Sweden by LJ Foto & Montage/VTT-Grafiska, Vimmerby 1996

To my wife

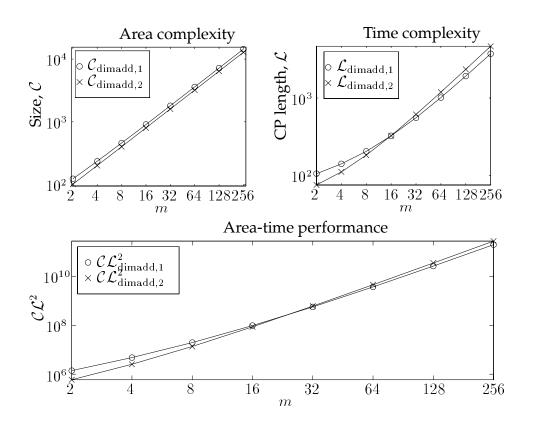

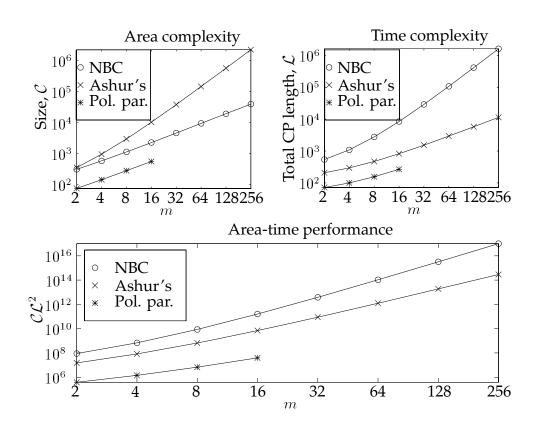

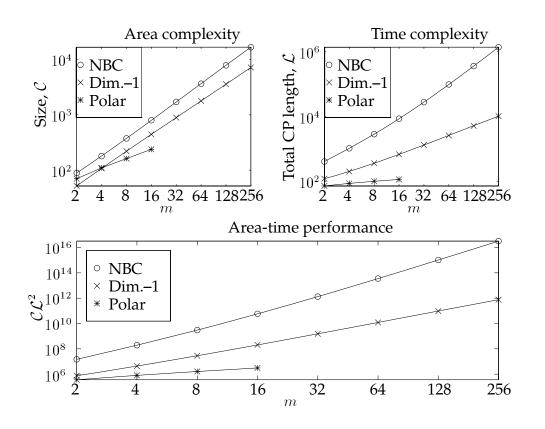

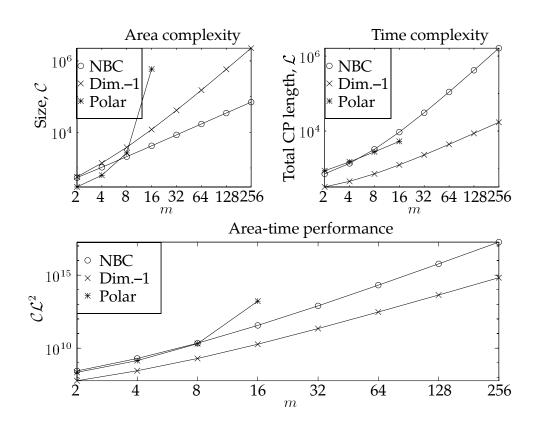

Anneli

and to our children Michaela, Sebastian, Jonathan, and Antonia

## Abstract

The properties of arithmetic operations in Fermat integer quotient rings  $\mathbb{Z}_{2^m+1}$ , where  $m = 2^t$ , are investigated. The arithmetic operations considered are mainly those involved in the computation of the Fermat number transform. We consider some ways of representing the binary coded integers in such rings and investigate VLSI architectures for arithmetic operations, with respect to the different element representations. The VLSI architectures are mutually compared with respect to area (*A*) and time (*T*) complexity and area-time performance ( $AT^2$ ). The VLSI model chosen is a linear switch-level *RC* model.

In the polar representation, the nonzero elements of a field are represented by the powers of a primitive element of the field. In the thesis we particularly investigate the properties of arithmetic operations and their corresponding VLSI architectures with respect to the polar representation of the elements of Fermat prime fields. Some new results regarding the applicability of the Fermat number transform when using the polar representation are also presented.

## Acknowledgements

My time as a PhD student has come to an end. I have really enjoyed teaching, studying, and doing research, which have been my main duties during these years. One of the main reasons why I wanted to join the Data Transmission group was the friendly and inspiring atmosphere that was — and still is — prevalent among the people in the group. I would like to thank all members of the Data Transmission group for providing this friendly and inspiring atmosphere.

I particularly would like to thank my supervisor, Professor Thomas Ericson, for giving me the opportunity to join the Data Transmission group. He has been an excellent guide on my tour into the world of science and he has always supported my work with a proper balance between friendly encouragements and educating directions.

I also appreciate the fruitful discussions with Professor Stefan Dodunekov, Professor Christer Svensson, and Dr. Edoardo Mastrovito.

Finally, I would like to thank my wonderful family, to whom I dedicate this thesis. The seemingly never-ending process of writing the thesis has come to an end. From now on, I will spend a lot more time with You!

Linköping, March 1996

Lasse Alfredsson

There are certain privileges of a writer, the benefit whereof, I hope, there will be no reason to doubt; Particularly, that where I am not understood, it shall be concluded, that something very useful and profound is couched underneath.

> – Jonathan Swift (Tale of a Tub, preface 1704)

Not that the story need to be long, but it will take a long while to make it short.

- Henry David Thoreau (Letter, 16 Nov. 1867.)

# Contents

| 1 | Intro | oductio | n                                                 | 1  |

|---|-------|---------|---------------------------------------------------|----|

| 2 | Bin   | ary Ari | thmetic in the Fermat Integer Quotient Ring       | 3  |

|   | 2.1   | The In  | teger Quotient Ring                               | 3  |

|   | 2.2   | The N   | umber Theoretic Transform                         | 4  |

|   |       | 2.2.1   | Suitable Integer Rings                            | 6  |

|   | 2.3   | The Fe  | ermat Number Transform                            | 10 |

|   |       | 2.3.1   | Fermat Numbers                                    | 10 |

|   |       | 2.3.2   | The Transform Kernel                              | 12 |

|   |       | 2.3.3   | Butterfly Computations                            | 16 |

|   | 2.4   | Eleme   | nt Representation                                 | 23 |

|   |       |         |                                                   |    |

| 3 | Арр   | licatio | ns                                                | 25 |

|   | 3.1   | Convo   | olution and Correlation of Real Integer Sequences | 26 |

|   | 3.2   | Decod   | ling of Reed-Solomon Codes                        | 30 |

| 4 | The | VLSI   | Model                                  | 33 |

|---|-----|--------|----------------------------------------|----|

|   | 4.1 | Introd | luction                                | 34 |

|   | 4.2 | Comp   | plexity and Performance                | 36 |

|   |     | 4.2.1  | The Delay Model                        | 36 |

|   |     | 4.2.2  | Area and Time Complexities             | 38 |

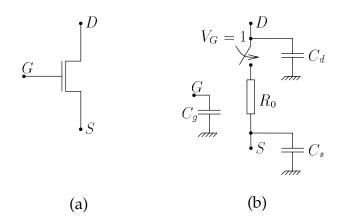

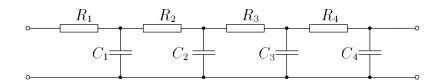

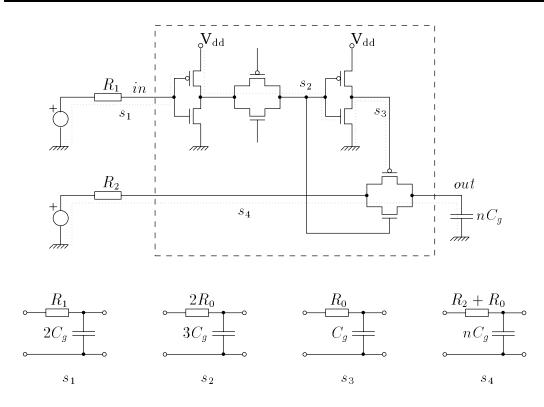

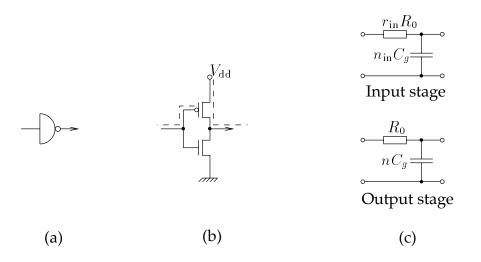

|   | 4.3 | Basic  | CMOS Building Blocks                   | 42 |

|   |     | 4.3.1  | The Inverter and the Transmission Gate | 42 |

|   |     | 4.3.2  | The Two-Input Multiplexer              | 44 |

|   |     | 4.3.3  | Two-Input Gates                        | 44 |

|   |     | 4.3.4  | The Single-Bit Adder                   | 47 |

|   |     | 4.3.5  | The Register                           | 51 |

|   |     | 4.3.6  | Table of Complexity Parameters         | 55 |

|   | 4.4 | Imple  | menting the Fermat Number Transform    | 57 |

| 5 | The | Norma  | al Binary Coded Representation         | 59 |

|   | 5.1 | Archi  | tectures for Arithmetic Operations     | 59 |

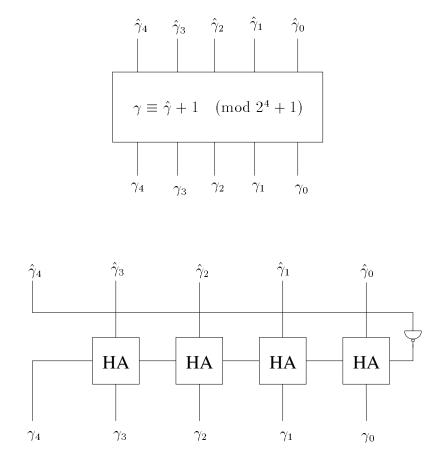

|   |     | 5.1.1  | Modulus Reduction                      | 60 |

|   |     | 5.1.2  | Negation                               | 68 |

|   |     | 5.1.3  | Addition and Subtraction               | 72 |

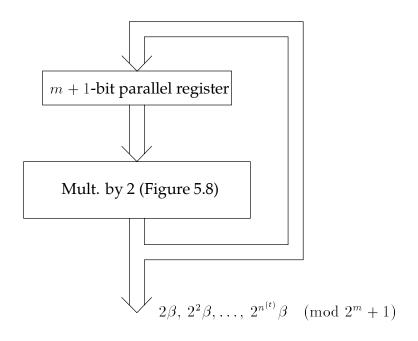

|   |     | 5.1.4  | Multiplication by Powers of 2          | 77 |

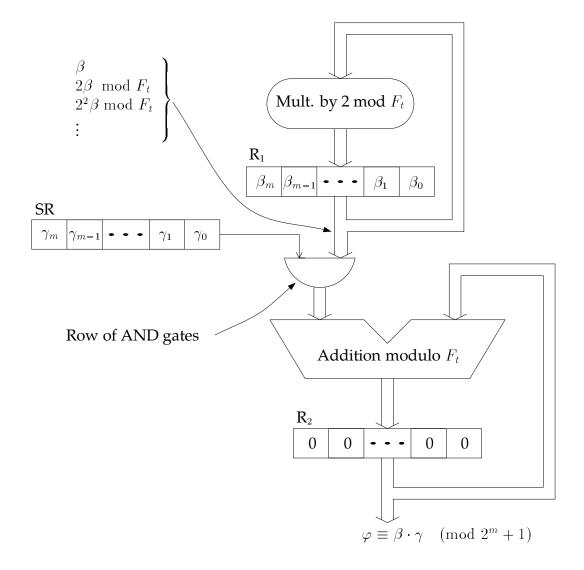

|   |     | 5.1.5  | General Multiplication                 | 81 |

|   |     | 5.1.6  | Exponentiation of the Transform Kernel | 84 |

|   | 5.2 | Summ   | nary                                   | 87 |

|   |     |        |                                        |    |

| 6 | The | Dimin  | ished-1 Representation                 | 89 |

| Contents |

|----------|

|----------|

|   |     | 6.1.1   | Arithmetic Operations                  | 90  |

|---|-----|---------|----------------------------------------|-----|

|   | 6.2 | The U   | se of a Zero Indicator                 | 93  |

|   | 6.3 | The D   | Piminished–1 Representation            | 98  |

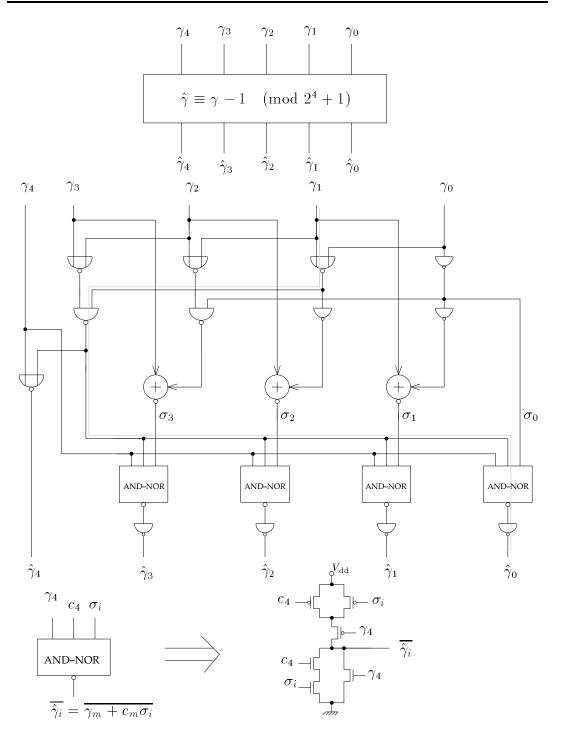

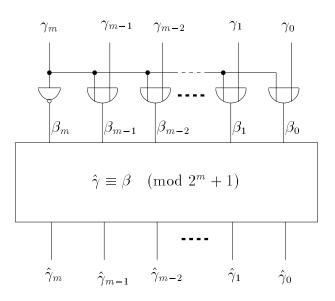

|   |     | 6.3.1   | Code Translation                       | 98  |

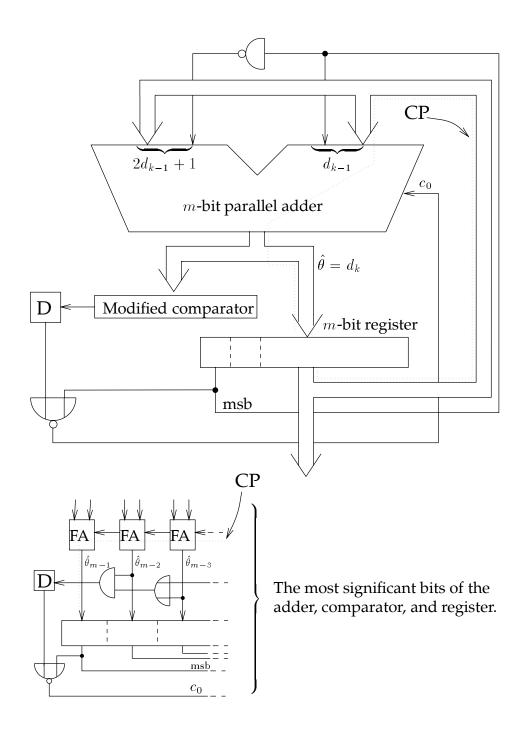

|   |     | 6.3.2   | Modulus Reduction                      | 106 |

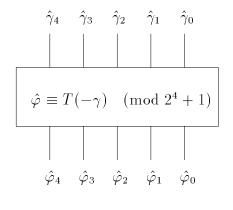

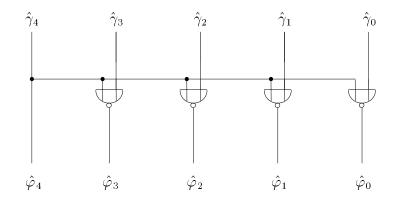

|   |     | 6.3.3   | Negation                               | 106 |

|   |     | 6.3.4   | Addition and Subtraction               | 108 |

|   |     | 6.3.5   | Multiplication by Powers of 2          | 122 |

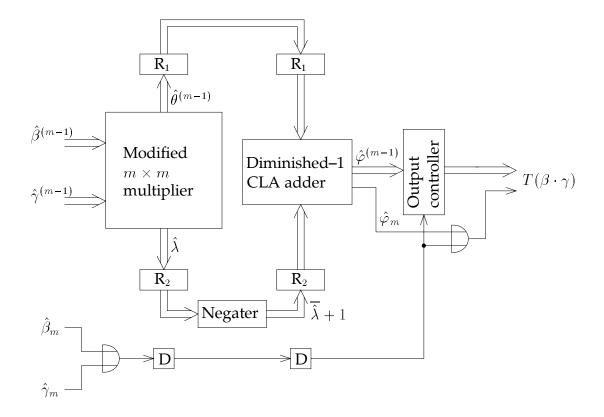

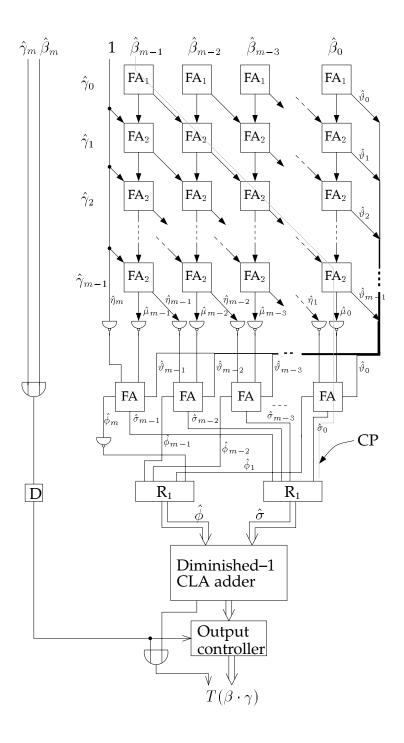

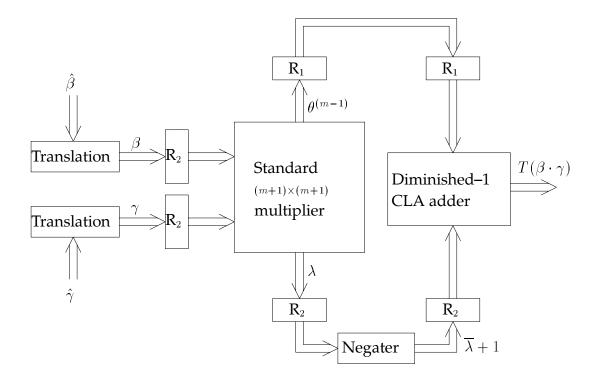

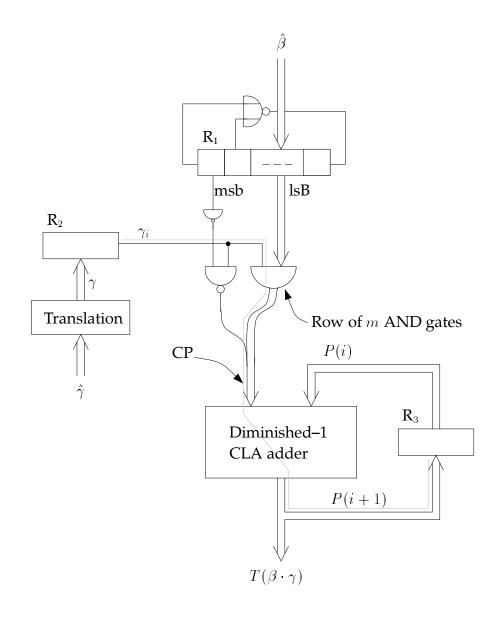

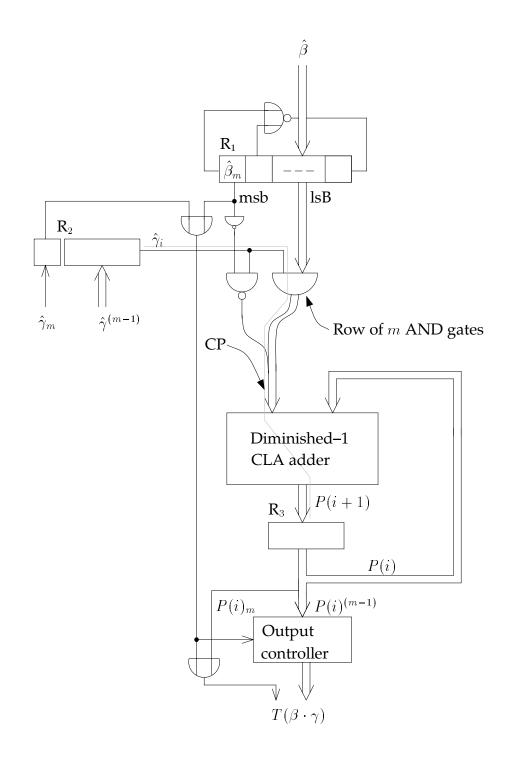

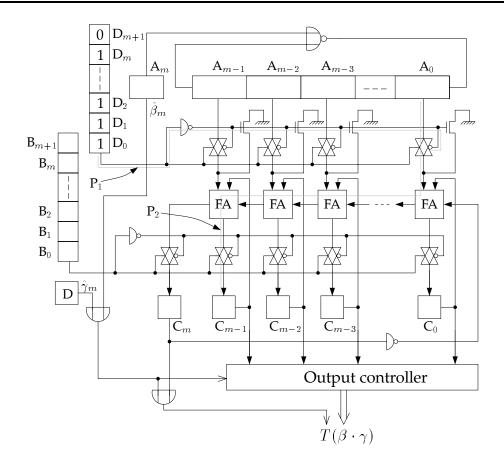

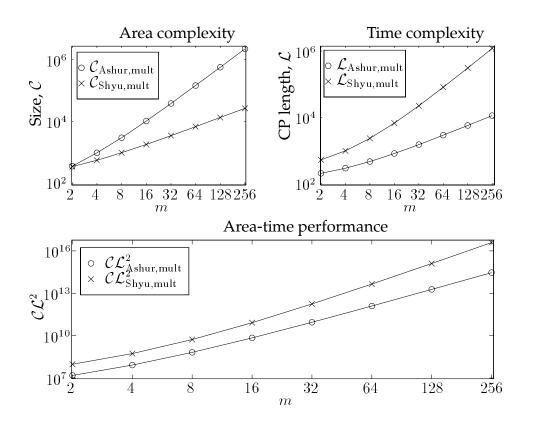

|   |     | 6.3.6   | General Multiplication                 | 128 |

|   |     | 6.3.7   | Exponentiation of the Transform Kernel | 152 |

|   | 6.4 | Summ    | nary                                   | 152 |

|   |     |         |                                        |     |

| 7 | The | Polar l | Representation                         | 155 |

|   | 7.1 | Introd  | luction                                | 155 |

|   | 7.2 | Arith   | metic Operations                       | 156 |

|   |     | 7.2.1   | Discrete Exponentiation                | 157 |

|   |     | 7.2.2   | The Discrete Logarithm                 | 157 |

|   |     | 7.2.3   | Modulus Reduction                      | 159 |

|   |     | 7.2.4   | Negation                               | 159 |

|   |     | 7.2.5   | Addition and Subtraction               | 160 |

|   |     | 7.2.6   | General Multiplication                 | 161 |

|   |     | 7.2.7   | Multiplication by Powers of $\omega$   | 162 |

|   | 7.3 | Zech's  | s Logarithm                            | 165 |

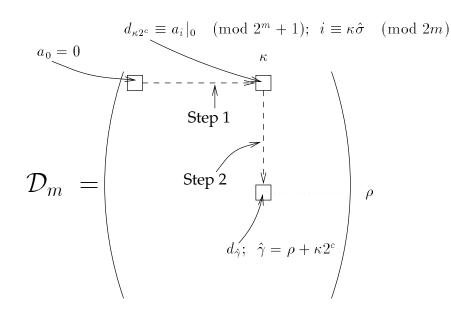

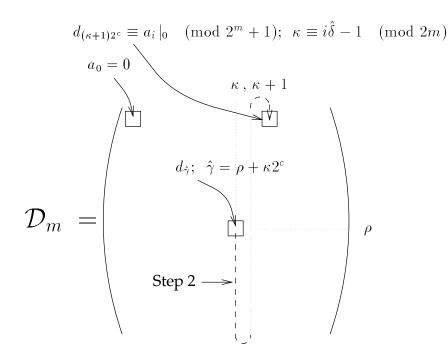

|   | 7.4 | Prope   | rties of the $\mathcal{D}_m$ Matrix    | 167 |

|   |     | 7.4.1   | Discrete Exponentiation                | 173 |

|   |     |         |                                        |     |

|   |     | 7.4.2   | The Discrete Logarithm                                   | 177 |

|---|-----|---------|----------------------------------------------------------|-----|

|   |     | 7.4.3   | Zech's Logarithm                                         | 179 |

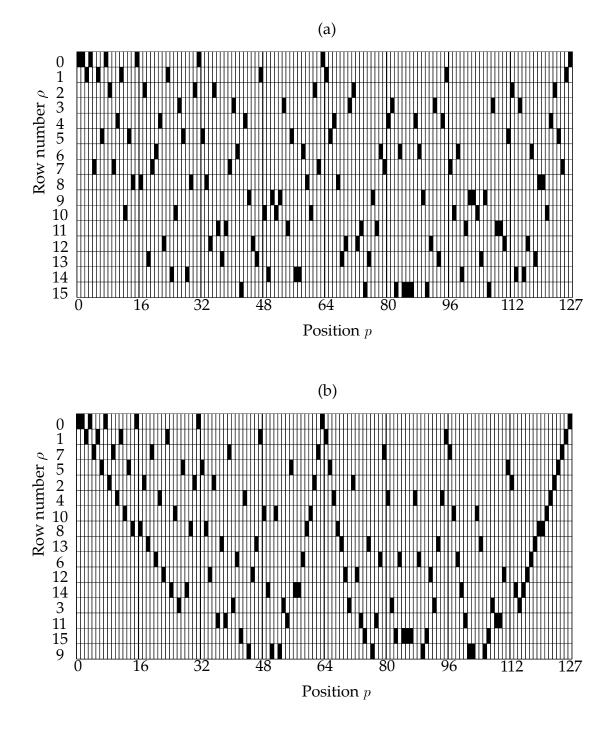

|   | 7.5 | The M   | firror Sequence $\mathcal{M}_m$                          | 182 |

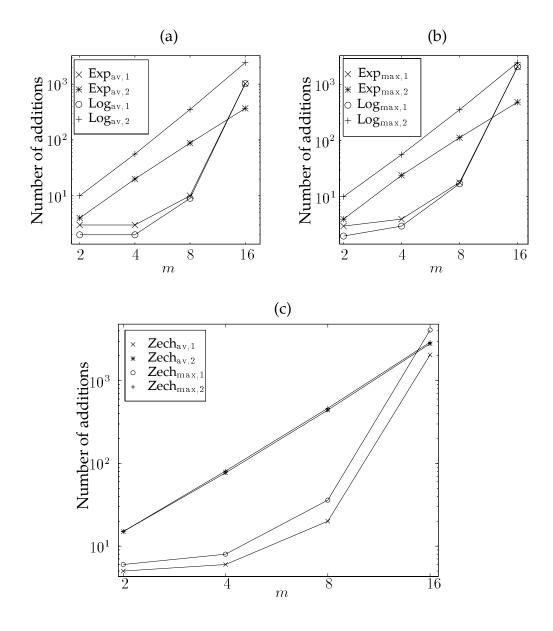

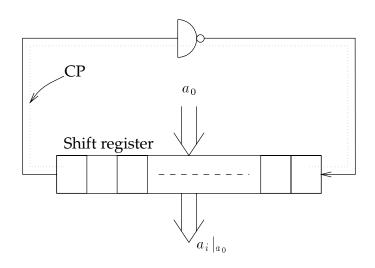

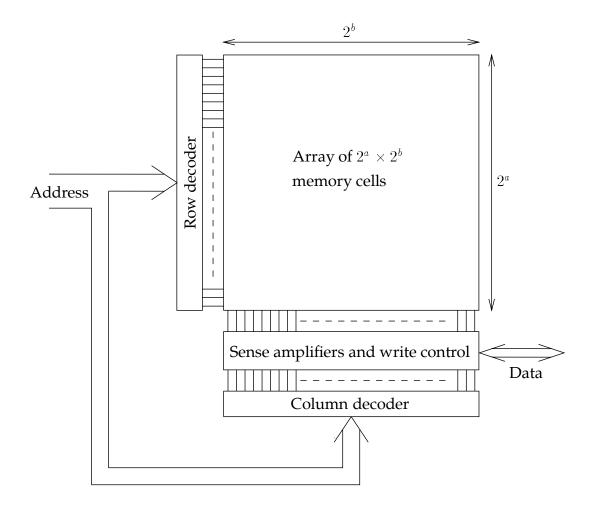

|   |     | 7.5.1   | Discrete Exponentiation Using a Look-Up Table            | 183 |

|   |     | 7.5.2   | The Discrete Logarithm Using a Look-Up Table             | 183 |

|   |     | 7.5.3   | The Mirror Properties of $\mathcal{M}_m$                 | 185 |

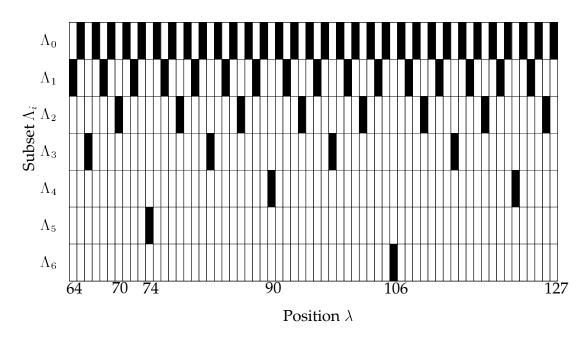

|   |     | 7.5.4   | Finding the Unique Distinct Positions in $\mathcal{M}_m$ | 189 |

|   |     | 7.5.5   | Addressing the Look-Up Table for Discrete Logarithm      | 195 |

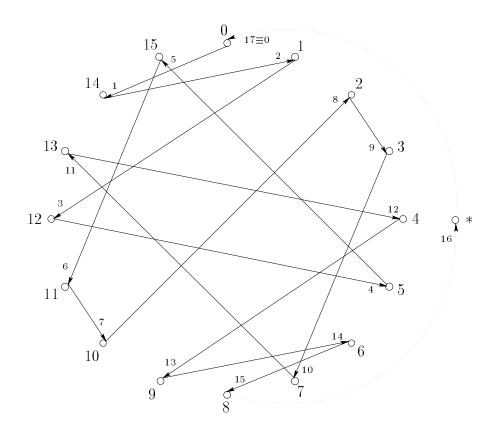

|   | 7.6 | Archit  | tectures for Arithmetic Operations                       | 197 |

|   |     | 7.6.1   | Discrete Exponentiation                                  | 197 |

|   |     | 7.6.2   | The Discrete Logarithm                                   | 205 |

|   |     | 7.6.3   | Negation                                                 | 206 |

|   |     | 7.6.4   | Addition                                                 | 208 |

|   |     | 7.6.5   | General multiplication                                   | 219 |

|   |     | 7.6.6   | Multiplication by powers of $\omega$                     | 223 |

|   | 7.7 | Summ    | nary                                                     | 231 |

| 8 | Con | npariso | ons Between Element Representations                      | 233 |

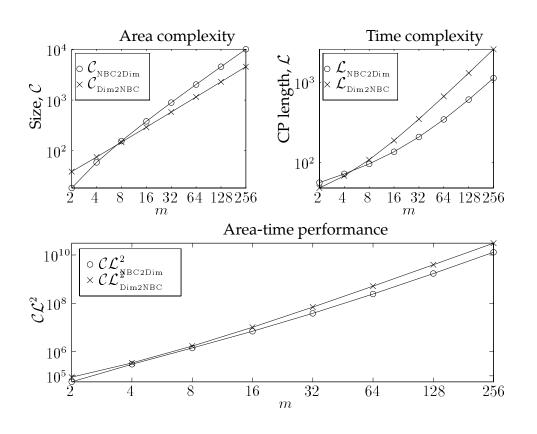

|   | 8.1 | Arithr  | metic Operations                                         | 233 |

|   |     | 8.1.1   | Modulus Reduction                                        | 233 |

|   |     | 8.1.2   | Code Translation                                         | 234 |

|   |     | 8.1.3   | Negation                                                 | 235 |

|   |     | 8.1.4   | Addition                                                 | 236 |

|   |     | 8.1.5   | General Multiplication                                   | 238 |

|   |     | 8.1.6   | Multiplication by Powers of $\omega$                     | 239 |

| Сс | ontents                                 | xi  |

|----|-----------------------------------------|-----|

|    | 8.1.7 Butterfly Computations            | 242 |

|    | 8.2 Other element representations       | 246 |

| 9  | Conclusions                             | 249 |

| A  | Proofs of Some Theorems                 | 251 |

|    | A.1 Proof of Theorem 2.1                | 251 |

|    | A.2 Proof of Theorem 2.3                | 253 |

|    | A.3 Proof of Theorem 2.5                | 254 |

| В  | A Table of Some Primes                  | 257 |

| C  | Further Properties of Zech's Logarithms | 261 |

|    | Bibliography                            | 269 |

Contents

## Introduction

In 1972 Rader [77] proposed transforms in the ring of integers modulo a Mersenne or a Fermat number  $(2^n - 1 \text{ and } 2^m + 1; m = 2^t = 1, 2, 4, 8, ..., \text{ respec$  $tively})$  to compute error-free convolutions of real integer sequences. Later, Agarwal and Burrus [2] showed that for some transform lengths the radix-2 Fermat number transform can be implemented using only addition, subtraction, and bit shifting, i.e. without using multiplication. This transform was shown to be faster than the conventional fast Fourier transform over the complex field.

There are also other applications of the Fermat number transform. Justesen [54] was one of the first to consider Reed-Solomon codes over the finite field of integers modulo a Fermat prime. He stated that the decoding complexity of such codes can be reduced if the Fermat number transform is used to evaluate the syndromes and error magnitudes. This was further investigated by Reed et al. [82] and others.

The special attributes of the Fermat number transform have led several researchers to consider the VLSI (Very Large Scale Integration) implementation of arithmetic operations in the ring of integers modulo a Fermat number. These operations are traditionally implemented using binary logic circuits, which means that the elements of the ring have a binary coded form of representation. The  $2^m + 1$  binary coded elements of the ring of integers modulo a Fermat number can be represented using m + 1 bits. We thus get numerous ways of representing the elements of the ring. The complexity and performance of architectures for arithmetic operations depend inter alia on the representation chosen.

The most known representations are the ones proposed by McClellan [65] and Leibowitz [58]. Their coding schemes are linear coordinate transformations of the normal binary coded representation of the elements in the ring. Using their representations, operations like addition, multiplication by two, and the code translation can be carried out fairly easy in VLSI. Also, for some relatively small transform lengths, the transform multiplications by powers of the transform kernel can be carried out as binary shifts. This is a well known property of the Fermat number transform. One of the main disadvantages of using McClellan's or Leibowitz' element representation is that for most other possible transform lengths, the resulting transform computation involves general multiplications (by powers of the transform kernel). Nevertheless, Leibowitz' so called *diminished–1* representation is used by most people who consider the VLSI implementation of the Fermat number transform.

In this thesis we investigate various ways of representing the binary coded elements of the ring of integers modulo a Fermat number. For each element representation considered, the properties of the arithmetic operations involved in the computation of the Fermat number transform are thoroughly investigated. Some other (arithmetic) operations are also considered. We also investigate VLSI architectures for the arithmetic operations. Some architectures are previously known and some are new. We show how each of these architectures is derived from its associated analytical expression for the arithmetic operation in question.

One of our main goals is to find a representation that makes it possible to compute the Fermat number transform with favourable area-time performance for *all* possible transform lengths. In particular, we focus on the arithmetic operations obtained when using the *polar representation* of the elements of Fermat prime fields. In the polar representation, the elements of a field are represented by powers of some primitive element of the field.

## Binary Arithmetic in the Fermat Integer Quotient Ring

In this chapter we give a formal introduction to the number theoretic transform in general and the Fermat number transform in particular. The chapter contains several known results from the area of number theory. We also consider some fast Fourier transform algorithms for implementing the Fermat number transform. For each algorithm, we find out which arithmetic operations are needed and the complexity of computing the transform. The purpose of the survey is to get our work into perspective. The chapter is concluded by presenting some aspects of representing the binary coded integers of the Fermat integer quotient ring.

### 2.1 The Integer Quotient Ring

A *ring* is an algebraic system consisting of a set of elements together with addition, subtraction, and multiplication. The result of any of these arithmetic operations is always an element of the original set. It may also be possible to divide in a ring. Then the *multiplicative inverse* of the divisor must exist in the ring.

A natural example of a ring is  $\mathbb{Z}$ , the ring of integers; for  $a, b \in \mathbb{Z}$ , we have  $a + b, a - b, a \cdot b \in \mathbb{Z}$ . Denote by  $\mathbb{Z}_q$  the *quotient ring* of integers modulo an integer q: It consists of the set  $\{0, 1, 2, ..., q - 1\}$  of integers and the result of every arithmetic operation is reduced modulo q. Thus, an integer c maps into  $\mathbb{Z}_q$  as the remainder r of c divided by q. If we have c = r + dq for some integer

d, then c and r are congruent modulo q. The notation for such a congruence is

$$c \equiv r \pmod{q}$$

The multiplicative inverse of an element of  $\mathbb{Z}_q$  exists if and only if the element is relatively prime to the modulus q.<sup>1</sup> If q is a prime number, then every nonzero element of  $\mathbb{Z}_q$  has a multiplicative inverse and thus division becomes a general operation in the ring. Then  $\mathbb{Z}_q$  is called a *field*.<sup>2</sup> For a detailed mathematical survey on the theory of rings and fields, see for example Lidl and Niederreiter [60] or Herstein [50].<sup>3</sup>

In this thesis we investigate VLSI architectures for arithmetic operations in the integer quotient ring  $\mathbb{Z}_q$ , where q is a Fermat number. Even though the development of multiple-valued logic has progressed over the years [29] it is still a difficult problem to design q-valued logic circuits for large q. Therefore, we restrict ourselves to representations of the integers modulo q as *binary* coded symbols and use binary logic circuits in the VLSI architectures for the arithmetic operations in  $\mathbb{Z}_q$ .

### 2.2 The Number Theoretic Transform

Before going into details about the Fermat number transform, we give the definition of the number theoretic transform in an arbitrary integer quotient ring  $\mathbb{Z}_q$ . We also discuss which moduli q are most suitable, with respect to the complexity of computing the number theoretic transform. The computation of the number theoretic transform (NTT) involves integer ring arithmetic operations. The NTT is a DFT-like (discrete Fourier transform) transform which is computed in the ring of integers modulo some integer:

**Definition 2.1** In the ring  $\mathbb{Z}_q$  of integers modulo a positive integer  $q = p_1^{n_1} p_2^{n_2} \cdots p_k^{n_k}$  the number theoretic transform of the sequence  $\mathbf{x} = \{x_n\}_{n=0}^{N-1}$  of elements  $x_n \in \mathbb{Z}_q$  is a sequence  $\mathbf{X} = \{X_k\}_{k=0}^{N-1}$ ,  $X_k \in \mathbb{Z}_q$ , given by

<sup>&</sup>lt;sup>1</sup>If  $a \in \mathbb{Z}_q$  and q are relatively prime, then we have  $1 = ab + dq \equiv ab \pmod{q}$  where b and d are integers. The integer  $b \mod q$  is then referred to as the multiplicative inverse of a under multiplication modulo q.

<sup>&</sup>lt;sup>2</sup>Thus, a field is a ring in which it is also possible to divide.

<sup>&</sup>lt;sup>3</sup>The quotient ring  $\mathbb{Z}_q$  is denoted by  $\mathbb{Z}/(q)$  and  $J_q$  in [60] and [50] respectively. The notation  $\mathbb{Z}_q$ , which we conveniently use in this thesis, is very common in many other books on abstract algebra and number theory.

$$X_k \triangleq \sum_{n=0}^{N-1} x_n \omega^{kn} \pmod{q}; \quad k = 0, 1, \dots, N-1 , \qquad (2.1)$$

where  $\omega$  is any element with order N in  $\mathbb{Z}_q$ .

The factors  $p_1, p_2, \ldots, p_k$  of q are distinct primes.

Remark: Let  $\omega$  and q be relatively prime positive integers. Then, the least positive integer N such that  $\omega^N \equiv 1 \pmod{q}$  is called the *order of*  $\omega$  *modulo* q. We denote the order of  $\omega$  modulo q by  $\operatorname{ord}_q \omega$ . Thus, for the *transform kernel*  $\omega$  we get  $\operatorname{ord}_q \omega = N$ . Sometimes,  $\omega$  is said to be a *primitive* Nth root of unity.

Because we have  $\operatorname{ord}_q \omega = N$ , the product kn in the exponent of  $\omega$  in (2.1) is calculated modulo N. It is easy to show that the NTT, as well as the DFT, possesses the cyclic convolution property, i.e. the transform of a cyclic convolution of two sequences is equal to the product of their transforms. There are also other properties of the DFT that have their counterparts in the NTT. The inverse number theoretic transform is given by

$$x_n \stackrel{\Delta}{=} N^{-1} \sum_{k=0}^{N-1} X_k \omega^{-kn} \pmod{q}; \quad n = 0, 1, \dots, N-1,$$

(2.2)

where  $N^{-1}$  is the multiplicative inverse of N modulo q, i.e. the least positive integer M for which  $N \cdot M \equiv 1 \pmod{q}$ . Such an inverse exists if and only if gcd(N, q) = 1. The factor  $\omega^{-kn}$  in (2.2) is congruent to  $\omega^{N-kn \mod N} \mod q$ . Therefore, (2.2) involves multiplication by *positive* powers of  $\omega$  modulo q.

It is sometimes convenient to use the multiplicative inverse  $\omega^{-1}$  of  $\omega$  modulo q instead of  $\omega$  as the transform kernel of the inverse NTT.<sup>4</sup> If there exists an integer  $\omega$  with order N modulo q, then its inverse  $\omega^{-1} \equiv \omega^{N-1} \pmod{q}$  also exists.

Thus, we can say that a number theoretic transform of length N and its inverse transform exist in  $\mathbb{Z}_q$  if there is an integer  $\omega$  with order N modulo q and N has a multiplicative inverse modulo q. The following theorem may be useful when determining the possible lengths of an invertible transform in an integer quotient ring:

<sup>&</sup>lt;sup>4</sup>We have  $\omega^{-kn} = (\omega^{-1})^{kn}$ .

**Theorem 2.1** There exists an invertible NTT of length N in  $\mathbb{Z}_q$  if and only if  $N \mid (p_i - 1)$  for every prime  $p_i$  that divides q.

**Proof:** See Section A.1 of Appendix A.

Thus, the theorem says that the transform length N must satisfy

$$N \mid \gcd(p_1 - 1, p_2 - 1, \dots, p_k - 1),$$

(2.3)

where  $q = p_1^{n_1} p_2^{n_2} \cdots p_k^{n_k}$ . In particular, if q = p is a prime, then every nonzero element of the *prime field*  $\mathbb{Z}_p$  has a multiplicative inverse and there exists an NTT of every length N that divides p - 1.

#### 2.2.1 Suitable Integer Rings

There exist infinitely many number theoretic transforms. The modulus  $q = p_1^{n_1} p_2^{n_2} \cdots p_k^{n_k}$  should be chosen in a suitable way with respect to the complexity and performance of the architectures for the binary coded integer arithmetic operations modulo q, and with respect to the possible NTT lengths that will be obtained. Multiplication by powers of the transform kernel  $\omega$  is usually the most complex arithmetic operation involved in the computation of the NTT. Therefore, the efficiency of a VLSI implementation of an NTT is often largely determined by the efficiency by which such multiplications can be carried out.

The direct computation of an NTT of length N requires in the order of  $N^2$  multiplications and N(N - 1) additions. If the transform length is composite the NTT can be decomposed into several transforms of smaller sizes which may be computed using some fast Fourier transform (FFT) algorithm [17, Ch. 4]. The FFT algorithm is most efficiently computed if the transform is a single-radix transform with a small radix, i.e. if the transform length can be expressed as a power of a small integer. For example, if  $N = r^b$ , for some r and b, the NTT can be computed using a *radix-r* FFT algorithm. Such an algorithm requires in the order of  $k(r-1)N \log_r N$  multiplications and  $(r-1)N \log_r N$  additions, where k depends on N and the choice of  $\omega$  [33, 35]. Hence, the complexity of computing the NTT can be significantly reduced by choosing a suitable transform length and using an FFT algorithm. From (2.3) it follows that it is the modulus that determines the possible transform lengths.

From a VLSI implementation point of view, the reduction modulo q of a binary coded integer is simplest to perform when q is close to a power of two or when the binary coded representation of q contains few ones. The modulus reduction in  $\mathbb{Z}_{2^m}$  is very simple and straightforward, but since 2 is a prime factor of

$q = 2^m$  the maximum possible NTT length in any ring of size  $2^m$  is 1. The same conclusion holds for every even modulus q. Integer quotient rings with even modulus are therefore not interesting from an NTT application point of view.

Any odd natural number q can be written on the form  $q = a \cdot r^m + 1$  for some natural numbers a, r, and m, where r does not divide a. When q is a prime, we see from (2.3) that the possible transform lengths are the ones that divide  $a \cdot r^m$ . Therefore, the maximum radix-r transform length in the prime field  $\mathbb{Z}_{a \cdot r^m+1}$  is  $r^m$ . Because a radix-r transform of length  $N = r^b$  involves in the order of  $(r-1)N \log_r N$  multiplications and additions, the transform is most efficiently computed if N is highly composite, i.e. r is small.

Chevillat gives a table [33, Tab. II] of 8-bit to 16-bit moduli whose associated integer quotient rings each contains a single-radix transform of length  $N \ge 16$ . Some of these moduli are composite, but most of them are prime numbers. The modulus should be chosen such that the modulus reduction is not a very complex operation. As an example we consider  $\mathbb{Z}_q$  with a prime modulus q = 39367, for which  $q - 1 = 2 \cdot 3^9$ . This is one of Chevillat's numbers. The maximum transform length of a single-radix NTT in  $\mathbb{Z}_{39367}$  is  $3^9 = 19683$ . However, because the normal binary representation of q = 39367 is 1001100111000111, the reduction modulo q may not be as simply performed as when q can be represented by much fewer ones or when it is closer to a power of two.

We mentioned above that multiplication by powers of the transform kernel should be carried out as simply as possible. The complexity of such a multiplication depends inter alia on the kernel chosen. However, in an arbitrary integer quotient ring there may not exist a suitable kernel for which this complexity is low. In general, even if there exist single-radix transforms of great lengths in an integer ring, it is not certain that a transform multiplication can be computed using a procedure that is simpler than general multiplication.

#### Mersenne numbers

A set of integers of particular interest is the set of *Mersenne numbers*. These numbers are of the form  $2^m - 1$ , where  $m = 2, 3, 4, \ldots$ . We denote such numbers by  $M_m$ . The NTT in a Mersenne integer quotient ring  $\mathbb{Z}_{M_m}$  is usually called the Mersenne number transform. One of the first to consider Mersenne number transforms was Rader in 1972 [77]. Arithmetic operations are easily carried out in  $\mathbb{Z}_{M_m}$  if the elements are represented as normal binary coded *m*-bit integers, because then the complexity of performing the operations equals the complexity of one's-complement arithmetic: Because  $2^m \equiv 1 \pmod{2^m - 1}$ , the modulus reduction is equivalent to the procedure for handling overflow in one's-complement arithmetic.

| m  | $M_m = 2^m - 1$ | $M_m - 1 = 2(2^{m-1} - 1)$                            |

|----|-----------------|-------------------------------------------------------|

| 3  | 7               | $2 \cdot 3$                                           |

| 5  | 31              | $2 \cdot 3 \cdot 5$                                   |

| 7  | 127             | $2 \cdot 3^2 \cdot 7$                                 |

| 13 | 8 1 9 1         | $2\cdot 3^2\cdot 5\cdot 7\cdot 13$                    |

| 17 | 131 071         | $2\cdot 3\cdot 5\cdot 17\cdot 257$                    |

| 19 | 524 287         | $2\cdot 3^3\cdot 7\cdot 19\cdot 73$                   |

| 31 | 2147483647      | $2\cdot 3^2\cdot 7\cdot 11\cdot 31\cdot 151\cdot 331$ |

**Table 2.1**: The first 7 Mersenne prime numbers.

There is, however, no general fast algorithm for the computation of the Mersenne number transform. Let  $m = \lambda k$  where  $\lambda$  is a prime number. Then  $2^{\lambda} - 1$  divides  $2^{\lambda k} - 1$ . This is easily shown by using the relation  $x^k - 1 = (x-1)(x^{k-1} + x^{k-2} + \cdots + x+1)$  for  $x = 2^{\lambda}$  which gives  $2^{\lambda k} - 1 = (2^{\lambda} - 1)(2^{\lambda(k-1)} + 2^{\lambda(k-2)} + \cdots + 2^{\lambda} + 1)$ , and thus we get  $(2^{\lambda} - 1) | (2^{\lambda k} - 1)$ . If m = 2k is even then  $2^2 - 1 = 3$  is a prime factor of  $M_m$  which, from (2.3), implies that the transform length divides 2. Thus, a transform of meaningful length can only be obtained when m is odd. Furthermore, if  $M_m = 2^m - 1$  is prime then m must also be prime, i.e. k equals 1 in the previous factorisation of  $2^{\lambda k} - 1$ . The converse, however, is not always true - for example  $2^{11} - 1 = 2047 = 23 \cdot 89$  is not a prime number. This shows, by applying (2.3) to the prime factorisation of  $M_m$ , that the possible lengths of the NTT in  $\mathbb{Z}_{M_m}$  are relatively small when m is odd and  $M_m$  is composite.

When  $M_m$  is prime the NTT length must divide  $M_m - 1 = 2^m - 2$ . The third column of Table 2.1 shows the prime factorisations of  $M_m - 1$  for the first 7 Mersenne numbers. We see that for large  $M_m$  the number  $M_m - 1$  is *not* highly composite. Therefore, there may not exist any efficient FFT-type algorithm to compute transforms of great lengths in  $\mathbb{Z}_{M_m}$ . Properties of Mersenne number transforms and some applications are further discussed in Chapter 6.3 of Blahut [17] and by Rader [77].

#### Numbers of the form $2^n - 2^m + 1$

The final set of numbers to be considered here are prime numbers of the form  $q = 2^n - 2^m + 1$ , where 0 < m < n. Several of these numbers can also be found in the set of Chevillat numbers. In 1976, Pollard [73] stated that such numbers are good choices as integer ring moduli.

The normal binary representation of the *n*-bit modulus  $q = 2^n - 2^m + 1$  is

$$\underbrace{\underbrace{11\cdots 1}_{n-m \text{ ones }} \underbrace{00\cdots 0}_{m-1 \text{ zeros}}}^{n \text{ bits}} 1,$$

i.e. a block of n - m ones followed by a block of m - 1 zeros and a one in the least significant bit position. It is quite easy to perform the modulus reduction in VLSI when the modulus has this form and if the integer to be reduced is less than  $2^n$ . Because  $2^n - 2^m + 1 \equiv 0 \pmod{2^n - 2^m + 1}$  we get  $2^n - 2^m \equiv -1 \pmod{2^n - 2^m + 1}$ . Therefore, when the n - m most significant bits of an integer not greater than  $2^n - 1$  are all ones, the modulus reduction is carried out by changing these bits to zero and subtract one (1) from the resulting binary coded integer. When the integer to be reduced is greater than  $2^n - 1$ , the modulus reduction procedure is just slightly more complicated.

**Example:** n = 8,  $m = 5 \Rightarrow q = 2^8 - 2^5 + 1 = 225$ . Modulus reduction  $235 \equiv 10 \pmod{225}$ :

|   | 11101011                           | = | 235          |

|---|------------------------------------|---|--------------|

|   | $\downarrow \downarrow \downarrow$ |   | $\downarrow$ |

|   | $0\ 0\ 0\ 0\ 1\ 0\ 1\ 1$           | = | 11           |

| — | 1                                  |   | - 1          |

|   | 00001010                           | = | 10           |

In Section 5.1.1 we show how subtraction by one can be carried out in VLSI in a simple way.

For prime moduli q, the possible transform lengths divide  $q - 1 = 2^m (2^{n-m} - 1)$ , which implies that there exist radix-2 NTTs of length  $N = 2^b$ , where  $b \le m$ , in the corresponding prime fields  $\mathbb{Z}_q$ . In Table B.1 of Appendix B we present the factorisations of q - 1 together with n, m, and q for all primes q of the form  $q = 2^n + 2^m + 1$  where  $0 < m < n \le 32$ . These primes were found by computer search. In order to obtain a transform of great length, m should be large. On the other hand, in order to make efficient use of the n-bit representation of the integers in  $\mathbb{Z}_q$ , m should be as small as possible ( $m \ge 1$ ). The best choice of m with respect to n may differ, depending on the NTT application in question.

We have not found any general structure of the prime factorisations of composite moduli  $q = 2^n - 2^m + 1 = 2^m(2^{n-m} - 1) + 1$ . However, it may be profitable to consider subsets of this set of moduli for which the NTT in the corresponding integer rings possesses some of the desirable properties. Such a subset may, for example, consist of moduli for which n - m is constant. Properties of the NTT in  $\mathbb{Z}_q$  can then be examined separately in each subset.

We see in Table B.1 of Appendix B that there are several prime moduli for which n - m is small. A report on primes of the form  $k \cdot 2^m + 1$  was published by Robinson in 1958 [83]. In [83] he also presented a table of all such primes for k < 100 and m < 512. Liu et al. [62] considered primes of the form  $2^m(2^m - 1) + 1$ , i.e. for n = 2m, for some values of m. Number theoretic transforms in the integer ring modulo  $2^m(2^m - 1) + 1$  have also been considered by Dubois and Venetsanopoulos [38, 39]. Some other researchers have investigated properties of moduli of the form  $3 \cdot 2^m + 1$ , i.e. for n - m = 2, see for example Golomb [47] and Golomb et al. [48]. In [48] the authors discuss how to perform arithmetic operations in  $\mathbb{Z}_{3\cdot 2^m+1}$ .

The above-mentioned numbers are all special cases of numbers of the form  $q^{(p-1)n} + q^{(p-2)n} + \cdots + q^n + 1 = (q^{pn} - 1)/(q^n - 1)$  for some integers q, p, and n. In a recent article by Dimitrov et al. [37], the authors define number theoretic transforms in integer quotient rings with such moduli for q = 2, p = 3, 5, and 7, and for some appropriate values of n.

In the present thesis we consider moduli  $q = 2^m(2^{n-m}-1)+1$  for n-m = 1, i.e moduli of the form  $q = 2^m + 1$ . For *m* equal to a power of two, such numbers are called *Fermat numbers*.

### 2.3 The Fermat Number Transform

#### 2.3.1 Fermat Numbers

In this section we study number theoretic transforms in integer quotient rings with moduli of the form  $2^m + 1$  for some m.

**Theorem 2.2** If  $2^m + 1$  is a prime then m is a power of two.

**Proof:** (From [42, pp. 23–24]) Suppose *m* has an odd factor *k*, say m = nk. Using the factorisation  $x^{k}+1 = (x+1)(x^{k-1}-x^{k-2}+x^{k-3}-\cdots+x^{2}-x+1)$  for  $x = 2^{n}$  we get  $2^{m}+1 = 2^{nk}+1 = (2^{n}+1)(2^{n(k-1)}-2^{n(k-2)}+2^{n(k-3)}-\cdots+2^{2n}-2^{n}+1)$ , which apparently is composite. The only numbers that have no odd factor are the powers of two. We have shown that  $2^m + 1$  is *not* a prime when *m* is *not* a power of two, but for which  $m = 2^t$  do we get a prime? The number

$$F_t \triangleq 2^m + 1; \qquad m \triangleq 2^t,$$

where  $t \in \mathbb{N}$ , is defined as the *t*th *Fermat number*.<sup>5</sup> Fermat observed that the first five such numbers are all prime:

$$\begin{split} F_0 &= 2 + 1 &= 3, \\ F_1 &= 2^2 + 1 &= 5, \\ F_2 &= 2^4 + 1 &= 17, \\ F_3 &= 2^8 + 1 &= 257, \\ F_4 &= 2^{16} + 1 &= 65\,537 \end{split}$$

Fermat expressed his belief that *every*  $F_t$  is a prime, but admitted that he had no proof.

From Fermat's little theorem [84, Th. 5.3] it follows that if p is a prime and a is a positive integer, then  $a^p \equiv a \pmod{p}$ , that is  $p \mid (a^p - a)$ . <sup>6</sup> In general, if a is a positive integer and q is a composite positive integer that divides  $a^q - a$ , then q is usually called a *pseudoprime to the base* a. One of the reasons for Fermat's statement that every  $F_t$  is a prime may have been that in fact all Fermat numbers are either primes or *pseudoprimes*.

We see that for every Fermat number  $F_t = 2^{2^t} + 1$ , where  $t \in \mathbb{N}$ , the relation  $F_t | (2^{F_t} - 2)$  holds [93, Exerc. 2]: For *any* positive integer t we have  $t + 1 \le 2^t$ , and thus  $2^{t+1} | 2^{2^t}$ . Consequently, we have  $(2^{2^{t+1}} - 1) | (2^{2^{2^t}} - 1) = 2^{F_t - 1} - 1$ . Because  $2^{2^{t+1}} - 1 = (2^{2^t} + 1)(2^{2^t} - 1)$  we get  $F_t = (2^{2^t} + 1) | (2^{F_t - 1} - 1)$  and hence  $F_t | (2^{F_t} - 2)$ .

Therefore, all composite Fermat numbers  $F_t$  are pseudoprimes to the base 2. When trying to find the factors of composite Fermat numbers, the following theorem is of good use:

<sup>&</sup>lt;sup>5</sup>Henceforth, whenever the number  $2^m + 1$  appears in the thesis we always mean the Fermat number  $F_t$ , i.e. we implicitly assume  $m = 2^t$  for some natural number t.

<sup>&</sup>lt;sup>6</sup>Even the ancient Chinese had a test for primality which is similar to Fermat's little theorem. The test said that an integer p is a prime if *and only if*  $p \mid (2^p - 2)$ . By Fermat's little theorem we know that the test is correct when p is an odd prime, but the converse is not always true. For example, the ancient Chinese did not discover that the smallest composite integer that passes their test is  $341 = 11 \cdot 31$ . It can easily be verified that  $2^{341} \equiv 2 \pmod{341}$  and thus  $341 \mid (2^{341} - 2)$ .

**Theorem 2.3** Every prime divisor of the Fermat number  $F_t = 2^{2^t} + 1$ , where  $t \ge 2$ , is of the form  $k \cdot 2^{t+2} + 1$ , for some natural number k.

**Proof:** See Section A.2 of Appendix A. The proof involves Euler's theorem and the concept of quadratic residues.  $\Box$

Thus, every prime divisor of  $F_t$  is congruent to 1 modulo  $2^{t+2}$  for  $t \ge 2$ . Actually, because the product of two numbers of the form  $k \cdot n+1$  is also of this form, *any* divisor of  $F_t$  is congruent to 1 modulo  $2^{t+2}$  for  $t \ge 2$ . Lucas [36, pp. 376–379] was the first to prove that every prime factor of  $F_t$  is of the form  $k \cdot 2^{t+2} + 1$ . Prior to Lukas' proof Euler showed that  $5 \cdot 2^7 + 1 = 641$  is a factor of  $F_5$ . The complete factorisations of  $F_5$  and  $F_6$  are

$$F_5 = (5 \cdot 2^7 + 1)(3 \cdot 17449 \cdot 2^7 + 1);$$

Euler 1732

$$F_6 = (3^2 \cdot 7 \cdot 17 \cdot 2^8 + 1)(5 \cdot 47 \cdot 373 \cdot 2998279 \cdot 2^8 + 1);$$

Landry 1880

To this day, *no Fermat prime greater than*  $F_4$  *has been found*. Since the days of Euler, finding the prime factors of composite Fermat numbers or proving that certain Fermat number *are* composite have been two of the most famous problems in number theory. In 1958, Robinson presented a list [83, Table 2] of all known prime factors of composite Fermat numbers together with the dates of discovery. Using today's powerful computing tools still more prime factors have been found. In [28, page lxxxviii], Brillhart et al. published a table of all factors of composite Fermat numbers known in 1988. To the author's knowledge, the largest Fermat number with known factorisation is  $F_{11} = 2^{2^{11}} + 1$ , which was factored by Brent and Morain in 1988 using the elliptic curve method [24], [25]. The ninth Fermat number  $F_9$  was factored by A. K. Lenstra, H. W. Lenstra Jr., M. S. Manasse, and J. M. Pollard in 1990 by means of the number field sieve [59]. The complete factorisation of  $F_{10}$  is still not known. The largest Fermat number with a known factor is  $F_{23471}$ . It is divisible by  $5 \cdot 2^{23473} + 1$ .

#### 2.3.2 The Transform Kernel

The number theoretic transform in the Fermat integer quotient ring  $\mathbb{Z}_{F_t}$  is often referred to as the Fermat number transform (FNT). A great advantage of the FNT is that the possible transform lengths are all highly composite. As shown in Section 2.3.1, a composite Fermat number  $F_t$  can be factorised into prime

powers as

$$F_t = (k_1 2^{t+2} + 1)^{n_1} (k_2 2^{t+2} + 1)^{n_2} \cdots (k_l 2^{t+2} + 1)^{n_l},$$

for some  $k_1, k_2, \ldots, k_l$  and  $n_1, n_2, \ldots, n_l$ . Let  $2^{\hat{k}}$  be a common factor of  $k_1, k_2, \ldots, k_l$  for some  $\hat{k}$ .<sup>7</sup> Equation (2.3) then implies that there exist radix-2 transforms in  $\mathbb{Z}_{F_t}$ . The transform length N must divide  $2^{t+\hat{k}+2}$ . Furthermore, when  $F_t$  is prime the possible lengths N divide  $F_t - 1 = 2^{2^t}$ . Thus, the radix-2 FNT in  $\mathbb{Z}_{F_t}$  is of length

$$N = 2^{b}; \quad \begin{cases} 0 \le b \le t + \hat{k} + 2; & F_t \text{ is composite} \\ 0 \le b \le m \ (= 2^{t}); & F_t \text{ is prime} \end{cases}$$

(2.4)

Because the FNT length N is a power of two the transform can be computed using a fast and efficient algorithm. Using the radix-2 Cooley-Tukey FFT algorithm [35], a transform of length  $N = 2^b$  in a Fermat integer quotient ring  $\mathbb{Z}_{F_t}$ can be computed using only  $(N/2) \log_2 N$  multiplications and  $N \log_2 N$  additions modulo  $F_t$ . Since elements of the sequence that is to be transformed are multiplied by powers of the kernel  $\omega$ , the complexity of computing the transform depends strongly on the choice of  $\omega$ .

Using binary arithmetic, multiplication by a power of two can be implemented in VLSI as binary shifts. We see by the congruence

$$1 = (-1)^2 \equiv 2^{2m} \pmod{2^m + 1}$$

that the integer 2 has order  $2m = 2^{t+1} \mod 2^m + 1$  and hence can be used as the kernel of an FNT of length 2m. Then, all multiplications involved in the transform computation can be carried out as binary shifts. Equation (2.4) implies that N must divide  $2^{t+\hat{k}+1}$  when  $F_t$  is composite, i.e. for t > 4. In particular it can be verified that  $\hat{k}$  is zero for  $F_5$ ,  $F_6$ , and  $F_7$ , i.e. the  $k_i$ 's in the factorisations of these numbers are all odd (see page 12 and [28, page lxxxviii]). Thus for  $F_5$ ,  $F_6$  and  $F_7$  the maximum transform length is  $2^{t+2} = 4m$ .

A suitable kernel of a 4*m*-length transform is an integer that has 2 as its square. Such an integer exists if the congruence  $x^2 \equiv 2 \pmod{F_t}$  has a solution. By the definition of quadratic residues in Section A.2, the integer 2 is then called a *quadratic residue* modulo  $F_t$ . The least positive solution *x* to the mentioned congruence is often denoted  $\sqrt{2}$  in the literature. The following theorem says that there really exists such a solution *x*.

<sup>&</sup>lt;sup>7</sup>In general, we have  $gcd(k_1, k_2, ..., k_l) = k' \cdot 2^k$  for some k' and  $\hat{k}$ , but here we are only interested in the cases when the transform length is a power of two.

**Theorem 2.4** *The integer 2 is a quadratic residue modulo each Fermat number*  $F_t$  *for*  $t \ge 2$ .

**Proof:** From the proof of Theorem 2.3, given in Section A.2, we know that the integer 2 is a quadratic residue modulo every odd prime factor  $p_i$  of the Fermat number  $F_t = p_1^{n_1} p_2^{n_2} \cdots p_k^{n_k}$  for  $t \ge 2$ . Then, 2 is also a quadratic residue modulo  $p_i^{n_i}$  (see for example Stewart, [95, Prop. A.13]). By Proposition A.10 of [95] we then get that the integer 2 is a quadratic residue modulo  $F_t$  for  $t \ge 2$ .  $\Box$

The square of the element  $\sqrt{2}$  can be expressed in the following way:

$$\left(\sqrt{2}\right)^2 = 2 = (-1) \cdot 2 \cdot (-1) \equiv -2 \cdot 2^m = 2^{\frac{m}{2}} (-1 + 1 - 2 \cdot 2^{\frac{m}{2}})$$

$$\equiv \left(2^{\frac{m}{4}}\right)^2 \left((2^{\frac{m}{2}})^2 + (-1)^2 + 2(-1 \cdot 2^{\frac{m}{2}})\right)$$

$$= \left(2^{\frac{m}{4}} (2^{\frac{m}{2}} - 1)\right)^2 \pmod{2^m + 1},$$

and thus we get

$$\sqrt{2} \equiv 2^{\frac{m}{4}} (2^{\frac{m}{2}} - 1) \equiv 2^{\frac{3m}{4}} + 2^{\frac{5m}{4}} \pmod{2^m + 1}.$$

Powers of  $\sqrt{2}$  can be written as

$$\left(\sqrt{2}\right)^{n} = \begin{cases} 2^{\frac{n}{2}}; & n \text{ even} \\ 2^{\frac{n-1}{2}}\sqrt{2} \equiv 2^{\frac{3m+2n-2}{4}} + 2^{\frac{5m+2n-2}{4}} \pmod{2^{m}+1}; & n \text{ odd} \end{cases}$$

(2.5)

which means that multiplication by powers of  $\sqrt{2}$  can be implemented in VLSI as binary shifts when the exponent n is even, and two binary shifts and one addition when the exponent is odd. This is the reason why the element  $\sqrt{2}$  is practically always used as the kernel of the FNT of length 4m in  $\mathbb{Z}_{2^m+1}$ . It can easily be shown that the order of  $\sqrt{2}$  modulo  $F_t$  is 4m for  $t \ge 2$  [2, App. C].

Because we have  $4m = 2^m = N_{\text{max}}$  for m = 4, the kernel  $\sqrt{2}$  will yield the maximum length FNT in  $\mathbb{Z}_{F_2}$ . The same kernel will also yield the maximum length FNT in  $\mathbb{Z}_{F_t}$  for t = 5, 6, and 7. However, in several applications the transform length 4m is still relatively small. In general, one-dimensional prime field FNTs of length greater than 4m require nontrivial multiplications. For a maximum length FNT ( $N = 2^m$ ) in a Fermat prime field, the transform kernel must be a *primitive element*.

| t | $m = 2^t$ | $F_t - 1 = 2^m$                     | N for $\omega = 2$ | N for $\omega = \sqrt{2}$ | N for $\omega = \alpha$ |

|---|-----------|-------------------------------------|--------------------|---------------------------|-------------------------|

| 0 | 1         | 2                                   | 2                  | —                         | —                       |

| 1 | 2         | 4                                   | 4                  | —                         | 4                       |

| 2 | 4         | 16                                  | 8                  | 16                        | 16                      |

| 3 | 8         | 256                                 | 16                 | 32                        | 256                     |

| 4 | 16        | $65\ 536$                           | 32                 | 64                        | 65 536                  |

| 5 | 32        | 4 294 967 296                       | 64                 | 128                       | —                       |

| 6 | 64        | $2^{64} \approx 1.8 \times 10^{19}$ | 128                | 256                       | —                       |

**Table 2.2:** Some parameters for the FNT. The boldfaced numbers are the maximum obtainable transform lengths. The kernel  $\alpha$  is any primitive element modulo  $F_t$ .

Every primitive element of a prime field  $\mathbb{Z}_p$  has maximum order p-1 modulo p.<sup>8</sup> In Chapter 7 we find use of the following property:

**Theorem 2.5** The integer 3 is a primitive element of each Fermat prime field  $\mathbb{Z}_{F_t}$  where  $t \geq 1$ .

Proof: See Appendix A.3.

Remark: Cunningham (see [36, page 199]) noted that for  $t \ge 2$ , the integers 3, 5, 6, 7, 10, and 12 are all primitive elements of the field of integers modulo a Fermat prime  $F_t$  for  $t \ge 2$ .

By Theorem 2.5 the maximum length FNT in a Fermat prime field can be computed using the primitive element 3 as transform kernel. Table 2.2 shows the relations between some kernels and their corresponding FNT lengths for the seven first Fermat numbers.

For each primitive element  $\alpha \in \mathbb{Z}_{2^{m+1}}$ , where  $2^{m} + 1$  is a prime, we have  $\alpha^{2^{m}} = (\alpha^{2^{m-b}})^{2^{b}} \equiv 1 \pmod{2^{m} + 1}$ . Because the order of the element  $\alpha^{2^{m-b}}$  modulo  $2^{m} + 1$  equals  $2^{b}$ , it may be chosen as the kernel of an FNT of arbitrary length  $N = 2^{b}$  for  $0 \leq b \leq m$ . This is further discussed in Section 7.2.7.

As previously mentioned, we would like to calculate the radix-2 FNT with as low complexity and high performance as possible for *every* such transform

<sup>&</sup>lt;sup>8</sup>In general, if  $\alpha$  and q > 0 are relatively prime integers such that  $\operatorname{ord}_q \alpha = \phi(q)$ , where  $\phi$  denotes Euler's totient function, then  $\alpha$  is called a *primitive root modulo* q.

length  $N = 2^b$ . Hence, we would like its approximately  $N \log_2 N$  additions together with its  $(N/2) \log_2 N$  multiplications by powers of the kernel to be carried out as simply as possible. In the present section we do not go into detail about what we mean by 'simple'. Complexity issues are further discussed in Chapter 4.

One purpose of our work is to find suitable ways of representing the binary coded integers of  $\mathbb{Z}_{2^{m}+1}$ , in order to simplify the arithmetic operations (especially multiplication by powers of the transform kernel) involved in the computation of the FNT of every possible length  $N = 2^{b}$ . We are particularly interested in the rings for which  $2^{m} + 1$  is a prime, i.e. the Fermat prime fields.

### 2.3.3 Butterfly Computations

#### The Radix-2 Decimation-In-Time Algorithm

We mentioned above that the FNT of length  $N = 2^b$  can be computed using a radix-2 FFT algorithm. When using the well known *decimation-in-time* algorithm, which is due to Cooley and Tukey [35], the FNT of the form in (2.1) is first split into two parts as follows.<sup>9</sup>

$$X_{k} \equiv \sum_{n=0}^{N-1} x_{n} \omega^{kn} = \sum_{n \text{ even}} x_{n} \omega^{kn} + \sum_{n \text{ odd}} x_{n} \omega^{kn}$$

$$= \sum_{r=0}^{N/2-1} x_{2r} \omega_{N/2}^{kr} + \omega^{k} \cdot \sum_{r=0}^{N/2-1} x_{2r+1} \omega_{N/2}^{kr}$$

$$= G_{k} + \omega^{k} \cdot H_{k} \pmod{F_{t}}, \qquad k = 0, 1, \dots, N-1,$$

where  $G_k$  and  $H_k$  are the N/2-point FNTs of the sequences  $\{x_{2r}\}_{r=0}^{N/2-1}$  and  $\{x_{2r+1}\}_{r=0}^{N/2-1}$ , respectively. The order of the kernel  $\omega_{N/2} \stackrel{\triangle}{=} \omega^2$  modulo  $F_t$  is N/2. Because  $\omega^{N/2} \equiv -1 \pmod{F_t}$  we have  $\omega^{k+N/2} \equiv -\omega^k \pmod{F_t}$  and thus the FNT can be expressed as

$$X_k \equiv G_k + \omega^k \cdot H_k \pmod{F_t}$$

$$X_{k+N/2} \equiv G_k - \omega^k \cdot H_k \pmod{F_t},$$

<sup>&</sup>lt;sup>9</sup>The derivation of the decimation-in-time FFT algorithm can be found in most books on digital signal processing, e.g. [74, Ch. 9.3.3].

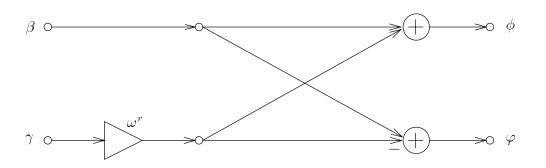

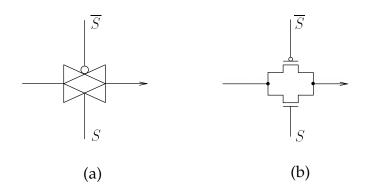

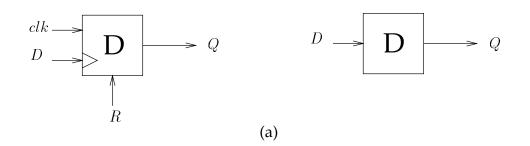

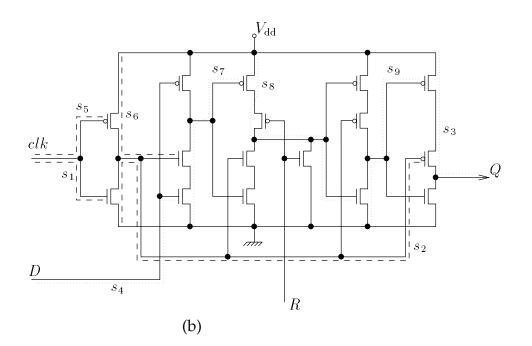

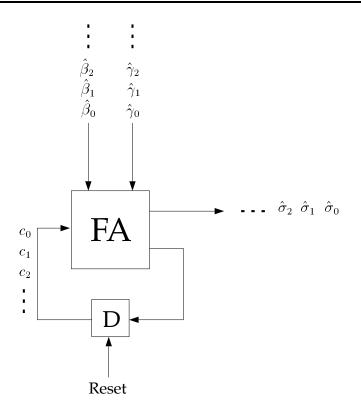

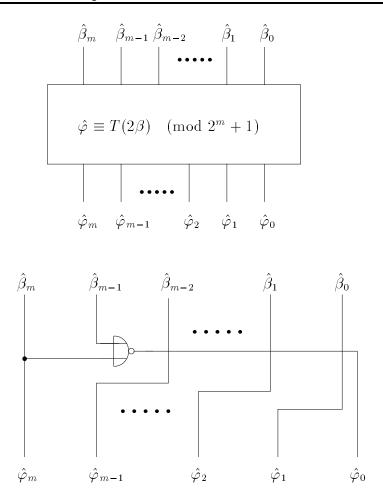

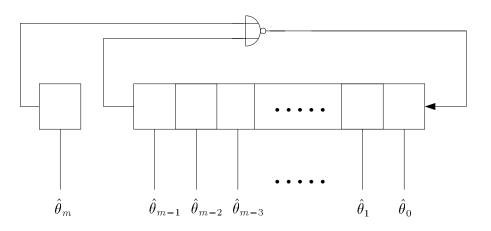

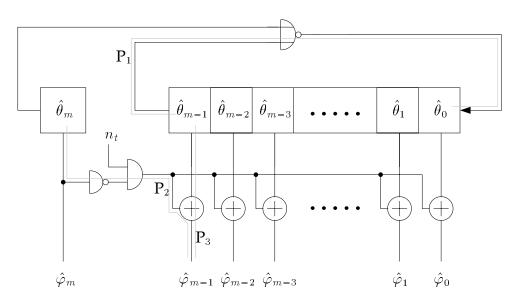

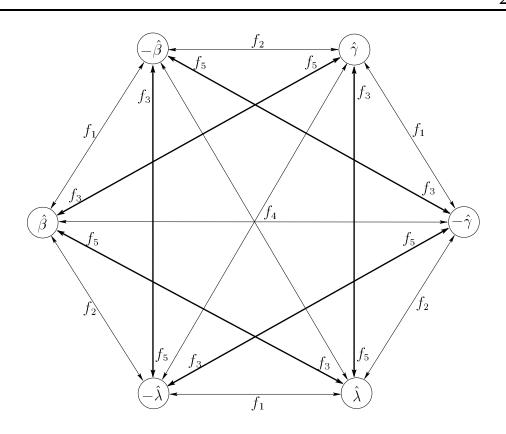

**Figure 2.1**: *Butterfly of a radix-2 decimation-in-time FFT.*

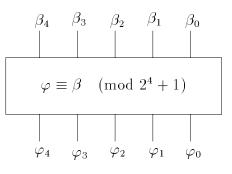

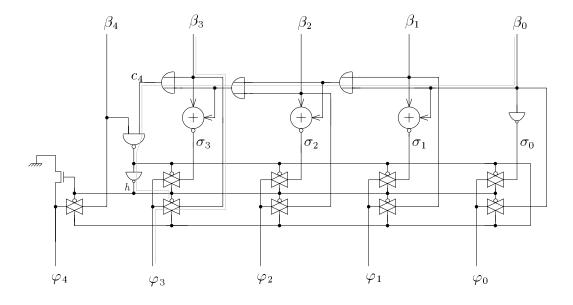

for k = 0, 1, ..., N/2 - 1. The name decimation-in-time is due to the decimation of  $x_n$  by a factor of 2. A repeated decimation of the sequences  $\{x_{2r}\}$ and  $\{x_{2r+1}\}$  will result in four N/4-point FNTs after the second step, eight N/8point FNTs after the third step and so on, until we end up in N/2 2-point FNTs after step  $\log_2 N - 1$ . Thus, the computation of the FNT of length  $N = 2^b$  may be carried out in  $\log_2 N$  stages, where each stage consists of N/2 2-point FNTs [74, Fig. 9.14]. Hence, the FNT can be computed as  $(N/2) \log_2 N = (N/2)b$  FNTs of length 2. Figure 2.1 illustrates how such a basic 2-point FNT is computed. Because of the flow graph symmetry of the 2-point transform, it is usually called a *butterfly*. The two output signals from the decimation-in-time butterfly of Figure 2.1 are

$$\phi \equiv \beta + \omega^r \gamma \pmod{F_t}$$

$$\varphi \equiv \beta - \omega^r \gamma \pmod{F_t},$$

for some r and where  $\beta$  and  $\gamma$  are the butterfly inputs. Because each butterfly involves two additions and one multiplication, the total number of additions modulo  $F_t$  equals  $N \log_2 N$  and the total number of multiplications modulo  $F_t$  equals  $(N/2) \log_2 N$ , as we have previously indicated.<sup>10</sup>

When the FFT algorithm is used for computing the ordinary DFT, the real and imaginary parts of the factors  $\omega^r = e^{-j2\pi r/N}$ , which are often called the *twiddle factors*, are usually stored in a table. This yields the fastest algorithm, to the cost of a look-up table. Concerning the FNT, by choosing a suitable kernel for the transform it may not be necessary to store the different powers of the kernel modulo  $F_t$ . For example, for  $\omega = \sqrt{2}$  and  $N = 4m = 2^{t+2}$  multiplication by powers of  $\omega$  can be carried out as two binary shifts and one addition, as mentioned in connection with (2.5). For such kernels the *b*-bit exponents *r* may be

<sup>&</sup>lt;sup>10</sup>Subtraction is regarded as addition, because it can be carried out by adding the minuend to the negated subtrahend (see Section 5.1.3).

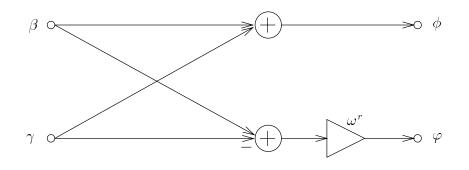

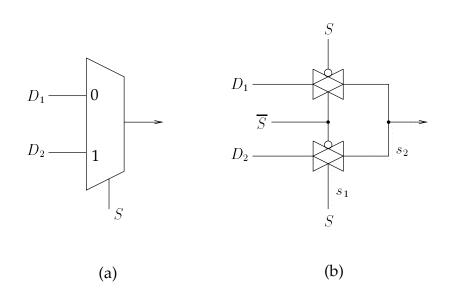

Figure 2.2: Butterfly of a radix-2 decimation-in-frequency FFT.

generated by some control logic for small transform lengths [101]. For larger transform lengths, the exponents are preferably stored in a table [90]. However, if there is no suitable kernel  $\omega$  for which multiplication by powers of  $\omega$  can be carried out simpler than the procedure for general multiplication, then we may still want a table of the twiddle factors involved in the computation of the transform.

#### The Radix-2 Decimation-In-Frequency Algorithm

When using the decimation-in-time FFT algorithm, the input sequence must appear in a bit-reversed order [74, Ch. 9.3.3]. The transformed sequence is, however, obtained in natural order. Using the radix-2 *decimation-in-frequency* FFT algorithm, we have the opposite situation. Then the input occurs in the right order while the output is obtained in bit-reversed order. The decimationin-frequency algorithm is obtained by repeatedly divide the transform into two transforms, one which depends on the first half of the sequence and the other depending on the second half of the sequence. This algorithm is due to Gentleman and Sande [45].

As for the decimation-in-time algorithm, the decimation-in-frequency algorithm also divides the *N*-length transform into  $\log_2 N$  stages of N/2 butterflies. Figure 2.2 shows the butterfly for the decimation-in-frequency algorithm.

For the butterfly input variables  $\beta$  and  $\gamma$ , we have the output variables

$$\phi \equiv \beta + \gamma \pmod{F_t}$$

and

$$\varphi \equiv (\beta - \gamma)\omega^r \pmod{F_t},$$

for some r.

The computations in both the decimation-in-time and decimation-in-frequency algorithms are done *in place*, which means that the same memory locations that hold the N elements of the sequence  $\{x_n\}$  can be used to store the results of the butterfly computations at each of the  $\log_2 N$  stages. Also, both algorithms involve  $(N/2) \log_2 N$  butterfly operations, each consisting of one multiplication by a twiddle factor and two additions. The two algorithms can be arranged such that both the input and output sequences are maintained in natural order. However, the resulting algorithms are no longer in-place algorithms, which implies that additional memory is required.

Remark: Because of the similarity between the FNT and its inverse transform, they can be computed using the same FFT algorithm. The two transforms differ only in the factor 1/N and the sign of the exponent of  $\omega$ .

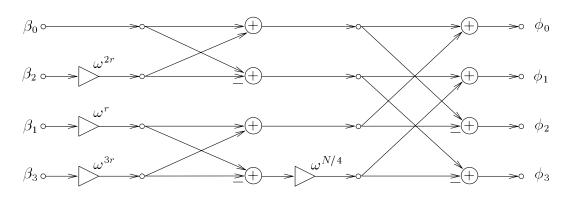

#### **Radix-4 Algorithms**

If  $b = \log_2 N$  is even we have  $N = 4^{b/2}$  and thus the transform can be computed using a radix-4 FFT algorithm. Such an algorithm can be obtained by repeatedly dividing the input sequence into four parts in a manner that is similar to the procedure for deriving a radix-2 algorithm [74, Ch. 9.3.4]. The radix-4 FFT algorithm consists of b/2 stages of N/4 butterflies. The four outputs, say  $\phi_0$ ,  $\phi_1$ ,  $\phi_2$ , and  $\phi_3$ , of a decimation-in-time butterfly can be expressed in matrix form as

$$\begin{pmatrix} \phi_0 \\ \phi_1 \\ \phi_2 \\ \phi_3 \end{pmatrix} \equiv \begin{pmatrix} 1 & 1 & 1 & 1 \\ 1 & \omega^{N/4} & (\omega^{N/4})^2 & (\omega^{N/4})^3 \\ 1 & (\omega^{N/4})^2 & (\omega^{N/4})^4 & (\omega^{N/4})^6 \\ 1 & (\omega^{N/4})^3 & (\omega^{N/4})^6 & (\omega^{N/4})^9 \end{pmatrix} \begin{pmatrix} \omega^0 \beta_0 \\ \omega^r \beta_1 \\ \omega^{2r} \beta_2 \\ \omega^{3r} \beta_3 \end{pmatrix} \pmod{F_t},$$

for some r and where  $\beta_0$ ,  $\beta_1$ ,  $\beta_2$ , and  $\beta_3$  and the four butterfly input data. Because the order of  $\omega^{N/4}$  modulo  $F_t$  is 4 we get the congruences  $(\omega^{N/4})^2 \equiv (\omega^{N/4})^6 \equiv -1 \pmod{F_t}, (\omega^{N/4})^3 \equiv -\omega^{N/4} \pmod{F_t}, (\omega^{N/4})^4 \equiv 1 \pmod{F_t},$ and  $(\omega^{N/4})^9 \equiv \omega^{N/4} \pmod{F_t}$ . In order to reduce the number of additions, the butterfly is usually derived from the following factorised twiddle-factor matrix:

$$\begin{pmatrix} 1 & 1 & 1 & 1 \\ 1 & \omega^{N/4} & \omega^{2N/4} & \omega^{3N/4} \\ 1 & \omega^{2N/4} & \omega^{4N/4} & \omega^{6N/4} \\ 1 & \omega^{3N/4} & \omega^{6N/4} & \omega^{9N/4} \end{pmatrix} \equiv$$

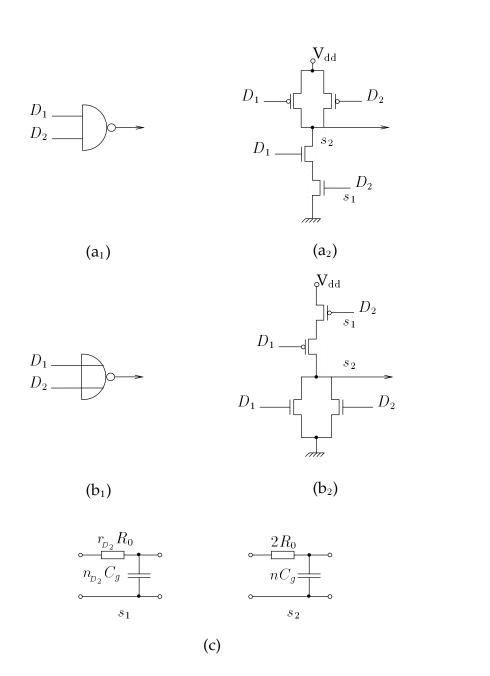

**Figure 2.3**: Butterfly of a radix-4 decimation-in-time FFT.

$$\equiv \left(\begin{array}{rrrrr} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & \omega^{N/4} \\ 1 & 0 & -1 & 0 \\ 0 & 1 & 0 & -\omega^{N/4} \end{array}\right) \left(\begin{array}{rrrr} 1 & 0 & 1 & 0 \\ 1 & 0 & -1 & 0 \\ 0 & 1 & 0 & 1 \\ 0 & 1 & 0 & -1 \end{array}\right) \pmod{F_t}.$$

A radix-4 decimation-in-time butterfly is shown in Figure 2.3. The two-stage structure of the butterfly is due to the factorisation of the twiddle-factor matrix. Note that the input is in bit-reversed order, because then the computations can be carried out in place.

For the ordinary DFT, which has kernel  $\omega = e^{-j2\pi/N}$ , we have  $\omega^{N/4} = -j$  (see [74, Eq. 9.3.44]).

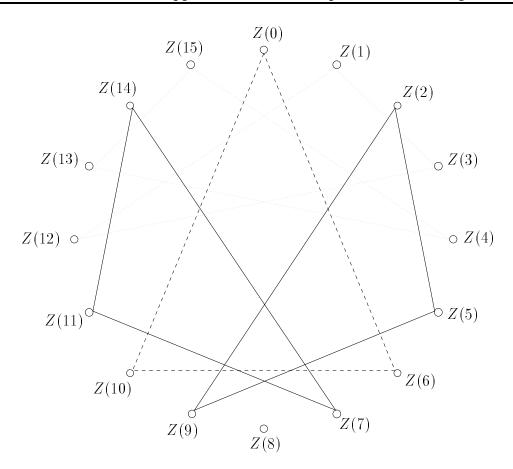

Let  $\vartheta \equiv \omega^{N/4} \pmod{F_t}$ . It can be proved that for prime  $F_t \geq 5$ , the four incongruent solutions to the congruence  $\vartheta^4 \equiv 1 \pmod{F_t}$  are  $\pm 1$  and  $\pm 2^{m/2}$ modulo  $F_t$ . By Theorem 8.8 in [84] there are  $\phi(4) = 2$  incongruent integers of order 4 modulo a prime  $F_t$ . Obviously, the integers

$$\vartheta_0 \equiv 2^{m/2} \pmod{F_t} \vartheta_1 \equiv -2^{m/2} \equiv 2^{3m/2} \pmod{F_t}$$

are these two incongruent integers. In particular, we see that for the FNTs of length N = 2m and N = 4m and with kernels  $\omega = 2$  and  $\omega \equiv \sqrt{2} \pmod{F_t}$ , respectively, we have  $\vartheta \equiv \omega^{N/4} \equiv 2^{m/2} \pmod{F_t}$ .

We showed earlier that for composite  $F_t$ , the maximum radix-2 FNT length is at least  $4m = 2^{t+2}$ .<sup>11</sup> Because the order of 2 modulo  $F_t$  is  $2m = 2^{t+1}$  it

<sup>&</sup>lt;sup>11</sup>For most composite  $F_t$  with at least one factor known, the maximum length is *exactly* 4m.

follows that for all transform lengths  $N = 2^b$ , where  $0 \le b \le t + 1$ , we have  $\operatorname{ord}_{F_t} 2^{2m/N} = N$ . Therefore, for every such transform length there exists a kernel which is a power of two.

Hence, by choosing a suitable kernel  $\omega$ , the radix-4 butterfly multiplication by  $\omega^{N/4}$  can simply be carried out as some binary shifts modulo  $F_t$  for every Fermat number  $F_t$  and every possible transform length in  $\mathbb{Z}_{F_t}$ . Therefore, using *three* general multiplications and eight additions modulo  $F_t$  per butterfly, a radix-4 FNT can be computed using  $3 \cdot (N/4) \cdot \log_4 N = (3N/8) \log_2 N$  multiplications and  $8 \cdot (N/4) \cdot \log_4 N = N \log_2 N$  additions modulo  $F_t$ .

Compared with the radix-2 FNT algorithm, the radix-4 algorithm requires 25% less multiplications but the same number of additions, i.e. we get the same complexity reduction as is obtained for the "ordinary" radix-4 DFT (see [74, Ch. 9.3.4]).

By using appropriate decimating procedures, it is also possible to define fast algorithms for radix-r transforms for r > 4. These algorithms are quite similar to the radix-2 and radix-4 algorithms, and they do not result in a significant reduction of the number of arithmetic operations. Therefore, they are not considered here.

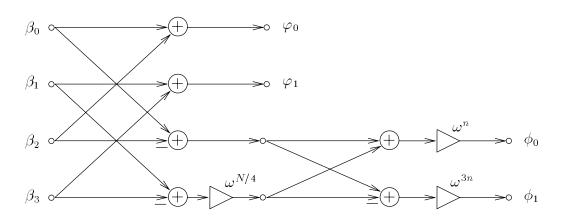

#### The Split-Radix Algorithm

The *split-radix* algorithm, which is due to Duhamel and Hollman [40], [41], is presently the most efficient radix-2 FFT algorithm. The decimation-in-frequency algorithm is derived by using a radix-2 decomposition of the even-indexed terms and a radix-4 decomposition of the odd-indexed terms. In the first stage, the even-indexed terms are inputs to a radix-2 transform of length N/2 and the odd-indexed terms are again decomposed into two sequences of length N/4, which becomes the inputs of two radix-4 transforms. The even-indexed terms are given by

$$X_{2k} \equiv \sum_{n=0}^{N/2-1} (x_n + x_{n+N/2}) \,\omega^{2kn} \pmod{F_t},$$

for k = 0, 1, ..., N/2 - 1 and the two radix-4 transforms are given by

$$X_{4k+1} \equiv \sum_{n=0}^{N/4-1} \left[ \left( x_n - x_{n+N/2} \right) + \omega^{N/4} \left( x_{n+N/4} - x_{n+3N/4} \right) \right] \omega^n \omega^{4kn}$$

and

$$X_{4k+3} \equiv \sum_{n=0}^{N/4-1} \left[ \left( x_n - x_{n+N/2} \right) - \omega^{N/4} \left( x_{n+N/4} - x_{n+3N/4} \right) \right] \omega^{3n} \omega^{4kn},$$

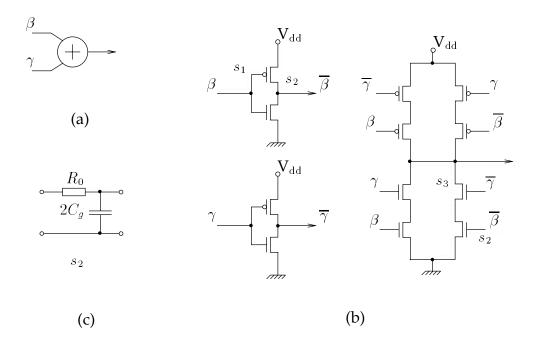

Figure 2.4: Butterfly of a split-radix decimation-in-frequency FFT.

for k = 0, 1, 2, ..., N/4 - 1 and where both congruences are reduced modulo  $F_t$ . As shown on page 21, in  $\mathbb{Z}_{F_t}$  the factor  $\omega^{N/4}$  equals some power of two. Thus, using a binary coded element representation, multiplication by  $\omega^{N/4}$  can be carried out as binary shifts modulo  $F_t$ . Figure 2.4 shows a butterfly of a split-radix decimation-in-frequency FFT.

In the first stage of the algorithm, the input variables  $\beta_0$ ,  $\beta_1$ ,  $\beta_2$ , and  $\beta_3$  are  $x_n$ ,  $x_{n+N/4}$ ,  $x_{n+N/2}$ , and  $x_{n+3N/4}$ , respectively, for some n. The output variables  $\varphi_0$  and  $\varphi_1$  are used to calculate some of the even-indexed terms of the transformed sequence, and  $\phi_0$  and  $\phi_1$  are used to calculate the terms with odd indices of the forms 4k + 1 and 4k + 3, respectively, for some k.

Because the split-radix algorithm is a kind of mixture of a radix-2 and a radix-4 FFT, it does not progress stage by stage. Therefore, the indexing will be more complicated compared with for example a fixed-radix FFT algorithm. It has been shown that a split-radix FFT can be computed using in the order of  $(N/3)\log_2 N$  multiplications and  $N\log_2 N$  additions for great transform lengths N (see for example Proakis et al. [75, Ch. 2.14] or Skodras and Constantinides [94]).

As seen above, the only arithmetic operations that are involved in the computation of the FNT and its inverse transform are addition, subtraction (i.e. negation followed by addition), multiplication by powers of the transform kernel, and multiplication by powers of two modulo  $F_t$ . In this thesis we mainly focus on these arithmetic operations and others that may be needed in connection with the transform computation. Examples of such operations are general multiplication, the discrete logarithm, and exponentiation modulo  $F_t$ . We do not care about which FFT algorithm is used (radix-2, radix-4, split-radix, or

| -         |                   |  |  |  |

|-----------|-------------------|--|--|--|

| Integer   | Normal binary     |  |  |  |

|           | coded repr.       |  |  |  |

| $2^m$     | $1000 \cdots 000$ |  |  |  |

| $2^m - 1$ | $0111 \cdots 111$ |  |  |  |

| $2^m - 2$ | $0111 \cdots 110$ |  |  |  |

| $2^m - 3$ | $0111 \cdots 101$ |  |  |  |

| •         | •                 |  |  |  |

| •         | •                 |  |  |  |

| •         | •                 |  |  |  |

| 3         | $0000 \cdots 011$ |  |  |  |

| 2         | $0000 \cdots 010$ |  |  |  |

| 1         | $0000 \cdots 001$ |  |  |  |

| 0         | 0000 · · · 0000   |  |  |  |

**Table 2.3**: The normal binary coded integer representation.

any other). We are only interested in the arithmetic operations involved in the computation of the transform.

## 2.4 Element Representation

We mentioned in Section 2.1 that we represent the elements of the Fermat integer quotient rings  $\mathbb{Z}_{2^{m}+1}$  as *binary coded integers* and use binary logic circuits in the VLSI architectures for the arithmetic operations in  $\mathbb{Z}_{2^{m}+1}$ . It is clear that m+1 bit positions are needed to represent the  $2^{m}+1$  elements of  $\mathbb{Z}_{2^{m}+1}$ . Thus, there are

$$\underbrace{2^{m+1} \cdot (2^{m+1}-1) \cdot (2^{m+1}-2) \cdots (2^m+1) \cdot 2^m}_{2^m+1 \text{ factors}} = \frac{2^{m+1}!}{(2^m-1)!}$$

different ways of representing these elements. The very well known normal binary coded representation of integers is illustrated in Table 2.3.

This representation, however, may not be the best one with respect to the complexity and performance of the VLSI architectures for arithmetic operations in  $\mathbb{Z}_{2^{m+1}}$ . Depending on how complexity and performance are defined, it may require a great effort to find the 'optimum' representation among the  $2^{m+1}!/(2^m + 1)!$  possible ones, e.g. there are about  $2 \times 10^{23}$  ways to represent the 5-bit binary coded integers of  $\mathbb{Z}_{2^{4}+1}$ . We therefore choose to restrict ourselves to consider a subset of representations that can be expressed as elementary functions of the normal binary coded representation.

The first form of representation considered is the normal binary coded representation. In Chapter 5 we study VLSI architectures for arithmetic operations using this representation. Linear coordinate transformations of the normal binary coded representation and the corresponding VLSI architectures are considered in Chapter 6. Finally, in Chapter 7 we particularly focus on the polar representation, which can be regarded as a nonlinear coordinate transformation of the normal binary coded representation.

# Applications

The Fermat number transform (FNT) is one of the most useful and powerful number theoretic transforms. As mentioned in Chapter 1, in the beginning of the 1970's the interesting properties of the FNT attracted several researches. In this chapter we describe some of the main applications of the FNT. In particular, we consider digital convolution and correlation in Fermat integer quotient rings and Reed-Solomon codes over Fermat prime fields.

There are also other applications of the FNT. Siu and Constantinides [87] have shown that the number of multiplications required to compute the discrete Fourier transform can be reduced by using number theoretic transforms. In [88] they particularly consider the FNT for reducing the complexity of computing the discrete Fourier transform. Truong et al. [102] later considered the computation of the discrete Fourier transform using the FNT in a quadratic residue Fermat number system. Several other researchers have also studied the computation of the discrete Fourier transform using number theoretic transforms.

Boussakta and Holt have shown that the discrete Hartley transform can be calculated using the FNT [20, 21]. In [22], the same authors showed how to compute the Walsh-Hadamard transform using the FNT and vice versa. Two decades ago, Rader [78] discussed number theoretic transforms for use in a block-mode image filtering scheme. A microprocessor-based architecture for block-mode image filters using the FNT was later implemented in VLSI by Shakaff et al. [90].

Boussakta et al. [23] showed that the FNT of periodic data has a regular structure with many transform components equal to zero. Any small imperfection in the periodic data significantly changes the high regularity of its FNT. As a consequence of the results in [23], the authors conclude that the FNT is highly applicable in areas like for example the detection of errors in maskmaking for integrated circuit design and defect detection in industrial inspection. They also suggest applications for image compression and data storage, where only the nonzero elements of the FNT of periodic data need to be stored together with their locations.

# 3.1 Convolution and Correlation of Real Integer Sequences

Discrete convolution and correlation are two very common operations in digital signal processing (see for example Blahut [17]). The cyclic convolution of two sequences  $\{x_n\}_{n=0}^{N-1}$  and  $\{h_n\}_{n=0}^{N-1}$  is given by the sum

$$y_n = \sum_{k=0}^{N-1} x_k h_{n-k \, (\text{mod} \, N)} \,; \qquad n = 0, 1, \dots, N-1$$

(3.1)

Correlation and convolution are computationally equivalent. The cross-correlation of two sequences  $\{x_n\}$  and  $\{h_n\}$  is obtained by convolving  $\{x_n\}$  with  $\{h_{-n}\}$ .

Like the discrete Fourier transform the FNT also has the cyclic convolution property, i.e. the transform of a cyclic convolution of two sequences is equal to the product of their transforms. Because the method of computing the convolution sum using transform calculations is often faster than the direct computation of the sum, the procedure is sometimes called *fast convolution*. The method is particularly efficient when the sequence length is highly composite, because then some FFT algorithm can be applied to compute the transform.

It is often possible – and sometimes preferable – to let computations in one algebraic field be carried out in another field, which is then usually called a *surrogate* field. Depending on the application in question, this computational procedure may also apply to rings. A computation of interest where this is applicable is convolution via transform calculations. Using a computer or a digital signal processor, these calculations are often carried out in the complex field  $\mathbb{C}$ , i.e. the discrete Fourier transform is used. However, if the sequences that are to be convolved consist of *real integers*, the convolution can instead be computed in an integer quotient ring  $\mathbb{Z}_q$ , for some suitable modulus q [2].

There are some advantages of computing the transforms in  $\mathbb{Z}_q$  rather than in the complex field: A complex multiplication requires *several* real multiplications while a multiplication in  $\mathbb{Z}_q$  is a *single* and often simpler operation (integer multiplication). The computation precision is also improved since computations in a finite ring are exact. Another very important consequence of the simplified arithmetic is that, depending on q, the complexity and performance of the hardware implementation of a transform in  $\mathbb{Z}_q$  can be smaller than the complexity and performance of the corresponding implemented transform in  $\mathbb{C}$ .

The modulus q must be chosen such that every element  $x_n$ ,  $h_n$ , and  $y_n$ , for n = 0, 1, ..., N-1, is contained in the ring  $\mathbb{Z}_q$ . Because of the congruence relation modulo q in the ring  $\mathbb{Z}_q$ , negative integers are represented as positive integers, in accordance with the congruence  $-x \equiv q - x \pmod{q}$ .

In the following example we illustrate how discrete cyclic convolution of real integers can be computed in an integer quotient ring.

**Example 3.1** If the convolution of two positive real integer sequences x and h are to be carried out in the surrogate field  $\mathbb{Z}_q$ , then the greatest integer in the convolution sum must be less than the modulus q, i.e. q must not exceed the dynamic range of  $y_n$  (and  $x_n$  and  $h_n$ ). For  $\mathbf{x} = \{4, 11, 7, 4\}$  and  $\mathbf{h} = \{9, 0, 8, 14\}$ , by (3.1) we can compute the convolution  $\mathbf{y} = \{246, 229, 151, 180\}$ . The prime modulus  $q = 257 = 2^8 + 1$  is greater than the maximum value of  $\mathbf{y}$ . Consequently, this convolution can be carried out in  $\mathbb{Z}_{2^8+1}$ . Furthermore, because the sequences involved have length 4, which divides 257 - 1 = 256, the convolution  $\mathbf{y}$  can be obtained by using FNT calculations in  $\mathbb{Z}_{2^8+1}$ .

Because the order of the integer 16 is 4 modulo  $2^8 + 1$ , it can be chosen as the kernel  $\omega$  of an FNT of length N = 4. Thus, the 4-point FNT of x is

$$X_k \equiv \sum_{n=0}^{3} x_n 16^{kn \mod 4} \pmod{257}; \quad k = 0, 1, 2, 3$$

with a similar relation for the transform of h. Using matrix notations we have

$$\begin{pmatrix} X_0 \\ X_1 \\ X_2 \\ X_3 \end{pmatrix} \equiv \begin{pmatrix} 1 & 1 & 1 & 1 \\ 1 & 16 & 256 & 241 \\ 1 & 256 & 1 & 256 \\ 1 & 241 & 256 & 16 \end{pmatrix} \begin{pmatrix} 4 \\ 11 \\ 7 \\ 4 \end{pmatrix} \equiv \begin{pmatrix} 26 \\ 109 \\ 253 \\ 142 \end{pmatrix} \pmod{257}$$

and

$$\begin{pmatrix} H_0 \\ H_1 \\ H_2 \\ H_3 \end{pmatrix} \equiv \begin{pmatrix} 31 \\ 34 \\ 3 \\ 225 \end{pmatrix} \pmod{257}$$

Each component  $Y_k$  of the FNT of y is then obtained by multiplying  $X_k$  by  $H_k$  modulo 257, which gives

$$\begin{pmatrix} Y_0 \\ Y_1 \\ Y_2 \\ Y_3 \end{pmatrix} \equiv \begin{pmatrix} 35 \\ 108 \\ 245 \\ 82 \end{pmatrix} \pmod{257}.$$

Regarding the inverse transform we need to know  $N^{-1}$  and  $\omega^{-1}$ . From the congruences  $4 \cdot 193 \equiv 1 \pmod{257}$  and  $16 \cdot 241 \equiv 1 \pmod{257}$  we get  $N^{-1} = 4^{-1} \equiv 193 \pmod{257}$  and  $\omega^{-1} = 16^{-1} \equiv 241 \pmod{257}$ , respectively. Hence, the inverse transform is

$$\begin{pmatrix} y_0 \\ y_1 \\ y_2 \\ y_3 \end{pmatrix} \equiv 193 \cdot \begin{pmatrix} 1 & 1 & 1 & 1 \\ 1 & 241 & 256 & 16 \\ 1 & 256 & 1 & 256 \\ 1 & 16 & 256 & 241 \end{pmatrix} \begin{pmatrix} 35 \\ 108 \\ 245 \\ 82 \end{pmatrix} \equiv \begin{pmatrix} 246 \\ 229 \\ 151 \\ 180 \end{pmatrix} \pmod{257},$$

which agrees with the convolution y obtained when using the conventional convolution sum in (3.1).

Let x be the input sequence of a linear time-invariant system with impulse response h. Let A be the dynamic range of  $x_n$ , i.e. we have  $|x_n| \le A$  for n = 0, 1, ..., N - 1. If  $x_n$  can take on negative numbers, the convolution sum yields

$$|y_n| \le A \sum_{k=0}^{N-1} |h_k| \le \frac{q-1}{2},$$

and thus

$$A \leq \frac{q-1}{2\sum_{k=0}^{N-1} |h_k|}.$$

If *A* is also the dynamic range of  $h_n$  and the computations are carried out in  $\mathbb{Z}_{2^m+1}$ , we get  $|h_k| \leq A$ ,  $q = 2^m + 1$ , and  $N = 2^b$ . Thus, we have

$$A \leq \sqrt{\frac{2^m + 1 - 1}{2 \cdot 2^b}} = 2^{\frac{m - b - 1}{2}}$$

| b                                         | m |        |                       |                       |          |                                  |  |  |

|-------------------------------------------|---|--------|-----------------------|-----------------------|----------|----------------------------------|--|--|

|                                           | 2 | 4      | 8                     | 16                    | 32       | 64                               |  |  |

| 1                                         | 1 | 2      | 8                     | 128                   | $2^{15}$ | $2^{31}$                         |  |  |

| 2                                         | 0 | 1      | 4                     | 64                    | $2^{14}$ | $2^{30}$                         |  |  |

| 3                                         | - | 1<br>0 | 4                     | 64                    | $2^{14}$ | $2^{30}$                         |  |  |

| 4                                         | - | 0      | 2                     | 32                    | $2^{13}$ | $2^{30}$<br>$2^{30}$<br>$2^{29}$ |  |  |

| 5                                         | - | _      | 2                     | 32                    | $2^{13}$ | $2^{29}$                         |  |  |

| 6                                         | - | _      | 1                     | 16                    | $2^{12}$ | $2^{28}$                         |  |  |

| 7                                         | - | -      | 4<br>2<br>1<br>1<br>0 | 16                    | $2^{12}$ | $2^{28}$                         |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | - | _      | 0                     | 8                     | _        | $2^{27}$                         |  |  |

| 9                                         | - | _      | _                     | 8                     | _        | —                                |  |  |

| 10                                        | - | _      | _                     | 4                     | -        | -                                |  |  |

| 11                                        | - | _      | -                     | 4                     | _        | -                                |  |  |

| 12                                        | - | -      | -                     | 2                     | _        | -                                |  |  |

| 13                                        | - | _      | -                     | 4<br>2<br>1<br>1<br>0 | —        | —                                |  |  |

| 14                                        | - | -      | -                     | 1                     | _        | -                                |  |  |

| 15                                        | - | _      | -                     | 1                     | —        | —                                |  |  |

| 16                                        | - | _      | -                     | 0                     | _        | -                                |  |  |

**Table 3.1:** The dynamic range of  $x_n$  and  $h_n$ , for which the corresponding sequences are of length  $N = 2^b$ . In  $\mathbb{Z}_{2^m+1}$  we have  $0 \le b \le m$  for m = 1, 2, 4, 8, and 16, and  $2^b \le 4m$  for m = 32 and m = 64.

which implies that the maximum dynamic range is

$$A = \lfloor 2^{\frac{m-b-1}{2}} \rfloor,$$

i.e. the greatest integer less than or equal to  $2^{(m-b-1)/2}$ . Table 3.1 shows the dynamic range of  $x_n$  and  $h_n$  for some values of m and b. Because of the relatively poor dynamic range for small m, digital filtering of real integer sequences is generally considered to be applicable primarily for  $m \ge 32$ .

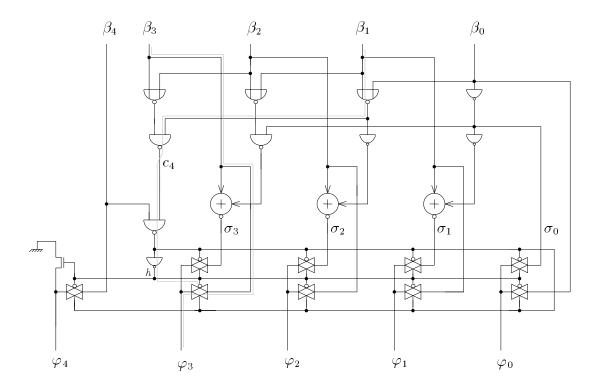

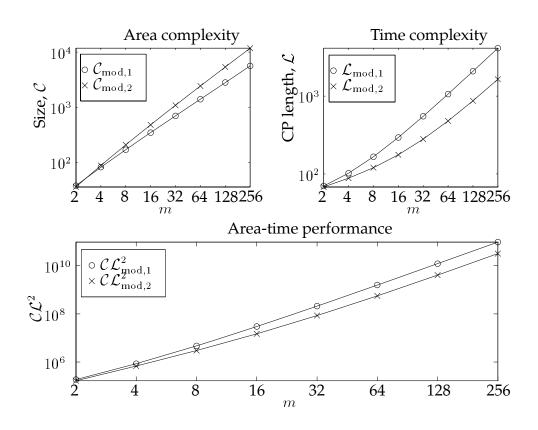

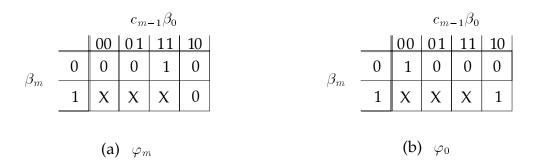

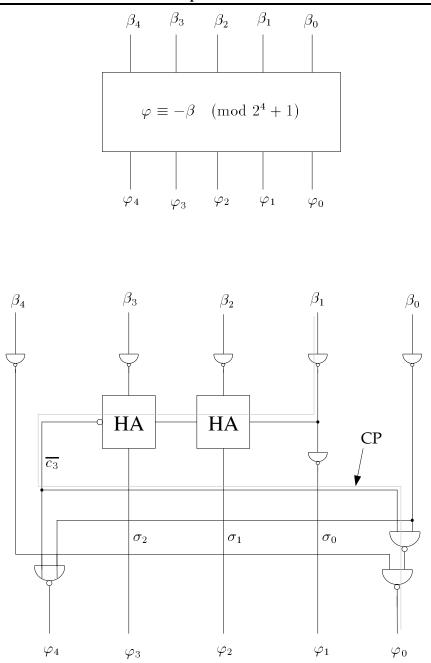

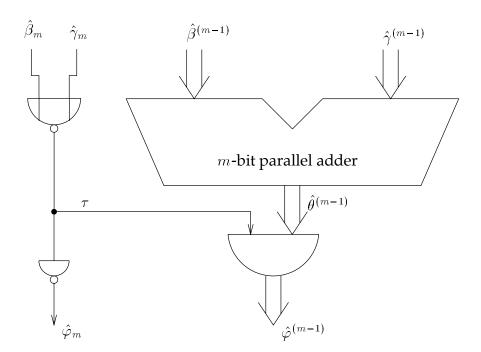

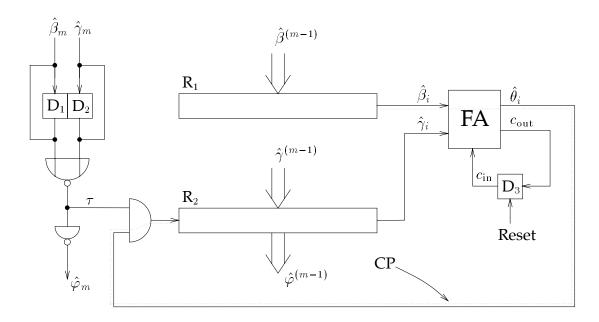

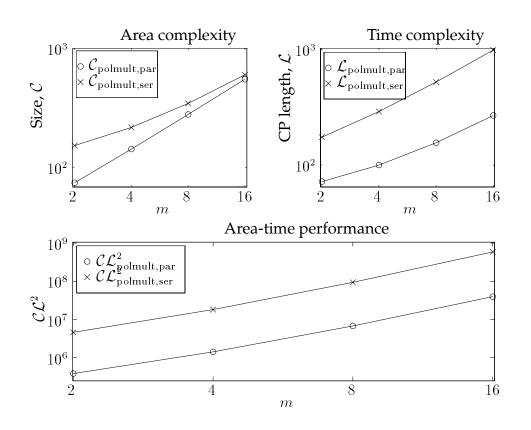

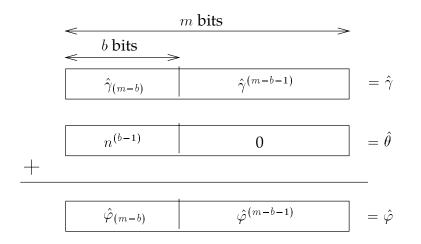

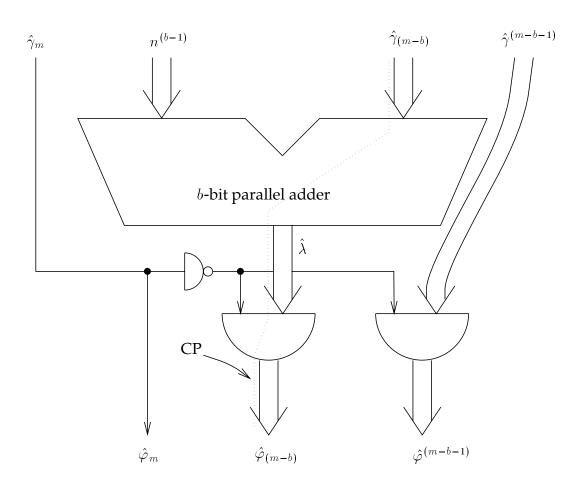

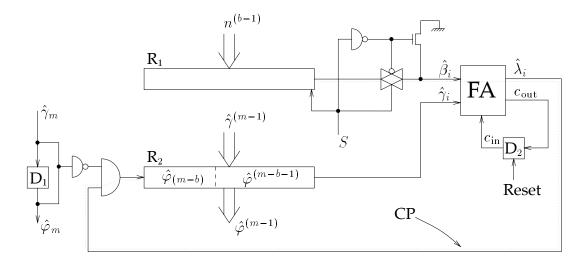

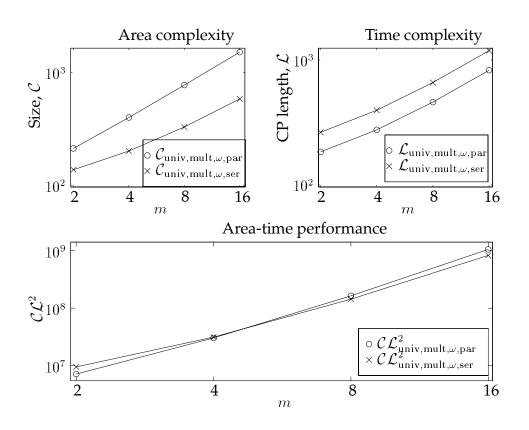

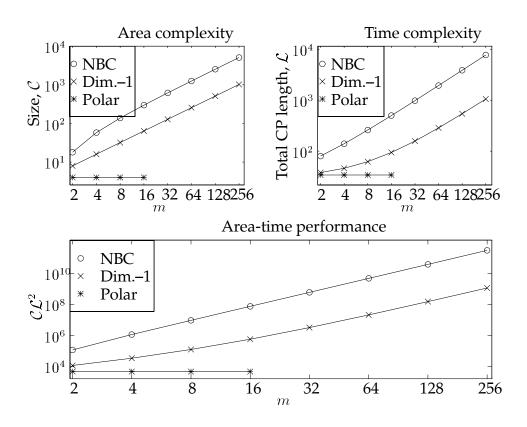

A common situation in filtering applications is the filtering of a relatively long sequence by an FIR filter of much shorter length. This involves a linear convolution of great length which can be impractical to compute. There exist, however, two well known techniques that simplify the computation of great-length linear convolutions: Using the *overlap-add method* or the *overlap-save method*, the longer sequence is sectioned into shorter length subsequences that are cyclically convolved with the impulse response [79, Ch. 2.25]. Truong et al. [103, 107] have devised a general overlap-save method for filters of arbitrary length using the Fermat number transform.